**POLITECNICO DI TORINO**

Master Degree Course in Electronic Engineering

Master Degree Thesis

**Design and Evaluation of

Reconfigurable Systolic Arrays for

Neural Networks**

**Politecnico

di Torino**

**Advisors**

Prof. Mario Roberto CASU

Dr. Edward MANCA

**Candidate**

Sergio Ivano FIERRO

ACADEMIC YEAR 2024-2025

# Summary

In recent years, Deep Neural Networks (DNNs) have achieved unprecedented accuracy across a wide range of tasks. These gains, however, come with substantial increases in model complexity and per-inference computational cost. As a result, deploying DNNs presents new challenges, and devising efficient methods to execute their computations has become a central concern in research. Modern DNN workloads comprise many nested loops, with Multiply-and-Accumulate (MAC) operations dominating. In this context, Systolic Arrays (SAs) have emerged as an architecture that connects and coordinates large numbers of Processing Elements (PEs) operating in parallel. Usually, SAs are composed of PEs that communicate only with their direct neighbors. This neighbor-to-neighbor connectivity allows them to have low fan-out connections. Moreover, SAs supports dataflow organizations that enable operand reuse, and relax the back-pressure to the memory to feed the PEs with new values. Finally, their regular structure aligns well with lightweight control units, usually composed by counters. All these properties make them a good choice to compute the kernels of DNNs such as matrix multiplication and convolution. On the other hand, both the shape of the array — i.e., the number of elements along rows and columns — and the dataflow scheme the array is designed for — namely Output Stationary (OS), Weight Stationary (WS), or Input Stationary (IS) — have a significant impact on computational efficiency. Each combination of shape and dataflow determines a computation strategy that better fits a given algorithm and a different design point in the latency, silicon area, and power consumption analysis. The goal of this thesis is to explore and design reconfigurable SAs that support multiple shapes and/or multiple dataflows. To this end, I explored the design space given by SAs with different shapes and dataflows, over a class of selected DNN kernels - i.e. convolutions, linear, and attention layers. For each configuration I verified the correctness with RTL simulation tools. Moreover, I collected the number of clock cycles needed by the SA to complete the computation, and I synthesized them on a 28 nm digital library to also collect latency, silicon area, and power consumption results. Overall, these data allowed me to rank the various shapes and dataflows on an efficiency metric of OPC/mW, and to select the most efficient SA configurations. Once the best configurations have been selected, I designed and verified a reconfigurable SA supporting more than one

configuration in the same design. Since the number of configurations to support directly influence the overhead coming from the reconfigurability, I explored architectures that implements two/three configurations at most in the same SA. This design has been simulated and synthesized on the same 28 nm technology library to validate its efficiency with the same OPC/mW metric. The study demonstrates the importance of architectural choices in the SA design process and proposes a path to have more efficient reconfigurable SAs that can optimally execute more than one DNN algorithm with the same SA structure. Looking forward, this approach may serve as a foundation to study and efficiently compute the algorithms of novel DNN layers, leveraging run-time reconfiguration.

# Acknowledgements

I would like to sincerely thank Professor Mario Roberto Casu and Dr. Edward Manca, without whose expert and constant guidance this work would not have been possible. Also, a special acknowledgment goes to the entire research group whose availability, competence and constructive support provided a solid foundation for the development of this thesis.

I want to thank my family, whose constant support and encouragement not only made possible this academic journey but has always accompanied me at every stage of my life. Particularly, I am grateful to my brother, whose presence and constant support, even from afar, have been of inestimable value, especially during the most challenging times.

I am also deeply beholden to my significant other for her profound understanding, continuous encouragement, and for the meticulous contribution, especially for revising this manuscript, which improved its clarity and overall cohesion.

Finally, I would like to thank all my friends, whose constant presence and support accompanied me throughout my university journey, making it lighter, richer, and unforgettable.

# Contents

|          |                                                                                               |           |

|----------|-----------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                                           | <b>1</b>  |

| 1.1      | Deep Learning Evolution and Efficiency Challenges . . . . .                                   | 1         |

| 1.1.1    | Evolution of deep learning . . . . .                                                          | 1         |

| 1.1.2    | Increase in model complexity . . . . .                                                        | 2         |

| 1.1.3    | Computational and energy inefficiency in training and inference                               | 3         |

| 1.2      | Contribution and Thesis Objectives . . . . .                                                  | 4         |

| 1.3      | Thesis Outline . . . . .                                                                      | 5         |

| <b>2</b> | <b>Conventional Systolic Arrays</b>                                                           | <b>7</b>  |

| 2.1      | Systolic Array Fundamentals . . . . .                                                         | 7         |

| 2.1.1    | Operating principles and general architecture . . . . .                                       | 7         |

| 2.1.2    | Key concepts: data reuse, spatial and temporal loops . . . . .                                | 9         |

| 2.1.3    | Analysis of different dataflows . . . . .                                                     | 11        |

| 2.2      | State of the Art in SA Architectures . . . . .                                                | 14        |

| <b>3</b> | <b>Efficiency of Conventional SAs in executing NNs</b>                                        | <b>23</b> |

| 3.1      | Mapping Neural Networks to Systolic Arrays . . . . .                                          | 23        |

| 3.1.1    | Fully-Connected Layers . . . . .                                                              | 24        |

| 3.1.2    | Convolutions (CNN) - GEMM via im2col . . . . .                                                | 27        |

| 3.1.3    | Transformer and Self-Attention . . . . .                                                      | 30        |

| 3.2      | Evaluation Methodology . . . . .                                                              | 33        |

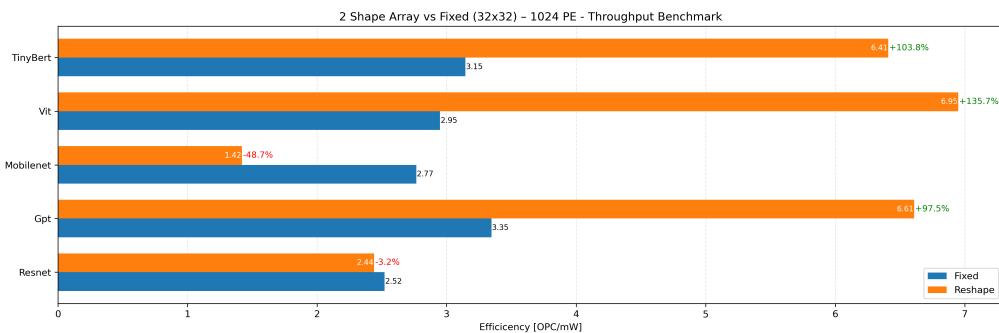

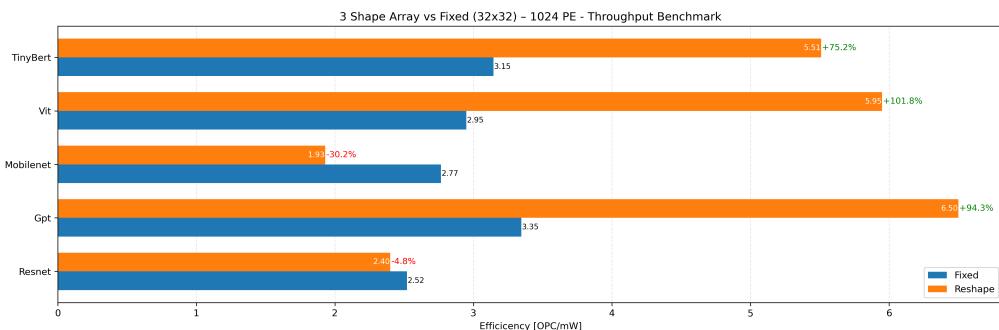

| 3.2.1    | Performance estimation method . . . . .                                                       | 33        |

| 3.3      | Performance Results . . . . .                                                                 | 37        |

| 3.4      | Discussion . . . . .                                                                          | 51        |

| <b>4</b> | <b>Proposed Reconfigurable Systolic Array Architecture</b>                                    | <b>53</b> |

| 4.1      | Design Goals and Specifications . . . . .                                                     | 53        |

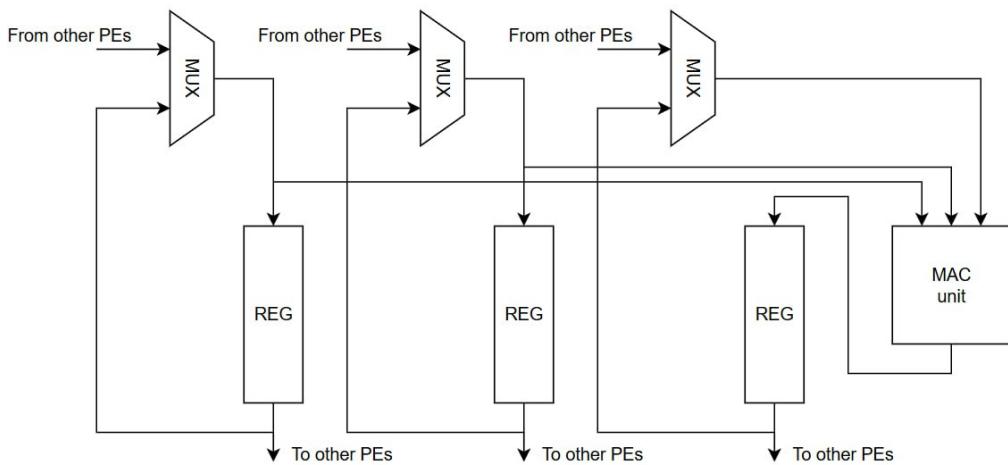

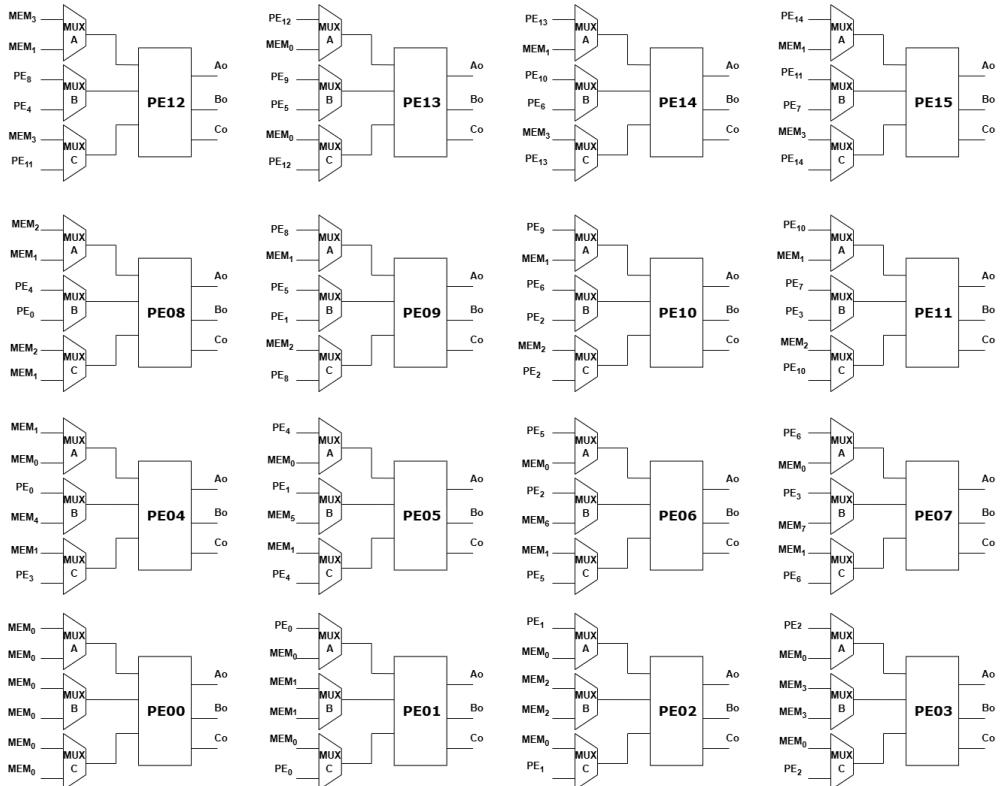

| 4.2      | Processing Element (PE) Design . . . . .                                                      | 54        |

| 4.3      | Reconfiguration Mechanism . . . . .                                                           | 56        |

| 4.4      | Performance Results . . . . .                                                                 | 58        |

| 4.4.1    | Methodology for data computation and reason behind the selection of comparison shape. . . . . | 58        |

|                        |                                         |    |

|------------------------|-----------------------------------------|----|

| 4.4.2                  | Synthesis and Resource-Overhead Results | 60 |

| <b>5</b>               | <b>Conclusions and Future Work</b>      | 65 |

| 5.1                    | Conclusion                              | 65 |

| 5.2                    | Future Work                             | 66 |

| <b>List of Figures</b> |                                         | 69 |

# Chapter 1

## Introduction

### 1.1 Deep Learning Evolution and Efficiency Challenges

#### 1.1.1 Evolution of deep learning

With the advent of the digital age, much of the data that was once accessible only in an “analog” form has been transferred to and made available on digital systems. In particular, today—considering the enormous amount of information produced, processed, and stored in scientific, industrial, and research contexts—we increasingly speak of a true “era of big data.”

Consequently, traditional tools for the analysis and manipulation of collected information have had to evolve. It is within this context that Neural Network Learning emerged — a system designed to emulate the behavior of the human brain. When comparing a machine and a brain in terms of data storage and access, their differences are immediately clear: the human brain (which can roughly be compared to a computer’s CPU) does not have a central memory unit where information is saved and later retrieved (as occurs in a computer’s hard drive). Instead, the brain creates connections among accessible data, allowing it to retrieve past information through associative processes. The goal, in this regard, has always been to replicate such behavior in machines, avoiding the creation of massive, slow, and difficult-to-access data repositories.

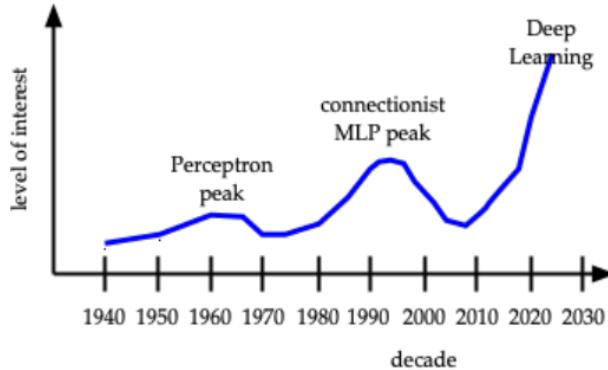

**Figure 1.1:** Three wave of neural network research[1].

This way of envisioning machines as networks of interconnected neurons has actually existed in research much longer beyond anything one could imagine. As reported in various studies, neural network learning has gone through three main waves of research activity. This trend is clear in Figure 1.1: the first wave dates back to the 1960s, with *Frank Rosenblatt*'s "Perceptron" [2], the first supervised learning algorithm capable of classifying linear patterns, *Bernard Widrow* and *Marcian Hoff*'s "MADALINE" [3], which introduced for the first time a multilayer network based on adaptive learning rules — laying the foundation for future neural architectures.

The second wave started in the 1980s, when *John Hopfield* showed that recurrent neural networks could address NP-hard combinatorial optimization problems . Around the same time, the introduction of the backpropagation algorithm made it possible to effectively train multilayer networks, sparking renewed interest in deep learning research

Finally, the third and most significant wave is the one we are experiencing today. It began around 2012, when deep convolutional neural networks were first used for image classification [4]. The fundamental difference between the early neural networks and those designed for deep learning lies in the number of hidden layers, i.e., the computational layers between the input and output nodes. In recent years, deep learning—thanks especially to its ability to process and learn from much larger volumes of data than previous systems—has become the reference paradigm within the field of machine learning.

### 1.1.2 Increase in model complexity

In recent years, the field of deep learning has experienced rapid growth not only in terms of application adoption but also—and above all—in the size and complexity

of the models used. This evolution is justified by the empirical scaling laws, which show that increases in the number of parameters, the amount of training data, and the available computational resources lead to better performance. At the same time, there is a human drive to tackle increasingly complex tasks (such as computer vision and natural language processing) that require models capable of generating ever richer and more abstract representations.

A clear example is represented by language models—for instance, GPT-2 and related architectures—which have demonstrated that the generalization error (i.e., how well a learning model performs on unseen data) decreases according to a power law as the model size, training data, and computational budget grow. These studies [5] suggest that, to improve model quality, one of the most effective strategies is simply to scale up: more parameters, more data, and more computation.

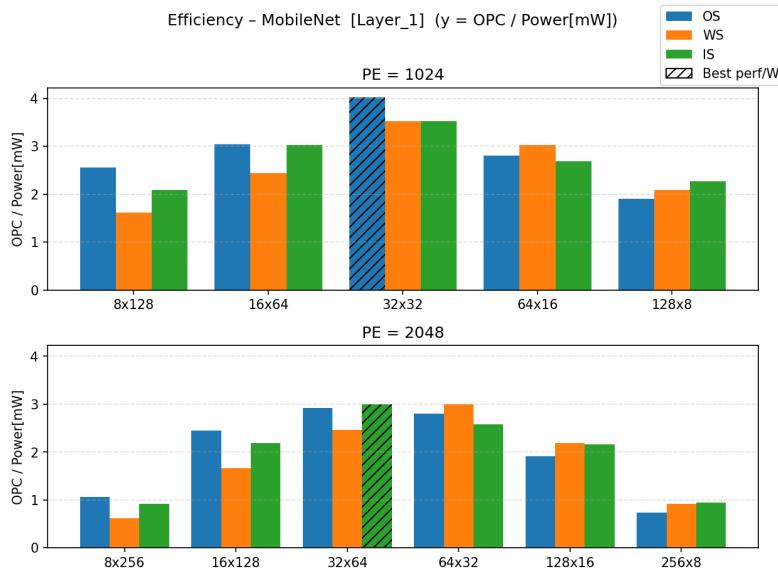

In practice, models such as ResNet (Residual Networks) used in computer vision architectures, or attention-based models like Transformers used in natural language processing, have become extremely deep or contain billions of parameters. This design is motivated by the need for models capable of robustly understanding entities, relationships, and contexts in complex tasks such as image recognition, machine translation, or text generation. In this sense, model complexity is regarded as a necessary means to achieve the desired performance leap.

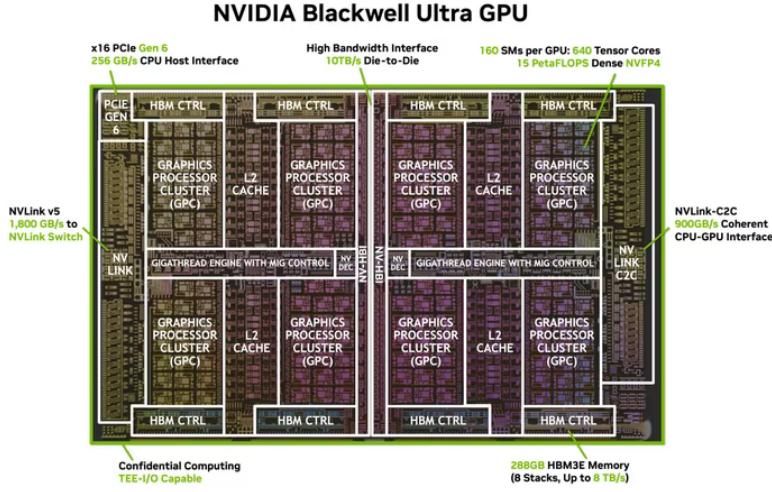

Two key factors have enabled the evolution of neural networks in this direction: the exponential increase in available data and the rapid development of specialized hardware (GPUs, TPUs, accelerators, systolic arrays, FPGAs), which can now train increasingly dense networks on a daily basis. As a result, large-scale models are today the rule rather than the exception in cutting-edge research. For instance, it has been estimated that the computational requirements of certain language models have increased by several orders of magnitude in just a few years—according to a recent analysis, by approximately  $300,000\times$  between 2012 and 2018 [6].

In summary, the growing complexity and scale of deep learning models stem from two main factors. On one side, the abundance of data, advances in hardware, and improved design expertise drive the development of larger architectures. On the other, empirical scaling laws and the quest for emergent capabilities make increasing model size more beneficial than focusing just on architectural improvements.

### 1.1.3 Computational and energy inefficiency in training and inference

Such progress has led to a significant increase in the resources required — both in terms of computational power and energy consumption — during both the training phase, in which the model processes large amounts of data to learn its parameters, and the inference phase, in which the already trained model is employed to generate predictions or decisions on new inputs. Both stages share a fundamental characteristic: the need to perform an extremely high number of mathematical

operations, mainly multiplications and accumulations (MAC, Multiplication and Accumulation), whose volume grows proportionally with the model’s complexity and depth.

During these operations, activations, weights and gradients must be continuously read from and written to memory with a constant exchange of information between different cache levels, main memory and compute arrays. These data flows entail considerable energy expenditure, not only for the arithmetic operations themselves but also for memory transfers and synchronization among the various hardware units. Overall efficiency therefore depends not only on the algorithmic design of the model but also on the hardware’s ability to manage these operations efficiently, minimizing waste due to latency or redundancy.

From this perspective, hardware efficiency emerges as a critical factor. Although modern GPUs and specialized accelerators provide remarkable computational power for artificial intelligence tasks, they also entail significant energy demands, particularly during prolonged use or when training large-scale models.

Energy consumption during the inference phase should not be underestimated either, considering that these models are now used daily by millions of users. The study by Patterson et al.(2021) [7] shows that, for certain large-scale models, the total energy consumption resulting from distributed inference can even exceed that required for the initial training, particularly in contexts where the model is executed millions of times per day.

In summary, the issue of efficiency — both computational and energetic — represents one of the major challenges in neural network engineering today. It concerns not only the speed at which a model can be trained or deployed, but also directly affects the overall sustainability of the field and the possibility of making artificial intelligence a truly scalable, accessible, and responsible technology.

## 1.2 Contribution and Thesis Objectives

This thesis lies within the context of hardware accelerator design for Deep Neural Networks (DNNs), with a particular focus on architectural efficiency and execution flexibility. In recent years, the prevailing approach has been to design dedicated hardware optimized for the execution of a single algorithm, aiming to achieve the lowest possible latency and power consumption. However, it is often necessary to handle layers that exhibit very different computational characteristics — not only between the training and inference phases, but sometimes even within the same network, depending on the specific operation being executed at a given time step.

This exposes the fundamental problem that this work aims to address: it is not feasible to rely on a fixed hardware architecture that remains optimal under all possible conditions.

In this context, Systolic Arrays (SAs) have emerged as a highly regular and scalable computational paradigm, particularly well-suited for the execution of massively

parallel workloads [8]. SAs differ from one another in terms of the organization and dataflow of their Processing Elements (PEs). At the same time, these very design choices — which define their operational flexibility — also represent their main limitation. Indeed, both the shape of the array and the dataflow scheme are fixed at design time. Since different classes of layers within the same neural network exhibit different computational patterns and reuse characteristics, one must select a single architectural configuration that represents a reasonable compromise across all layers, rather than the optimal solution for each individual case.

The scenario described above forms the starting point for this work, whose goal is to explore, in terms of area and power, the existing design space of systolic architectures and to propose a new approach based on architectural reconfigurability. The core idea is to enable the array to dynamically adjust its shape and dataflow in order to adapt to the computational requirements of the currently executed layer. In this way, by incurring only a modest area overhead (due to the additional reconfiguration circuitry), it becomes possible to balance power consumption and latency, achieving improved performance or energy efficiency depending on the desired operating point.

The main contribution of this thesis unfolds along two complementary directions. First, a systematic performance study was conducted to establish a solid reference design to be used for comparison with the proposed architecture. Several SA configurations were analyzed, varying both the shape and the dataflow, and their impact was evaluated across a representative set of neural network workloads. Second, a Systolic Array capable of supporting multiple shapes within a single hardware design was implemented and verified. The architecture is equipped with a control mechanism that could, in principle, modify dynamically — even during the execution of a single layer — to the configuration that offers the best performance or energy trade-off.

Through this approach, the thesis aims to provide a general design and evaluation methodology applicable to a wide range of systolic accelerators, laying the groundwork for future research toward dynamic and adaptive architectures for efficient neural network computation.

## 1.3 Thesis Outline

The present thesis is organized as follows.

**Chapter 2** provides the theoretical and architectural foundations required to understand the design decisions made in this work. It outlines the fundamental concepts of Deep Neural Networks (DNNs), detailing their core computational operations and data reuse patterns. The discussion then shifts to Systolic Array architectures, explaining their operating principles, the various dataflow strategies, and the key design trade-offs involving performance, area, and power consumption

**Chapter 3** describes the design space exploration conducted on different configurations of Systolic Arrays. Several architectures with varying shapes and dataflows are analyzed and evaluated in terms of performance, area, and energy consumption. The results of this analysis are discussed to identify the configurations that achieve the highest efficiency according to a performance metric defined as "Operations Per Cycle" per Watt (OPC/W). In addition, a short discussion is included on how neural networks can be mapped and executed on Systolic Arrays, and why these architectures are particularly suitable for efficiently running such algorithms.

**Chapter 4** presents the design and implementation of the proposed reconfigurable Systolic Array architecture, capable of supporting multiple shapes within the same hardware design. The architectural modifications required to support multiple configurations are described, along with the approach adopted to activate each configuration and to assess its impact in terms of area and power consumption. Furthermore, this chapter reports the experimental evaluation of the reconfigurable architecture, followed by an analysis of the proposed design and a comparison with the fixed-shape Systolic Arrays introduced in the previous chapters, highlighting the results obtained in terms of efficiency and flexibility. The reported data refers to different neural network workloads, using as basis for comparison the number of clock cycles, silicon area, and power consumption.

**Chapter 5** reviews what has been achieved in this thesis, drawing attention to the main contributions. The discussion also looks ahead, suggesting how some of the ideas developed here could evolve into future applications or be explored under different design constraints.

# Chapter 2

# Conventional Systolic Arrays

The following chapter aims to explain the fundamental concepts necessary to justify and understand some of the design choices made during the experimental phase concerning the systolic architecture.

The first part introduces the operating principles, structure, and characteristics that make Systolic Arrays (SAs) particularly well suited for parallel computation, and, in this sense, for efficiently executing the algorithms at the core of neural networks.

The second part, on the other hand, provides an overview of the architectures available in the current state of the art, with the goal of contextualizing the evolution of SAs in the field of hardware acceleration for deep learning and identifying the existing solutions that inspired some of the design decisions presented in this thesis.

## 2.1 Systolic Array Fundamentals

### 2.1.1 Operating principles and general architecture

The concept of Systolic Arrays was first introduced by *Kung* and *Leiserson* in 1979 [8]. Their proposal described an architecture designed to achieve the highest possible degree of parallelism by exploiting a regular and highly organized structure composed of a number  $N$  of Processing Elements, referred to as PEs.

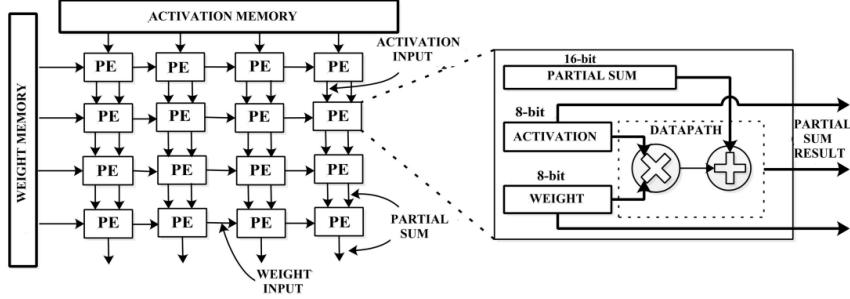

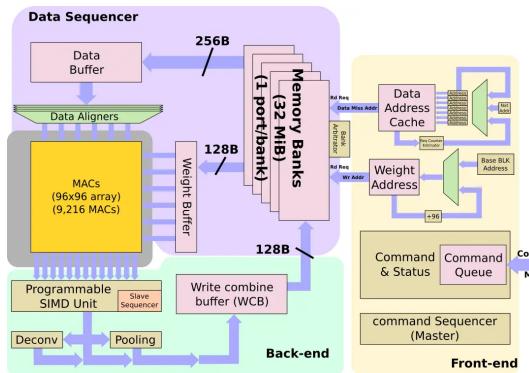

**Figure 2.1:** Implemented TPU’s Systolic Array model[9].

The term *systolic* was chosen by *Kung* and *Leiserson* by analogy with the functioning of the human circulatory system. In the heart, during the systole phase, blood is pumped in a rhythmic and coordinated way through a network of vessels. Similarly, in a Systolic Array (SA), data flows through a network of Processing Elements following a regular and synchronized rhythm.

A systolic array is essentially a two-dimensional grid of PEs interconnected with one another. Since this architecture is not limited to a specific application domain, the internal behavior of the PEs may vary depending on the computational task the array is meant to perform. In the case analyzed here, each PE mainly performs Multiply-and-Accumulate (MAC) operations. In the baseline architecture studied by *Kung* and *Leiserson*, the PEs communicate only with their direct neighbors. This local communication reduces interconnection complexity and allows data to propagate through the array in a deterministic and deeply pipelined manner.

The operation of a systolic array can be easily understood by analyzing how matrix multiplication (MAT-MUL) can be mapped onto such an architecture. In this scenario, one of the matrices (e.g., A) is transmitted into the array from left to right, while the other matrix (e.g., B) is injected from the bottom and propagated vertically. Each PE—assuming, as in this case, that it performs MAC operations—computes a partial product and forwards it to the next PE, which adds it to its own result. As computation proceeds, partial sums move diagonally across the array until they reach the upper-right corner, where the final results are produced. This example highlights the key characteristics of Systolic Arrays:

- **Regularity:** structure is composed of identical PEs connected periodically.

- **Locality:** short and predictable interconnections between elements.

- **Parallelism:** many operations are performed simultaneously.

These properties make systolic architectures particularly suitable for compute-intensive tasks such as matrix multiplications, convolutions, and other linear algebra kernels that form the core of modern Deep Neural Networks (DNNs).

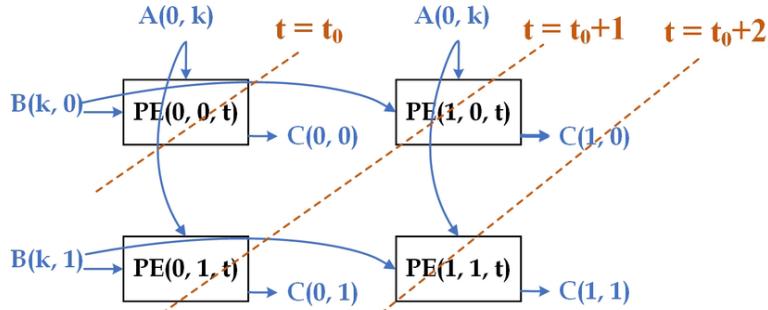

### 2.1.2 Key concepts: data reuse, spatial and temporal loops

One of the greatest advantages of systolic architectures is their ability to exploit, in an extremely efficient way, the data reuse properties that characterize Machine Learning (ML) algorithms. On the other hand the main bottlenecks in high-performance computing systems is the latency introduced by the countless accesses to the outer memory layers – generally slower than the processing system itself. Systolic Arrays (SAs) are designed to minimize the number of read–write cycles to external memories by ensuring that the same operands are reused multiple times within the array.

This efficient data reuse is made possible by the regular and synchronized propagation of information among the various PEs. Assuming that the PE at position  $(x, y)$  within the computation matrix needs, at time  $t+1$ , the same data  $d$  it had at time  $t$ , one can imagine that  $d$  does not move to its neighbor but instead circulates back to itself, thereby avoiding a second memory access.

In the context of systolic arrays, it is in fact possible to identify two distinct types of reuse: spatial and temporal.

- **Temporal reuse** occurs when data fetched by a PE is used by itself in the next clock cycles .

- **Spatial reuse** occurs when data fetched by a PE are transferred to neighbor PEs to be reused in the next clock cycles.

**Figure 2.2:** Spatial-temporal mapping onto a systolic array with its data access and data reuse.[10]

Properties shown in Figure 2.2 prove very useful when mapping ML algorithms, since the fundamental operations that compose such algorithms — and in particular deep neural networks (DNNs, CNNs, Transformers, etc.) — can be represented as a set of nested loops. These loops, which iterate over the dimensions of the input tensors, the weights, and the output features, describe how the data required for computation can be reused within the array. Furthermore, they algorithmically define the entire computational process: for each output element, sums and products

are performed by iterating over the internal dimensions.

For example, a matrix multiplication — at the heart of many operations in ML models — can be formalized as:

$$C_{i,j} = \sum_{k=0}^{K-1} A_{i,k} \times B_{k,j} \quad (2.1)$$

that, in pseudo-code, is equal to three nested loop:

---

**Algorithm 1** Matrix Multiplication (Nested Loops Representation)

---

```

1: for  $i = 0$  to  $M - 1$  do                                 $\triangleright$  Rows of  $A$  and  $C$

2:   for  $j = 0$  to  $N - 1$  do                       $\triangleright$  Columns of  $B$  and  $C$

3:      $C[i][j] \leftarrow 0$

4:     for  $k = 0$  to  $K - 1$  do                   $\triangleright$  Inner dimension loop

5:        $C[i][j] \leftarrow C[i][j] + A[i][k] \times B[k][j]$

6:     end for

7:   end for

8: end for

```

---

In the same way, convolutions in Convolutional Neural Networks (CNNs) or attention mechanisms in Transformers can be described as more complex loop structures, yet always based on the same principle. From the nested loops that describe matrix multiplication, which are directly mapped into hardware, it is possible to distinguish:

- **Spatial loops:** they represent operations that are executed simultaneously by different PEs, exploiting the parallelism of the array by distributing operations along the physical dimensions.

- **Temporal loops:** they represent operations that, over time, are executed by the same PE. In fact, each clock cycle introduces new input data, while the previous ones move to the subsequent PEs.

Returning to the example of matrix multiplication execution, each element of matrix A is transmitted horizontally along a row, while the elements of matrix B move vertically along a column. This means that a single element of A can be used by all PEs in the same row, and an element of B by all those in the same column. This scheme achieves extremely efficient spatial reuse and temporal reuse. An additional advantage is that the entire computation process takes place under very simple local control: each PE is governed by counters or regular synchronization signals, without the need for a centralized control unit or complex scheduling logic. This structural simplicity makes Systolic Arrays particularly scalable, both in terms of grid size and operating frequency. In the context of Deep Neural Networks (DNNs), this property becomes crucial.

### 2.1.3 Analysis of different dataflows

The execution time and efficiency of a Systolic Array (SA) in performing a given algorithm do not depend only on the number of Processing Elements (PEs) and their spatial organization, but also — and above all — on the logic underlying the interconnections, that is, on how data are moved and utilized within the structure.

From this, it is possible to introduce the concept of “dataflow,” which refers to the strategy through which operands and intermediate results move within the array. In a Machine Learning algorithm, three different types of data can be distinguished: inputs, weights, offsets, and outputs, which, by drawing a correspondence with the previously discussed MAT-MUL case, correspond - respectively - to A, B, and C.

The dataflow simply specifies which of these data are kept stationary within the PEs and which, instead, are circulated among them. It is worth noting that these three data types necessarily have different bitwidths, and depending on how the layer is mapped onto the SA, the various dataflows may require a different number of memory accesses, that can negatively influence execution efficiency in terms of latency and power. In real systems, the choice of dataflow is closely related to the type of layer being accelerated, since each algorithm exhibits different data reuse patterns. The three most common types — widely employed in architectures designed for deep neural network acceleration — are:

- Output-Stationary (OS)

- Weight-Stationary (WS)

- Input-Stationary (IS)

#### Output-Stationary (OS)

In the Output-Stationary case, the partial results are kept locally within the PEs until the computation is completed. Inputs and weights, on the other hand, flow among the various nodes, contributing to the accumulation of the final result. Mathematically, the operation can be described as:

$$P_{(i,j)}^{(t+1)} = P_{(i,j)}^{(t)} + A_{(i,k)}^{(t)} \cdot W_{(k,j)}^{(t)} \quad (2.2)$$

In this case,  $(C_{(i,j)})$  (the partial output) remains stationary within the PE until the computation of the entire element of the output matrix is completed. Only once the accumulation is finished the result is written to external memory. This approach minimizes the traffic of partial sums (in terms of bitwidth are the most significant), since only the final result leaves the corresponding PE. This type of dataflow is particularly suitable for Fully Connected (FC) layers — in these layers the number of weights is large and the final result depends on many intermediate products.

The OS case is also the simplest to implement, since it does not require diagonal paths for the propagation of partial sums: each PE locally manages its own accumulation. Therefore, the OS scheme significantly reduces the internal traffic of intermediate results and is particularly well-suited for highly dense layers, but it loses efficiency in the case of small computations.

**Figure 2.3:** Systolic Array - Output-Stationary (OS) configuration[11]

### Weight-Stationary (WS)

In the Weight-Stationary dataflow, the layer weights are preloaded and kept fixed within the PEs for the entire duration of the computation. Inputs (activations) and partial sums, instead, flow horizontally and vertically across the grid, interacting with the locally stored weights. Formally, each PE( $(i,j)$ ) performs the operation:

$$P_{(i,j)}^{(t+1)} = P_{(i,j)}^{(t)} + A_{(i,k)}^{(t)} \cdot W_{(k,j)} \quad (2.3)$$

where:

- $(W_{(k,j)})$  is the weight kept fixed inside the PE

- $(A_{(i,k)}^{(t)})$  represents the input flowing horizontally

- $(P_{(i,j)}^{(t)})$  is the partial sum accumulated over time.

The key benefit of this approach is the maximization of weight reuse: each weight element ( $W_{(k,j)}$ ) can serve multiple input values without requiring repeated reads from external memory. This substantially reduces the energy expenditure linked to weight retrievals, which can constitute a considerable fraction of the overall power consumption in these systems

In this architectures, each PE contains a small local memory (often just a simple register) - for WS dataflow used to store weights -, which are loaded only once per input batch. The WS approach proves particularly advantageous when each filter (i.e., a subset of weights) is reused to compute multiple “regions” of the input tensor. The drawback, on the other hand, is the intrinsic need to constantly move partial sums, which considerably increases internal data traffic.

**Figure 2.4:** Systolic Array - Weight-Stationary (WS) configuration[11]

### Input-Stationary (IS)

In the Input-Stationary dataflow, the input data remain fixed within the PEs, while the weights and partial sums are propagated across the array. The operation performed by each PE can be represented as:

$$P_{(i,j)}^{(t+1)} = P_{(i,j)}^{(t)} + A_{(i,k)} \cdot W_{(k,j)}^{(t)} \quad (2.4)$$

In this scheme, each input element ( $A_{(i,k)}$ ) is reused for multiple combinations of weights, thus maximizing its spatial and temporal reuse. The result is a reduced

number of input memory reads, which can be beneficial in terms of energy consumption.

The IS approach is beneficial whenever the same input is involved in generating multiple outputs, as seen in convolutional layers or attention blocks in Transformer models. However, this also results in increased bandwidth demands for weight transfers, since weights must be repeatedly transmitted across the computation array.

**Figure 2.5:** Systolic Array - Input-Stationary (IS) configuration[11]

## 2.2 State of the Art in SA Architectures

In recent years, Systolic Arrays have become one of the most widely adopted architectural models — both in industry and academia — when discussing accelerators for neural networks. Their widespread use is not only the result of the simplicity of the architecture — originate from the regularity of computation and the straightforward dataflow, as discussed in previous sections — but, above all, due to their versatility. As observed in recent years, SAs adapt very well to the increasingly diverse range of modern DNNs, which feature layers with different numerical and dimensional characteristics. Today, with the evolution of the systolic paradigm, designers are progressively moving away from the traditional square shape and fixed dataflow, techniques that are making SAs extremely efficient systems.

The most recent studies on these architectures have shown that their success is closely tied to the ease with which these systems scale. SAs can be replicated,

aggregated, and/or organized into subgroups, forming very large computation matrices while still maintaining predictable behavior and a highly localized communication pattern. These characteristics make them ideal for optimization in terms of throughput per  $mm^2$  (crucial aspect in advanced technology nodes).

The adoption of these systems in industrial accelerators has raised the emergence of increasingly specialized variants. Asymmetric arrays have been introduced to match the shapes and sizes of matrices typical of Transformers, and pod-based structures have been designed to improve horizontal scalability. There is also a growing integration of systolic pipelines within GPU-like architectures, and increasingly often, support for multiple numerical formats is provided. This variety of configurations demonstrates that the SA model is no longer bound to its historical form, but is instead becoming a building block that designers can customize according to constraints on area, bandwidth, and data reuse.

Very often, such accelerators are designed with the premise that the computational part is less restrictive than the data-movement model, for this reason they are adopted in data-heavy context like NN computation. In fact, the modularity of systolic arrays facilitates pairing with dedicated buffers and in some of the most modern architectural solutions, the shape of the array is designed based on available bandwidth rather than the opposite, as was common in older systems.

Considering all these aspects, the role of systolic arrays in modern architectures is no longer limited to the regular computation of matrix products. These systems are becoming a flexible paradigm that can be reinterpreted in various ways to respond to the increasing complexity of deep learning models. The following sections will explore how these solutions have materialized in industrial and academic applications, highlighting the differences among the various approaches currently available on the market.

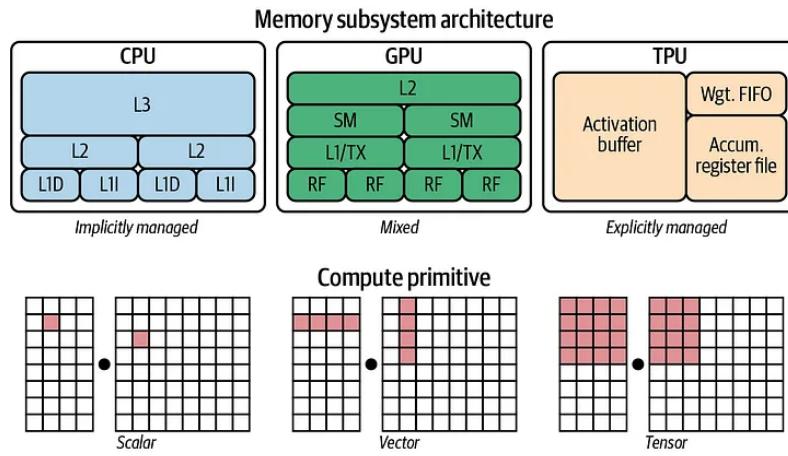

### Differences between SA and GPU-based computation

In the domain of neural-network accelerators, systolic arrays are often compared to GPUs, which today represent the reference platform for training and inference of most existing models. Both architectures aim for massive parallelism, but they differ substantially in the way data is managed, and these differences impact performance, efficiency, and predictability.

Figure 2.6: CUDA Cores - NVIDIA GPU[12]

GPUs (Figure 2.6) are general-purpose systems designed to maximize throughput by exploiting a very large number of independent cores. In these systems, operations are split into thousands of threads, each dynamically scheduled according to resource availability. Such a system is extremely flexible, allowing GPUs to be used in a wide range of fields. However, this flexibility comes at a cost: the control structure, the memory system, and the complex interconnection fabric must sustain a high level of concurrency across computing units. The result is an extremely powerful architecture, but one with a significant energy cost.

SAs, on the other hand, follow a fundamentally different approach. Computation is not divided into independent threads but is distributed across a network of identical units. Data flows through the PEs, which compute a partial result and propagate it to the next node. This organization eliminates the need for complex control and drastically reduces dependence on external memory thanks to the high reusability of operands at the local level. The consequence is clear: the ratio between energy consumed and operations performed is far more favorable, making this architecture ideal where efficiency is a fundamental requirement.

Another significant difference lies in temporal predictability. In GPU-based systems, data latency can vary substantially depending on core saturation and the state of the memory system supporting the compute units. In systolic arrays, the dataflow is evaluable regardless of external conditions, allowing the global computation latency to be determined in advance—an essential feature in real-time or embedded systems where timing stability is a strict requirement.

Finally, while GPUs rely heavily on processing large batches in parallel — experiencing notable efficiency loss when required workloads are small — systolic arrays maintain stable performance even on significantly smaller batch sizes, since their efficiency depends on the match between the shape of the array and the matrices being processed. This peculiarity makes them particularly suitable for inference

workloads, where memory systems are a major limitation (especially for large batch sizes).

In TPUs[13], for example, the systolic array becomes the structure that concentrates the computational capability, while the rest of the chip is organized to continuously feed it with weights and activations. This model has significantly contributed to the widespread adoption of SAs in subsequent designs, demonstrating how a highly specialized implementation can outperform general-purpose solutions in terms of energy efficiency and throughput predictability.

**Figure 2.7: CPU vs GPU vs TPU[14]**

Overall, even though GPUs and SAs are often directly compared, they represent two complementary solution spaces. The former are designed to maximize flexibility and raw computational power, while the latter focus on efficiency and predictability. For this reason, the current state of the art shows an increasingly tight integration between these models. It is not uncommon to find GPU-based systems that incorporate systolic elements, as well as SAs that inherit configuration features typical of general-purpose GPUs.

### SA based architecture - Google TPU v1-v3

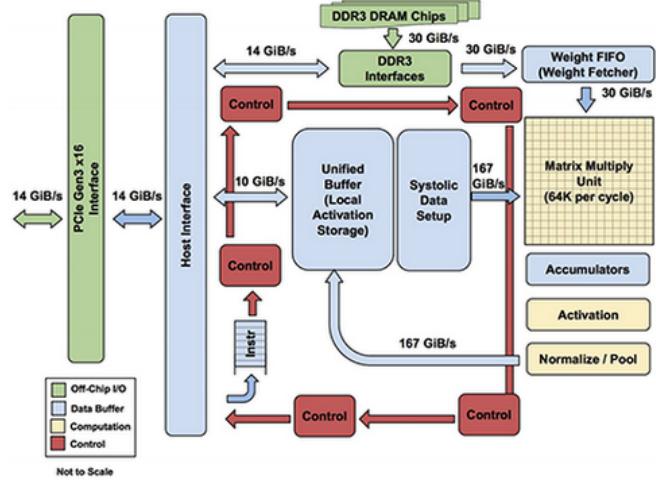

The first generation of TPU developed by Google represents one of the most significant cases in which a systolic array has been employed on a large scale in an industrial product. In the official technical blog[13], Google describes the TPU v1 as an accelerator built “around a systolic array” (Figure 2.8) and specifies that the computational core of the chip is a  $256 \times 256$  matrix of 8-bit MAC units, for a total of 65,536 multiply-accumulate operations per cycle. The array operates at a frequency of 700 MHz, achieving a theoretical throughput of approximately 92 Tera-MAC/s (value computed as  $65,536 \times 700$  MHz).

**Figure 2.8:** Internal MXU structure - Google TPU v1[13].

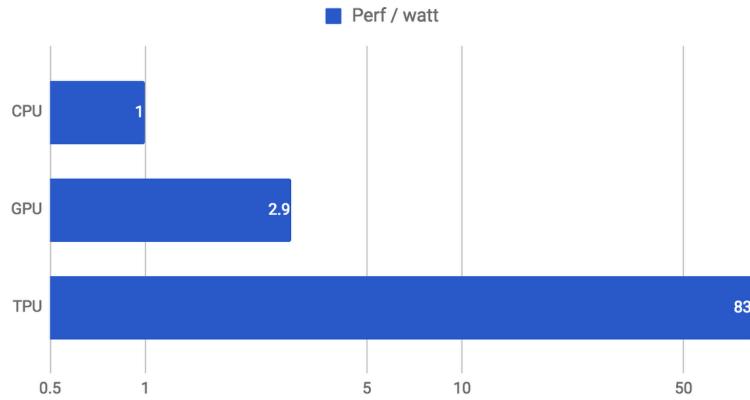

The chip, fabricated in 28 nm CMOS, consumes approximately 40 W, placing it in a very favorable energy-efficiency regime compared to contemporary CPU and GPU solutions. According to data published by Google, TPU v1 achieved improvements from 15 $\times$  to 30 $\times$  in absolute performance and from 30 $\times$  to 80 $\times$  in performance per watt compared to the general-purpose processors of the time (Figure 2.9).

**Figure 2.9:** Performance comparison between TPU v1, CPU and GPU on different workloads[13].

Dataflow within the chip is an important aspect of understanding the systolic array's role. As pointed out by Google, once the weights are loaded into the MXU matrix, they are reused locally during the whole duration of the operation without any further access to external memory. This fully aligns with the systolic paradigm:

computation progresses by “streaming” operands through adjacent nodes to reduce heavy data movement and minimize dependence on off-chip bandwidth. The fact that the TPU uses a PCIe Gen3  $\times 16$  link providing only 12.5 GB/s bandwidth also shows that the architecture is designed under the assumption of high internal data reuse.

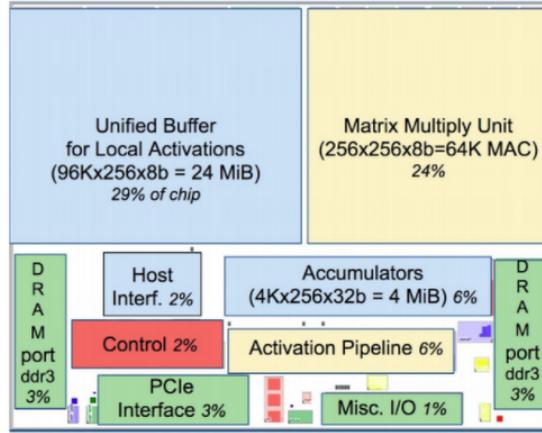

**Figure 2.10:** Google TPU v1 internal floorplan[13].

Another feature that characterizes the TPU v1 is the simplicity of its control logic. According to their datas, the internal control circuitry occupies less than 2% of the die area (Figure 2.10), with most of the silicon dedicated to pure computation, and is designed to support an extremely regular dataflow without sophisticated scheduling structures or parallelism-management mechanisms. That is one of the key differences with a GPU, in which much of the complexity arises from co-ordinating thousands of independent threads. The performance results validate the approach: for real latency, Google reports speedups up to  $71\times$  over reference CPUs on convolutional workloads (CNN1), besides more predictable temporal behavior. The systolic structure enables not only high throughput but also more predictable execution times, a key feature for distributed inference systems and large-scale cloud services.

### Tesla FSD (Full Self-Driving) Chip

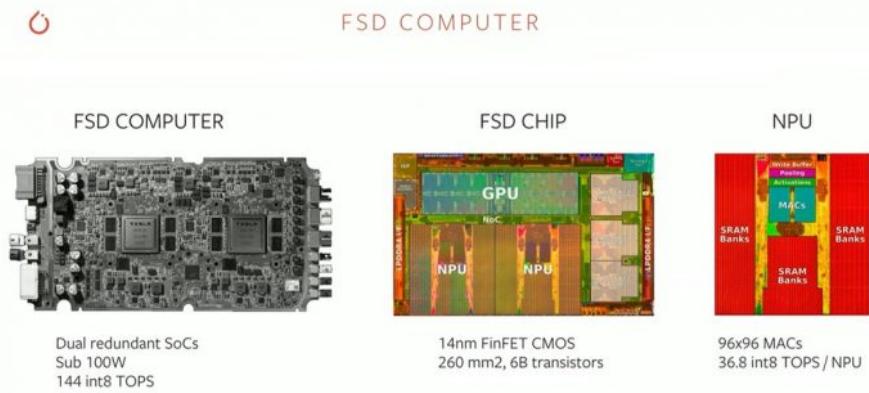

The Tesla FSD (Full Self-Driving) Chip introduced with the “HW 3.0” platform represents one of the most important industrial implementations of an architecture specifically devoted to real-time neural network execution. The device is designed specifically to meet automotive constraints that require predictable latencies, a low power consumption, and a highly regular computation flow. Inside the chip, there are two neural processing units (NPUs), each integrating a  $96 \times 96$  array of MAC units optimized for 8-bit operations with 32-bit accumulation. According to the

technical analysis reported by WikiChip Fuse[15], this structure allows each NPU to reach a theoretical throughput of about 36 TOPS.

**Figure 2.11:** Tesla FSD chip[16].

A particularly relevant feature for comparison with systolic arrays is the way the  $96 \times 96$  array is fed. In the FSD chip's NPUs, the 32 MiB local memory is subdivided into numerous independent banks and can sustain up to 256 bytes of activations and 128 bytes of weights per cycle. This corresponds to a maximum bandwidth of about 786 GB/s—a value that is necessary both to keep the utilization rate of the MAC array high and to reduce access to external DRAM[15]. This physical proximity between the array and the local buffer is a fundamental architectural element and reflects one of the main features of systolic arrays: reduction of the “distance of data movement,” which is essential for keeping energy consumption under control.

**Figure 2.12:** Tesla FSD chip internal floorplan[13].

From an internal organization point of view, the dataflow of Tesla's array is

not formally described as a classical systolic pipeline; it exhibits similar characteristics since data is delivered to the elements of the array according to regular patterns by using horizontal and vertical broadcast mechanisms and propagation paths that maximize operand reuse[15]. Due to this regularity of data movement, together with the grid topology, Tesla’s NPU gets closer to the behavior of systolic arrays, although there are some operational differences driven by the necessity of supporting highly heterogeneous network models and real-time tasks.

It can also be perceived that the FSD chip is part of a much larger system including a general-purpose processor, video controllers, and high-speed interfaces. These NPUs are utilized as dedicated engines for the heavy steps of inference using a pipeline devised to ensure consistent latency. The architectural approach here shows that, even in application domains quite different from training and datacenter-scale workloads, the use of regular and predictable arrays remains an effective strategy for high throughput and deterministic behavior. The Tesla FSD Chip is an interesting example of such an industrial accelerator because it adopts a large MAC array, a substantial local memory hierarchy, and regular dataflows-elements that clearly put it into the same conceptual family as systolic arrays, even if it does not follow the classical formulation exactly.

## Where this thesis takes place?

As it clearly comes out from the survey of the analyzed architectures, regular structures for accelerating neural-network workloads represent an established choice both in industrial and academic domains. Solutions such as Google’s TPU v1, Tesla FSD Chip and other similar projects share a computation strongly organized around MAC units arranged in regular grids, fed by local memory hierarchies optimized to maximize data reuse. These examples clearly illustrate the effectiveness of the systolic — or systolic-like — approach when the workload is dominated by dense and repetitive operations.

At the same time, these architectures share a common trait: while being extremely effective in a specific domain of application, the systolic array shape and dataflow remain essentially fixed. Solutions presented here tend to prefer regular structures deeply optimized for specific use scenarios, leaving little room for dynamically changing the array structure, data propagation mode, or PEs internal organization. This design choice — totally coherent with an industrial goal of predictability and maximum efficiency — on the other hand reduces their possibility to adapt to models that have various geometric requirements or to kernels that present less regular structures and dependencies.

It is in this framework that the present work finds its place, investigating the possibility of designing reconfigurable systolic arrays capable of changing their shape or data flow in order to adapt to more types of operations and a wider range of layers. It is not intended to supplant the existing architectures but to propose an

alternative that brings more flexibility within the same paradigm. This research takes a complementary approach with respect to what has been done so far: identifying reconfigurability as a potential answer to increasing model heterogeneity in deep learning while preserving the advantages of regularity, predictability, and locality that made systolic arrays one of the most robust and efficient solutions for neural computation.

# Chapter 3

## Efficiency of Conventional SAs in executing NNs

In this chapter, the main transformations used to execute DNN layers on systolic architectures will be introduced. This is followed by an overview of the metrics adopted for analyzing, in terms of efficiency, the non-reconfigurable architectures currently present in the state of the art. The discussion examines how the array shape, dataflow, and data reuse strategies influence throughput and energy consumption across different types of layers. The goal is to quantitatively assess the limitations of fixed-shape solutions and to motivate the need for more flexible approaches.

### 3.1 Mapping Neural Networks to Systolic Arrays

The properties that make hardware acceleration of neural networks through Systolic Arrays (SAs) extremely efficient is the ability to reduce, through appropriate transformations, different types of layers to a limited set of computational primitives.

The most widely used of these is the transformation of layers into dense matrix multiplications, or GEMM (General Matrix-Matrix Multiplication). A large portion of the computation in a Deep Neural Network (DNN) can be expressed as a matrix product of the form ( $C = A \times B$ ), where each element of the product is a matrix — properly derived and conditioned — from the input tensors.

These types of transformations are particularly advantageous in the context of SAs because, by their very operating principle, they are naturally optimized for GEMM-type operations, which consist of a series of regular, pipelined, and highly parallelizable steps. For this reason, most software frameworks and the majority of hardware accelerators (such as TPUs and GPUs) adopt a common strategy: they “map” high-level layers (FC, CNN, Attention) onto one or more GEMM operations.

In the following sections, the main mapping techniques will be analyzed depending on the type of layer being considered. The layers can be classified as follows:

- **Fully-Connected (FC) layers:** have a 1:1 mapping with GEMM, meaning they can be directly expressed as a matrix multiplication;

- **Convolutional layers (CNNs):** require transformations such as `im2col` or its variants;

- **Attention blocks in Transformers:** are composed by Q/K/V projections and attention scores. Those computations can also be reduced to matrix-matrix multiplications.

### 3.1.1 Fully-Connected Layers

Fully-connected (or dense) layers represent the simplest and most direct linear operator within deep neural networks. Despite their apparent simplicity, they play a central role in numerous models, such as multilayer perceptrons, final classifiers in CNNs, and — even more significantly — the MLP blocks in Transformers. From a computational standpoint, FC layers are particularly well-suited for execution on systolic architectures, since their structure perfectly matches the form of a dense matrix multiplication (GEMM).

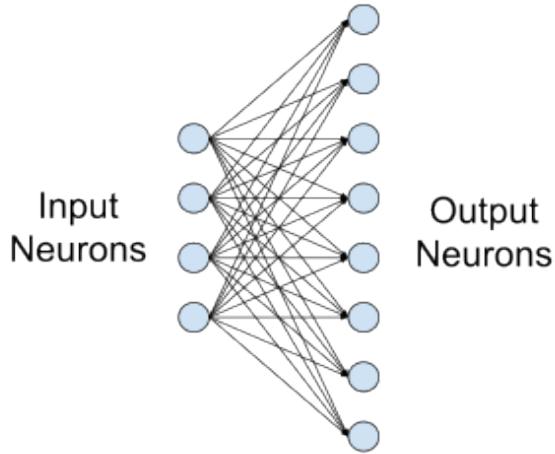

**Figure 3.1:** Example of a small fully-connected layer with four input and eight output neurons[17].

They are called "fully connected" because every input neuron can influence every

output neuron. In the context of FC networks, all three phases of network training can be rewritten as GEMM operations.

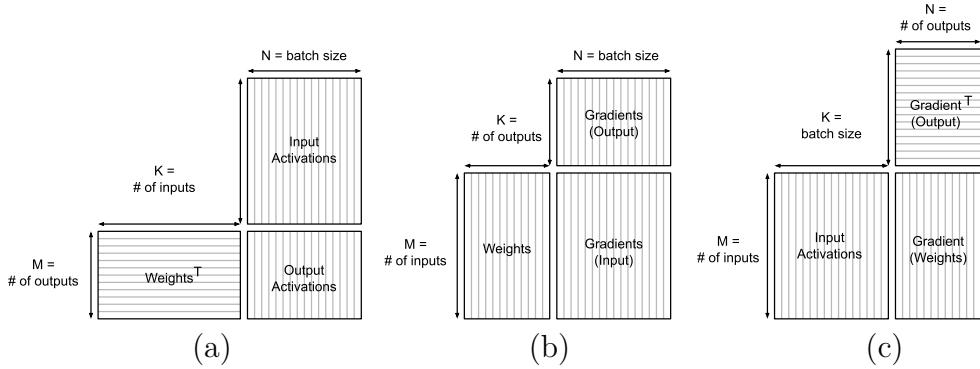

**Figure 3.2:** Dimensions of equivalent GEMMs for (a) forward propagation, (b) activation gradient, and (c) weight gradient computations of a fully-connected layer[17].

### Mathematical Formulation of the Fully Connected Layer

A fully-connected layer performs a linear transformation:

$$y = Wx + b \quad (3.1)$$

where:

- $(x \in \mathbb{R}^{d_{\text{in}}})$  is the input vector,

- $(y \in \mathbb{R}^{d_{\text{out}}})$  is the output vector,

- $(W \in \mathbb{R}^{d_{\text{out}} \times d_{\text{in}}})$  is the weight matrix,

- $(b \in \mathbb{R}^{d_{\text{out}}})$  is the bias vector.

When processing multiple samples in parallel (batch size (B)), the inputs are organized as:

$$X \in \mathbb{R}^{d_{\text{in}} \times B} \quad (3.2)$$

and the layer becomes:

$$Y = WX + b1_B^\top \quad (3.3)$$

where  $b1_B^\top$  is simply a matrix composed by the vector B repeated  $b_{\text{out}}$  times. It's the mathematical way to say that the same bias is applied to the entire computation. The dominant operation, in previous equation, is the matrix multiplication:

$$Y = WX \quad (3.4)$$

which corresponds to a GEMM with dimensions:

$$M = d_{\text{out}}, \quad K = d_{\text{in}}, \quad N = B \quad (3.5)$$

### Computational Complexity

The total number of operations (MACs) is:

$$\text{MACs} = d_{\text{out}} \cdot d_{\text{in}} \cdot B \quad (3.6)$$

This makes FC layers extremely costly in models such as Transformers, where MLP blocks typically cover 40–60% of the total computational cost. Also in Vision-based models, with very large fully-connected layers, using multiple batches makes this value increases rapidly.

### Data Reuse Patterns

The fully-connected layer represents the most favorable case for systolic arrays in terms of data reuse. In fact:

- **Weight reuse:** each row of (W) is reused for all input vectors in the batch and also with large batch sizes, each weight is reused dozens or even hundreds of times (optimal for WS dataflows)

- **Input reuse:** each column of (X) is reused for all rows of (W). This makes Input-Stationary (IS) dataflow appealing.

- **Output Local Accumulation:** each element ( $Y_{(i,j)}$ ) is obtained through accumulation which can be performed entirely within each PE. This behaviour is ideal for Output-Stationary (OS) dataflow.

In conclusion, all three dataflows are reasonably applicable to FC layers. However, the optimal choice depends on the shape of the SA and the batch size.

### 3.1.2 Convolutions (CNN) - GEMM via im2col

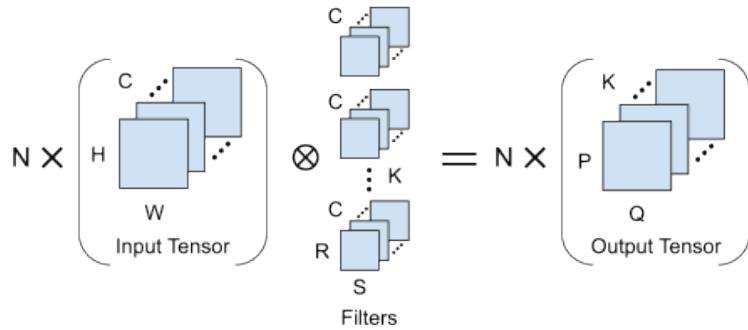

Two-dimensional convolutions represent one of the most fundamental operators in Convolutional Neural Networks (CNNs). Although the convolution operation is not, in its native form, a matrix multiplication, it can be transformed into a GEMM through a reorganization of the input tensors known as im2col (“image-to-column”). This transformation is widely adopted in major frameworks (such as cuDNN, PyTorch, and TensorFlow) and in dedicated hardware accelerators, as it enables the use of highly optimized GEMM implementations.

**Figure 3.3:** Convolution of an NCHW input tensor with a KCRS weight tensor, producing a NKQP output[17].

A 2D convolution is a mathematical operation where a smaller matrix called the "filter" or "kernel" is slid over an input matrix (often an image) to extract meaningful features. The process of convolution can be described step by step as follows:

1. The kernel is placed over a specific region of the input matrix.

2. The two matrices are multiplied element-wise.

3. The resulting products are summed to compute the output value for the current position (pixel).

4. The filter is then shifted to the next position.

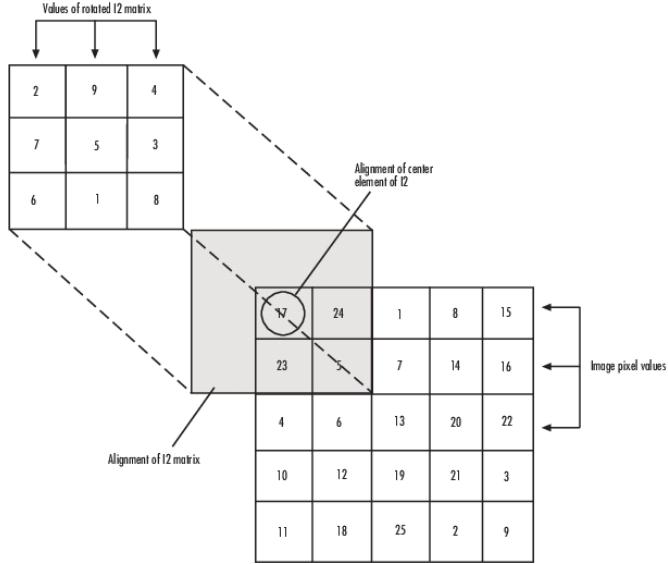

**Figure 3.4:** 2D discrete convolution of two input matrices[18].

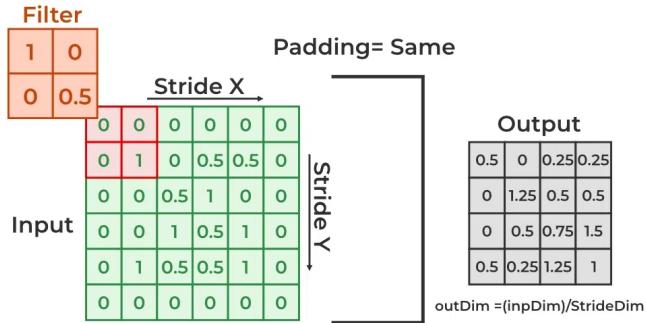

This process produces an output matrix that captures certain patterns depending on the filter used, such as edges, textures, or shapes. In a 2D convolution, two parameters are very important: stride and padding. Stride determines how far the filter moves at every step, in terms of coordinates. Different DNNs use different stride values depending on the desired behavior for example to control the spatial resolution of the output.

Padding is necessary when the filter size is not an integer submultiple of the input matrix. In those cases, the filter may exceed the matrix boundaries during the edge iterations inducing computational errors. A common solution is to add rows and/or columns of zeros around the input matrix such that the filter remains within valid bounds ensuring that the original data are not distorted.

**Figure 3.5:** Stride and Padding in 2D-Convolution[19].

In the following mathematical discussion, stride will be fixed at 1 for simplicity.

Filter size is an integer submultiple of input so padding will be not required.

## 2D Convolution Mathematical Formulation

Start considering a basic 2D convolution between a three-dimensional input tensor:

$$X \in \mathbb{R}^{C_{\text{in}} \times H \times W} \quad (3.7)$$

and a set of filters:

$$K \in \mathbb{R}^{C_{\text{out}} \times C_{\text{in}} \times R \times S} \quad (3.8)$$

The output of the convolution is given by:

$$Y_{(c_o, i, j)} = \sum_{c_i=0}^{C_{\text{in}}-1} \sum_{r=0}^{R-1} \sum_{s=0}^{S-1} K_{(c_o, c_i, r, s)} \cdot X_{(c_i, i+r, j+s)} \quad (3.9)$$

The coordinates  $((i, j))$  span all spatial positions where the kernel can be applied, for a total of:

$$H_{\text{out}} = H - R + 1, \quad W_{\text{out}} = W - S + 1 \quad (3.10)$$

Thus, the final output has dimensions:

$$Y \in \mathbb{R}^{C_{\text{out}} \times H_{\text{out}} \times W_{\text{out}}} \quad (3.11)$$

This operation involves a triple nested loop over channels and spatial coordinates — which is inefficient to compute directly in hardware.

## The Idea Behind im2col

The goal of im2col is to convert the convolution into a single large matrix–matrix multiplication. Each application of the  $(R \times S)$  kernel over a region of the input can be viewed as a dot product between a vector containing the kernel values, and a vector obtained by “flattening” the corresponding image patch. Each filter is flattened into a vector of length:

$$K_{\text{flat}} = C_{\text{in}} \cdot R \cdot S \quad (3.12)$$

By stacking all filters as rows, the weight matrix of the GEMM is obtained:

$$K_{\text{mat}} \in \mathbb{R}^{C_{\text{out}} \times (C_{\text{in}} R S)} \quad (3.13)$$

For each valid position of the input tensor  $((i, j))$  the corresponding patch is extracted and then is flattened into a vector of length  $(C_{\text{in}} R S)$ . Each of these vectors is then appended as a column, forming:

$$X_{\text{col}} \in \mathbb{R}^{(C_{\text{in}} R S) \times (H_{\text{out}} W_{\text{out}})}. \quad (3.14)$$

Once these two matrices are constructed, the convolution operator becomes the simply GEMM that is previously analyzed in Fully Connected Layers (subsection 3.1.1):

$$Y_{\text{mat}} = K_{\text{mat}} \cdot X_{\text{col}} \quad (3.15)$$

where:

$$Y_{\text{mat}} \in \mathbb{R}^{C_{\text{out}} \times (H_{\text{out}} W_{\text{out}})} \quad (3.16)$$

which can then be reshaped back into its three-dimensional form:

$$Y \in \mathbb{R}^{C_{\text{out}} \times H_{\text{out}} \times W_{\text{out}}} \quad (3.17)$$

In summary: the input image is a tensor, but to make it suitable for processing within a Systolic Array, it must be converted into a matrix. To do so, a “patch” (or small region) of the tensor is extracted and flattened along its third dimension, producing a vector. By placing all such vectors side by side, the GEMM input matrix is obtained. Similarly, each filter is also flattened into a vector, forming the weight matrix. The resulting matrix multiplication is thus equivalent to evaluating — in parallel — the dot product of every filter with every subregion of the image.

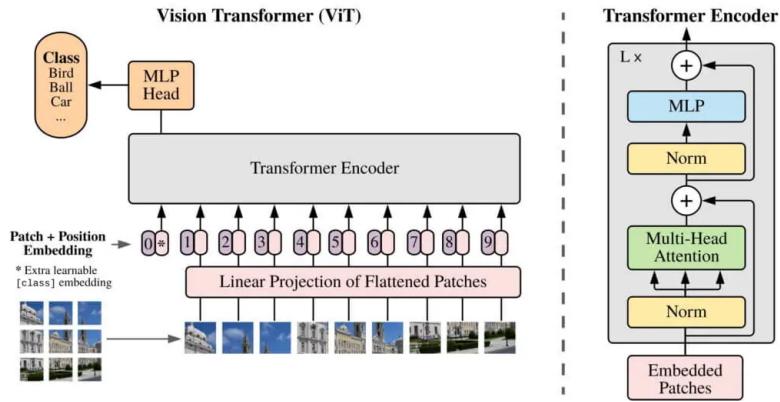

### 3.1.3 Transformer and Self-Attention

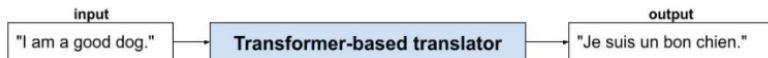

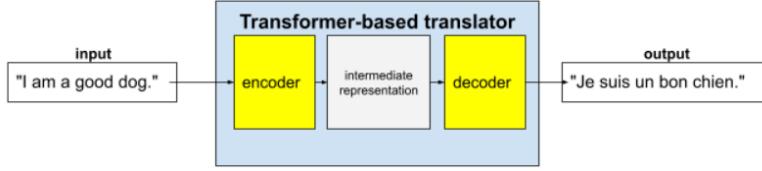

The self-attention mechanism is the core element of Transformer architectures and represents one of the most computationally significant kernels in modern deep learning. Transformers currently define the state of the art in the domain of Large Language Models (LLMs). A full Transformer model consists of an encoder and a decoder, both implemented as deep neural networks with multiple layers of attention and feed-forward components.

**Figure 3.6:** A Transformer-based application that translates from English to French[20].

As described by Google[20]:

“For example, in a translator:

- The encoder processes the input text (for example, an English sentence) into some intermediate representation.

- The decoder converts that intermediate representation into output text (for example, the equivalent French sentence).

**Figure 3.7:** A full Transformer contains both an encoder and a decoder[20].

The ‘self’ in ‘self-attention’ refers to the input sequence. Some attention mechanisms weigh relations of input tokens to tokens in an output sequence, like in translation, or to tokens in some other sequence. But self-attention only weighs the importance of relations between tokens in the input sequence.”

Although the behavior of the attention mechanism is more complex than that of a fully connected or convolutional layer, from a mathematical and computational standpoint it can be largely expressed as a sequence of dense matrix multiplications. This makes it particularly well-suited for execution on systolic array architectures, which are optimized for regular, parallel GEMM operations. In this section, the main operations involved in the Attention block are analyzed, with a particular focus on data reuse patterns and computational implications.

### Mathematical Formulation of Attention Block in Transformer Layer

Given an input tensor:

$$X \in \mathbb{R}^{T \times d_{\text{model}}} \quad (3.18)$$

where ( $T$ ) represents the sequence length and ( $d_{\text{model}}$ ) the model dimensionality, the multi-head attention mechanism constructs three linear projections — query, key, and value — as follows:

$$Q = XW_Q, \quad K = XW_K, \quad V = XW_V \quad (3.19)$$

with:

$$W_Q, W_K, W_V \in \mathbb{R}^{d_{\text{model}} \times d_{\text{head}}}, \quad d_{\text{head}} = \frac{d_{\text{model}}}{h} \quad (3.20)$$

where ( $h$ ) is the number of heads, meaning the number of different subspaces (or “perspectives”) the model attends to simultaneously when making a decision.

Each transformation is a GEMM of the form:

$$(T \times d_{\text{model}})(d_{\text{model}} \times d_{\text{head}}) \quad (3.21)$$

In this formulation are evident that high data reuse can be exploited. The same inputs ( $X$ ) are used three times and each weight matrix ( $W$ ) is reused ( $T$ ) times, once for each token in the sequence. Thus, the construction of ( $Q$ ), ( $K$ ), and ( $V$ ) is computationally very similar to a fully-connected layer.

Another step that requires GEMM calculation is the computation of Attention Scores: ( $S = QK^\top$ ). The core of the attention mechanism is the compatibility matrix:

$$S = QK^\top, \quad S \in \mathbb{R}^{T \times T} \quad (3.22)$$

Each element is defined as:

$$S_{(i,j)} = \langle Q_i, K_j \rangle \quad (3.23)$$

which measures how relevant token (j) is to token (i). From a computational point of view the product ( $QK^\top$ ) is a square GEMM of dimension:

$$(T \times d_{\text{head}})(d_{\text{head}} \times T) \quad (3.24)$$

Also in this case the algorithm has an high data reuse, in fact, each row of (Q) and (K) are reused (T) times. Hence, ( $QK^\top$ ) represents an almost ideal case for a Systolic Array since dense tensors with highly regular computation pattern are organized in square matrix structure (high parallelism potential) that exploit extensive data reuse along both rows and columns. Last step is the computation of the Weighted Output ( $O = \tilde{S}V$ ). The final output of the attention mechanism, for a single head, is:

$$O = \tilde{S}V, \quad O \in \mathbb{R}^{T \times d_{\text{head}}} \quad (3.25)$$

where ( $\tilde{S}$ ) is the normalized attention score matrix (after applying softmax). Also in this case is a rectangular GEMM:

$$(T \times T)(T \times d_{\text{head}}) \quad (3.26)$$

The high and regular reuse pattern makes this computation very suitable for systolic array architectures. In this case each row of ( $\tilde{S}$ ) is reused ( $d_{\text{head}}$ ) times and represents a probability distribution. Instead, each row of (V) is reused (T) times. In conclusion, the entire Attention block (for a single head) is dominated by five GEMM operations:

1. Three GEMMs to produce (Q), (K), and (V).

2. One square GEMM for ( $QK^\top$ ).

3. One rectangular GEMM for ( $\tilde{S}V$ ).

Each of these operations maps efficiently onto systolic array architectures, highlighting why Transformers — despite their apparent algorithmic complexity — can be effectively accelerated through GEMM-optimized hardware.

## 3.2 Evaluation Methodology

To evaluate the efficiency of the different systolic array configurations, a two-phase methodology was adopted.

First, an RTL-level analysis was performed to estimate the number of clock cycles required to fully execute specific DNN kernels.

Next, the corresponding architecture was synthesized using a 28 nm technology node, which was employed to estimate area and power consumption at a fixed operating frequency of 500 MHz. This frequency value is widely adopted in the literature related to DNN accelerators implemented in this or comparable technology nodes. Works such as MAGNet by NVIDIA[21], NullHop[22], and SHARP[23] use target frequencies in the range of 400–600 MHz for post-synthesis evaluations. Operating within this frequency range allows for reliable estimations of area and power while ensuring a fair comparison among the different configurations under analysis. It remains true, however, that the architecture — as well as the synthesis scripts — is fully modular. As a result, obtaining the same results at a different operating frequency becomes extremely straightforward.

### 3.2.1 Performance estimation method

For each array configuration, the total number of clock cycles, the size of the local buffers, and the bandwidth required by the array to execute a given kernel were estimated. The goal was to obtain a latency model that did not depend on memory-access constraints but focused exclusively on the intrinsic properties of the architecture. The analysis is based on a Python function implementing an analytical model of the array’s behavior, which, unlike full RTL simulation, allows for rapid exploration of the configuration space and helps narrow down the number of candidates in a first approximation. The results obtained for the proposed architectures were compared against RTL simulation runs to verify the correctness of the analytical estimates.

#### Bandwidth estimantion

The first step consists of estimating the local resources and the required bandwidth. For each dimension of the array — identified as D1, D0, and S — all parameters necessary for sizing the local memory are determined, such as the amount of data to store, the number of access ports, and the theoretical bandwidth required to feed the PEs. This phase quantifies the communication overhead, which is useful for assessing the integrability of the array in memory-constrained systems, but it does not affect the latency computation, which remains idealized.

## Wavefront-Steps Definition

A characteristic aspect of systolic architectures is the initial latency needed for the data stream to propagate through the entire array. This latency depends on the dimensions of the array and is modeled as:

```

wavefront_steps = arr_shape_D1 + arr_shape_D0 - 1

```

This value corresponds to the number of cycles required for the wavefront to reach the last PE in the array. During this interval, the PEs do not yet operate at full throughput, but this phase is essential to obtain a fully filled pipeline.

## Per-Tile latency and total number of tiles

DNN kernels are divided into submatrices, or "tiles", defined by:

- number of submatrices along D1 (`N_tiles_D1`)

- number of submatrices along D0 (`N_tiles_D0`)

- number of submatrices along dimension S (`N_tiles_S`)

From that is possible to derive the total number of tiles such:

```

N_tiles = N_tiles_D1 * N_tiles_D0 * N_tiles_S

```

Each tile requires a number of cycles equal to:

```

steps_per_tile = arr_shape_S

```

since the accumulation along this dimension determines the number of steps needed to complete the partial computation associated with the tile.

## Computation Latency Model

The total number of clock cycles is therefore given by:

```

tot_CC = (steps_per_tile * N_tiles) + wavefront_steps - 1

```

The first term represents the effective computation time of the tiles, while the second accounts for the delay introduced by filling the wavefront and draining the pipeline at the end of the computation. This formula — derived directly from the synchronization model of the array — matches, within the granularity of the ideal analytical model, the behavior observed in RTL simulations.

### Mapping Function - Fully Connected

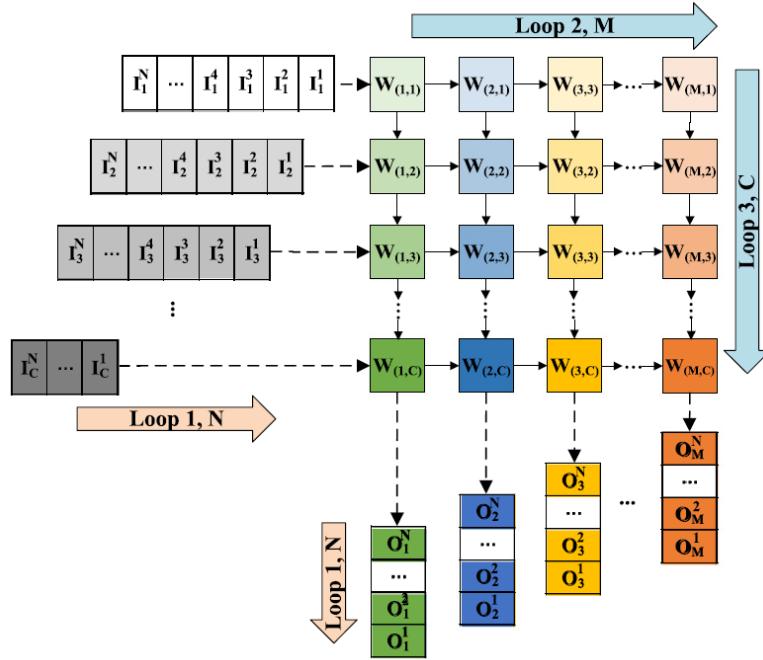

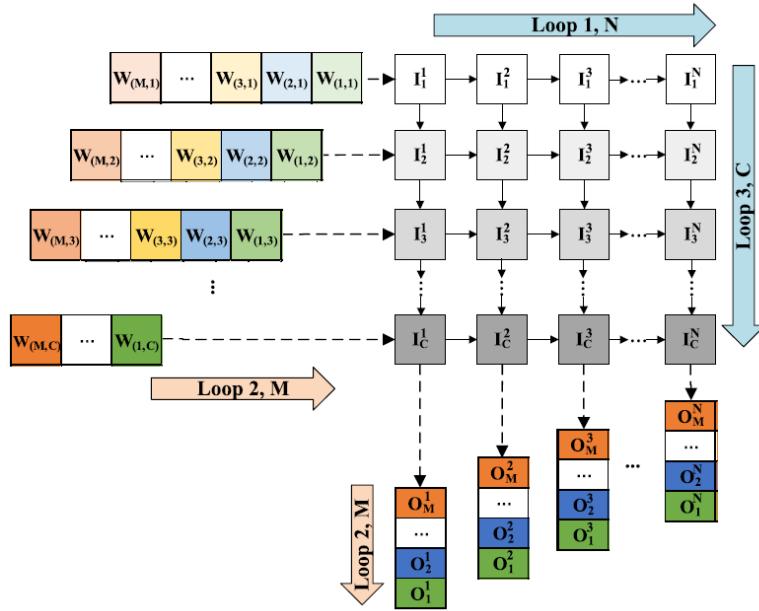

To compare the performance of different SA configurations, each layer of every neural network must be expressed in a form compatible with the computational model of the array. As discussed earlier, modern DNNs are far from being simple GEMMs, but with the appropriate transformations the problem can be reduced to a form that systolic arrays can efficiently handle. To uniformly evaluate latency and throughput across configurations, it is therefore necessary to have a function that maps each layer to a standard three-dimensional domain  $((D1, D0, S))$ , representing the cube of MAC iterations required to complete its computation. Given the shapes of tensors a layer needs to compute, a python function was built to return the boundaries of the for-loops of the c-code that would perform the computation of the layer, reordering the boundaries based on the dataflow under analysis (i.e., Output-Stationary, Weight-Stationary, or Input-Stationary).

In the case of a fully-connected layer, the computation is simply the multiplication between an activation matrix and a weight matrix. The function used to complete this task only assigns the three dimensions  $(D1)$ ,  $(D0)$ , and  $(S)$  to the relevant quantities of the layer depending on the dataflow:

- Output Stationary (OS): Output elements remain resident in the PEs.

```

D1 = out_rows, D0 = out_cols, S = input_cols

```

- Weight Stationary (WS): Weights remain fixed in the PEs, inputs flow through the array.

```

D1 = weight_rows, D0 = weight_cols, S = input_rows

```

- Input Stationary (IS): Activations remain fixed, weights propagate across the array.

```

D1 = input_cols, D0 = input_rows, S = weight_rows

```

This conversion enables each fully-connected layer to be modeled as a uniform three-dimensional domain, directly compatible with the systolic array latency model.

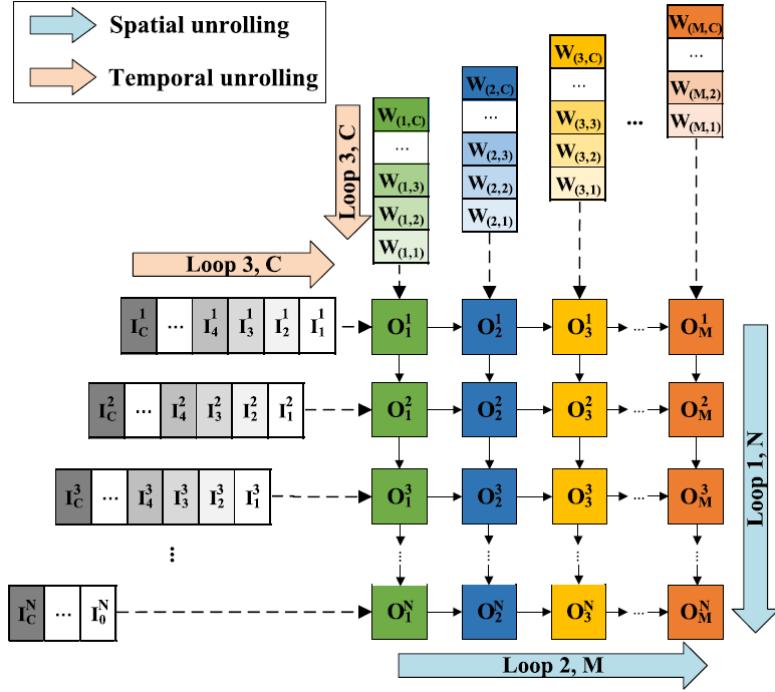

### Mapping Function - CNN

Convolutional layers must also be mapped into the same domain. The convolution is interpreted as a matrix–matrix product by flattening both patch tensors and filter tensors. For the CNN case, another function is needed to transform the layer. In brief, the difference between the FC and the CNN case is one step in which the im2col algorithm previously presented is applied. This function builds the triplet

((D1, D0, S)) by relating the number of spatial output positions, the number of output channels and the internal kernel dimension (input channels  $\times$  filter area) following the organization of the data vector imposed by the chosen dataflow. In particular:

- **Output Stationary (OS):**

$$D1 = N * H_{out} * W_{out}, D0 = C_{out}, S = C_{in} * K_h * K_w$$

- **Weight Stationary (WS):**

$$D1 = C_{out}, D0 = C_{in} * K_h * K_w, S = N * H_{out} * W_{out}$$

- **Input Stationary (IS):**

$$D1 = C_{in} * K_h * K_w, D0 = N * H_{out} * W_{out}, S = C_{out}$$

This recoding makes it possible to process convolutional layers using exactly the same tiling mechanism as other operators. Moreover, since everything has been reduced to a matrix multiplication, the same analytical latency model can be used for performance estimation.

### Definition of Efficiency Metric

Identify the boundaries of the for-loops both for FC and CNN layers is an essential step to also figure out the number of MAC operations. Moreover, in order to compare the different configurations of the systolic array in a homogeneous way, an efficiency metric was adopted that combines computational capability and power consumption into a single value.

The metric Operations Per Cycle (OPC) is defined as the ratio between the total number of MAC operations actually executed and the overall number of clock cycles required to complete them. To incorporate power consumption into this value, the result is then normalized with respect to the dissipated power. In other words, the throughput is first measured in terms of MAC per cycle, obtained by accumulating the total number of operations performed and the corresponding cycles used across the entire sub-layer under consideration. This value is then divided by the average power, expressed in milliwatts, obtained from the design synthesis. The result is a metric expressed as OPC/mW, which describes how much effective work the architecture can perform per unit of energy.

This metric, in addition to being easy to interpret, makes it possible to compare configurations with different array shapes, different dataflows, or different levels of parallelism, highlighting which solutions offer the best compromise between performance and power consumption.

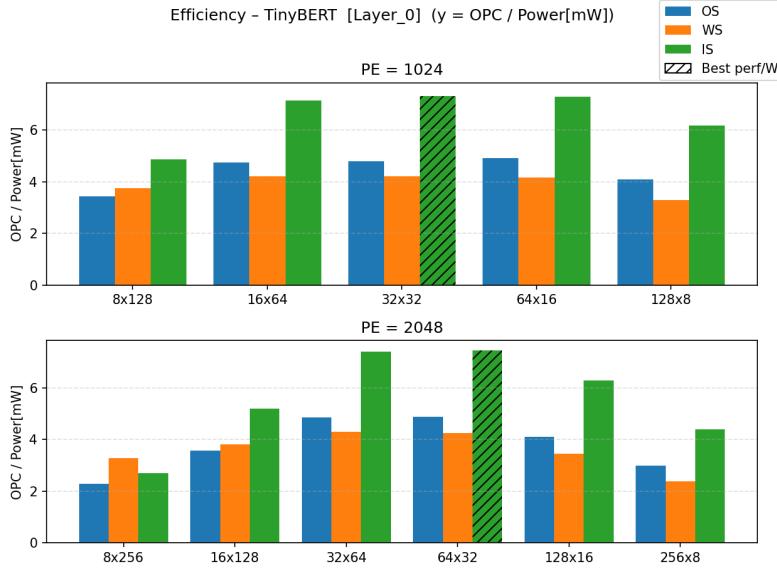

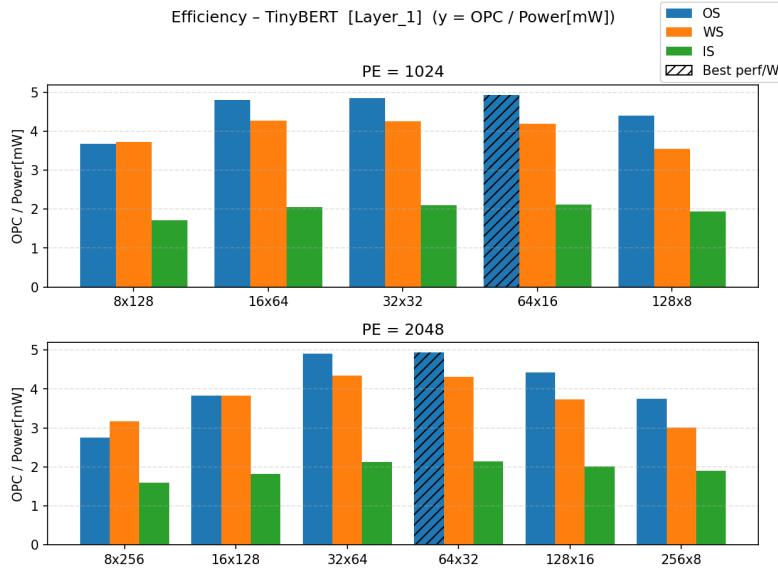

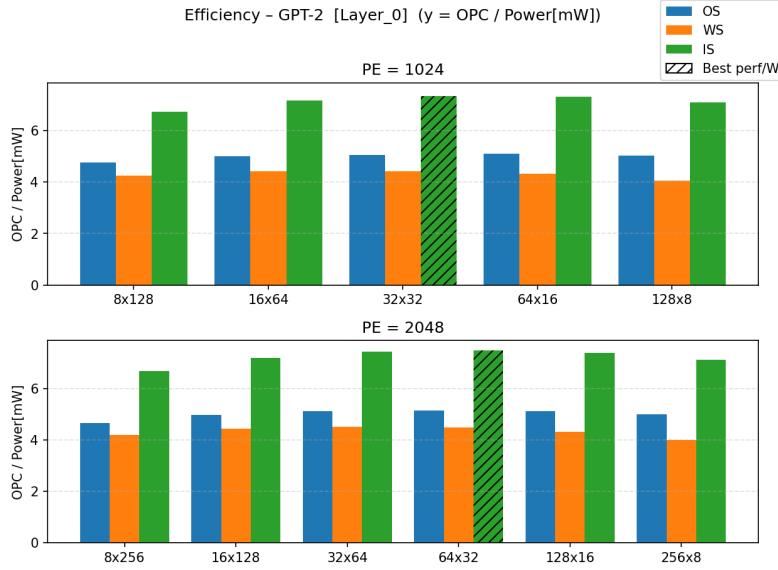

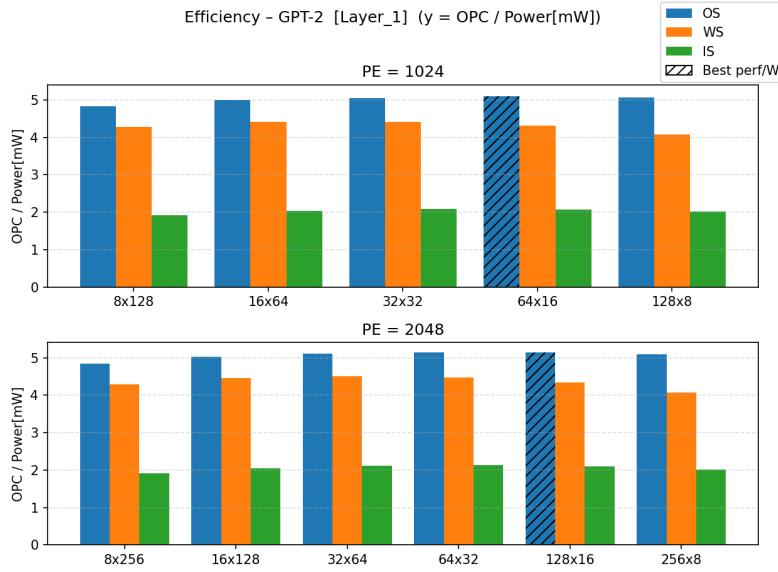

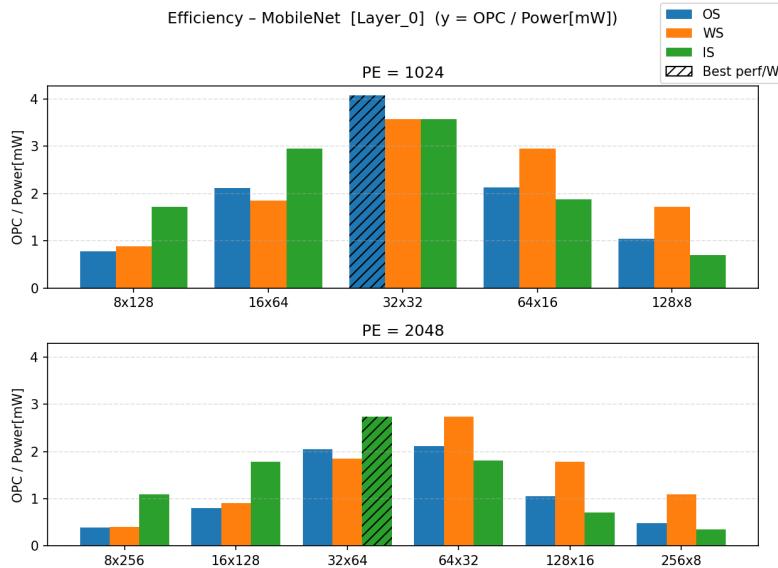

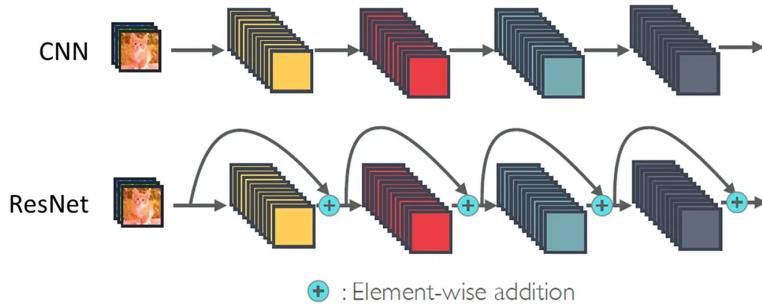

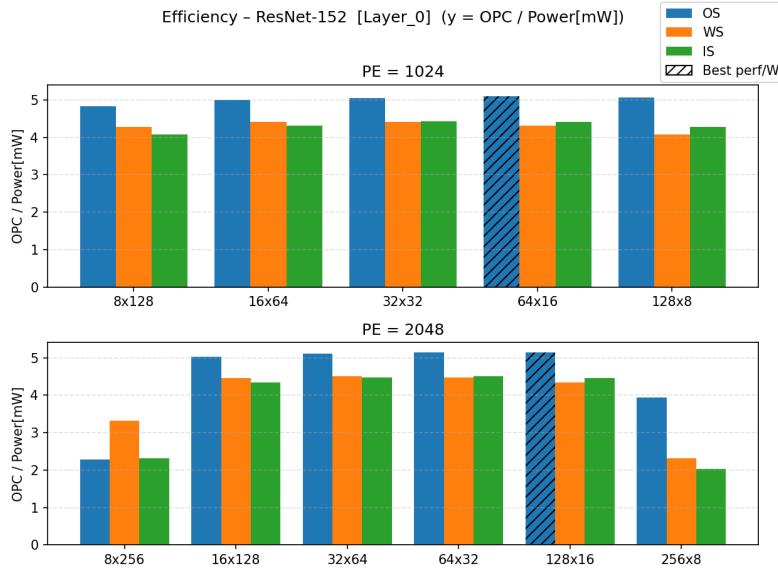

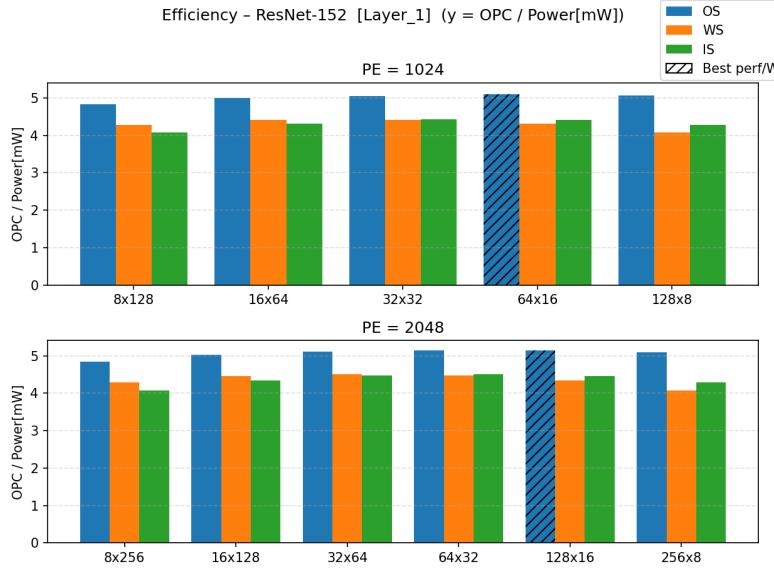

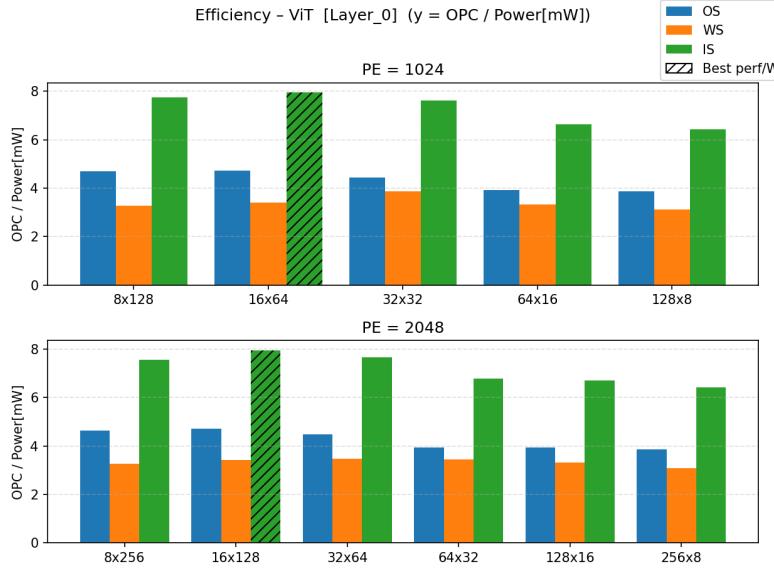

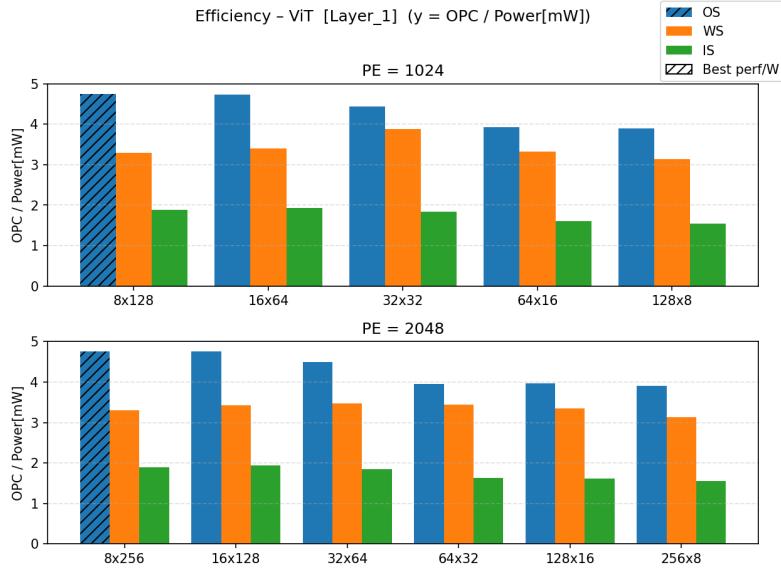

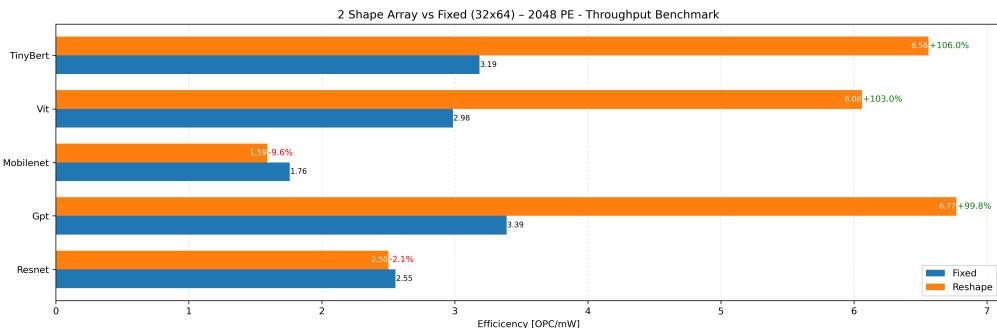

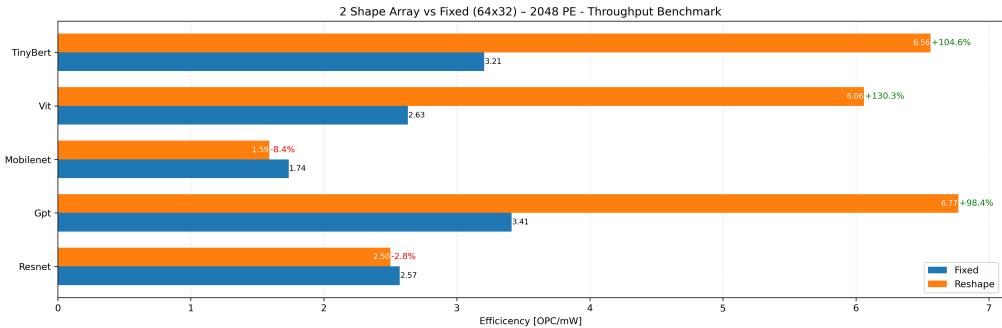

### 3.3 Performance Results

In this paragraph, the performance of the various SA configurations considered during the design space exploration will be evaluated systematically. Since performance, in terms of efficiency, varies depending on the specific dataflow scheme and array shape, five models — each composed of two layers — were selected to cover operation types that are representative of modern deep neural networks.

For each layer, a plot will be presented summarizing the efficiency of the different configurations according to the OPC/mW metric, together with observations on latency, area, and dynamic power consumption. The aim is not to examine every collected value in detail, but to highlight the combinations of shapes and dataflows that prove to be the most efficient for the structure of the layer under analysis.

This approach made it possible to identify relationships between the type of layer being executed and the optimal architecture, which are crucial for selecting the most versatile configurations. These selected configurations will later be integrated into the reconfigurable architecture developed in the second part of the work.

| Model       | Layer 0           | Layer 1           | Category    |

|-------------|-------------------|-------------------|-------------|

| GPT-2       | Self-attention    | Feed-forward      | Transformer |

| ViT-L/16    | Self-attention    | Feed-forward      | Transformer |

| ResNet-152  | Bottleneck B2     | Bottleneck B4     | Deep CNN    |

| TinyBERT    | Self-attention    | Feed-forward      | Transformer |

| MobileNetV2 | Inverted residual | Inverted residual | CNN         |