# POLITECNICO DI TORINO

DIPARTIMENTO DI ELETTRONICA E TELECOMUNICAZIONI

CORSO DI LAUREA MAGISTRALE IN INGEGNERIA ELETTRONICA

Riduzione dei tempi di simulazione mediante modellazione

analogica comportamentale e semplificazione del DSP negli

IP SerdDes a 64Gbps

Sessione di laurea: Dicembre 2025

**Relatore:**

Guido Masera

**Tutor aziendale:**

Darjn Esposito

**Candidato:**

Vincenzo Castilletti

(s323764)

# Abstract

La crescente complessità delle IP PHY SerDes necessaria per garantire elevati data-rate in applicazioni come High Performance Computing (HPC), Data Center e AI/ML, ha reso la simulazione di questi dispositivi sempre più onerosa dal punto di vista computazionale. Questa tesi in azienda, svolta in Synopsys, si concentra sul miglioramento delle velocità di simulazione degli IP Synopsys (PHY), prendendo come riferimento un IP PCIe6. Il lavoro si articola in due principali direzioni: l'ottimizzazione delle simulazioni digitali e lo sviluppo di modelli analogici comportamentali.

La prima parte del lavoro riguarda l'ottimizzazione dei tempi di simulazione digitali, fondamentale per consentire ai customer un'accurata verifica dei loro SoC, contenenti più istanze dei SerDes PCIe6 prodotti da Synopsys. A livello customer, per motivi di protezione della proprietà intellettuale, le simulazioni sono basate su netlist GTECH, sintetizzata tramite una libreria di standard cell technology independent. Nel contesto di verifica delle IP a livello SoC, le simulazioni vengono effettuate utilizzando canali di trasmissione ideali, pertanto l'uso di tecniche di avanzate di DSP non è necessario. Da ciò nasce la possibilità di intervenire, tramite strumenti di Simulation Profiling integrati nei tool di simulazione, per individuare quali blocchi DSP risultano rilevanti per i tempi di simulazione, e semplificarli. Dato che tali modifiche devono essere applicate solo in fase di simulazione, sono state introdotte tramite direttive di preprocessore.

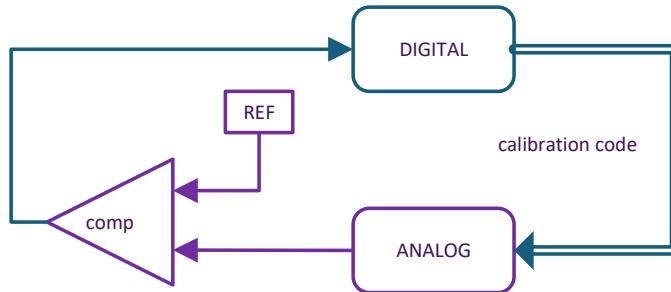

La seconda parte del lavoro riguarda lo sviluppo di modelli analogici utili per la verifica ad high-coverage della logica hardware e del firmware durante la fasi di calibrazione dei circuiti analogici. L'architettura del SerDes presa come riferimento implementa una serie di blocchi logici per l'esecuzione degli algoritmi di calibrazione. L'utilizzo di modelli complessi e dettagliati dei circuiti analogici non renderebbe possibile effettuare queste simulazioni a causa dell'eccessivo tempo di esecuzione. Per verificare il loop di calibrazione, sono stati sviluppati modelli in Verilog che emulano il comportamento dei blocchi analogici durante la fase di calibrazione generando tutti i segnali necessari per l'interfacciamento con il dominio digitale. Questi modelli sono stati sviluppati a partire dalle specifiche funzionali fornite dall'azienda e dall'analisi degli schematici analogici. L'obiettivo è quello co-simulare firmware, RTL e macro analogica, per analizzarne l'interazione in tempi di simulazione ridotti. Anche

in questo caso, l'utilizzo di strumenti di simulation profiling integrati nei tool di simulazione, ha permesso di valutare l'impatto di questi modelli sul tempo complessivo di simulazione, focalizzandosi sull'individuazione di soluzioni semplici ed efficaci. Infine, dall'esecuzione di simulazioni utilizzando i modelli complessi preesistenti e i modelli sviluppati si è evinta una riduzione dei tempi di simulazione. I risultati ottenuti evidenziano benefici sia quantitativi, con tempi di simulazione ridotti, sia qualitativi, grazie alla semplificazione del debug rispetto a modelli analogici complessi.

# Indice

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduzione e motivazioni</b>                                | <b>1</b>  |

| <b>2</b> | <b>Panoramica sui Ser-Des e PCIe</b>                             | <b>5</b>  |

| 2.1      | Ser-Des . . . . .                                                | 5         |

| 2.2      | Problematiche di un High Speed Ser-Des . . . . .                 | 10        |

| 2.2.1    | Inter Symbol Interference . . . . .                              | 10        |

| 2.2.2    | Jitter e Skew . . . . .                                          | 13        |

| 2.3      | Equalization e Adaptation . . . . .                              | 14        |

| 2.4      | Physical Layer: Lane Transmitter . . . . .                       | 16        |

| 2.4.1    | Encoder . . . . .                                                | 16        |

| 2.4.2    | TX FFE . . . . .                                                 | 17        |

| 2.4.3    | Serializer . . . . .                                             | 18        |

| 2.4.4    | Digital to Analog Converter . . . . .                            | 18        |

| 2.4.5    | Duty Cycle Correction . . . . .                                  | 19        |

| 2.5      | Physical Layer: Lane Receiver . . . . .                          | 20        |

| 2.5.1    | CTLE . . . . .                                                   | 20        |

| 2.5.2    | VGA . . . . .                                                    | 20        |

| 2.5.3    | ADC . . . . .                                                    | 21        |

| 2.5.4    | RX FFE . . . . .                                                 | 21        |

| 2.5.5    | DFE . . . . .                                                    | 22        |

| 2.5.6    | RX Clock Data Recovery . . . . .                                 | 24        |

| <b>3</b> | <b>GTECH Speed-up</b>                                            | <b>27</b> |

| 3.1      | Introduzione alla libreria GTECH . . . . .                       | 27        |

| 3.2      | Giustificazioni per la semplificazione della parte DSP . . . . . | 28        |

| 3.3      | Metodo di analisi delle performance . . . . .                    | 29        |

| 3.3.1    | Simulation Profiler . . . . .                                    | 29        |

| 3.3.2    | Testbench utilizzato . . . . .                                   | 30        |

| 3.3.3    | Simulazione di riferimento . . . . .                             | 32        |

| 3.4      | Implementazione delle semplificazioni . . . . .                  | 34        |

| 3.4.1    | RX FFE . . . . .                                                 | 35        |

| 3.4.2    | RX CDR FFE . . . . .                                             | 36        |

| 3.5      | Analisi risultati ottenuti . . . . .                             | 37        |

|                                                              |           |

|--------------------------------------------------------------|-----------|

| <b>4 Sviluppo di modelli analogici</b>                       | <b>41</b> |

| 4.1 Introduzione alle calibrazioni . . . . .                 | 41        |

| 4.2 Modelli analogici flat con calibrazioni . . . . .        | 43        |

| 4.2.1 Implementazione generale modelli . . . . .             | 44        |

| 4.3 Simulazioni per calibrazioni . . . . .                   | 45        |

| 4.3.1 Verifica dei modelli . . . . .                         | 45        |

| 4.4 Calibrazioni RX . . . . .                                | 46        |

| 4.4.1 RX CTLE, VGA, SIGDET calibration . . . . .             | 47        |

| 4.4.2 RX ATT calibration . . . . .                           | 48        |

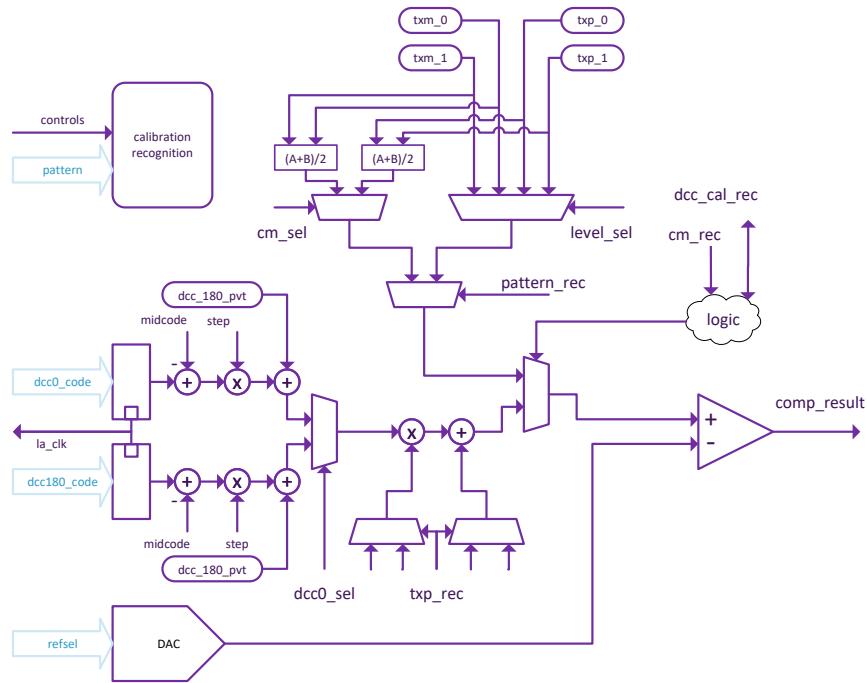

| 4.4.3 RX DCC calibration . . . . .                           | 49        |

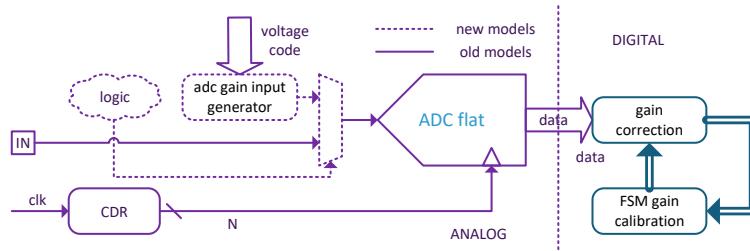

| 4.4.4 RX ADC calibrations . . . . .                          | 50        |

| 4.4.5 RX ADC offset . . . . .                                | 51        |

| 4.4.6 RX ADC Gain . . . . .                                  | 52        |

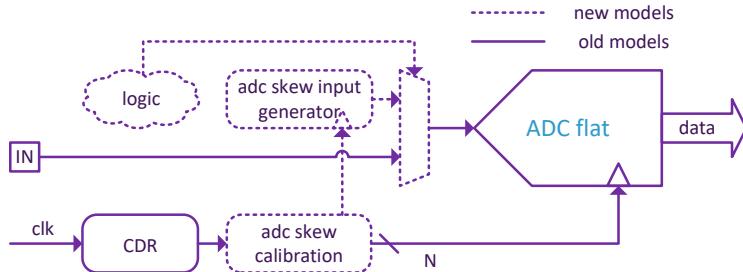

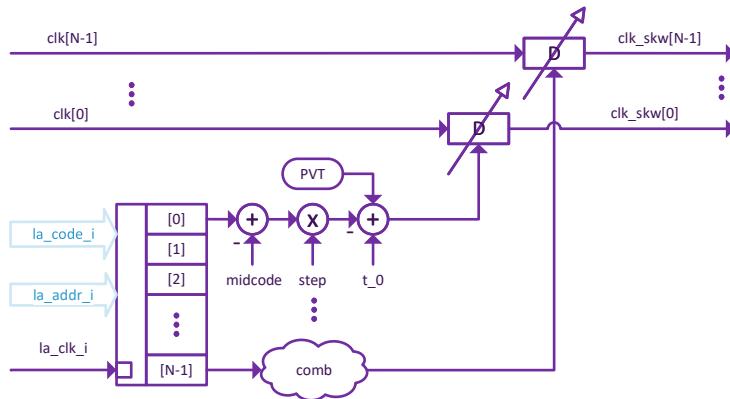

| 4.4.7 RX ADC skew . . . . .                                  | 52        |

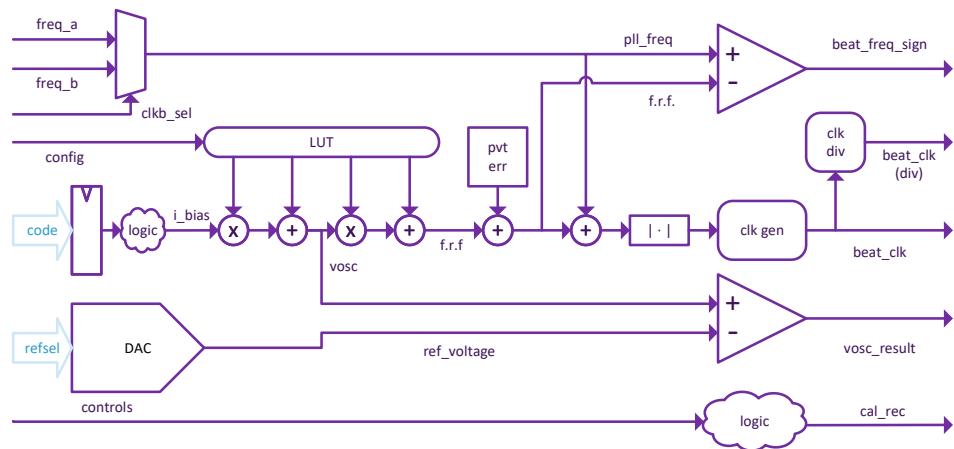

| 4.4.8 RX ILO calibration . . . . .                           | 56        |

| 4.4.9 RX QLL calibration . . . . .                           | 58        |

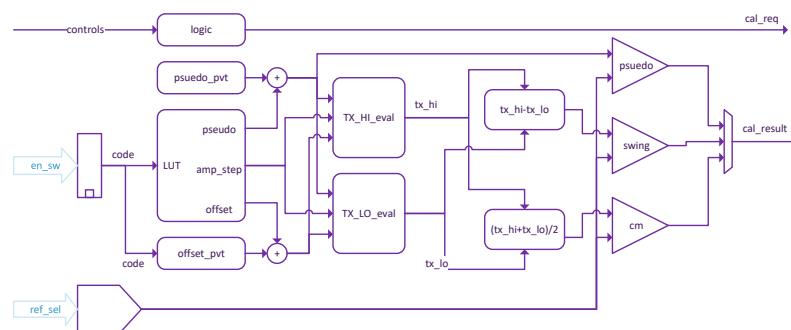

| 4.5 Calibrazioni TX . . . . .                                | 61        |

| 4.5.1 TX DCC calibration . . . . .                           | 61        |

| 4.5.2 TX LVL calibration . . . . .                           | 65        |

| 4.6 Analisi prestazioni simulative dei modelli . . . . .     | 66        |

| 4.6.1 Impatto sul tempo di simulazione complessivo . . . . . | 66        |

| 4.6.2 Confronto con i modelli già esistenti . . . . .        | 67        |

| <b>5 Conclusioni</b>                                         | <b>69</b> |

# Elenco delle figure

|      |                                                                                                            |    |

|------|------------------------------------------------------------------------------------------------------------|----|

| 1.1  | I/O Bandwidth vs Year                                                                                      | 2  |

| 2.1  | Struttura base di un Serializer-Deserializer (Ser-Des)                                                     | 6  |

| 2.2  | Rappresentazione di una lane                                                                               | 6  |

| 2.3  | Peripheral Component Interconnect Express (PCIe) Layers                                                    | 7  |

| 2.4  | Esempio di modulazione PAM-4                                                                               | 8  |

| 2.5  | Confronto tra eye diagram di codifica Not Return to Zero (NRZ)<br>e Pulse Amplitude Modulation - 4 (PAM-4) | 8  |

| 2.6  | Diagramma ad occhio di un segnale affetto da distorsione [10]                                              | 10 |

| 2.7  | Simbolo distorto a causa di banda limitata                                                                 | 11 |

| 2.8  | Esempio di simbolo in uscita in un canale non ideale                                                       | 11 |

| 2.9  | Esempio di errore di trasmissione dovuto all'Inter Symbolic Interference (ISI)                             | 12 |

| 2.10 | Eye Diagram per un canale di trasmissione con ISI                                                          | 12 |

| 2.11 | Esempio di come il jitter influenza il campionamento del segnale<br>in ricezione                           | 13 |

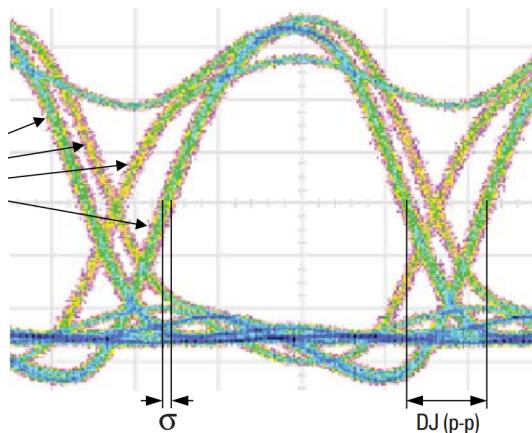

| 2.12 | Differenza tra jitter casuale e deterministico                                                             | 13 |

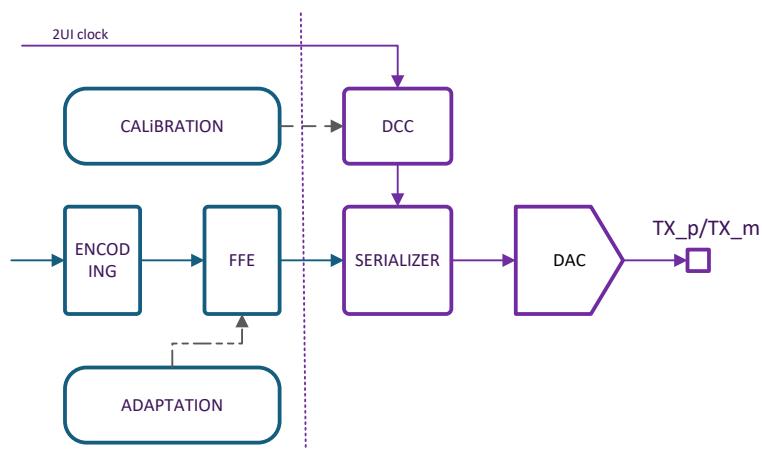

| 2.13 | Schema a blocco tipico di un trasmettitore                                                                 | 16 |

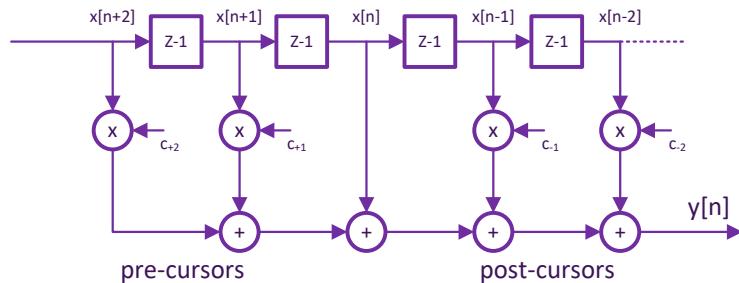

| 2.14 | Struttura tipica di un fir                                                                                 | 17 |

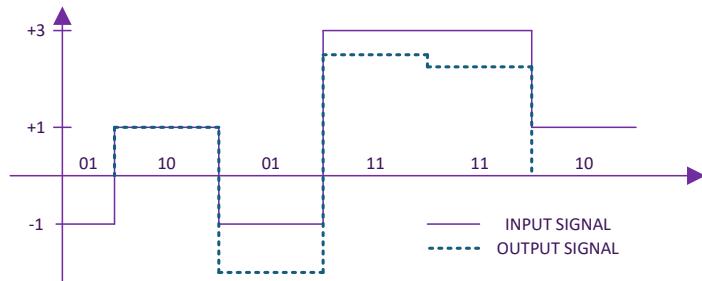

| 2.15 | Esempio di funzionamento di un Feed Forward Equalizer (FFE)                                                | 18 |

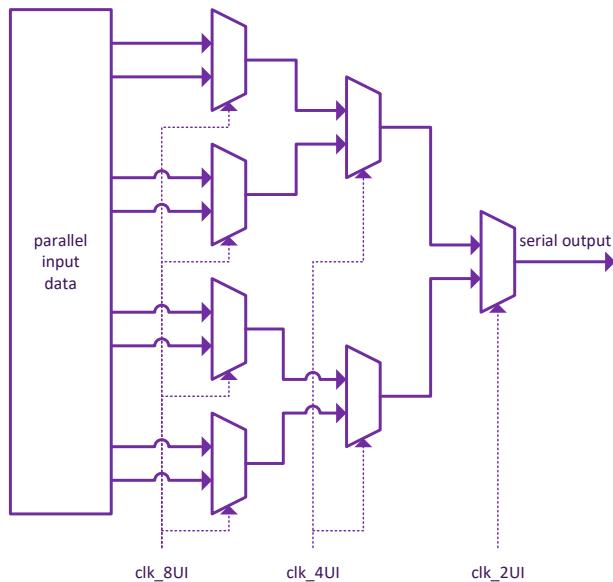

| 2.16 | Schema di principio di un serializzatore a 8 ingressi                                                      | 19 |

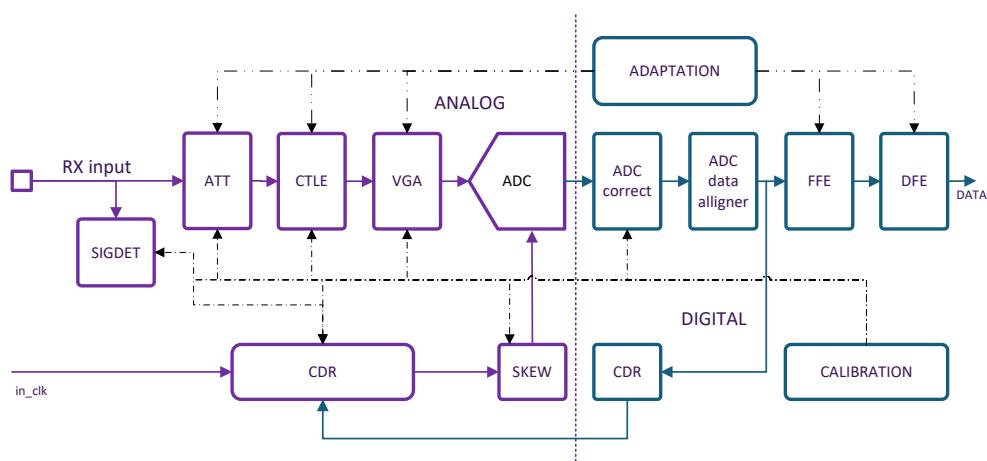

| 2.17 | Schema di un ricevitore                                                                                    | 20 |

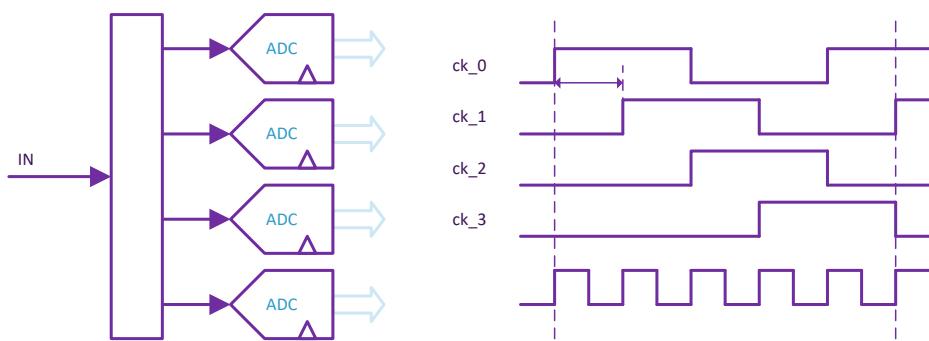

| 2.18 | Esempio di Analog to Digital Converter (ADC) interleaving                                                  | 21 |

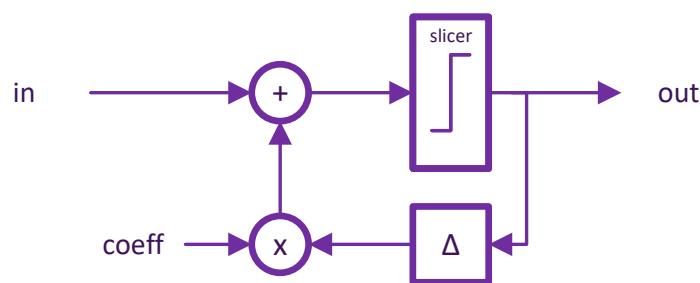

| 2.19 | Schema di funzionamento di un Decision Feedback Equalizer<br>(DFE)                                         | 22 |

| 2.20 | Esempio funzionamento DFE                                                                                  | 23 |

| 2.21 | Linear interpolator code mapping                                                                           | 25 |

| 3.1  | Esempio di sommario del Simulation Profiler                                                                | 30 |

| 3.2  | Esempio della vista Instance del Simulation Profiler                                                       | 31 |

| 3.3  | Struttura base del testbench                                                                               | 32 |

| 3.4  | Sommario sul tempo di simulazione iniziale della netlist GTECH                                             | 32 |

| 3.5  | Report dettagliato tempi di simulazione GTECH iniziale                                                     | 33 |

|      |                                                                                                |    |

|------|------------------------------------------------------------------------------------------------|----|

| 3.6  | Esempio di semplificazione applicata ad un filtro Finite Impulse Response (FIR) . . . . .      | 34 |

| 3.7  | Report del tempo di simulazione per <i>RX_FFE</i> . . . . .                                    | 35 |

| 3.8  | Report del tempo di simulazione per <i>RX_FFE</i> . . . . .                                    | 36 |

| 3.9  | Report del tempo di simulazione per <i>RX_FFE_CDR</i> . . . . .                                | 36 |

| 3.10 | Report del tempo di simulazione per <i>RX_FFE_CDR</i> . . . . .                                | 37 |

| 3.11 | Final Summary . . . . .                                                                        | 38 |

| 3.12 | Report dettagliato verilog nel caso complessivo . . . . .                                      | 38 |

| 4.1  | Schema di un tipico loop di calibrazione . . . . .                                             | 42 |

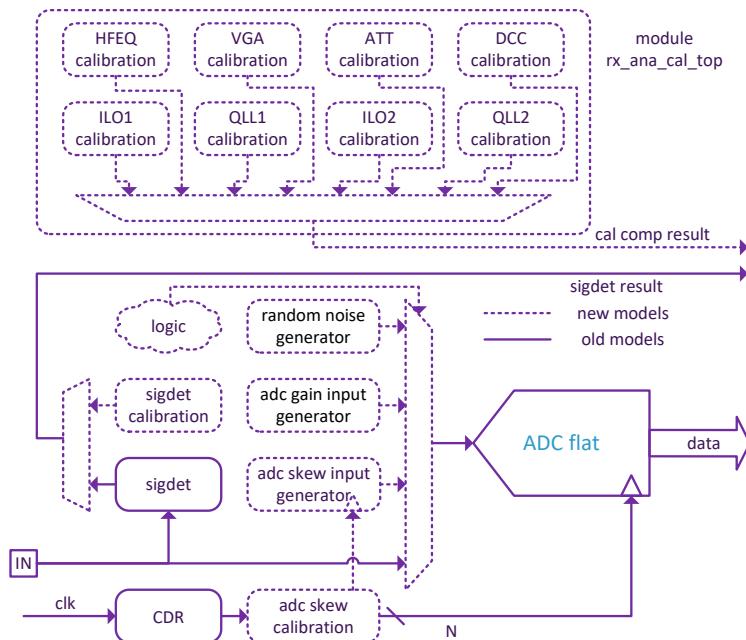

| 4.2  | Rappresentazione semplificata del modello <i>rx_ana_flat</i> . . . . .                         | 46 |

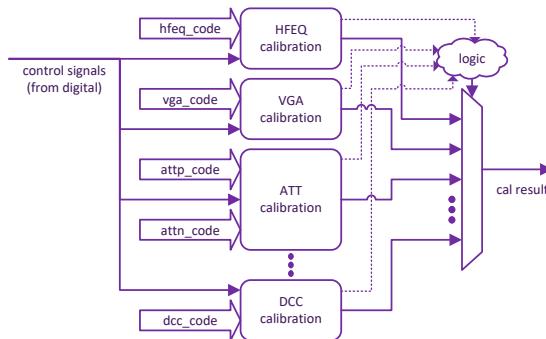

| 4.3  | Multiplexer per il risultato di calibrazione . . . . .                                         | 47 |

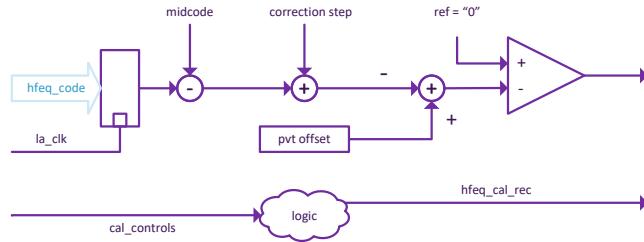

| 4.4  | Schema di funzionamento modulo High Frequency Equalizer (HFEQ) calibration . . . . .           | 48 |

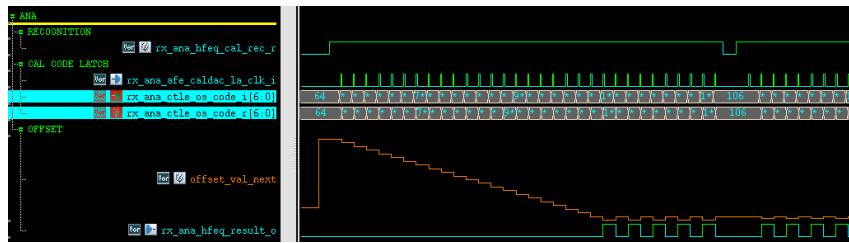

| 4.5  | Risultati simulazioni HFEQ calibration . . . . .                                               | 48 |

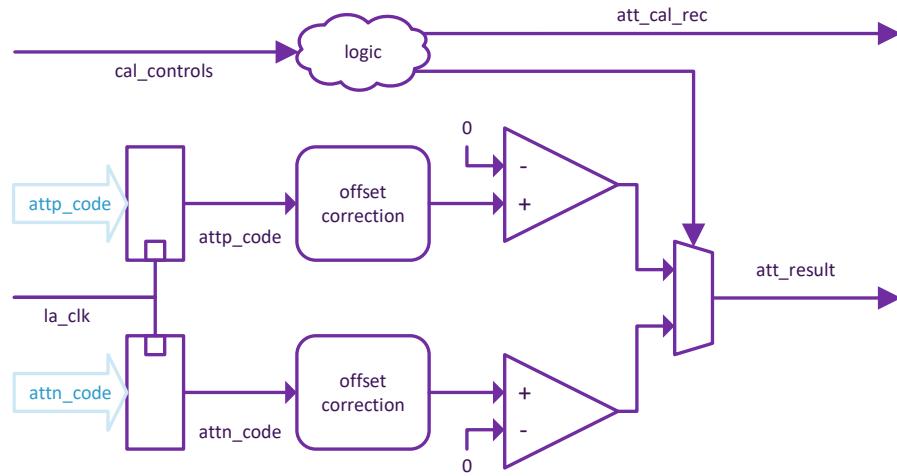

| 4.6  | Schema di funzionamento modulo Attenuator (ATT) calibration                                    | 49 |

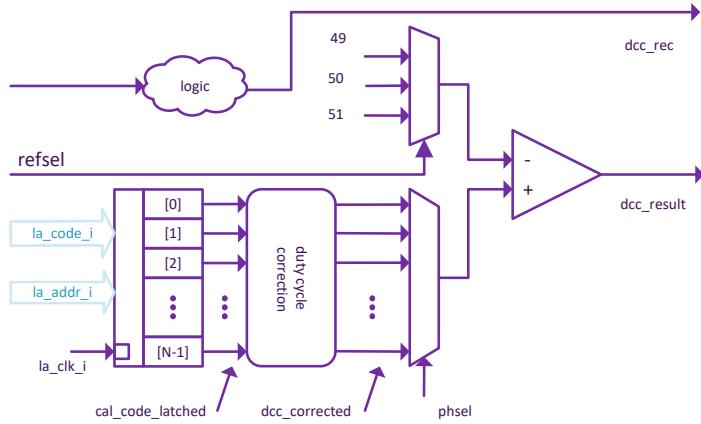

| 4.7  | Schema di funzionamento modulo Receiver (RX) Duty Cycle Correction (DCC) calibration . . . . . | 50 |

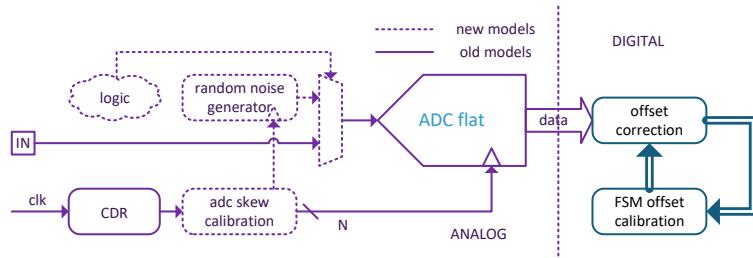

| 4.8  | Schema ADC offset calibration . . . . .                                                        | 51 |

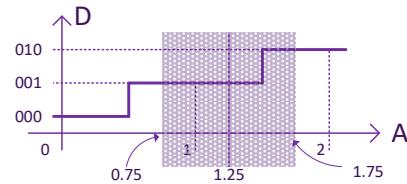

| 4.9  | Dithering sulla caratteristica dell'ADC . . . . .                                              | 52 |

| 4.10 | Schema ADC offset calibration . . . . .                                                        | 52 |

| 4.11 | Panoramica della calibrazione . . . . .                                                        | 53 |

| 4.12 | Schema di principio ADC Skew Calibration . . . . .                                             | 54 |

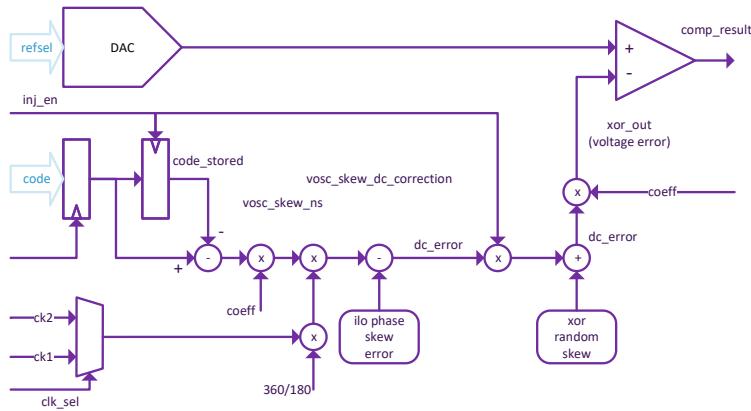

| 4.13 | Schema calibrazione Injection Locking Oscillator (ILO) . . . . .                               | 57 |

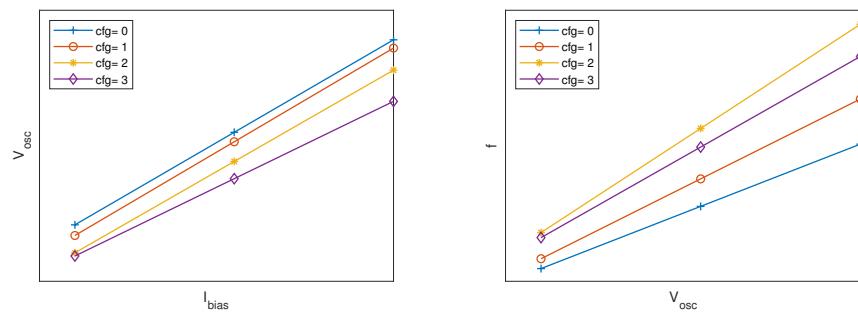

| 4.14 | Grafico caratteristica linearizzato oscillatore ILO . . . . .                                  | 57 |

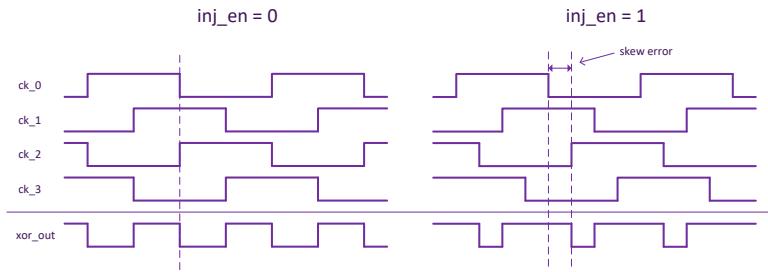

| 4.15 | Skew tra le fasi in uscita dell'ILO . . . . .                                                  | 59 |

| 4.16 | Diagramma calibrazione QLL . . . . .                                                           | 61 |

| 4.17 | Panoramica delle calibrazioni nel modello analogico flat del trasmettitore . . . . .           | 61 |

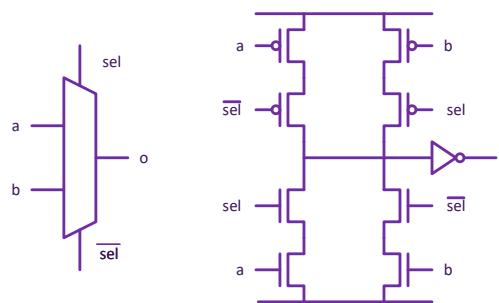

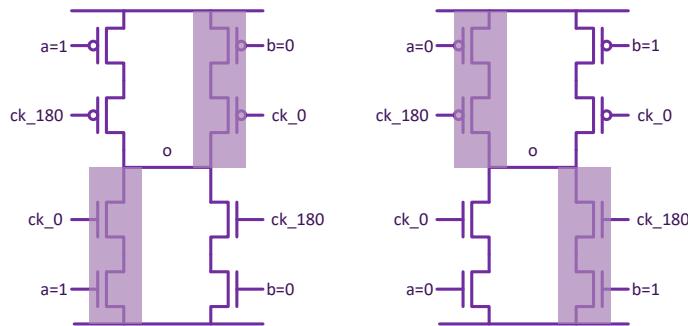

| 4.18 | Esempio di multiplexer utilizzato per la serializzazione . . . . .                             | 62 |

| 4.19 | Clock in uscita dal multiplexer in funzione dei pattern di ingresso                            | 63 |

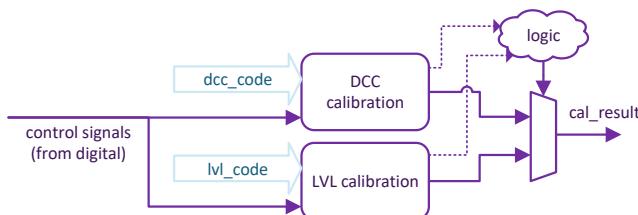

| 4.20 | Schema di funzionamento TX DCC calibration . . . . .                                           | 64 |

| 4.21 | Schema di principio LVL calibration . . . . .                                                  | 65 |

# Capitolo 1

## Introduzione e motivazioni

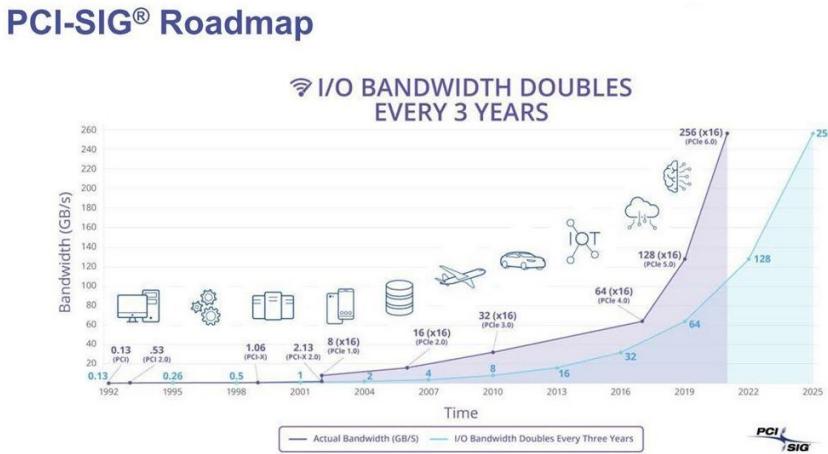

Il trend relativo alla domanda di prestazioni e alla banda di comunicazione nel mercato dei data center e dell'High-Performance Computing (HPC) mostra una crescita costante. Applicazioni come Artificial Intelligence (AI) e Machine Learning (ML) rappresentano un chiaro esempio dell'aumento dei volumi di calcolo e di trasferimento dati: i modelli moderni richiedono non solo una fase di training intensiva, ma anche elevate capacità di inferenza. Anche l'Internet of Things (IoT), con il numero sempre crescente di dispositivi connessi e il loro continuo scambio di informazioni, contribuisce ad accrescere ulteriormente il fabbisogno di banda e di potenza computazionale. Tutte queste applicazioni si prestano bene al Cloud Computing, ovvero all'elaborazione dei dati in remoto, con un conseguente aumento del carico sui data center.

Parallelamente, anche in settori come l'industria e l'automotive si osserva un incremento delle prestazioni e della banda di comunicazione richieste. Un esempio significativo è rappresentato dagli Advanced Driver Assistance Systems (ADAS), che per eseguire i propri algoritmi necessitano di un elevato numero di sensori e quindi di una grande mole di dati da processare. Queste applicazioni hanno guidato lo sviluppo tecnologico di dispositivi in grado di soddisfare le nuove esigenze del mercato.

Se da un lato lo sviluppo di System On Chip (SoC) allo stato dell'arte ha portato ad uno scaling tecnologico che ha permesso un incremento di prestazioni richiesto, ciò non può essere detto per ciò che si occupa di far comunicare il chip con il mondo esterno, come le interconnessioni chip-to-chip [3]. A causa di limiti fisici, lo scaling delle interconnessioni e dei packaging non è stato efficiente quanto quello sulla logica, diventando il collo di bottiglia principale nello sviluppo di un chip, portando al cosiddetto *pad-limited design*. Questo fenomeno è inoltre amplificato dal fatto che l'incremento di prestazioni si traduce in una maggior mole di dati da processare, stressando maggiormente i limiti delle interfacce di comunicazione.

Come mostrato in [figura 1.1](#) l'incremento della banda di comunicazione cresce in maniera esponenziale, in accordo con quanto accade per la densità di capacità di calcolo dei in un SoC.

Figura 1.1: I/O Bandwidth vs Year

L'utilizzo di tecniche di trasmissione parallela dei dati non sarebbe in grado di sostenere questo aumento di prestazioni. In questo genere di interfacce di comunicazione, sarebbe necessario agire principalmente sull'incremento del numero di pin e non sulla frequenza di lavoro. L'aumento del numero di pin è una opzione non sostenibile per diverse motivazioni, sia legate all'area e al non efficace scaling dei pin di IO di un die, sia su aspetti legati allo skew e al sincronismo tra i vari bit di un bus. [1] Immaginando infatti applicazioni dove sono presenti bus per connessioni chip-to-chip in un pcb, il routing potrebbe causare problematiche di skew e un non corretto allineamento dei dati da trasmettere, senza parlare di problematiche di crosstalk, potenza, interferenza elettromagnetica ...

Una tipologia di interfacce che permettono di assecondare la crescita di prestazioni senza risultare un collo di bottiglia sono le interfacce seriali, chiamate Ser-Des, attraverso le quali è possibile gestire l'incremento di velocità aumentando la frequenza di trasmissione. Lo stato dell'arte di questi dispositivi possiede una complessità non indifferente, al fine di sopprimere i vincoli che caratterizzano queste tipologie di interfacce di comunicazione. Ne è di esempio l'interfaccia PCIe, sviluppata e mantenuta dall'associazione Peripheral Component Interconnect - Special Interest Group (PCI-SIG), che al fine di adeguarsi alla richiesta di banda sempre maggiore ha visto un aumento della complessità del protocollo da una generazione alla successiva. Basta citare il passaggio dalla modulazione NRZ a quella PAM-4 [9]. Come possibile intuire, un dispositivo del genere per funzionare correttamente richiede l'implementazione di tecniche complesse, sia dal punto di vista comunicazionario, implementando algoritmi di Digital Signal Processing (DSP) ed equalizzazione avanzata per soccombere alle non idealità introdotte dai canali di trasmissione, sia dal punto di vista tecnologico che architetturale, al fine di garantire dei dispositivi che funzionino rispettando i vincoli Power Performance Area (PPA)

richiesti.

La progettazione di queste interfacce richiede architetture allo stato dell'arte, capaci di integrare componenti digitali complessi e blocchi analogici di precisione. Tale complessità si traduce in lunghi tempi di sviluppo e in una fase di verifica particolarmente onerosa. Per semplificare questo processo, i Ser-Des vengono spesso distribuiti sotto forma di Intellectual Property (IP), ovvero moduli riutilizzabili facilmente integrabili all'interno dei SoC, garantendo di accelerare il *silicon bring-up*.

In questo contesto si inserisce il presente lavoro di tesi, svolto in collaborazione con *Synopsys*, con l'obiettivo di incrementare le prestazioni delle simulazioni di sistemi Ser-Des PCIe. Synopsys si occupa della progettazione di IP Physical Layer (PHY) PCIe 6.0 che consentono connettività real-time a bassa latenza e ad elevato throughput per HPC, storage, e AI SoCs.

L'IP sviluppato da Synopsys sul quale si basa l'elaborato consiste nell'implementazione del PHY, ovvero il layer a più basso livello che comprende la parte digitale e la parte analogica, che chiameremo rispettivamente *macro digitale* e *macro analogica*. È possibile effettuare una distinzione anche tra *soft macro* e *hard macro*. La prima è quella parte di cui è implementata sotto forma di Register Transfer Level (RTL) sintetizzabile, la cui sintesi e P&R è a discrezione del customer. La seconda è invece fornita al cliente sotto forma di layout già completamente testato e implementato nella tecnologia di riferimento, utilizzata in quelle parti soggette ad una maggiore complessità implementativa, come le parti di datapath digitali ad alta velocità e la macro analogica.

Per l'azienda risulta fondamentale riuscire a verificare i suoi IP per fornire il miglior servizio possibile ai customer che li acquistano. Da ciò nasce la necessità della prima parte del lavoro di tesi, ovvero lo speed-up di una netlist del circuito digitale, basata su una libreria *technology independent*, chiamata Generic Technology (GTECH). Questa tipologia di netlist è spesso fornita ai clienti che richiedono un IP come alternativa ai file sorgente RTL, in modo da proteggerne la proprietà intellettuale. Esse sono utilizzate dai customer per effettuare simulazioni a livello SoC, cioè alto livello, che non richiedono una simulazione completa di tutta l'architettura, ma solamente le parti necessarie a comprendere come il PHY è integrato nella loro architettura.

La crescente complessità nell'architettura di un Ser-Des si traduce in una complessità maggiore della fase di validazione, test e debug dell'IP. Non basta solamente una verifica funzionale della logica digitale, ma risulta fondamentale anche l'integrazione di strumenti che permettano la co-simulazione di firmware e logica digitale ed analizzarne la loro interazione con la macro analogica. Un requisito fondamentale per queste simulazioni è la velocità, è facile intuire infatti in ambito firmware i tempi di simulazione richiesti possano essere elevati e utilizzare modelli analogici complessi non è sostenibile in questi contesti. In questo contesto è possibile utilizzare dei modelli *flat*, che descrivono la parte

analoga in maniera comportamentale, per velocizzare le simulazioni. Il lavoro quindi che si svolgerà in nella seconda parte della tesi è quello di ampliare questi modelli comportamentali, focalizzandosi sullo sviluppo tutti quegli aspetti necessari a supportare la co-simulazione delle procedure di calibrazione. L'obiettivo quindi di questi modelli è quello di fornire un degli strumenti aggiuntivi di supporto al team, accelerando i tempi di debug e rendendo possibile l'analisi di corner-case critici.

Per guidare nella lettura della tesi in seguito è riportata una descrizione di come è stato strutturato l'elaborato:

- il [capitolo 2](#) presenta una panoramica dello stato dell'arte delle architetture SerDes, illustrando le principali strategie adottate sia nella parte digitale sia in quella analogica. L'obiettivo è chiarire sfide e complessità tipiche di queste architetture e fornire una base per gli sviluppi affrontati nei capitoli successivi.

- Il [capitolo 3](#) descrive gli interventi effettuati per ottenere uno speed-up sulle simulazioni della netlist GTECH, spiegando il contesto, le modifiche RTL apportate e i benefici ottenuti in termini di performance simulativa.

- Il [capitolo 4](#) approfondisce il tema delle calibrazioni nella progettazione analogica e descrive la realizzazione dei modelli flat comportamentali. In questo modello si parte da una introduzione su come i meccanismi di calibrazione agiscono in un dispositivo di questo tipo, descrivendo le tecniche implementative e le soluzioni utilizzate. Al termine del capitolo mostra i risultati ottenuti e quanto questi modelli possano portare a miglioramenti effettuando dei confronti con altre soluzioni e modelli.

- Infine, il [capitolo 5](#) di conclusione che riassume i risultati ottenuti e gli sviluppi futuri.

# Capitolo 2

## Panoramica sui Ser-Des e PCIe

Lo scopo di questo capitolo è fornire una panoramica sul mondo degli High Speed Ser-Des (HS Ser-Des), al fine di chiarire le principali circostanze e sfide che caratterizzano un sistema di trasmissione ad alta velocità. Il capitolo è strutturato in una prima parte dedicata ai concetti generali, seguita dalla descrizione di un'architettura base di trasmettitore e ricevitore. Vengono illustrate le criticità principali e introdotte le motivazioni che giustificano la presenza di specifici blocchi di calibrazione, i cui modelli analogici sono implementati nella seconda parte del presente lavoro di tesi.

### 2.1 Ser-Des

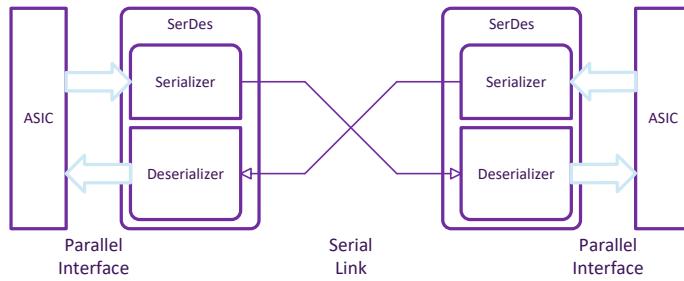

Un Serializer-Deserializer (Ser-Des) è un blocco che si occupa di serializzare e deserializzare i dati in comunicazioni chip-to-chip ad alta velocità [8]. Nel caso in cui è necessario effettuare una connessione tra due Application Specific Integrated Circuit (ASIC), il Ser-Des interviene effettuando la conversione di dati da parallelo a seriale, la trasmissione sul canale e la riconversione in parallelo per consentire all'ASIC a valle di poter interpretare i dati ([figura 2.1](#)). Il ruolo principale di un serdes è quello di minimizzare il numero di pin I/O di un IC, parti che hanno un rilevante impatto al fine di contenere i costi e l'area di Integrated Circuits (ICs), senza compromettere le prestazioni e introdurre colli di bottiglia nella trasmissione dei dati.

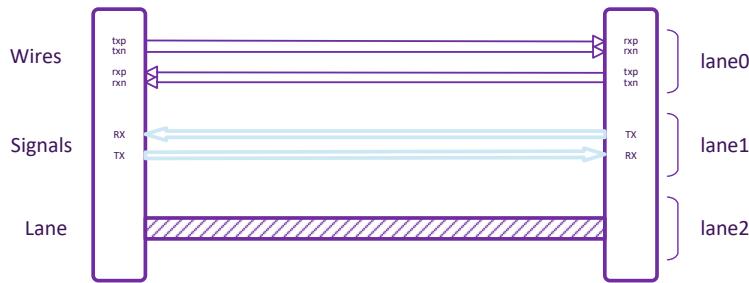

In generale, in un Ser-Des è possibile identificare una struttura composta da un numero variabile di *lane* ([figura 2.2](#)). Ogni lane rappresenta un canale di trasmissione dati seriale indipendente ed è costituita da una coppia di ricetrasmettitori, al fine di consentire una connessione *Full Duplex*. L'utilizzo di più lane in parallelo consente di aumentare la velocità di trasmissione suddividendo i dati tra più canali fisici.

Un esempio ne è lo standard di comunicazione seriale PCIe che permette di ottenere una connessione di tipo point-to-point per connessioni ad alta velocità.

Figura 2.1: Struttura base di un Ser-Des

Figura 2.2: ogni lane è composta da un segnale differenziale per i dati da trasmettere e da ricevere, nel complesso sono presenti due flussi di dati, uno per il ricevitore e uno per il trasmettitore.

Nasce come una evoluzione della sua antenata interfaccia parallela Peripheral Component Interconnect (PCI) ed è stata sviluppata dal consorzio PCI-SIG.

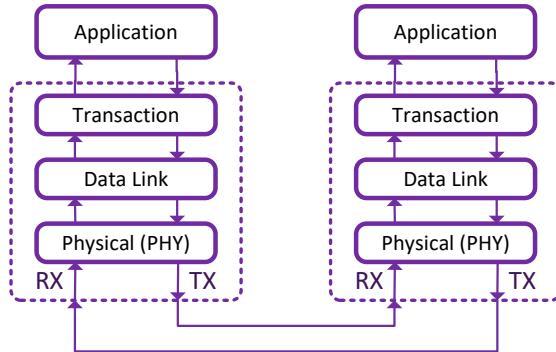

Lo standard PCIe è composto da una serie di layer di astrazione [9], come mostrato in [figura 2.3](#):

- **Application Layer:** questo è il layer più esterno, esso è chiamato anche host layer e non è definito dallo standard, ma dipende dal tipo di applicazione. Nello specifico è il blocco che genera le richieste di comunicazione e interpreta le risposte;

- **Transaction Layer:** Questo è il primo vero e proprio layer che gestisce la configurazione del dispositivo e la trasmissione dei dati da e verso la memoria;

- **Data Link Layer:** questo layer si occupa della gestione e della creazione dei pacchetti, nonché della verifica della loro integrità. In questa fase è possibile applicare tecniche di codifica dei dati, come la Forward Error Correction (FEC), che permettono di migliorare l'affidabilità della trasmissione. Nelle generazioni più recenti, come la Gen6, l'adozione

Figura 2.3: PCIe Layers

di meccanismi di correzione degli errori risulta fondamentale per ridurre il tasso di errore. Inoltre, è a questo livello che viene stabilito se un pacchetto contenente errori debba essere ritrasmesso;

- **Physical layer (PHY):** è il livello più basso del protocollo e consiste in tutte le componenti analogiche e digitali che permettono di trasformare i bit in arrivo dai layer superiori in un segnale elettrico da trasmettere e viceversa riuscire a trasformare il segnale elettrico in informazioni da inviare ai layer superiori.

Per avere chiarezza delle prestazioni di un IP PCIe 6 è possibile analizzare le seguenti specifiche:

- velocità di trasferimento fino a 64 Gbps per singola lane (da considerare come raw bits);

- da x1 a x16 lane, per una velocità di 128GBps in configurazione x16;

- retrocompatibilità con tutte le altre generazioni;

- passaggio dalla modulazione NRZ a PAM-4, per incrementare le prestazioni senza aumento di banda;

- introduzione di codifica FEC per la mitigazione del BER;

### Modulazione PAM-4

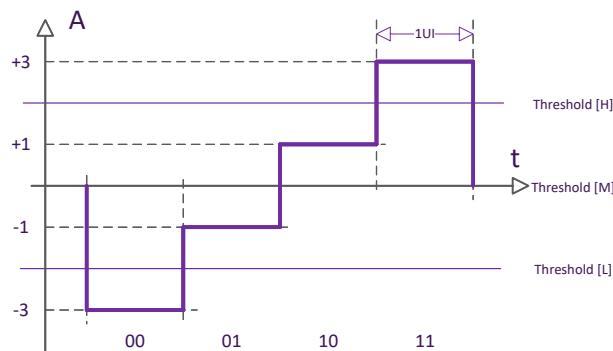

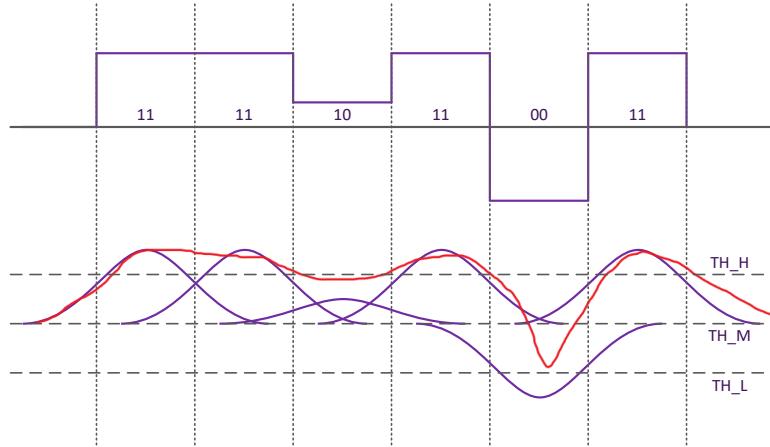

A differenza delle precedenti generazioni, per poter garantire la velocità di trasmissione richiesta delle specifiche, viene implementata una modulazione Pulse Amplitude Modulation - 4 (PAM-4). Grazie a essa è possibile raddoppiare il bit-rate senza modificare il baud-rate, e quindi mantenendo invariati

i requisiti di banda del canale di trasmissione. Questa codifica permette di poter codificare con un singolo simbolo 2 bit, su quattro livelli di tensione differenti([figura 2.4](#)).

La presenza di 4 livelli differenti di tensione fa sì che, a differenza di una codifica NRZ, ci siano ben 3 soglie per la decisione del simbolo.

Figura 2.4: Esempio di modulazione PAM-4

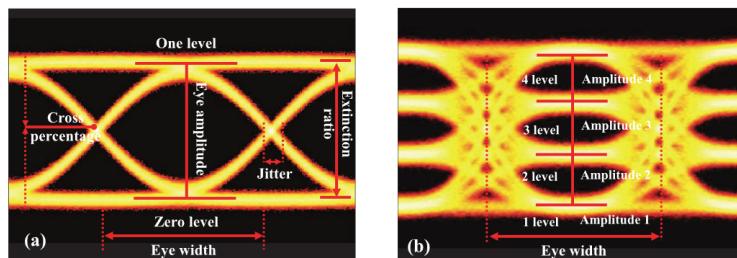

Figura 2.5: a) modulazione NRZ, b) modulazione PAM-4

Il diagramma ad occhio in [figura 2.5](#) mostra chiaramente le criticità e difficoltà che risiedono nell'utilizzo della codifica PAM-4, quella principale riguarda i margini di rumore ridotti e quindi alla prossimità tra le varie soglie. Confrontandolo con la codifica NRZ si nota come l'apertura del diagramma ad occhio sia nettamente diminuita.

L'assegnazione tra l'ampiezza dei simboli da trasmettere ai bit può già essere un primo punto che consente la riduzione degli errori. Una assegnazione come in [figura 2.4](#) presenta infatti una criticità: se ad esempio a causa di un errore il simbolo "+1" non è in grado di oltrepassare la soglia "M" ed è riconosciuto come il simbolo "-1" si causa un errore di 2 bit. L'utilizzo di una codifica Gray che implica il cambiamento di un solo bit tra un livello e il successivo, porta ad ottenere un solo bit di errore.

L'architettura di un IP Ser-Des che sfrutta la codifica PAM-4 risulta molto complessa e con numerose tecniche che permettono di ricostruire in maniera accurata il segnale.

## 2.2 Problematiche di un High Speed Ser-Des

Architetture sempre più complesse usate per ottenere velocità di trasmissione maggiori mettono alla luce una serie di criticità e non idealità durante la progettazione di un High Speed Ser-Des (HS Ser-Des). Ad esempio l'introduzione della codifica PAM-4 porta ad una sensibilità maggiore al rumore, dato che anche una minima variazione sul simbolo porta ad una non corretta discriminazione di ciò che è stato trasmesso. Lo scopo di questa sezione è quello di analizzare le principali sorgenti di errore in un HS Ser-Des per comprendere al meglio come una architettura è sviluppata.

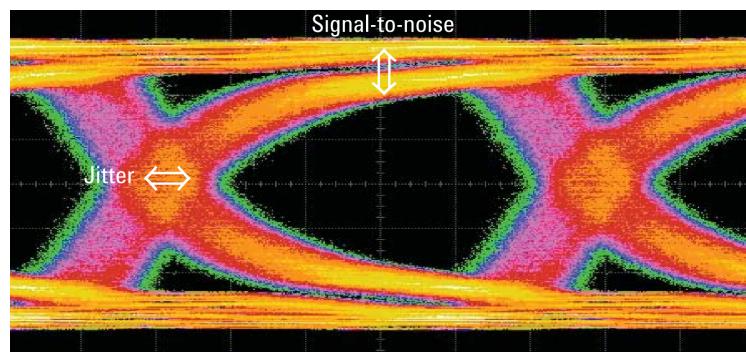

Figura 2.6: Diagramma ad occhio di un segnale affetto da distorsione [10]

Le motivazioni principali risiedono nella presenza di non idealità che derivano da punti di vista differenti. In figura 2.6 è possibile distinguere due principali tipologie di errori: il Signal to Noise Ratio (SNR) (gli errori che influenzano l'ampiezza del simbolo) e il *jitter* (errori dovuti al punto in cui il simbolo è campionato). Entrambi portano al medesimo risultato: il livello di tensione che associa al simbolo nel punto in cui è campionato, è differente da quello ideale, oltrepassando la soglia di discriminazione del simbolo e causando un aumento del Bit Error Rate (BER). Successivamente sono descritte le sorgenti che causano queste non idealità.

### 2.2.1 Inter Symbol Interference

Una importante non idealità su cui bisogna focalizzare l'analisi è quella che riguarda il canale di trasmissione. La non idealità che presenta un generico canale di trasmissione riguarda la sua banda limitata. La presenza di elementi resistivi e reattivi, rende fisicamente impossibile ottenere un canale con una banda sufficientemente grande da essere considerata illimitata.

Come enunciato nei principi di teoria dei segnali se il simbolo presente in ricezione possiede una banda limitata, avrà un supporto temporale illimitato. A titolo di esempio è possibile notare in figura 2.7 come i quattro simboli

Figura 2.7: Simbolo distorto a causa di banda limitata

di una modulazione PAM-4 ideale risultano in uscita da un canale a banda limitata.

Figura 2.8: Esempio di simbolo in uscita in un canale non ideale

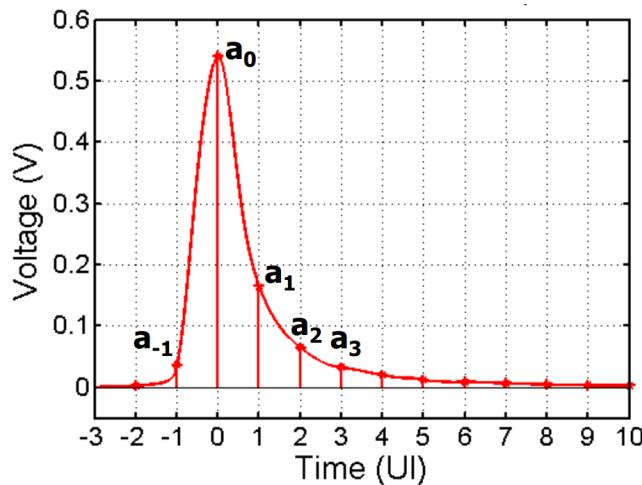

Considerando un simbolo isolato  $x[n]$  e trasmettendolo attraverso il canale di trasmissione è possibile notare come anche a distanza superiore ad  $1UI$ , dove per  $UI$  si intende la distanza tra un simbolo e il successivo, siano ancora presenti dei contributi in tensione dovuti a esso (figura 2.8). Questi contributi sono classificati in questo modo:

- **Precursors:** tutti quei contributi che si presentano nei campionamenti precedenti ( $a_{-1}, a_{-2}, \dots$ );

- **Cursor:** il contributo effettivo dovuto al simbolo attualmente ricevuto, cioe  $a_0$  che si trova a  $0UI$ ;

- **Postcursors:** sono i contributi che andranno ad interferire nei simboli che sono trasmessi dopo il simbolo attuale ( $a_{n+1}, a_{n+2}, \dots$ ).

Da questo si evince poi che trasmettendo una moltitudine di simboli tutti a distanza di  $1UI$  i contributi di tutti i simboli continuano a sommarsi rendendo

impossibile determinare il corretto livello del simbolo e generando un errore in ricezione ([figura 2.9](#)). Da qui nasce il fenomeno di Inter Symbolic Interference (ISI).

Figura 2.9: Esempio di errore di trasmissione dovuto all'ISI

Tale problematica si considera responsabile di una riduzione del BER e una chiusura del EYE Diagram. In questo caso il livello di ogni simbolo può non rientrare all'interno dei margini di rumore prefissati e quindi può portare all'interpretazione errata. Questo fenomeno emerge maggiormente nelle comunicazioni i cui simboli sono discretizzati con un numero maggiore di livelli e ravvicinati tra loro, come nella codifica PAM-4.

Tramite il diagramma ad occhio in [figura 2.10](#) è possibile notare come l'ISI influenza il valore in cui viene campionato il simbolo.

Figura 2.10: Eye Diagram per un canale di trasmissione con ISI

### 2.2.2 Jitter e Skew

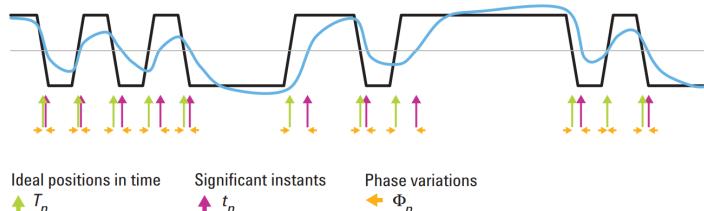

Come stato discusso la motivazione che porta all'analisi del jitter in un sistema di comunicazione ad alta velocità è legato a contenere l'aumento del BER.

Figura 2.11: Esempio di come il jitter influenza il campionamento del segnale in ricezione

La definizione enuncia che il jitter è definito come variazione di fase rispetto alla sua posizione ideale. Da questo si deduce che il jitter può essere cruciale nel campionamento di un segnale.

Figura 2.12: Differenza tra jitter casuale e deterministico

Esistono differenti tipologie di jitter, a seconda delle sorgenti e del comportamento, come si evince in [figura 2.12](#):

- **Random Jitter (RJ):** È la tipologia di jitter dovuta a delle sorgenti di rumore casuali, la Probability Density Function (PDF) di questa tipologia di jitter infatti è tipicamente una gaussiana. Le sorgenti di questo rumore sono innumerevoli, possono derivare da phase noise, thermal noise, amplitude noise, ...

In questa tipologia di jitter risulta impossibile definire una ampiezza picco-picco, ma si utilizzano concetti di media e deviazione standard [10];

- **Deterministic Jitter (DJ):** Questa tipologia di jitter è causata da una sorgenti di anche ampia entità. È definito come deterministico a causa del fatto che, in teoria, conoscendo il sistema sarebbe possibile stimare la sua entità. Esempi di sorgenti di DJ sono interferenze elettromagnetiche, riflessioni sul canale, ISI; come tutte quei fenomeni deterministiche che possono portare ad una variazione in ampiezza del segnale, ma che spostano il punto di campionamento del segnale rispetto ad una certa soglia. A sua volta può essere distinto in:

- **Periodic Jitter (PJ):** quella tipologia di jitter che si ripete in maniera periodica, dovuta ad effetti come *spread spectrum clock* o *feedthrough* del reference clock del Phase Locked Loop (PLL).

- **Data Dependant Jitter (DDJ):** Soni i contributi di jitter legati ai dati trasmessi, conoscendo:

- \* **ISI:** contributo legato alle non idealità del canale di trasmissione e alla sovrapposizione dei simboli

- \* **Duty Cycle Distortion (DCD):** in questo caso errori di Duty Cycle portano ad una non corretta durata dei simboli, ( esempio [sottosezione 2.4.3](#) ) .

- **Bounded Uncorrelated Jitter (BBJ):** Non dipende direttamente dai dati trasmessi, ma è legato a fenomeni come il crosstalk, generano una variazione in ampiezza che si traduce in una variazione di jitter del segnale dei dati.

## 2.3 Equalization e Adaptation

In precedenza è stato detto che le non idealità del canale possono portare conseguenze sulla trasmissione delle informazioni. Esistono quindi una serie di strategie utilizzate per mitigare questi effetti, al fine di ottenere una risposta in frequenza costante sul canale.

Le principali strategie introdotte riguardano una serie di filtri analogici e digitali, studiati al fine di ottenere una migliore risposta possibile:

- TX FFE, ovvero un filtro digitale che permette effettuare un boost delle alte frequenze prima di trasmettere il segnale, esso permette di compensare il comportamento passa basso del canale;

- RX CTLE + RX VGA, filtro lineare analogico in ricezione composto che ha un filtro passa alto permette di effettuare un'attenuazione delle basse frequenze, e poi grazie all'amplificatore amplificare a valle tutto il segnale ricevuto per ristabilire i livelli corretti.

- RX FFE, filtro digitale lineare volto alla rimozione di ISI agendo sui termini lineari.

- RX DFE, filtro che permette di compensare anche le non linearità del canale di trasmissione, e che punto agisce in maniera non lineare.

Tutti questi elementi verranno introdotti in seguito. Questi strumenti sono utilizzati al fine di correggere le non idealità lineari e non lineari del canale.

Ognuno di questi elementi presenta dei coefficienti, e il valore di ognuno di questi deve essere scelto in modo da ottenere una risposta in frequenza complessiva che sia costante al variare della frequenza. È possibile dedurre quindi che tutti questi valori dipendano dalla effettiva risposta in frequenza del canale di trasmissione.

In alcuni casi possono esistere dei preset per questi coefficienti, in altri, è necessario implementare determinati algoritmi in hardware, che permettono di valutare il set migliore di coefficienti che portano ad un occhio ben aperto. Queste algoritmi fanno parte delle procedure di adaptation del Ser-Des.

## 2.4 Phisical Layer: Lane Transmitter

Il trasmettitore è il blocco presente all'interno della lane che si occupa della serializzazione dei dati e della loro conversione nel segnale che verrà effettivamente trasmesso, rappresentando di fatto l'interfaccia diretta con il canale di comunicazione. Esso è composto da una parte digitale, la cui responsabilità principale riguarda l'elaborazione dei dati, e da una parte analogica, che genera il segnale modulato secondo lo schema PAM-4.

Data la complessità e le criticità evidenziate nel capitolo precedente, si rende necessario introdurre alcuni sistemi e tecniche che permettano di mitigare tali problematiche, riducendole al minimo. In [figura 2.13](#) è possibile vedere una tipica implementazione di questo blocco.

Figura 2.13: Schema a blocco tipico di un trasmettitore

In seguito sono descritti i vari blocchi fondamentali.

### 2.4.1 Encoder

Lo stadio di encondig può avere un ruolo rilevante durante il progetto di un sistema. Alcune delle motivazioni che richiedono l'introduzione di uno stadio di codifica sono le seguenti:

- garantire il bilanciamento della componente continua (DC).

- assicurare transizioni sufficienti per il clock recovery.

- rilevare e correggere errori.

Esistono diverse tipologie di codifica che presentano differenti vantaggi e svantaggi. Un semplice esempio, usato dalle prime generazioni di PCIe, è

la codifica  $8b/10b$ , una codifica ridondante, che introduce degli overhead in termini di bit trasmessi. Bisogna precisare che a seconda della generazione gli stadi di codifica possono essere anche presenti in nei layer superiori.

In questo stadio, nel caso di modulazione PAM-4, può essere anche introdotta la *Codifica Gray* che consente di ridurre il numero di transizioni tra i bit di due simboli adiacenti, al fine di ridurre l'errore nel caso in cui un simbolo non venga riconosciuto correttamente.

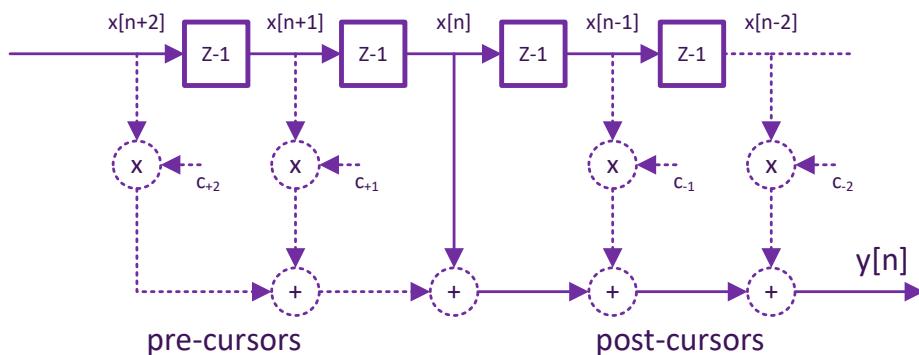

### 2.4.2 TX FFE

Come descritto in precedenza, nel trasmettitore è necessario effettuare una predistorsione del segnale in modo da enfatizzare le alte frequenze e garantire in uscita dal canale un segnale con un Eye Diagram che riporta determinate caratteristiche, riuscendo a compensare l'ISI. Il Transmitter (TX) Feed Forward Equalizer (FFE) è il dispositivo utilizzato a questo scopo. La struttura base di questo componente è quella di un filtro FIR digitale, come mostrato in figura 2.14.

Figura 2.14: Struttura tipica di un fir

L'equazione (2.1) rappresenta la classica equazione di un filtro FIR

$$y[n] = \sum_{i=-N}^{i < M} c_i \cdot x[n+i] \quad (2.1)$$

dove  $N$  indica il numero di *Postcursors*, ovvero i taps introdotti per la correzione dell'ISI relativa ai simboli precedentemente inviati, e  $M$  indica il numero di *Precursors*, ovvero i taps relativi ai che sono stati inviati dopo il simbolo attuale.

I vari coefficienti  $c_i$  saranno calcolati durante la fase di adattamento e dipendono, in maniera intuitiva, da quanto siano elevati i valori residui derivati dai simboli adiacenti a quello attuale.

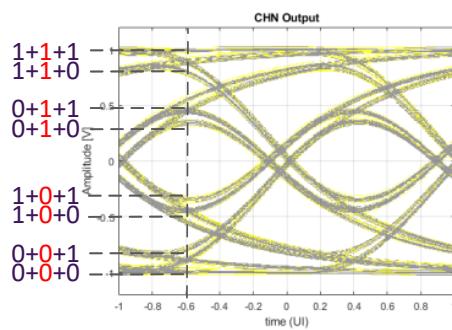

Figura 2.15: Esempio di funzionamento di un FFE

Un esempio di possibile segnale di ingresso e uscita è mostrato in [figura 2.15](#). In questo caso per semplicità è stato considerato un FFE con 2 tap, un postcursor e un precursor. Ad esempio, nel terzo simbolo inviato, "01" la sua ampiezza è stata aumentata visto che i simboli adiacenti possiedono una ampiezza di segno opposto.

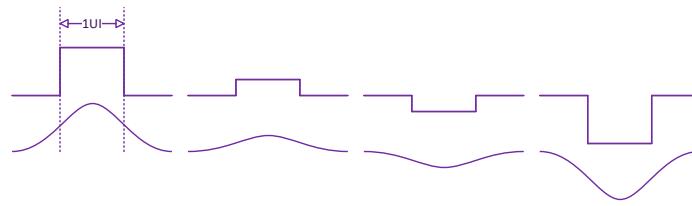

### 2.4.3 Serializer

Il serializer è quella parte del dispositivo che si occupa di una trasformazione dei dati da un formato parallelo a seriale ([figura 2.16](#)). In ingresso al serializzatore arrivano i simboli in formato parallelo generati in uscita dal FIR.

Questa serializzazione dei dati è effettuata tramite una serie di multiplexer 2 to 1 che seleziona i dati in relazione al clock di ingresso. Si nota come ogni stadio di multiplexer possiede come selettore una versione divisa del clock di ingresso.

In questa configurazione è possibile notare come un Duty Cycle non ideale possa portare a delle distorsioni sul segnale trasmesso, in particolare sul multiplexer finale che possiede un clock 2UI.

Infatti quando il clock assume valore alto sono riportati in uscita i simboli "pari" e nel caso opposto quelli di ordine "dispari". Se il duty cycle non assume un valore del 50% esiste la possibilità che non tutti i simboli abbiano una durata di 1UI, non garantendo, in ricezione, il campionamento dei dati nel punto ottimale, generando gli errori di DCD jitter. Nei capitoli successivi verrà discusso una particolare calibrazione con l'obiettivo di mitigare questo problema.

### 2.4.4 Digital to Analog Converter

In questo caso tramite un Digital to Analog Converter (DAC) è possibile riuscire a convertire il simbolo generato in un livello di tensione da trasmettere

Figura 2.16: Schema di principio di un serializzatore a 8 ingressi

al canale.

Data la presenza dell'equalizzatore FFE i livelli effettivi di segnale generati in uscita non sono solo i quattro possibili ottenibili dalla codifica PAM-4, ma è necessario codificarli con un numero superiore di bit.

Inoltre è necessario ricordare che in uscita ogni lane trasmette il segnale in maniera differenziale.

#### 2.4.5 Duty Cycle Correction

Come anticipato precedentemente il blocco di Duty Cycle Correction (DCC) si occupa di regolare il Duty Cycle del clock necessario al serializzatore. La sua interfaccia possiede un codice di calibrazione che, opportunamente impostato dalla logica digitale, permette una correzione del duty cycle.

## 2.5 Phisical Layer: Lane Receiver

La struttura base di un ricevitore è solitamente più complicata di quella di un trasmettitore, infatti si ha la necessità di dover ricostruire il segnale. In aggiunta sarà presente anche un blocco di Clock Data Recovery (CDR), il quale permette di allineare il clock di riferimento con i dati.

In [figura 2.17](#) è presente la tipica architettura di un ricevitore, le cui parti verranno dettagliate in seguito:

Figura 2.17: Schema di un ricevitore

### 2.5.1 CTLE

Il Continuos Time Linear Equalizer (CTLE) (nella trattazione chiamato anche HFEQ) è un filtro utilizzato per contrastare l'effetto dovuto al naturale comportamento a banda limitata del canale di comunicazione. Il suo compito principale è quello di amplificare le alte frequenze, che vengono attenuate dal canale. Il comportamento reale di questo filtro è assimilabile a quello di un filtro passa-alto, ovvero attenua le componenti a bassa frequenza per equalizzare a quelle ad alta frequenza.

Dato che il canale non è conosciuto a priori, è necessario effettuare una procedura di *adaptation/equalization* per eseguire il tuning della funzione di trasferimento del filtro.

### 2.5.2 VGA

Il Variable Gain Amplifier (VGA) è utilizzato all'interno del ricevitore per amplificare il segnale proveniente dal CTLE, infatti il segnale in uscita dal CTLE risulta attenuato, ed è necessario ristabilire un livello di ampiezza adeguato.

### 2.5.3 ADC

L'Analog to Digital Converter (ADC) presente in questo ricevitore ha la necessità di essere ad elevate prestazioni, data la necessità di avere un elevato throughput. Per questa motivazione l'architettura sfrutta la strategia del *Timing Interleaving*: al fine di massimizzare le prestazioni è possibile utilizzare differenti ADC (figura 2.18), che lavorano in modo sfasato e alternato nel tempo, riuscendo ad incrementare la frequenza di campionamento complessiva, simulando un ADC complessivo con prestazioni più elevate.

Figura 2.18: Esempio di ADC interleaving

Anche se non sono richieste prestazioni e latenze ridotte per ogni singolo ADC, è comunque presente una certa criticità nei segnali di clock generati, dato che lo sfasamento tra ognuno di essi è legato fortemente alla distanza tra un simbolo e il successivo. Da ciò è possibile dedurre come lo skew tra le varie fasi diventa un elemento determinante, visto che è il responsabile del campionamento dei simboli in ingresso. Avere uno sfasamento non perfettamente ideale causa un campionamento non ottimale dei dati in ingresso, portando ad una non perfetta determinazione dei simboli.

### 2.5.4 RX FFE

Anche nel ricevitore la presenza di interferenza intersimbolica risulta necessita di essere attenuata tramite un Feed Forward Equalizer (FFE).

Il funzionamento di base è uguale a quello proposto nel TX FFE (sottosezione 2.4.2), solo che in questo caso il calcolo dell'ISI è effettuato considerando i campioni che arrivano dall'ADC.

I valori dei *precursors* e *postursors* sono valutati durante la fase di adaptation.

Il valore del simbolo attuale viene calcolato compensando il contributo di ISI che ci si aspetta, considerando i simboli precedenti e successivi. Per fare un esempio il contributo  $c_{-1} \cdot x[n - 1]$  sarà uguale in ampiezza al contributo di ISI presente simbolo attuale, dovuto al simbolo precedentemente inviato, ma avrà segno opposto, e così via con tutti i tap considerati nell'FFE.

È possibile affermare, contrariamente a quanto avviene nel trasmettitore, i simboli non sono più codificati sui 4 livelli tipici del PAM-4, ma su un numero elevato di bit. Questo evidenzia la presenza di alcune problematiche, ovvero che i contributi di correzione di ISI valutati da questo filtro sono calcolati considerando i simboli in ingresso ancora distorti, ovvero contenete del rumore/crosstalk o a sua volta, altri contributi di interferenza intersimbolica[5].

Basti pensare ad esempio che se un simbolo precedente o successivo presenta un contributo di rumore/crosstalk esso sarà anche riportato su tutti gli altri simboli adiacenti.

### 2.5.5 DFE

Il DFE è un equalizzatore non lineare integrato all'interno del ricevitore, impiegato per consentire la riduzione dell'ISI. La necessità di introdurre un sistema di questo tipo nasce dal fatto che l'utilizzo di un equalizzatore lineare, come l'FFE utilizzato nello stadio precedente, non è sufficiente a compensare i contributi del canale dovuti alla presenza di riflessioni, connettori, ... o altre non idealità presenti nella risposta in frequenza del canale [6].

Figura 2.19: Schema di funzionamento di un DFE

Un rilevante vantaggio nell'utilizzare un equalizzatore di questo tipo risiede nella capacità di non introdurre rumore, dato che i dati che arrivano dal feedback sono quelli discretizzati ottenuti a valle del decisore [5] . L'architettura base è mostrata in figura 2.19.

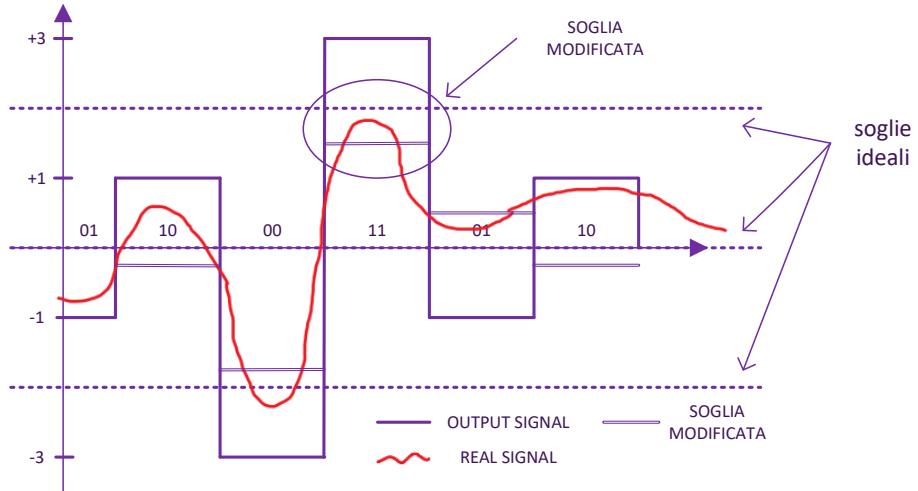

In sostanza il dispositivo in questione agisce modificando i Decision Level (D-Lev), ovvero le soglie di decisione del protocollo PAM-4 in funzione dei dati precedentemente ricevuti quindi delle decisioni prese in precedenza.

Figura 2.20: Esempio funzionamento DFE

Per chiarire il funzionamento è possibile analizzare il comportamento riportato in figura 2.20: ipotizzando che il simbolo attuale sia " + 3 " (codifica i bit 11) e il simbolo precedentemente ricevuto sia stato " - 3 ", ci si aspetta che il simbolo attuale, abbia un forte contributo di ISI, che agisce riducendo il suo valore effettivo, rendendo impossibile superare la soglia predisposta. Il DFE agisce, tramite l'informazione del simbolo precedentemente ricevuto, introducendo un termine di correzione all'ingresso del decisore che può essere visto come una riduzione delle soglie [7].

Come si nota in figura 2.19, nel percorso è presente un loop, e questo può portare a problematiche nei vincoli di timing, si ricorda infatti che solitamente il DFE è implementato in maniera digitale. Una possibile soluzione, chiamata *unrolled DFE*, consiste nel precalcolare i coefficienti del feedback e poi selezionare quella corretta. In questo modo il contributo di ritardo del sommatore e moltiplicatore nel loop è sostituito dal solo ritardo di selezione del multiplexer, non risultando più un vincolo nell'incremento delle prestazioni. Questa soluzione è possibile grazie alla presenza di solo quattro possibili uscite e alla presenza di un solo TAP, altrimenti precalcolare tutte le altre combinazioni porterebbe ad un impegnativo dispendio di risorse.

Inoltre è possibile notare come il DFE sia quell'elemento nel quale avviene la quantizzazione del segnale. Infatti in ingresso i dati che rappresentano i simboli sono espressi con un numero elevato di bit ( dipende dal numero di bit in dell'adc e del FFE) e sono convertiti nei due bit che rappresenta il simbolo

PAM-4.

### 2.5.6 RX Clock Data Recovery

Una fondamentale parte di una architettura di un ricevitore è quella che si occupa della generazione del clock necessario per campionare i dati. La presenza delle non idealità definite precedentemente rende necessario stabilire con precisione l'istante di tempo in cui ogni simbolo è campionato. Analizzando un classico diagramma ad occhio in ricezione, si nota come anche un minimo disallineamento porta al campionamento dei dati in un punto dove risulta impossibile riuscire a discriminare il valore dei segnali in arrivo. Ancor di più lo è in una modulazione PAM-4 dove la presenza di soglie ravvicinate tra loro causerebbe un drastico aumento del BER. [4] [2].

In un protocollo asincrono come il PCIe, è necessario creare riuscire a generare il clock di campionamento dei dati a partire dai soli segnali in ingresso. Tutto ciò è effettuato dal blocco di Clock Data Recovery (CDR). Esistono differenti architetture, quella presa in considerazione usa un approccio misto tra il digitale e l'analogico, e che sfrutta l'utilizzo di un Phase Interpolator (PI) e ILO.

A differenza di un sistema come un PLL, che riesce a recuperare il clock da un segnale periodico, la sfida di un CDR è quella di utilizzare un segnale con un generale andamento casuale. Per evitare la problematica di operare con dei dati che presentano lunghe sequenze di uni o zeri, e quindi senza transizioni utili per il recupero del clock, nei layer superiori sono implementate particolari codifiche che permettono di ottenere una distribuzione del segnale casuale.

#### Phase detector

Come si evince dall'architettura mostrata in [figura 2.17](#) La prima parte del loop del CDR sfrutta i dati in arrivo dall'ADC, per poi andare in ingresso al phase detector. Esso si occupa di generare una informazione riguardante lo sfasamento tra il clock attuale e i dati in ingresso, fornendo una informazione se il clock è in anticipo o ritardo rispetto al punto ottimale in cui campionare i dati.

Un sistema per ottenere questa informazione potrebbe essere quella di sovraccampionare il dato, e valutando con precisione dove avviene la transizione. In un HS Ser-Des questa opzione non è implementabile a causa delle elevate frequenze di lavoro. Quello che rimane è sfruttare per queste applicazioni è un *Boude Rate Phase Detector*, che permettono di recuperare l'informazione di fase usando come riferimento un solo campione per ogni simbolo, uno tra questi è il Mueller Muller Phase Detector (MM-PD).

Esso sfrutta le misure di ampiezza dei campioni in arrivo, per cercare di determinare se il simbolo è stato campionato nel suo punto di massimo. Quello che si immagina infatti è che avere dei simboli che presentano un contributo di

interferenza intersimbolica, abbiano un valore di ampiezza non costante, quindi campionando il segnale in un punto differente a quello ideale la sua ampiezza diminuisce.

Come possibile immaginare un sistema di questo tipo non è in grado di funzionare nel caso un cui il segnale di ingresso abbia un comportamento simile a uno ideale, infatti basta pensare che se il simbolo ha un inviluppo quasi costante non è se campionato con un differente sfasamento, il risultato non produce rilevanti differenze e non è possibile capire se anticipare o ridurre lo sfasamento.

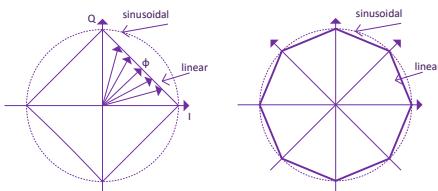

### Phase Interpolator

Il Phase Interpolator (PI) è il blocco usato per effettuare la correzione di fase. Agisce utilizzando diverse fasi in ingresso sfasate tra di loro e genera un clock in uscita come somma pesata delle varie fasi in ingresso. I pesi di queste fasi sono quelli che permettono di ottenere uno sfasamento del segnale in uscita e possono essere controllati tramite un codice digitale.

Un classico esempio è basato su due fasi di ingresso (componenti I/Q) le quali sono utilizzate per la generazione di una uscita con fase arbitraria  $\phi$  ([equazione \(2.2\)](#)).

$$\begin{aligned} y(t) &= \sin(2\pi f_o t + \varphi) = \\ &= \sin(2\pi f_o t) \cos(\phi) + \cos(2\pi f_o t) \sin(\phi) \end{aligned} \quad (2.2)$$

Come si nota, le ampiezze delle componenti in fase e in quadratura non possono essere decise arbitrariamente. Immaginando di codificare ad esempio  $\phi$  in un codice digitale di controllo, sfruttando la funzione sin e cos si ha la possibilità di ottenere le corrette ampiezze delle due componenti che portano ad una relazione lineare tra il codice e lo sfasamento ottenuto in uscita.

Una ulteriore possibile funzione di mappatura tra sfasamento desiderato e ampiezze delle fasi è quella che sfrutta una approssimazione lineare ([figura 2.21](#)) e permette di ridurre la complessità dell'implementazione, ma al costo di ottenere un andamento non lineare tra il codice applicato e lo sfasamento ottenuto.

Figura 2.21: Linear interpolator code mapping

In una implementazione reale è utilizzato un numero superiore di fasi, incrementando la complessità ma ottenendo un minor errore utilizzando una valutazione lineare dei pesi.

$$y(t) = \sum_{i=0}^{N-1} A_i \cos(\omega t + \frac{2\pi}{N}) \quad (2.3)$$

## ILO

Come detto, per poter sfruttare il PI è necessario ottenere un numero elevato di fasi equispaziate. Queste fasi sono generate localmente tramite un particolare tipo di oscillatore chiamato, l'Injection Locking Oscillator (ILO).

Un elemento di questo tipo è composto da un oscillatore di riferimento che genera un certo numero di fasi e con una determinata frequenza detta free running frequency (f.r.f.), questo oscillatore può essere un Voltage Controlled Oscillator (VCO), la cui frequenza di lavoro è definita tramite un codice digitale. Al suo ingresso è presente un clock di riferimento, come quello di un PLL. Se le due frequenze sono simili, i due segnali tenderanno a oscillare alla stessa frequenza, attraverso il fenomeno dell'*Injection Locking*.

Questo fenomeno si ritrova non solo in fenomeni elettrici ma anche meccanici. Un esempio è quello di utilizzare prendere 2 pendoli a frequenze leggermente diverse e sfasamenti diversi. Se posti a distanza ravvicinata, a causa di vibrazioni e fenomeni di accoppiamento, tenderanno a convergere alla stessa frequenza di oscillazione e senza alcuno sfasamento. La presenza di questa injection permette di ottenere una sincronizzazione tra due oscillatori.

I vantaggi di una configurazione di questo tipo è rendono più efficace e rapido le fasi di recupero del clock.

L'accoppiamento tra le due frequenze risulta possibile solo nel caso in cui le due frequenze di oscillazione sono ravvicinate. Da questo nasce l'esigenza di effettuare delle calibrazioni che siano in grado di misurare la differenza tra le due frequenze e minimizzarla. Un ulteriore fenomeno si manifesta durante la fase di injection: si genera un errore di sfasamento tra le varie fasi prodotte proporzionale alla differenza tra l'injection frequency e la free running frequency. Si deduce quindi anche la presenza di meccanismi per la correzione dello skew.

# Capitolo 3

## GTECH Speed-up

Lo scopo di questo capitolo dell’elaborato è quella di chiarire e descrivere le semplificazioni effettuate nella hard macro digitale del PHY, descritta in [sezione 2.4](#) e [sezione 2.5](#), partendo da una introduzione sulla libreria GTECH, sulle metriche utilizzate, come sono state implementate le semplificazioni e i risultati ottenuti.

### 3.1 Introduzione alla libreria GTECH

La Generic Technology (GTECH) è una libreria di porte logiche generiche, utilizzata per effettuare la sintesi dell’RTL e generare una netlist. Un possibile esempio della descrizione di queste celle in *Verilog* è mostrato in [listato 3.1](#). Queste celle sono tutte definite a livello comportamentale, risultando completamente prive di informazioni come *strength*, capacità, tempi di propagazione... tipici di una libreria classica standard-cell per la sintesi logica. L’assenza di ritardi di propagazione impedisce l’analisi e l’ottimizzazione del *timing* basata su dati reali da parte del sintetizzatore. In alcuni casi, è possibile modellarle con ritardi unitari, uguali per tutte le celle. Ne consegue che, a differenza di una sintesi basata su una libreria logica standard, non sono presenti file Standard Delay Format (SDF) o Standard Delay Constraint (SDC), contenenti le annotazioni dei vincoli e dei ritardi necessari per la simulazione della netlist.

```

1 module MUX2 ( A, B, S, Z );

2   input A;

3   input B;

4   input S;

5   output Z;

6

7   assign Z = (S) ? B : A;

8 endmodule

9

10 module NAND2 ( A, B, Z );

11   input A;

12   input B;

```

```

13     output Z;

14

15     assign Z = ~(A & B);

16 endmodule

17

18 module FD2 ( D, CP, CD, Q, QN );

19     input D;

20     input CP;

21     input CD;

22     output Q;

23     output QN;

24

25     wire Q;

26     wire QN;

27     wire s_CP;

28     wire s_D;

29     reg s_Q;

30

31     assign s_CP = CP;

32     assign #(‘Thld) s_D = D;

33

34     always @ (posedge s_CP or negedge CD) begin

35         if (!CD)

36             s_Q <= #(‘Tco) 1'b0;

37         else

38             s_Q <= #(‘Tco) s_D;

39     end

40

41     assign Q = s_Q;

42     assign QN = ~s_Q;

43 endmodule

```

Listing 3.1: Esempio di porte della libreria GTECH

Come già anticipato, esistono molteplici motivazioni che giustificano l'utilizzo di una netlist di questo tipo. La principale è legata alla necessità, da parte del committente dell'IP, di disporre di un modello simulabile, garantendo al contempo a Synopsys la possibilità di offrire questo servizio senza divulgare informazioni o file coperti da proprietà intellettuale, come l'RTL originale.

### 3.2 Giustificazioni per la semplificazione della parte DSP

La libreria GTECH è utilizzata come strumento di supporto fornito al customer per facilitare l'integrazione dell'IP nel SoC, analizzandone il comportamento ad alto livello. In tali condizioni non è necessario effettuare delle simulazioni in maniera fedele di ciò che accade a basso livello, ed è possibile simulare scenari di funzionamento ideali. Principalmente l'utilizzo di un canale di trasmissione ideale, quindi non soggetto alle problematiche descritte precedentemente come l'ISI. In questo contesto le tecniche di DSP implementate nel datapath digitale non forniscono alcun vantaggio, ma al contrario, sono elementi che rendono più complessa la simulazione. Un canale ideale infatti implica che i valori dei

coefficienti dei vari filtri siano valutati in maniera tale da rendere trascurabile il loro effetto.

Quanto descritto fin ora è da vedere come l'opportunità che permette la semplificazione della parte DSP dell'architettura durante la sintesi della netlist.

### 3.3 Metodo di analisi delle performance

Per avere una idea di quali siano le istanze che portano ad un maggiore dispendio di tempo di simulazione e capire su quali elementi è necessario agire, esiste la necessità di effettuare una serie di simulazioni al fine di analizzarne come il tempo di simulazione è suddiviso tra le varie istanze. L'utilizzo di uno strumento come un *Simulation Profiler* diventa indispensabile.

Questo strumento fa parte dell'ambiente utilizzato per effettuare le simulazioni, basato sui seguenti tool di Synopsys:

- **Synopsys VCS:** esso si occupa di compilare i file necessari per la simulazione, l'RTL o la netlist, ed effettua la simulazione producendo il file Fast Signal Database (FSDB) che contiene le informazioni delle forme d'onda ottenute.

- **Synopsys Verdi:** un tool utilizzato per visualizzare o i risultati ottenuti da VCS.

#### 3.3.1 Simulation Profiler

Il *Simulation Profiler* è uno strumento integrato in *Synopsys VCS* utilizzato per l'analisi delle performance di una simulazione logica, sia di RTL che gate-level, al fine di analizzare come il tempo di simulazione è distribuito nelle varie parti.

Durante una simulazione vengono raccolte informazioni sul quanto ogni blocco è utilizzato durante la simulazione, che siano essi `assign`, `always`, `forever`, ...

E' possibile abilitare il *Simulation Profiler* agendo sul comando di *VCS* , come mostrato in [listato 3.2](#).

```

1 vcs -kdb -simprofile ...

```

Listing 3.2: Comando per avilitare il simulation profiler

Al termine della simulazione è poi disponibile un report che presenta tutte le informazioni necessarie al fine di valutare il tempo di simulazione. È possibile visualizzarlo tramite un apposito comando di *Verdi* che permette di avere una visualizzazione più dettagliata ([listato 3.3](#)).

```

1 verdi -profilePath [simprofile dir] -ssf [fsdb dir]

```

Listing 3.3: Comando per visualizzare i risultati del simulation profiler

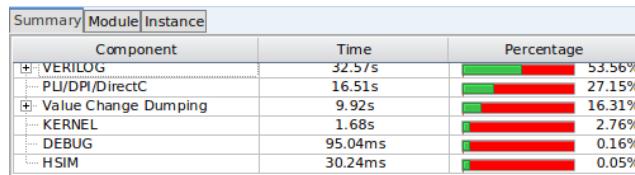

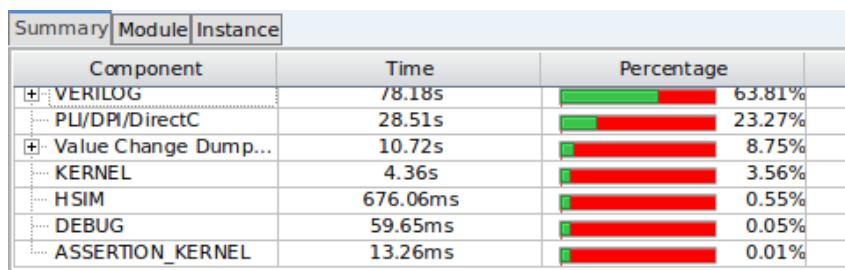

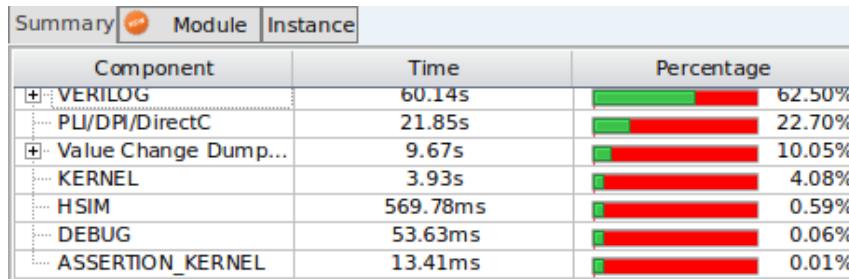

Ogni report da analizzare è composto da un sommario, che riporta come il tempo totale è suddiviso tra le varie componenti della simulazione, ovvero la simulazione del verilog, le chiamate a funzioni esterne, la generazione dei file di output, il tempo necessario per lo scheduling, elaborazione dei segnali, l'overhead introdotto dal profiler (figura 3.1)...

Questo implica il fatto che se si effettuano delle migliorie per un determinato blocco è presente anche un ulteriore miglioramento dovuto alle altre parti della simulazione, per fare un esempio se alcuni elementi vengono rimossi diminuisce anche il tempo necessario per effettuare il dump delle waveform di uscita.

Figura 3.1: Esempio di sommario del Simulation Profiler

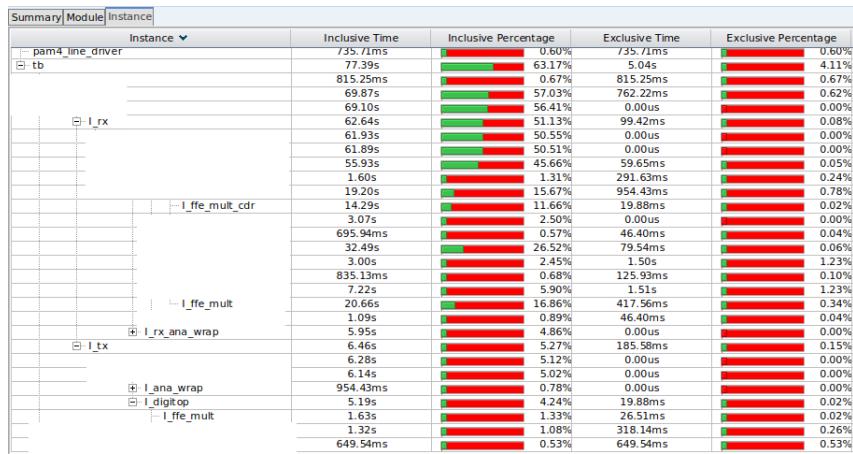

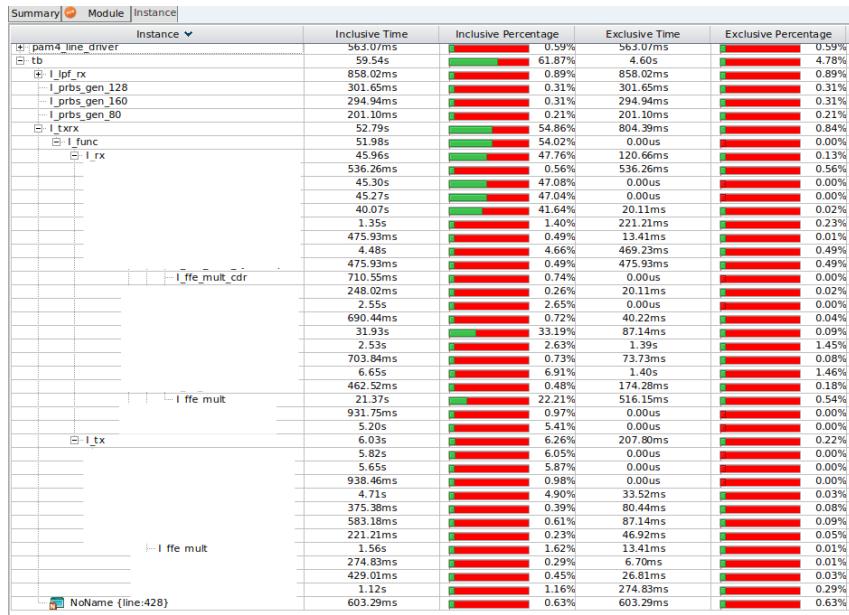

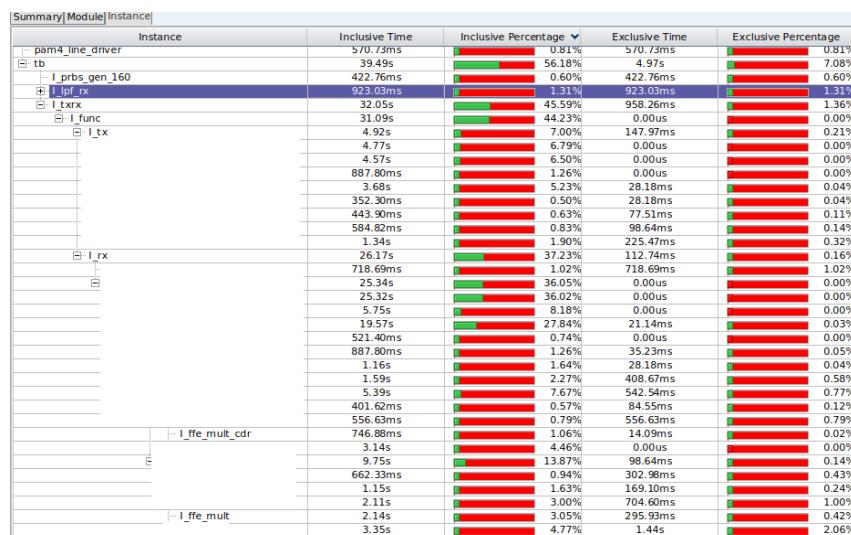

La seconda schermata, figura 3.2, riporta come il tempo di simulazione è impiegato all'interno dei vari moduli istanziati nella gerarchia. Una precisazione da fare riguarda il fatto che i tempi indicati riguardano il solo tempo necessario per la simulazione del Verilog. Nel report sono presenti 4 colonne:

- Inclusive Time/Percentage: indica il tempo in valore assoluto/percentuale per simulare in maniera complessiva quell'istanza e anche tutti i moduli istanziati al suo interno;

- Exclusive Time/Percentage: Indica il tempo necessario per simulare solo il modulo in questione, escludendo tutti i moduli che sono istanziati al suo interno. Utile se è necessario analizzare solamente i processi/-segnali (always, assign) che sono definiti all'interno del modulo stesso, trascurando i moduli istanziati al suo interno.

Nel caso in questione verranno presi come riferimento gli Inclusive Time/-Percentage, dato che la GTECH essendo una netlist, presenta all'interno di ogni modulo delle istanze di altre celle, il che renderebbe non apprezzabile il tempo di simulazione esclusivo di gerarchia superiore.

### 3.3.2 Testbench utilizzato

Come è possibile intuire, il tempo necessario per completare una simulazione può essere influenzato in modo significativo dal modo in cui il testbench stimola

| Inclusive Time | Inclusive Percentage | Exclusive Time | Exclusive Percentage |

|----------------|----------------------|----------------|----------------------|

| 574.59ms       | 0.95%                | 574.59ms       | 0.95%                |

| 31.98s         | 52.60%               | 1.76s          | 2.90%                |

| 220.33ms       | 0.36%                | 220.33ms       | 0.36%                |

| 233.29ms       | 0.38%                | 233.29ms       | 0.38%                |

| 354.26ms       | 0.58%                | 354.26ms       | 0.58%                |

| 444.98ms       | 0.73%                | 444.98ms       | 0.73%                |

| 462.26ms       | 0.76%                | 462.26ms       | 0.76%                |

| 1.02s          | 1.68%                | 1.02s          | 1.68%                |

| 27.62s         | 45.43%               | 25.92ms        | 0.04%                |

| 27.59s         | 45.38%               | 0.00us         | 0.00%                |

| 1.89s          | 3.11%                | 0.00us         | 0.00%                |

Figura 3.2: Esempio della vista Instance del Simulation Profiler

i segnali del design da simulare. Esistono due aspetti da considerare: il primo riguarda quali segnali vengono effettivamente attivati all'interno del testbench durante la simulazione e quindi quali parti del design vengono stimolate di conseguenza. Il secondo riguarda il *tempo simulato*, ovvero la durata virtuale della simulazione.

Entrambi i due aspetti possono portare infatti ad avere risultati differenti in termini di *tempo di esecuzione* della simulazione (il tempo necessario per elaborare la simulazione), visto che non chiariscono univocamente il carico effettivo per il simulatore.

Ad esempio, un testbench può simulare un intervallo di tempo molto lungo, ma se non genera transizioni sui segnali o non attiva blocchi significativi del design, il carico computazionale sarà ridotto, e quindi anche la durata reale della simulazione sarà breve. Al contrario, in altri casi, una simulazione con un tempo interno breve può richiedere molto tempo per essere completata, a causa dell'elevato numero di segnali coinvolti e delle numerose valutazioni richieste.

Questo comportamento è strettamente legato al funzionamento del simulatore stesso. I simulatori utilizzati per la verifica RTL o netlist sono infatti *event-driven*, e non *time-driven*. Ciò significa che l'elaborazione avviene solo quando si verificano eventi, come un cambiamento di valore su un segnale, piuttosto che scorrere ciclicamente tutti i segnali a ogni passo temporale. Di conseguenza, la complessità della simulazione dipende in larga parte dal numero e dalla frequenza degli eventi generati, e non semplicemente dalla durata del tempo simulato.

Per questo motivo, tutte le simulazioni verranno condotte facendo riferimento a un tempo di simulazione nominale comune, cercando di lavorare in delle condizioni reali, in cui tutti i blocchi fondamentali devono essere attivi che consentano di ottenere dei risultati simili a quelle delle applicazioni.

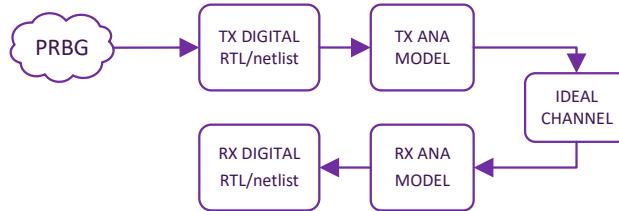

Il testbench utilizzato è strutturato in questo modo: una parte preliminare del è esegue la gestione delle procedure di startup, in cui è emulato uno stato di inizializzazione, considerando l'attivazione di tutti i blocchi principali, una seconda parte dove avviene la comunicazione dei dati vera e propria, e infine uno stato di power-off.

Bisogna anche chiarire quali sono i blocchi istanziati all'interno del testbench: oltre ai blocchi principali digitali del trasmettitore e del ricevitore sono

presenti dei modelli analogici, sia del trasmettitore che del ricevitore, come mostrato in [figura 3.3](#).

Figura 3.3: Struttura base del testbench

Questo implica che il contributo del tempo di simulazione non sarà da attribuire del tutto alla netlist sintetizzata con la libreria GTECH, ma anche alla presenza di questi modelli analogici.

Tutto questo per ottenere delle informazioni del profiler che siano il più verosimili possibili e che permettano una corretta individuazione dei blocchi responsabili di rallentamenti sul tempo di esecuzione della simulazione. Una precisazione da fare riguarda quindi la durata complessiva della simulazione.

### 3.3.3 Simulazione di riferimento

Come già detto, prima di procedere con le ottimizzazioni è necessario stabilire una condizione di partenza e ottenere dei risultati del profiler al fine di individuare i blocchi con una maggiore influenza il tempo di esecuzione. I risultati ottenuti sono visibili in [figura 3.4](#) e [figura 3.5](#).

Figura 3.4: Sommario sul tempo di simulazione iniziale della netlist GTECH

Dalla [figura 3.4](#) è possibile ottenere il tempo complessivo di simulazione:

$$T_{ref,tot} = 122.52 \text{ s} \quad (3.1)$$

Questo tempo di simulazione potrebbe sembrare non eccessivo, e si potrebbe pensare che non sia necessario apportare miglioramenti. Tuttavia, si tratta

Figura 3.5: Report dettagliato tempi di simulazione GTECH iniziale

solo di una soluzione di riferimento. Nella realtà, infatti, gli algoritmi da testare in queste simulazioni possono avere una durata molto maggiore, anche di diverse ore. Per questo motivo, ottenere dei risultati più rapidamente potrebbe essere particolarmente vantaggioso.

Dalla [figura 3.5](#) si nota come l'elemento critico sia il ricevitore, gli elementi che spiccano sono i due filtri FFE, uno quello utilizzato dal datapath e l'altro quello utilizzato dal sistema di CDR. Entrambi i blocchi sono semplificabili visto che sono legati all'equalizzazione del canale di trasmissione.

Anche se il trasmettitore non è fondamentale per la diminuzione del tempo di simulazione può anch'esso essere semplificato, sempre per quanto riguarda il modulo *tx\_ffe*.

In queste analisi si è preferito tenere in considerazione dei valori assoluti dato che, dal momento che una volta che si iniziano ad introdurre dei diverse modifiche può capitare che i valori percentuali possano essere falsati dal fatto che introducendo una modifica e ad esempio riducendo il tempo di simulazione di un blocco, un altro blocco che fino a prima aveva un tempo di simulazione trascurabile poi diventa dominante anche se rispetto alla condizione iniziale non porta alcun miglioramento.

In [tabella 3.1](#) sono riportate le principali instanze semplificabili:

| modulo            | $T_{ref}$ [s] | $\frac{T_{ref}}{T_{ref,tot}}$ [%] |

|-------------------|---------------|-----------------------------------|

| <i>rx_ffe</i>     | 20.66         | 16.86                             |

| <i>rx_ffe_cdr</i> | 14.29         | 11.66                             |

| <i>tx_ffe</i>     | 1.63          | 1.33                              |

Tabella 3.1: Tempo iniziale dei blocchi che influenzano la simulazione

### 3.4 Implementazione delle semplificazioni

A livello di datapath è possibile rappresentare in generale le operazioni svolte, utilizzando come esempio un filtro FIR, il quale ha il funzionamento simile a quello dell'FFE. anche se le istanze su cui si è sviluppata l'ottimizzazione presentano delle implementazioni differenti che rendono molto vantaggioso e andare a rimuover quanto visto.

Figura 3.6: Esempio di semplificazione applicata ad un filtro FIR

In figura 3.6 è possibile identificare con linea tratteggiata gli elementi non necessari per la valutazione dell'output del filtro.

Queste modifiche devono essere fatte in modo tale da non influenzare il comportamento del timing e funzionamento del blocco, ma principalmente agendo sulla logica combinatoria e inoltre devono essere inserite in modo tale che non si vada ad intaccare l'RTL sintetizzabile. Per rispettare questi requisiti è stato deciso di inserire una macro che, nel caso in cui venga definita permette, di selezionare il modulo semplificato per la sintesi con la GTECH.

```

1 '#ifndef GTECH_OPTIMIZE

2

3 // modulo per la sintesi con GTECH

4 module rx_...

5   input wire in1,

6   ...

7 );

8   ...

9   //descrizione modulo originale

10 endmodule

11

12 '#else

13

14 // modulo per la sintesi con GTECH

15 module rx_...

```

```

16      input wire in1,

17      ...

18  );

19  ...

20  // modulo semplificato

21 endmodule

22

23 'endif

```

Listing 3.4: Esempio di come sono istanziate le modifiche

### 3.4.1 RX FFE

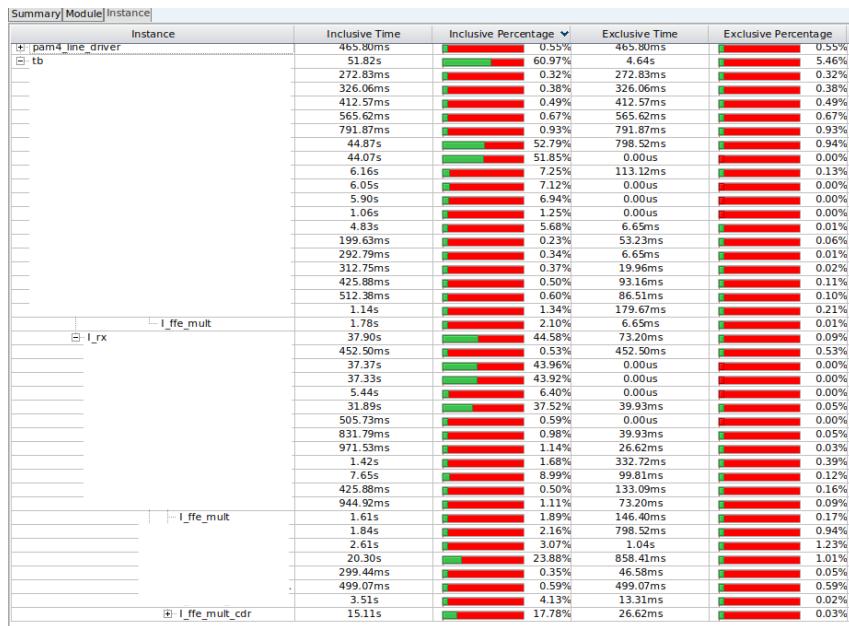

Una volta effettuate le semplificazioni ed effettuato una nuova sintesi con la libreria GTECH il report del profiler è mostrato in [figura 3.7](#) e [figura 3.8](#).

E' possibile estrarre l'informazione sul tempo complessivo di simulazione

$$T_{new,tot} = \frac{52.34}{0.6157} = 85.00 \text{ s}$$

con un guadagno in percentuale di

$$= \frac{85.0 \text{ s} - 122.52 \text{ s}}{122.52 \text{ s}} = -30.62\%$$

per quanto riguarda la componente Verilog, il guadagno ottenuto è il seguente:

$$T_{ref} = 20.66 \text{ s}$$

$$T_{new} = 1.61 \text{ s}$$

che si traduce in un guadagno in termini percentuale di:

$$= \frac{1.61 \text{ s} - 20.66 \text{ s}}{122.52 \text{ s}} = -15.54\%$$

Si nota in maniera evidente come in questo caso, una parte considerevole di vantaggio si ottiene anche da tutte le altre componenti di simulazione.

| Component            | Time     | Percentage |

|----------------------|----------|------------|

| VERILOG              | 52.34s   | 61.57%     |

| PLI/DPI/DirectC      | 20.76s   | 24.42%     |

| Value Change Dump... | 8.58s    | 10.10%     |

| KERNEL               | 2.77s    | 3.26%      |

| HSIM                 | 499.07ms | 0.59%      |

| DEBUG                | 39.93ms  | 0.05%      |

| ASSERTION_KERNEL     | 6.65ms   | 0.01%      |

Figura 3.7: Report del tempo di simulazione per *RX\_FFE*

Figura 3.8: Report del tempo di simulazione per *RX\_FFE*

### 3.4.2 RX CDR FFE

Uno dei possibili blocchi in cui è possibile effettuare un miglioramento è una seconda versione del filtro FIR del ricevitore inserito all'interno del blocco di CDR.

Il filtro in questione possiede un numero elevato di elementi combinatori che possono essere esclusi. Purtroppo non è possibile mostrare nel dettaglio quale sia il datapath e come si è andato ad agire, ma dopo aver sintetizzato nuovamente la netlist con libreria GTECH e lanciato la simulazione con lo stesso testbench fatto in precedenza il report ottenuto è mostrato in [figura 3.9](#) e [figura 3.10](#).

Figura 3.9: Report del tempo di simulazione per *RX\_FFE\_CDR*

Il tempo complessivo di simulazione risulta:

$$T_{new,tot} = \frac{60.14}{0.6250} = 96.22 \text{ s}$$

Figura 3.10: Report del tempo di simulazione per *RX\_FFE\_CDR*

con un guadagno in percentuale di:

$$= \frac{96.22\text{ s} - 122.5\text{ s}}{122.5\text{ s}} = -21.47\%$$

Per quanto riguarda la componente Verilog, il guadagno ottenuto è il seguente:

$$T_{ref} = 14.29\text{ s}$$

$$T_{new} = 0.71\text{ s}$$

che in percentuale è espresso come: