# Politecnico di Torino

ELECTRONIC ENGINEERING

A.a. 2024/2025

Sessione di laurea Dicembre 2025

## An exploration on connectivity and efficiency in Coarse-Grain Reconfigurable Architectures

Relatori

Prof Maurizio Martina

Dott Luigi Giuffrida

Candidato

Mattia Cozzolino

# Indice

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| <b>Elenco delle figure</b>                                              | VI |

| <b>1 Introduction and Context</b>                                       | 1  |

| 1.1 Motivations and Objectives . . . . .                                | 2  |

| 1.2 Technological Context . . . . .                                     | 3  |

| 1.3 Design Approach . . . . .                                           | 3  |

| 1.4 Results . . . . .                                                   | 5  |

| <b>2 Background and State of the Art</b>                                | 6  |

| 2.1 Introduction to CGRA Architectures . . . . .                        | 6  |

| 2.2 Computation Models and CGRA Classification . . . . .                | 7  |

| 2.3 Modern Microarchitectures and Processing Element Features . . . . . | 8  |

| 2.4 Generation Frameworks and Compiler Toolchains . . . . .             | 9  |

| 2.5 Memory Systems, Data Movement, and DMA in Modern CGRAs .            | 11 |

| <b>3 Architecture of the Proposed CGRA</b>                              | 12 |

| 3.1 General Overview . . . . .                                          | 12 |

| 3.1.1 Design Objectives . . . . .                                       | 15 |

| 3.1.2 Hierarchical Structure of the Architecture . . . . .              | 16 |

| 3.1.3 Data Flow and Synchronization . . . . .                           | 16 |

| 3.2 DMA AXI-Stream . . . . .                                            | 18 |

| 3.2.1 Internal Architecture and State Machine . . . . .                 | 19 |

| 3.2.2 AXI-Stream Protocol Handling . . . . .                            | 20 |

| 3.2.3 Internal Memory . . . . .                                         | 21 |

| 3.2.4 Robustness . . . . .                                              | 21 |

| 3.2.5 Conclusion and Considerations . . . . .                           | 21 |

| 3.3 Frame Loader . . . . .                                              | 22 |

| 3.3.1 Ping-pong Buffer . . . . .                                        | 24 |

| 3.3.2 Internal Structure . . . . .                                      | 25 |

| 3.3.3 State Machine and State Management . . . . .                      | 26 |

| 3.3.4 Swap Handling and Stability of the ACTIVE Planes . . . . .        | 28 |

|       |                                                                                          |    |

|-------|------------------------------------------------------------------------------------------|----|

| 3.3.5 | Robustness, Error Handling and Prevention of Anomalous Conditions . . . . .              | 29 |

| 3.3.6 | Integration with the Top-Level and with the PE Matrix . . . . .                          | 30 |

| 3.3.7 | Timing, Performance Aspects and Relation to Global Throughput . . . . .                  | 31 |

| 3.3.8 | Scalability and Adaptation to Different Matrix Sizes . . . . .                           | 31 |

| 3.3.9 | Final Design Considerations . . . . .                                                    | 32 |

| 3.4   | Processing Element . . . . .                                                             | 32 |

| 3.4.1 | Structure of the PE Module . . . . .                                                     | 33 |

| 3.4.2 | Internal ALU . . . . .                                                                   | 35 |

| 3.4.3 | Validation and Output Signals . . . . .                                                  | 36 |

| 3.4.4 | Interaction with the Matrix Topology . . . . .                                           | 36 |

| 3.4.5 | Robustness of Synchronization and Prevention of Critical Conditions . . . . .            | 37 |

| 3.4.6 | Final Considerations on the Processing Element Design . . . . .                          | 38 |

| 3.5   | Parametric $N \times N$ Matrix: Structure, Scalability and Topology Management . . . . . | 39 |

| 3.5.1 | Introduction and Role of the Matrix in the CGRA . . . . .                                | 39 |

| 3.5.2 | General Structure of the Module and Parametricity Criteria . . . . .                     | 39 |

| 3.5.3 | Integration Between Selectors, Topology and PE Behavior . . . . .                        | 41 |

| 3.5.4 | Data Synchronization and Propagation of Validity Signals . . . . .                       | 42 |

| 3.5.5 | Architectural Scalability and Implementation Implications . . . . .                      | 43 |

| 3.5.6 | Final Considerations . . . . .                                                           | 43 |

| 3.6   | Implemented Topologies in the Matrix . . . . .                                           | 44 |

| 3.6.1 | FULL Topology . . . . .                                                                  | 44 |

| 3.6.2 | MESH4 Topology . . . . .                                                                 | 45 |

| 3.6.3 | D-MESH Topology . . . . .                                                                | 47 |

| 3.6.4 | D-TORUS Topology . . . . .                                                               | 48 |

| 3.7   | Scalability of the Matrix and Architectural Implications . . . . .                       | 49 |

| 3.7.1 | Functional Complexity of the Matrix as $N$ Grows . . . . .                               | 50 |

| 3.7.2 | Effects of the Topology on Internal Latency . . . . .                                    | 50 |

| 3.7.3 | Interaction Between Selectors, Validity, and Synchronization . . . . .                   | 51 |

| 3.8   | Implementation Considerations: Regularity, Area, and Timing . . . . .                    | 51 |

| 3.8.1 | 3.8.1 Combinational Logic and Critical Depth . . . . .                                   | 52 |

| 3.8.2 | Real-Time Behaviour and the “Border Effect” . . . . .                                    | 52 |

| 3.8.3 | Practical Implications for Matrix Usage . . . . .                                        | 53 |

| 3.9   | Chapter Conclusions . . . . .                                                            | 53 |

| 4     | <b>Functional verification and testing methodology</b>                                   | 55 |

| 4.1   | Functional Verification and Testing Methodology . . . . .                                | 55 |

| 4.1.1 | Verification Goals . . . . .                                                             | 55 |

|                     |                                                             |           |

|---------------------|-------------------------------------------------------------|-----------|

| 4.1.2               | Simulation Environment . . . . .                            | 56        |

| 4.1.3               | Input Pattern Generation . . . . .                          | 59        |

| 4.1.4               | Logging and Data Tracing . . . . .                          | 61        |

| 4.1.5               | Verification Scripts and External Tools . . . . .           | 61        |

| 4.1.6               | Functional Verification Results . . . . .                   | 62        |

| 4.1.7               | Final Considerations on Verification . . . . .              | 63        |

| <b>5</b>            |                                                             | <b>64</b> |

| 5.1                 | Synthesis Flow and Implementation Considerations . . . . .  | 64        |

| 5.1.1               | Synthesis Goals . . . . .                                   | 64        |

| 5.1.2               | Synthesis Environment . . . . .                             | 65        |

| 5.1.3               | Impact of Topologies on Synthesis . . . . .                 | 66        |

| 5.1.4               | Analysis of Synthesis Results . . . . .                     | 67        |

| 5.1.5               | Scalability and Implications for a Real ASIC Implementation | 70        |

| <b>6</b>            |                                                             | <b>72</b> |

| 6.1                 | Experimental Results and Critical Discussion . . . . .      | 72        |

| 6.1.1               | Objectives of the Experimental Analysis . . . . .           | 72        |

| 6.1.2               | Comparison Between Topologies . . . . .                     | 73        |

| 6.1.3               | Scalability with Increasing $N$ . . . . .                   | 74        |

| 6.1.4               | Discussion of Design Limitations . . . . .                  | 75        |

| 6.1.5               | Possible Future Extensions . . . . .                        | 76        |

| 6.1.6               | Conclusions on the Experimental Results . . . . .           | 76        |

| <b>Bibliografia</b> |                                                             | <b>78</b> |

# Elenco delle figure

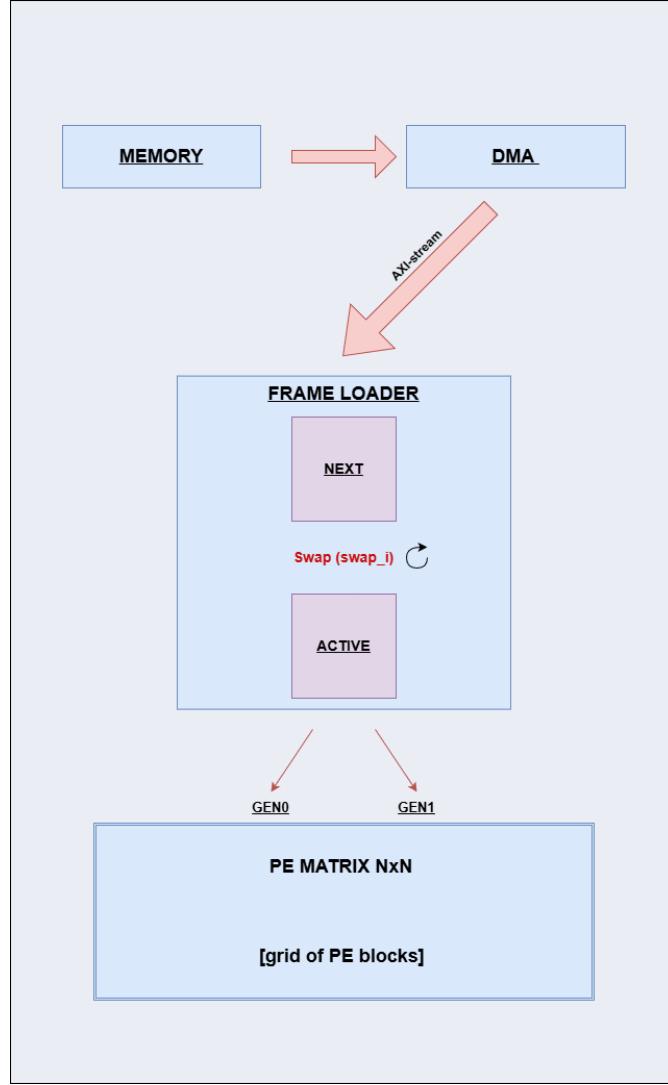

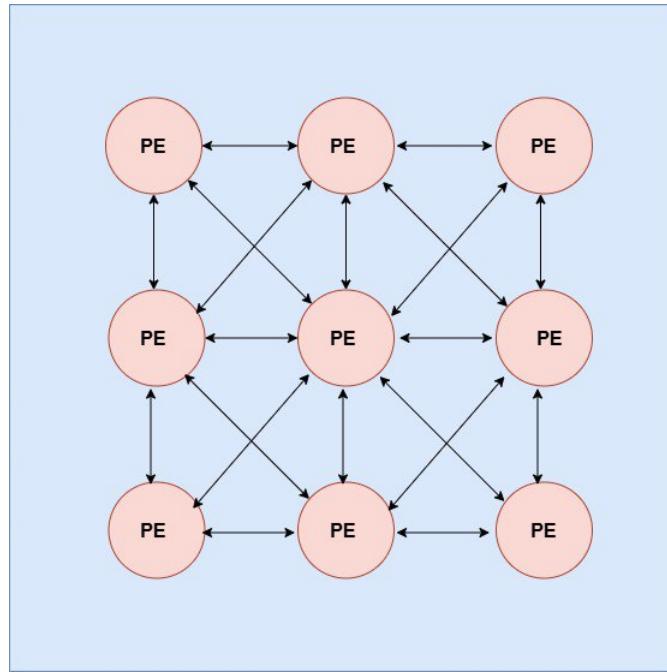

- 3.1 Three main components of the processing pipeline are shown in this figure. The AXI-Stream DMA, the Frame Loader and the parametric matrix of Processing Elements - PEs. These modules cooperate in receiving the input planes and reconstructing them inside the ping-pong buffers. and process them in parallel within the CGRA. . . . . 13

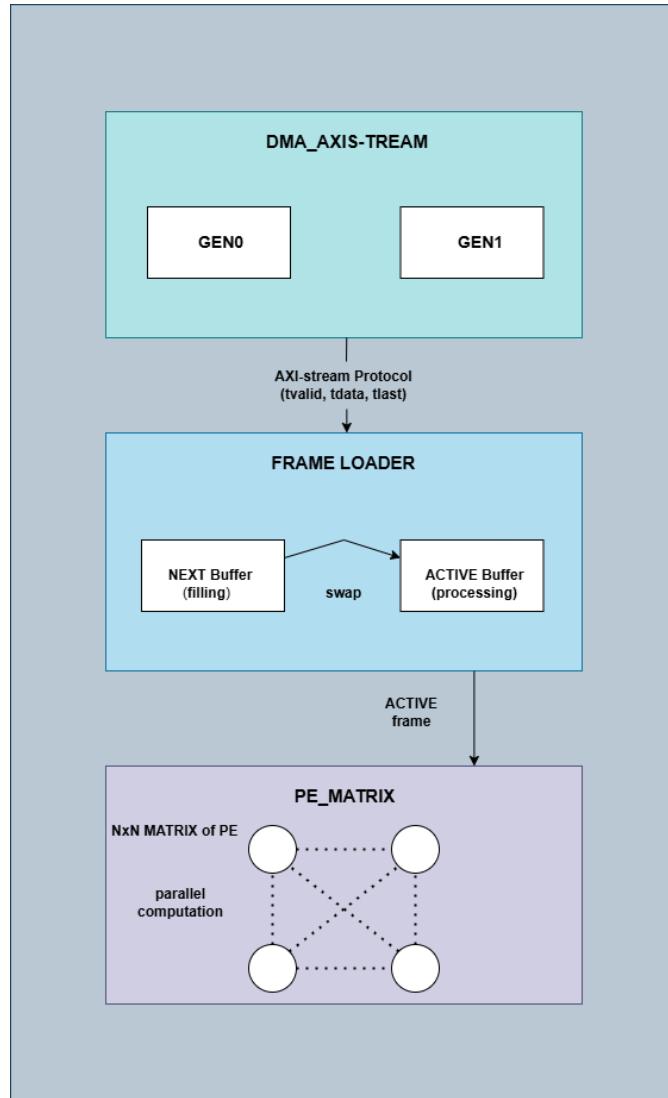

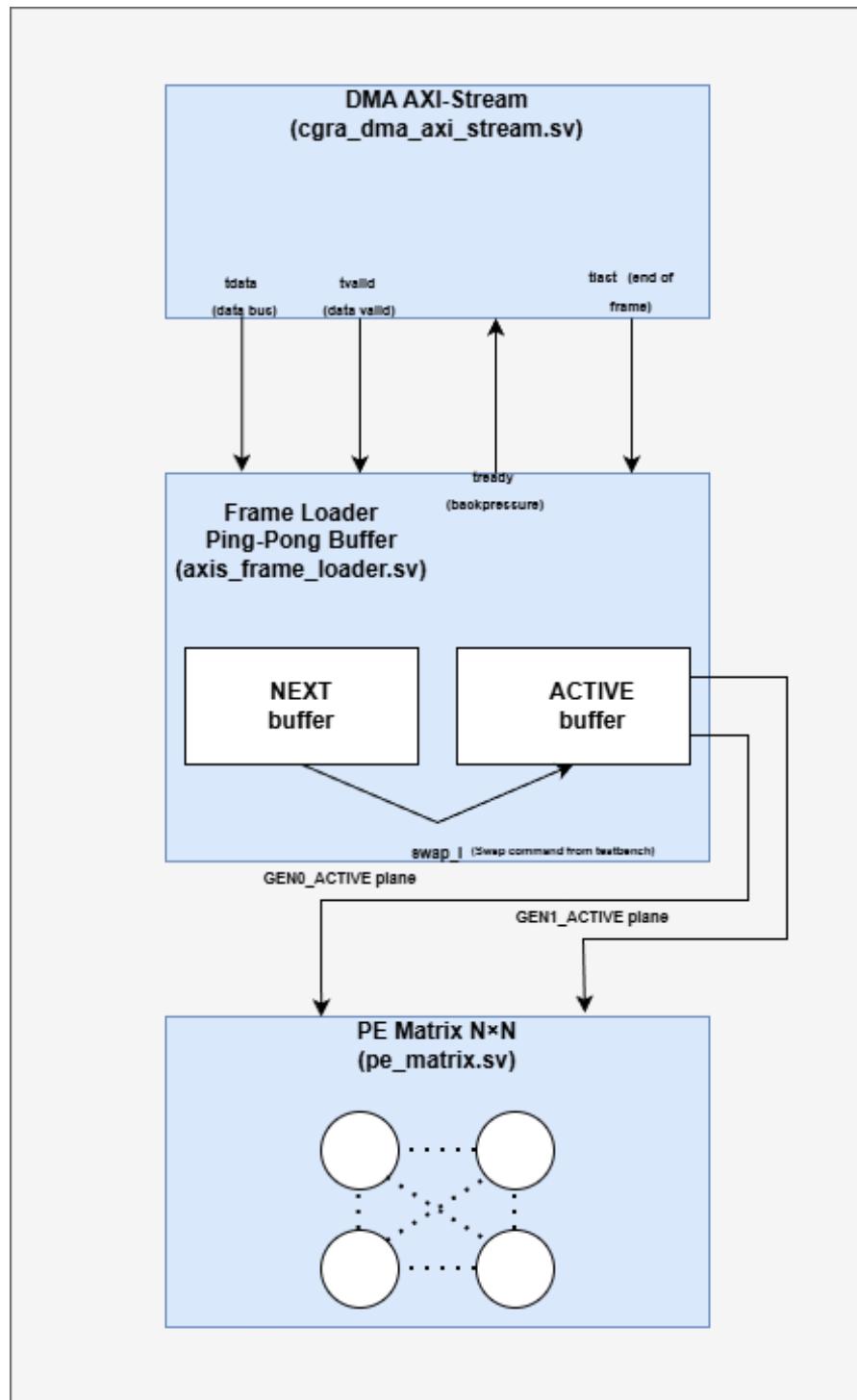

- 3.2 The DMA transfers the two input planes, GEN0 and GEN1, through AXI-Stream. The Frame Loader reconstructs the frame inside the NEXT buffer, while the PE Matrix processes the ACTIVE buffer. When NEXT is fully loaded and the matrix finishes the current frame, the swap signal synchronizes the ping-pong mechanism so that loading and computation keep executing continuously in parallel. 17

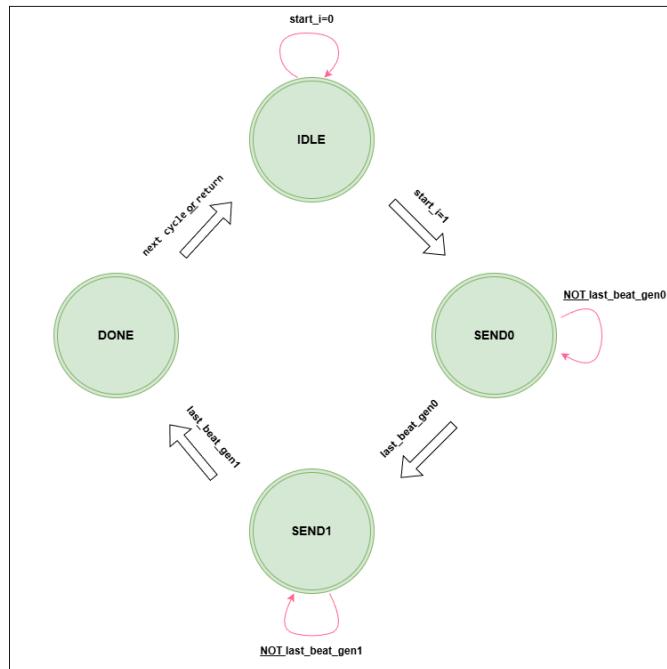

- 3.3 The DMA sequences the transmission of GEN0 and GEN1 over AXI-Stream through the IDLE, SEND0, SEND1, and DONE states.. 19

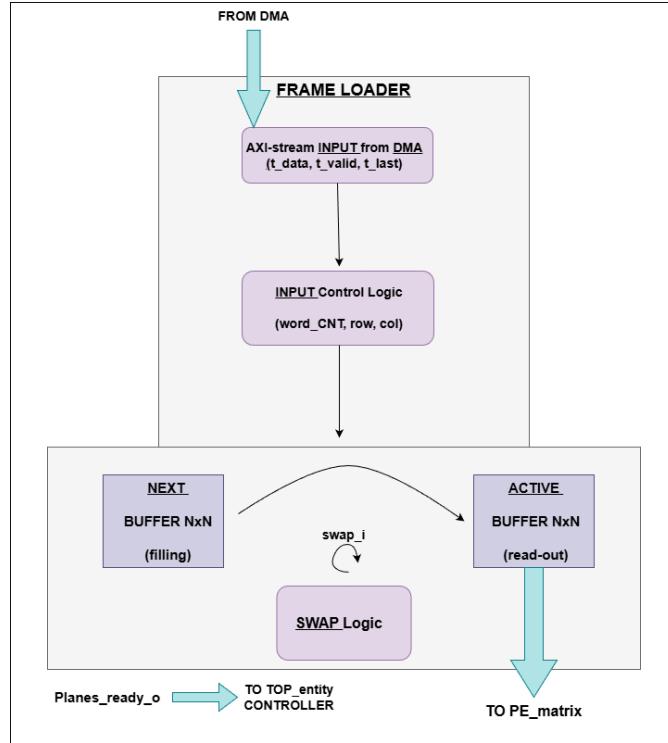

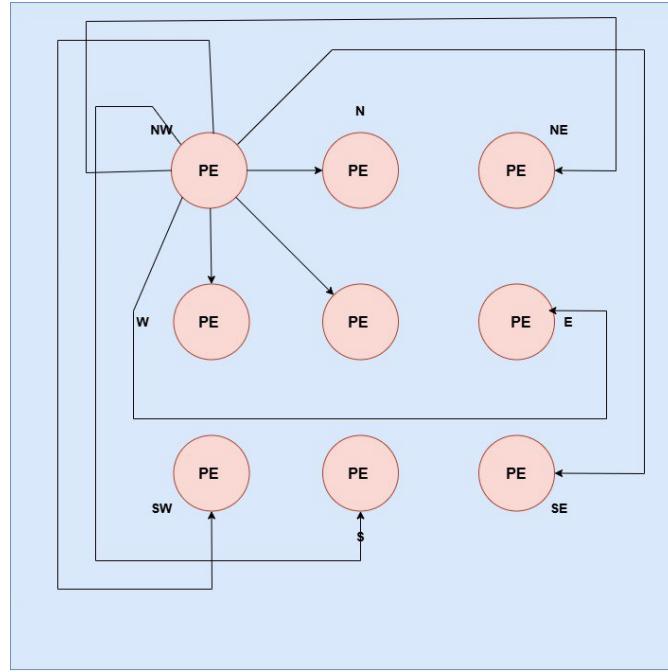

- 3.4 The module receives the AXI-Stream data from the DMA, reconstructs the incoming planes inside the NEXT buffer through the input control logic (row/col indexing), and exposes the ACTIVE buffer to the PE Matrix. Swap logic toggles the roles of NEXT and ACTIVE upon swap\_i, implementing the ping-pong mechanism used for continuous frame processing. . . . . 23

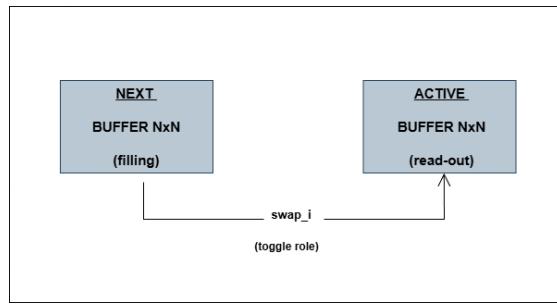

- 3.5 The Frame Loader maintains two memory banks: NEXT, which is being filled by the DMA stream, and ACTIVE, which is consumed by the PE Matrix. When both the frame loading and the current computation are done, the swap\_i signal toggles the roles of the two banks, enabling continuous dataflow without stalling the matrix. . . 24

|      |                                                                                                                                                                                                                                                                                                                                                                       |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

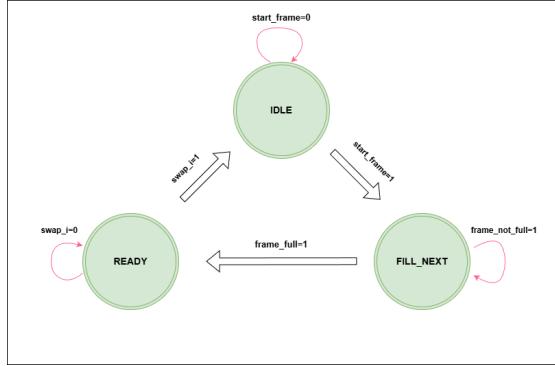

| 3.6  | This state machine has three phases of operation: waiting for the first GEN0 beat to arrive, loading all the beats into the NEXT buffer while monitoring counters and TLAST, and checking the completeness of a frame before asserting planes_ready_o. This structure ensures synchronous, reliable, and protocol-compliant reconstruction of the two planes. . . . . | 27 |

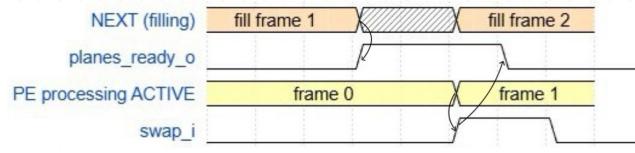

| 3.7  | The signal planes_ready_o is asserted at the end of the NEXT filling phase. The swap only occurs when both conditions are satisfied: NEXT is fully loaded, and the PE Matrix is done processing the ACTIVE frame. The swap_i pulse toggles the buffer roles and initiates the next pipeline iteration. . . . .                                                        | 28 |

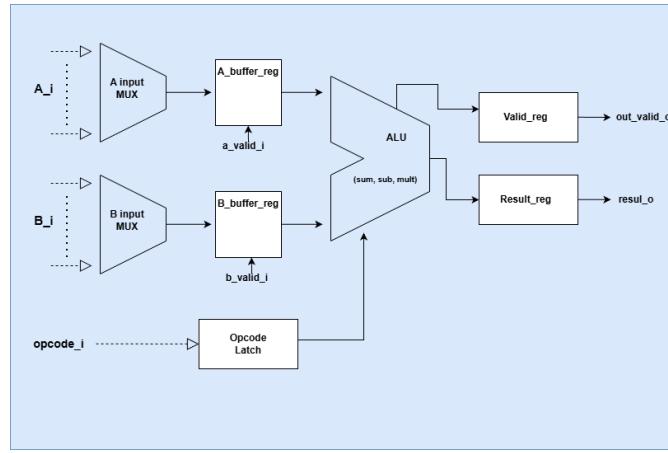

| 3.8  | The operands A and B are selected via input multiplexers, are stored in local registers, combined through the ALU according to the latched opcode, and finally exported via registered outputs with an associated validity flag. . . . .                                                                                                                              | 33 |

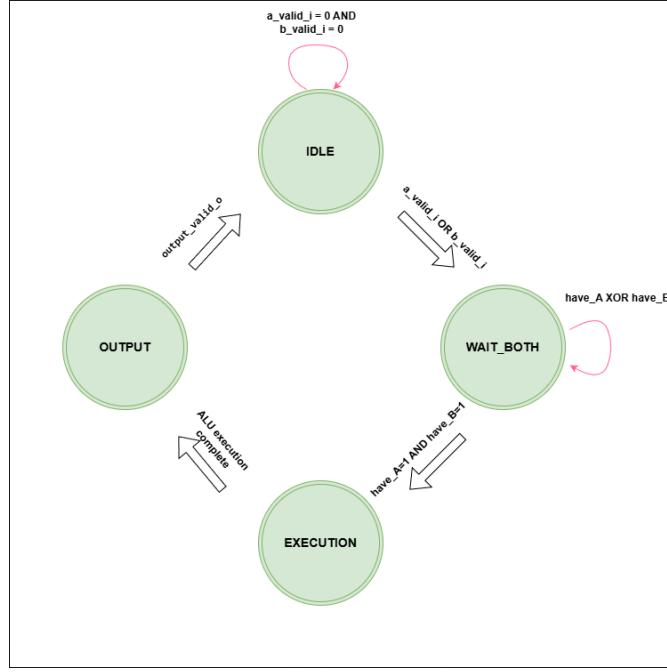

| 3.9  | It first evaluates the availability of operands A and B, stores them in local registers, and then proceeds to the execution phase when both operands and the opcode are valid. The result and its validity bit from the ALU are registered, after which the PE transitions back to the idle state for the next operation. . . . .                                     | 35 |

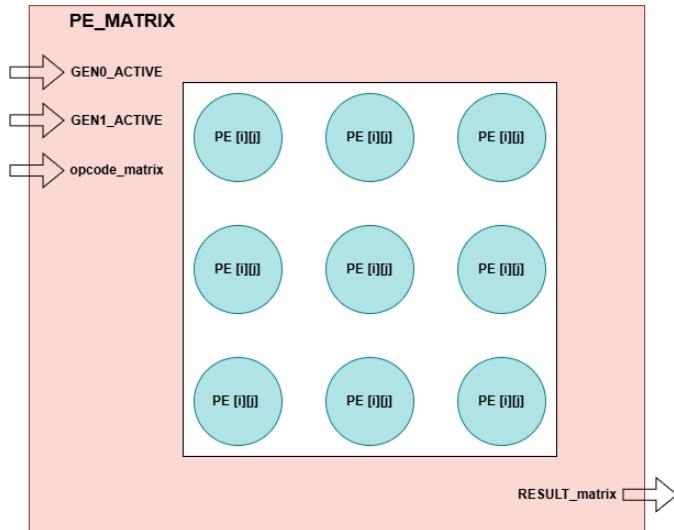

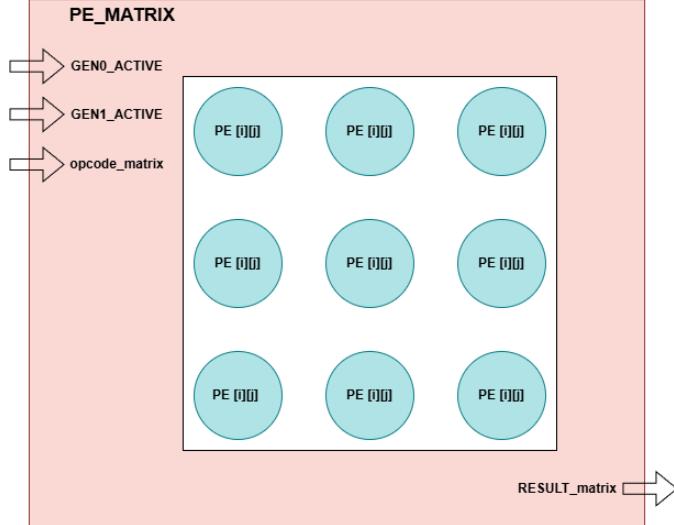

| 3.10 | Each PE operates independently and in parallel, receiving data from the ACTIVE buffer and producing results through a parametrically generated grid structure. . . . .                                                                                                                                                                                                | 40 |

| 3.11 | Each PE operates independently and in parallel, receiving data from the ACTIVE buffer and producing results through a parametrically generated grid structure. . . . .                                                                                                                                                                                                | 45 |

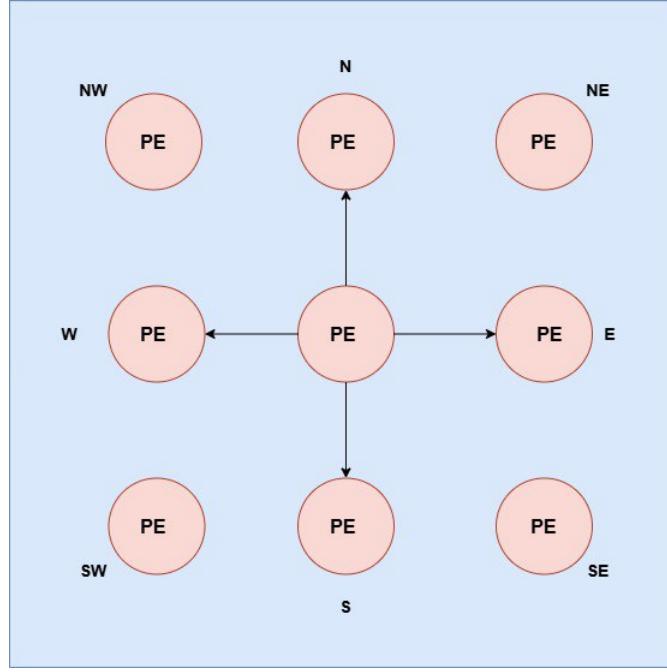

| 3.12 | Each Processing Element is connected only to its four orthogonal neighbours: North, South, East, and West. This structure reduces the complexity in routing while still preserving the locality and regularity, hence is considered one of the most common topologies for CGRA scalable architectures. . . . .                                                        | 46 |

| 3.13 | Processing Elements are connected to their eight immediate neighbours around themselves, including the diagonal links; that is, NW, NE, SW, and SE. Compared to the MESH4 topology, the D-MESH increases the routing flexibility and reduces communication distance, still avoiding global interconnections. . . . .                                                  | 47 |

| 3.14 | Each PE operates independently and in parallel, receiving data from the ACTIVE buffer and producing results through a parametrically generated grid structure. . . . .                                                                                                                                                                                                | 48 |

|     |                                                                                                                                                                                                                                                                                                                                                                    |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

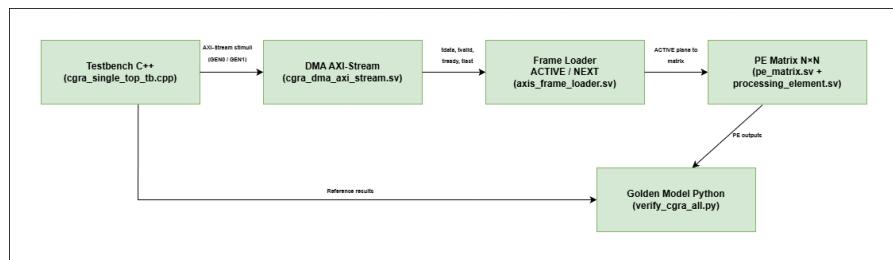

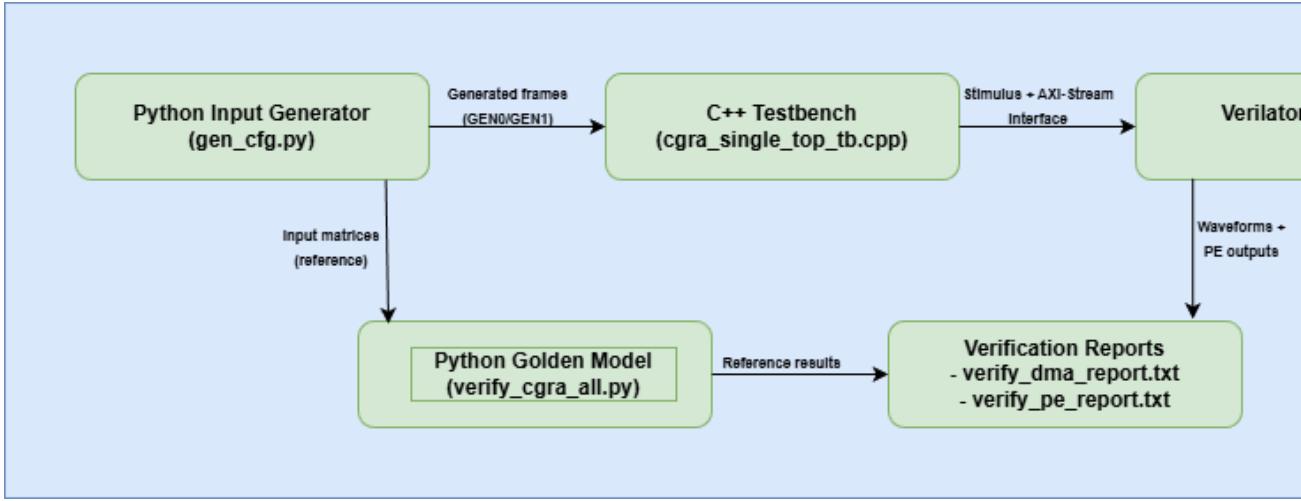

| 4.1 | Overview of the simulation environment. The C++ testbench based on Verilator instantiates the CGRA top module, provides AXI-Stream stimuli via a DMA emulator, and monitors key Control signals, while a Python-based golden model is utilized for its validation.                                                                                                 | 56 |

| 4.2 | AXI-Stream data path from the DMA emulator to the CGRA. The DMA generates tdata, tvalid and tlast, while the Frame Loader asserts tready and reconstructs the incoming frame into the ACTIVE and NEXT buffers. Once a frame is complete, the ACTIVE buffer is fed to the PE Matrix for computation. . . . .                                                        | 58 |

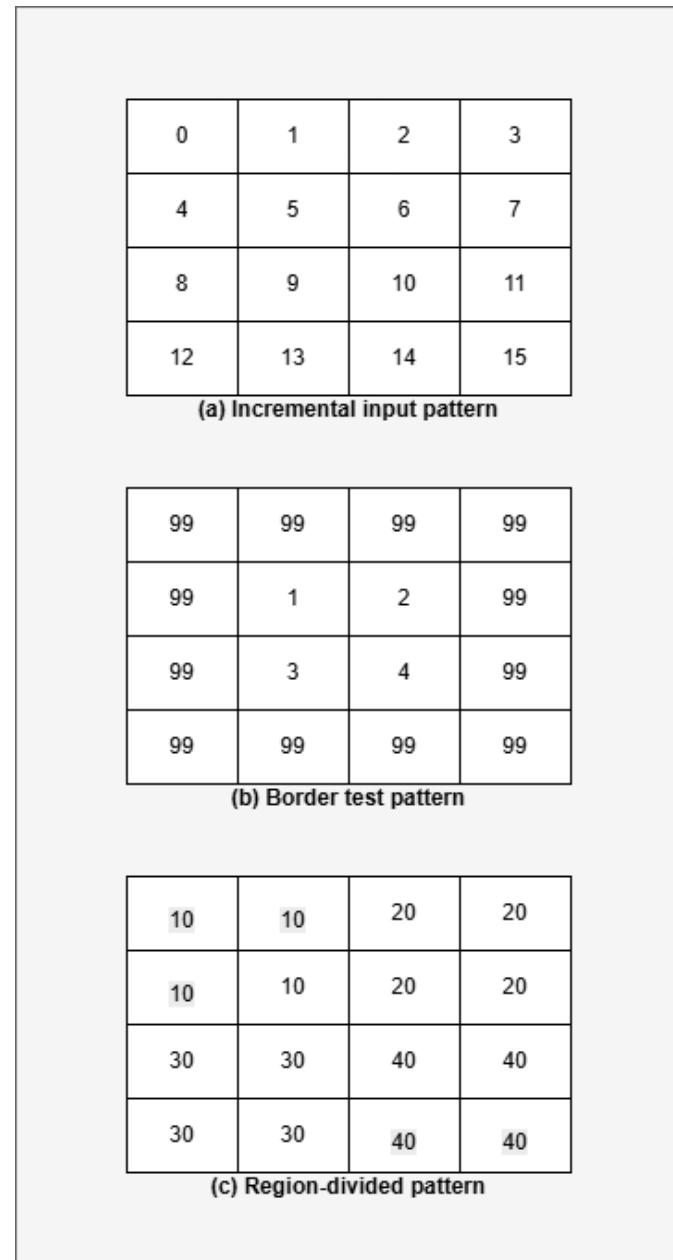

| 4.3 | Example input patterns used during functional verification. Incremental, border-based, and region-divided patterns are employed for Highlight alignment issues, boundary conditions and reconstruction problems. in the Frame Loader as well as along the data path. . . . .                                                                                       | 60 |

| 4.4 | Verification workflow. Python scripts generate input frames, the C++ testbench drives the Verilator simulation, and a Python-based golden model validates the CGRA outputs and produces verification reports. . . . .                                                                                                                                              | 62 |

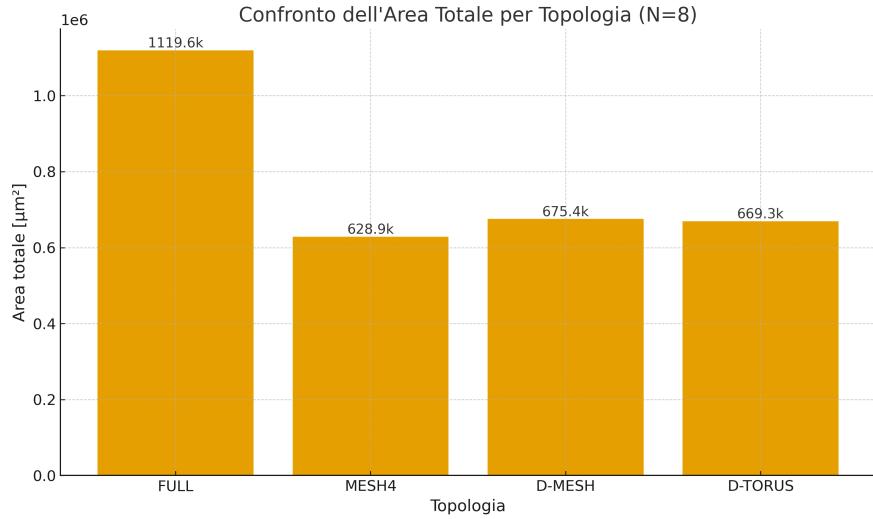

| 5.1 | FULL indeed features a much larger total cell area due to its dense network of interconnects, which are implemented through a large amount of multiplexers and routing logic. By contrast, the MESH4, D-MESH, and D-TORUS topologies feature much smaller and similar areas; the reduction compared to FULL is more than 40% in all three cases. . . . .           | 67 |

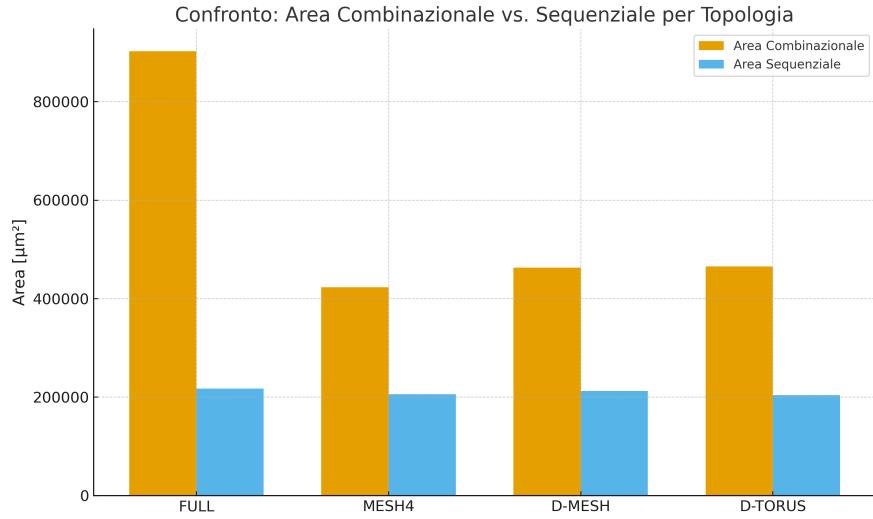

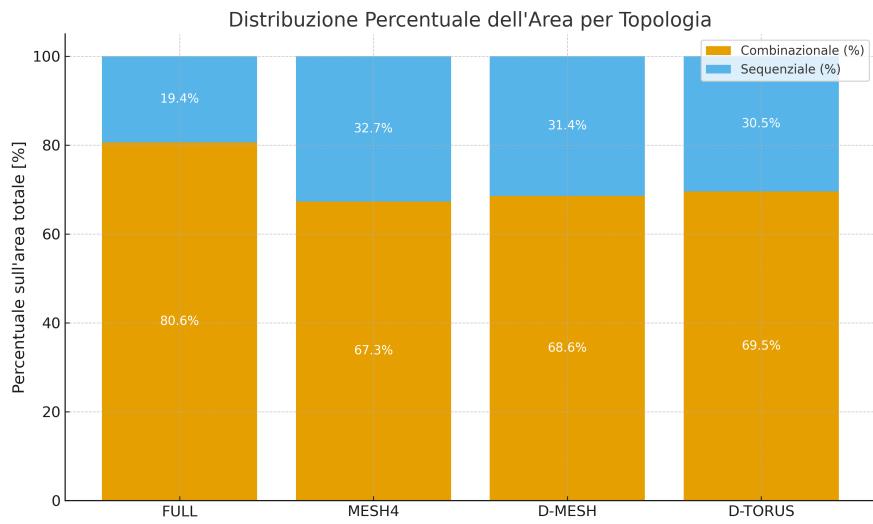

| 5.2 | The combinational logic clearly dominates the total in all cases, especially in the FULL topology where it accounts for over 80% of the total. Sequential area remains roughly constant between configurations and serves to confirm that the main source of overhead is indeed the interconnection fabric rather than the processing elements themselves. . . . . | 68 |

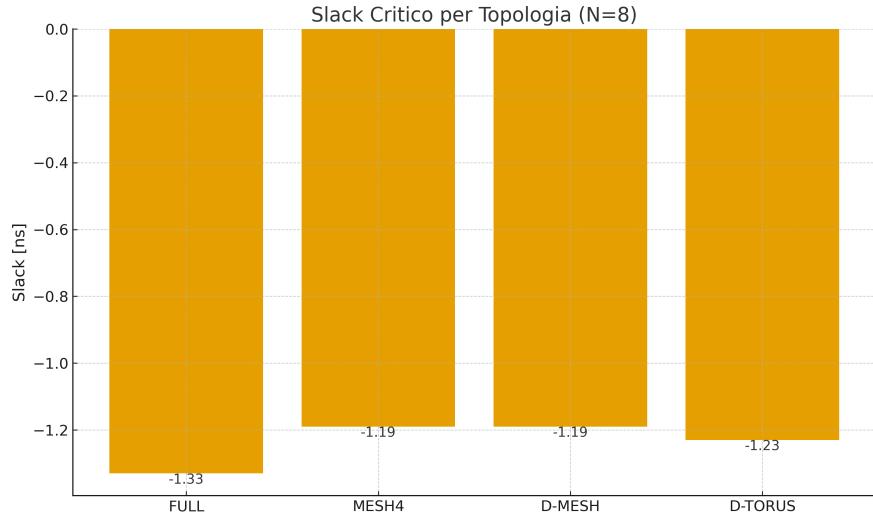

| 5.3 | All topologies present a little negative slack value, since no aggressive timing optimization was applied. FULL is the most timing-constrained topology owing to its deeper logic levels and higher fan-in. MESH4, D-MESH, and D-TORUS present very similar slack values, reflecting their lower combinational complexity. . . . .                                 | 69 |

| 5.4 | If FULL topology devotes about 80% of the area to combinational logic, this really underlines the heavy impact of its extensive connectivity. The other topologies have a more even distribution, where combinational logic occupies something like 67–70% of the area, so they are much more structurally efficient and easier to scale. . . . .                  | 70 |

# Capitolo 1

## Introduction and Context

In recent years, reconfigurability and parallelism have taken a central role in the evolution of modern computing architectures. This trend is driven by the need to keep power consumption under control while still maintaining high computational performance, pushing both the scientific and industrial communities to seriously consider hardware solutions that are specialized yet flexible. Coarse-Grained Reconfigurable Architectures (CGRAs) emerge in this scenario as an increasingly relevant research area because they offer a very attractive compromise: they combine ASIC-like performance with the flexibility typically associated with FPGAs.

A CGRA can be described as a matrix of processing units, the Processing Elements (PEs). PEs are programmable units in terms of arithmetic operations and interconnect configuration, allowing communication with nearby elements through configurable links. Thanks to this feature, each CGRA can be programmed for different applications, exploiting data and operation-level parallelism as much as possible. The main difference that distinguishes CGRAs from FPGAs lies in the granularity of the operations processed by the two systems. CGRAs operate on larger “coarse-grained” blocks and work at a higher abstraction level compared to FPGAs. This means that they do not implement elementary logic gates, but arithmetic functions or mid-level logic blocks. This characteristic leads to significant benefits in terms of area, operating frequency, and power consumption.

Since high performance and reconfigurability have become equally important in many domains, the attention has shifted strongly toward CGRAs. Their flexibility allows them to address different requirements across different applications without needing to redesign the hardware each time. In practical fields such as machine learning, signal processing, artificial intelligence, and generally in systems requiring high computational capability, CGRAs now play a key role. Within these scenarios lies the present thesis work, whose main goal is the design of a fully parametric CGRA, capable of adapting to different configurations by allowing the user to modify both its topology and its size, while still enabling verification and synthesis.

## 1.1 Motivations and Objectives

The project originates from the idea of investigating the impact that different levels of interconnection among the PEs may have in terms of area and timing. The goal is to build a CGRA architecture reconfigurable at the RTL level, allowing the user to parameterize the size of the matrix ( $N \times N$ ) and the interconnection topology among the Processing Elements during computation. Thanks to this implementation, it becomes possible to experimentally observe how the degree of connectivity affects the key design parameters.

In this project, unlike other simpler implementations, the aim is not only to simulate the behavior of the various processing units connected in a certain way, but to operate by creating a truly functioning system, capable of receiving input data and providing output data, so that it can be connected, if necessary, to other external modules without having repercussions on the overall operation.

The way in which data is transferred to the matrix that will then process them is through a DMA (Direct Memory Access) module that uses an AXI-Stream module. Through a double-buffer mechanism with a logic called ping-pong, this DMA is always in contact with another module called Frame Loader, which is responsible for managing the frames and sending them correctly to the matrix.

The system is indeed reconfigurable through a series of RTL parameters that, together with dedicated logic, determine which sources can be used as input by the various PEs.

The topologies implemented in this project are four:

- **FULL**: each PE can communicate with all the others in the matrix;

- **MESH4**: each PE communicates with the four neighbors (north, south, east, west);

- **D-MESH**: communication extends to the eight surrounding neighbors, including the diagonals;

- **D-TORUS**: similar to D-MESH but with wrap-around connections on the borders.

## 1.2 Technological Context

The limitations of traditional solutions such as ASICs and FPGAs have inevitably shifted the focus toward reconfigurable architectures. ASICs offer excellent performance and low power consumption, but they are completely static in terms of functionality: once a chip is manufactured, changing its behavior requires designing a new one. FPGAs, on the other hand, offer much greater reconfigurability but with limitations in area and operating frequency. CGRAs lie exactly in between these two extremes, offering a solid compromise. In CGRAs, each PE corresponds to a functional logic block rather than a LUT, which allows for higher operating frequencies and reduced routing complexity.

Another fundamental aspect of the entire project is certainly the comparison of the various topologies. It is important to underline how the different topologies are all generated from the same RTL with slight modifications, yet still within the same code. These are also synthesized following the exact same flow, so thanks to these small details it is possible to perform an effective comparative analysis and see what the real impact of the topology is on the design.

## 1.3 Design Approach

The entire project has been written in SystemVerilog, a language that ensures clarity in the descriptions and facilitates a modular and parametric structure. For testing and verification, Verilator has been used together with a C++ testbench. Inside this testbench, an automated flow was implemented, capable of generating stimuli, handling data loading through the DMA, running the required computations, and producing CSV files containing the information needed for final verification.

Entering the core of the project, the Processing Elements operate independently and execute 32-bit arithmetic operations such as addition, subtraction, and multiplication. Their execution is synchronized through validation signals. A separate logic block is responsible for constructing the matrix based on the selected topology and size, generating a real interconnected structure in which the links between PEs correspond exactly to the configuration chosen by the user.

A module of utmost importance is certainly the DMA (Direct Memory Access), which is responsible for retrieving data from a memory and "transporting" them—in this case toward another module—through the AXI-Stream protocol. What the DMA does, in short, is read data from memory and send them together with the control signals `tvalid`, `tready`, and `tlast`, which are signals that will then be interpreted by another module and help determine the validity of the data as well as their termination, without needing external triggers for this operation.

The Frame Loader is based on a ping-pong double buffer. It receives the packets sent by the DMA and places them into two memory banks, **NEXT** and **ACTIVE**. When the **NEXT** bank becomes full, a swap signal allows the data in **NEXT** to move into **ACTIVE**, enabling the DMA to immediately refill the **NEXT** bank. This mechanism maintains a constant throughput and prevents unnecessary stalls in the system.

The parametric PE matrix is the central part of the project. Each PE receives two inputs ( $A$  and  $B$ ), which can be selected from a list that includes the two values provided by the DMA (**GEN0** and **GEN1**) as well as the outputs of other PEs. The number of input sources available to each PE depends on the chosen topology. The executed operation is defined by the opcode received in that cycle, and the result is produced within a single cycle and synchronized through validation signals. The chosen topology significantly affects the system, as it changes the number of available sources, and therefore the size of the multiplexer and its selection signal. This has a direct impact on both area and timing.

All the modules described above are connected together in the top-level file `cgra_single_top.sv`. The project is fully parametric, and the values **N** and **TOPOLOGY** can be modified through parameters passed either to the simulator or to the synthesis tool (`-GN` and `-GTOPOLOGY` for Verilator, or environment variables for Design Compiler).

## 1.4 Results

For synthesis, Synopsys Design Compiler was used. Through standard **gtech** libraries, the tool produced results consistent with professional synthesis flows. In order to carry out an objective analysis of the obtained results, each topology was synthesized in fully equivalent environments with identical timing constraints. Once the reports were generated, an analysis of the fundamental parameters was performed to evaluate how the different topologies influenced multiplexer complexity and the length of the critical paths.

A crucial point of the entire work is the comparison among the four topologies. This comparison makes it possible to understand how internal connections, and their increasing complexity, affect the overall design. The results clearly show that a topology with very dense connectivity, such as **FULL**, provides maximum flexibility in the distribution of information, but at the cost of a significant increase in area and delay. Conversely, topologies with fewer connections, such as **D-MESH** and **MESH4**, exhibit lower latency and smaller area usage, although they introduce limitations in terms of data distribution. Positioned between these extremes is the **D-TORUS** topology, which represents a true compromise, improving data distribution by periodically adding wrap-around connections at the edges while keeping area costs under control.

From this analysis emerges the main objective of the study: identifying a balance between physical cost and flexibility, highlighting the importance of topology selection when designing scalable CGRAs. The work presented in this thesis aims to build a connection between academic rigor and practical hardware design. The possibility to vary the interconnection topology dynamically offers a controlled way to study how the internal structure influences communication. The approach adopted in this project is fully based on RTL descriptions and real synthesis flows, enabling the extraction of reliable and consistent results and laying the groundwork for future developments aimed at automatic optimization of connectivity.

# Capitolo 2

## Background and State of the Art

### 2.1 Introduction to CGRA Architectures

Coarse-Grained Reconfigurable Arrays (CGRAs) have gradually consolidated their role as one of the most promising classes of programmable accelerators. Their appeal stems from the ability to combine flexibility and specialization in a balanced manner—a characteristic that becomes increasingly crucial in modern computing platforms. A detailed and influential overview of the field is provided by Podobas et al. [1], who trace the evolution of CGRAs from early DSP-oriented designs to the highly heterogenous and application-driven solutions seen today.

What distinguishes CGRAs from more traditional reconfigurable technologies, such as FPGAs, is the level of abstraction at which programmability is exposed. Instead of manipulating single bits or LUTs, CGRAs operate on coarse computational blocks, typically *Processing Elements* (PEs). Each PE includes an ALU, small registers, and lightweight interconnect interfaces that allow local communication with neighbouring nodes. This coarse granularity leads to dramatically lower configuration latencies and much more predictable execution patterns, both of which are essential in embedded and edge scenarios where energy and area budgets are tightly constrained.

From an architectural perspective, CGRAs were originally conceived to accelerate structured numerical kernels such as matrix multiplications, filtering operations, and finite impulse response pipelines. These workloads align well with the spatial execution model in which data dependences remain stable and regular. Over time, however, the interest in CGRAs expanded significantly, driven by three converging trends: the stagnation of general-purpose CPU scaling, the proliferation of data-intensive tasks at the edge (e.g., computer vision, tinyML, multi-sensor fusion),

and the desire to deploy accelerator-like performance in environments where FPGA devices may be too costly or power-hungry.

One of the central strengths of CGRAs lies in their communication locality. Many computations involve short-range data dependences that can be satisfied directly within the fabric, without relying on multi-level caches or complex coherence mechanisms. Architectures such as OpenEdgeCGRA [2] explicitly leverage this principle: adjacent PEs can exchange data with negligible overhead, reducing pressure on external memory and enabling sustained streaming execution. This locality-driven approach is particularly advantageous in embedded systems, where the gap between on-chip computation and memory access latency is often large.

In summary, CGRAs occupy a unique position in the design space of programmable accelerators: more flexible than ASICs, significantly more energy-efficient than generic processors, and far easier to reconfigure than fine-grained FPGA fabrics. This combination makes them a compelling candidate for next-generation edge-computing platforms, especially when predictability, efficiency, and scalability are equally important.

A comprehensive and widely cited overview of this architectural family is provided by Podobas et al. [1], who classify CGRAs based on granularity, reconfigurability model, and interconnect structure. Their analysis highlights how CGRAs evolved from early DSP-oriented accelerators toward more heterogeneous and compiler-driven systems, setting the conceptual foundations for much of the modern research discussed in this chapter.

## 2.2 Computation Models and CGRA Classification

The diversity of applications that rely on CGRAs has fostered a correspondingly diverse set of execution models. One well-established distinction is between *spatial* and *spatio-temporal* architectures.

Spatial CGRAs maintain a fixed mapping of operations onto PEs for the entire duration of a kernel. Each PE performs a single arithmetic or logical function, and the whole dataflow graph (DFG) is laid out statically across the array. This execution model greatly simplifies control, minimizes instruction overhead, and allows for highly predictable performance. However, it presupposes that the DFG fits onto the available hardware resources. For kernels with many operations, deep dependency chains, or frequent branching, such direct mapping may be impractical.

Spatio-temporal architectures introduce a temporal dimension: instead of assigning exactly one operation to each PE, they allow each element to execute a short sequence of instructions across multiple cycles. This approach extends the range of kernels that can be mapped on a fixed-size array and supports more complex

behaviours. The STRELA accelerator [3] embodies this philosophy through an *elastic* execution model, where ready/valid signalling and small internal buffers help PEs synchronize dynamically and tolerate variable latencies. Elastic designs thus offer more flexibility, though they increase control complexity and area footprint.

Another major classification axis concerns the dataflow semantics. In **static dataflow**, all data dependences are determined during compilation, producing deterministic schedules. Although this simplifies analysis and optimization, it complicates the execution of kernels with data-dependent control flow or irregular memory accesses. **Dynamic dataflow** architectures, by contrast, allow tokens to carry control information at runtime. Systems such as RipTide [4] and SNAFU [5] demonstrate how dynamic dataflow can be realized even under ultra-low-power constraints. RipTide, in particular, takes advantage of the network-on-chip, delegating several control-flow primitives to routing components while keeping PEs lightweight.

A third dimension of classification arises from the role of compilation. Traditional CGRAs relied heavily on manual mapping, but recent proposals have placed much more emphasis on automated toolchains. Morpher [6] is emblematic of this shift, introducing an *Architectural Description Language* (ADL) that allows designers to specify PEs, interconnects, and scheduling policies with fine granularity. The compiler—rather than the architecture—drives exploration, enabling rapid prototyping of variants and facilitating reproducibility. This is a decisive step forward, reflecting the broader transition from monolithic CGRA designs to modular, reusable design ecosystems.

Finally, interconnect topology remains one of the most distinctive elements in CGRA classification. Meshes and tori represent the mainstream solutions due to their simplicity and scalability. However, more expressive fabrics exist: multi-hop connections in architectures related to HyCUBE, as described by Juneja et al. [6], reduce average communication distances at the cost of moderately more complex routing logic. The interconnect, more than any other component, profoundly influences the system’s performance, energy consumption, and ability to sustain concurrency.

## 2.3 Modern Microarchitectures and Processing Element Features

The Processing Element (PE) constitutes the computational core of a CGRA, and its microarchitectural design largely determines the overall efficiency of the system. Different CGRA families emphasize different trade-offs, but many recent proposals agree on a minimalist PE structure: an ALU supporting basic arithmetic and logic

operations, a handful of registers to buffer intermediate values, multiplexed input paths, and—when temporal behaviour is allowed—a tiny instruction memory.

OpenEdgeCGRA [2] offers a clear example of this design philosophy. Each PE includes a 32-bit ALU capable of basic operations, a small local memory for storing up to a few dozen instructions, and simple routing logic that supports direct communication with neighbouring PEs in a toroidal configuration. This simplicity keeps area and power overhead minuscule, enabling the array to scale to multiple rows and columns even within modest silicon budgets.

More sophisticated PEs appear in designs that target near-sensor computing, where complex control-flow structures and nested loops are frequent. The Integrated Programmable Array (IPA) accelerator described by Das et al. [7] includes a richer set of local resources, complemented by a tightly coupled multi-bank TCDM memory subsystem. This allows the array to handle a broader class of kernels, including those featuring non-trivial conditional execution.

Elastic architectures introduce yet another form of PE complexity. In systems like STRELA [3], each PE contains ready/valid buffers that act as local synchronization points. While these additions increase hardware cost, they allow the system to tolerate latency variations caused by memory accesses or network congestion. They also relax the pressure on the global scheduler, which no longer needs to impose strict timing alignment across all nodes.

Communication among PEs, finally, plays a central role. Whereas some CGRAs employ direct neighbour-to-neighbour links, others adopt multi-hop routing or rely partly on buffers inside the interconnect. The HyCUBE architecture described in [6] explores a lightweight multi-hop model that achieves a balance between routing flexibility and hardware simplicity. As communication overhead increasingly dominates energy expenditure in modern workloads, the structure of the interconnect becomes a first-class architectural component.

## 2.4 Generation Frameworks and Compiler Tool-chains

The growing architectural diversity of CGRAs has made the compiler a decisive part of the design process. Unlike conventional processors, where instruction scheduling and register allocation dominate the compilation flow, CGRA compilation must additionally handle spatial placement, routing, pipeline initiation intervals, memory bank selection, and buffer management. Each of these steps can profoundly influence the overall execution efficiency.

Historically, early CGRA compilers were tightly coupled to specific architectures, often relying on fixed templates and manual mapping. This approach limited scalability and prevented designers from exploring heterogeneous PEs or alternative

routing fabrics. As CGRAs became more expressive, such rigid toolchains proved increasingly inadequate.

A significant conceptual leap arrived with frameworks that embraced architectural parametrization and full-stack modularity. Morpher [6] is perhaps the most mature example of this new generation. The framework introduces an extensible *Architectural Description Language* (ADL) that allows architects to define the structure of PEs, functional units, register files, buffers, memory subsystems, and the topology of the interconnect. By separating architecture specification from compiler internals, Morpher enables rapid exploration of entire design families while preserving functional correctness and toolchain stability.

One of Morpher’s strengths is its integration with LLVM, which automates the extraction of DFGs from C code. This high-level flow is particularly valuable in research contexts, where exploring multiple architectural variants is as important as pushing performance. The ADL also helps enforce consistency between hardware and software, reducing manual effort and minimizing the risk of mismatches between RTL implementation and compiler assumptions.

At the opposite end of the design spectrum lies SNAFU [5], a framework deliberately crafted for ultra-low-power environments. Instead of pursuing maximal flexibility, SNAFU is built around a simple, almost frugal philosophy: keep PEs lightweight, make network routers bufferless, and enforce strictly in-order dataflow. This approach pays off in scenarios where nanowatt-to-microwatt efficiency is the priority. Notably, SNAFU’s mapping and scheduling algorithms explicitly avoid complex heuristics, ensuring deterministic compilation and minimal overhead.

Between these two extremes—full architectural agility and fully energy-optimized specialization—lies a broad middle ground occupied by a wide variety of academic and industrial frameworks. Although they differ in scope, most share three common objectives:

1. provide a structured way to describe CGRA components,

2. automate mapping and routing,

3. ensure correctness even under complex control-flow or memory behaviors.

An additional, increasingly relevant line of work concerns frameworks that integrate architecture generation with application-driven optimization. This is exemplified by systems such as DSAGEN (commonly referenced within the CGRA community), which start from a set of representative workloads and automatically synthesize a CGRA optimized for them. These designs highlight how workload-aware generation can yield significantly more efficient architectures.

All these trends underline an important fact: the rise of CGRAs has been fueled not only by advances in silicon architectures but also by the emergence of flexible, robust toolchains capable of managing the complexity of spatial computing.

Without such toolchains, even elegant CGRA architectures would struggle to find adoption beyond research prototypes.

## 2.5 Memory Systems, Data Movement, and DMA in Modern CGRAs

Data movement is often the hidden bottleneck in CGRA-based systems. As applications become more data-intensive and memory hierarchies grow more heterogeneous, sustaining a consistent throughput requires careful orchestration of memory access patterns, buffering, and communication paths. Thus, modern CGRAs tend to incorporate memory subsystems that minimize global memory traffic and exploit locality whenever possible.

One common strategy is the adoption of multi-bank scratchpads or TCDM (Tightly Coupled Data Memory) structures. In the IPA accelerator [7], a multi-bank TCDM is tightly integrated with the CGRA fabric, enabling several PEs to issue concurrent load/store operations while spreading requests across independent banks. This design significantly reduces contention and prevents memory hotspots, which are particularly harmful for dataflow execution where a single delayed operand can stall an entire pipeline.

Another strategy—increasingly popular in embedded and edge platforms—is the use of multiple parallel DMA engines. OpenEdgeCGRA [2] A recent evaluation by Carpentieri et al. [8] further demonstrates the practical relevance of OpenEdge-CGRA, showing that its distributed DMA structure and lightweight routing fabric enable efficient acceleration of convolutional layers. Their study confirms that even relatively small CGRA instances can sustain high throughput when the memory subsystem is carefully co-designed with the computational array.

# Capitolo 3

## Architecture of the Proposed CGRA

### 3.1 General Overview

In the proposed thesis, the core architecture is designed with a specific goal: creating a fully parametric platform in which both the size of the array and the interconnections can be modified while keeping the overall processing flow unchanged. Another central aspect of this work is not simply building an accelerator capable of performing its task, but providing a platform that allows the designer to investigate which configuration best suits specific needs. This is achieved by evaluating which interconnection topology between the Processing Elements is more appropriate for given requirements and by observing how different topologies influence the actual behavior of the digital design.

The base architecture consists of three main blocks responsible for organizing and processing the data flow. The blocks are:

- an AXI-Stream DMA that handles the propagation of input data and acts as a conveyor belt from memory to the PE matrix,

- a ping-pong frame loader that receives the data transported by the DMA and forwards them in the correct order to the matrix,

- an  $N \times N$  matrix of Processing Elements with a selectable topology that processes the data and produces results.

**Figura 3.1:** Three main components of the processing pipeline are shown in this figure. The AXI-Stream DMA, the Frame Loader and the parametric matrix of Processing Elements - PEs. These modules cooperate in receiving the input planes and reconstructing them inside the ping-pong buffers. and process them in parallel within the CGRA.

To keep the overall process as linear as possible, a pipeline has been implemented to maintain a continuous flow without interruptions. These three blocks have different roles, allowing a clear separation of responsibilities: the DMA transfers the stream, the frame loader normalizes it and transforms it into frames, and finally the PE matrix processes it according to the selected topology.

A major strength of the project lies in the ability to freely modify the topology

of the interconnections between the processing elements (PEs) without altering the behaviour of the remaining blocks. This characteristic enables reliable comparative analysis, allowing different architectural configurations to be evaluated without introducing undesired side effects.

From a functional point of view, the entire system can be modelled as a three-stage pipeline: *production*, *loading*, and *processing*. Each of these stages is characterised by distinct timing constraints and responsibilities.

The process starts at the DMA, which can be interpreted as a conveyor belt continuously sending two data packets, **GEN0** and **GEN1**, through an AXI-Stream interface. These packets are emitted at a constant rate, while the receiving module regulates the effective data transfer via the standard handshake signals **TVALID** and **TREADY**, ensuring that communication proceeds only when both ends are ready.

The receiver, namely the *frame loader*, decodes the packets transmitted by the DMA and stores them into two memory banks, **ACTIVE** and **NEXT**. The **ACTIVE** bank contains the data currently being consumed by the PE array, whereas the **NEXT** bank holds the data scheduled for processing in the following iteration.

Once the loading of **ACTIVE** into the matrix is complete, a swap mechanism moves the contents of **NEXT** into **ACTIVE** and triggers a new handshake cycle that allows the DMA to refill **NEXT**. Finally, the PE matrix processes the data stored in **ACTIVE** and generates outputs that, depending on the topology, can be used as new inputs for other PEs. The internal structure of each PE is intentionally simple, since the goal is to isolate the behavior produced by the topology itself: two input values are processed using basic arithmetic operations (addition, subtraction, multiplication) to generate an output.

The overall organization of the system is intentionally simple and highly predictable. While the processing matrix handles the current frame, the frame loader is already preparing the next one. Once the computation finishes, the **NEXT** buffer is cleared and promptly refilled as the DMA streams in new data. This continuous, stall-free flow ensures that the entire pipeline operates smoothly and, more importantly, that synthesis results remain reproducible and directly comparable across different system configurations.

### 3.1.1 Design Objectives

In this project, the main guiding principles were modularity, parametricity, and observability.

Modularity was achieved through the complete independence of each module from the others. The three main modules - DMA, Frame Loader, and Matrix-do does not share internal signals that could compromise the operation of one module with respect to another. They are not generated using fixed assumptions about the array size, and such information is not required for their internal functionality. Communication happens through formal interfaces only. This permits each module that can be independently verified, analyzed, and replaced if needed, without in turn affect the whole system.

Parametricity is the guiding design principle. All modules adapt correctly to the  $N \times N$  array size selected at configuration time. The matrix is generated using Produce constructs that would make it dependent on constant  $N$  set by the user. Signals such as multiplexer selectors, which determine for each PE its inputs, are will be created automatically, depending on the topology selected. The frame loader and DMA adapt dynamically: the DMA simply delivers information packets without caring about their content, while the frame loader adjusts the buffer sizes according to the selected configuration.

Finally, there is observability as another critical aim. The purpose is to assess how different topologies influence synthesis metrics. This is enabled by the low design complexity: a shallow pipeline, explicit interfaces, simple control logic and Isolated combinational paths. All these aspects make it possible to analyze results. and reach conclusions without vague or misleading behavior.

### 3.1.2 Hierarchical Structure of the Architecture

From an RTL point of view, the architecture is organized with a regular and fully synthesizable hierarchy. The main module, `cgra_top.sv`, is responsible for assembling and connecting the three functional blocks. Inside it we find:

- the instance of the AXI-Stream DMA, configurable according to the data width,

- the instance of the ping-pong frame loader, responsible for reconstructing the frames,

- the generation of the PE matrix through a double `genvar` loop,

- the generative module that builds the interconnections between the PEs based on the selected topology.

The top-level does not contain complex control logic: the pipeline is designed so that each module behaves as a closed box, with explicit synchronization and clear validity signals. The AXI-Stream interfaces ensure a strict separation between data transmission and data consumption, reducing the risk of unexpected stalls.

### 3.1.3 Data Flow and Synchronization

Data flow is deterministic in the platform, and there is a well-defined temporal sequence. The **DMA** will continue generating data as long as the frame loader asserts its **TREADY** signal. The loader writes into the **NEXT** bank until the frame is complete. At the swap signal, **ACTIVE** and **NEXT** swap their roles, and the **PE matrix** immediately starts consuming the data now stored in **ACTIVE**, propagating values according to the selected **topology**.

**Figura 3.2:** The DMA transfers the two input planes, GEN0 and GEN1, through AXI-Stream. The Frame Loader reconstructs the frame inside the NEXT buffer, while the PE Matrix processes the ACTIVE buffer. When NEXT is fully loaded and the matrix finishes the current frame, the swap signal synchronizes the ping-pong mechanism so that loading and computation keep executing continuously in parallel.

### 3.2 DMA AXI-Stream

Communication protocols in CGRA architectures represent a clear critical point, mainly because modern accelerators increasingly require linearity in data transmission, as the goal is to obtain a rhythmic and predictable processing flow. In the proposed thesis, the task of data transmission is assigned to a DMA, which is intended to act as a “conveyor belt” between the local memory and the logic responsible for loading the frames into the processing pipeline.

The protocol selected for the transmission of data is **AXI-Stream**. The main role of **DMA** is designed to fetch data blocks from the memory, divide them into AXI-Stream packets, which are **GEN0** and **GEN1** in this project. Whole design was conceived with the main purpose of providing for continuous data Transfer while fully conforming with **AXI-Stream** criteria both to meet modern system requirements and enable easier integration of this module with the frame loader.

Entering more into the details and trying to understand the intrinsic functioning of the DMA, one can see that it extracts “raw” data from memory and transforms them into AXI-Stream packets. For each iteration, the DMA provides two packets—**GEN0** and **GEN1**—which correspond to the two planes on which the system’s start phase is based, since they contain the initial input values for each PE. The decision to adopt two physically separate packets was made to maintain simplicity and order in the design, a simplicity that allows the frame loader to associate each input with its specific value without ambiguity. Since the packets are separated, there can be no interleaving that would lead to incorrect computation due to mismatched inputs. The DMA therefore plays a crucial role in the project, as it must guarantee precise ordering and reproducibility with constant timing.

### 3.2.1 Internal Architecture and State Machine

The operation of the module is based on a state machine composed of four main states: `idle`, `send0`, `send1`, and `done`. In the first state, everything is deactivated—the AXI-Stream output port as well as the memory address pointer—while the module waits for a start command. Once the start command is received, it transitions to the next state, where the two base addresses for the planes to be transferred are stored, along with the number of words that will form the two planes.

During the `send0` state, the DMA reads the internal memory starting from the specified address and continues sequentially; once a word is extracted, it is placed on the `tdata` signal (AXI-Stream bus), and immediately after, the `tvalid` signal is asserted. The exchange also depends on the availability of the receiver: only when `tready` is active do the two protocols perform the handshake. Otherwise, the DMA blocks the entire flow, keeping the `tdata` value frozen to avoid unnecessary memory reads and preventing undesired interruptions.

**Figura 3.3:** The DMA sequences the transmission of GEN0 and GEN1 over AXI-Stream through the IDLE, SEND0, SEND1, and DONE states..

### 3.2.2 AXI-Stream Protocol Handling

This state machine design was necessary for several reasons: primarily, to maintain coherence with the AXI-Stream protocol itself, but even more importantly, to allow the frame loader to manage its internal operation in a simple and rhythmic way, without having to deal with potential data loss or overruns.

A key element of AXI-Stream is the **tlast** signal, which indicates when the last word of the packet has been reached. In the DMA designed for this project, **tlast** is generated using a counter that counts the internal beats and marks the last position. This signal is extremely useful, especially for the receiver, which thanks to **tlast** can easily identify the end of the **GEN0** and **GEN1** packets.

The main reason for this mechanism lies in the frame loader buffer: without a signal like **tlast**, the buffer could be filled with values that do not belong to the same packet, creating overlaps and processing errors. Thanks to this protocol, this allows the frame loader to correctly fill its buffer and ensure that **GEN0** and **GEN1** packets without overlap.

Once the transmission of the first packet is completed, the DMA moves to the **send1** state, which replicates the logic already seen for sending **GEN0**, except for the memory pointer. Moreover, the data transmission occurs immediately and sequentially, following the same logical rules and guaranteeing ordered and coherent modularity.

When the packet transmission is finished, the module enters the **done** state, where it generates a pulse on the **done\_o** signal, allowing the upper-level logic to understand that the transfer is complete. In this project, this signal is mainly used by the testbench, which can then send either the swap command to the frame loader or a new start for an additional data transfer.

### **3.2.3 Internal Memory**

A brief analysis must also be made regarding the DMA’s internal memory: this is not a real memory, but rather it is implemented in the simulation environment as a register vector. It was designed this way to verify correct DMA behavior in a realistic situation, but it is not a distinct module; instead, it is directly integrated within the DMA, which therefore does not include any communication protocol toward the outside—an element that could certainly be added in future work.

This memory is used solely to simulate the DMA’s real behavior and is filled with random values by the testbench. The issue with this memory appears during synthesis, because register vectors are synthesized as millions of flip-flops, making the synthesis results unrealistic. For this reason, the memory structure is excluded during synthesis using conditional directives that separate the RTL code and prevent this memory from being synthesized.

### **3.2.4 Robustness**

One of the strengths of this design lies in the robustness of the communication protocol. The state machine that handles data transmission was designed to prevent simultaneous activation of multiple start commands or unexpected interruptions during packet transfer.

The entire module relies on synchronous logic, in order to avoid undesirable situations such as data arriving out of order and to prevent malfunctions if the receiver is not yet ready. The internal counters are designed never to exceed valid limits, thus ensuring that no more data than necessary is read. Similarly, the mechanism that controls the memory read address prevents access outside the region dedicated to the current plane. In this way, any unexpected variations in AXI-Stream signals are handled without side effects, and potential anomalies are prevented from propagating toward the frame loader or compromising the execution of the entire matrix.

### **3.2.5 Conclusion and Considerations**

The decision to adopt a very simple logic was driven by the idea that, if in the future the module needed to be expanded—for example, by adding more planes or modifying the frame size—the entire architecture would not need to be redesigned. Moreover, the AXI-Stream protocol is widely used in the vast majority of embedded systems, which means that this architecture can easily be extracted and integrated into a different context, whether another CGRA or a different type of project.

Everything therefore relies on the coherence of the design and the simplicity of the state machine, which together enable implementations suitable even for more advanced technologies.

### 3.3 Frame Loader

In the developed architecture, the frame loader, which is placed as a “connection” element between the DMA and the matrix of Processing Elements, has a crucial role in guaranteeing the specific features that have already been widely discussed. What the frame loader does is to take the AXI-Stream flow produced by the DMA and convert it into suitable two-dimensional structures that will then be processed by the PE matrix. Its task is also to decouple the serial nature of the DMA from the parallelism of the CGRA, so that each Processing Element immediately has the initial data available for computation, without having to deal with the data transfer logic itself.

To understand the usefulness of this module, it is useful to state a few basic requirements that the Processing Element matrix must satisfy in order to operate correctly:

- the data must be organized in the intended position  $(i, j)$ ;

- the two planes `gen0` and `gen1` must be available in a synchronous way, that is, without sudden variations or updates during normal execution;

- the loading of the following data must not interfere in any way with the computation that is currently in progress.

**Figura 3.4:** The module receives the AXI-Stream data from the DMA, reconstructs the incoming planes inside the NEXT buffer through the input control logic (row/col indexing), and exposes the ACTIVE buffer to the PE Matrix. Swap logic toggles the roles of NEXT and ACTIVE upon  $swap_i$ , implementing the ping-pong mechanism used for continuous frame processing.

All these requirements are fulfilled precisely thanks to the addition of the frame loader module, which stabilizes the system by taking a completely linear data stream, without any intrinsic subdivision into planes and possibly irregular because of AXI backpressure, and transforming it into something stable and ordered, ready to be used by the matrix.

Moreover, its functionality does not stop here: it also serves to keep the CGRA always operational. While the PE matrix is processing the current data, the frame loader is not idle, but it is already taking care of loading the next frame. All of this is implemented with a dedicated mechanism; without it, the CGRA would be forced to remain in a stall phase until the AXI loading was completed and only then could it resume computation. The presence of the frame loader therefore allows a better throughput, precisely thanks to this dedicated logic.

### 3.3.1 Ping-pong Buffer

In modern architectures that require continuity in the data flow, the use of ping-pong buffers is quite common. In the developed project this mechanism becomes even more important, because the frame loader has to cooperate with a fully parametric matrix, which is therefore independent from the loading mechanism.

The basic idea is simple: there are two buffers. One is called **ACTIVE**, and it contains the values used by the matrix for the current computation. The other one is called **NEXT**, and it contains the data coming from the DMA. When the transfer is completed, the system remains in that state until a swap signal arrives. Through this swap signal, the data that were in **NEXT** move to **ACTIVE**, and the **NEXT** buffer can be filled again with new values from the DMA.

**Figura 3.5:** The Frame Loader maintains two memory banks: **NEXT**, which is being filled by the DMA stream, and **ACTIVE**, which is consumed by the PE Matrix. When both the frame loading and the current computation are done, the **swap\_i** signal toggles the roles of the two banks, enabling continuous dataflow without stalling the matrix.

This has been done to guarantee a clear separation between:

- the **data in use**, that is, the data that the matrix is using at that moment to perform the requested computation;

- the **data being loaded**, that is, the data coming from the DMA following the rhythm of the AXI transfer.

In addition, adopting a double-buffer system avoids unpleasant issues such as unwanted overwrites while data are still being processed, or long stall situations where the PE matrix remains idle.

We can say that the double buffer introduces a temporal decoupling level: the matrix (through the frame loader) and the DMA become almost completely independent modules, connected only through the swap signal.

### 3.3.2 Internal Structure

Looking at the internal structure of the module, it contains several macro-components that communicate with each other. The whole block has been designed in a non-trivial way in order to correctly handle the AXI-Stream flow.

The module can be divided into three main blocks:

- **AXI-Stream front-end**, which manages the protocol signals (`tvalid`, `tready`, `tdata`, `tlast`) and also takes care of checking and regulating the input data, that is, whether they arrive in the correct format, at the right moment, and in compliance with the protocol constraints;

- **2D plane reconstruction**, where row and column counters are used to make the addressing of beats inside the buffer very simple. The beats are placed in their predetermined position, and this process is not influenced by the AXI transfer rate;

- **Ping-pong management**, which is the macro-block responsible for selecting the bank (`ACTIVE` or `NEXT`) and managing the storage of frames as well as the generation of the `planes_ready_o` signal and the swap signal.

The beats can be seen as flowing through a pipeline composed of these three macro-blocks. Everything is fully synchronous, in order to avoid critical combinational paths and to make the synthesis of the system easier.

If we want to analyze in more detail the flow of reconstruction of the bidimensional frame, we can start from what happens immediately after the frame loader receives the AXI flow from the DMA. The frame loader transforms the sequence of values into two bidimensional matrices of size  $N \times N$ . This process is not trivial, because the management of the row and column counters must be very precise: they must respect both the rules of the AXI-Stream protocol and the structure that each Processing Element expects to receive.

The two counters are managed as follows:

- the column counter is incremented every time the frame loader receives one beat from the AXI stream;

- the row counter is incremented each time the column counter reaches the value  $N - 1$ .

In this way, all beats are mapped to the correct position  $(i, j)$  in the `NEXT` buffer. Moreover, thanks to the `tlast` signal, which is a characteristic of the AXI protocol, misalignment errors in the frames can be avoided. This is possible because the frame loader constantly checks both the state of the counters and the expected

position of the last beat, and it verifies that **TLAST** arrives exactly where it is supposed to.

Thanks to this constant checking, several non-negligible issues are avoided, such as:

- **premature end**, where part of the matrix remains empty and therefore without valid values, which would lead to completely wrong computations by the PE matrix;

- **delayed end**, which causes overflow in the counters;

- **mismatch between **TLAST** and the internal progression**, which is one of the most common issues in streaming-based systems.

Once the **gen0** matrix has been completed, the state changes, the counters are reset, and exactly the same flow is repeated for **gen1**.

To make the internal flow of the frame loader clearer, it can be summarized in the following steps:

1. accept a beat from the DMA if both **tvalid** and **tready** are active;

2. interpret the data as belonging to **gen0** or **gen1** according to the current state;

3. compute the position  $(i, j)$  using the row and column counters;

4. write the value into the **NEXT** buffer at the corresponding position;

5. update the counters, checking whether a row increment is required;

6. handle **TLAST**, verifying that it occurs at the correct position.

The sequence may seem linear and simple, but a correct result is guaranteed only if the synchronization between all these steps is extremely strict.

### 3.3.3 State Machine and State Management

The state machine of the frame loader is divided into three main phases. It is designed to be very simple but at the same time robust. The process is handled from the first incoming beat up to the moment when the entire frame is fully available.

**Figura 3.6:** This state machine has three phases of operation: waiting for the first GEN0 beat to arrive, loading all the beats into the NEXT buffer while monitoring counters and TLAST, and checking the completeness of a frame before asserting `planes_ready_o`. This structure ensures synchronous, reliable, and protocol-compliant reconstruction of the two planes.

- **The first phase is a waiting phase:** the module is idle, waiting for the first beat of the `gen0` packet. The counters are in reset state, as are the internal structures. The receiver keeps `tready` high to inform the DMA that it is ready to receive data.

- **The second phase is the frame loading phase:** as soon as the AXI-Stream flow starts, the frame loader accepts beats one by one, placing them in the `NEXT` buffer according to the current state of the counters. It monitors the transition from the `gen0` plane to the `gen1` plane and verifies the `LAST` signal. In this phase there is still no communication between the matrix and the frame; the objective is to reconstruct the frame as precisely as possible.

- **The third phase is the validation phase:** when the last beat of `gen1` has been received, a coherence check of the transfer is performed. After that, the loader stops the counters and sets a flag indicating that a complete frame is available. Finally, it asserts the `planes_ready_o` signal toward the top level.

The activation of `planes_ready_o` does not automatically trigger the `swap` signal. This is an intentional design choice, so that this mechanism can be controlled externally, for example through another state machine or, as in this case, simply by the testbench. In this way, it is possible to decide exactly when the new frame should be passed to the matrix and to avoid building a system that iterates indefinitely.

This mechanism makes the entire CGRA more flexible, since it can also accept computations triggered by other peripherals or external controllers.

### 3.3.4 Swap Handling and Stability of the ACTIVE Planes

The moment dedicated to the swap between the two buffers is one of the most delicate steps of the entire component. The frame loader must ensure that the replacement of the planes does not interfere with the computation already in progress, guaranteeing that the PE matrix always operates on a stable and unchanged set of values for the entire duration of the computation.

To obtain this result, the system performs the swap only when it receives an explicit command from the upper level, represented by the `swap_i` signal.

**Figura 3.7:** The signal `planes_ready_o` is asserted at the end of the NEXT filling phase. The swap only occurs when both conditions are satisfied: NEXT is fully loaded, and the PE Matrix is done processing the ACTIVE frame. The `swap_i` pulse toggles the buffer roles and initiates the next pipeline iteration.

When the swap request arrives, the module performs three fundamental operations:

1. it deactivates the buffer currently marked as ACTIVE;

2. it promotes the NEXT buffer to the role of new ACTIVE;

3. it prepares the old ACTIVE buffer to contain the next frame.

It is essential to note that the frame loader never performs the swap autonomously: this prevents unwanted or premature updates and ensures that the entire matrix always sees consistent data.

The toggle between the two planes is done at RTL level merely by toggling the bit `active_bank_q`, which determines which bank must be presented to the PEs. This design choice greatly reduces hardware cost and avoids the need to physically copies the data, making this solution very efficient.

### 3.3.5 Robustness, Error Handling and Prevention of Anomalous Conditions

Beyond correct data routing, a crucial part of the frame loader concerns its ability to react to irregularities in the AXI-Stream flow. Even if the protocol is quite flexible, it may produce non-ideal conditions such as unexpected delays, extended backpressure or beats that are not perfectly aligned in time. The module must therefore guarantee the correct reconstruction of the frame even in the absence of a constant rhythm.

To deal with these situations, the design implements two complementary forms of protection:

- **temporal protection:** each beat is accepted only if `tvalid` and `tready` are both active at the same time, preventing premature reads;

- **structural protection:** the system prevents counter advancement or state transitions if the flow does not respect the expected order.

In other words, every beat is treated as an independent event and becomes valid only if all the expected conditions are met. If something appears inconsistent, the module automatically suspends its progression until the input returns to a correct state. This avoids overwriting data in the NEXT buffer and prevents the generation of corrupted frames.

At the same time, the loader verifies that:

- the total number of beats for each plane is the expected one;

- the `TLAST` signal appears only on the last beat of the plane;

- both planes — `gen0` and `gen1` — are complete before `planes_ready_o` is asserted.

If any of these constraints is violated, for example because of a misplaced `TLAST`, the system asserts the `err_protocol_o` signal, informing the upper level that an anomaly has occurred. This approach drastically reduces debugging time and prevents the error from propagating into the matrix.

### 3.3.6 Integration with the Top-Level and with the PE Matrix

The true importance of the frame loader becomes clear when it is observed in the wider context of the architecture. Its logic has been developed to integrate naturally both with the DMA, which is responsible for the AXI-Stream flow, and with the PE matrix, which instead requires parallel data that are perfectly stable.

On the input side, the frame loader communicates with the DMA through the main AXI-Stream signals:

- `tdata`, which carries the data content;

- `tvalid`, which indicates when the data are available;

- `tready`, which tells the DMA that the frame loader is ready to receive;

- `tlast`, which marks the end of a plane.

This full adherence to AXI-Stream makes the module highly reusable and compatible with any AXI-Stream source, increasing the modularity of the entire project.

On the output side, the interface toward the PEs is intentionally kept simple: `gen0_active_o` and `gen1_active_o` are presented as static arrays, already ready to be used by the matrix, without any handshake or validity logic. In this way:

- the data path toward the PEs remains extremely linear;

- the matrix is completely isolated from the complexity of the AXI protocol;

- the planes remain stable for the entire duration of the computation.

Even while the DMA is already sending the next frame, the matrix continues to work without interruptions on the `ACTIVE` plane, maintaining deterministic and reliable behavior.

### 3.3.7 Timing, Performance Aspects and Relation to Global Throughput

One of the key goals of the architecture is to avoid situations where the CGRA has to wait for data loading, so that it can quickly move from one frame to the next. The frame loader contributes directly to this goal through two fundamental mechanisms:

- the ability to fill the NEXT buffer while the matrix is working on the ACTIVE buffer;

- the fact that the swap is performed only when requested by the controller.

In this way, the time required by the DMA to send the data does not directly affect the overall throughput of the architecture. Loading becomes a “shadow” activity that proceeds in parallel with the actual computation.

For example, if the matrix needs 2000 cycles to complete a batch, and the DMA needs 1400 cycles to transmit the next frame, the architecture can operate without any pause: by the time the matrix finishes, the next frame is already ready in the NEXT storage.

From a performance point of view, this means that the maximum speed is determined almost exclusively by the computation time, while the AXI-Stream transmission is hidden behind the processing. This makes the architecture particularly effective in streaming or iterative scenarios.

### 3.3.8 Scalability and Adaptation to Different Matrix Sizes

One of the most interesting features of the **frame loader** is its ability to scale together with the size of the **matrix**. Thanks to the automatic generation of the internal structure, the module can be easily adapted for matrices of any size without modification of the core logic.

As the parameter  $N$  increases, we mainly observe:

- a proportional increase in the memory required for the ACTIVE and NEXT buffers;

- a higher number of beats needed to complete each plane;

- longer cycles to fill the NEXT buffer;

- slightly longer stream-to-matrix reconstruction times.

Despite this, the internal organization — `TLAST` management, counters, FSM and ping-pong mechanism — remains unchanged. This allows the frame loader to be used both in compact configurations and in large designs, making it extremely flexible.

In an ASIC context, this property is particularly useful, since the only resource that really grows is the internal memory, which can be efficiently implemented with dedicated SRAM blocks.

### 3.3.9 Final Design Considerations

The double-buffer frame loader is one of the cornerstones of the entire architecture. Its ability to translate an AXI-Stream flow into two coherent bidimensional planes, while keeping loading and computation separated, makes it an essential element from both an architectural and a performance perspective.

The combination of:

- structured frame reconstruction,

- double `ACTIVE/NEXT` buffer,

- full adherence to AXI-Stream specifications,

- swap controlled by the upper level,

- complete isolation between the serial data flow and the parallel domain of the matrix,

allows the CGRA to reach performance levels typical of much more complex systems, without sacrificing modularity, readability of the RTL code, or scalability.

## 3.4 Processing Element