**POLITECNICO DI TORINO**

Cybersecurity National Lab - CINI

Master Degree Thesis

Master Degree in Cybersecurity

**Vulnerability Assessment of Low-Cost

IoT Devices:

Towards a Virtual Hardware Security

Training Environment**

Author: Alessandro GENOVA

Advisor: Samuele Yves CERINI

Co-Advisor: Nicolò MAUNERO

December, 2025

# Abstract

Consumer-grade Internet of Things (IoT) devices, such as low-end routers, IP cameras and other always-connected appliances, have become an integral part of modern life, providing everyday connectivity and digital services in homes and small businesses. However, their affordability often comes at the expense of security. Manufacturers targeting the consumer market prioritise cost and usability, resulting in devices with critical vulnerabilities that can be exploited to gain unauthorised access and steal sensitive data. Tampered devices containing Trojan horses can also be reintroduced into the market. This widespread fragility highlights systemic weaknesses in the IoT ecosystem and emphasises the need for a practical approach to understanding hardware security.

At the same time, opportunities for hands-on hardware security training remain limited. Practical exercises on physical devices are rare and are often confined to expensive, hard-to-reach conferences. Furthermore, access to virtual platforms capable of realistic hardware simulation is restricted. Unlike software-focused Capture the Flag (CTF) exercises, which can be set up quickly with minimal resources, hardware-oriented education faces higher development barriers. It is difficult to provide learners with realistic device responses and interactions, not to mention reliable teaching materials that accurately reflect actual device behaviour. These limitations create a gap between the vulnerabilities present in everyday devices and the ability of professionals to study and mitigate them in a reproducible learning environment.

To address the issue, the study evaluates real consumer IoT devices to identify vulnerabilities in their hardware, firmware, companion mobile apps, and network protocols. The aim is to transform the findings into educational resources by collecting as much information as possible about the devices' behaviour. Such resources are intended to provide a basis for virtual training environments in which learners can perform exercises based on these artefacts to explore the hardware security domain, examine exploitation techniques, analyse vulnerabilities and discover defensive techniques — all without the need for physical hardware. This will lower barriers and make hands-on hardware security training more accessible.

The evaluation revealed several vulnerabilities, such as poor or complete lack of authentication in serial consoles, which could allow full system control upon hardware connection. Similarly, firmwares were found to be at risk due to unprotected flash memories and bootloaders lacking secure boot, which could enable tampering and supply-chain attacks. Companion app communications were sometimes unencrypted — exposing certain sensitive data such as video streams in RTP — or lacked certificate validation, leaving them susceptible to man-in-the-middle attacks.

# Acknowledgements

I would like to express my deepest gratitude to everyone who supported me throughout this journey.

I would like to thank my supervisors, Samuele Yves Cerini and Nicolò Maunero, for giving me the opportunity to work on this thesis and collaborate with the ARTIC SERICS project at CINI. This experience has taught me a lot and allowed me to explore areas that are not easy to find and that I have long been interested in.

I would also like to thank my parents, my sister, and all my grandparents. Your constant support and encouragement have always motivated me to do my best in my studies and in life. Thank you for your love, your sacrifices, and for instilling in me the values that guide me every day.

Thank you to all my friends for all the beautiful memories we have shared and will share. I love you all.

Thank you to my girlfriend, who has always been there for me. You have always believed in me, even when I have doubted myself. Love you. Even if sometimes I'm difficult, thank you for putting up with me.

Thank you to my best friend. You are like a brother to me, sharing the same values, and I know I can always find you by my side. Thank you for all the great moment we've shared and will share.

Forza Palermo Sempre.

# Contents

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| <b>List of Tables</b>                                                   | 7  |

| <b>List of Figures</b>                                                  | 8  |

| <b>1 Introduction</b>                                                   | 9  |

| <b>2 Background</b>                                                     | 11 |

| 2.1 Foundations of Hardware Security . . . . .                          | 11 |

| 2.1.1 The Role of Hardware in Cybersecurity . . . . .                   | 11 |

| 2.1.2 Hardware Security Threats and Adversary Motivations . . . . .     | 13 |

| 2.1.3 Technical Aspects of Hardware Compromise . . . . .                | 14 |

| 2.2 Embedded Systems Fundamentals . . . . .                             | 15 |

| 2.2.1 What is an Embedded System . . . . .                              | 16 |

| 2.2.2 Commercial Embedded Systems and Common Components . . . . .       | 16 |

| 2.2.3 Different Types of Non-Volatile Storage . . . . .                 | 16 |

| 2.2.4 MTD Partitions and Common Filesystems . . . . .                   | 17 |

| 2.2.5 Common CPU Architectures and Memory Models . . . . .              | 19 |

| 2.2.6 U-Boot: Practical Overview and Interaction . . . . .              | 19 |

| 2.2.7 Real-Time Operating Systems (RTOS) vs Linux-Based Systems . .     | 20 |

| 2.3 Hardware and Software Tools for Embedded Systems Analysis . . . . . | 21 |

| 2.3.1 Hardware Instrumentation . . . . .                                | 22 |

| 2.3.2 Software Toolchain . . . . .                                      | 23 |

| 2.3.3 Analysis Methodology and Procedural Phases . . . . .              | 24 |

| <b>3 State of the Art</b>                                               | 27 |

| 3.1 National Research Projects Enabling the Work . . . . .              | 27 |

| 3.2 Hardware Security Training Landscape . . . . .                      | 27 |

| 3.2.1 Professional Conferences and Training . . . . .                   | 28 |

| 3.2.2 Overview of Hardware Security Competitions and CTFs . . . . .     | 29 |

| 3.2.3 Identified Gaps in the Field . . . . .                            | 31 |

| 3.3 Exploitability Factors in Low-Cost IoT Devices . . . . .            | 32 |

| 3.3.1 Exposed Debug Interfaces . . . . .                                | 32 |

| 3.3.2 Accessible Non-Volatile Storage and Hard-coded Secrets . . . . .  | 33 |

| 3.3.3 Lack of Hardware Root of Trust and Secure Boot . . . . .          | 33 |

| 3.3.4 Firmware, Network and Update Vulnerabilities . . . . .            | 33 |

|          |                                                                 |    |

|----------|-----------------------------------------------------------------|----|

| 3.3.5    | Physical Accessibility and Side-Channel Exposure                | 34 |

| <b>4</b> | <b>Contributions</b>                                            | 35 |

| 4.1      | Motivations for Reproducible Hardware Security Training         | 35 |

| 4.2      | Investigation and Documentation of Hardware Security Weaknesses | 35 |

| 4.3      | Generation and Curation of Artifacts for Realistic CTFs         | 36 |

| 4.4      | Proposed Hardware CTF Framework                                 | 37 |

| <b>5</b> | <b>Experimental Results</b>                                     | 41 |

| 5.1      | TP-Link WR841N Router Analysis                                  | 41 |

| 5.1.1    | UART Pin Identification and Connection                          | 41 |

| 5.1.2    | Bootlog and Gained System Informations                          | 43 |

| 5.1.3    | Flash Dump and Root Password Extraction                         | 45 |

| 5.1.4    | Interacting with U-Boot                                         | 46 |

| 5.1.5    | Linux Shell Access and Filesystem Exploration                   | 47 |

| 5.1.6    | Modifying Wi-Fi and Router Passwords                            | 48 |

| 5.1.7    | Boot Process and Initialization Scripts                         | 49 |

| 5.1.8    | Executable Analysis (usr/bin/httpd)                             | 50 |

| 5.1.9    | CVE-2023-33538 Vulnerability Test                               | 50 |

| 5.1.10   | Impact and Recovery Strategy                                    | 51 |

| 5.1.11   | Memory Access and Recovery Trials in U-Boot                     | 51 |

| 5.1.12   | External Flash Programming and Recovery                         | 54 |

| 5.1.13   | Network and Storage Behavior                                    | 55 |

| 5.1.14   | Service Analysis                                                | 57 |

| 5.1.15   | Supply-chain Attack via Backdoor Insertion                      | 60 |

| 5.2      | Ezviz C6N IoT Camera Analysis                                   | 64 |

| 5.2.1    | Hardware and Interface Discovery                                | 64 |

| 5.2.2    | Boot Process and Environment                                    | 66 |

| 5.2.3    | Onboarding and Network Scanning                                 | 68 |

| 5.2.4    | U-Boot Commands and Flash Dump                                  | 71 |

| 5.2.5    | Flash Partition Analysis                                        | 72 |

| 5.2.6    | Binary and Ghidra                                               | 75 |

| 5.2.7    | Boot and Execution Flow                                         | 76 |

| 5.2.8    | LAN Live View Authentication and Cryptographic Exchange         | 78 |

| 5.2.9    | RTSP Stream Analysis and Plaintext Video Delivery               | 81 |

| 5.2.10   | Application Architecture and Native Components                  | 82 |

| 5.2.11   | Cloud Communications and SSL Pinning                            | 84 |

| 5.3      | Mi Router 4C                                                    | 86 |

| 5.3.1    | Storage and Hardware Identification                             | 86 |

| 5.3.2    | UART and Boot Log                                               | 87 |

| 5.3.3    | Network Service Enumeration                                     | 88 |

| 5.3.4    | Flash Dump and Analysis                                         | 88 |

| 5.3.5    | Enabling UART                                                   | 91 |

| 5.3.6    | UART Echo-Back Timing                                           | 92 |

| 5.3.7    | Possible Weaknesses and Runtime Analysis                        | 93 |

|                                      |     |

|--------------------------------------|-----|

| <b>6 Conclusions</b>                 | 95  |

| 6.1 Summary of Findings . . . . .    | 95  |

| 6.2 Future Work . . . . .            | 96  |

| <b>A Full TP-Link Router Bootlog</b> | 97  |

| <b>B Full EZVIZ minisys Bootlog</b>  | 105 |

| <b>C Full Mi Router Bootlog</b>      | 109 |

| <b>Bibliography</b>                  | 121 |

# List of Tables

|                                                                                        |    |

|----------------------------------------------------------------------------------------|----|

| 3.1 Approximate costs for hardware security trainings (excludes travel/hardware kits). | 28 |

|----------------------------------------------------------------------------------------|----|

# List of Figures

|     |                                                                                                                                                                                                                                         |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Hardware Security, Hardware-based Security and Hardware Trust relationship [26] . . . . .                                                                                                                                               | 12 |

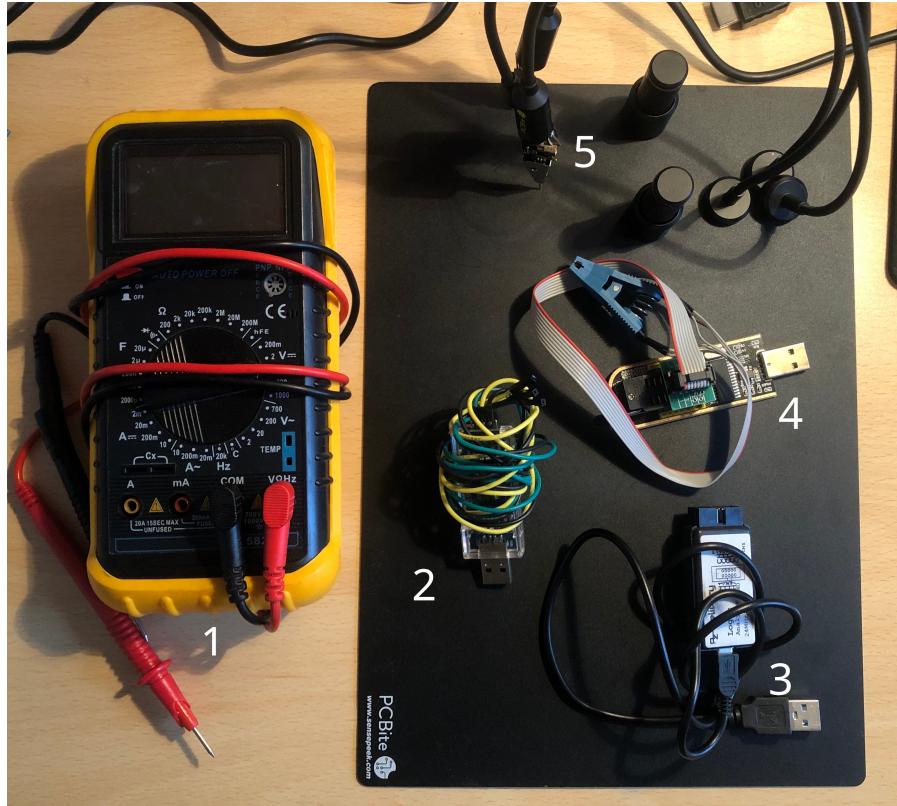

| 2.2 | Typical hardware hacking tools . . . . .                                                                                                                                                                                                | 22 |

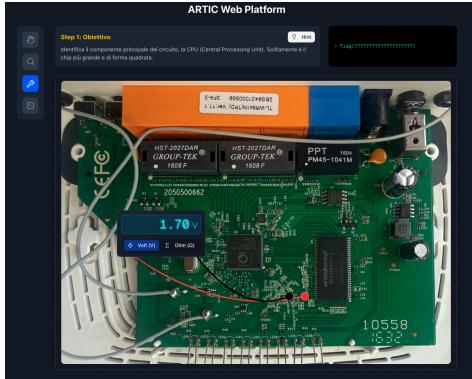

| 4.1 | <b>Virtual Electrical Measurement:</b> Users simulate using a multimeter to acquire annotated voltage and continuity readings on the PCB, crucial for pin identification. . . . .                                                       | 39 |

| 4.2 | <b>Interactive Serial Access:</b> Once pins are identified, a virtual terminal console opens, replaying our complete bootlogs and responding to <i>bootloader</i> or <i>shell</i> commands based on recorded behavioral models. . . . . | 39 |

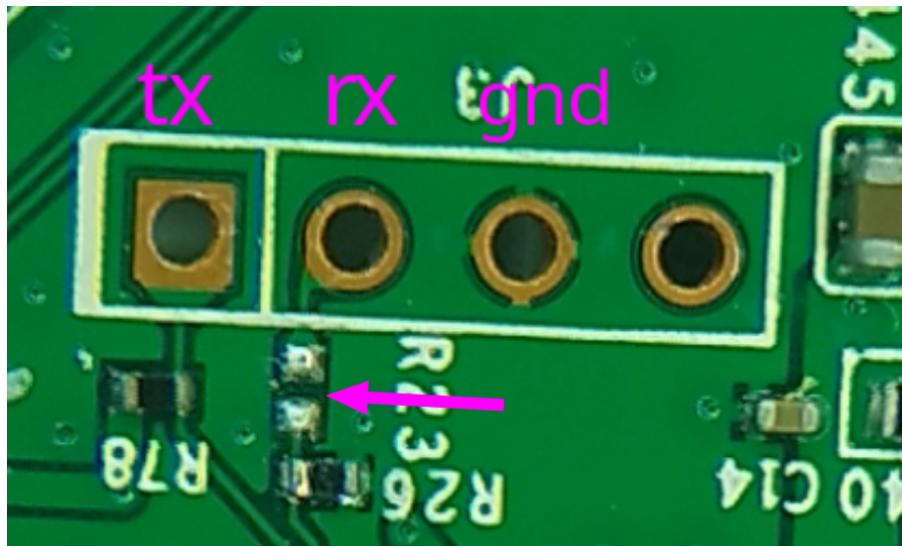

| 5.1 | TP-Link WR841N UART RX electrical connection gap . . . . .                                                                                                                                                                              | 42 |

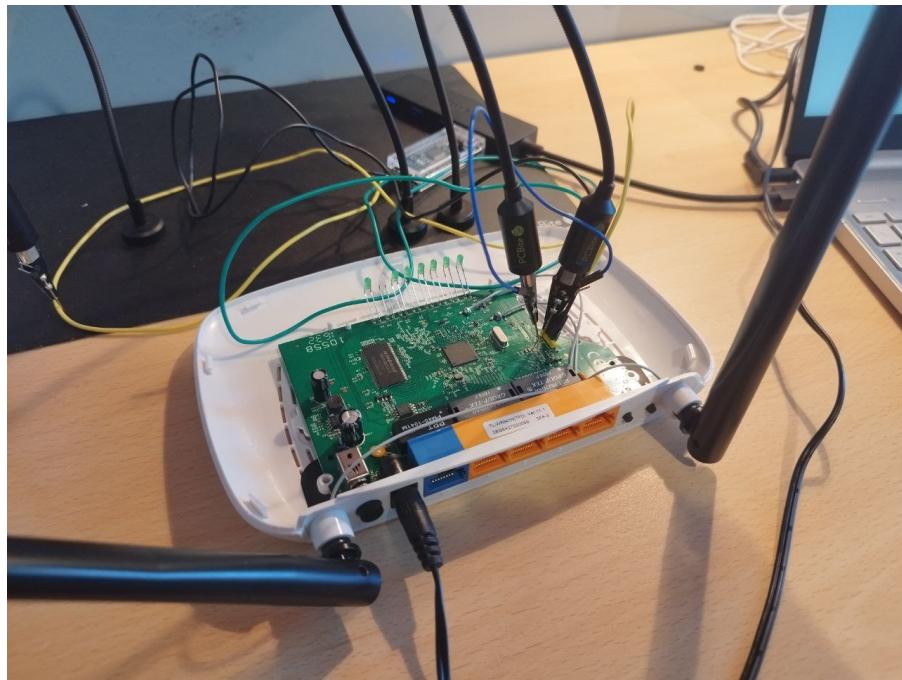

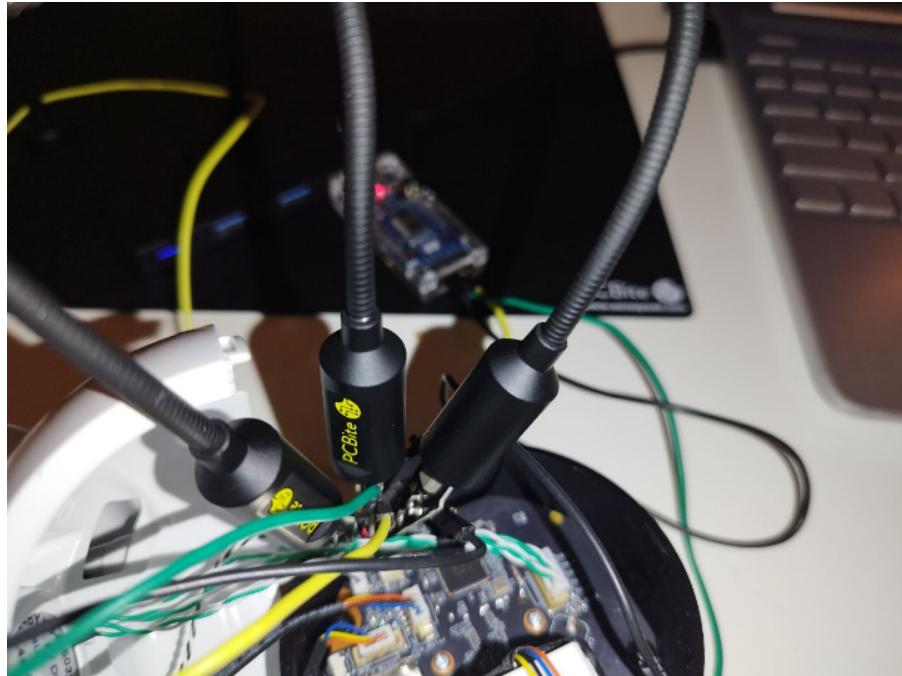

| 5.2 | TP-Link WR841N with UART connection aided by PCBite . . . . .                                                                                                                                                                           | 43 |

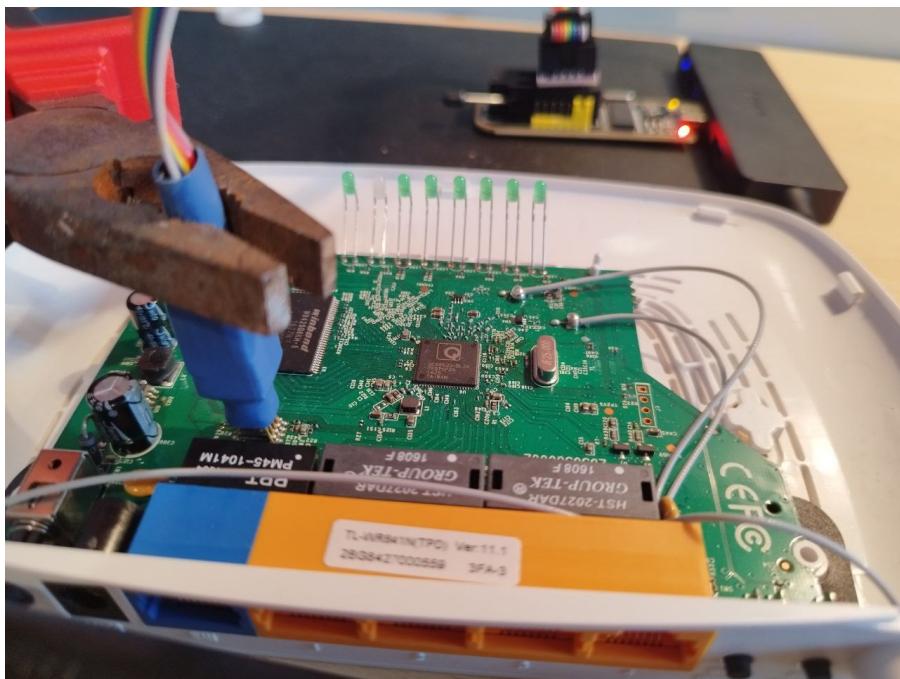

| 5.3 | TP-Link WR841N flash dump using CH341A programmer and SOP8/SOIC8 test clip . . . . .                                                                                                                                                    | 45 |

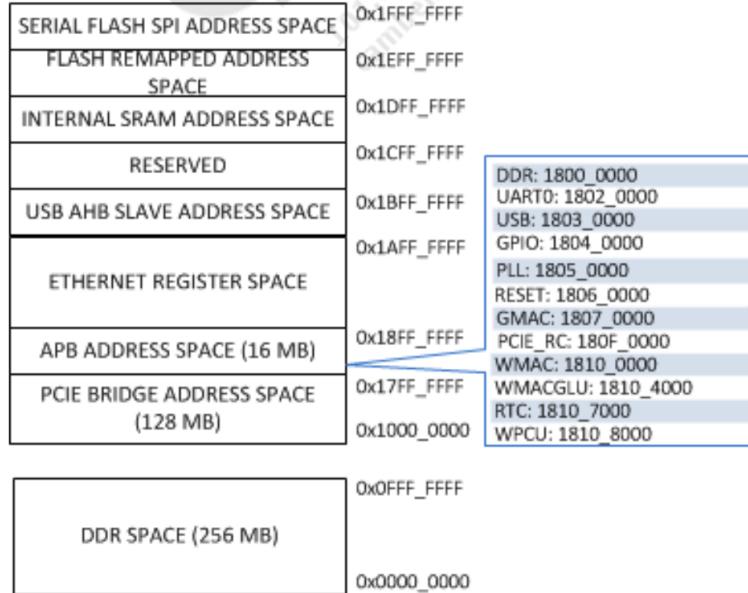

| 5.4 | QCA Physical Address Map [4] . . . . .                                                                                                                                                                                                  | 52 |

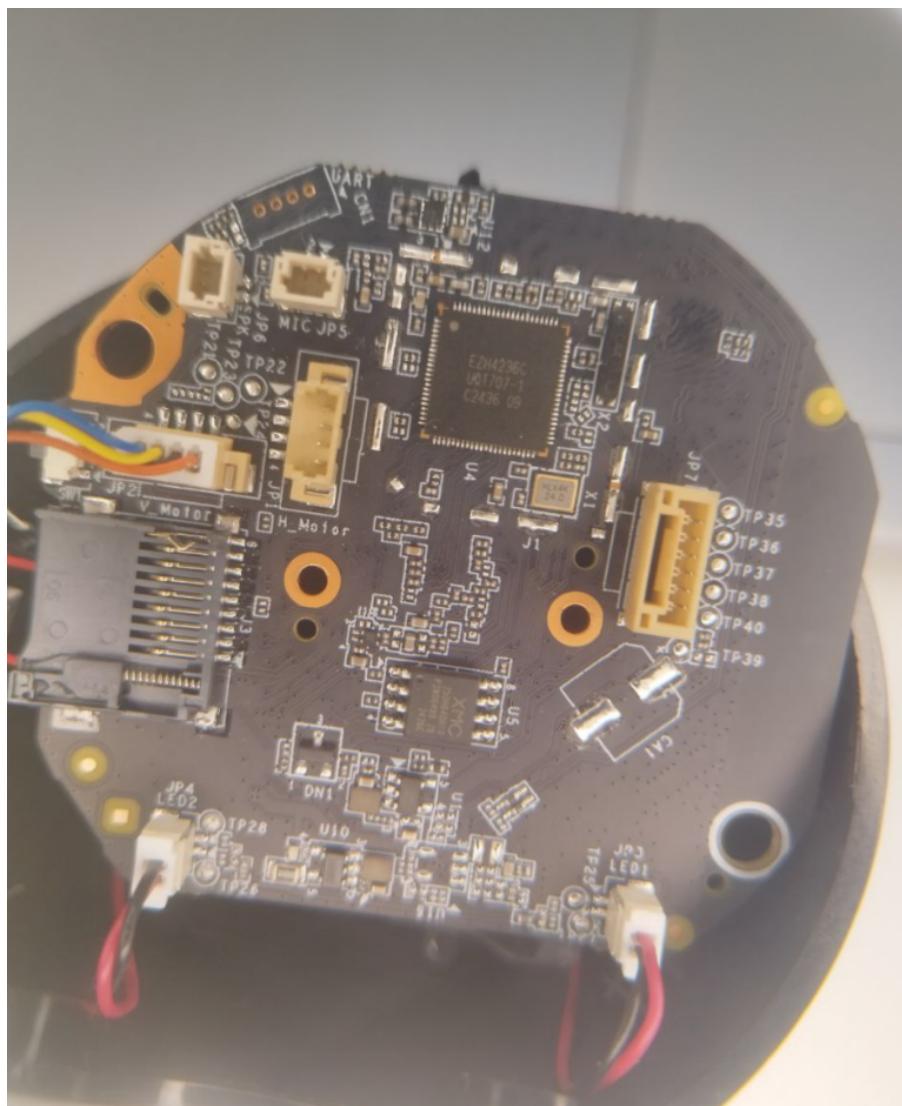

| 5.5 | EZVIZ C6N PCB . . . . .                                                                                                                                                                                                                 | 65 |

| 5.6 | EZVIZ C6N with UART connection aided by PCBite . . . . .                                                                                                                                                                                | 66 |

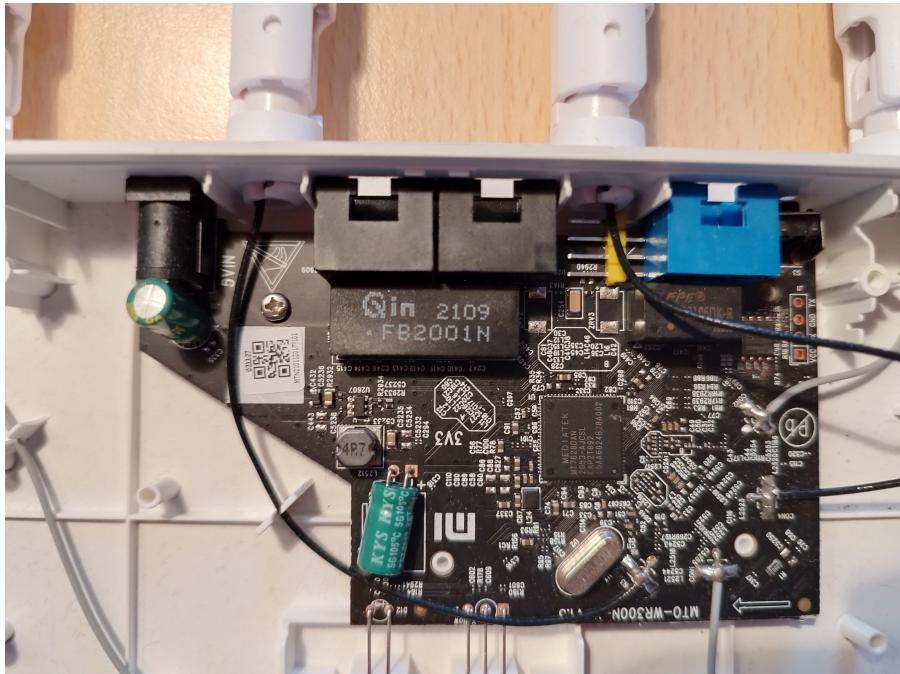

| 5.7 | Mi Router 4C PCB . . . . .                                                                                                                                                                                                              | 86 |

# Chapter 1

## Introduction

In the contemporary era, technological devices and systems are ubiquitous, thereby rendering security a pivotal concern. The Internet of Things (IoT), however, is based on a different principle, where manufacturers prioritise cost reduction and essential functionality over the implementation of robust security measures. The market provides consumer-grade embedded devices, such as home routers and surveillance cameras, which are equipped with only basic security features. The market is confronted with a dilemma where the necessity to render devices economical is in direct opposition to the necessity to ensure their security. This has resulted in a multitude of products that are inherently vulnerable to security breaches. These weaknesses extend far beyond individual devices. For instance, a flaw in a single webcam model can allow attackers to access live video streams from an entire family of similar devices, while insecure routers can provide entry points into entire home or office networks. In addition, attackers have demonstrated their ability to conduct supply-chain attacks by distributing compromised units within the market.

The pervasive issue of insecurity is made worse by a significant educational problem, as students do not have enough accessible resources to pursue studies in the domain of hardware security. The software domain offers accessible online courses and virtual Capture the Flag (CTF) competitions; however, hardware security remains a niche field with high barriers to entry. The financial burden of professional training courses, in conjunction with the necessity for specialised equipment and laboratory facilities, poses significant obstacles for beginners trying to take their first steps in the field. Consequently, many individuals in the field possess only a rudimentary understanding of hardware security, which may impede their capacity to identify and address vulnerabilities in hardware systems.

This thesis addresses two key issues: firstly, the prevalence of insecure consumer IoT devices, and secondly, the educational gap in hardware security. The present study evaluates the security of low-cost embedded devices by testing their hardware interfaces (e.g. UART debug ports and SPI NOR flash), firmware structures, network protocols, and companion applications. The research documents discovered vulnerabilities alongside the tools, methodologies, and procedures used to identify them, producing a comprehensive set of artifacts — including firmware images extracted from SPI flash, filesystem dumps (e.g. SquashFS and JFFS2), network captures, UART bootlogs and exploitation techniques — that reflect real world security conditions.

The educational dimension of this work is central to its purpose. The findings and artefacts gathered during these assessments are intended to support the development of virtual hardware security training platforms, contributing to a larger initiative supported by the ARTIC Project, under the Spoke 4 umbrella of Fondazione SERICS. The overarching vision is to create web-based environments that simulate realistic hardware scenarios, utilising visual representations of printed circuit boards (PCBs) and interactive tool interfaces. This approach enables learners to engage with device analysis and exploitation techniques, such as identifying and accessing UART debug interfaces or analysing firmware with tools like `binwalk` or `Ghidra`, without the necessity for physical hardware. Consequently, it democratises access to this specialised knowledge, thereby bridging the gap between theoretical knowledge and practical application.

The security assessments conducted in this research show that a significant proportion of low-cost IoT devices are found to be deficient in fundamental security controls. The experimental results indicate critical system vulnerabilities, including debug interface authentication deficiency, the absence of secure boot and firmware anti-tampering mechanisms, outdated software, unencrypted network communication (e.g. RTSP plaintext video streaming). The analysis demonstrates how attackers utilise these vulnerabilities to gain unauthorised hardware access, intercept sensitive communications, and insert backdoors into the system. The thesis documents actual threats to create educational materials. These reduce entry barriers for hardware security learning by addressing both insecure device design problems and workforce training deficiencies.

The remainder of the document is organized as follows. In Chapter 2, *Background*, established the foundational concepts of hardware security, embedded systems, and the threat models relevant to IoT devices, providing the reader with the necessary context to understand the subsequent analyses. Chapter 3, *State of The Art*, reviews the current landscape of security in IoT and embedded systems, as well as existing hardware security training platforms, contextualizing this work within the literature and identifying gaps in current approaches. Chapter 4, *Contributions*, presents the primary contributions of this thesis, outlining the motivation for the vulnerability assessment of IoT devices and explaining how this research forms the basis for developing accessible hardware security training environments. Chapter 5, *Experimental Results*, details the outcomes obtained from the security assessments of multiple consumer IoT devices, documenting the methodologies employed, the vulnerabilities discovered, and the progressive insights gained throughout the analysis. Finally, Chapter 6, *Conclusion*, summarizes the findings, discusses their implications, and outlines directions for future work.

# Chapter 2

## Background

The present chapter establishes the fundamental knowledge required to comprehend the vulnerabilities inherent in embedded and Internet-of-Things devices, as well as the methodologies employed to exploit them. The research examines attacker objectives and the ways in which hardware-based security breaches influence the overall security of systems, outlining the motivations behind such attacks and the threat types they generate. This chapter does not proceed by demonstrating specific attack methods. Rather, it establishes a conceptual framework for readers to analyse forthcoming analyses of chapters. This is achieved by means of an explanation of hardware security concepts and threat models, and embedded system characteristics. The section also provides a summary of standard tools and methods used for hardware and firmware analysis, which help detect and fix security weaknesses.

### 2.1 Foundations of Hardware Security

Hardware is the foundational element that provides support for all upper-level security systems, encompassing software protections, cryptographic protocols and access controls. The security of this system level is pivotal in determining the protection of all systems that come after it, as attackers can potential flaws and vulnerabilities at this stage to access and circumvent software security measures. The repercussions of such actions extend beyond the confines of individual devices, thereby enabling large-scale exploitation.

#### 2.1.1 The Role of Hardware in Cybersecurity

A rigorous taxonomy is imperative to delineate the multifaceted roles of hardware in cybersecurity. Paolo Prinetto asserts [26] that three distinct yet interconnected concepts must be accorded equal consideration: *Hardware Security*, *Hardware-based Security*, and *Hardware Trust*. The three components serve distinct purposes and protect against different threats during various stages of system development. It is these factors that establish the basis for reliable embedded systems.

Figure 2.1. Hardware Security, Hardware-based Security and Hardware Trust relationship [26]

*Hardware Security* encompasses all aspects pertaining to hardware components, such as vulnerabilities with the associated attacks and protective measures, irrespective of the implementation technology, design tools, or abstraction level utilised. Hardware Security is responsible for the provision of protective solutions that have been developed with the purpose of preventing vulnerabilities and attacks during every stage of the process of developing hardware. The protection is initiated through security-by-design during the specification and production phases, and is sustained through runtime mitigation and field patching for deployed devices. The discipline is designed to safeguard the hardware substrate, thereby facilitating the effective operation of higher-layer protective measures. This constitutes the last line of defense against potential attacks.

Considering the *Hardware-based Security* concept, its function is to utilise hardware components to protect system elements, encompassing software and firmware, in addition to data and communication channels, from attacks that leverage non-hardware system vulnerabilities. The paradigm establishes a chain of trust that originates in silicon and persists through the system stack. This is achieved by employing a series of security measures, including secure boot, measured boot, remote attestation, sealed storage, and isolated execution environments. Key implementations include Trusted Platform Module (TPM) and Trusted Execution Environment (TEE) standards, Memory Protection Units (MPUs), hardware ciphers, true random number generators, proprietary solutions (ARM

*TrustZone, Intel SGX, Apple Secure Enclave*), open platforms (*SEcube™, USB Armory*), and repurposed safety features in microcontrollers. The root of trust's integrity serves as the fundamental basis, since a compromised hardware substrate can result in the failure of all connected protections depending on it. It is evident that Hardware Security constitutes a fundamental enabler for Hardware-based Security.

*Hardware Trust* protects hardware components by verifying their authenticity and origin, maintaining their expected behaviour, and defending against physical tampering, malware attacks and physical interference. The presence of counterfeit products in the marketplace may include items that have been recycled, modified, overproduced, or defective; in addition, they may contain cloned parts, which can lead to accelerated deterioration and unaddressed security vulnerabilities. The process of detection is contingent upon the utilisation of electrical testing, X-ray imaging, and provenance tracking methodologies. Conversely, the prevention of such devices necessitates the implementation of unique device identities, such as the ones enabled by the use of Physically Unclonable Functions (PUFs) and secure provisioning mechanisms. The establishment of trust is predicated on the presence of cryptographic attestation, which serves as a foundational element in the development of trust-based systems.

The three concepts exist in a dependent relationship because *Hardware Security* functions as the foundation for *Hardware-based Security*, which then supports *Hardware Trust* through its defense of authenticity mechanisms.

The research proposed in this thesis focuses on embedded and IoT *Hardware Security*, studying the effects of the lack of basic *Hardware-based Security* primitives such as TPM, TEE, and secure boot, and *Hardware Trust* mechanisms including PUF-based keys and anti-recycling measures, with the final goal of establishing threat models and defense strategies.

### 2.1.2 Hardware Security Threats and Adversary Motivations

Adversaries targeting hardware systems pursue objectives that shape their choice of targets, resource allocation, and operational persistence. These include financial gain, strategic or competitive advantage, ideological aims, political influence, and military objectives. Financial incentives are particularly prevalent, facilitated by dark web marketplaces where vulnerabilities are traded. Such motivations drive theft of intellectual property (IP), counterfeiting, unauthorized cloning, overproduction in untrusted foundries, ransomware, botnet formation for Distributed Denial of Service (DDoS) campaigns (e.g., the Mirai botnet [2]), and illicit use of computational resources for cryptocurrency mining.

State-sponsored actors, including nation-states and intelligence agencies, operate with large, long-term resources, specialized personnel, and diplomatic cover. Such operations often combine key extraction, covert backdoor installation, and persistence measures for espionage and potential future sabotage against critical infrastructure. Insider threats pose similar risks, introducing hardware Trojans (HTs), leaking source code, or sabotaging tape-outs through disgruntled employees. Corporate espionage employs device acquisition, reverse engineering, and talent poaching, while security researchers and hacktivists may responsibly disclose zero-day vulnerabilities that can be misappropriated for malicious purposes.

Hardware security threats span the entire device lifecycle, from specification and design

to fabrication, deployment, maintenance, and decommissioning. The complexity of global supply chains exposes systems to untrusted actors, including IP vendors, offshore foundries, subcontracted test houses, and secondary resale markets. Malicious modifications during design, fabrication, assembly, or post-market resale — often manifesting as hardware Trojans — may remain dormant until triggered. Broader systemic risks arise from supply-chain compromises, such as tampered firmware images, breaches of update servers, or the introduction of counterfeit units through uncontrolled manufacturing. Counterfeit or recycled components bypass quality controls, introducing defects that compromise safety and reliability.

The impact of these attacks is severe. Unauthorized firmware extraction and functional cloning allow replication of device designs and identification of latent vulnerabilities. Such devices can void warranties, enable malware propagation, bypass digital-rights protections (DRM), and threaten IoT networks. Active manipulation of hardware or embedded software can degrade performance, induce denial-of-service, or inflict physical damage to critical infrastructure, as exemplified by Stuxnet [11]. Trust breaches at a single point can propagate across product families sharing components, firmware, or update infrastructure, as with Spectre [19] and Meltdown [22].

Mitigation requires a layered, lifecycle-oriented approach. Supply-chain diversification, split manufacturing, logic locking, and proactive market surveillance enhance long-term resilience [30]. Secure hardware elements and device-unique identities (e.g., on-die identifiers) reinforce provenance, while firmware protections—including secure boot, encrypted storage, update verification, and rollback prevention—ensure confidentiality and integrity [9].

### 2.1.3 Technical Aspects of Hardware Compromise

Hardware subversion employs diverse techniques for privilege escalation, data extraction, or control hijacking, exploiting physical access or implementation weaknesses.

#### Extracting Secrets and Firmware

Confidential assets, comprising cryptographic keys, authentication tokens, and proprietary algorithms, can be obtained to facilitate IP theft, industrial espionage, or the crafting of further attacks. Firmware extraction enables reverse engineering and the identification of vulnerabilities.

Acquisition can be performed using three main categories of methods:

- *Non-invasive* techniques: In-system Flash dumping via serial interfaces (UART) or interception of Over-the-Air (OTA) updates.

- *Invasive* approaches: Decapsulation, Ball Grid Array (BGA) package desoldering, and chip-off extraction.

- *Semi-invasive* attacks: Dumping Flash storage by connecting an external programmer in-situ (e.g., using a CH341A-based board), or dumping RAM via cold-boot attacks (which exploit residual data in RAM immediately after power-off to recover sensitive information like encryption keys [13]).

*Side-channel analysis* is a powerful non-invasive technique that infers secrets by measuring physical signals—power consumption, electromagnetic (EM) emissions, and timing variations—during cryptographic operations. Techniques include Simple Power Analysis (SPA) for visual pattern detection, Differential Power Analysis (DPA) [20] for statistical key extraction, and Correlation Power Analysis (CPA) [8] which utilizes leakage models. EM analysis similarly observes emissions to reveal internal activity without interfering with execution.

To ensure confidentiality, firmware must be encrypted and obfuscated to hinder analysis. Modern System-on-Chip (SoC) designs utilize tamper-resistant components, such as firmware TPMs (fTPMs) and Physical Unclonable Functions (PUFs), to safeguard keys; physical probing of a PUF alters its inherent characteristics, destroying the secret it protects. Against side-channel attacks, effective countermeasures include constant-time execution, blinding, masking, and tamper-resistant packaging or EM shielding [6]. While earlier standards like FIPS 140-2 missed these vectors, FIPS 140-3 introduces Test Vector Leakage Assessment (TVLA) to evaluate information leakage [32, p. 422].

### Gaining Control and Tampering the System

Attackers may attempt to modify device behaviour by inserting Trojans, bypassing DRM, or altering main functionalities to obtain full control.

Exposed debug interfaces (UART/JTAG/SWD) and unprotected bootloaders allow attackers to halt cores, inspect memory/registers, or modify boot variables to execute unauthorised kernel code. It is also possible to reflash storage using external programmers. Vulnerabilities are amplified by insecure processes such as unsigned OTA procedures or untrusted software distribution channels.

Active *fault-injection* techniques — including voltage or clock glitching, electromagnetic pulses, laser/optical strikes, and Rowhammer [18] — can momentarily disturb a device’s computations without physical modification. Precisely timed faults (e.g., using tools like ChipWhisperer) may induce skipped checks or corrupted intermediate values, enabling attackers to bypass secure-boot flows or undermine access controls. Such attacks have been demonstrated even against hardware wallets like the *Trezor* family [32, p. 223].

Operational safeguards against these integrity attacks include guarded debug-interface access and continuous monitoring. This involves anomaly detection, canary-based integrity checks, and dedicated sensors for fault or glitch detection [27]. Finally, a robust root-of-trust implementation with immutable measurements ensures only authorized code is executed, protecting against persistent modification.

## 2.2 Embedded Systems Fundamentals

Understanding embedded architecture is essential for threat contextualization and analysis. While commercial devices rely on standardised, reusable components that accelerate development, they also create shared vulnerability surfaces.

### 2.2.1 What is an Embedded System

Embedded Systems are specialized computing platforms integrated within larger mechanical/electronic systems, designed for dedicated functions under constraints of power, size, cost, and real-time responsiveness. Unlike general-purpose systems, embedded platforms often feature fixed firmware, minimal peripherals, and application-specific instruction sets. They range from simple 8-bit microcontrollers in appliances to 64-bit SoCs in smart TVs, often operating headless for their entire lifecycle.

### 2.2.2 Commercial Embedded Systems and Common Components

Many modern embedded devices are built around System-on-Chip (SoC) designs, which integrate multiple functional blocks or intellectual-property (IP) cores on a single die. Depending on the product, a SoC may include analog front-ends (for example, ADCs or RF front-ends), digital processors (CPUs, GPUs, or DSPs), cryptographic accelerators, on-chip memory (RAM, ROM, and flash), and power-management circuitry.

Embedded products frequently make extensive use of commercial off-the-shelf (COTS) components and modules to shorten time-to-market and reduce development cost. Standard debug and test interfaces (for example, UART, JTAG/SWD) simplify validation and development but can also expose attack surfaces if left accessible in production units. Although these interfaces can be permanently disabled — for instance by blowing eFuses that lock the chip’s debug interfaces — this is not always practical, as manufacturers and end users may occasionally require legitimate troubleshooting or recovery access, which discourages complete removal.

Ecosystem-level reuse is common: widely used bootloaders (e.g., U-Boot), operating systems (Linux and various RTOSes), vendor SDKs (ESP-IDF, STM32Cube, etc.), and popular development modules and boards (ESP32 modules, Raspberry Pi Compute Modules, Arduino boards) combine to produce ready-to-deploy embedded platforms. While this reuse accelerates development, it can also propagate vulnerabilities across products.

A number of insecure practices are repeatedly observed across the industry — for example, unchanged default credentials, disabled or absent secure-boot configurations, insufficiently authenticated update mechanisms, and embedded or hardcoded cryptographic material — all of which increase the risk of compromise if not addressed.

### 2.2.3 Different Types of Non-Volatile Storage

- **SPI NOR:** small-capacity Flash memory (usually 1–64 MB, occasionally up to 256 MB). It can execute code directly (*XIP*, execute in place: the CPU can run code directly from Flash without copying it to RAM, but this has typically slower execution than running on RAM). Access is simple via low-pin-count serial interfaces. It lacks an internal storage controller (no FTL); the host manages data directly. Such type of memory is extremely common and one of the most used type of Flash memory in embedded systems.

- **Raw NAND:** high density low cost Flash memory (hundreds of MB to GB). Organized in pages/blocks (not byte-addressable). It’s connected via a parallel bus to the external controller: the host must implement the driver/FTL for ECC (Error Correction Code),

wear-levelling, and Bad Block Management (BBM). Used for large data storage in legacy systems and high-end industrial routers.

- **SPI NAND:** A hybrid solution offering the high density of NAND with the simpler serial interface of SPI (reduced pin count). Unlike legacy Raw NAND, modern SPI NANDs often include on-die ECC, offloading the bit-correction burden from the host, although the host must still manage logical-to-physical mapping and bad blocks. Ideal for high-capacity storage in IoT devices, where SPI NOR is too small-sized and eMMC too costly.

- **Managed NAND (eMMC/UFS):** NAND Flash with a sophisticated integrated controller that hides the complexity of NAND physics (ECC, wear-leveling, BBM) behind a standard block device interface. UFS (high-speed serial interface, standard in modern smartphones) is faster and more advanced than eMMC (parallel interface, common in legacy or low-cost mobile/embedded). BGA packaging usually requires desoldering or socket programming for chip-level access.

- **EEPROM:** byte-addressable and small data size (typically less than 1MB) memory optimized for high endurance. Used for small configuration data (calibration, MAC addresses, serial numbers). Found in microcontrollers and SoCs.

- **OTP / eFuses:** One-Time Programmable memory implemented via physical fuses (burning silicon links). Critical for the *Hardware Root-of-Trust*: they store the Public Key Hash (ROTPK) for Secure Boot validation, JTAG disable bits, and unique device encryption seeds. Once blown, the state is immutable at the hardware level.

The interface type and packaging affect how easy it is to access the memory. SPI NOR devices are typically offered in SOIC-8/SOP-8 packages, which makes them easy to probe in-situ via test clips (with an external programmer, e.g. CH341A) [32, p.89]. Parallel NAND, SPI NAND, and BGA-packaged eMMC/UFS usually require desoldering, socket programming, or specialized programming interfaces.

## 2.2.4 MTD Partitions and Common Filesystems

### Memory Technology Device (MTD)

In Linux-based embedded systems, access to raw Flash memory is provided through the MTD subsystem, which offers a unified interface for Flash devices that differs from standard block or character devices. A key characteristic of Flash memory is that an entire block must be erased before it can be rewritten. While modern block devices (SSDs, USB drives, eMMC, etc.) use the same NAND Flash technology, their built-in Flash Translation Layer (FTL) hides this requirement, allowing them to behave like ordinary block devices. The MTD subsystem, in contrast, exposes the erase-before-write behavior directly to software. Flash memory also exhibits random-access capabilities and wear-out characteristics, unlike simple character streams (e.g. mouse or keyboard). Data cannot be overwritten at the byte level; instead, entire blocks (typically 64-256 KiB) must be erased to all 1s before any bit can be set to 0.

Flash memory is generally organised into various partitions, which encompass the bootloader, environment variables, kernel, root filesystem, and user or configuration data. There are two methods that can be employed in order to verify the layout of partitions. The initial method involves inspecting the `/proc/mtd` directory, or alternatively, the examination of the boot log messages. The second approach involves conducting a direct analysis of the firmware blob, with the objective of manually identifying the various areas or partitions, as well as any system file, which collectively define the partition layout.

## Common Filesystems

- **JFFS2 (Journaling Flash File System v2)** A log-structured filesystem for raw Flash (NOR/NAND) operating directly on MTD, provides support for compression through `zlib`, `lzo`, and `lzma`, and enables features such as hard links, wear-leveling, and garbage collection. It's characterised by the concurrent storage of metadata and data in sequential nodes, which are located within eraseblocks that bear version numbers. The process of garbage collection has the function of reclaiming obsolete nodes and evenly spreading erase cycles across all eraseblocks to prevent some blocks from wearing out faster than others. It skips any blocks that the MTD layer has identified as unreliable/bad, so it never allocates data there; it also performs scan of all nodes during the mounting process, with the objective of restoring the entire filesystem to its original state. It functions in the absence of power interruptions; however, it requires a greater duration to mount large partitions.

**Use in embedded systems:** It functions as a writable filesystem. It has been engineered to provide native support for the management of wear and bad blocks, as well as power loss resilience, without the necessity for a block-emulation layer. This development is expected to result in enhanced reliability for raw NAND/NOR.

- **SquashFS** A read-only compressed file system that has been optimised for use on memory-constrained embedded systems. It supports a variety of compression algorithms, including `zlib`, `lz4`, `lzo`, `xz`, `lzma2`, and `zstd`, and block sizes ranging from 4 KiB to 1 MiB. It has been developed to store both data and metadata in a unified manner, whilst providing support for a range of file formats, including fragments, directory indexes, sparse files, and NFS export. It has been engineered to prevent runtime wear by operating in read-only mode. However, in order to apply updates, users are required to create a new image with the `mksquashfs` program.

**Use in embedded systems:** It is used as static system partitions, encompassing the kernel, libraries and firmware, due to the fact that it delivers 2-3x compression results and expeditious mount times, whilst exhibiting zero runtime wear (since read-only).

## Extraction Tools

Tools like `jefferson` (JFFS2) and `sasquatch` (SquashFS) allow users to extract and rebuild these file systems by working with raw Flash images.

### 2.2.5 Common CPU Architectures and Memory Models

Modern systems rely on a few dominant CPU architectures, balancing performance, power efficiency, and security through mechanisms like memory protection and virtual addressing.

- **ARM Family:** Dominant architecture in embedded and IoT, ranging from microcontrollers to high-performance SoCs. Key features include memory access control and TrustZone security (a TEE).

- *Cortex-M Series:* Low-power microcontrollers (e.g., STM32, nRF52/53). Simplified memory model: no MMU, optional MPU (Memory Protection Unit) with few regions, direct memory access. Ideal for lightweight IoT.

- *Cortex-A Series:* Powerful SoCs (e.g., Linux-based gateways, routers). Features MMUs providing virtual memory support and page tables. Memory types include Normal (can be cached, reorderable) and Device (uncached, non-reorderable).

- **MIPS:** Found in legacy or entry-level embedded systems (e.g., routers). Often uses a fixed virtual-to-physical segmentation for cores without a full MMU. Segments include KUSEG (user virtual, TLB-translated), KSEG0 (kernel cached, direct-mapped), and KSEG1 (kernel uncached, direct-mapped).

- **Other Architectures:** Includes RISC-V (emerging open-source ISA for low-power IoT), Xtensa cores (configurable, popular in ESP32/Wi-Fi/BLE devices), and AVR/PIC (basic automation, e.g., ATmega in Arduino).

ARM cores dominate modern IoT, covering both higher-performance SoCs (Cortex A) and low-power microcontrollers (Cortex M). ESP32/Xtensa remains popular in maker and consumer devices. RISC-V is emerging in low-power and experimental designs, while MIPS and AVR/PIC persist mainly in legacy or cost-sensitive applications.

### 2.2.6 U-Boot: Practical Overview and Interaction

**Overview** U-Boot (Das U-Boot) is a universal open-source bootloader widely used in embedded and IoT devices (routers, webcams). It executes immediately after the SoC Boot ROM loads it from non-volatile storage. U-Boot initializes essential hardware, provides a UART console, manages persistent environment variables, and supports flexible booting (local/network).

**Boot stages and initialization** U-Boot often uses a two-stage process: a minimal *Secondary Program Loader* (SPL) for initial setup (like DRAM initialization), followed by the full U-Boot binary. It enables only required peripherals (UART, Flash, Ethernet). The boot sequence is defined by the configurable `bootcmd`. Control is passed to the OS kernel entry point once loaded.

**Interactive shell and commands** If interrupted, U-Boot enters an interactive shell. This allows memory inspection/modification (`md`, `mw`), Flash access (`mmc`, `sf`, `nand`), network operations (`tftpboot`), and manual booting (`bootm`, `bootz`). Persistent variables (`bootcmd`, `bootargs`) are managed with `printenv`, `setenv`, and `saveenv`.

**Physical interaction and typical workflows** Interaction requires a USB-TTL adapter connected to the UART pins (typically 3.3V/1.8V, 115200 baud). Pressing any key within the `bootdelay` window grants shell access. Attackers can examine or modify Flash/memory (e.g., `sf read/write`) or alter boot parameters, such as setting `init=/bin/sh` in `bootargs` to gain a root shell, assuming the kernel honors the command line.

**Security considerations** Most consumer devices ship with an unlocked UART console and lack secure boot enforcement, making full system compromise trivial with physical access. An attacker can easily modify U-Boot or the kernel. Security requires SoC-level authentication of signed bootloader binaries as the trust anchor, followed by verified boot for the kernel, and the disabling or restriction of debug interfaces (UART, JTAG). If the SoC ROM does not authenticate U-Boot, downstream protections fail. U-Boot is the first user-accessible stage after the SoC ROM, representing a critical attack surface.

### 2.2.7 Real-Time Operating Systems (RTOS) vs Linux-Based Systems

The IoT landscape can be divided into **Linux-based systems** and **real-time operating systems (RTOS)**, reflecting a trade-off between rich functionality and deterministic behavior. Hardware characteristics drive this choice: gateways and edge devices typically favor Linux, while sensor and actuator nodes rely on lightweight RTOS.

#### Key RTOS Characteristics

RTOS ensure predictable, low-latency operation on constrained microcontrollers (typically <1 MB RAM, often without an MMU). Representative examples include:

- **RT-Thread**: Modular, small-footprint kernel (base kernel ~3 KB, can grow with optional modules) with preemptive scheduling, priority inheritance, and thread-safe IPC. Supports ARM and RISC-V. Optional GUI and filesystem middleware are available. Suitable for wearables, IoT hubs, and safety-critical applications requiring deterministic response.

- **eCos**: Highly configurable kernel (10-100 KB depending on configuration) with HAL abstraction, lightweight networking, and rapid boot-time. Optimized for deeply embedded, low-power systems and legacy industrial controllers.

- **FreeRTOS**: Minimalistic kernel (6-10 KB for basic configurations) with preemptive priority scheduling, software timers, and lightweight IPC. Supports multiple architectures (ARM Cortex-M, RISC-V, ESP32) and integrates with various middleware. Suitable for simple sensors and moderately complex embedded nodes.

RTOS commonly employ static memory allocation and tickless idle modes. Context-switch latency can be very low (often tens of microseconds or below on small MCUs), but exact values depend on the hardware and kernel configuration.

### Linux-Based IoT Systems

Linux-based environments encompass both general-purpose distributions (e.g., OpenWrt, Ubuntu Core) and custom images generated via build systems (e.g., Buildroot). These systems deliver rich networking stacks, complex filesystems, and extensive driver ecosystems. They rely on dynamic memory, multitasking, and POSIX compliance. Standard Linux scheduling introduces nondeterministic latency. The PREEMPT\_RT patch can improve real-time behavior, typically reducing soft real-time response to hundreds of microseconds by making Linux more "interruptible" so high priority tasks can preempt almost any kernel operation, though it has more complexity compared to a native RTOS.

### Design Trade-Offs

- **Determinism:** RTOS provide predictable latency; Linux offers best-effort scheduling.

- **Footprint:** RTOS operate with tens of KB; Linux requires tens of MB.

- **Functionality:** Linux enables rich connectivity, user-space processes protections, better and easier support development; RTOS favor reliability, static allocation, and simplified certification.

### Hybrid Architectures

A common approach couples Linux on a high-performance core for connectivity and user interfaces with an RTOS on a co-processor or low-power core for real-time tasks, ensuring deterministic control while leveraging Linux scalability.

### Application Guidance

- **RTOS:** Preferred for battery-powered sensors, control loops, or safety-critical applications requiring low-latency, predictable behavior.

- **Linux:** Suitable for gateways, edge devices, or nodes needing complex connectivity, rapid prototyping, and extensive software libraries.

## 2.3 Hardware and Software Tools for Embedded Systems Analysis

Instrumental support for embedded systems analysis comprises a set of hardware interfaces and software utilities selected to enable physical access, artifact acquisition, and behavioural examination. The following text adopts an academic register and employs passive constructions; methods and tools are described in narrative form with concrete examples of commonly used instruments, commands and parameters to avoid excessive generality.

### 2.3.1 Hardware Instrumentation

Measurement and interfacing instruments are required to perform reliable analysis. In figure 2.2 there are, ordered by number in the picture, the following tools: (1) multimeter, (2) UART-to-TTL adapter, (3) logic analyzer, (4) CH341A external programmer with a SOIC8/SOP8 test clip, (5) PCBite probes and holders.

Figure 2.2. Typical hardware hacking tools

- **Multimeters and oscilloscopes:** Precision digital multimeters and oscilloscopes are used for measuring voltage, current, and timing, and for locating debug interfaces.

- **Logic analyzers:** Logic analyzers are used to capture and decode serial buses (e.g., SPI, UART, etc.). Both commercial devices, such as the Saleae Logic series, and lower-cost alternatives are commonly employed for this purpose.

- **UART access and JTAG/SWD discovery:** USB-to-UART (USB-to-TTL) adapters serve as the main connection between device consoles and debug output systems because they link the host PC with the target UART pins through TX->RX, RX->TX, and GND connections and typically operate at 115200 baud. Instead, for low-level access via JTAG/SWD, specialized tools like BlueTag [3] and JTAGulator are typically used to identify the relevant pins, and enabling interaction with the interface for debugging and firmware extraction.

- **External Flash programmers - in-situ & chip-off:** External Flash programmers, such as the CH341A, are tools used to access memory chips either in-situ with test clips or off the board (chip-off). In-situ dumps are convenient but less reliable, often requiring multiple reads, hash verification, and careful repositioning of the clip to avoid corrupted data. Chip-off access, with the Flash removed, offers more stable and reliable results.

- **PCBite-style probes:** PCBite pogo pins and holders provide stable, non-destructive electrical contact with test points on a live board. These spring-loaded pogo pins use an internal spring mechanism that allows the probe tip to move back slightly when pressed against a surface. This ensures consistent pressure and a reliable temporary connection during debugging or measurement, without the need for soldering.

- **Fault injection and side-channel tools:** Fault injection platforms and side-channel analysis tools are applied when active manipulation is necessary. For instance, ChipWhisperer is widely used for voltage and clock glitching and for power-analysis (SCA) experiments. These setups demand precise synchronization between instruments to ensure repeatable and meaningful results.

### 2.3.2 Software Toolchain

A modular software toolchain complements the hardware suite and supports extraction, static inspection, dynamic instrumentation and network analysis.

- **Firmware acquisition:** utilities are used to read and write Flash memories; `flashrom` is commonly invoked with a command such as `flashrom -p ch341a_spi -r dump.bin` to perform SPI/NOR dumps via a CH341A programmer, and verification is achieved by subsequent hashing (e.g., `sha256sum dump.bin`).

- **Binary unpacking and filesystem discovery:** tools (for example, `binwalk -Me dump.bin`, `allyourbase` [1] or `7z x`) enable identification and extraction of embedded archives and compressed filesystems (LZMA, SquashFS, U-Boot environment). Extraction steps typically include `binwalk -dd='.*' dump.bin` to carve known signatures, and `unsquashfs` to expand SquashFS images.

- **Entropy analysis:** Entropy measurements are used to detect encrypted or compressed regions. A Shannon entropy above approximately 7.5 bits per byte often indicates compression or encryption. However, high entropy does not always imply encryption, as some types of normal data, such as video, can naturally exhibit high entropy without being encrypted.

- **Disassembly and decompilation:** frameworks such as Ghidra are employed to reconstruct program structure, annotate functions and inspect control/data flow; recommended project steps include architecture selection, selection of binary base address, auto-analysis pass, importing symbols where available and applying function signatures from common libraries. Complementary tools such as radare2 or IDA Pro (where licensed) are used for cross-validation.

- **Dynamic instrumentation:** frameworks (for example, Frida) allow runtime hooking and API interception on mobile devices: this is particularly useful when analyzing companion mobile apps that control IoT devices. An example invocation is `frida-trace -f ./binary -i "open*"` to monitor file-open calls.

- **Network capture and analysis:** utilities (Wireshark, PCAPDroid for Android captures) are applied to examine protocol implementations, communication vulnerabilities, and OTA mechanisms; passive captures and active enumeration using `nmap -sV -p- <target>` are used to characterise exposed interfaces.

- **Password recovery and cryptanalysis:** specialized utilities (for example, `hashcat` with appropriate hash-mode flags and tuned GPU parameters) are applied when credential material or hashed secrets are encountered.

- **Certificate and key inspection:** artifacts are inspected using `openssl` commands such as `openssl x509 -in cert.der -inform der -text -noout` and `openssl asn1parse` for finer-grained decoding.

### 2.3.3 Analysis Methodology and Procedural Phases

Embedded systems analysis is organised into reproducible phases that progress from low-impact reconnaissance to active testing.

**Preliminary reconnaissance (open-source & regulatory)** Before any physical handling or device acquisition, an initial reconnaissance phase collects technical and regulatory data to form hypotheses about the hardware design, interfaces and required tooling. Publicly available information is surveyed — vendor datasheets, FCC filings (FCC: US regulatory filings, which often contain PCB photos and diagrams), vendor support threads, community forums and public vulnerability databases (NVD/CVE - NVD: NIST database providing CVE details with CVSS scores, which quantify the severity and impact of each vulnerability). Datasheets, FCC filings and PCB images are primarily used to infer hardware characteristics (likely Flash package types, e.g. SOP8/SOIC8 footprint versus BGA), identify probable UART pins, JTAG headers and test points, and assess whether existing equipment (SOIC8/SOP8 test clips, CH341A, UART adapters, BlueTag, etc.) will be adequate or if additional tools must be procured. Vendor threads, community reports and vulnerability entries (CVE/NVD) are consulted to collect past reports, known weaknesses, default credentials and remediation history; this information feeds the threat model and helps prioritise which interfaces and firmware components deserve early attention.

**On-board non-invasive reconnaissance** Initial on-board assessment is conducted with minimal physical intrusion guided by the preliminary reconnaissance hypotheses. Typical UART identification starts by locating four candidate pins that are likely to be part of the serial interface. Using a multimeter, GND is identified by continuity to ground (0V), VCC by a stable voltage (typically 3.3-5V). TX is recognized by voltage fluctuations between 0V and VCC immediately after power-on, caused by bootloader or firmware output such as initialization messages, while the remaining pin is RX, which stays stable at 0V or VCC. Pinout hypotheses are validated by temporarily connecting a USB-UART adapter

and checking for bootloader messages at standard baud rates (try 115200, then 57600 and 9600). The presence of bootloaders such as U-Boot is inferred from recognizable prompts. On-board JTAG/SWD are enumerated using passive discovery tools such as Logic Analyzer, BlueTag, JTAGulator. Flash device packages are visually inspected and cross-referenced with manufacturer markings to determine chip storage model name and characteristics before any direct read attempt.

**Firmware acquisition** Firmware acquisition proceeds based on the available hardware interfaces and the trade-off between invasiveness and reliability.

Non-destructive in-situ reads of SPI/NOR devices using a test clip (e.g. SOIC8/SOP8) and a programmer (e.g. CH341A) are preferred when feasible, but they are intrinsically less reliable than chip-off due to clip contact issues and to circuit interactions on the board (parts of the surrounding circuitry may power or drive the Flash pins when the clip is attached, introducing bus contention or corrupting reads). A recommended canonical sequence for in-situ extraction is: attach the test clip to the storage device, run `flashrom -p ch341a_spi -r dump.bin` and compute `sha256sum dump.bin`. Repeat the read several times, disconnecting/reconnecting the clip, to verify that the hash is reproducible and the dump is consistent.

When higher reliability is required, chip-off — physically removing the flash memory for external reading — is the preferred method, though it is destructive and demands proper handling skills and suitable equipment.

If direct hardware access is unavailable, bootloader-mediated techniques are attempted. Examples include using TFTP via a serial boot protocol to transfer data off-board, or exploiting U-Boot commands to read memory and emit its contents over the serial console (bootloader prints a hex ASCII memory dump to UART — the output can be reconstructed into a binary with a simple conversion script). Network-based acquisition is also used: OTA update packages are captured by intercepting traffic (creating a MITM if needed, e.g. via bettercap) to retrieve update images for offline analysis.

**Static analysis** Static inspection begins with file carving and entropy scanning (`binwalk -Me dump.bin`); extracted components are processed with format-specific tools (`unsquashfs` for SquashFS, `7z x` for LZMA, `dd` with offsets for raw partitions). Strings are extracted with `strings -t x dump.bin` and correlated with disassembly to locate configuration tables, hard-coded credentials and certificate blobs. Certificate parsing and key discovery are performed using `openssl` and simple ASN.1 inspection; private-key leakage is checked by searching common key encodings and file headers. Disassembly projects are constructed in Ghidra with the target architecture specified (ARM/ARM64/MIPS/XTENSA etc.); before importing, determine the binary's load/base address (for example with `allyourbase`) and set that base in Ghidra so addresses and cross-references line up correctly. Automatic analysis is followed by manual function renaming and cross-referencing against public library signatures (for example, using Ghidra Function ID database). Finally, potential vulnerabilities — such as missing input validation — are investigated either by inspecting the decompiled code directly or by examining the installed binaries and their versions for known security issues.

**Dynamic analysis** In this phase, devices are observed at runtime. Testing begins with passive packet captures (pcap) analyzed in Wireshark to verify authentication, transport security and update delivery, then moves to active scans (e.g. nmap -sV -p-), simulated server/client interactions and MITM testing. Mobile companion apps are dynamically instrumented with Frida to remove SSL pinning when needed, perform function-level tracing and intercept APIs, validating static-analysis hypotheses and mapping the mobile app <-> device (device under test) network protocol. Device emulation (e.g., QEMU) can replace physical hardware to enable GDB-attached debugging, easier fuzzing, snapshots and instrumentation, but it requires nontrivial setup and can miss or misrepresent some hardware (e.g., RF) behaviors. JTAG/SWD and serial interfaces such as UART provide low-level firmware access for interactive shells and memory/process inspection. Oscilloscopes and logic analyzers capture bus activity, timing and side-channel signals; in particular, ChipWhisperer can be employed for side-channel analysis and fault injection (glitching): EM/power analysis provokes and measures failures to assess robustness, while protocol fuzzing and on-device firmware modification reproduce vulnerabilities and recover runtime secrets.

**Automation techniques** Machine learning and pattern-matching methods can assist in anomaly detection and vulnerability discovery: they are useful for identifying recurring patterns in network traffic, large logs, binaries, or decompiled code. However, all automated findings must be validated through manual analysis to minimize false positives and ensure reliability.

# Chapter 3

## State of the Art

### 3.1 National Research Projects Enabling the Work

National and institutional research projects contribute to the infrastructure and funding environment that enables research into security training and cyber ranges. One of the main and recent projects relevant to the Italian context is coordinated by the SERICS Foundation (SEcurity and RIghts in the CyberSpace), whose projects include ARTIC (Affordable, Reusable and Truly Interoperable Cyber ranges), the context within which this thesis work was born.

**SERICS (Security and Rights in the CyberSpace)** SERICS is a PNRR-funded extended partnership dedicated to enhancing cybersecurity, data protection, and digital rights research. Coordinated by academic institutions, it aims to foster academic-industry collaboration and strengthen advanced educational programs. The foundation supports the development of new cyber ranges and training facilities, establishing the necessary infrastructure for scalable security education.

**ARTIC (Affordable, Reusable and Truly Interoperable Cyber ranges)** ARTIC is a specific project under the Spoke 4 umbrella of Fondazione SERICS, focused on engineering cost-effective, scalable, and interoperable cyber ranges. By leveraging containerization, microservice architectures, and digital twin integration, ARTIC aims to reduce deployment costs and facilitate cross-domain scenarios. These objectives are directly relevant to this work, which applies ARTIC's principles of scalability and reuse to the domain of embedded and IoT security training.

### 3.2 Hardware Security Training Landscape

The domain of hardware security training occupies a narrower niche compared with the broader ecosystem of cybersecurity education (web, network, reverse engineering, and cryptography). Educational offerings for embedded device security range from formal academic initiatives, professional short courses, vendor-led challenges, and conference

workshops. Furthermore, there is a divergence in the technical intricacy and accessibility of these systems. The subsections below summarise the predominant activity categories.

### 3.2.1 Professional Conferences and Training

The primary conferences and events comprise specialised short courses and workshops, with a focus on embedded exploitation and side-channel analysis, fault injection, and secure hardware design. The programs incur considerable expense, with registration fees and workshop expenses commencing at hundreds of euros and sometimes reaching thousands. These programs are often targeted at experienced practitioners, and in many cases are funded by employers rather than by individual participants.

Hardware security **training** is delivered at a number of different events and venues, including Black Hat USA 2025 (August, Las Vegas) with courses on embedded security delivered by experts; DEF CON 33 (August 2025, Las Vegas) via its Hardware Hacking Village, featuring workshops on IoT; Hardwear.io USA 2025 (May, Santa Clara) and NL 2025 (November, Amsterdam), emphasizing practical exploitation. Dedicated providers like S4X offer standalone 2-day courses on applied hardware attacks, while UKRISE provides free HW security training roadshows for UK PhD and post-doc students. Other notable options include SANS Institute's IoT-focused penetration testing series.

To illustrate the cost spectrum, the following table summarizes training offerings with some examples in Table 3.1:

| Provider/Event | Course Examples                                                                          | Duration    | Cost                                        |

|----------------|------------------------------------------------------------------------------------------|-------------|---------------------------------------------|

| Black Hat USA  | From JTAG, UART, SPI to SDR, BLE, Firmware, TPM Sniffing, and Drone Systems              | 2 to 4 days | €3810 to €5200 [7]                          |

| DEF CON        | Offensive IoT Exploitation / SDR101 / RFID & EPACS Hacking / Medical Device PT & Defense | 2 to 4 days | €2165 to €2770 [10]                         |

| Hardwear.io NL | Automotive, RF/Baseband, Chip-Level RE, Side-Channels, Faults, FPGAs, TEE & Secure Boot  | 3 days      | €2810 [15]                                  |

| S4X            | Applied Hardware Attacks: Embedded/IoT Systems                                           | 2 days      | €3075 + tax [28]                            |

| SANS Institute | IoT and Wireless Penetration Testing                                                     | 3 to 6 days | €4935 to €8230 [29]                         |

| UKRISE         | HW Security Training Roadshow                                                            | 2 days      | Free, but reserved for UK PhD/post-doc [31] |

Table 3.1. Approximate costs for hardware security trainings (excludes travel/hardware kits).

### 3.2.2 Overview of Hardware Security Competitions and CTFs

This section presents a non-exhaustive list of hardware CTF platforms. The selected examples are examined based on their format, accessibility limitations, and relevance to the visual simulation goals of this thesis.

- **eCTF** MITRE’s eCTF is a free, embedded competition structured in two distinct phases. In the first phase, teams are tasked with the creation of secure systems in accordance with specified requirements. In the second phase, these systems are then subjected to an attempt at breach by teams representing opposing factions. The competition is conducted entirely online, facilitated by MITRE, which provides reference implementations, comprehensive documentation, and a designated set of development boards per team. Additionally, hardware emulators or remote servers are made available as required. Past challenges are archived in the MITRE Cyber Academy repositories, supporting study and pedagogical reuse.

- **RHme** The RHme series commenced as Riscure products prior to the introduction of versions by Keysight. These versions focused on Arduino-class boards that address fundamental hardware problems through side-channel analysis, fault injection, and the exploitation of microcontrollers. These comprised the 2015 to 2017 editions, and they furnished participants with binaries, source artefacts and community write-ups through public repositories. However, 2017 edition also relied on hardware and it was shipped to selected participants. All supporting materials, including code, binaries and documentation, remain available online for continued access following the conclusion of the event.

- **HHV DEF CON** The DEF CON Hardware Hacking Village (HHV) runs hardware challenges on a rolling basis across multiple years. Challenge sets were created both for DEF CON’s live events, requiring on-site participation, and for remote engagement through posted recordings and downloadable data. Some editions — specifically DC28, DC29, Hackfest 2020, and DC32 — were designed to be accessible remotely, providing participants with firmware, logic analyzer captures, and circuit information to work on from home. Other editions, particularly the more recent live events like DC33, were primarily in-person: participation realistically required a DEF CON badge (around \$560) and hardware was available in limited quantities (e.g., eight devices secured to village tables). Organizers made shared tools, such as logic analyzers, available, but participants were generally expected to bring their own probes or analysers. After each event, HHV publishes challenge files and write-ups, and multiple past editions are archived on GitHub, preserving a historical record and enabling study or replication; however, the practical ability to replicate a challenge remotely depends on the edition, as some were designed specifically for in-person interaction.

- **Microcorruption** Microcorruption is an online platform that offers embedded firmware reverse-engineering exercises (notably for the MSP430 architecture). The platform exposes disassembly, live memory/views of registers, and an interactive debugger-like console. Its narrow architectural focus introduces limitations: the MSP430 is dated, far removed from the microcontrollers commonly used in contemporary IoT devices, and the challenges therefore do not reflect modern embedded systems.

It does not provide a photographic PCB view nor simulated physical instruments, but remains easily accessible and reproducible.

- **CSAW** The CSAW ESC (Embedded Security Challenge) is a recurring university-run competition with a long history of remote qualification rounds and on-site finals. The public has access to a variety of past challenge sets, virtual machines and challenge sources, which enable remote replication and analysis. The most advanced tasks in some editions are dependent on hardware platforms (e.g. ChipWhisperer Nano and Arduino), but the qualification stages typically run through remote execution.

- **Google CTF and public archives** Google’s Capture The Flag provides challenge archives and a public GitHub repository that contains many past challenge archives and infrastructure elements. Although not hardware-centric in general, the public availability of challenge materials makes it a relevant resource for CTF pedagogy and for reuse patterns across categories.

- **Hardwear.io and Hardware CTF** Hardwear.io, together with Hardware CTFs curated by teams such as Quarkslab and Ledger (the company behind the widely used Ledger hardware cryptocurrency wallets), represents a conference-level hardware competition ecosystem. These events are in-person and hardware-focused, offering benches equipped with tools for PCB reversing, microsoldering, RF analysis, and side-channel tasks. Organizers provide shared (across participants) equipment and guidance, but participation requires attendance and payment for the conference (typically \$200–\$850), with optional paid training tracks costing around \$3,250. Participants receive certificates of attendance for the conference and certificates of completion for the training programs. While some preparatory webinars and recorded presentations are publicly available, the challenges themselves remain largely inaccessible online, and published details are primarily limited to basic summaries. This setup emphasizes hands-on experience with physical hardware rather than remote or reproducible exercises.

- **Hack The Box** Platform providers that historically focused on software CTFs have introduced hardware categories; Hack The Box includes a **Hardware** challenge category and provides write-ups and tooling guidance for selected tasks. Some challenges are delivered via uploaded signal captures, SAL files, or firmware images; others require local hardware to be reproduced. However, the platform’s primary orientation remains virtual machines and software CTFs rather than a full visual hardware lab.

- **OWASP IoTGoat** The developers of OWASP IoTGoat created a firmware distribution system which contains OpenWrt-based vulnerable code for educational purposes. It is possible for users to operate this system on QEMU for virtual machine or container deployment, thus creating a platform upon which to study IoT problems and forming a practical dataset for lab exercises that focus on firmware vulnerabilities and emulation. Projects like IoTGoat facilitate reproducible, offline training and can be used as building blocks for challenge environments.

- **Hackropole** Hackropole hosts archived challenge sets from national competitions (France Cybersecurity Challenge) including hardware-tagged tasks. Typical tasks

include radio/IQ decoding, side-channel specimens and binary/firmware artefacts; many of the challenges are distributed as files (signals, traces) rather than as live physical benches. These let participants explore some practical aspects of embedded systems and hardware security, though they do not include instrument-level visual simulations and provide only a limited sense of working with live hardware.

An examination of public archives reveals two enduring characteristics: organizers typically either retain devices on-site or dispatch limited hardware packages to participants. Furthermore, post-event distribution of challenge materials is common, enabling retrospective review and education. However, the analysis of device-based problems heavily relies on face-to-face data collection during live events.

Overall, the materials exhibit three main distribution patterns:

1. *On-site hardware benches and shared devices*, typical of conference villages and Hardware and HHV events, where a limited number of devices are available on shared tables. Participation usually involves travel and accommodation expenses, adding to the overall cost of engaging with the conferences.

2. *Distributed hardware kits*, used in events such as MITRE eCTF or some editions of RHME, where organisers mail boards or minimal toolkits. These allow full remote participation.

3. *File-based archives*, including firmware, logic captures, SAL/IQ files, and write-ups, which enable remote replay and study after the event but lack the immediacy of physical hardware and interactive instruments.

### 3.2.3 Identified Gaps in the Field

A review of public archives, CTF platforms, and professional training offerings reveals several structural and pedagogical gaps in the current hardware security landscape:

1. **Limited browser-based, full-stack simulations.** While platforms like Microcorruption or IoTGoat provide firmware analysis, debugger consoles, or emulated environments, and Hackropole or HHV archives supply traces, binaries, or IQ captures, none replicate the experience of interacting with a real PCB in a visually guided, instrument-driven workflow. Tasks such as multimeter measurements, UART probing, or component identification are rarely simulated in-browser, creating a gap for learners who cannot access physical benches.

2. **High cost and logistical barriers for hands-on learning.** Conferences, professional courses, and live CTF events provide authentic hardware experience but often at significant financial and logistical expense, including conference registration, travel, accommodation, and sometimes hardware kits. The number of available devices is usually limited, further constraining practical participation.

3. **Partial reproducibility of challenge materials.** Post-event archives and repositories (firmware, SAL/IQ files, binaries, or virtual machines) allow retrospective study,