POLITECNICO DI TORINO

Master's Degree in Computer Engineering

Master thesis

**Automotive Ethernet and

100BASE-T1: State of the Art

of Communication Protocols

and Experimental Evaluation

of Time Synchronization using

gPTP**

Candidates:

Fabio Delbosco (S322244)

Referee:

Prof. Stefano Di Carlo

Prof. Alessandro Savino

Academic Year 2024 - 2025

A Laura che ha sempre creduto in me,

alla mia famiglia che mi ha sempre spronato

e spinto a dare il meglio

a chi mi vuole bene.

Fabio

---

# Contents

|          |                                                      |           |

|----------|------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                  | <b>2</b>  |

| 1.0.1    | Safety-Critical Communication . . . . .              | 2         |

| 1.0.2    | Architectural Evolution . . . . .                    | 2         |

| 1.0.3    | Bandwidth Requirements . . . . .                     | 3         |

| <b>2</b> | <b>Ethernet Automotive</b>                           | <b>5</b>  |

| 2.1      | Network Topologies . . . . .                         | 5         |

| 2.2      | BroadR-Reach and IEEE 802.3 . . . . .                | 7         |

| 2.3      | Physical Layer Overview . . . . .                    | 8         |

| 2.3.1    | Physical Coding Sublayer (PCS) . . . . .             | 9         |

| 2.3.2    | Physical Medium Attachment (PMA) . . . . .           | 9         |

| 2.3.3    | Media Independent Interface (MII) . . . . .          | 10        |

| 2.3.4    | Medium Dependent Interface (MDI) . . . . .           | 10        |

| 2.4      | 100BASE-T1 Physical Layer Implementation . . . . .   | 10        |

| 2.4.1    | Full and Half-Duplex Communication . . . . .         | 10        |

| 2.4.2    | PAM3 Signaling and Line Coding . . . . .             | 12        |

| 2.4.3    | Data Scrambling . . . . .                            | 13        |

| 2.4.4    | Node Synchronization . . . . .                       | 15        |

| 2.4.5    | Training Phase . . . . .                             | 16        |

| 2.4.6    | Cable Characteristics & connectors . . . . .         | 17        |

| 2.4.7    | Echo Cancellation . . . . .                          | 19        |

| 2.4.8    | DC Isolation . . . . .                               | 21        |

| 2.4.9    | Fault Tolerances . . . . .                           | 22        |

| 2.4.10   | Basic node Setup Review . . . . .                    | 23        |

| 2.5      | 100BASE-T1 Logical Link Control Layer . . . . .      | 24        |

| 2.5.1    | MII Data Stream and Frame Structure . . . . .        | 25        |

| 2.5.2    | Ethernet Frame Composition . . . . .                 | 25        |

| <b>3</b> | <b>Ethernet Automotive Application Protocols</b>     | <b>35</b> |

| 3.0.1    | DoIP . . . . .                                       | 35        |

| 3.1      | SOME/IP Middleware . . . . .                         | 38        |

| 3.1.1    | Communication Model . . . . .                        | 38        |

| 3.1.2    | SOME/IP Packet Structure . . . . .                   | 39        |

| 3.1.3    | Advantages in Automotive Networks . . . . .          | 39        |

| 3.2      | Time Sensitive Networking (TSN) . . . . .            | 39        |

| 3.2.1    | Key Features of TSN . . . . .                        | 40        |

| 3.2.2    | TSN Stream Model . . . . .                           | 40        |

| 3.2.3    | Frame Format . . . . .                               | 40        |

| 3.3      | Generalized Precision Time Protocol (gPTP) . . . . . | 41        |

| 3.3.1    | Best Master Clock Algorithm (BMCA) . . . . .         | 41        |

| 3.3.2    | PTP Message Types in gPTP . . . . .                  | 42        |

---

|                     |                                                                    |           |

|---------------------|--------------------------------------------------------------------|-----------|

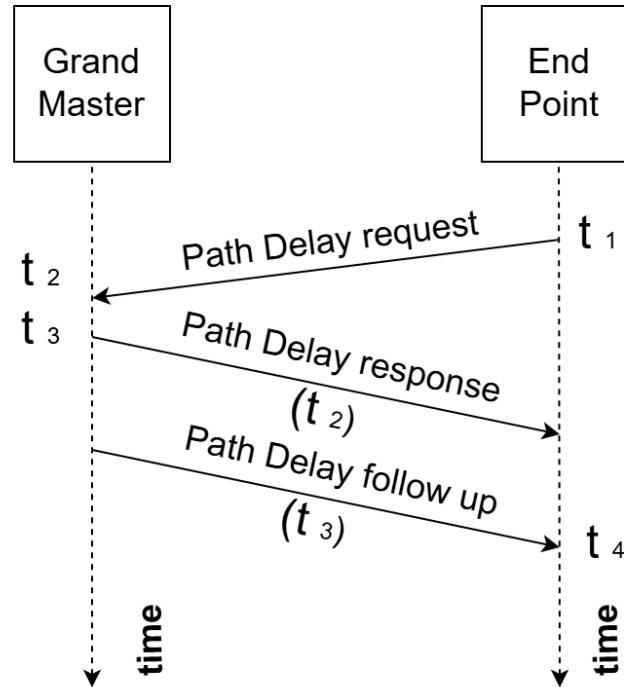

| 3.3.3               | Propagation Delay Measurement (Peer-to-Peer) . . . . .             | 42        |

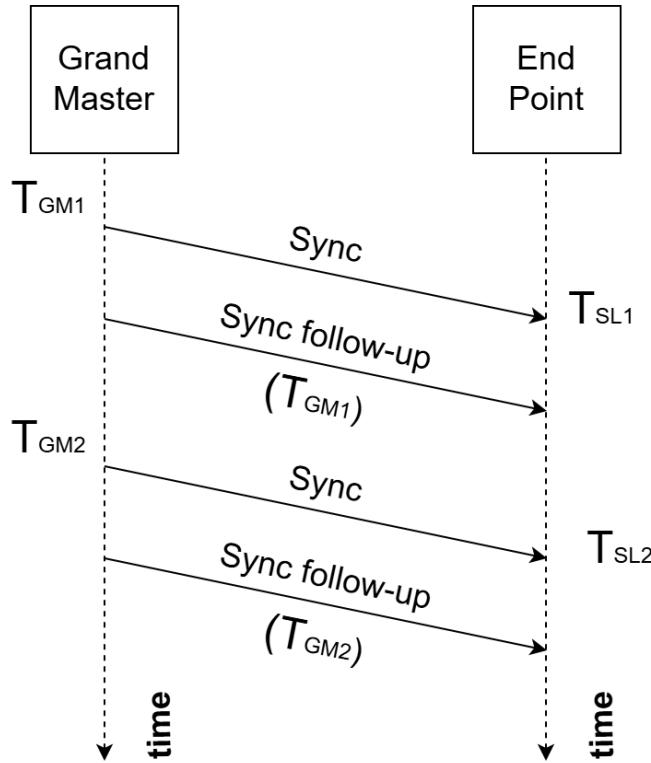

| 3.3.4               | Synchronization and Clock Adjustment . . . . .                     | 43        |

| <b>4</b>            | <b>Experimental Setup and Measurement Infrastructure</b>           | <b>45</b> |

| 4.1                 | Introduction . . . . .                                             | 45        |

| 4.2                 | Automotive Ethernet Support Infrastructure . . . . .               | 45        |

| 4.3                 | Embedded Hardware Platform . . . . .                               | 49        |

| 4.3.1               | Evaluation Boards . . . . .                                        | 49        |

| 4.3.2               | Programming and Debugging Tools . . . . .                          | 51        |

| 4.4                 | Network Architecture and Software Implementation . . . . .         | 51        |

| 4.4.1               | Reference Planes for Timestamping . . . . .                        | 52        |

| 4.5                 | Software Implementation . . . . .                                  | 53        |

| 4.5.1               | Ring Buffers . . . . .                                             | 53        |

| 4.5.2               | Main Loop Architecture . . . . .                                   | 54        |

| 4.5.3               | Polling Frequency and Buffer Dimensioning . . . . .                | 55        |

| 4.5.4               | gPTP Stack Integration . . . . .                                   | 56        |

| 4.5.5               | Switch Configuration and Integration . . . . .                     | 57        |

| <b>5</b>            | <b>Experimental Methodology and Evaluation Framework</b>           | <b>59</b> |

| 5.1                 | Data Acquisition and Logging Architecture . . . . .                | 59        |

| 5.2                 | Clock Offset Analysis . . . . .                                    | 61        |

| 5.2.1               | Offset stability . . . . .                                         | 61        |

| 5.2.2               | Path Delay analysis . . . . .                                      | 63        |

| 5.3                 | Impact of Network Traffic on Synchronization Performance . . . . . | 64        |

| 5.3.1               | Network Load Evaluation . . . . .                                  | 64        |

| 5.3.2               | Test Under Load Without VLAN Prioritization . . . . .              | 65        |

| 5.3.3               | VLAN-based Traffic Isolation under Load . . . . .                  | 67        |

| <b>6</b>            | <b>Conclusions and future work</b>                                 | <b>75</b> |

| Future Work         | . . . . .                                                          | 75        |

| <b>7</b>            | <b>Acknowledgements</b>                                            | <b>77</b> |

| <b>Bibliography</b> | . . . . .                                                          | <b>78</b> |

---

# List of Figures

|      |                                                                                                                                                                                                                                                                           |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

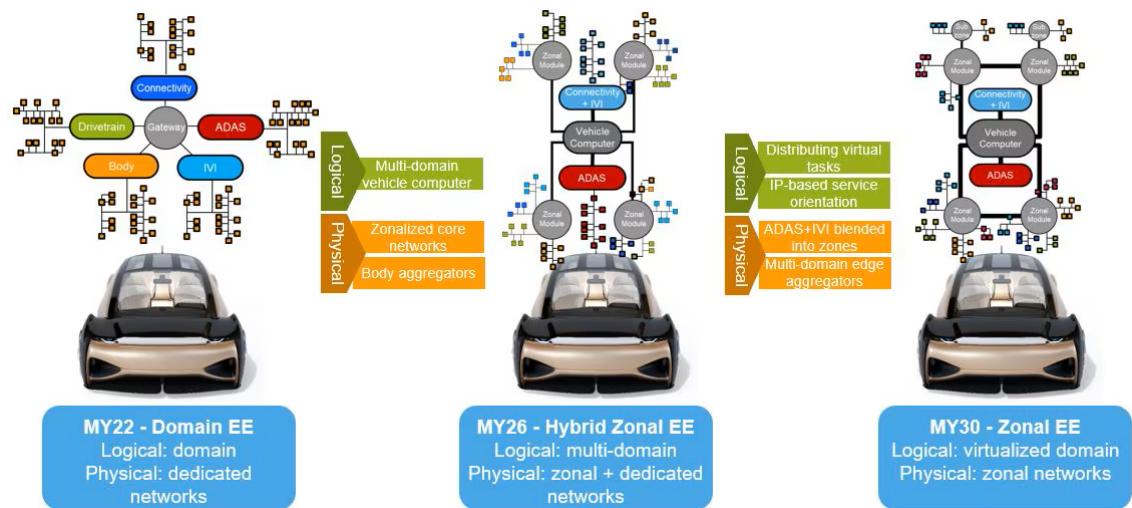

| 1.1  | Different types of automotive architectures now in use [1]. . . . .                                                                                                                                                                                                       | 3  |

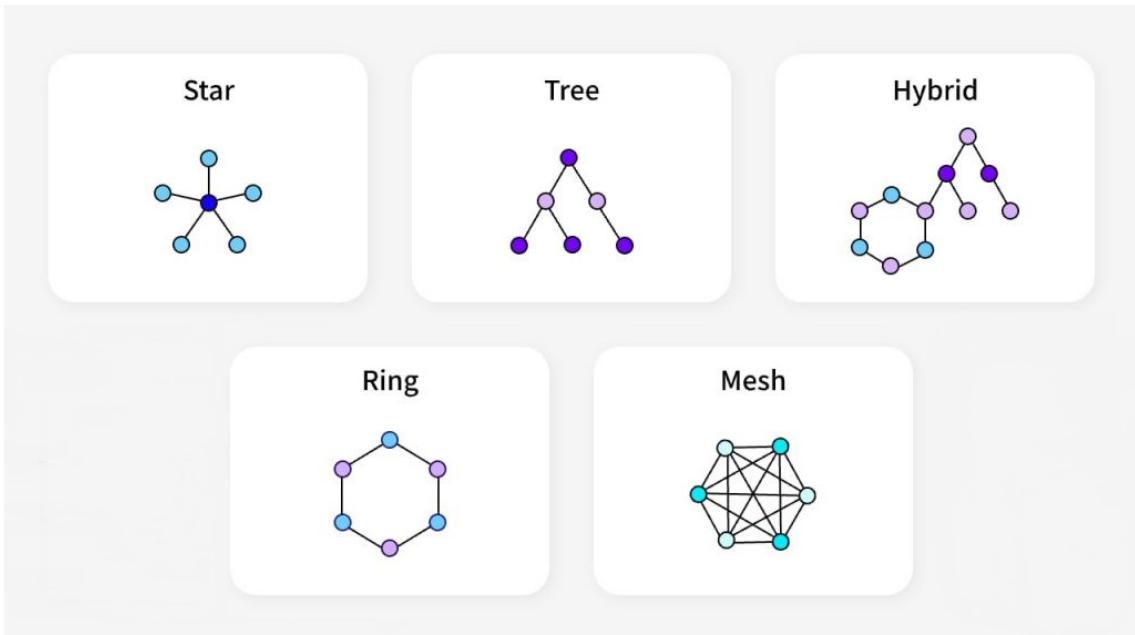

| 2.1  | Types of network topologies [2]. . . . .                                                                                                                                                                                                                                  | 6  |

| 2.2  | Broadcom Inc. is a major technology company specializing in the telecommunications field [2]. . . . .                                                                                                                                                                     | 7  |

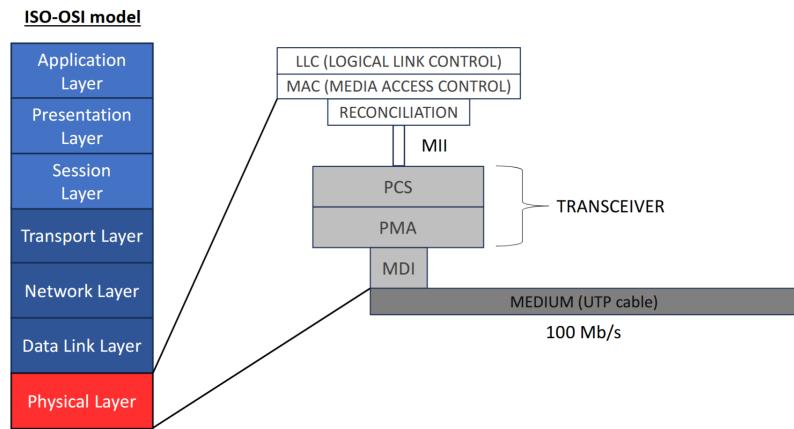

| 2.3  | Placement of 100BASE-T1 within the ISO/OSI communication model. . . .                                                                                                                                                                                                     | 8  |

| 2.4  | Architectural and functioning scheme of the Full-Duplex communication .                                                                                                                                                                                                   | 11 |

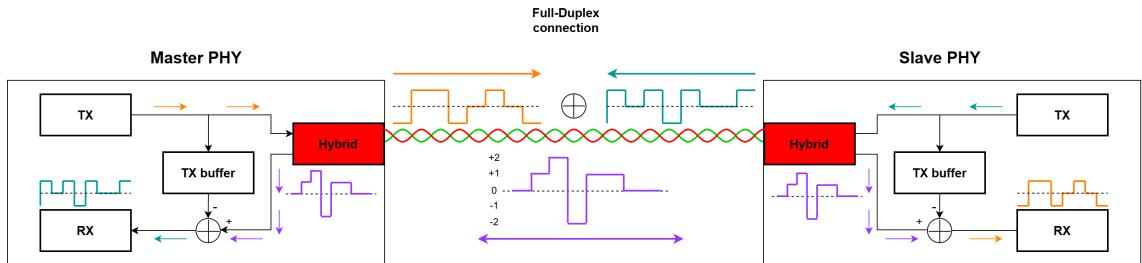

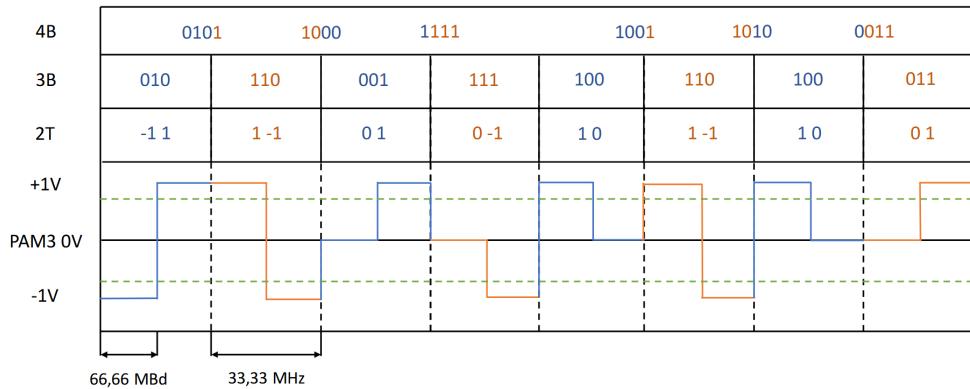

| 2.5  | PAM-3 encoding and ternary symbol representation. . . . .                                                                                                                                                                                                                 | 12 |

| 2.6  | Example of 4B/3B conversion with bit stuffing to align frame boundaries.<br>Source: [3] . . . . .                                                                                                                                                                         | 13 |

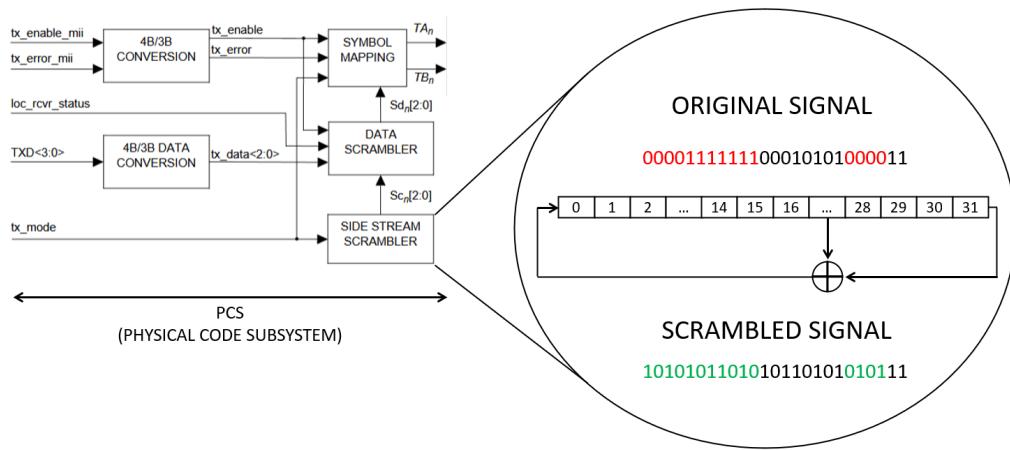

| 2.7  | PCS logical design and scrambler functioning example. Source: [3] . . . .                                                                                                                                                                                                 | 14 |

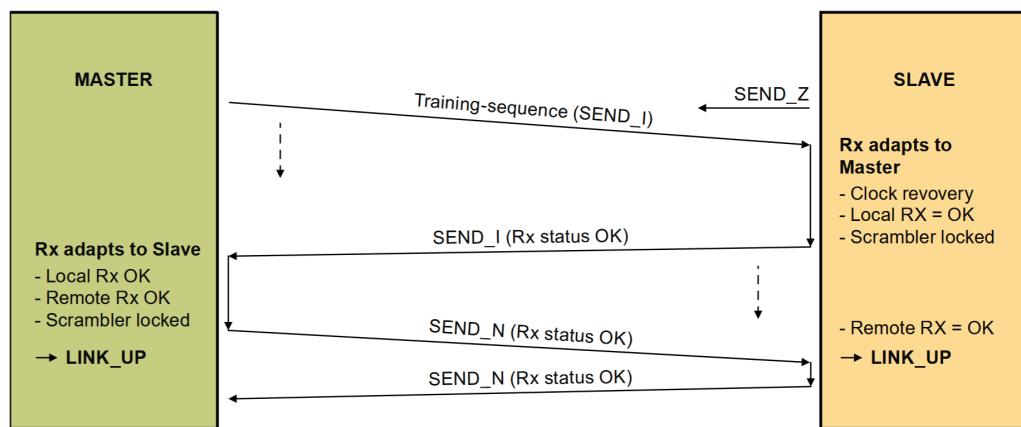

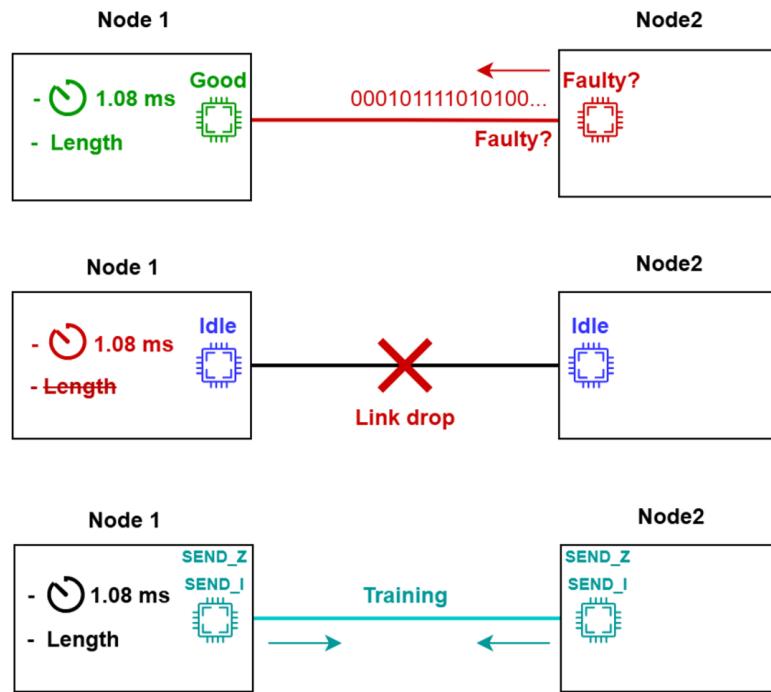

| 2.8  | Link training and establishment procedure. Source: NXP datasheet, consistent with IEEE 802.3 specifications. . . . .                                                                                                                                                      | 17 |

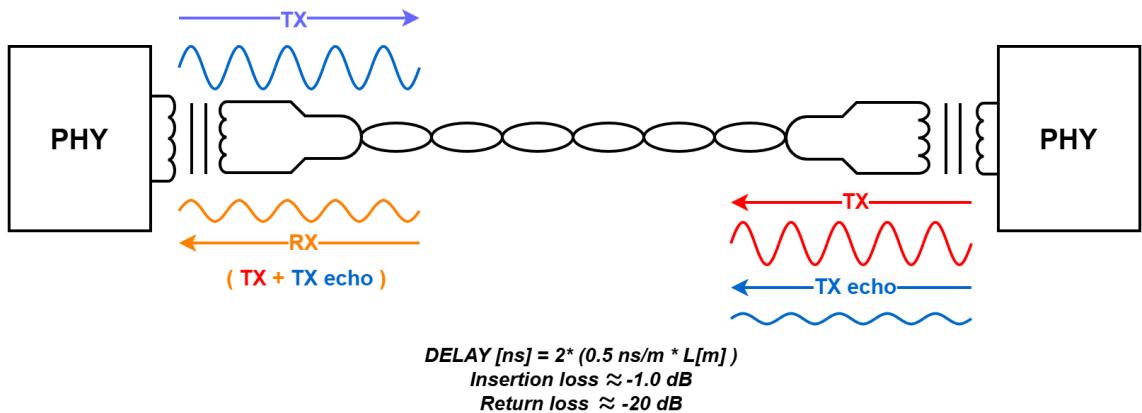

| 2.9  | Illustration of transmitted (TX) and received (RX) signals including the transmitter's echo, highlighting the role of echo cancellation. . . . .                                                                                                                          | 20 |

| 2.10 | Typical DC isolation and protection circuit for 100BASE-T1, including ESD protection, AC coupling capacitors, common-mode choke, and differential termination resistors [4]. . . . .                                                                                      | 21 |

| 2.11 | Overview of the 100BASE-T1 physical layer architecture, showing the interconnection between MAC, MII, PHY, MDI, and the differential cable link (adapted from [5]). . . . .                                                                                               | 23 |

| 2.12 | Placement of 100BASE-T1 within the ISO/OSI communication model. . . .                                                                                                                                                                                                     | 24 |

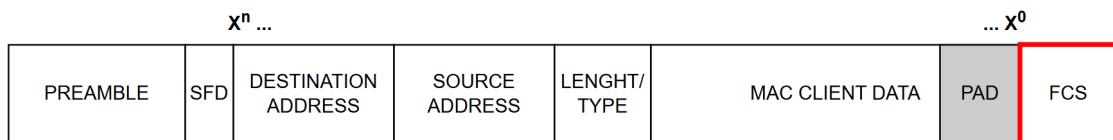

| 2.13 | Ethernet frame architecture take from IEEE 802.3 standard [3]. Transmission is performed LSB first for each byte. Byte transmit order is instead MSB first. . . . .                                                                                                       | 26 |

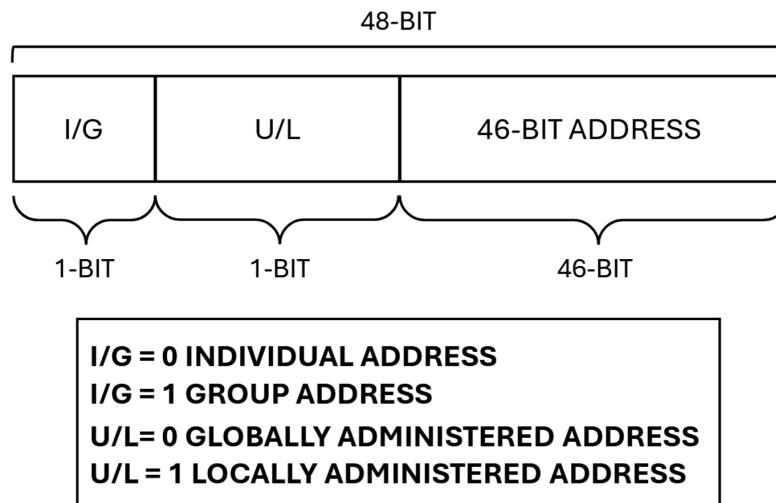

| 2.14 | Structure and bit significance of the MAC address. . . . .                                                                                                                                                                                                                | 27 |

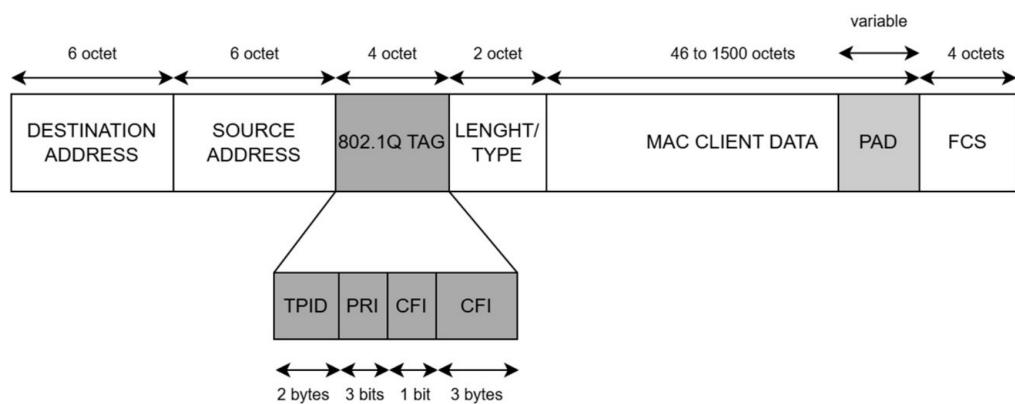

| 2.15 | Qtagged frame structure . . . . .                                                                                                                                                                                                                                         | 30 |

| 2.16 | CRC calculation field with bit sequence order . . . . .                                                                                                                                                                                                                   | 31 |

| 2.17 | Jabber Error identification. . . . .                                                                                                                                                                                                                                      | 34 |

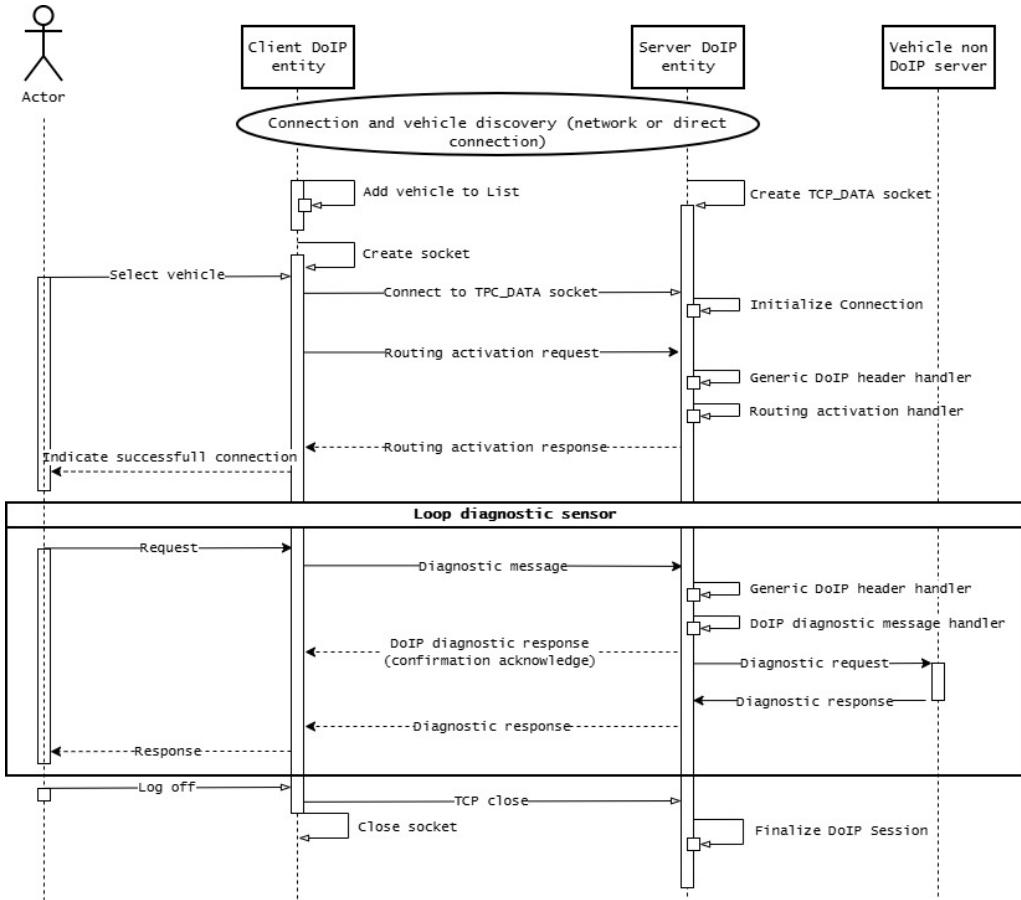

| 3.1  | The DoIP functional scheme highlights how diagnostic communication is handled over TCP/IP networks, enabling efficient routing, session management, and secure data exchange between external test equipment and in-vehicle ECUs. Figure rielaboration from [6] . . . . . | 38 |

| 3.2  | Pdelay calculation message exchange . . . . .                                                                                                                                                                                                                             | 43 |

| 3.3  | Periodically sync message sended by the master to the slaves . . . . .                                                                                                                                                                                                    | 44 |

| 4.1  | MDI of FC602 device are 2 cable clamp with screw to attach TP+ and TP- cables. Source: [7] . . . . .                                                                                                                                                                      | 46 |

| 4.2  | Cable connectors for the 100BASE-T1 side are choosen to be HMTD, compliant to most automotive network solutions. Source: [8] . . . . .                                                                                                                                    | 47 |

---

|      |                                                                                                                                                                                        |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3  | Cable connector for input data stream is Molex type. The two led assure controllability on link establishment and activity on the medium. Source: [9]                                  | 47 |

| 4.4  | Cable connectors for input data stream are HMTD type. Front LEDs assure the link establishment and data flowing through the PHYs and the logging ports. Source: [10]                   | 48 |

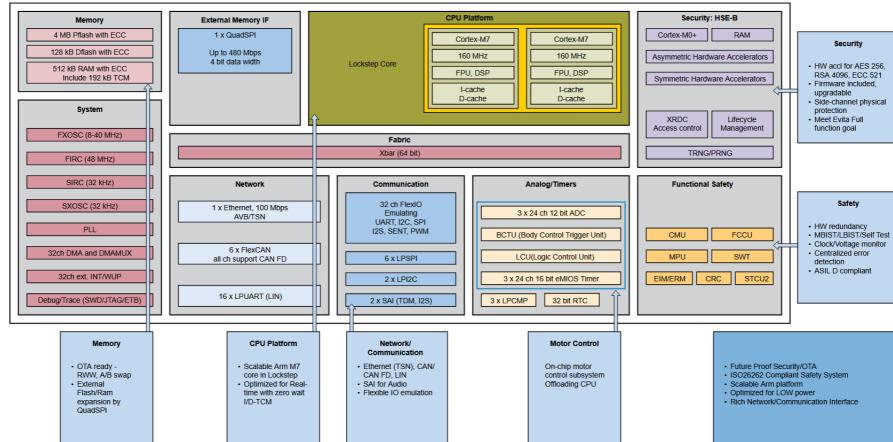

| 4.5  | Internal block diagram of the S32K344 microcontroller. Source: [11]                                                                                                                    | 49 |

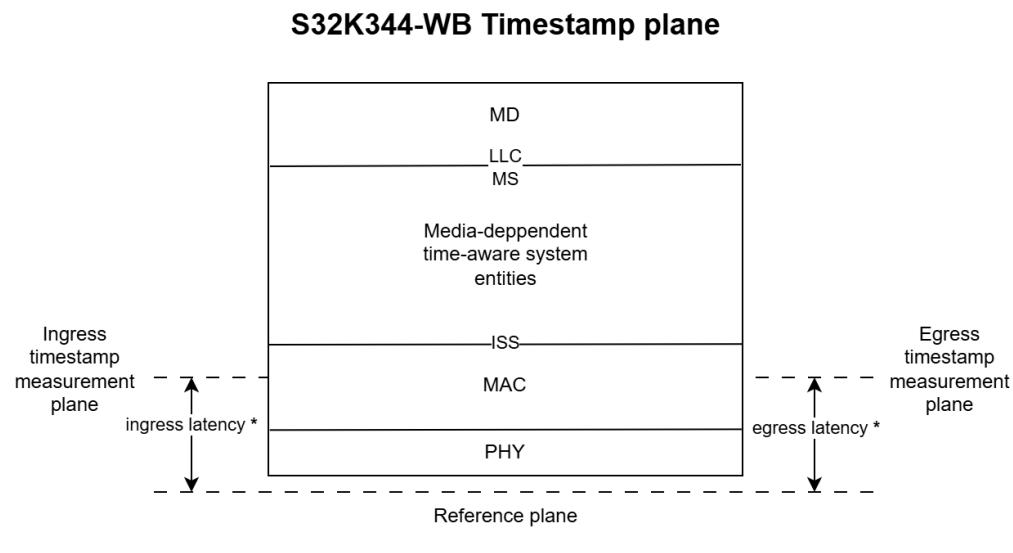

| 4.6  | Timestamp and reference plane difference in the WB board                                                                                                                               | 52 |

| 4.7  | Timestamp and reference plane difference in the CANHUB board. Note that ingress/egress delay is little comparing to 4.6 because of the presence of TJA1103, capable of HW timestamping | 53 |

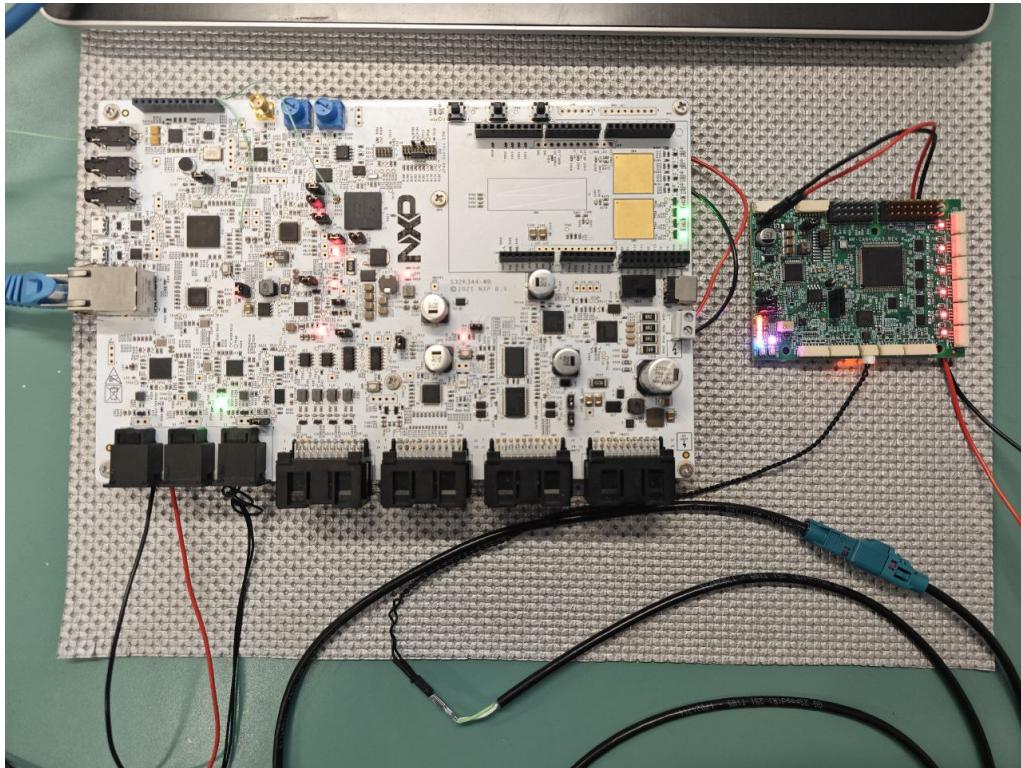

| 5.1  | Experimetal setup for data validation.                                                                                                                                                 | 60 |

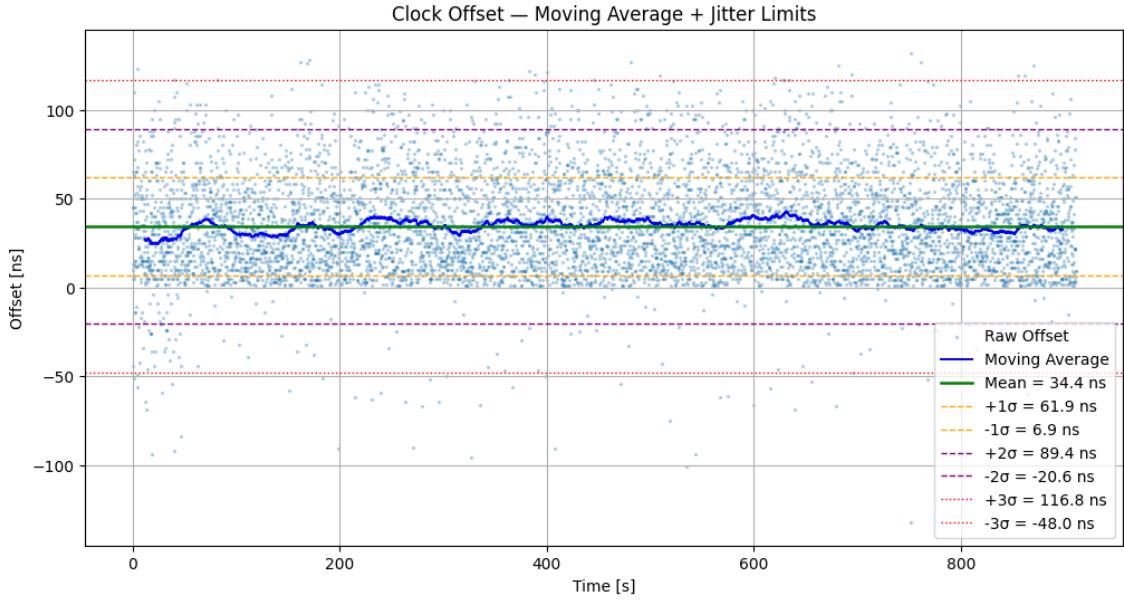

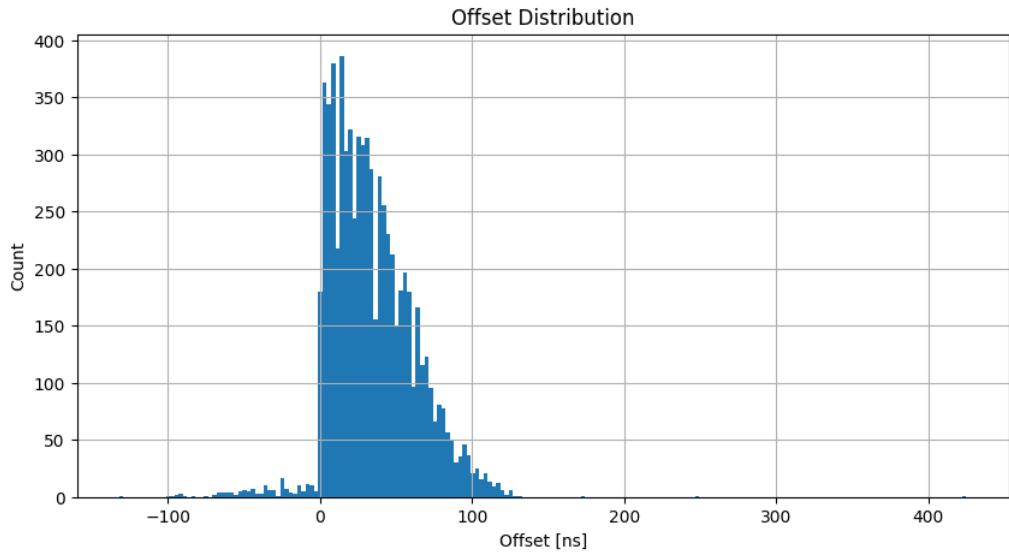

| 5.2  | Offset baseline over a 15-minute run                                                                                                                                                   | 62 |

| 5.3  | Statistical distribution of the computed offsets                                                                                                                                       | 62 |

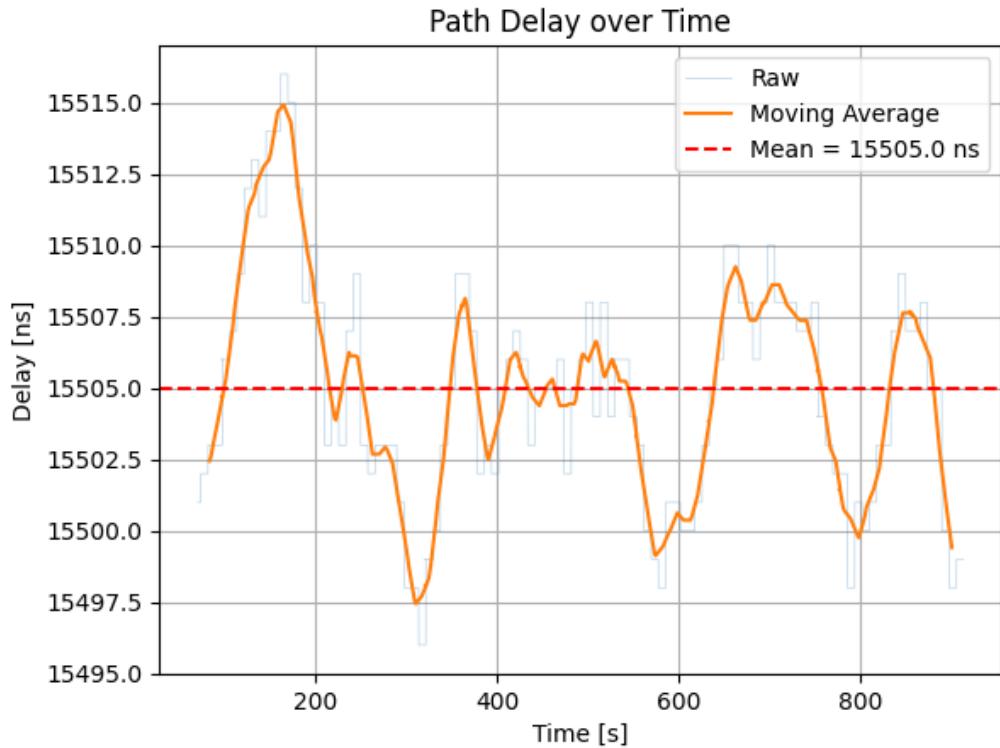

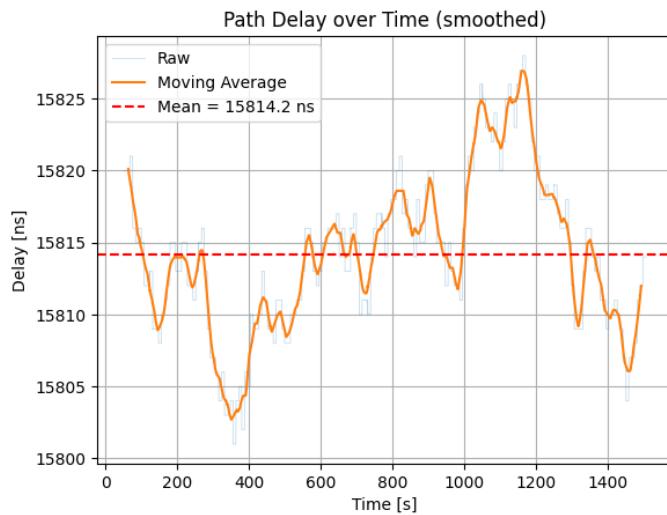

| 5.4  | Pdelay mean estimation                                                                                                                                                                 | 63 |

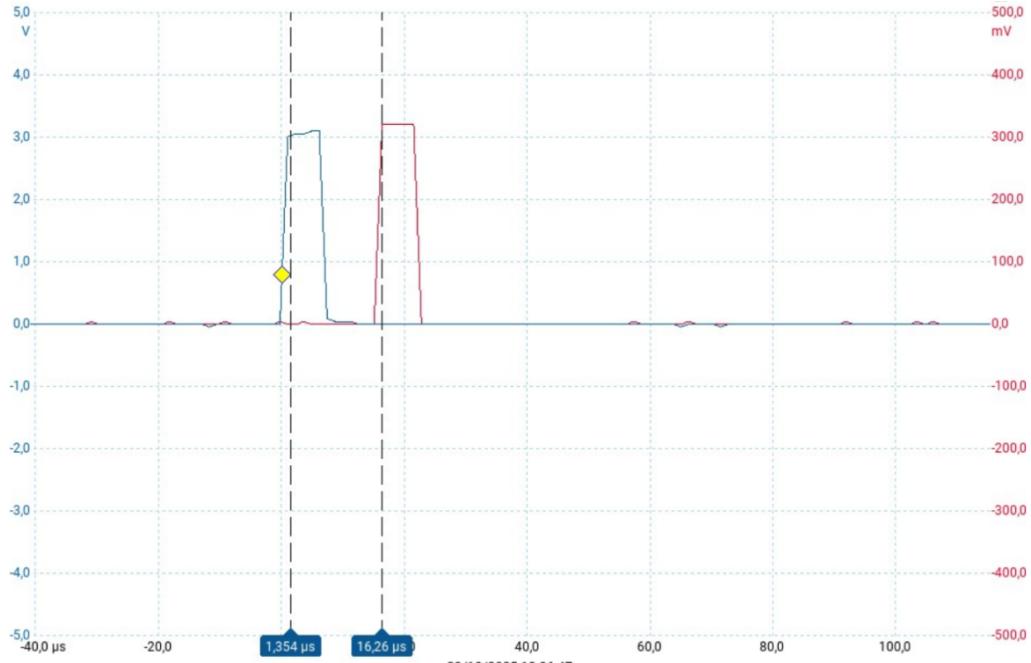

| 5.5  | Switch residence time: green signal is the Tx enable signal from the MCU and red one is the <i>TX_EN1</i> signal from the SJA1105 on the port1                                         | 64 |

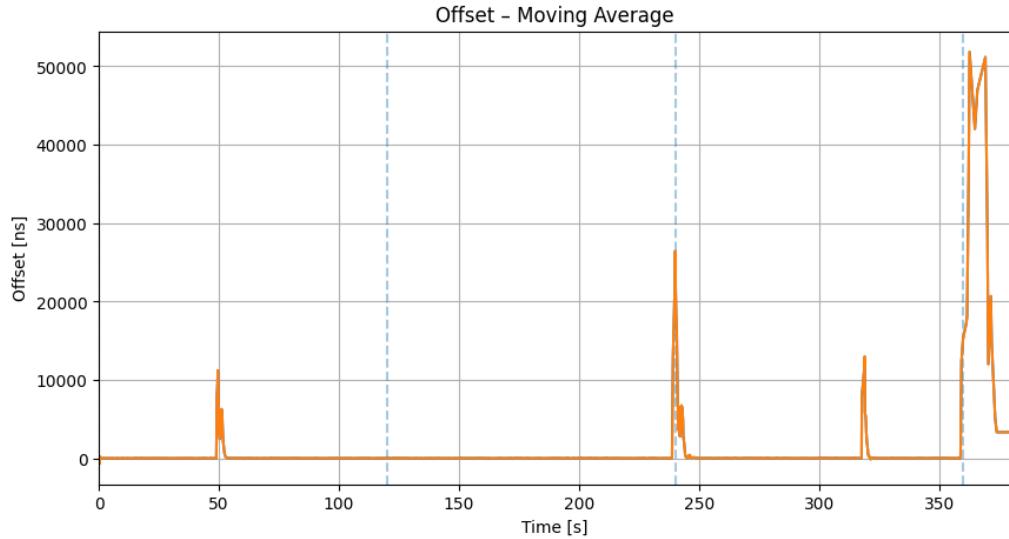

| 5.6  | Clock offset evolution without VLAN or traffic prioritization                                                                                                                          | 66 |

| 5.7  | Peer delay estimation under best-effort network load                                                                                                                                   | 66 |

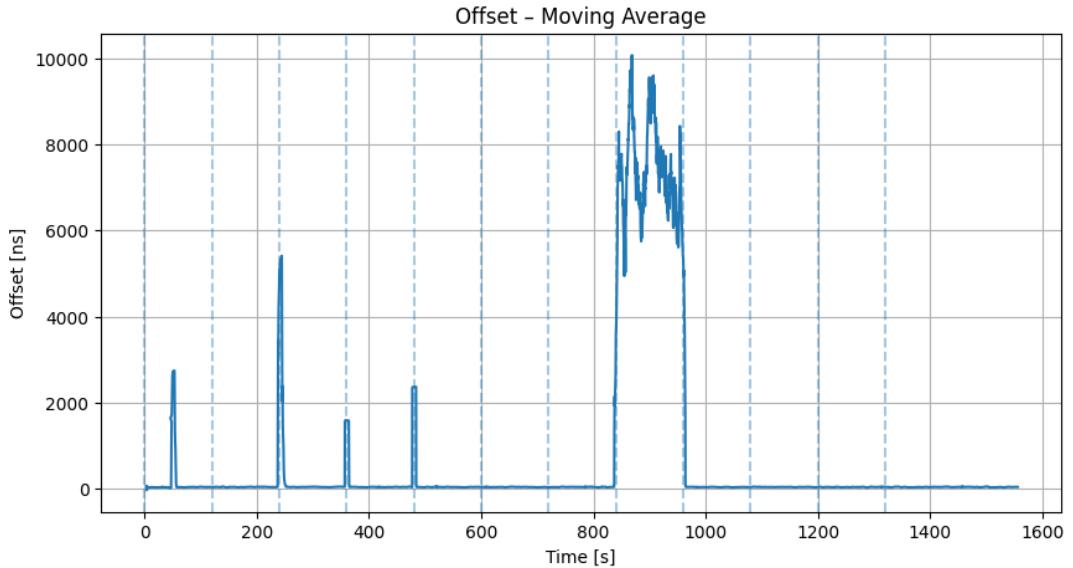

| 5.8  | Offset moving average – single VLAN (Case A). Dashed lines mark the beginning of each 120 s burst.                                                                                     | 68 |

| 5.9  | Offset moving average – dual VLAN (Case B). Dashed lines mark the beginning of each 120 s burst.                                                                                       | 68 |

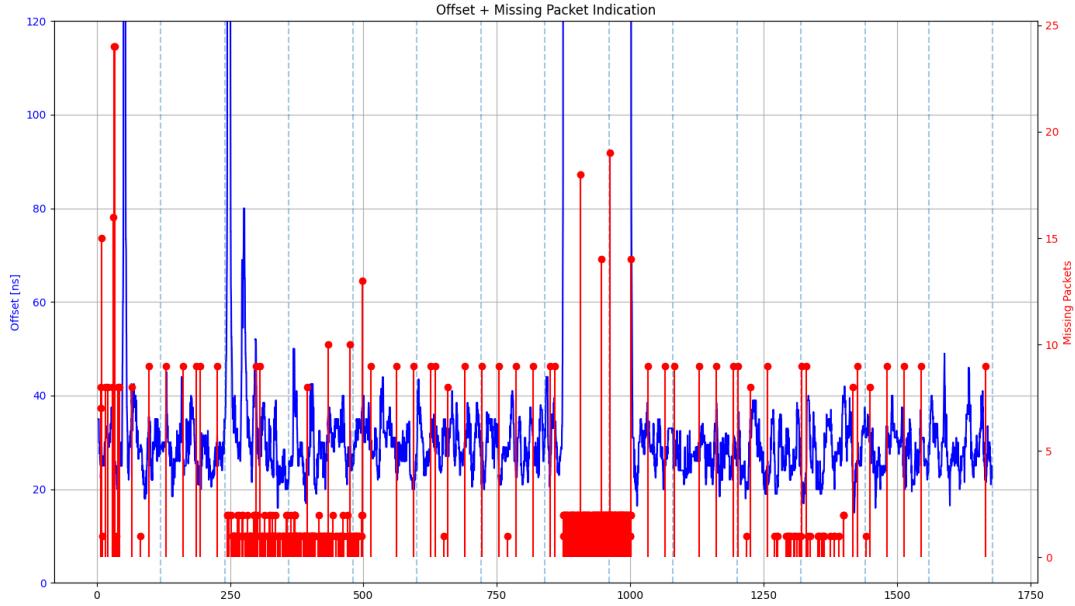

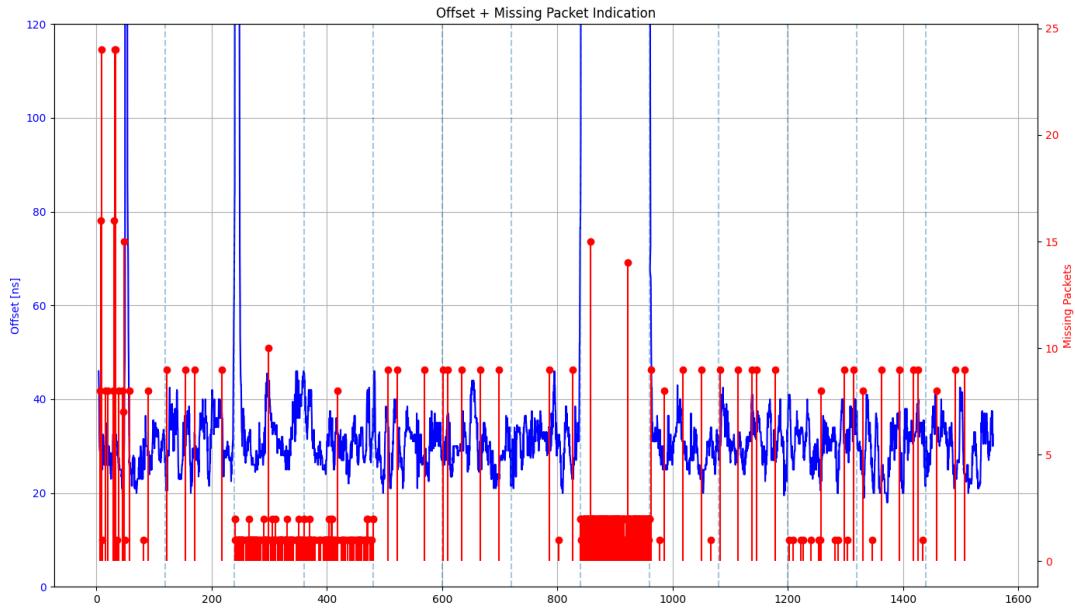

| 5.10 | Offset and missing Sync/Follow-Up packets – single VLAN (Case A). Blue: offset; red: estimated number of lost packets.                                                                 | 70 |

| 5.11 | Offset and missing Sync/Follow-Up packets – dual VLAN (Case B).                                                                                                                        | 70 |

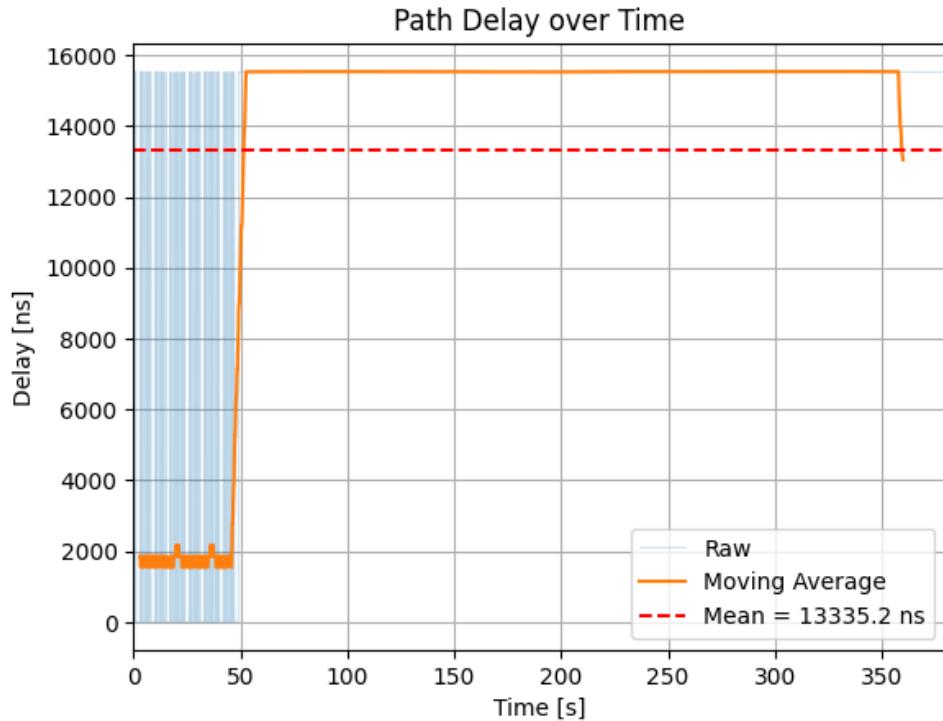

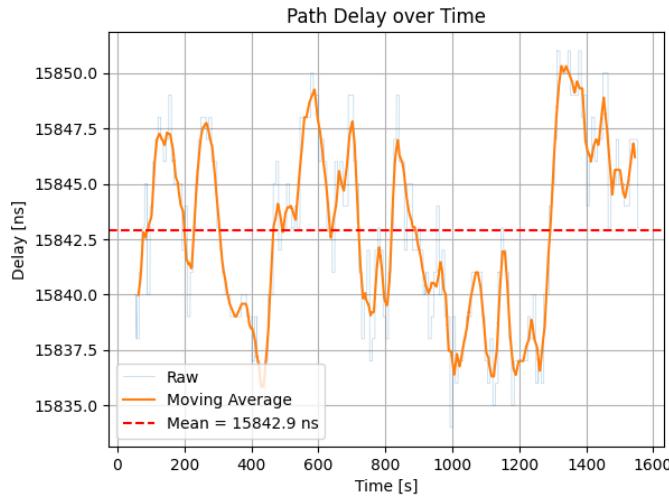

| 5.12 | Path Delay over time with moving average – single VLAN (Case A).                                                                                                                       | 71 |

| 5.13 | Path Delay over time with moving average – dual VLAN (Case B).                                                                                                                         | 71 |

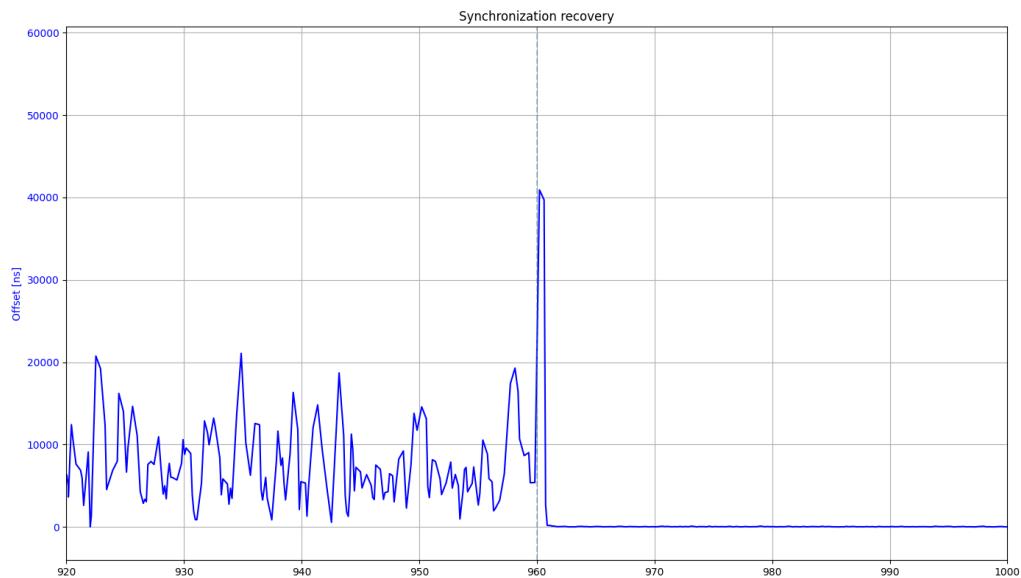

| 5.14 | Offset recovery after the high-load burst. Dashed line marks the instant where the dummy traffic returns to idle load.                                                                 | 72 |

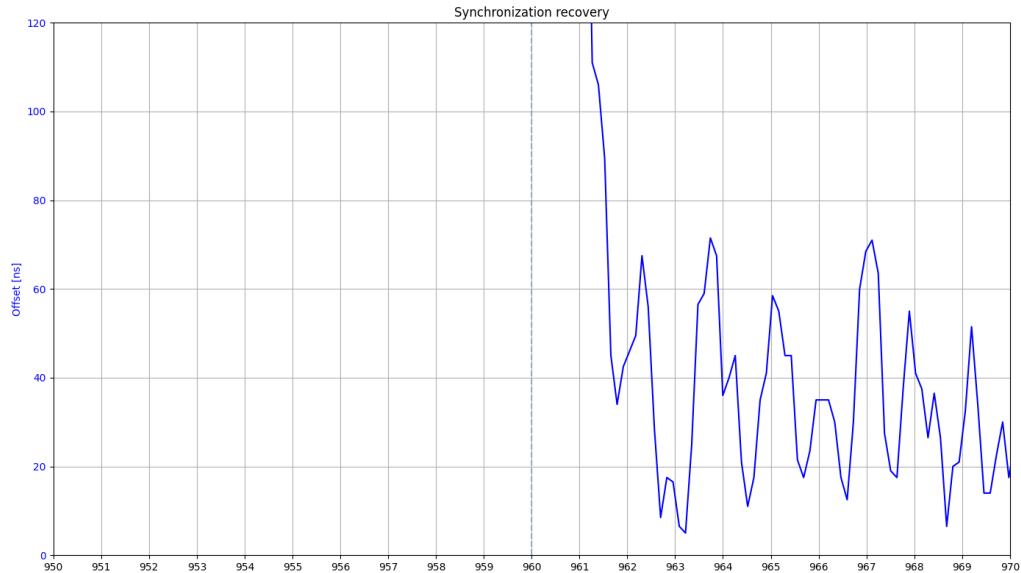

| 5.15 | Zoom of the recovery region, showing return to the steady-state band within a few seconds.                                                                                             | 73 |

---

# List of Tables

|     |                                                                                      |    |

|-----|--------------------------------------------------------------------------------------|----|

| 2.1 | Comparison between <b>SEND_I</b> and <b>SEND_N</b> symbol mappings. . . . .          | 16 |

| 2.2 | Main characteristics of H-MTD and Mate-Net automotive Ethernet connectors. . . . .   | 19 |

| 2.3 | Common EtherTypes in automotive Ethernet networks . . . . .                          | 29 |

| 2.4 | Hamming distance correlation with codeword length. . . . .                           | 33 |

| 3.1 | Protocol and Standard Mapping for DoIP Communication Stack . . . . .                 | 36 |

| 3.2 | Structure of a SOME/IP message header. . . . .                                       | 39 |

| 3.3 | PTP message type encoding (IEEE 802.1AS-2020). . . . .                               | 42 |

| 4.1 | Main components of the S32K344-CANHUB board used in the experimental setup . . . . . | 50 |

| 4.2 | Main hardware features of the S32K344-WB evaluation board. . . . .                   | 51 |

| 4.3 | Summary of SJA1105Q/S Switch Configuration for gPTP Validation . . . . .             | 57 |

| 5.1 | Traffic profiles and theoretical bandwidth usage (Mbps). . . . .                     | 65 |

| 5.2 | VLAN and PCP configuration for gPTP and dummy traffic . . . . .                      | 67 |

---

# Abstract

The increasing complexity of modern vehicles, driven by the integration of ADAS, infotainment, and connected services, demands communication networks with higher bandwidth and precise time synchronization capabilities compared to traditional CAN-based systems. In this context, Automotive Ethernet, and particularly the 100BASE-T1 (BroadR-Reach) standard, enables full-duplex communication over a single twisted pair, combining high data throughput with reduced wiring complexity. This thesis investigates the physical layer and the main Automotive Ethernet communication protocols — including TSN, SOME/IP, DoIP, and gPTP (IEEE 802.1AS) — focusing on their role in time-sensitive and service-oriented automotive architectures. An experimental setup was developed using two NXP S32K344-based boards, configured to communicate over a 100BASE-T1 point-to-point link. The gPTP synchronization stack provided by NXP was adapted to a bare-metal environment without AUTOSAR dependencies, enabling both hardware and software timestamping for network synchronization analysis. The work provides a complete experimental characterization of the implemented system, offering insights into the accuracy, stability, and practical limitations of gPTP synchronization in Automotive Ethernet networks and its suitability for future zonal architectures.

---

# CHAPTER 1

---

## Introduction

The continuous evolution of modern vehicles has led to a dramatic increase in the amount of data exchanged inside the in-vehicle network. Advanced driving assistance systems (ADAS), high-resolution cameras, radar and lidar sensors, connectivity services, and infotainment features all require reliable, high-bandwidth communication between Electronic Control Units (ECUs). As the level of autonomy and intelligence in vehicles increases, the in-vehicle communication infrastructure becomes a key enabler of safety, performance, and user experience.

Traditional automotive networks such as CAN, LIN, and FlexRay are no longer sufficient to handle these bandwidth demands. For this reason, Ethernet technology has been progressively introduced as the backbone of the in-vehicle communication system. Among the different variants standardized for automotive environments, **100BASE-T1** (IEEE 802.3bw) represents a crucial milestone, enabling 100 Mbit/s full-duplex communication over a single unshielded twisted pair (UTP) cable. This reduces weight, cost, and harness complexity while maintaining excellent signal integrity and EMC performance [12].

### 1.0.1 Safety-Critical Communication

Many new functions in the vehicle fall under the category of mission- and safety-critical systems:

- Powertrain and chassis control (braking, steering assistance)

- Perception and decision modules for autonomous driving

- Low-latency sensor fusion and actuation loops

These applications impose strict timing requirements: bounded latency, very low jitter, and guaranteed availability. Ethernet alone is not sufficient to ensure deterministic behavior, therefore additional protocols and mechanisms are required, such as:

- Time-Sensitive Networking (TSN)

- IEEE 802.1AS / gPTP time synchronization

- Service-oriented middleware such as SOME/IP

### 1.0.2 Architectural Evolution

To integrate both legacy fieldbuses and Gigabit-class Ethernet, the in-vehicle network architecture is undergoing a fundamental transformation.

## Domain Architecture

Historically, ECUs have been grouped into functional domains: body, powertrain, infotainment, etc. Each domain typically has a gateway to route traffic to other parts of the vehicle. While effective for earlier vehicles, cross-domain communication creates bottlenecks as data volumes increase.

## Zonal Architecture

The emerging *zonal architecture* restructures the wiring into geographical zones, each controlled by a zonal ECU. High-performance computing units act as a centralized processing cluster, while communication between zones is handled through a high-speed Ethernet backbone.

This approach significantly reduces harness length and weight, improves scalability, and aligns with future over-the-air (OTA) update and cloud connectivity strategies.

Figure 1.1: Different types of automotive architectures now in use [1].

### 1.0.3 Bandwidth Requirements

The exponential growth in network bandwidth is mostly driven by ADAS sensors and infotainment systems. Data production from a single perception sensor can exceed the capacity of entire legacy vehicle networks. Typical bandwidth demand includes:

- Radar: 100 Mbit/s

- Cameras: 500 Mbit/s per stream or higher

- Lidar: several Gbit/s

In this context, **100BASE-T1** is widely adopted for sensor connectivity and ECU backbone links thanks to its bandwidth, robustness, and cost-effectiveness. It also serves as a fundamental building block toward higher-speed variants such as 1000BASE-T1 and Multi-Gig automotive Ethernet.

In summary, the shift toward software-defined vehicles and autonomous driving strongly depends on automotive Ethernet technologies. The 100BASE-T1 standard, combined with

TSN and gPTP, enables real-time communication and synchronized operations that are essential for safety-critical automotive applications. This thesis focuses on the behavior of a gPTP slave in a 100BASE-T1 network and the impact of packet loss and master unavailability on synchronization stability.

---

## CHAPTER 2

---

# Ethernet Automotive

The first Ethernet LAN was projected in at least 30 years ago by Robert Metcalfe at Xerox and the first published standards from the Digital Equipment Corporation of Intel in collaboration with Xerox.[13] In 1985 the Institute of Electrical and Electronics Engineers (IEEE) published the LAN standard with the initial number 802. Now the actual Ethernet standard is the 802.3 but, to assure conformance with the OSI model, some modification was done to the original Ethernet standard.

### 2.1 Network Topologies

Traditional in-vehicle networks, such as CAN, LIN historically relied on BUS topology that offers low cost and simplicity but limited bandwidth. Automotive Ethernet transition also introduce the need to redesign the network topologies as mentioned in the previous chapter. The following section describes briefly the most used Ethernet network topology also used in conventional IT networks, yet optimized for automotive constraint such as electromagnetic compatibility, deterministic latencies and cable weight:

- **Point-to-Point:** the foundation of the Ethernet standard, topology that works on the functionality of sender and receiver. It provides good quality connection and high bandwidth, such as the only destination of the message from the sender side is his receiver counterpart.

- **Mesh :** Every device included in the Mesh topology has a dedicated link to any another with a special connection on a dedicated channel, known as Link. Supposing to have  $N$  node, the total number of port in a node is  $N-1$ , therefore the total number of links in the network is given by  $N*(N-1)/2$ . The advantages are multiple: very fast communication; a robust architecture that can still manages to deliver the message to a node, even if the point-to-point connection with his neighbor is lost; fault detection is really fast and secure.

Disadvantages arises in the high cable demand required to make all the connection between the nodes, also the maintenance of the network is difficult and high time consuming, redundancy reducing is difficult in such a redundant configuration.

- **Star:** Star topology comprehend a set of  $N$  nodes and a central HUB on which every node is connected to. Central HUB can be passive and forward passively all the message without a logic inside or active where all ports have transceivers to receive and send frame. The adoption of this topology is very large because the number of cables needed are equal to the nodes number, each node has only to have one dedicated port and also because of the fault identification and isolation is very

easy. Obviously the disadvantage are due to the centrality of the hub, in fact if it fails all the nodes became unable to communicate with all the other

- **Ring:** Ring topology forms a ring in which all node in the network has exactly 2 neighbor device. The communication arbitration works with the usage of Token Ring that is passed through the network, at any time the node that holds the token has the permission to send data in the network. Repeaters are used along the topology in order to avoid data loss in long message trip. This architecture has low possibility of collision, due to the token ring, high speed transmission and it has a low cost of installation. Of course this is not a robust topology as if one or more node fails entire chunk of the ring can be unreachable.

- **Tree:** takes some characteristics from star and bus topology. It presents with a gerarchical structures with lower nodes connected to HUBs as in the star topology and higher levels HUBs are connected each other with a sort of backbone that has as a parent HUB. The data flowing is bottom up from lower to higher levels. The advantages from the star topology is that the distances of a node from the central hub is decreased as the message travelled through devices instead of the cable. Maintenance and device adding in the network is easy. The disadvantages are also inherited from the Star topology as if the central bug fail the entire network fails and the cost is high due to the cable usage and difficult reconfiguration due to a device adding operation on the network.

- **Hybrid:** it is a combination of all the above described topology. This topology is extremely flexible as can be designed on the actual composition and problem of the network, it can be expanded easily adding new devices or entire new section. On the other hand HUBs in this configurations are very expensive as they had to support various type of communication protocols.

Figure 2.1: Types of network topologies [2].

## 2.2 BroadR-Reach and IEEE 802.3

IEEE 802.3 is the standard that defines Ethernet at the physical layer and the Logical Link Control (LLC) sublayer since its first edition in the 1980s. Over the decades, the 802.3 family has been continuously expanded with several physical layer variants, such as 100BASE-TX and 1000BASE-T, in order to meet the increasing demands for higher data rates and different transmission media. Modifications and updates are published as amendments and later integrated into consolidated editions of the standard, such as IEEE 802.3-2012, IEEE 802.3-2018, and the latest IEEE 802.3-2022.

The growing demand for bandwidth in the automation and automotive fields identified Ethernet as a suitable base technology, offering lighter and more robust cabling solutions and lower implementation costs. At the end of the 1990s, Broadcom developed a new transceiver solution enabling full-duplex communication over a single balanced twisted pair of conductors. This technology was named *BroadR-Reach*. It provided a 100 Mbit/s bandwidth over a single unshielded twisted pair (UTP) cable, using a reduced signal bandwidth and advanced techniques to minimize electromagnetic interference (EMI), making it ideal for automotive environments. In 2011, the OPEN Alliance published the BroadR-Reach specification, making it openly available to the industry in order to promote its integration and adoption in automotive applications [4].

Figure 2.2: Broadcom Inc. is a major technology company specializing in the telecommunications field [2].

In order to further standardize this new technology and ensure interoperability with traditional Ethernet switches, it became necessary to integrate BroadR-Reach functionality and specifications into the IEEE 802.3 framework. The IEEE 802.3bw Working Group [14] developed and evaluated the solution for transmitting a 100 Mbit/s data stream over a single twisted pair cable. The work concluded with the publication of *IEEE Std 802.3bw-2015*, which defines **100BASE-T1** as a new standard for industrial and automotive applications. After the publication of this amendment, the modifications related to 100BASE-T1 were incorporated into later consolidated versions of IEEE 802.3 (starting from IEEE 802.3-2018). These steps are typical of the IEEE standardization process:

- Initial development and publication as a technical amendment.

- Subsequent integration into consolidated versions of the standard.

The publication of IEEE Std 802.3bw-2015 marked a turning point in the evolution of Ethernet technology, introducing for the first time an officially recognized single-pair physical layer within the IEEE 802.3 family. The 100BASE-T1 standard inherited the

fundamental Ethernet architecture — same frame structure, MAC functions, and upper-layer compatibility — while redefining the physical transmission medium and signaling methods to fit the constraints of automotive environments.

In traditional Ethernet implementations such as 100BASE-TX or 1000BASE-T, data transmission is carried out over multiple twisted pairs using separate wires for each direction of communication. In contrast, 100BASE-T1 achieves full-duplex communication over a single balanced twisted pair by means of sophisticated digital signal processing (DSP) techniques.

This approach drastically reduces cable weight and connector complexity while maintaining deterministic performance and high electromagnetic compatibility (EMC), both essential for in-vehicle networks.

The IEEE 802.3bw amendment specifies the complete set of physical layer parameters: modulation scheme, link segment characteristics, and transceiver requirements. These specifications were defined with a clear focus on interoperability between different vendors, long-term reliability under automotive conditions (vibration, and noise), and compliance with the general IEEE 802.3 MAC service interface.

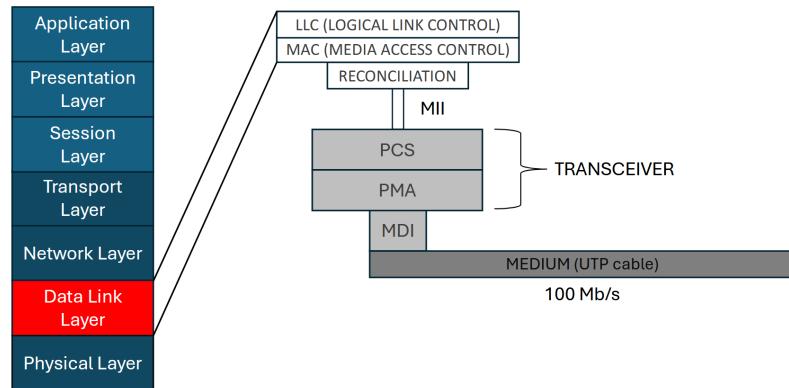

Figure 2.3 conceptually places 100BASE-T1 within the ISO/OSI model. The technology corresponds entirely to the **Physical Layer (Layer 1)**, while maintaining the same Logical Link Control (LLC) and Media Access Control (MAC) layers as other Ethernet variants.

Figure 2.3: Placement of 100BASE-T1 within the ISO/OSI communication model.

The definition of the 100BASE-T1 physical layer also paved the way for subsequent developments such as 1000BASE-T1 (IEEE 802.3bp) and Multi-Gigabit Single Pair Ethernet (IEEE 802.3ch), which further extended the performance of single-pair Ethernet to higher data rates. Therefore, understanding the 100BASE-T1 physical layer provides the fundamental basis for comprehending the entire family of automotive and industrial Single Pair Ethernet (SPE) technologies.

The following section will therefore analyze the **Layer 1 structure** of 100BASE-T1, including the transceiver architecture, modulation schemes, and the synchronization mechanisms.

## 2.3 Physical Layer Overview

The **100BASE-T1** PHY operates in **full-duplex mode** over a single **unshielded twisted pair (UTP)** cable, using **echo cancellation** to separate transmitted and received signals. It interfaces with the **MII**, **PCS**, and **PMA** sublayers to exchange data with the **MDI**,

which connects to the physical medium. The 100BASE-T1 leverages techniques derived from 1000BASE-T and 100BASE-TX PHYs, operating at a nominal rate of **100 Mb/s**, but introduces specific implementations of the PCS and PMA optimized for single-pair transmission.

- **MDI (Medium Dependent Interface)** — the first interface of the transceiver. It receives the electrical signal from the cable and delivers a corresponding digital stream to the upper modules.

- **PMA (Physical Medium Attachment)** — transmits and receives data between the PCS and the MDI, supporting link management and control functions.

- **PCS (Physical Coding Sublayer)** — manages data encoding and decoding between the MII and PMA, ensuring proper mapping and synchronization of digital symbols.

- **MII (Media Independent Interface)** — provides a standardized logical and electrical connection between the MAC and PHY layers.

### 2.3.1 Physical Coding Sublayer (PCS)

The **PCS** provides the logical mapping between the digital data of the MAC and the analog signal used on the medium. This module defines how the data are *scrambled* to maintain synchronization and minimize electromagnetic emissions, how bits are *encoded*, and how they are grouped into *symbols*.

Typical PCS operations include:

- Data encoding and scrambling to minimize electromagnetic emissions and ensure sufficient signal transitions for synchronization;

- Symbol management and error detection on the received data symbols;

- Frame delimiter and start-of-frame control for reliable transmission.

This sublayer is not identical across all IEEE 802.3 physical standards. For example, the **1000BASE-T** PCS uses a 5-level PAM encoding, while **100BASE-T1** employs a **PAM-3** modulation optimized for single-pair full-duplex transmission over unshielded twisted-pair cables.

By separating logical encoding from the physical signal interface, the PCS ensures design flexibility and supports a wide range of PHY implementations using a common MAC interface.

### 2.3.2 Physical Medium Attachment (PMA)

The **PMA** acts as the bridge between the symbol-level processing performed by the PCS and the electrical interface of the MDI. Its main functions are **serialization and deserialization (SerDes)**, **clock recovery**, and **link training**, which adapt the transceiver parameters to the characteristics of the physical channel.

During transmission, the PMA serializes the parallel data from the PCS and transmits a continuous bit stream synchronized with the transmission clock. During reception, it recovers the incoming signal, performs clock and data recovery, aligns the symbols, and reconstructs the bit stream to be passed to the PCS.

In modern Ethernet PHYs, the PMA also performs **echo cancellation** and **equalization** to mitigate signal attenuation, crosstalk, and impedance mismatch. These functions are crucial in full-duplex operation, where transmission and reception occur simultaneously.

on the same wire pair. Effective noise reduction is particularly important in *automotive environments*, where cables and transceivers are exposed to strong electromagnetic interference and mechanical stress.

### 2.3.3 Media Independent Interface (MII)

The **Media Independent Interface (MII)** provides a standardized connection between the MAC and PHY. As its name suggests, it allows Ethernet controllers to integrate with different physical layers without hardware redesign.

The MII defines the set of *signals and pins* required to exchange data, control, and clock information between the MAC and PHY, for both transmit and receive paths. The number of pins depends on the data rate and specific implementation; variants such as **RMII** (Reduced MII) or **RGMII** (Reduced Gigabit MII) are often used to reduce pin count and simplify PCB layout.

### 2.3.4 Medium Dependent Interface (MDI)

The **MDI** represents the physical connection between the transceiver and the transmission medium, such as copper twisted-pair, coaxial cable, or fiber optics. It defines the **electrical characteristics**, **connector types**, and **impedance** of the link.

In the **100BASE-T1** standard, the MDI consists of a single unshielded twisted pair operating in full-duplex mode. Proper design of the MDI — including cable impedance control and connector layout — is crucial to meet the **EMC** and **signal integrity** requirements of automotive Ethernet systems.

## 2.4 100BASE-T1 Physical Layer Implementation

### 2.4.1 Full and Half-Duplex Communication

Ethernet communication can operate according to two main transmission modes: **half-duplex** and **full-duplex**. These two configurations differ in the way transmission and reception occur along the same communication medium.

#### Half-Duplex

In **half-duplex** mode, the communication channel is shared between transmission and reception, but only one direction can be active at a time. This means that a device must wait for the other to complete its transmission before being able to send its own data. A typical example of half-duplex communication is the operation of early Ethernet networks based on coaxial cable or hubs, where collision domains were managed by the *Carrier Sense Multiple Access with Collision Detection (CSMA/CD)* mechanism.

In these systems, if two devices attempt to transmit simultaneously, their signals collide, causing data corruption. Both transmitters must then stop and retry after a random delay. This approach, while simple and efficient for low traffic levels, limits the achievable bandwidth and increases latency, especially as the number of network nodes grows.

#### Full-Duplex

The evolution of Ethernet standards and the transition to switch-based topologies have made possible the introduction of **full-duplex** communication. In a full-duplex link, the two ends of the connection can transmit and receive simultaneously on the same physical medium. This effectively doubles the potential throughput compared to a half-duplex link of the same nominal data rate and completely eliminates collisions.

In full-duplex mode, each node can send frames independently without waiting for the line to be free, and there is no need for CSMA/CD mechanisms. However, simultaneous transmission and reception on the same cable introduces new physical challenges: the transmitted signal of a node inevitably couples into its own receiver path, generating what is known as **echo**. To correctly recover the information sent by the remote node, the receiver must therefore be capable of identifying and subtracting its own transmitted component from the incoming signal. This process is known as **echo cancellation** and is implemented in the *Physical Medium Attachment (PMA)* sublayer.

In 100BASE-T1 Ethernet, which operates over a single unshielded twisted pair (UTP) cable, full-duplex operation is achieved through careful analog design and sophisticated digital signal processing. Both ends of the link transmit continuously, with their signals superimposed in the medium. The received waveform is therefore a combination of the locally transmitted signal and the signal arriving from the remote end, each affected by the channel's propagation delay and attenuation.

Figure 2.4: Architectural and functioning scheme of the Full-Duplex communication

From a theoretical point of view, let  $s_A(t)$  and  $s_B(t)$  be the signals transmitted respectively by nodes  $A$  and  $B$ , and  $h(t)$  the channel impulse response. The signal received by node  $A$  can be expressed as:

$$r_A(t) = h(t) * s_B(t) + h_0(t) * s_A(t)$$

where  $h_0(t)$  models the coupling of the transmitted signal into its own receiver (the echo path). An accurate estimate of  $h_0(t)$  allows the receiver to subtract the echo and isolate  $s_B(t)$ , thus recovering the data sent by the other end.

The main advantages of full-duplex transmission are:

- **Increased throughput:** simultaneous bidirectional transmission effectively doubles the link capacity.

- **No collisions:** each direction operates independently, removing the need for collision detection.

- **Lower latency:** data can be transmitted immediately without waiting for the channel to become idle.

Full-duplex communication is therefore essential in modern high-speed Ethernet links, especially in automotive and industrial environments, where deterministic latency and continuous data flow are mandatory. The combination of full-duplex operation and advanced echo cancellation techniques represents one of the fundamental enablers of 100BASE-T1 technology, allowing robust, low-cost communication over a single twisted pair cable.

### 2.4.2 PAM3 Signaling and Line Coding

The **Physical Coding Sublayer (PCS)** of 100BASE-T1 is responsible for encoding and symbol generation, converting the data stream received from the **Media Independent Interface (MII)** into ternary symbols to be transmitted by the **Physical Medium Attachment (PMA)**.

At the interface with the MII, the PCS operates on a 4-bit data bus clocked at 25 MHz, corresponding to a raw throughput of 100 Mbit/s. However, before transmission, a **4B/3B** encoding process is applied: every 4 input bits are mapped into 3 output bits. This conversion introduces a rate mismatch, which is compensated by increasing the symbol rate at the PCS–PMA interface. To preserve the overall 100 Mbit/s bandwidth, the data frequency rises from 25 MHz to approximately 33.3 MHz.

Figure 2.5: PAM-3 encoding and ternary symbol representation.

The main signals exchanged between the MII and the PCS are:

- **tx\_enable\_mii**: enables data transmission through the MII interface.

- **tx\_error\_mii**: indicates a symbol encoding error detected in the PCS.

- **TXD $\langle 3:0 \rangle$** : 4-bit data nibbles exchanged between MII and PCS.

- **TX\_CLK**: 25 MHz clock that synchronizes MII data transfers.

Between the PCS and PMA, data are exchanged through a 3-bit interface, synchronized at 33.3 MHz:

- **tx\_data $\langle 2:0 \rangle$** : data triplet bus from PCS to PMA.

- **tx\_enable**: indicates valid data on the **tx\_data** lines.

- **pcs\_txclk**: 33.3 MHz transmission clock.

At the PMA output, the encoded symbols are mapped into voltage levels according to the **Pulse Amplitude Modulation with 3 levels (PAM-3)** scheme. Each ternary symbol can assume one of three voltage states, typically  $[-1, 0, +1]$  V, transmitted as a differential signal across the twisted pair. A symbol transition thus represents one of three possible voltage changes, which encodes 3 bits per symbol pair.

Different transmission modes — **SEND\_N**, **SEND\_I** and **SEND\_Z** — are used to represent the ternary symbol transitions, depending on the logical state of the transceiver during transmission and idle phases.

The transmission clock defines a **symbol pair period** of 30 ns, corresponding to a symbol rate of approximately 33.3 Mbaud. Given that each symbol pair encodes 3 bits, the resulting data rate is:

$$T_s = 30 \text{ ns} \quad \Rightarrow \quad f_s = \frac{1}{T_s} = 33.3 \text{ Msymbol/s}$$

$$R_b = f_s \times 3 \text{ bit/symbol} = 33.3 \text{ Msymbol/s} \times 3 = 100 \text{ Mbit/s}$$

During frame transmission, the PCS converts the **TXD(3:0)** nibbles into 3-bit symbols. Because Ethernet frame lengths are not always multiples of three, a **bit stuffing** mechanism is employed to complete the last symbol group. These extra bits are appended to the frame and discarded at the receiver side once the end-of-frame boundary is reached.

Figure 2.6: Example of 4B/3B conversion with bit stuffing to align frame boundaries.

Source: [3]

The **12-byte Inter Packet Gap (IPG)** defined by the Ethernet standard ensures that the receiver can flush any residual stuffed bits from the PCS buffer before the next frame begins, avoiding FIFO overflow and maintaining symbol alignment.

In summary, the PAM-3 encoding and 4B/3B mapping provide an efficient compromise between spectral efficiency, EMI reduction, and hardware complexity. This scheme allows 100BASE-T1 to maintain a 100 Mbit/s throughput using a single unshielded twisted pair while keeping signal bandwidth within 66 MHz — a key factor for reliable automotive transmission channels.

#### 2.4.3 Data Scrambling

Scrambling is employed as an additional processing step to enhance synchronization and maintain DC balance in the transmitted signal.

##### Scrambler

Build on a randomizing algorithm it is use to eliminate long strings of consecutive identical symbols transmitted on the medium. This technique allow to avoid the presence of spectral

lines, such as high peak, in the signal spectrum without changing the signal frequency rate. There are two main types of scrambler:

- **Self-synchronous** where the next scrambling state is dependent only on the prior  $n$  bits of the last output. It's counter part, **descrambler**, can acquire the correct scrambling state from the incoming signal.

- **Side-stream** a additional device is present to calculates the next state, depending only on the previous scrambling state and not also on the produced output. De-scrambler chose a state either searching for a state that decodes a know pattern or by agreement at a known state with the scrambler.

Side-stream scrambler is adopted in the 100BASE-T1 protocol, it is implemented by a 33-bit LFSR able to generate pseudo random sequence that has same probability to have 0 or 1 in each position. This sequence will be then XORED with the data coming from the 4B/3B data converter.

Figure 2.7: PCS logical design and scrambler functioning example. Source: [3]

Different polynomials are employed depending on the node role, depending on the value in the PMA\_CONFIG.indication message. Implementation of master and slave PHY side-scramblers is formed by a shift register where bits are stored in a register delay line. At time  $n$  is  $SRC_n[32 : 0]$  and at each symbol time shift register is advanced by one position and new value is presented at  $SRC_n[0]$ . For obvious reason this register cannot ever shall be initialized with all 0's.

$$\text{Master} \quad \Rightarrow \quad g_M(x) = 1 + x^{13} + x^{33}$$

$$\text{Slave} \quad \Rightarrow \quad g_M(x) = 1 + x^{20} + x^{33}$$

To ensure proper data recovery, the scrambler and descrambler must operate in a synchronized manner, sharing an identical shift-register state at the start of communication. This synchronization is typically established during the training or IDLE phase, when known data patterns are exchanged. By observing the received symbols and comparing them with the expected scrambled values, the receiver gradually reconstructs the internal state of the transmitter's scrambler. Once the descrambler output remains consistent over several symbol periods, synchronization is considered locked. Some implementations also include automatic polarity detection: the receiver assumes a polarity, verifies descrambler convergence, and, if necessary, retries with the opposite assumption. This mechanism guarantees reliable state acquisition without requiring explicit transmission of the scrambler state.

#### 2.4.4 Node Synchronization

##### Master & Slave

Node synchronization as to be assured between all the point to point connection in order to exploit the full-duplex communication mode. For this reason MASTER-SLAVE assignment for each link end is necessary for establishing timing control on each transceiver. Indeed to assure a good quality connection, slave device must be able to retrieve the clock signal from master's data and thus maintain a good synchronization. PHY mode can be chosen either by hardware switch or by setting the proper value in the dedicated control registers, present in each transceiver. Master-slave couplings will trigger errors during the **training phase**, resulting in an incorrect training procedure that will prevent the establishment of a connection between the two points.

##### Clock synchronization

In the **100BASE-T1 Ethernet** standard, there is *no dedicated* clock line shared by the MASTER. Instead, both data and timing information are transmitted over a *single differential* pair. As a result, the **SLAVE** device must recover the clock directly from the received data stream.

The **periodicity of signal transitions** — both rising and falling edges — is ensured by the **scrambler** in the transmitter node. This scrambler introduces sufficient data transitions to maintain clock recovery, provided that both the **scrambler** and **descrambler** are *perfectly synchronized* to guarantee reliable encoding and decoding operations.

Clock synchronization is achieved by a **phase detector and phase shifter** circuit, which continuously compares the *incoming clock* phase with the local *oscillator* running at **33.3 MHz**. Any detected phase difference is used to *adjust the local clock* so that it remains in sync with the transmitter's timing, ensuring stable and synchronized data communication between MASTER and SLAVE.

##### Operational Modes

Three operational mode are available to specify the sequence of code-groups sent by the transmitter.

- **SEND\_N**: continuously asserted when the transmission of sequences of code-groups representing MII data stream, control mode or idle mode is to take place.

- **SEND\_I**: continuously asserted in case of transmission of sequences of code-groups representing the idle mode

- **SEND\_Z**: continuously asserted in case of transmission of consecutive zero is needed.

Various pattern mode are distinguishable for their symbols composition and entropy, for example in SEND\_N idle pattern will have low entropy than the data pattern. Those three mode are used to identify the various steps of the training phase and error occurrences.

| $Sd_n [2 : 0]$ | $Ta_n$   | $TB_n$    | $Sd_n [2 : 0]$   | $Ta_n$ | $TB_n$ |

|----------------|----------|-----------|------------------|--------|--------|

| 000            | -1       | 0         | 000              | -1     | -1     |

| <b>001</b>     | <b>0</b> | <b>1</b>  | 001              | -1     | 0      |

| 010            | -1       | 1         | 010              | -1     | 1      |

| <b>011</b>     | <b>0</b> | <b>1</b>  | 011              | 0      | -1     |

| 100            | 1        | 0         | Used for SSD/ESD |        |        |

| <b>101</b>     | <b>0</b> | <b>-1</b> | 0                | 0      |        |

| 110            | 1        | -1        | 100              | 0      | 1      |

| <b>111</b>     | <b>0</b> | <b>-1</b> | 101              | 1      | -1     |

|                |          |           | 110              | 1      | 0      |

|                |          |           | 111              | 1      | 1      |

(a) Symbol mapping in **SEND\_I** mode.(b) Symbol mapping in **SEND\_N** mode.Table 2.1: Comparison between **SEND\_I** and **SEND\_N** symbol mappings.

### SSD/EDS code-sequence

SSD and ESD are 3 code sequences used, by the PMA only in SEND\_N mode, to specify the start and the end of a packet frame. SSD is a 3 symbols code preceding the transmission of a frame. ESD is a 3 symbol code that follows the end of the frame and the deassertion of the TX\_EN signal identifying the end of a transmission. ESD with error is also attached to the end of the frame signaling the presence of an error occurred during the transmission.

$$\begin{aligned}

SSD &\Rightarrow (00), (00), (00) \\

ESD &\Rightarrow (00), (00), (11) \\

ESD \text{ with } tx\_error &\Rightarrow (00), (00), (-1 - 1)

\end{aligned}$$

#### 2.4.5 Training Phase

As 100BASE-T1 leverages a full-duplex communication protocol, an initialization and training phase must be performed between the **MASTER** and **SLAVE**. During the training phase, both devices send data patterns that allow to:

1. Train the echo canceller with the transmitter signal, in order to be able to filter it out when the signal is received at the receiver side.

2. Lock the scrambler synchronization (see Section 2.4.3).

3. Synchronize the SLAVE clock to the MASTER clock retrieved from the data signal.

4. Adjust the signal conditioning in order to tune filters according to the received signal, which is essential to further eliminate noise sources or fine-tune other signal parameters.

This phase should last a maximum of 200 ms. Two timers are used to keep this constraint under control.

### Link Establishment

The training phase is always initiated by the MASTER device, which transmits a training sequence in **SEND\_I** mode. This mode allows the remote SLAVE to receive a predictable pattern used to calibrate internal circuits — including the echo canceller, equalizer, and clock synchronization — as described in IEEE 802.3bw Clause 96 [3]. The overall process can be summarized as follows:

1. The MASTER begins transmission in **SEND\_I** mode, while the SLAVE remains in **SEND\_Z**. During this interval, the MASTER uses the known training signal to adapt its own echo canceller and ensure stable transmission [15].

2. The SLAVE receives the idle pattern, checks for correct symbol decoding, and then trains its echo canceller. It also recovers the MASTER's clock from the data stream and locks its own scrambler to match the MASTER's state.

3. Once the recovered clock remains stable for approximately 1.8  $\mu$ s, the SLAVE begins transmitting its own idle pattern in **SEND\_I** mode. This allows the MASTER to confirm that the SLAVE's receiver is correctly synchronized.

4. When both sides complete all synchronization procedures, the **LINK\_STATUS** register is set to 1, indicating that **LINK\_UP** has been successfully achieved. The MASTER can then begin data or idle transmission in **SEND\_N** mode.

If the `loc_rcvr_status` flag does not reach the `OK` state within 200 ms, the training phase is considered failed. In this case, the SLAVE enters the `SLAVE_SILENT` mode, and its transmitter switches to `SEND_Z`. The MASTER detects the continuous stream of zeros, interprets it as a failed training attempt, and restarts the initialization procedure.

A link drop may occur when an invalid ternary pair is detected, when the local receiver can no longer recover the clock, or in case of a physical fault such as a short circuit in the connection. Depending on the PHY implementation, a high rate of errors — such as `SSD`, `ESD`, `transmit_err`, or `receiver_err` — may also trigger a retraining sequence to reestablish the link. These mechanisms are designed to ensure robust operation under the high-noise and EMI conditions typical of automotive environments [?, ?].

Figure 2.8: Link training and establishment procedure. Source: NXP datasheet, consistent with IEEE 802.3 specifications.

## 2.4.6 Cable Characteristics & connectors

The 100BASE-T1 standard specifies the use of a single unshielded twisted pair (UTP) cable with a **characteristic differential impedance** of  $100 \Omega \pm 10\%$ . This value is not arbitrary but results from both physical transmission constraints and the need for interoperability within the IEEE 802.3 Ethernet family.

The characteristic impedance of a transmission line depends on its distributed inductance  $L'$  and capacitance  $C'$  per unit length, and can be expressed as:

$$Z_0 = \sqrt{\frac{L'}{C'}}.$$

Maintaining the same impedance at the transmitter, cable, and receiver interfaces ensures proper **impedance matching**, preventing reflections and standing waves that would otherwise degrade the signal quality and cause inter-symbol interference (ISI). This matching condition is essential for reliable high-speed transmission, especially in **full-duplex operation** where simultaneous transmission and reception occur on the same medium.

Moreover, the use of a **balanced differential pair** with  $Z_0 = 100 \Omega$  guarantees a high level of **common-mode noise rejection**. In differential signaling, the two conductors carry equal and opposite signals, so any external electromagnetic interference (EMI) coupled into both wires is largely canceled at the receiver input. This property is fundamental in automotive environments, where cables are often routed near noisy sources such as power lines, motors, and switching converters.

However, despite its robustness, the 100BASE-T1 physical layer is limited to a maximum cable length of approximately **15 meters**. This restriction derives from the inherent sensitivity of full-duplex transmission over a single pair: as both ends transmit and receive simultaneously, **echo and near-end crosstalk** become dominant noise sources. Longer cable runs would exacerbate attenuation and phase distortion, making echo cancellation increasingly difficult and reducing the signal-to-noise ratio (SNR) below the required operational margin. Therefore, the 15 m limit represents a practical trade-off between link reliability, data integrity, and EMC performance within the intended automotive use case.

Finally, the choice of a  $100 \Omega$  impedance maintains compatibility with other twisted-pair Ethernet physical layers (e.g., 100BASE-TX, 1000BASE-T), simplifying transceiver design and allowing reuse of existing magnetics, connectors, and testing equipment optimized for this impedance range. Hence, the  $100 \Omega$  balanced twisted pair represents the optimal compromise between signal integrity, EMI immunity, mechanical simplicity, and cost efficiency for the 100BASE-T1 physical layer.

At the moment there are no standards that regulate the connector for the automotive ethernet protocol. Most used MDI in the automotive world are the H- MTD connector and the Mate-Net ones. There are several solutions for single and multiple male/female connector, all of them has to follow the automotive standards with a CPA connector and has to be waterproof. All compliant connectors have to follow the impedance of the cable and surely assure the datarate of the link connected to them.

### MDI Connectors in Automotive Ethernet

At present, there are no IEEE standards that define a unique connector type for the **100BASE-T1** automotive Ethernet physical layer. Instead, the choice of the **Media Dependent Interface (MDI)** connector is left to manufacturers, provided that the interface ensures compliance with electrical and mechanical requirements defined by the standard and automotive-grade specifications.

Among the most widely used solutions in the automotive market are the **H-MTD** connector, developed by Rosenberger, and the **Mate-Net** connector, developed by TE Connectivity. Both solutions are designed for high-speed differential transmission over a  $100 \Omega$  balanced twisted pair and meet the environmental and mechanical constraints typical of automotive environments, including vibration resistance, humidity protection, and secure locking through **CPA (Connector Position Assurance)** mechanisms.

All compliant connectors must maintain impedance continuity with the transmission line to prevent signal reflections and ensure proper **signal integrity**. They must also

support the data rate required by the physical layer (up to 100 Mbit/s for 100BASE-T1) and, in many cases, are designed with a higher bandwidth margin to support potential reuse for faster protocols (up to several Gbit/s).

Table 2.2: Main characteristics of H-MTD and Mate-Net automotive Ethernet connectors.

| Connector                         | Main Characteristics                                                                                                                                                                                                                                                                    |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>H-MTD (Rosenberger)</b>        | <ul style="list-style-type: none"> <li>• 100 <math>\Omega</math> differential impedance</li> <li>• Frequency range up to 20 GHz</li> <li>• Data rates up to 56 Gb/s</li> <li>• Waterproof design</li> <li>• CPA locking system</li> <li>• Mating cycles <math>\geq 25</math></li> </ul> |

| <b>Mate-Net (TE Connectivity)</b> | <ul style="list-style-type: none"> <li>• Supports up to 6 Gb/s data rate</li> <li>• NanoMQS terminal system</li> <li>• Compact, sealed single-port design</li> <li>• Automotive-grade waterproofing</li> </ul>                                                                          |

In summary, both connectors satisfy the stringent automotive EMC and environmental requirements while preserving the 100  $\Omega$  impedance continuity required by 100BASE-T1 links. The **H-MTD** connector provides higher frequency capabilities and scalability up to multi-gigabit links, making it more suitable for future Ethernet generations (e.g., 2.5GBASE-T1 or 10GBASE-T1). Conversely, the **Mate-Net** connector offers a more compact and cost-efficient solution, ideal for low-to-medium data rate applications such as sensors or control modules.

#### 2.4.7 Echo Cancellation

In full-duplex communication, signals in both directions between two nodes propagate simultaneously over the same 100  $\Omega$  balanced cable. Even though the line ends are terminated with 100  $\Omega$ , signal reflections can still occur due to impedance mismatches or mechanical imperfections in the cable or MDI connector.

To mitigate this, the receiver employs advanced signal reconstruction and filtering techniques, most importantly **echo cancellation**. The echo canceller continuously adapts to the received signal to estimate and remove the transmitter's own reflected signal from the incoming data.

Echo is a key factor limiting the maximum cable length. The canceller must wait for the reflected signal to evaluate its contribution. For example, for a cable of length  $L$  [m], the round-trip propagation delay can be estimated as:

$$\text{Delay [ns]} = 2 \cdot (5 \text{ ns/m} \cdot L \text{ [m]}) \quad (2.1)$$

where the factor 5 ns/m corresponds to the propagation velocity in typical automotive twisted pair cables. For a 15 m cable, the resulting delay is 150 ns, which is also affected by **insertion loss** and other noise sources. If the cable is too long, the echo canceller cannot reliably estimate the reflected signal, increasing the risk of signal degradation and bit errors.

Typical values for automotive Ethernet links, taken from [5], are:

- **Insertion loss:**  $\sim -1.0$  dB, representing the attenuation of signal amplitude along the cable.

- **Return loss:**  $\sim -20$  dB, indicating the fraction of signal reflected back due to impedance discontinuities.

Figure 2.9 illustrates the concept, showing the transmitted signal (TX), the received signal (RX), and the echo component of the transmitter that must be cancelled to preserve signal integrity.

Figure 2.9: Illustration of transmitted (TX) and received (RX) signals including the transmitter's echo, highlighting the role of echo cancellation.

### Data Path and Propagation Delay

The overall **data delay** in a 100BASE-T1 link is the sum of multiple contributions along the transmission path. Distinct delays are observed in the transmit and receive directions, as the received signal must pass through additional processing blocks such as the **echo canceller** and the **equalizer**, which introduce extra latency.

The **reception delay** (path from MDI to MII) typically ranges between 760 ns and 941 ns, depending on the implementation and adaptive filter complexity. Conversely, the **transmission delay** (path from MII to MDI) is lower, varying between 140 ns and 300 ns.

In addition to PHY-internal latency, there is also the **propagation delay** introduced by the physical cable, which can be approximated as 5 ns/m. For the maximum recommended cable length of 15 m, this corresponds to a delay of approximately 75 ns.

Therefore, the overall worst-case propagation time from one node to another can be expressed as:

$$T_{\text{propagation, TX}} = T_{\text{cable}} + T_{\text{PHY, TX path}} = 75 \text{ ns} + 300 \text{ ns} = 375 \text{ ns} \quad (2.2)$$

$$T_{\text{propagation, RX}} = T_{\text{cable}} + T_{\text{PHY, RX path}} = 75 \text{ ns} + 941 \text{ ns} = 1.016 \mu\text{s} \quad (2.3)$$

$$T_{\text{total, worst-case}} = T_{\text{propagation, TX}} + T_{\text{propagation, RX}} = 1.391 \mu\text{s} \quad (2.4)$$

These values highlight that the receive path is inherently slower due to the digital signal processing required for echo cancellation and equalization. Understanding these timing

characteristics is essential for evaluating system-level latency in time-sensitive automotive Ethernet networks.

#### 2.4.8 DC Isolation

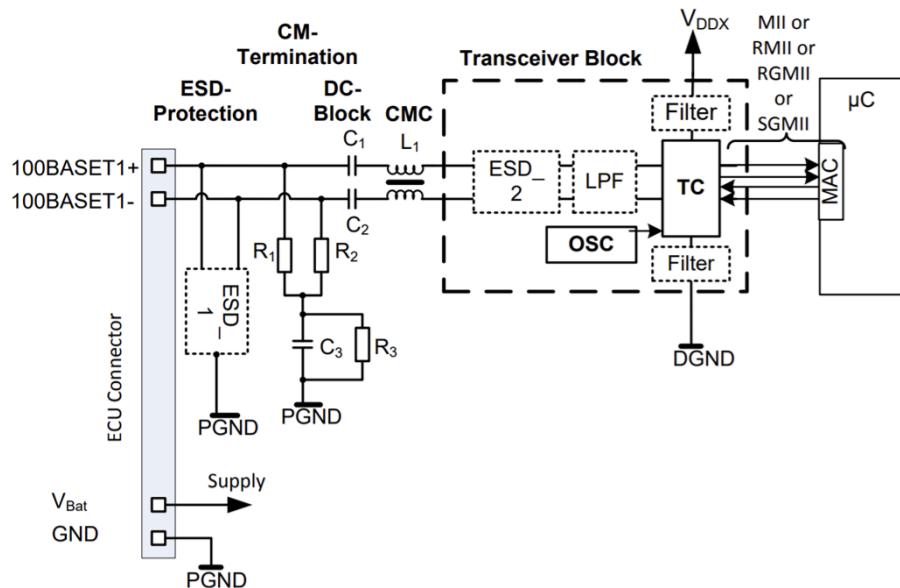

The **ESD protection module** is responsible for safeguarding the transceiver from possible **electrostatic discharges (ESD)** or transient voltages that may be induced through the connected cables. Proper ESD protection is essential to ensure compliance with automotive EMC standards and to guarantee long-term reliability of the physical layer.

Capacitors **C1** and **C2**, each with a value of 100 nF, provide **DC isolation** between the transceiver differential pins and the external line. These capacitors block any DC offset while allowing high-frequency data signals to pass, ensuring the correct AC coupling between the PHY and the cable.

Another key protection element in the interface is the **Common Mode Choke (CMC)**, which filters out **Electromagnetic Interference (EMI)** and suppresses common-mode noise that may affect the data lines. The CMC thereby improves the overall signal integrity and reduces emissions radiated by the link, a critical aspect in the automotive environment.

The resistors **R1** and **R2**, typically 50  $\Omega$  each, ensure a proper impedance matching by providing:

- **50  $\Omega$  single-ended termination** for each signal line.

- **100  $\Omega$  differential termination** for the differential pair.

Accurate termination and impedance matching are fundamental to minimize signal reflections, echo noise, attenuation, and ultimately to prevent data packet loss.

Figure 2.10 shows the typical DC isolation and protection network, as specified by the **OPEN Alliance IEEE 100BASE-T1 System Implementation Specification** [4].

Figure 2.10: Typical DC isolation and protection circuit for 100BASE-T1, including ESD protection, AC coupling capacitors, common-mode choke, and differential termination resistors [4].

### 2.4.9 Fault Tolerances

According to the IEEE 802.3 standard, the **Media Dependent Interface (MDI)** is required to tolerate a variety of electrical stress conditions without sustaining permanent damage. In practice, this means that the twisted-pair lines must withstand short circuits either between the two conductors or between any conductor and ground or supply potentials (up to +50 V DC), with the source current limited to 150 mA, for an indefinite period of time. Once the fault condition is removed, the transceiver must be capable of resuming normal operation without performance degradation.

In addition to short-circuit tolerance, the MDI must also be resilient against high-voltage transient disturbances and **Electrostatic Discharges (ESD)** as defined by the automotive application requirements. These robustness constraints ensure the reliability of the physical layer in harsh environments typical of in-vehicle networks, where frequent transient events can occur due to switching loads, inductive components, or electrostatic coupling through the cable harness.

A further reliability feature of the 100BASE-T1 link is the automatic handling of **polarity inversion**. If the differential pair is connected with reversed polarity, the **slave PHY** automatically detects the condition and compensates it internally by swapping the polarity of its transmitter and receiver paths. This mechanism guarantees that no damage or loss of communication occurs due to incorrect wiring during installation or manufacturing.

Finally, if the link is lost or becomes unstable, the PHY initiates a new **training phase** to re-establish the connection. During this process, the transceivers exchange synchronization patterns to adapt their internal equalization and echo-cancellation filters, restoring a stable communication channel without manual intervention.

## Media Independent Interfaces and PHY Integration

The automotive-Ethernet single-pair physical layer defined by IEEE 802.3 Clause 96 (100BASE-T1) mandates a well-defined interface between the MAC/domain controller and the PHY device. According to the standard, the PHY must support full-duplex communication over a single balanced twisted pair cable and integrate seamlessly with the MAC via a "Media Independent Interface" (MII) or one of its reduced variants. [3]

These specify, for example, that the MAC-PHY interface may be implemented in standard MII, Reduced MII (RMII) or even RGMII modes, as long as the interface meets timing, signalling and EMC constraints of the automotive environment.

**Standard MII** In its classical implementation, the MII interface provides a 4-bit parallel transmit bus (TX[3:0]) synchronized at 25 MHz, a 4-bit receive bus (RX[3:0]), an error signalling line and an enable/strobe line indicating the PHY's readiness to transmit data. This configuration supports 100 Mbit/s throughput when used in conjunction with a PHY compliant to Clause 96.

**Reduced MII (RMII)** To reduce pin-count and simplify PCB routing – a key objective in automotive ECUs – the RMII variant halves the number of data lines by multiplexing signals and uses a faster reference clock (typically 50 MHz). This allows the MAC-PHY connection to maintain the same nominal data rate while optimizing footprint and cost.

**RGMII and other variants** For higher-speed PHYs or more advanced embedded systems, the Reduced Gigabit MII (RGMII) is often supported. Although not strictly required

for 100BASE-T1, many PHYs intended for automotive networking include RGMII in order to support future scalability (for example 1000BASE-T1). Automotive PHYs provide “xMII flexibility” supporting MII, RMII, RGMII, SGMII and others. [5]

#### 2.4.10 Basic node Setup Review

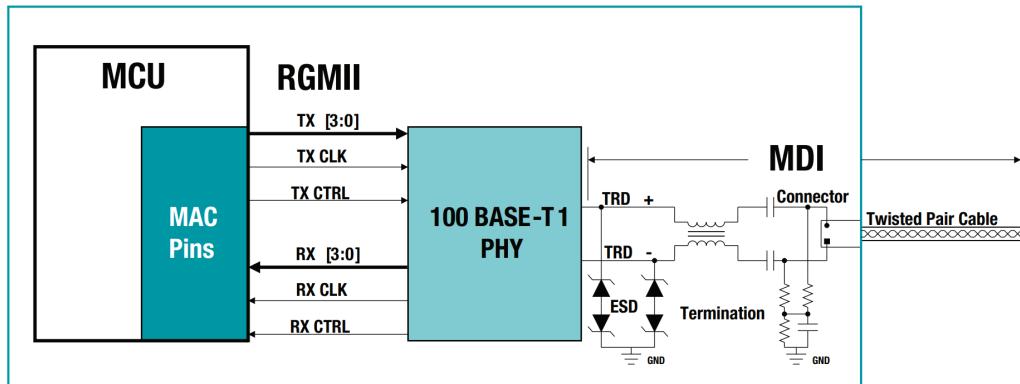

The basic architecture of a 100BASE-T1 node consists of a **Physical Layer (PHY)** device responsible for transmitting and receiving data over the differential pair, and a **Microcontroller Unit (MCU)** or **MAC controller** managing higher-level protocol functions. The communication between these two subsystems is implemented through a **Media Independent Interface (MII)**, which ensures a standardized data exchange between the digital MAC domain and the analog physical medium.

The standard MII defines a 4-bit parallel data bus (TX[3:0]) synchronized with a 25 MHz clock, complemented by control lines for transmission enable and error indication. A symmetric structure is used for reception through the RX[3:0] bus. This interface supports a theoretical data rate of 100 Mbit/s, corresponding to a 25 MHz data clock and 4-bit word width.

Inside the transceiver, the transmitted data undergoes a series of signal processing stages. The 4-bit nibbles are first converted into 3-bit symbols and serialized at an internal clock rate of approximately 33 MHz, preserving the overall throughput of 100 Mbit/s. The data stream is then **encoded using ternary signaling** and transmitted over the differential link with three voltage levels  $\{-1, 0, +1\}$ , resulting in a peak-to-peak amplitude below 2.2 V.

On the receiving side, the PHY performs **echo cancellation**, **equalization**, and **clock recovery** to reconstruct the transmitted signal while compensating for channel losses, impedance mismatches, and reflections along the twisted pair. These operations are essential to ensure signal integrity and compliance with the stringent electromagnetic and timing requirements of automotive environments.

A high-level representation of the complete physical layer architecture, from the MAC interface to the MDI and cable connection, is shown in Figure 2.11, adapted from the Texas Instruments 100BASE-T1 implementation guide [?].

Figure 2.11: Overview of the 100BASE-T1 physical layer architecture, showing the interconnection between MAC, MII, PHY, MDI, and the differential cable link (adapted from [5]).

## 2.5 100BASE-T1 Logical Link Control Layer

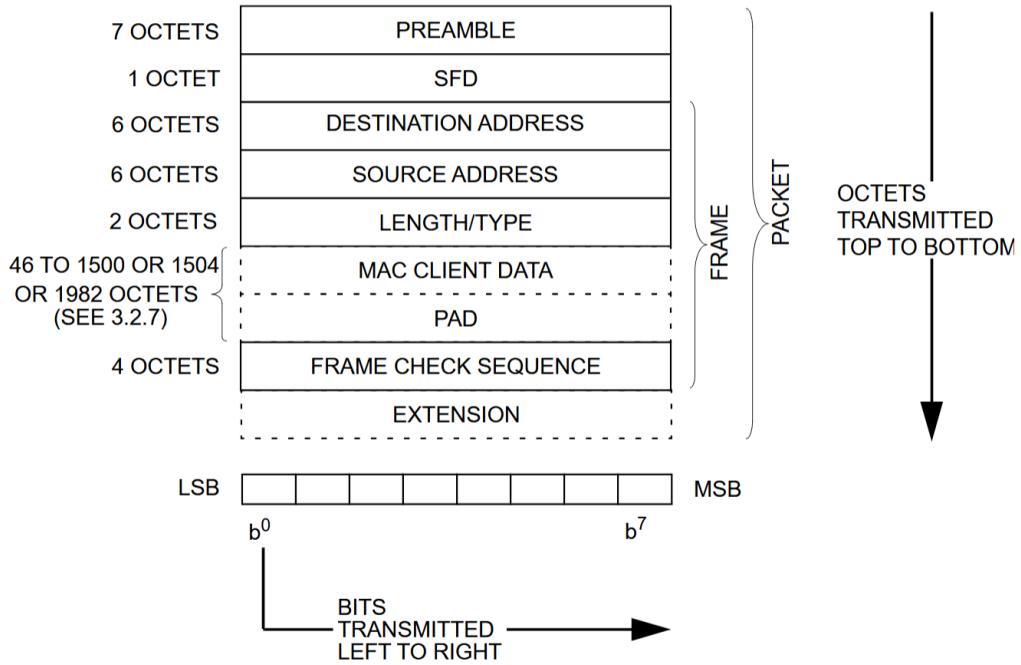

The *Data Link Layer (DLL)* is responsible for the framing, transmission, and reception of data packets over the physical medium. It acts as an intermediary between the Network Layer and the Physical Layer, ensuring that data units are properly encapsulated and synchronized for reliable communication.

According to the IEEE 802.3 standard, the Data Link Layer is subdivided into two functional sublayers:

- **Media Access Control (MAC):** manages access to the shared physical medium and defines the rules for frame transmission and reception. It appends addressing information (MAC addresses) and error detection codes to the frame, coordinating the communication timing with the underlying physical interface.

- **Logical Link Control (LLC):** provides the interface between the Data Link Layer and the Network Layer. It handles frame delimitation, flow control, and logical addressing for upper-layer protocols. In automotive Ethernet implementations, the LLC typically offers minimal overhead, as the protocol is designed to maximize throughput and minimize latency, without performing retransmission or error recovery mechanisms.

Figure 2.12: Placement of 100BASE-T1 within the ISO/OSI communication model.

In the following sections, the fundamental characteristics and functionalities of these two sublayers are described in detail, emphasizing their role in the implementation of the 100BASE-T1 communication protocol.

### Communication primitives

The Ethernet concept of point-to-point communication means that the every station can only talk and send message to the master/slave end point connected to the other end of the link. The task of handling routing and adding destination addresses is entrusted to the upper Network IP layer. MAC has 2 primitives which can be used to communicate with the lower physical layer and signaling a reception of a message or request to send one: