POLITECNICO DI TORINO

Master degree course in Computer Engineering

Master Degree Thesis

# Optimization of Spiking Neural Networks execution on low-power microcontrollers

## Advisors

Prof. Gianvito Urgese

Dr. Andrea Pignata

Dr. Vittorio Fra

## Candidate

Simone Delvecchio

December 2025

# Abstract

The rapid proliferation of AI has prompted researchers to direct significant attention towards the development of novel and innovative solutions that optimise its performance and power consumption. Spiking Neural Networks (SNN) represent a particular type of neural network that emulates the behaviour of the biological brain to enhance neural computation. This results in advantages such as low-power consumption, effective memory-processing colocation, and event-driven execution.

The potential benefits of neuromorphic computing could be realised through the utilisation of optimised neuromorphic hardware, such as SpiNNaker 2 and Intel Loihi 2. However, these accelerators are difficult to obtain and often expensive due to their experimental nature.

The present work investigates a potential solution to be implemented on microcontroller units (MCUs) to run SNN in small and low-power systems. To this end, SNN models are deployed leveraging HW modules such as DSP and memory access accelerators, available in the target architectures.

The development focused on reproducing Leaky-Integrate and Fire (LIF) and Izhikevich neurons, implementing fully-connected, one-by-one, and recurrent connectivity. This effort led to the implementation of the `snn2mcu` C library which currently supports two neuron models, three connectivity patterns, and two target MCUs.

The first target of the `snn2mcu` library is the general-purpose ARM Cortex M7 core from STMicroelectronics. Quantization has been implemented converting floating point network parameters to fixed-point data types compatible with the ARM DSP library (CMSIS) that provides an optimised implementation of common math operations and vectorised functions. The second target is the open source GAP8 architecture with Risc-V processors. Optimization have been implemented by exploiting the multi-level memory layout and the multiple cores available in the system.

`snn2mcu` also supports SNNs described with the Neuromorphic Intermediate Representation (NIR) framework. An automatic tool has been designed to generate optimized firmware starting from the high level NIR description of the SNN, thus removing the need for manual coding and facilitating development on embedded systems.

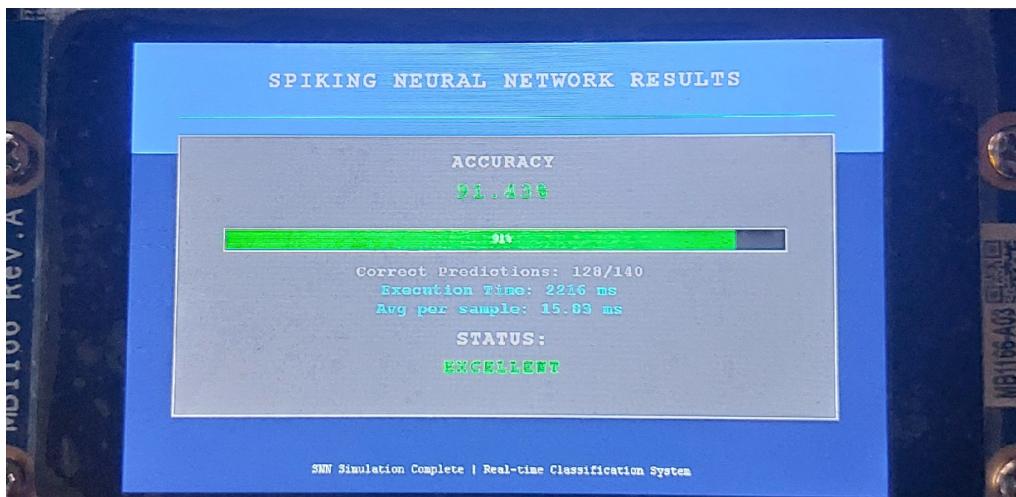

To evaluate the usability of the library, two SNN models were deployed on the GAP 8 and ARM core. The first is a SNN designed to classify seven Braille characters using input spikes from a robotic finger that produces twelve signal channels. The second is a classifier for handwritten numbers taken from the MNIST dataset. The Braille SNN model on the ST-ARM was executed 6x faster than floating point SNN simulators achieving the same accuracy of 91.43% over a 140-sample test dataset. The second model achieved an average energy consumed per sample of 10.54 mJ and an execution time of 187.82 ms per sample, and power consumption in line with a specific optimised FPGA design. In summary, the present work demonstrates that the utilisation of optimisation techniques, such as fixed-point mathematics with reduced bit-depth, DSP vectorised functions, multilevel cache, and code efficiency, can enable an effective deployment of SNNs on a wide variety of commercial grade MCUs.

# Contents

|                                                                      |    |

|----------------------------------------------------------------------|----|

| <b>List of Figures</b>                                               | 7  |

| <b>List of Tables</b>                                                | 9  |

| <b>1 Introduction</b>                                                | 11 |

| <b>2 Background</b>                                                  | 15 |

| 2.1 SNN: overview and neuromorphic computing over the Edge . . . . . | 15 |

| 2.2 Use cases of SNNs . . . . .                                      | 19 |

| 2.2.1 Neu-BrAuER . . . . .                                           | 20 |

| 2.2.2 SNN-based HAR on Commercial Edge devices . . . . .             | 21 |

| 2.3 HW designed for neuromorphic applications . . . . .              | 22 |

| 2.3.1 Spinnaker 2 . . . . .                                          | 22 |

| 2.3.2 Intel Loihi 2 . . . . .                                        | 23 |

| 2.4 Frameworks to develop SNNs . . . . .                             | 24 |

| 2.4.1 snnTorch . . . . .                                             | 24 |

| 2.4.2 Neuromorphic Intermediate Representation . . . . .             | 25 |

| 2.5 Analysis of low power HW . . . . .                               | 26 |

| 2.5.1 STM32H757I-EVAL . . . . .                                      | 26 |

| 2.5.2 GAP-8 . . . . .                                                | 30 |

| 2.6 Tools to support NN at the Edge . . . . .                        | 32 |

| 2.6.1 PULP-NN . . . . .                                              | 32 |

| 2.6.2 ST Edge AI Core . . . . .                                      | 33 |

| 2.7 SNNs for widely available HW platforms . . . . .                 | 34 |

| 2.7.1 Spiker+ . . . . .                                              | 34 |

| 2.7.2 SNN decoder for Implantable Brain Machine Interfaces . . . . . | 35 |

| 2.8 Proposed solution . . . . .                                      | 36 |

| <b>3 Materials and methods</b>                                       | 39 |

| 3.1 SNN Model Architecture . . . . .                                 | 39 |

| 3.1.1 The model and its purpose . . . . .                            | 39 |

| 3.1.2 LIF neuron structure . . . . .                                 | 40 |

|                     |                                                           |           |

|---------------------|-----------------------------------------------------------|-----------|

| 3.2                 | SNNTorch Implementation . . . . .                         | 42        |

| 3.2.1               | Training and Validation of the model . . . . .            | 42        |

| 3.3                 | SNN for ST Board (snn2mcu) . . . . .                      | 44        |

| 3.3.1               | Initialisation of the environment . . . . .               | 44        |

| 3.3.2               | SNN execution and optimisations . . . . .                 | 45        |

| 3.3.3               | LCD implementation . . . . .                              | 48        |

| 3.4                 | Izhikevich on ST Board . . . . .                          | 49        |

| 3.4.1               | Izhikevich neuron model . . . . .                         | 49        |

| 3.4.2               | Izhikevich for ST Board . . . . .                         | 50        |

| 3.5                 | SNN for GAP8 processor . . . . .                          | 51        |

| 3.5.1               | Program flow and Implementation . . . . .                 | 51        |

| 3.6                 | NIR-to-C translator . . . . .                             | 54        |

| 3.6.1               | From SNNTorch to NIR . . . . .                            | 54        |

| 3.6.2               | From NIR to C . . . . .                                   | 55        |

| 3.7                 | Used tools . . . . .                                      | 57        |

| <b>4</b>            | <b>Results and discussion</b>                             | <b>59</b> |

| 4.1                 | Braille Model Results . . . . .                           | 59        |

| 4.1.1               | LIF neuron Behaviour: snnTorch VS Board . . . . .         | 59        |

| 4.1.2               | ds_test across different platforms . . . . .              | 63        |

| 4.2                 | MNIST Benchmark using Spiker+ and NIR generator . . . . . | 70        |

| 4.2.1               | Spiker+ SNN description and training . . . . .            | 70        |

| 4.2.2               | extract_nir and translation to C . . . . .                | 71        |

| 4.2.3               | Benchmark over ST Board . . . . .                         | 72        |

| 4.2.4               | Comparison against FPGA . . . . .                         | 75        |

| <b>5</b>            | <b>Conclusion</b>                                         | <b>77</b> |

| 5.1                 | Validation and Performance Analysis . . . . .             | 78        |

| 5.2                 | Challenges and Limitations . . . . .                      | 79        |

| 5.3                 | Future Research Directions . . . . .                      | 79        |

| 5.4                 | Final Reflections . . . . .                               | 80        |

| <b>A</b>            | <b>Inference Results tables</b>                           | <b>83</b> |

| <b>Bibliography</b> |                                                           | <b>89</b> |

# List of Figures

|      |                                                                                                                     |    |

|------|---------------------------------------------------------------------------------------------------------------------|----|

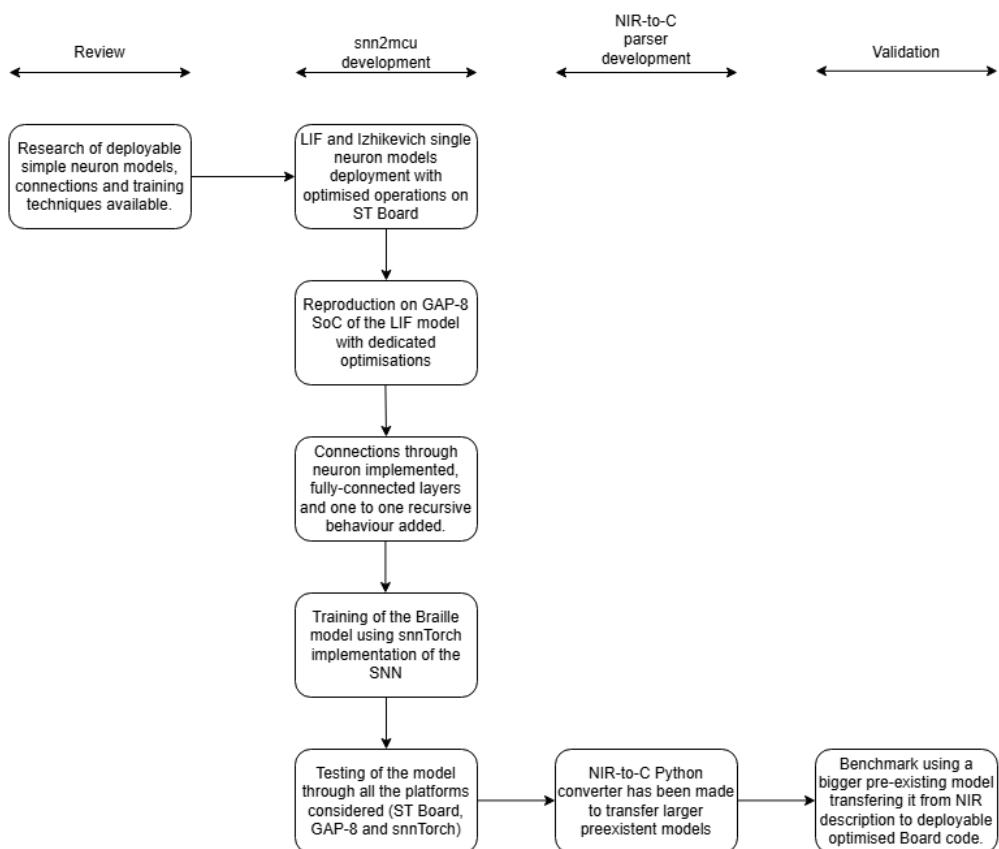

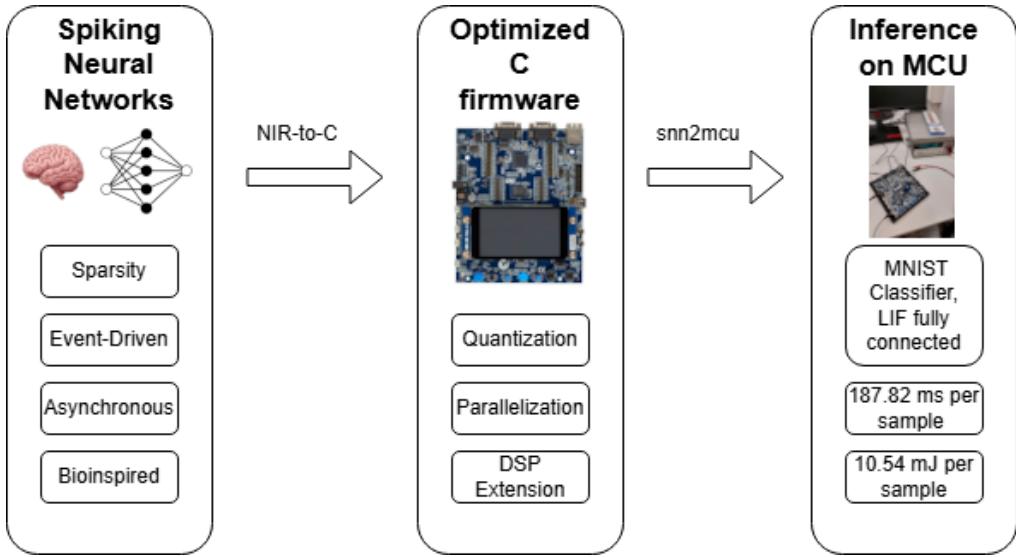

| 1.1  | Workflow followed for the thesis . . . . .                                                                          | 13 |

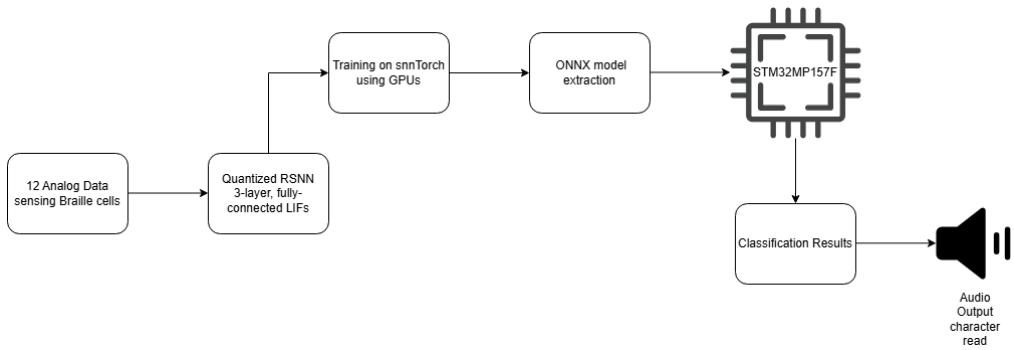

| 2.1  | Workflow of Neu-BrAuER development . . . . .                                                                        | 20 |

| 2.2  | STM32H757I-EVAL ST Board . . . . .                                                                                  | 28 |

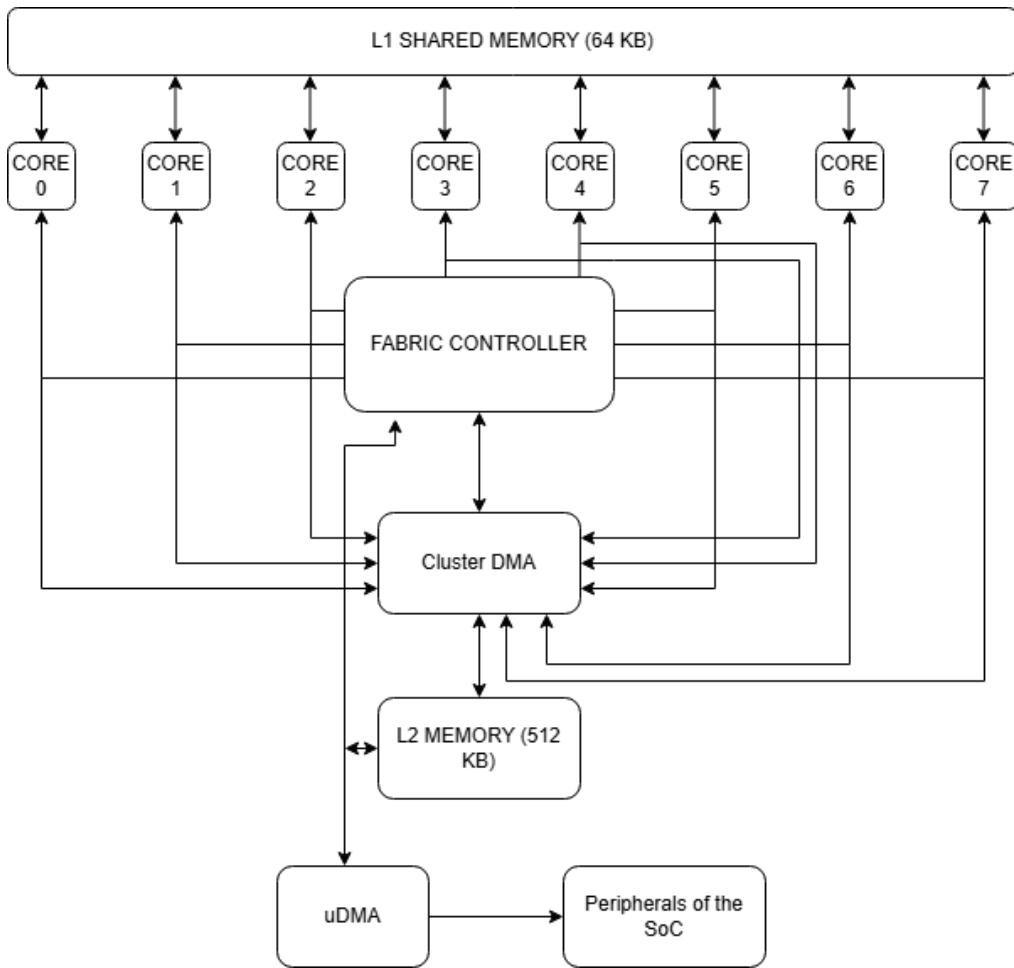

| 2.3  | GAP-8 structure scheme . . . . .                                                                                    | 31 |

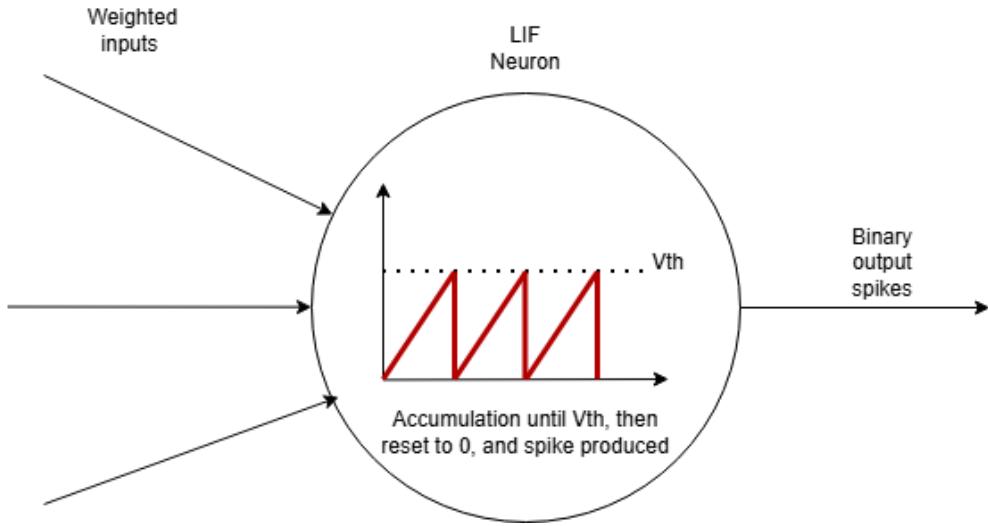

| 3.1  | LIF Behaviour scheme. . . . .                                                                                       | 42 |

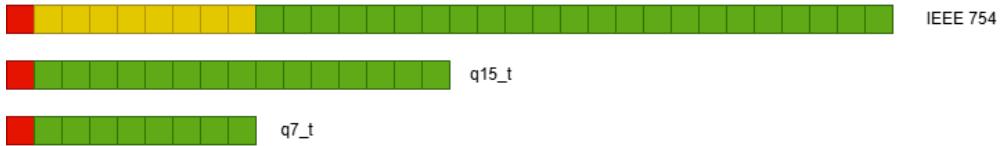

| 3.2  | Comparing data types, standard, fixed q15 and fixed q8. Red is sign, Yellow is exponent, Green is mantissa. . . . . | 46 |

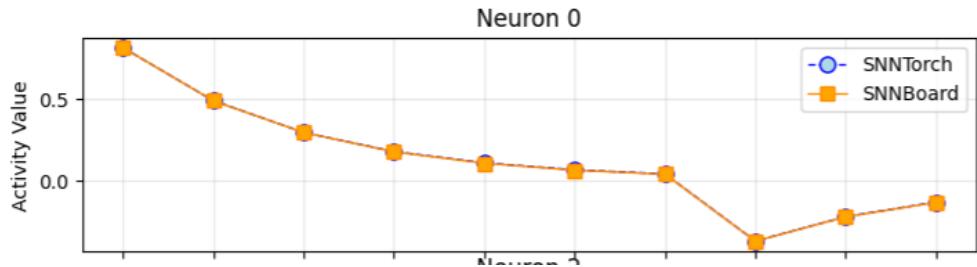

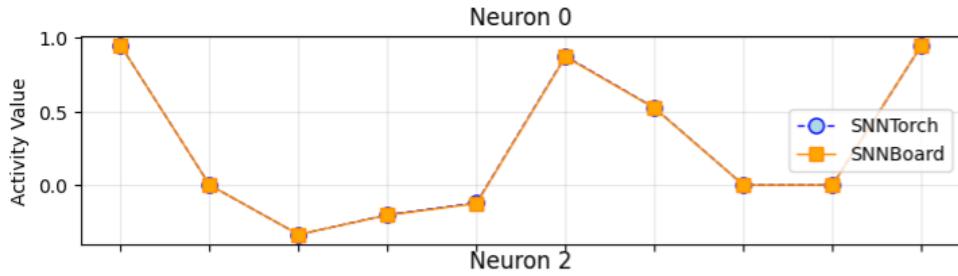

| 4.1  | N0 behaviour for Input1 pattern across the timesteps. . . . .                                                       | 60 |

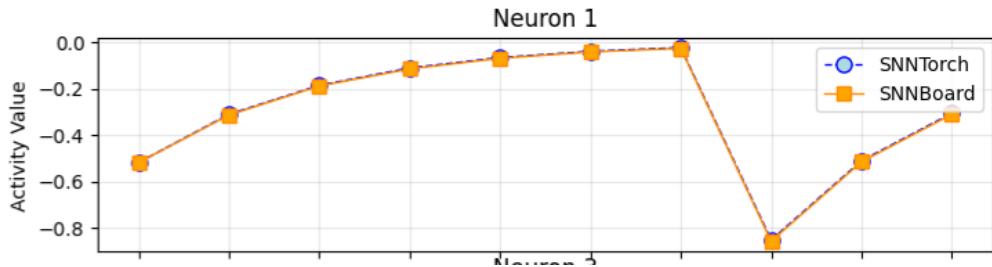

| 4.2  | N1 behaviour for Input1 pattern across the timesteps. . . . .                                                       | 60 |

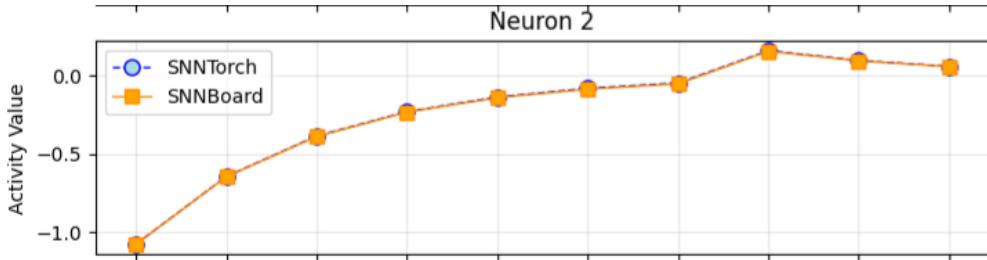

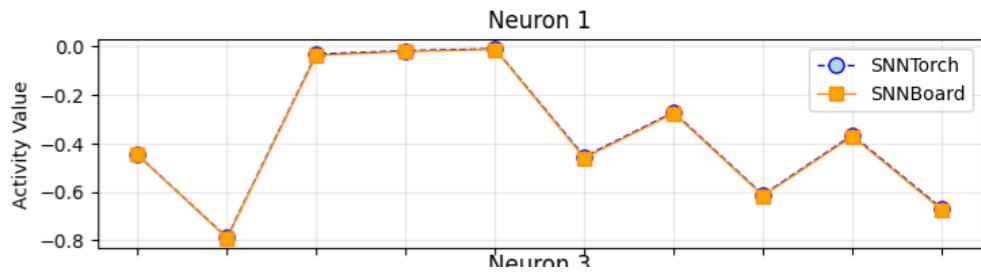

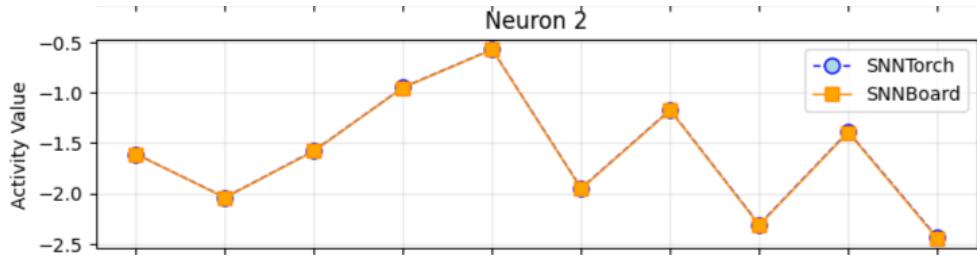

| 4.3  | N2 behaviour for Input1 pattern across the timesteps. . . . .                                                       | 61 |

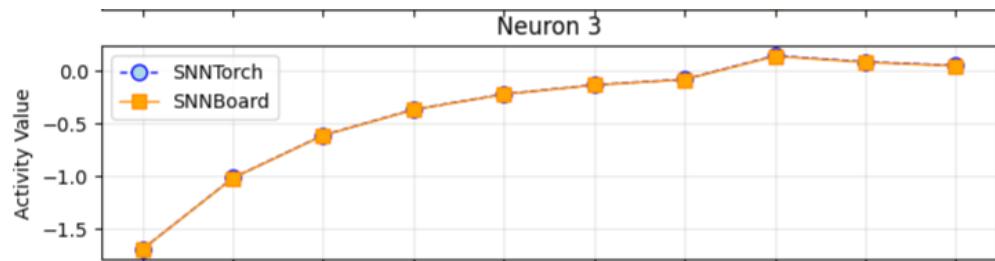

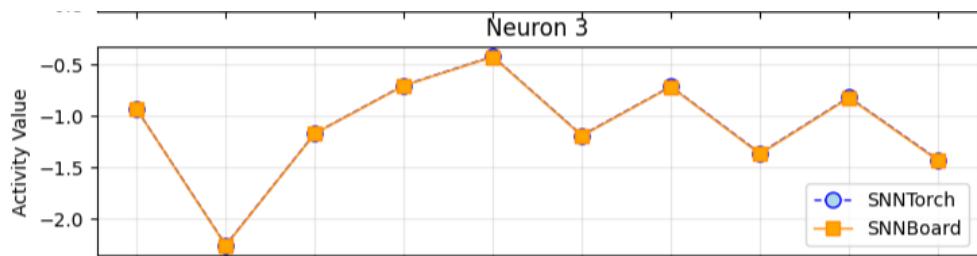

| 4.4  | N3 behaviour for Input1 pattern across the timesteps. . . . .                                                       | 61 |

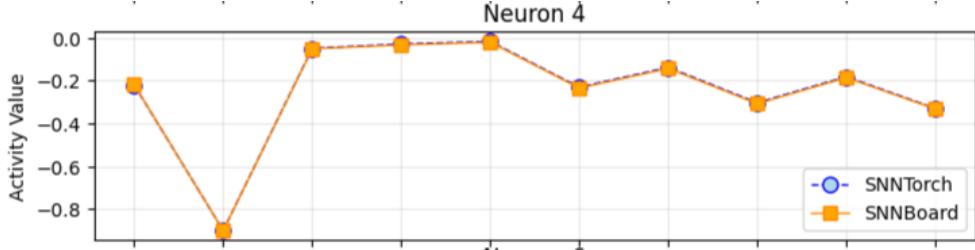

| 4.5  | N4 behaviour for Input1 pattern across the timesteps. . . . .                                                       | 61 |

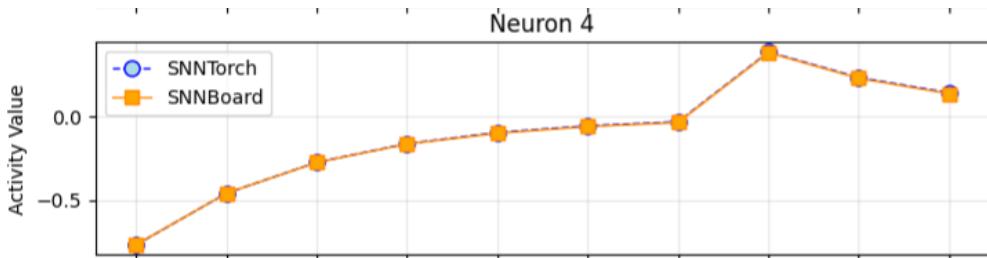

| 4.6  | N5 behaviour for Input1 pattern across the timesteps. . . . .                                                       | 61 |

| 4.7  | N6 behaviour for Input1 pattern across the timesteps. . . . .                                                       | 62 |

| 4.8  | N0 behaviour for Input2 pattern across the timesteps. . . . .                                                       | 63 |

| 4.9  | N1 behaviour for Input2 pattern across the timesteps. . . . .                                                       | 63 |

| 4.10 | N2 behaviour for Input2 pattern across the timesteps. . . . .                                                       | 63 |

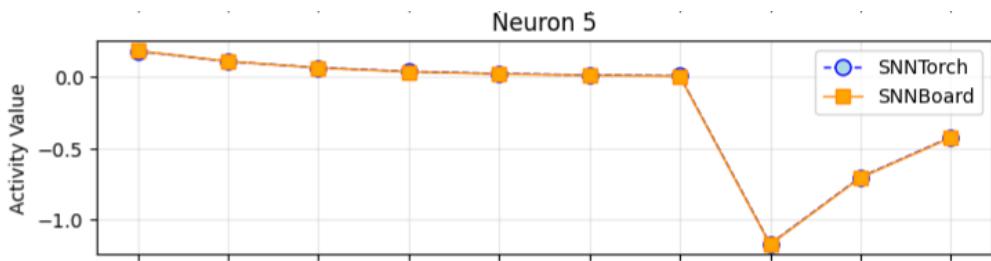

| 4.11 | N3 behaviour for Input2 pattern across the timesteps. . . . .                                                       | 63 |

| 4.12 | N4 behaviour for Input2 pattern across the timesteps. . . . .                                                       | 64 |

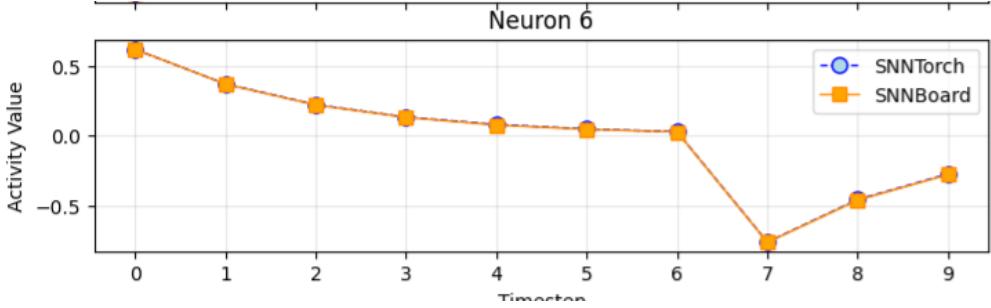

| 4.13 | N5 behaviour for Input2 pattern across the timesteps. . . . .                                                       | 64 |

| 4.14 | N6 behaviour for Input2 pattern across the timesteps. . . . .                                                       | 64 |

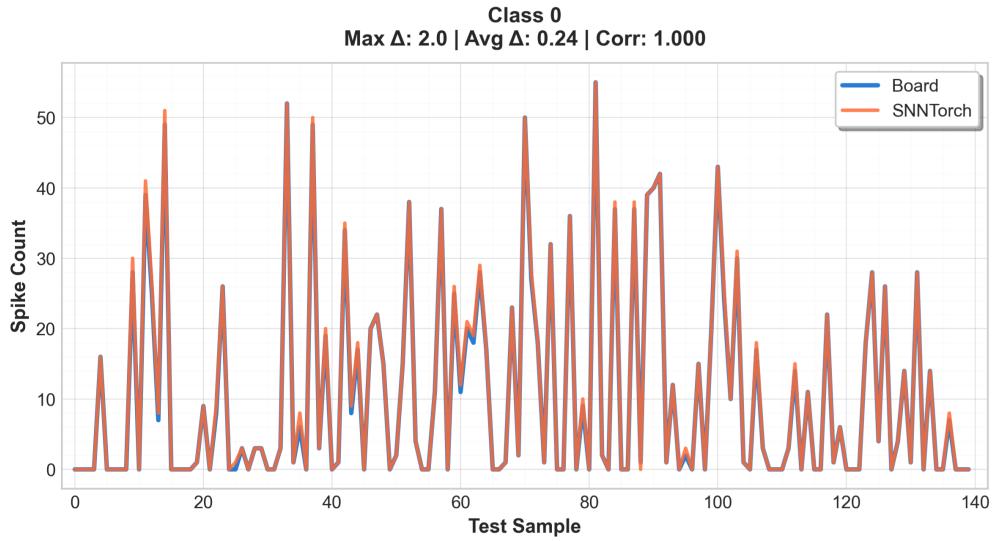

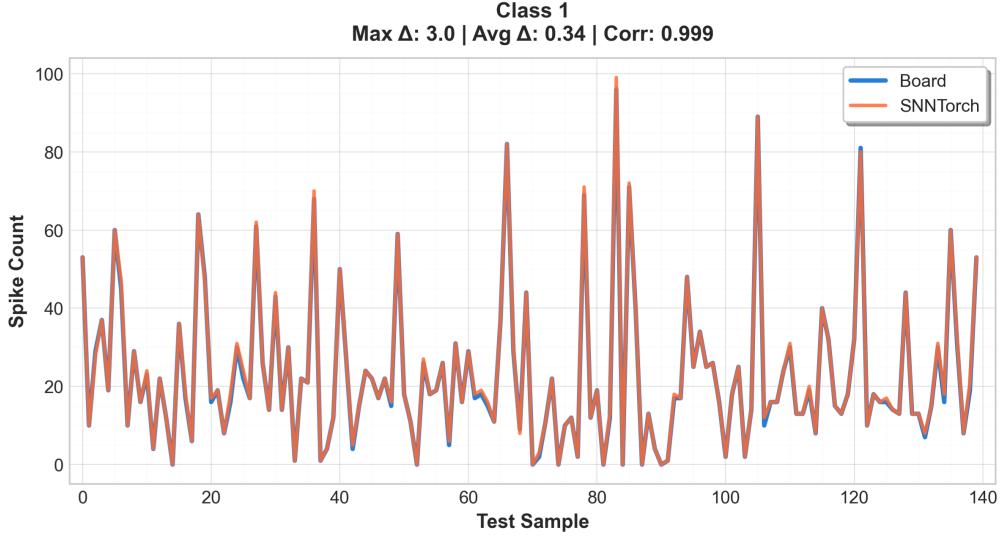

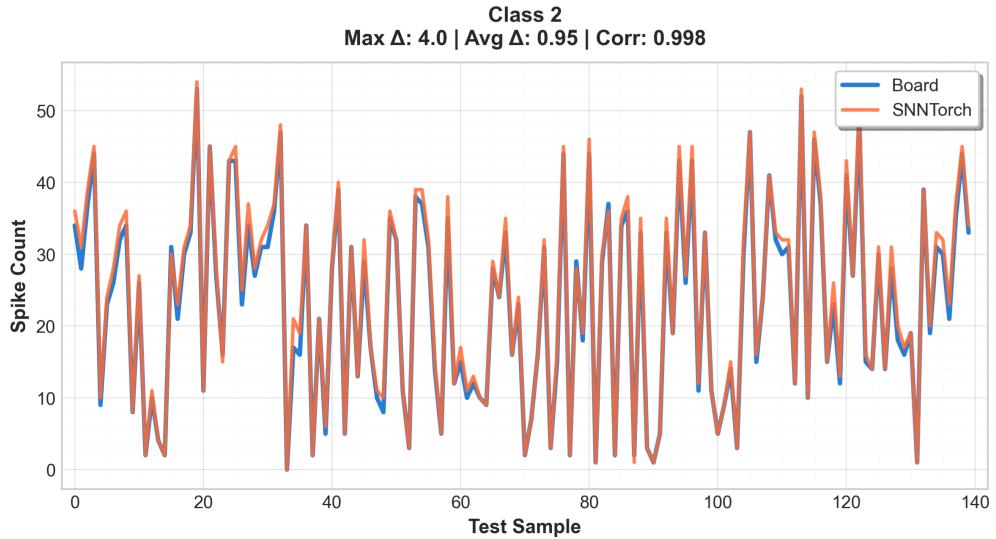

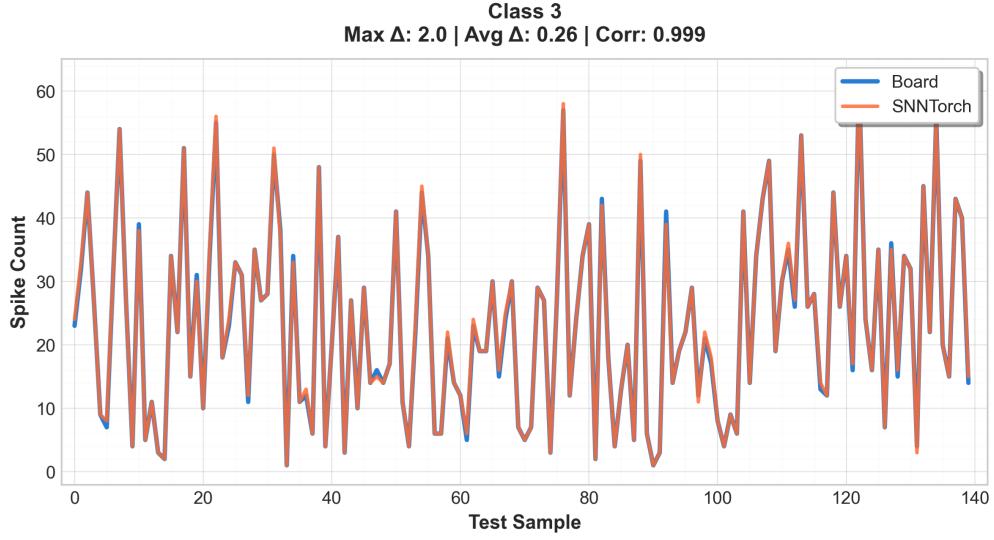

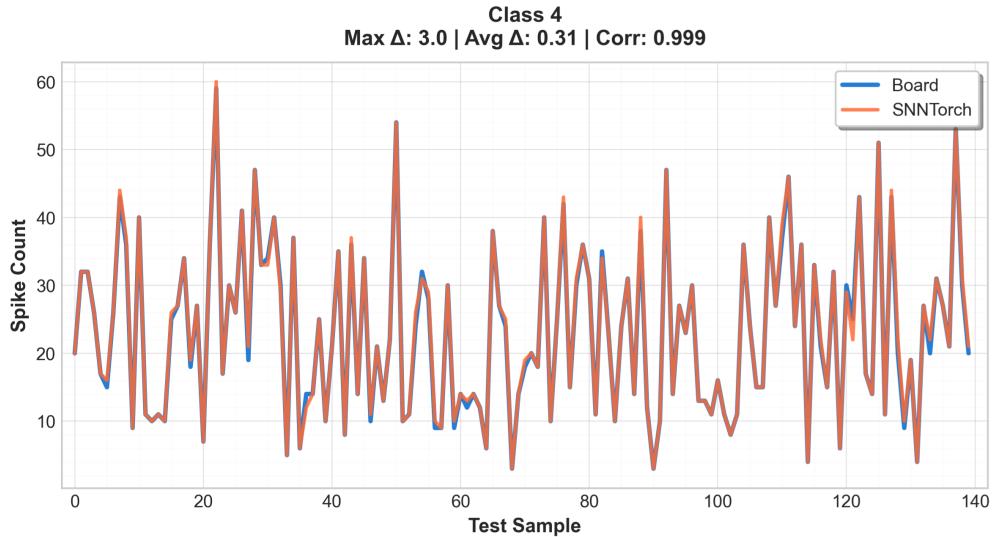

| 4.15 | N0 spike accumulation ds_test . . . . .                                                                             | 65 |

| 4.16 | N1 spike accumulation ds_test . . . . .                                                                             | 66 |

| 4.17 | N2 spike accumulation ds_test . . . . .                                                                             | 66 |

| 4.18 | N3 spike accumulation ds_test . . . . .                                                                             | 67 |

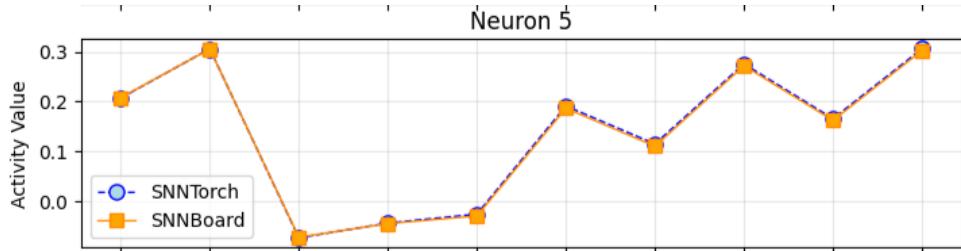

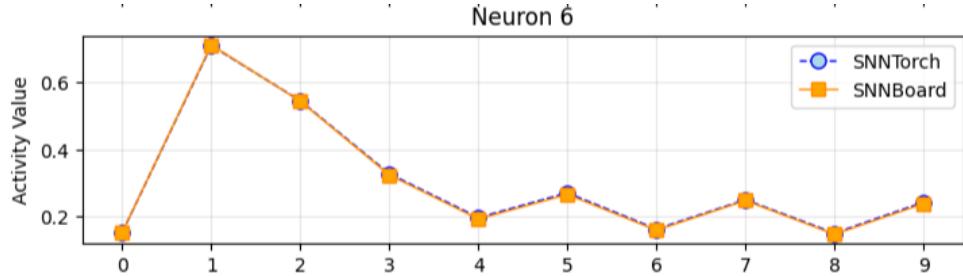

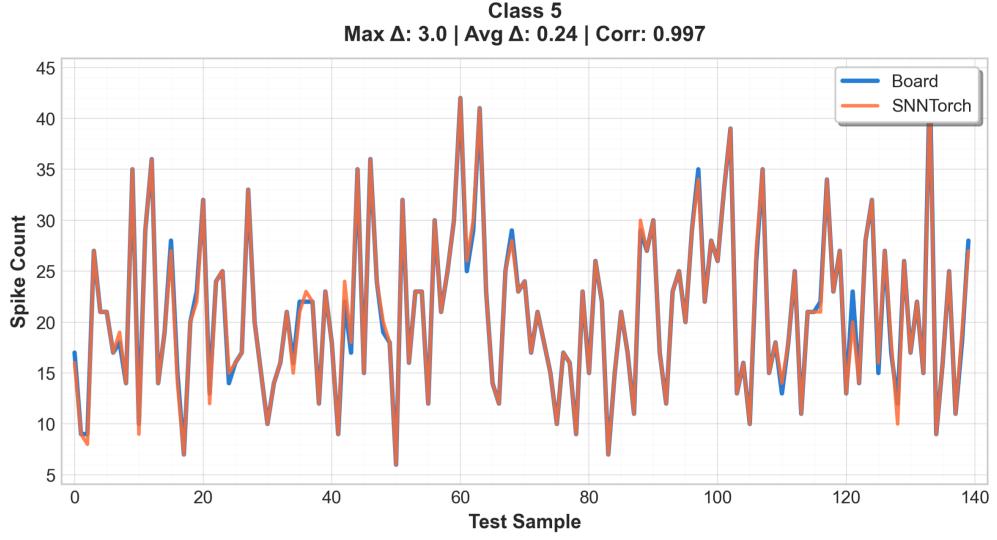

| 4.19 | N4 spike accumulation ds_test . . . . .                                                                             | 67 |

| 4.20 | N5 spike accumulation ds_test . . . . .                                                                             | 68 |

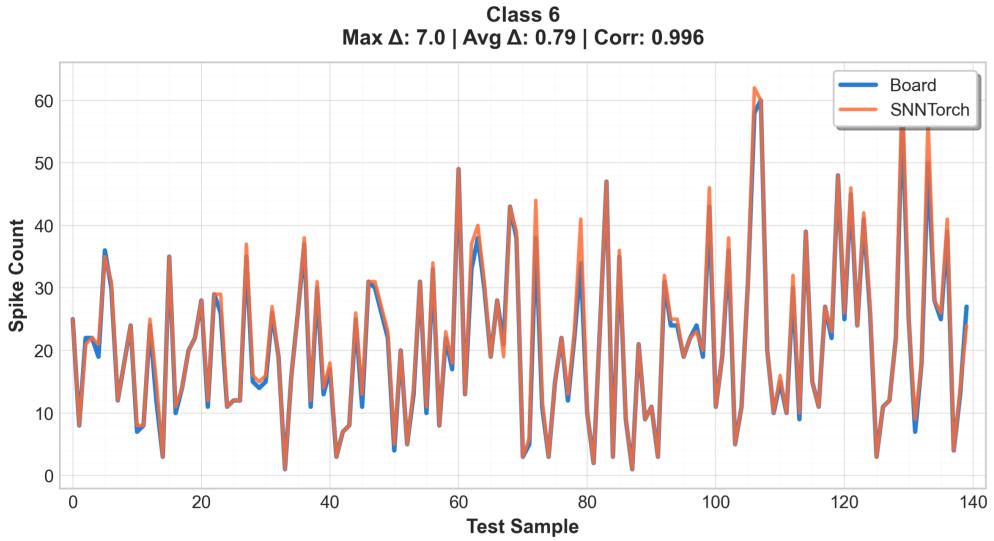

| 4.21 | N6 spike accumulation ds_test . . . . .                                                                             | 68 |

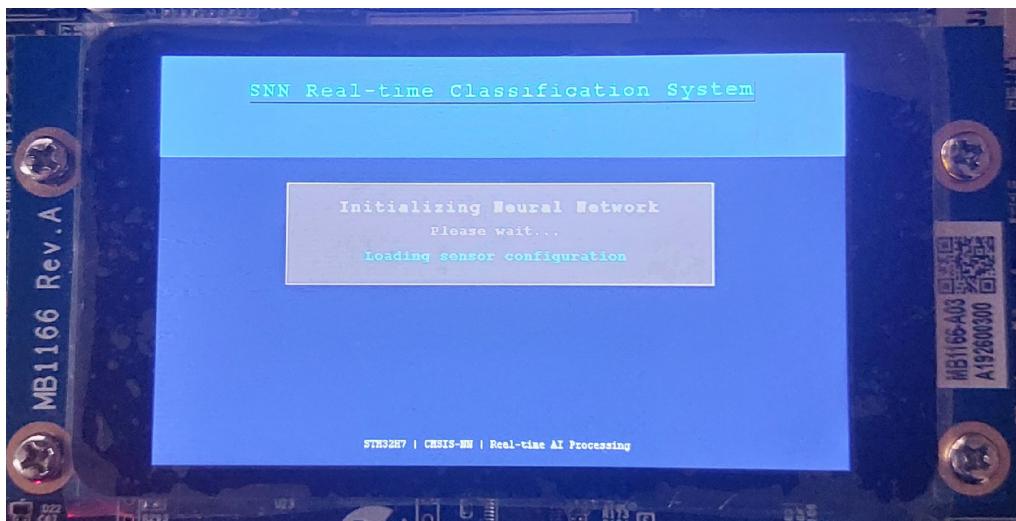

| 4.22 | Startup screen LCD . . . . .                                                                                        | 69 |

| 4.23 | Results over LCD . . . . .                                                                                          | 69 |

|      |                                                                |    |

|------|----------------------------------------------------------------|----|

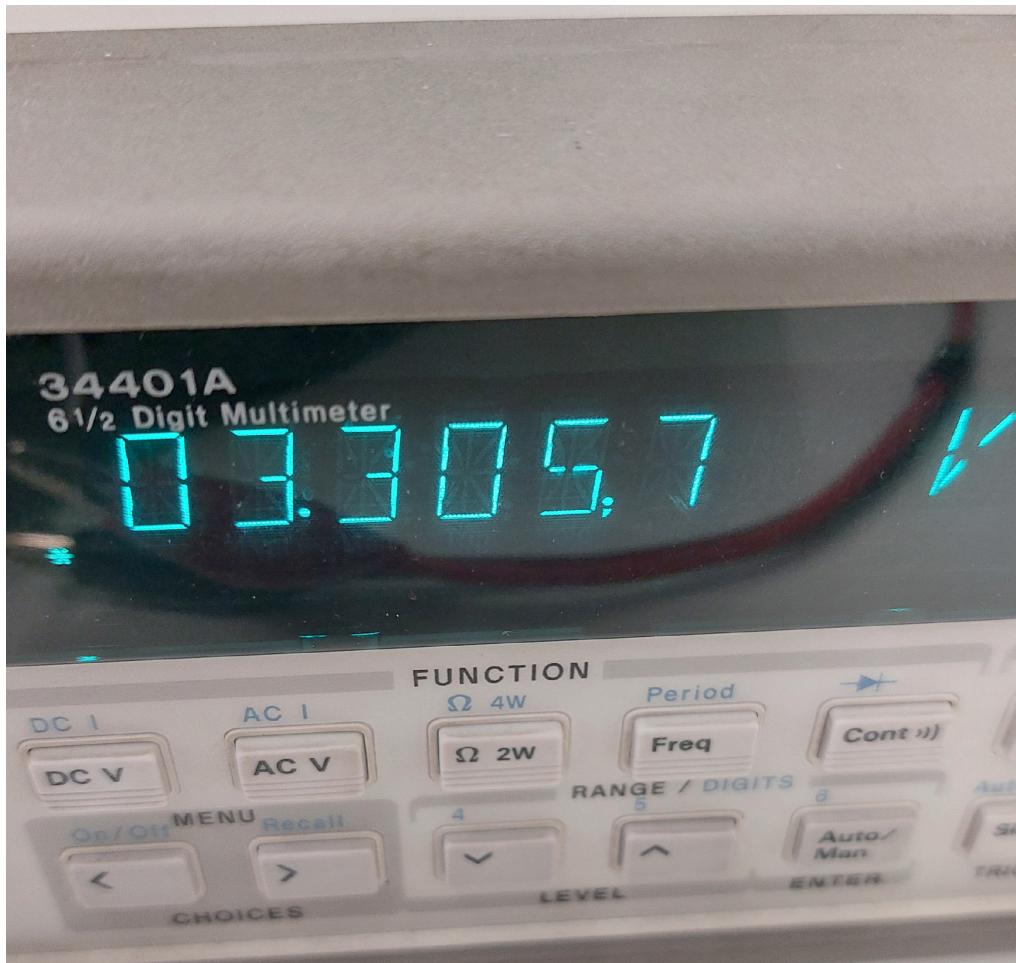

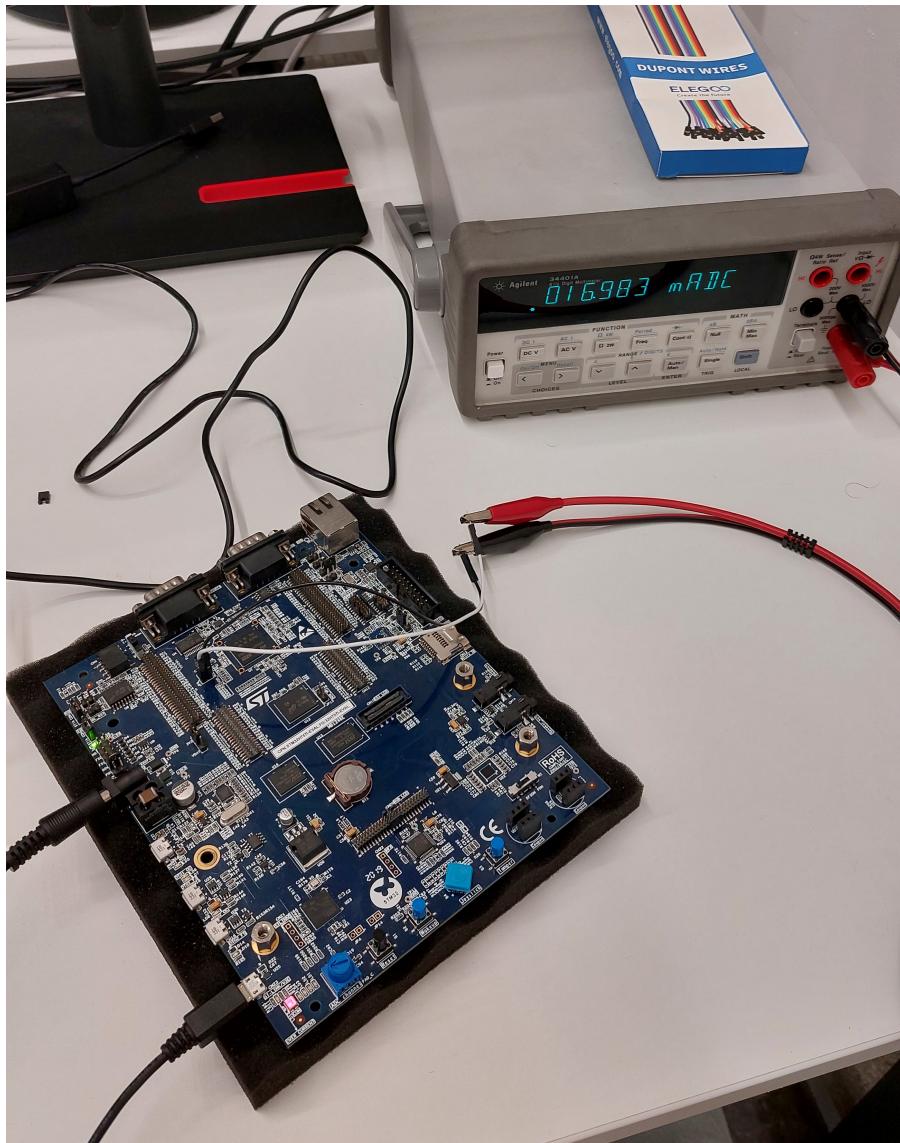

| 4.24 | Tension of the board while executing. . . . .                  | 73 |

| 4.25 | One sample of the current value when executing MNIST . . . . . | 74 |

| 4.26 | Output UART MNIST classifier . . . . .                         | 74 |

| 5.1  | Summary of the complete System . . . . .                       | 78 |

# List of Tables

|     |                                                                                                              |    |

|-----|--------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Input1 Pattern Across Timesteps (Neurons 0 to 11) . . . . .                                                  | 60 |

| 4.2 | Input2 Pattern Across Timesteps (Neurons 0 to 11) . . . . .                                                  | 62 |

| 4.3 | Comparison of snn2mcu and spiker+ . . . . .                                                                  | 75 |

| A.1 | 140 sample ds_test, T stands for snnTorch, B for ST Board, and G for GAP8 SoC. More details in 4.1 . . . . . | 86 |

# Chapter 1

## Introduction

The rapid diffusion of artificial intelligence into everyday devices has created a strong demand for solutions that can run sophisticated models directly on low-power, resource-constrained hardware at the edge, such as microcontroller-based boards and small system-on-chip platforms. Traditional deep neural networks are typically executed on GPUs, high-end CPUs, or specialised accelerators, making them very difficult to integrate into embedded systems that must operate with strict limits on energy, memory, and real-time responsiveness. Neuromorphic computing and, in particular, Spiking Neural Networks(SNNs) offer a compelling alternative because they model information processing using discrete spikes and event-driven dynamics, enabling sparse activity, local state, and a natural fit for low-power, always-on sensing tasks. However, bridging the gap between advanced neuromorphic models and widely available microcontrollers remains challenging due to the lack of dedicated hardware support and standard, reusable software workflows.

Current approaches to neuromorphic computing have largely focused on specialised hardware platforms such as SpiNNaker 2 and Intel Loihi 2, which integrate custom accelerators, advanced memory hierarchies, and event-driven architectures to execute SNNs with high efficiency. These platforms demonstrate excellent performance and energy efficiency but are often expensive, hard to access, and not suitable for large-scale deployment in commercial embedded products. At the same time, software frameworks such as snnTorch and the Neuromorphic Intermediate Representation (NIR) have significantly simplified the design, training, and representation of SNN models at a high level, but they do not natively provide optimised, turnkey support for deployment on generic low-power microcontrollers. Other edge-oriented toolchains, like PULP-NN for GAP-based SoCs and ST Edge AI Core for STM32 devices, strongly optimise classical quantised neural networks yet offer little or no direct support for SNN-specific primitives and spike-based execution. As a result, there is a clear gap between high-level SNN research tooling and practical, reusable workflows for deploying SNNs on common MCU platforms such as ARM Cortex-M7 and RISC-V based systems like GAP-8.

This thesis addresses that gap by proposing and implementing a complete workflow and software library for executing SNNs on low-power microcontrollers using only widely available hardware and open or standardised software components. The work centres on the design and deployment of the `snn2mcu` C library, which supports two neuron models, Leaky-Integrate-and-Fire (LIF) and Izhikevich neurons, and multiple connectivity patterns, such as fully connected, recurrent, and one-by-one topologies, targeting both ARM Cortex-M7 based STM32H757I-EVAL board and the GAP-8 RISC-V SoC. High-level SNNs are first designed and trained in Python using `snnTorch`; then, through a quantisation and optimisation process, they are translated into efficient fixed-point implementations that exploit DSP extensions, vectorised arithmetic, and multi-level memory structures available on the target MCUs. The library is further made compatible with NIR, so that SNN models described in NIR can be automatically converted into optimised embedded code, enabling a hardware-agnostic, reproducible pipeline from research prototypes to deployable firmware. The methodology is validated using two representative case studies: a Braille tactile classifier and a handwritten digit classifier based on MNIST, demonstrating that commercial MCUs can achieve accuracy and energy efficiency comparable to more specialised solutions when properly optimised.

The methodology followed to develop this system is briefly described as follows:

- **Research and analysis:** A review of all the tools used has been conducted, including common SNN models, neuron dynamics, training strategies, and state-of-the-art neuromorphic hardware and frameworks. This was done to identify gaps in SNN support on widely available MCUs.

- **Single-neuron modelling:** The neuron equations are then replicated in hardware platforms using smart quantisation and optimised operations. The LIF neuron dynamics and Izhikevich implementation are adapted for fixed-point arithmetic.

- **Single-network implementation:** Trials have been conducted on very small networks, and the Braille classifier has been reproduced on both the ST Board and the GAP-8 SoC, with validation against the `snnTorch` reference simulations.

- **NIR-to-C parser:** A translator has been developed that converts SNNs described in NIR into the corresponding C code and headers, which are compatible with `snn2mcu` and, in particular, the ST Board.

- **Parser benchmarking on a real use case:** Ultimately, the parser was evaluated using a real-world SNN. In this case, it was a MNIST model that was generated using pre-existing tools: Spiker + combined with the NIR exporter. Correctness checks were performed, and the execution time and energy per inference were benchmarked on the ST Board.

Figure 1.1: Workflow followed for the thesis

# Chapter 2

## Background

One of the most challenging aspects of this project is identifying and utilising novel solutions to optimise SNNs on edge devices. The first section will explain why SNN inferences on the edge are an effective solution for neuromorphic computing, providing a detailed description of the features and characteristics that define this approach. Subsequently, the underlying equations of the neuron model will be examined in more detail. This analysis will also emphasise how the model is employed and why it outperforms conventional neural networks. Several existing SNN implementations will also be described to determine the primary fields in which these architectures are used. The use of specific accelerators in academic settings will be examined, focusing on their effectiveness in executing SNN operations. The investigation will delve into the intricacies of these accelerators, elucidating their strengths and limitations. Furthermore, the chapter will examine frameworks for developing SNNs at a higher level using high-level languages such as Python. It will provide descriptions and details of the hardware used and explore its potential applications in general neural network inference. The analysis will present specific tools and libraries, demonstrating how the research in this thesis fills a significant gap in the field of SNNs. Several specific tools for developing edge SNNs have already been developed, and these will be described in the following section. Finally, the chapter will conclude with an explanation of the importance of all the previously described research and projects to this contribution.

### 2.1 SNN: overview and neuromorphic computing over the Edge

Among the best ways to deploy intelligence at the edge, i.e., directly on a hardware platform, is surely the use of neuromorphic computing. As described in [1], neuromorphic computing exploits methods for developing intelligent systems inspired by the biological brain. This particular implementation allows for greater efficiency,

scalability, and adaptability in intelligent applications.

**Neuromorphic computing features** Traditional Von Neumann architectures are based on the hard decoupling of computing units (CPUs) and memory units (typically RAM). This results in high energy consumption and speed bottlenecks caused by the transfer of data between memory and processing units. The idea of neuromorphic computing, on the other hand, is to couple memory and computation, shortening the distance between them using different types of architecture. This is achieved by incorporating neurons into intelligent architectures that endow applications with smart behaviour simply by preserving a state, generating spikes, and processing weights.

Another important feature of neuromorphic computing is sparsity: indeed, neurons in a network can perform actions sparsely, i.e. not all neurons are active throughout the execution of each step, but only some of them. This enables energy consumption to be kept low, with an average overall neuron activity that is sparse for each timestep.

Traditional AI systems typically rely on global backpropagation during learning, which causes high energy consumption when updating all the weights across all the layers of the network. Instead, neuromorphic systems could improve this learning process by focusing on local pre- and postsynaptic activity. By exploiting these rules, the system can update weights based on local activity features, favouring continuous learning.

Neuromorphic systems can also perform actions across a wide range of timesteps, operating with fast synaptic iteration as well as slower training, and have high temporal processing capabilities. This feature is fundamental when different sensed data need to be processed in a short amount of time for real-time applications.

Another key feature of neuromorphic systems is their brain-inspired hierarchical organisation, which, alongside layer structure, enables the easier processing of large and complex sensory information while reducing redundancy, a characteristic of normal non-hierarchical structures.

Ultimately, brain-inspired technology is also easy to deploy on hardware systems with strict memory limitations. This is because it uses spike event-driven technology instead of computing specific inputs, as is the case with normal deep learning models. The intrinsic parallelisation of the networks also allows systems to be developed that exploit the parallel execution of different neurons in a layer altogether to improve overall performance.

**SNN models and training** In order to facilitate a more profound comprehension of the Spiking Neural Network behaviour and its characteristic dynamics, a concise presentation of the aforementioned networks and the manner in which they are exploited is herein provided. As stated in the review by Nguyen (2021) [2], neurons are inspired by actual brain biological behaviours. However, it is specified here that the Hodgkin-Huxley model is the most accurate model in terms of brain behaviour, but that it is complex to use. In this review, other simpler neuron models are briefly described. One such example is the Izhikevich model, which, due to its dynamics and non-linear behaviour, represents an optimal trade-off between computational power and feasibility. Notwithstanding, the most frequently employed neuron models in accordance with the cited literature are the Leaky-Integrate and Fire (LIF) model and the more elementary Integrate and Fire (IF) model. The behaviour of these models is predicated on the accumulation of weight from preceding spikes, in conjunction with the dynamic generation of spikes at the level of spike generations. The membrane potential of the neuron attains a threshold value, thus instigating the aforementioned behaviour. Furthermore, the membrane potential undergoes a leakage loss over time, irrespective of the occurrence of spikes. In the event of a spike being performed, it is within the capabilities of the modeler to place the neuron in a recovery phase that temporarily disables it. The review elucidates that a number of models have been subjected to trials for the implementation of LIF (Leaky Integrate-and-Fire) or more straightforward models, which have demonstrated commendable performance. However, contemporary researchers are endeavouring to identify methodologies for the incorporation of computationally expensive neurons, such as Hodgkin-Huxley, within hardware devices. This objective is being pursued through the utilisation of numerical procedures, including the Euler method, for the purpose of simplifying these models.

In this review, the function of the synapse in SNNs is elucidated. The synapse is defined as a connection between neurons in the network, and it has been demonstrated that whenever a neuron spikes, the spike affects the neuron linked with a positive (excitatory) or a negative (inhibitory) behaviour on the state of the connected neuron. The management of this process is facilitated by the synaptic weights. In contrast to conventional artificial neural networks, these weights demonstrate plasticity over time, adapting to the behaviour of spikes originating from pre- and post-synaptic neurons.

SNNs differ from conventional artificial intelligence in that they can be trained in various ways, making them more adaptable to different inferences. As previously mentioned, one training method exploits the adjustment of strengths according to the timing difference between pre- and postsynaptic spikes. This is known as spike-timing-dependent plasticity (STDP). In this context, the temporal proximity of spikes modulates the strength of connections. Reduced temporal proximity

enhances strength, while increased temporal proximity reduces it. However, this method is not employed for comprehensive learning due to its inability to coordinate complex learning across different layers in large networks. A more prevalent learning method is supervised learning, which is based on analysing the gradients used to minimise the distance between the expected and produced outputs. Spike generation is a discrete process involving non-differentiable activation functions. To overcome this issue, surrogate gradient activation functions are employed to convert the spikes into continuous real values, thus facilitating gradient flow during training. This approach has been shown to deliver levels of accuracy comparable to those of a standard artificial neural network. An alternative method involves converting previously trained artificial neural networks (ANNs) into spiking neural networks (SNNs). While this approach is effective, encompassing all ANN training methods, there is a caveat: not all ANNs can be translated into SNNs. In most cases, the optimisations made for ANNs cannot be transferred directly to SNNs. This can result in concerns regarding power consumption and a potential increase in complexity.

**A deeper look at LIF model** In [3], is provided a detailed explanation of what a LIF neuron is, how it works and the key equations and elements that describe its behaviour. As previously mentioned, this is one of the most common neuron models used in typical spiking neural networks (SNNs), and it has some core elements that describe its dynamics during execution.

- **Membrane voltage integration:** neuron integration of incoming current represented as input  $\mathbf{J}(t)$ .

- **Leakiness:** During execution, there is a leakage towards resting potential governed by a membrane time constant  $RC$ , where  $R$  stands for resistance and  $C$  stands for capacitance.

- **Firing threshold:** when the membrane voltage  $v(t)$  reaches threshold  $V_{th}$  the neuron generates a spike.

- **Reset and refractory behavior:** the neuron resets to resting potential for a refractory period indicated by  $t_{ref}$  after a spike; this is used to give the model more time awareness. Among the most commonly used reset state behaviours there are the reset to zero and the subtractive reset. The former assigns the neuron a membrane potential of 0, while the latter, when triggered by a spike, subtracts a potential amount equivalent to the threshold value. This process affords the neuron model enhanced temporal dynamics.

If we want to represent the neuron model dynamics using one single equation, which is time-continuous, in the same paper, the equation is described like:

$$RC \frac{dv(t)}{dt} = -v(t) + J(t)$$

From the same document, there is also a description of the Steady-State firing rate equation, often used to predict the spiking dynamic in a normal execution when  $J(t) = j$  is a constant current:

$$r(j) = \frac{1}{t_{ref} + RC \log\left(\frac{1}{1 - \frac{V_{th}}{j}}\right)}$$

if  $j$  is greater than  $V_{th}$ , 0 otherwise.

This equation is useful for training with this specific neuron model. As mentioned in previous research, the spike pattern must be 'smoothed' to make it compatible with common training techniques, such as back propagation. To achieve this, the following soft function is often used:

$$r(j) = \frac{1}{t_{ref} + RC \log\left(\frac{1}{1 - \frac{V_{th}}{\rho(j, \gamma)}}\right)}$$

where the element  $\rho(j, \gamma)$  is formed by:

$$\rho(j, \gamma) = \gamma \log\left(1 + \exp\left(\frac{j}{\gamma}\right)\right)$$

where  $\exp$  stands for the exponential function, and the factor  $\gamma$  is a smoothing parameter used to smooth the response curves made by LIF neurons for differentiability.

These are all the useful pieces for working with LIF neurons in the best way. Section 3.1.2 will describe the neuron dynamics used in this thesis, namely the LIF dynamic equation in the context of a discrete-time application. Indeed, if we discretise the aforementioned equation from the cited paper, we obtain:

$$V_{T+1} = V_{reset} + \beta(V_T - V_{reset}) + (1 - \beta)J(t)$$

Where the  $\beta$  will later be described as a factor derived from  $RC$  in the equation ( $RC = \tau$  there), and the input current  $(1 - \beta)J(t)$  corresponds directly to the strengths summed together during each executive cycle in that section.

## 2.2 Use cases of SNNs

In this section, a couple of use cases will be analyzed in order to be more aware of the current state-of-the-art architectures.

### 2.2.1 Neu-BrAuER

The first use case that deserves a mention is Neu-BrAuER [4]. The workflow is briefly summarised in Figure 2.1. This work focuses on the classification and audio reading of Braille letters from sensory touch data. Neu-BrAuER can interpret signals detected by commercial capacitive pressure sensors and enable the correct pronunciation of letters according to the classification after sensing. The network structure consists of a three-layer, fully connected recurrent spiking neural network (RSNN) that uses LIF neurons. The model senses data from 12 different channels and can be implemented directly on commercial edge devices. To optimise inference execution over the edge, quantisation is performed to reduce all neuron states to 4- and 8-bit precision within different network layers, achieving gains in memory and execution efficiency without significantly degrading learning dynamics. Training of the network was performed using GPU accelerators and SNNtorch, and the model was deployed as an ONNX model for use on commercial MPUs. The resulting system is fast and optimised for real-time scenarios involving the acquisition of numerous samples without degradation.

This work also reports excellent results. Indeed, a median classification accuracy of 73.09% is achieved, with a standard deviation of 1.08%, across 50 test runs on a balanced dataset containing 27 classes. Some letters achieved 100% accuracy, but others, such as O, P and Q, were more difficult to classify. The network was executed on an STM32MP157F board and the median inference time was 264 ms per sample, with a peak of 400 ms. These results were also achieved with thousands of sample executions. The energy consumption is 313 mJ per inference, which is suitable for wearable or battery-powered devices. These results demonstrate that good results can be achieved when executing SNNs, even with small bit-widths and commercial tools.

Figure 2.1: Workflow of Neu-BrAuER development

### 2.2.2 SNN-based HAR on Commercial Edge devices

To understand the power of SNN current implementations, it has been considered another use case presented in [5]. This work focuses on human activity recognition (HAR) using a neuromorphic architecture called L2MU, which is a spiking variant of the Legendre Memory Unit (LMU) model. This work enhances the LMU model’s capabilities by employing a LIF neuron structure that focuses on both simple LIF models and their more advanced synaptic variants. This architecture is designed to take raw sensor data; therefore, no layer is needed to convert that data, and it can be implemented directly on edge devices as well as on specialised neuromorphic hardware. The architecture incorporates an encoding module capable of transforming continuous sensed data into spiking activity using a multi-layer LIF-based neural population. The model also supports hyperparameter optimisation for network architecture and specific neuron dynamics, which is useful for selecting the optimal structure required for high HAR task recognition accuracy.

This model uses a dataset (WISDM) comprising smartwatch sensor data that represents various actions performed by multiple subjects. The samples are segmented into two-second windows and the network specialises in recognising hand-related activities, categorising them into seven different values. The data is divided into three sets: 60% for training, 20% for validation and 20% for testing. L2MU translates ordinary LMU equations by exploiting only LIF neuron populations and spike patterns, ensuring full neuromorphic flow.

Adaptations to embedded and real-time applications are made by exploiting weight pruning (via the Sconce Python library) and retraining. This is an innovative way to compress SNN models for hardware with resource constraints, resulting in only a small loss of accuracy. Trials were conducted using three different commercial platforms: STM32MP157F-DK2, Raspberry Pi 3B and Raspberry Pi 4B. These boards run standard Linux-based operating systems and SNN inference is conducted using ONNX Runtime with PyTorch-based conversion for snnTorch.

Overall, both leaky and synaptic neurons performed very well, with median test accuracy above 93%. However, LIF neurons performed slightly better, especially after compression, demonstrating superior accuracy, stability and greater efficiency in memory usage.

The same model, which uses LIF neurons, is deployed on each commercial board, achieving the following results:

- STM32MP1 board has used 65.7 MB of RAM with 0.13 s as Mean Inference Time and 215.1 mJ as Mean Energy per Inference.

- Raspberry Pi 3B board has used 77.8 MB of RAM with 0.06 s as Mean Inference Time and 268.8 mJ as Mean Energy per Inference.

- Raspberry Pi 4B board has used 77.4 MB of RAM with 0.03 s as Mean Inference Time and 153.9 mJ as Mean Energy per Inference.

The accuracy achieved is 93.91%, which is consistent across all models. Synaptic accuracy is slightly lower, but RAM consumption is consistently higher across all devices. Overall, this work demonstrates that, if correctly designed and implemented, simple neuron models such as LIF can achieve high enough accuracy to justify their usage, even for commercial devices.

## 2.3 HW designed for neuromorphic applications

SNNs provide good results when executed on commercial platforms, but SNNs perform best when designed specifically for hardware devices optimised for neuromorphic operations. This section will describe two different types: Spinnaker 2 and Loihi 2 by Intel.

### 2.3.1 Spinnaker 2

Spinnaker 2 introduced several innovations in the field of neuromorphic computing, with a focus on energy efficiency, scalability and hybrid computation for neural networks. As stated in [6], the chip uses advanced 22 nm FDSOI technology with adaptive body biasing to reduce energy consumption and address process variation. It efficiently performs at low voltages of around 0.5 V to ensure lower energy consumption. Dynamic voltage and frequency scaling (DVFS) connects power supplies and clocks directly to computations, primarily neural spiking, and can adapt power consumption dynamically and coherently in response to the workload. This results in around 60% less power consumption than using a static power supply for typical SNN operations.

The processor architecture is the ARM Cortex-M4F core with single-precision floating-point computation, an improvement on the previous Spinnaker design. There are also integrated accelerators within each processing element (PE), which boost typical neural network computations. These consist of dedicated MAC arrays (4x16 8-bit units) target matrix and convolution operations, executing in parallel independently from the main core to speed up neuromorphic operations. Other accelerators focus on exponentials, logarithmic operations and random number generation to facilitate neuromorphic simulations.

A quad-processing-element (QPE) modular unit is used to improve the architecture. Each unit incorporates four PEs and a Network-on-Chip (NoC) router in a Globally Asynchronous Locally Synchronous (GALS) layout, which minimises complexity and power demands. The NoC system incorporates two different interlaced structures for data and configuration, using two asynchronous FIFOs, logic to handle various neural events, error correlation features and out-of-order buffers to increase speed and enable scalable communication between multiple PEs. Local and distributed memory architectures separate SRAM banks, minimising access

contention to enable full parallel processing across elements.

So, Spinnaker 2 uses a hybrid approach, combining common processor architecture with a set of accelerators that optimise common, repetitive neural operations. This makes the system perform faster while consuming minimal energy. Its architecture is also optimised for event-driven MAC usage, enabling efficient multi-bit signal processing to mimic biological graded neuron responses, or it could be exploited for complex learning mechanisms.

To effectively demonstrate the model’s enhanced performance, standard benchmarks were conducted. SpiNNaker 2 achieves efficiency rates of approximately 16–20 CoreMarks per MHz and 1.47–1.75 TOPS/W for 8-bit operations, all at low supply voltages, when running standard benchmarks. The accelerators made it possible to execute convolutional and matrix operations using the MAC arrays, achieving speedups of up to 610x and energy consumption reductions of up to 652x for convolutional layers compared to executing the same kind of operations with the ARM core only. This hybrid approach enables support for the neural engineering framework (NEF) via the ARM core, while the accelerators handle all the repetitive, energy-intensive neuromorphic operations. Overall, this system’s scalability and architecture model make SNN development and execution much easier and faster.

### 2.3.2 Intel Loihi 2

Another important system that is highly optimised for neuromorphic operations, and more precisely, SNNs, is the Intel Loihi 2. The main features and characteristics of this model are described in detail in [7]. Its architecture comprises microprocessor cores and up to 128 asynchronous neuron cores, which are linked together with a network-on-chip (NoC). The neuron cores specialise in executing high-speed spiking neuron computations and spiking logic.

The neurons are programmable using custom microcode, which allows various custom neuron models to be implemented, not just common models such as LIFs. Improvements have been made on the previous model and this chip is now capable of computing spikes with integer-valued payloads, improving precision while maintaining the sparsity introduced by spiking behaviour. Loihi 2 can handle the latest learning algorithms, such as backpropagation, and its architecture can improve synaptic and neuronal density. It exploits advanced memory partitioning, convolutional, factorised and stochastic connectivity, and compressed synapse encodings to increase efficiency by up to 160x. As previously mentioned, performance is dramatically boosted with up to 10x faster spike generation, 5x faster synaptic operations and 2x faster neuron updates compared with previous models. Timesteps are executed at a speed of 200 ns to outperform real biological circuits. Thanks to Ethernet and GPIO ports, it is also easy to integrate with other systems to communicate with different sensors and environments.

The Loihi 2 offers many features for customising and optimising neuron behaviour. Unlike the previous model, it also has soft-partitioned, asynchronous memories to speed up memory access and neuron dynamics. In terms of results, this model also consumes less than 1 watt in real-world applications, which is lower than general-purpose GPUs or CPUs, which could consume 10 to 100s of watts for similar workloads. It also supports Sigma-Delta Neural Networks, achieving 10x faster speeds and lower energy consumption than previous neuron models. All other neuron updates are also improved. A single Loihi 2 chip can support up to one million neurons and 120 million synapses by exploiting compression and flexible resource allocation. Unlike other models, the Loihi 2 is supported by Lava, an open-source, community-driven software framework that makes this system easier to use and handle. Lava supports simulation and profiling across CPU, GPU and neuromorphic hardware, promoting broader adoption and facilitating experimentation. This model's strengths are undoubtedly its open-source software access and high programmability.

## 2.4 Frameworks to develop SNNs

As mentioned in previous sections of this chapter, SNNs produce excellent results in neuromorphic systems simply through their use. Frameworks are designed to facilitate and streamline their development. SNNTorch is a PyTorch-based framework for SNN development. SNNs can be represented using the Neuromorphic Intermediate Representation (NIR), which makes them easily portable between different development environments.

### 2.4.1 snnTorch

The main features of this Python framework are detailed in [8]. This framework optimizes spike representation through the networks using single-bit values, which greatly reduces computational costs, particularly when deployed on actual hardware platforms. The framework now supports LIF neurons, current-based neurons, recurrent structures and advanced models such as spiking LSTMs and spiking Transformers. SNNs can interpret and produce spikes using rate coding (encoding information in spike counts), latency coding (using the timing of spikes), delta modulation (responding to input changes) and population coding (distributing information across groups), providing significant compatibility with systems that use time-dependent inputs, such as vision, sound and biosignals.

SNNs have huge compatibility with deep learning tools simply by being expressed as discrete-time equations. Like these tools, SNNs can benefit from features such as batch normalisation, residual connections and automatic differentiation.

Supported training techniques include:

- **Surrogate Gradient Descent:** it overcomes the non-differentiability of spikes using a smooth, differentiable surrogate function during the backward pass, making spiking neural networks (SNNs) compatible with backpropagation through time (BPTT). Various surrogate functions can be employed, such as sigmoid, arctan and triangular, and these can be used as hyperparameters of the network.

- **Objective Functions:** there is also support for different loss/objective settings, such as spike-rate targets and spike-timing (latency) objectives. Objectives that operate directly on the membrane potential are also supported, enabling compatibility with both rate- and latency-based learning schemes.

- **Local and Online Learning Algorithms:** Alongside traditional backpropagation with temporal unrolling, localized, biologically inspired approaches are also supported, with methods such as e-prop, Decolle and event-based plasticity (three-factor rules) implemented to enhance biological plausibility.

SNNs can be defined and structured using a familiar deep learning syntax. Layers, synapses and neurons are also fully compatible with standard PyTorch modules. Following normal ANN workflows, training is eased by simply adding time-stepped simulations and spike-based activities. Optimizers such as Adam and SGD are also available. Parameters such as the decay factor, thresholds, weights, biases, and other typical parameters can be set to be learnable, thereby enhancing the network’s plasticity. The framework can easily bridge the gap between traditional ANN methods and new SNN methods, demonstrating that SNNs can be trained directly using deep learning methodologies while retaining brain-like characteristics. Along with the paper, the documentation is easily available online and contains ready-to-use tutorials for developing SNNs. Ultimately, the framework is excellent for easily training SNN models and has the tools to perform simulations on the models that can later be easily reproduced on specific target platforms.

## 2.4.2 Neuromorphic Intermediate Representation

The paper [9] describes the main features of the first standardised reference for neuromorphic computing, which is a powerful tool for future progress in this field. As NIR is completely platform-independent, it can be used to describe neuromorphic structures and computations at a high level of abstraction, facilitating the porting of the same model across different tools. NIR has definitive and fixed primaries that correspond to the standard features of neurons and connections between layers. These primaries can capture both continuous and discrete dynamics, enabling a complete description of SNNs, which can be deployed more easily and faithfully over hardware platforms. SNN development focuses solely on the model itself, not its specific implementation, enabling faster reproducibility. As the model

description is graph-based, the primitives of NIR are represented as nodes in this graph (e.g. leaky integrator, integrate-and-fire neurons, linear layers, convolutions and spikes), with edges representing signal flow. This makes it easy to manage the complexity of SNNs in simple structures, which also makes model development easier. NIR is purely declarative and completely machine-readable, and it also allows for the future extension of the primitive set as technology evolves and new structures and neurons emerge. NIR already supports seven neuromorphic simulators and four contemporary digital neuromorphic hardware platforms, including Intel Loihi 2, SynSense Speck, SpiNNaker2 and Xylo. This enables faster testing and benchmarking of the same model across different platforms, facilitating performance analysis and the identification of optimal solutions. Three representative tasks were used to conduct comprehensive experiments: a leaky integrate-and-fire neuron (basic), a spiking convolutional neural network (vision), and a spiking recurrent neural network (temporal processing). These models were then executed on all available platforms to examine qualitative and quantitative similarities in computational outcomes. In terms of accuracy, the Sequential Convolutional Neural Network (SCNN) model trained on neuromorphic MNIST achieved a mean test accuracy of 97.7%, with a standard deviation of 0.9%, resulting in the reliable preservation of the model across different simulators and processors. In summary, NIR occupies the same position in SNN development as ONNX or MLIR in deep learning, paving the way for a comprehensive, standardised representation of SNNs that has the potential to incorporate additional platforms.

## 2.5 Analysis of low power HW

One of the issues with the neuromorphic hardware previously described is that it is often difficult to acquire, expensive, and unavailable for purchase. This section will analyse two alternatives to traditional hardware that could be used to develop SNNs by exploiting the power of neuromorphic models. These are the STM32H757I-EVAL ST Board and the GAP-8 based on PULP.

### 2.5.1 STM32H757I-EVAL

The characteristics of the STM32H757I-EVAL ST Board (Figure 2.2<sup>1</sup> are detailed in the STMicroelectronics documentation [10]. It is clear from this documentation that the board is designed to deliver robust computational performance while optimising energy efficiency, making it suitable for demanding applications as well as power-sensitive deployments. The board has a dual-core setup with a high-speed

---

<sup>1</sup><https://www.st.com/en/evaluation-tools/stm32h757i-eval.html>

Arm Cortex-M7 and Cortex-M4 (optimised for low power and real-time signal processing), and provides 2 MB of flash memory and 1 MB of RAM for storing code and data. It also has a variety of peripherals that can be used to integrate developed applications with other environments, such as USB OTG HS/FS, Ethernet, CAN FD, audio interfaces (DAC, ADC and SAI), digital MEMS microphones and extensive memory support (SDRAM, SRAM, NOR and Quad-SPI flash, as well as a microSD card). The board also features a 4" 480×800 TFT colour touchscreen display with a MIPI DSI interface, as well as a hardware cryptographic accelerator, which is absent from the STM32H74xI variants. To enhance system compatibility with other environments, support for multiple connectivity interfaces has been enabled, including USB ports, Ethernet and CAN FD for high-speed networking, I2C and RS-232, as well as extension connectors. Complete debugging and programming support is also provided through the use of STLINK-V3E. The system also supports custom voltage supply to cores; in particular, the microcontroller's core voltage can be supplied by either the internal, high-efficiency, DC/DC switch-mode power supply (SMPS), or a linear regulator (LDO). The SMPS is set by default and is generally best for low power, but the LDO could also be used, or a hybrid approach could be employed. The board can also be configured using specific jumpers to select the desired features for particular applications. For example, a jumper can be used to select one of six independent power supply options. STLINK USB, multiple USB OTG ports, an external 5 V DC adapter or power from daughterboard connectors, enabling the board to be used in almost every scenario. Current limitation and overcurrent detection are also in place to protect the board itself and any linked daughter boards, and the board status can easily be seen through the use of embedded LEDs.

All of the described interfaces also have low-power modes. For example, the USB and Ethernet PHY interfaces can be configured for low-power states when not in use, and in specific scenarios, the RTC with backup battery can be used for ultra-low-power timekeeping. The board is equipped with various peripherals, including a potentiometer, a joystick, a tamper switch, a wake-up button, a reset button, multiple general-purpose LEDs and an LCD touchscreen, to facilitate interactive prototyping and HMI projects. The MFX IO expander provides additional GPIOs and peripheral control. The board is supported by many major development environments, such as IAR, KEIL MDK-ARM and STM32CubeIDE. Numerous example programs in the free STM32Cube MCU package demonstrate how to use the peripherals, along with the relevant libraries. These libraries allow you to create fully customised and optimised systems. Now, a deeper explanation of the main core will be given to demonstrate the power of this architecture in low-power scenarios.

**Arm Cortex-M7** All the main characteristics of the M7 core featured in the board are gathered in [11]. It adopts the Armv7E-M instruction set and boasts a

Figure 2.2: STM32H757I-EVAL ST Board

6-stage, dual-issue superscalar pipeline. This enables the parallel execution of multiple instructions, thereby increasing throughput in computationally intensive scenarios. It also has hardware branch prediction capabilities and integrated tightly-coupled memories (TCMs), giving the system high compatibility with real-time decision-making scenarios. Furthermore, it is described as outperforming previous models by achieving outstanding benchmark scores of 5.01 CoreMarks/MHz. To minimise memory latency, the system also has built-in instruction and data caches for memory-bound scenarios. Up to 16 MB of instruction and data TCMs

are designed to provide deterministic performance in real-time scenarios with predictable access times. Secure access control is also granted through the use of a Memory Protection Unit (MPU). One of the most important features of this core architecture is the advanced digital signal processor (DSP) extension, which features single-cycle multiply-accumulate (MAC) instructions and SIMD (single instruction, multiple data) arithmetic for parallel data processing (eight 16-bit operations per cycle). The hardware divide unit is particularly useful for the fast execution of mathematical operations. Operations such as multiply-accumulate, division and square root are supported by an optional floating-point unit (FPU) for single and double precision. The architecture is built around a high-speed AMBA4 AXI and AHB interconnect supporting wide (64-bit) communication with external memories and other system on a chip (SoC) peripherals. Advanced debugging, tracing and external system management are also facilitated through interfaces such as APB, ATB and private peripheral buses. Optional elements such as the embedded trace macrocell (ETM), the data watchpoint and trace (DWT) and the instrumentation trace functionality provide precise real-time debugging and trace analysis, which is particularly important in real-time scenarios. The Nested Vectored Interrupt Controller (NVIC) enables rapid interrupt handling and supports up to 240 configurable external interrupts and 256 priority levels, providing comprehensive customisable interrupt management for critical systems. To minimise the board’s energy consumption when the system must remain inactive, the optional Wake-up Interrupt Controller (WIC) and low-power sleep modes could be used to allow dynamic power consumption that is consistent with the workload.

Now, we will take a closer look at DSP extension to enhance the optimisations made to speed up mathematical operations.

**DSP** [12] indicates that the Digital Signal Processor (DSP) extension of the M7 processor comprises hardware and instruction set enhancements that enable it to perform optimally in signal processing fields such as audio, sensor data processing, telecommunications and control systems. This is achieved by combining high-speed arithmetic, parallel data processing and specialised memory access patterns to accelerate arithmetic operations beyond the capabilities of the standard core. In addition to the previously mentioned optimisations, there is also wide support for a variety of data types, such as integers, fractional formats and floating-point numbers, which provides flexibility for fixed- and floating-point computations. DSP MAC instructions can multiply and sum values in one step, which is a frequent operation in algorithms such as digital filters or fast Fourier transforms (FFTs). Operations are parallelised using SIMD instructions, which allow multiple smaller data elements to be processed simultaneously. For example, two 16-bit or four 8-bit calculations can be performed in parallel within a 32-bit register. Overheads and bottlenecks are optimised using techniques such as loop unrolling and efficient memory access (e.g. using FIFO buffers to emulate circular addressing), which

significantly reduces the cycle count of processors without a DSP. These optimisations, which are embedded directly in the M7 core, remove the need for a separate DSP chip, keeping the overall cost of boards with these cores low and making them more accessible.

### 2.5.2 GAP-8

The main features of the GAP8 SoC are detailed in [13]. The overall structure is synthetized in Figure 2.3. Its architecture focuses on optimising local data processing, minimising data transmission needs and enabling low battery consumption, making it well-suited to the IoT domain. The GAP8 comprises a dual-domain system-on-chip fabricated using a 55 nm low-power CMOS process. It is formed by an energy-efficient microcontroller called the Fabric Controller, which has a computing cluster. Based on an enhanced RISC-V core, it can manage various general device operations and interfaces, directly exploiting all the on-chip peripherals, such as QSPI, I2C, I2S, the camera and PWM. This facilitates real-time, multi-modal data acquisition.

The cluster operates in different voltage and frequency domains and is made up of eight identical RISC-V cores, with the same architecture of the controller. These cores are supplemented by a hardware convolution engine (HWCE), which is dedicated to accelerating convolutional neural network (CNN) inference. Using a flexible shared memory, it can easily parallelise all normal NN tasks and speed up all common executions. The memory hierarchy is organised to enable easy memory parallelisation access by all eight cores and is supported by a multi-channel DMA system designed for low-latency data transfers. The system can rely on 512 KB of on-chip memory and expandable external memory to easily extend hardware capabilities according to model demands.

The system’s software environment is built around GCC toolchains and offers native support for parallel programming via OpenMP. Developers can use explicit tools to automate memory tiling and scheduling, making it easier to manage the memory hierarchy. This approach facilitates the deployment of NN models by enabling them to be developed through high-level frameworks such as TensorFlow and by using explicit core generators for the target architecture. GAP-8 uses aggressive power optimisation mechanisms such as integrated DC/DC converters and deep retention modes. In deep sleep mode, power consumption can be reduced to as little as 3.6  $\mu$ W, and peak computational loads can be handled with just 75 mW. Overall, this permits longer execution times using standard batteries.

The system architecture is designed to easily adapt to different workloads. Nearly linear acceleration is observed when parallelising across its eight cores. The observed benchmarks are impressive: the SoC achieves up to 10 GMACs for CNN computations at 90 MHz, with an energy efficiency of 600 GMACs/W. Common NN tasks, such as CIFAR-10 image classification, can be completed in around 650

µs at 15 mW. This enables the execution of 10 frames per second for almost two years on a single AAA battery, guaranteeing continuous, intelligent sensing at the edge. The system can efficiently optimise operations such as FFTs, matrix multiplications, convolutions and advanced signal analytics, using both SIMD extensions to the RISC-V cores and the HWCE accelerator to achieve 10x better energy efficiency than software-only execution.

Using this architecture, systems that were previously thought to be deployed in cloud environments can now be easily deployed on an actual hardware platform, achieving faster speeds for real-time scenarios and dramatically reducing energy consumption. This architecture is excellent for easily sensing at the edge and directly computing fast, typical NN operations.

Figure 2.3: GAP-8 structure scheme

## 2.6 Tools to support NN at the Edge

In the previous section, some common hardware platforms were described to illustrate the characteristics that are useful for building Edge AI applications. These platforms also offer excellent support for the implementation of typical NNs through the use of ready-to-use dedicated tools and libraries: PULP-NN is used for the GAP-8 SoC, and the ST Edge AI Core is used for commercial ST boards.

### 2.6.1 PULP-NN

As described in [14], PULP-NN is an optimised, open-source software library designed for the efficient inference of quantised neural networks (QNNs) on multi-core, ultra-low-power RISC-V processors. Target architectures include the Parallel Ultra-Low Power (PULP) architecture and commercial implementations such as GAP-8. The library is suited to high-throughput applications with low power requirements. It supports aggressive quantisation using data types such as INT-8, INT-4, INT-2 and INT-1 for weights and activations. It contains optimized kernels, such as convolution, fully-connected, ReLU and max-pooling, which are tailored for reduced precision arithmetic. Binary kernels can be easily handled by exploiting the logical XNOR and bit-count instructions available in the instruction set architecture (ISA).

To drastically speed up typical neural network (NN) operations, the DSP instruction set architecture (ISA) extensions present in PULP-based RISC-V cores are used extensively, such as for SIMD operations (e.g. `sdotp4` for vector dot products), hardware loops, and efficient memory access. The cluster of eight cores is also exploited to parallelise workloads and achieve a near-linear speedup in mathematical operations. The library uses the HWC (height-width-channel) data layout for activations and weights to optimise memory bandwidth and target the optimisation of operations such as matrix multiplication. `im2col` routines and custom packing/unpacking functions for sub-byte data are implemented to make the operation more compatible with SIMD units and minimise the memory footprint. These optimisations achieve very good results in terms of throughput, delivering up to 15.5 multiply-accumulate operations per cycle (MACs/cycle) on INT-8 kernels when running optimised matrix multiplication. The library outperforms common NN libraries for commercial platforms such as ARM CMSIS-NN, delivering a speedup of up to  $63\times$  over the baseline sequential RV32IMC and significantly higher energy efficiency and performance than STM32L4 and STM32H7 MCUs when operating at maximum frequency. The library also enables GAP-8 to run a CIFAR-10 network in  $19.6\times$  fewer cycles than CMSIS-NN on STM32H7, offering  $14.1\times$  better energy efficiency than STM32L4.

The open-source nature of the system ensures adaptability and makes it open to further updates to improve performance as technology advances. It also permits

the efficient development of real-time applications, especially compared to other commercially available tools. This system paves the way for the deployment of highly quantised networks in environments with limited resources, demonstrating that aggressive quantisation (even down to 1 bit) is feasible on programmable parallel architectures with minimal loss of accuracy, provided that proper training techniques are employed. While this system could deliver very high performance, it undoubtedly requires a high degree of expertise in the field.

## 2.6.2 ST Edge AI Core

The main feature of the ST Edge AI Core tool could be extracted from the datasheet provided by ST in [15] and the cited web page. This freely available desktop software suite, developed by STMicroelectronics, is used to optimise, compile and deploy artificial intelligence (AI) models on a wide variety of ST hardware platforms, including STM32 and Stellar microcontrollers and microprocessors, as well as smart sensors equipped with ISPU and MLC functionalities. The tool’s primary function is to automatically transform pre-trained neural networks and classical machine learning models into highly optimised C code, facilitating the deployment of Edge AI applications from a standard model. It supports several AI frameworks, such as Keras and TensorFlow Lite, as well as any framework with ONNX export, such as PyTorch and MATLAB. This gives complete flexibility and compatibility for modern model workflows.

The tool further enhances computational efficiency by leveraging the generation of libraries that use dedicated hardware acceleration through the ST Neural-ART NPU wherever available. If the NPU does not support neural network operations, the tool seamlessly schedules these tasks to execute on the CPU, ensuring optimal use of resources. The software also enables users to assess RAM and flash usage during deployment, providing a more customisable environment. Optimisation options are provided to balance inference speed and binary size, catering for diverse application constraints. STEdgeAI-Core also features verification tools, allowing benchmarking and validation on host systems (Windows, MacOS and Linux) and actual ST hardware, ensuring reliability during edge AI development. The tool is accessible via a graphical interface and a command-line utility, and comes with comprehensive documentation to ease access and usage. STEdgeAI-Core is a key component of the ST Edge AI Suite, which aims to streamline every stage of AI deployment, from initial data management to final hardware integration, to create a robust, developer-friendly ecosystem. However, neither this tool nor the previously described one has direct SNN support. This is an issue that developers must overcome for their implementations with these tools to be as straightforward as standard NN deployment.

## 2.7 SNNs for widely available HW platforms

Following the analysis of commonly available, ready-to-use neural network (NN) tools for deployment on the edge, this paper will describe two solutions for developing spiking neural networks (SNNs) directly on widely available hardware devices. The first solution is Spiker+, which is specific to FPGA development, and the second is for deployment on RISC-V microcontrollers.

### 2.7.1 Spiker+

All Spiker+ features are fully described in [16]. It is a comprehensive framework designed to generate efficient hardware accelerators for spiking neural networks (SNNs) that are deployed on field programmable gate arrays (FPGAs) for edge inference applications. The framework is designed to efficiently integrate artificial neural networks (ANNs) at the edge for common critical real-time applications. The multi-layer architectures produced by this framework support both fully connected feed-forward (FF-FC) and recurrent (FC-R) SNN architectures, enabling the deployment of a large number of typical SNN models. The tool supports various Leaky Integrate and Fire (LIF) neuron model implementations (first- and second-order), with options for hard or subtractive reset mechanisms. Enhancements focus on minimising resource usage while maintaining computational accuracy. All network characteristics, such as network architectures, neuron types and input encoding schemes, can be described using a user-friendly Python interface. This makes the system more usable at a higher level of abstraction.

The hardware structure has been engineered to support high levels of both parallelism and modularity, while also ensuring a low-area footprint. The system utilises a start-ready handshake protocol for the purpose of synchronising and communicating between network components, thus optimising speed and power efficiency. The training framework utilises existing SNN training tools that support backpropagation through time (BPTT) with surrogate gradients. The process of optimisation and quantisation is also automatic, and is performed on neuron states such as synaptic weights and neuron parameters. This is done in order to balance accuracy and hardware constraints. The tool is also enriched by an automatic VHDL code generator with configurable memory storage options for synaptic weights. The system has been evaluated using two different datasets. In the first experiment, on the MNIST dataset, the feed-forward I-order LIF SNN was used, and Spiker achieved an accuracy of 93.85% with a classification latency of 780 microseconds per input image. This experiment also demonstrated that the system could consume only 180 mW of power on a low-end Xilinx XC7Z020 FPGA. In the second experiment, it was demonstrated that, using modest hardware resources, a compact and energy-efficient design suitable for resource-constrained edge devices could be achieved. In the context of audio classification, the Spiking Heidelberg Dataset (SHD) has

been found to be a particularly effective resource. Utilising recurrent architectures and II-order LIF neurons, the SHD has been demonstrated to achieve an accuracy of 72.99%, accompanied by a latency of 540 microseconds and a power consumption of 430 mW. This scenario encompasses a greater number of complex tasks, thus necessitating a greater quantity of memory and logic resources. However, it is notable that the results obtained demonstrate a favourable power-to-performance ratio in comparison to a significant number of contemporary FPGA SNN accelerators. It is evident that the system is capable of operating with minimal power consumption while achieving competitive levels of accuracy. It exhibits minimal utilisation of FPGA resources, thereby facilitating its deployment on compact, power-constrained devices. Additionally, it is equipped with a Python interface, which expedites the development of Edge SNNs. The impact of input spike activity and encoding schemes on power and latency is significant. Clock-driven update policies have been shown to be effective for small to medium-scale accelerators. Quantisation of neuron and synapse parameters has been demonstrated to have minimal impact on accuracy, but a significant impact on power savings. This facilitates larger implementable network sizes. However, it should be noted that memory capacity on the FPGA could be a limiting factor when implementing large and complex models. This tool is great for deploying SNNs on hardware, but it is limited to FPGAs, which are often expensive and generally require a high level of digital design expertise for deployment.

### 2.7.2 SNN decoder for Implantable Brain Machine Interfaces

All the details regarding this specific implementation over RISC-V microcontrollers are present in [17]. The system is a SNN designed as a neural decoder for regression tasks in implantable brain-machine interfaces (BMI). It is a low-complexity architecture comprising LIF neurons with trainable decay factors that are specific to each neuron rather than being uniform across the network. This design is flexible with regard to different temporal dependencies, which is an essential consideration for time-series neural decoding. The model uses 'spiking band power' (SBP), extracted from 96 channels, as the input feature. SBP uses a band-pass filter (300–1000 Hz) to reduce the data rate while retaining predominantly information from individual neural spikes — a choice that balances power efficiency and predictive accuracy. The architecture uses fully connected spiking layers, each containing 256 neurons, except for the output layer which predicts two-finger velocities. This process is handled entirely by neuron states, rather than exploiting any multi-step temporal convolutions, to optimise performance. Each neuron uses a custom reset-by-subtract scheme: whenever a neuron spikes, the membrane potential is decremented by the threshold value, giving the neurons more temporal

awareness. The network is trained using an enhanced spatio-temporal backpropagation (STBP) method. This method exploits trainable decay factors per neuron and noise injection before data normalisation for regularisation. Dropout is applied to the spatial dimensions during training (probability = 0.2) to combat overfitting. Batch normalisation uses threshold-dependent scaling and is fused into the weights and biases for deployment. Quantisation-aware training enables very low bit widths (down to 4 bits for the weights and 3 bits for the decays) with minimal loss of performance.

The input data used for training is prepared accurately to enhance the system's reliability and accuracy. Indeed, sequences are generated using a sliding window of 10 time steps and 9-step overlaps to increase the effective sample size via noise-based augmentation. The system is deployed on a RISC-V-based SoC (System on a Chip), the GAP9, and optimisations are made using DMA (Direct Memory Access) access for faster weight transfer and SIMD (Single Instruction Multiple Data) instructions to parallelise computations of neuron states and spikes. Distinct strategies for data movement and execution are applied to the input and spiking layers to minimise memory footprint (total storage of around 160 KB) and transfer overhead. When tested on two non-human primate benchmark datasets, the SNN achieved superior performance, with correlation coefficients of 0.783 and 0.624 for finger velocity prediction in datasets A and B respectively. This surpasses the performance of state-of-the-art Kalman filter (KF) and artificial neural network (ANN)-based decoders for offline inference. The system also achieved excellent efficiency results, consuming only 1.88  $\mu$ J of energy and 0.50 mW of power per inference via duty-cycled operation, with an average inference time of 0.12 ms. Using only 4-bit weights and higher-precision membrane potentials for stability has not resulted in relevant accuracy losses.

The results achieved here are excellent, but this work focused solely on one implementation using one target architecture, which makes it difficult to deploy different applications using the same optimisation approach.

## 2.8 Proposed solution

After analysing all state-of-the-art systems that exploit SNNs, their implementation advantages, and how they are used to optimise neuromorphic applications, this thesis will briefly describe the tools and approach used to solve some of the aforementioned solutions' problems, proposing a more standardised system that could be used to optimally deploy a simple SNN architecture over standard MCUs.

The system merges the strengths of the previously mentioned tools to achieve:

- Optimised SNN execution on classic, affordable, commercial microcontrollers.

- Two different hardware systems are targeted to perform custom-specific optimisations for specific hardware architectures.

- The library is generated directly from the NIR description to provide greater flexibility for the proposed solution in different SNN applications for one of the target systems that uses LIF neurons.

# Chapter 3

## Materials and methods

After analyzing previous trials in this field of research and after analyzing the hardware where the system must be implemented, in this chapter, I present the work I carried out to develop the final system solution, composed of a ready-to-work SNN across different platforms and hardwares. In particular, the focus is on:

- SNN model development using the snnTorch framework, with training and testing.

- Deployment of the same model in an ST Board with optimized features.

- Deployment of the model into GAP8 hardware platform.

- NIR-to-C translator capable of translating NIR described SNN with a similar architecture as the proposed one into a .h/.c file bootable on the board.

- Only on ST Board, an half-optimised version of the Izhikevich neuron model.

The chapter contains the implementation details of the solution with all the tools used to make the system work.

### 3.1 SNN Model Architecture

In this first section, I will discuss about the model of neurons used in the architecture and on how the neurons are linked to each other to make the system work.

#### 3.1.1 The model and its purpose

I decided to implement an SNN capable of making a classification of 7 different classes. The goal of such a model is to translate a signal input taken by a robotic hand when passing its finger over a Braille character [4].

The input comprises 12 channels from 12 analog sources. Each of these channels is monitored for temporal variations. When a channel's analog signal exceeds a predetermined threshold in either direction, a value of 1 is assigned to indicate a significant change. Conversely, periods during which the signal remains within the threshold result in the assignment of a value of 0, denoting stability. This threshold-based approach transforms the continuous analogue input into a binary sequence, where spikes represent moments of change and zeros indicate periods with constant signal values. This encoding method allows relevant dynamic information to be efficiently extracted from analog signals for subsequent classification tasks in the model.