## POLITECNICO DI TORINO

Master's Degree in Cybersecurity

Master's Degree Thesis

# Fault Injection Analysis of Automotive Benchmarks using HPC-Based Monitoring

Supervisors

Candidate

Prof. Stefano DI CARLO

Amalia Vittoria MONTEMURRO

Prof. Alessandro SAVINO

Doctor. Enrico MAGLIANO

October 2025

## Abstract

The downscaling of electronic components in terms of voltage and physical dimensions has enabled the development of modern high-performance microprocessors, which are increasingly adopted in safety-critical applications. However, their reduced dimensions have increased the sensitivity to radiation. Radiation-induced soft errors have become a key threat in terms of reliability in safety-critical real-time embedded systems (SACRES). A common technique used to enhance the hardware reliability is N-Modular Redundancy (NMR). With the growing complexity of modern microprocessors, this solution has become unaffordable. The development of lighter alternatives for implementing hardware/software error detection mechanisms has become a crucial area of research.

This thesis investigates the effects of fault injections on automotive benchmarks to assess the reliability of the target setup, a crucial step for studying new, lighter robustness solutions. The selected benchmarks are taken from the EEMBC MultiBench<sup>TM</sup> Multicore Benchmark Suite to strengthen the representativeness of the experimental environment. The strength of this approach lies in the fact that MultiBench combines a wide variety of application-specific workloads with the EEMBC Multi-Instance Test Harness (MITH), which is compatible and portable across most multicore processors and operating systems. The benchmarks are executed in a real-time scenario under FreeRTOS, exploiting its scheduling algorithm to enable task concurrency, on the Xilinx Pynq-Z2 board. With this setup, benchmarks are scheduled concurrently and executed across multiple runs of the system, resulting in different demos. Faults are injected into both memory and registers via host, and their effects are analyzed by leveraging Hardware Performance Counters (HPCs) to monitor micro-architectural events. To maximize the information gathered, each fault is executed multiple times so that its impact can be observed across different monitored events.

# Table of Contents

| Li           | st of | Tables                                  | vi  |

|--------------|-------|-----------------------------------------|-----|

| Li           | st of | Figures                                 | vii |

| $\mathbf{A}$ | crony | yms                                     | ix  |

| 1            | Intr  | roduction                               | 1   |

|              | 1.1   | Motivation                              | 1   |

|              | 1.2   | Verification and Validation             | 2   |

|              | 1.3   | Thesis Overview                         | 3   |

|              |       | 1.3.1 The basic workflow                | 4   |

|              | 1.4   | Structure of the Thesis                 | 5   |

| 2            | Bac   | kground                                 | 7   |

|              | 2.1   | Dependability                           | 7   |

|              |       | 2.1.1 A taxonomy of Dependability       | 8   |

|              | 2.2   | Faults in ISO 26262                     | 10  |

|              |       | 2.2.1 Soft Errors                       | 10  |

|              | 2.3   | Mitigation Techniques                   | 12  |

|              |       | 2.3.1 Classical Approaches: TMR and ECC | 12  |

|              |       | 2.3.2 AI-Based Detection                | 13  |

|              | 2.4   | Fault Injections Techniques             | 13  |

|              |       | 2.4.1 Hardware Fault Injection          | 13  |

|              |       | 2.4.2 Software Fault Injection          | 15  |

|              |       | 2.4.3 Other Categorization              | 16  |

|              |       | 2.4.4 Classification of Faults          | 17  |

|              | 2.5   | Related Works                           | 17  |

|              |       | 2.5.1 High-Level Details                | 18  |

|              |       | 2.5.2 Experimental Setup and Workflow   | 19  |

|              |             | 2.5.3    | Results                                                    | 21              |

|--------------|-------------|----------|------------------------------------------------------------|-----------------|

| 3            | Targ        | get Pla  | tform                                                      | 22              |

|              | 3.1         |          | Hardware Platform                                          | 22              |

|              | 0.1         | 3.1.1    | The Cortex-A9 processor                                    | 23              |

|              | 3.2         | _        | 'ime Operating System                                      | 25              |

|              | J. <b>_</b> | 3.2.1    | Tasks                                                      | $\frac{25}{25}$ |

|              |             | 3.2.2    | FreeRTOS                                                   | 26              |

|              |             | 3.2.3    | FreeRTOS Fundamentals                                      | 27              |

| 4            | Imp         | lomont   | tation Details                                             | 29              |

| -            | 4.1         |          | ench - Automotive Industrial Benchmarking                  | 29              |

|              | 1.1         | 4.1.1    | Benchmark Structures                                       | 30              |

|              |             | 4.1.2    | Benchmark Descriptions                                     | 31              |

|              | 4.2         |          | ation into the single workload campaigns                   | 33              |

|              | 4.3         | _        | workload campaigns                                         | 34              |

|              | 4.0         | 4.3.1    | High-level overview of MultiBench                          | 35              |

|              |             | 4.3.2    | Global Structure for HPC collection and task management .  | 36              |

|              |             | 4.3.3    | Timeline-based Multibench Scheduler                        | 38              |

|              |             | 4.3.4    | Fault Injector                                             | 39              |

| 5            | Exp         | erimer   | ntal Setup and Evaluation                                  | 41              |

| •            | 5.1         |          | aign Setup                                                 | 41              |

|              | 0.1         | 5.1.1    | Configuration of the target                                | 41              |

|              |             | 5.1.2    | Configuration of the Fault Injector                        | 42              |

|              |             | 5.1.3    | PMU Configuration                                          | 46              |

|              | 5.2         |          | et extraction and statistics for single-workload campaigns | 48              |

|              | 5.3         |          | et extraction and statistics for multi-workload campaigns  | 50              |

|              | 5.4         |          | ocessing                                                   | 51              |

|              | 0.1         | 5.4.1    | Dimensionality Reduction and Data Visualization            | 52              |

| 6            | Con         | clusion  | ns and Future Work                                         | 55              |

| $\mathbf{A}$ | Spe         | cificati | ons                                                        | <b>58</b>       |

| В            | Imp         | lement   | tation Code                                                | 60              |

| ט            | тшр         | remen.   |                                                            | UU              |

| Bi           | bliog       | graphy   |                                                            | 65              |

# List of Tables

| 3.1 | Cortex-A9 PMU Registers                                                                                                              | 24 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2 | Dataset statistics extracted from single_a2time and single_rspeed. Fault-level effectiveness summary for a2time and rspeed01 Dataset | 50 |

| A.1 | Common FreeRTOS APIs for Task Management and Synchronization                                                                         | 58 |

# List of Figures

| 1.1 | Experimental setup: fault injection via JTAG and PMU data acqui-   |    |

|-----|--------------------------------------------------------------------|----|

|     | sition on the PYNQ-Z2                                              | 3  |

| 1.2 | Basic workflow proposed in the experiments                         | 4  |

| 2.1 | The dependability tree from [15]                                   | 8  |

| 2.2 | Relationship between Fault, Error, and Failure                     | 10 |

| 2.3 | Causes of soft errors in modern microprocessors                    | 11 |

| 2.4 | High-Level architecture of the fault injection framework presented |    |

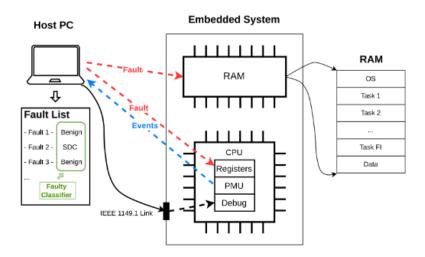

|     | in [12]                                                            | 18 |

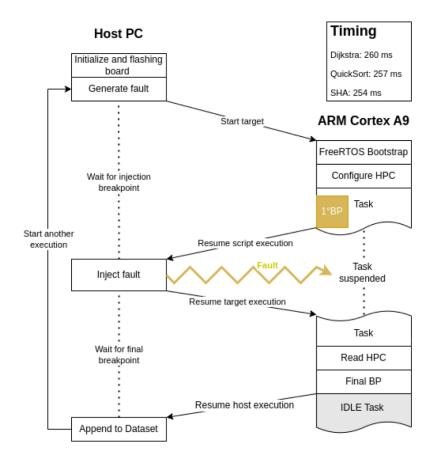

| 2.5 | Software execution flow taken from [12]                            | 20 |

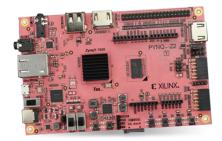

| 3.1 | Pynq Z2 board [54]                                                 | 22 |

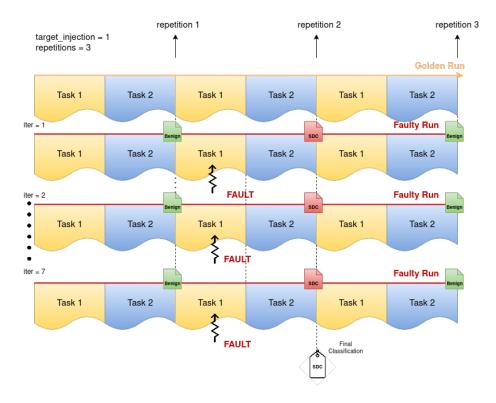

| 4.1 | Multi-workload campaigns workflow                                  | 37 |

| 4.2 | Timeline Scheduling workflow                                       |    |

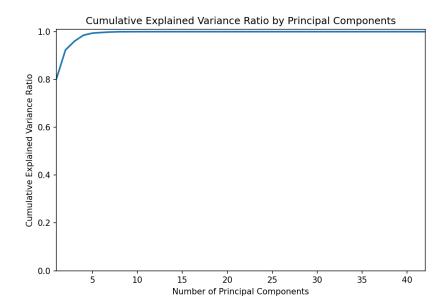

| 5.1 | Cumulative Explained Variance Ratio by Principal Components for    |    |

|     | a2time                                                             | 53 |

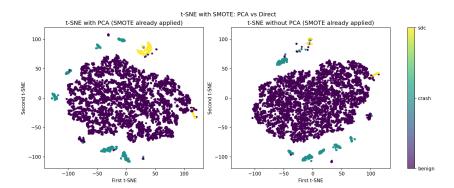

| 5.2 | t-SNE for a2time                                                   | 54 |

# Acronyms

#### a2time

Angle to Time Conversion

AI

Artificial Intelligence

API

Application Programming Interface

**ASIL**

Automotive Safety Integrity Levels

**BSP**

Board Support Packages

$\mathbf{BG}$

Background

$\mathbf{BRAM}$

Block Random Access Memory

CAN

Controller Area Network

canrdr01

CAN Remote Data Request

CCR

Cycle Count Register

#### CIA

Confidentiality, Integrity and Availability

#### CPU

Central Processing Unit

#### CRC

Cyclic Redundancy Check

#### **CSMS**

Cybersecurity Management System

#### CSV

Comma-Separated Values

#### ECC

Error Correction Code

#### **EEMBC**

Embedded Microprocessor Benchmark Consortium

#### $\mathbf{ELF}$

Executable and Linkable Format

#### **EMFI**

Electromagnetic Fault Injection

#### **FIB**

Focused Ion Beam

#### FG

Foreground

#### **FPGA**

Field-Programmable Gate Array

#### **GPIO**

General-Purpose Input/Output

#### HFI

Hardware Fault Injection

#### HDMI

High-Definition Multimedia Interface

#### HPC

Hardware Performance Counter

#### ISR

Interrupt Service Routine

#### ISO

International Organization for Standardization

#### **JTAG**

Joint Test Action Group

#### $\mathbf{LFI}$

Laser Fault Injection

#### $\mathbf{LED}$

Light Emitting Diode

### LU

Lower-Upper

#### matrix01

Matrix Arithmetic

#### MCR

Move to Coprocessor

#### MBU

Multi-Bit Data Upset

#### **MITH**

Multi-Instance Test Harness

#### **MRC**

Move from Coprocessor

#### **NIST**

National Institute of Standards and Technology

#### $\overline{NMR}$

N-Modular Redundancy

os

Operating System

**OTA**

Over-The-Air

PC

Personal Computer

$\mathbf{PC}$

Program Counter

#### PCA

Principal Component Analysis

#### **PMCR**

Performance Monitor Control Register

#### **PMCNTENSET**

Performance Monitor Count Enable Set

#### PMU

Perfomance Monitoring Unit

#### **PMSELR**

Performance Monitors Event Counter Selection Register

#### **PMXEVCNTR**

Performance Monitors Event Count Register

#### **PMXEVTYPER**

Performance Monitors Event Type Select Register

#### Pmod

Peripheral Module

#### **POSIX**

Portable Operating System Interface

#### **PRNG**

Pseudorandom Number Generator

#### **PYNQ**

Python on Zynq

#### **QEMU**

Quick Emulator

#### RAM

Random Access Memory

#### RDR

Remote Data Request

#### rspeed01

Road Speed Calculation

#### **RTOS**

Real-Time Operating System

#### **SACRES**

Safety-Critical Real-Time Embedded Systems

#### SBU

Single-Bit Data Upset

#### SDK

Software Development Kit

#### SDC

Silent Data Corruption

#### **SECDED**

Single Error Correction/Double Error Detection

#### **SEU**

Single Event Upset

#### $\mathbf{SFI}$

Software Fault Injection

#### **SMOTE**

Synthetic Minority Over-sampling Technique

#### SoC

System on a Chip

#### $\mathbf{SRAM}$

Static Random-Access Memory

#### **SUMS**

Software Update Management System

#### **TARA**

Threat Analysis and Risk Assessment

#### TCB

Task Control Block

#### TDC

Top Dead Center

#### TCL

Tool Command Language

#### TMR

Triple Modular Redundancy

#### t-SNE

t-distributed Stochastic Neighbor Embedding

#### UNECE

United Nations Economic Commission for Europe

#### VHDL

VHSIC Hardware Description Language

## $\mathbf{VLSI}$

Very-large-scale integration

## V&V

Verification and Validation

## XSCT

Xilinx Software Command Line Tool

## Chapter 1

## Introduction

### 1.1 Motivation

In recent years, several international standards for security and safety have been integrated into the traditional lifecycle development process. In this context, the automotive industry is among the sectors that have experienced the most significant impact. Some key standards are outlined below:

- ISO/SAE 21434:2021 Road Vehicles: Cybersecurity Engineering [1]: It establishes a framework for cybersecurity management throughout the product lifecycle. It also addresses the problem of standardizing roles and responsibilities during product development and emphasizes the importance of executive management's commitment to cybersecurity by providing specific guidelines. A new introduction of this regulation is the Threat Analysis and Risk Assessment, which provides a systematic approach to assess the cybersecurity risks.

- UNECE Regulation No. 155 (R155)[2]: This regulation focuses on the vehicle lifecycle, including the supply chain. Suppliers should adopt the secure by design approach, including cybersecurity management from the early stages of development. It also requires the implementation of a Cybersecurity Management System to ensure protection against cyber threats.

- UNECE Regulation No. 156 (R156)[3]: It is complementary to R155, and the purpose of this regulation is to ensure secure software updates throughout

the vehicle's lifetime. It requires the deployment of Software Update Management System which ensures that software updates are delivered securely, authenticated, and traceable. This is particularly challenging but necessary, given the increasing reliance on Over-The-Air updates in modern vehicles.

• ISO/SAE 24089:2023 — Road Vehicles: Software Update Engineering [4]: It complements UNECE-R156 by defining processes for planning, developing, verifying, validating and distributing software updates. By applying the standard, manufacturers can minimize risks introduced by frequent software changes.

Current standards and regulations emphasize the need for safety and security in modern vehicles: to address this necessity, Verification and Validation techniques and fault injection methods are widely used [5, 6]. These methods help evaluate safety in critical systems, and systematic test case analysis is essential for identifying and addressing potential failures.

The growing demand for improved reliability analysis and fault detection in the automotive sector drives the research and development presented in this thesis.

## 1.2 Verification and Validation

V&V are two complementary processes used to determine whether a product, service, or system satisfies its requirements and fulfills its intended purpose [7]. A key aspect of this process is that verification and validation should be considered as *independent* activities, meaning that they are ideally performed by an external entity rather than by the development team itself [8, 9]. Although the terms are often used interchangeably in practice, they describe distinct objectives and rely on different methodologies:

- Verification: it focuses on checking that the system has been built according to its design specifications. It can be performed at different stages of the development cycle, using procedures appropriate to each phase. Importantly, verification is not limited to the final stages; on the contrary, it should be applied as early as possible. From both a security and an economic perspective, detecting flaws in the early phases is crucial, since correcting them later may become significantly more costly and time-consuming [10].

- Validation: it refers to the set of activities used to demonstrate that the system, once implemented, actually meets the needs and expectations of the

end users in its operational environment. It includes the testing and validation of the actual product [10].

As demonstrated by the literature [5, 6], fault injections can be used in the V&V process of embedded automotive software as they enable assessing system reliability, evaluating fault tolerance, and identifying vulnerabilities.

#### 1.3 Thesis Overview

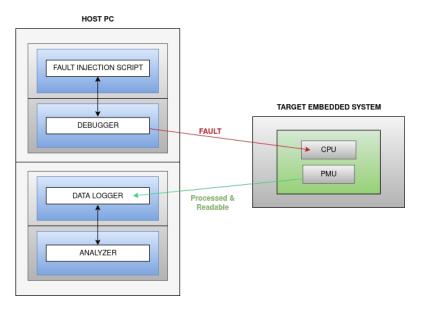

**Figure 1.1:** Experimental setup: fault injection via JTAG and PMU data acquisition on the PYNQ-Z2.

This thesis investigates the effects of fault injections on a target system and provides a comprehensive reliability analysis using automotive benchmarks from the Embedded Microprocessor Benchmark Consortium MultiBench<sup>TM</sup> Multicore Benchmark Suite[11]. Building on the work of [12, 13], which introduced a fault injection framework for Safety-Critical Real-Time Embedded Systems applications, this thesis enforces the usage of HPC-based monitoring and proposes an environment as close as possible to a real-time scenario. The environment is built by developing test cases in which multiple automotive benchmarks are executed, using specific scheduling algorithms provided by FreeRTOS. This setup is fundamental, since automotive systems perform several tasks in parallel. The correct profiling of

the target system is evaluated using the Hardware Performance Counters special-purpose registers, which track architectural events in the modern microprocessor. These registers are collected from the Perfomance Monitoring Unit using the developed fault injector. The ARM Cortex-A9 PMU provides six counters to gather statistics on the operation of the processor and memory system, and each counter can count any of the 168 events available [14]. This approach is portable and innovative thanks to the fault injector that can collect valuable data to enable better anomaly detection: common examples of trackable events are *cache misses*, instruction executed or branch misprediction. Although the proposed framework is highly modular and generalizable, the target system tested during the thesis is an Xilinx Pynq-Z2 board, built around the Xilinx Zynq 7020 System on a Chip.

#### 1.3.1 The basic workflow

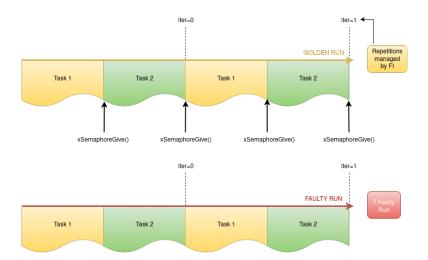

The workflow adopted consists of two different phases:

- The workload is first executed without any fault injection. The results of this fault-free run (called *golden run*) are stored and later used as a reference for comparison with subsequent executions;

- The workload is then re-executed on the benchmark selected as the injection target. Faults are injected through the board's debug interface, and multiple repetitions and iterations (the difference is explained in chapter 4) are performed in order to collect the architectural events required for the analysis.

Figure 1.2: Basic workflow proposed in the experiments

The setup phase is managed by the fault injector, implemented as a Python script, which allows precise targeting of the injections. In practice, this means that faults can be injected randomly into one of the two benchmarks executed, and their effects can then be evaluated. After executing the campaigns, the collected data are transformed into a format suitable for machine learning, which can aid in training models for fault detection purposes.

### 1.4 Structure of the Thesis

The thesis is organized into the following chapters:

### Chapter 1 — Introduction

This chapter introduces the context of the research, outlines the motivations and objectives, and describes the specific contributions made to the existing framework.

## Chapter 2 — Background

This chapter provides an overview of the theoretical background necessary for this research, including definitions of fault, error, and failure, as well as a taxonomy of fault injection techniques. It also reviews the state of the art, with particular emphasis on the framework proposed in [12, 13], which serves as the foundation for the developments presented in this thesis.

## Chapter 3 — Target Platform

Describes the tools and technologies used during this thesis. It provides architectural information on the target platform and its main components and also addresses the key features of Real-Time Operating System.

## Chapter 4 — Implementation Details

This chapter presents the design and implementation of the fault injection campaigns, including the system architecture, HPC-based monitoring integration, and

key improvements over previous work.

## Chapter 5 — Experimental Setup and Evaluation

This chapter is divided into two parts: the first part presents the setup and results of the fault injection campaigns, while the second part covers the preprocessing steps and data visualization of the resulting dataset.

## Chapter 6 — Conclusions and Future Work

This chapter summarizes the personal contributions to the framework used, discusses the main findings, and outlines possible directions for future research, particularly regarding the extension of fault injection techniques and the application of machine learning for anomaly detection.

## Chapter 2

# Background

This chapter provides an overview of the main concepts required to understand the choices behind the implementation and the terminology used in this thesis. It discusses a structured taxonomy that positions fault injection as a central concept for dependability evaluation and then provides details about the framework developed in [12, 13] that is utilized in this thesis.

## 2.1 Dependability

Dependability [15, 16] can be considered as the system's ability to perform its required function consistently and continuously, and it refers to the operational requirement of a system. Although often associated with modern computing, this is an old concept that first appeared in 1822 in the context of Babbage's Calculating Engine[17], even before the first generation of electronic computers. Some of the definitions of dependability are provided as follows:

- IFIP WG 10.4 [18]: "[..] the trustworthiness of a computing system which allows reliance to be justifiably placed on the service it delivers [..]";

- IEC IEV [19]: "Dependability (is) the collective term used to describe the availability performance and its influencing factors: reliability performance, maintainability performance, and maintenance support performance";

- Laprie [20]: "Trustworthiness of a computer system such that reliance can be placed on the service it delivers to the user".

As can be understood by these definitions, the property of dependability is highly related to different attributes such as **reliability**, **availability**, **safety**, and **security**.

#### 2.1.1 A taxonomy of Dependability

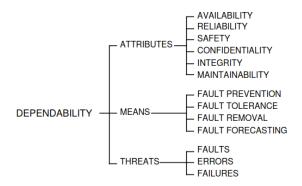

A detailed taxonomy of the fundamental concepts of dependability was presented by Avizienis et al. in 2001 [15]. According to the authors, dependability is structured into three main components: **threats**, **means**, and **attributes**.

Figure 2.1: The dependability tree from [15]

#### Attributes

The dependability tree identifies several key attributes: availability, reliability, safety, confidentiality, integrity, and maintainability. These attributes can be interpreted as the properties that characterize a system from the standpoint of dependability. It is important to note that the Confidentiality, Integrity and Availability triad - although fundamental to information security - is not sufficient by itself to guarantee dependability. Dependability should be understood as a probabilistic and inherently uncertain property, due to the possible presence of faults and their propagation into errors and failures [15].

#### Means

Avizienis et al. [15] also introduce the *means* to achieve dependability, introducing the families of techniques and methods employed to mitigate the impact of faults

on a system[21]:

- Fault Prevention: techniques aimed at preventing the occurrence or introduction of faults. These approaches can substantially reduce the likelihood of faults, but often involve significant cost and effort [22]. Examples are rigorous development processes, design reviews, or shielding.

- Fault Tolerance: techniques that enable the system to deliver correct service in the presence of faults. This is particularly crucial in SACRES, where service continuity must be preserved despite errors [22]. Examples are redundancy, error detection, and recovery.

- Fault Removal: techniques to reduce the *number* or the *severity* of faults, through verification, testing, debugging, and corrective maintenance [22].

- Fault Forecasting: techniques to estimate the current number of faults, their future incidence, and their potential consequences [22]. Typical examples are: reliability modeling, statistical testing, and field data analysis.

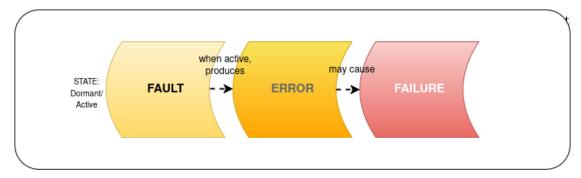

#### **Threats**

A threat can be defined as a potential danger to a computer system that may result in the interception, alteration, obstruction, or destruction of computational resources, as well as any other form of service disruption [23, 24]. When a threat damages a system asset, thereby preventing the system from delivering the expected service, a **failure** occurs. An **error** is defined as the part of the system state that may lead to a subsequent failure, whereas a **fault** constitutes the underlying cause of the error. A fault may be *active* when it actually produces an error, or *dormant* when it remains latent without immediate effect [20, 15, 25].

Because dependability reflects a computer system's ability to deliver a justifiably trusted service, it is essential to analyze both the causes of faults and their potential consequences to detect and mitigate anomalies. Furthermore, the concept of fault is central in legislative and regulatory contexts. International standards, such as **ISO 26262** [26], explicitly define frameworks and requirements to mitigate the presence and impact of faults in safety-critical systems.

#### 2.2 Faults in ISO 26262

Although first published in 2011 and revised in 2018, ISO 26262 remains particularly significant, as it requires organizations to provide *sufficient evidence* of compliance with safety requirements, and fault injection techniques can be used effectively to offer such evidence. According to *ISO document 10303-226* [27], a fault is defined as an abnormal condition or defect at the component, equipment, or subsystem level which may lead to a failure. A fault is active when it causes an *error*; otherwise, it is *dormant*. In this definition, there are some key concepts linked to faults:

• Failure: the event in which the service delivered by the system deviates from the expected correct one;

Figure 2.2: Relationship between Fault, Error, and Failure

A fault occurring on a target device does not always result in an error; often, faults remain inactive and have no observable effects. When a fault causes a temporary error, it is classified as a *soft error*.

#### 2.2.1 Soft Errors

Soft errors are transient faults that occur in electronic devices due to external or internal factors, causing temporary changes in the device's state or behavior. They can reverse or flip the data state of a memory cell, register, latch, or flip-flop; however, these disturbances do not permanently damage the circuit, which can still correctly store data once new values are written [28, 29].

Despite the transient nature of the fault, *soft errors* are becoming a concern in modern microprocessors, due to the increased sensitivity of smaller transistor

geometries and lower operating voltages. Under these conditions, circuits become more vulnerable to perturbations such as cosmic radiation, electrical noise and interference, as well as variability or defects introduced during manufacturing [30].

Figure 2.3: Causes of soft errors in modern microprocessors

Soft errors include Single Event Upsets, which can be further categorized into Single-Bit and Multi-Bit Data Upsets.

#### Single-Bit Data Upset

A Single-Bit Data Upset occurs when a high-energy particle, such as a cosmic ray or a neutron, strikes a sensitive region of a semiconductor device, altering the charge stored in a memory cell or flip-flop. The event changes the logical state of the storage element, from '0' to '1' or vice versa. In sequential logic, such as flip-flops, the upset manifests itself as a single erroneous bit, which is usually overwritten during the next valid clock cycle. While in many non-critical applications the effect of an SBU may be negligible, in safety-critical or mission-critical systems even a single incorrect bit can compromise correctness [31].

In Field-Programmable Gate Array, SBU may occur both in user data and in the (typically SRAM-based) configuration memory. In the latter case, a flipped configuration bit can alter the programmed functionality, leading to persistent misbehavior or the propagation of corrupted data. Mitigation commonly combines configuration memory scrubbing[32] (periodic readback and correction) with Error Correction Code [31, 33, 34].

#### Multi-Bit Data Upsets

Multi-Bit Data Upset arises when a single high-energy particle simultaneously affects multiple adjacent storage elements, causing two or more bits within a memory word or logic element to flip [35]. MBUs are particularly critical in memories where physically adjacent cells map to the same logical word, since they can produce errors that exceed the correction capability of standard ECC, resulting in uncorrectable errors. The spatial correlation of MBUs is highly dependent on the device layout: for instance, in SRAM memories, if the cells of a logical word are placed close together, the likelihood of uncorrectable MBUs increases. Conversely, modern FPGA architectures often physically separate the SRAM cells belonging to the same logical word, thereby reducing the probability that MBUs will corrupt multiple bits in a way that cannot be mitigated [36, 31].

Mitigation strategies for MBUs include the use of interleaved memory architectures (to physically separate adjacent bits of the same logical word physically), more advanced ECC schemes capable of detecting and correcting multiple-bit errors, as well as architectural hardening techniques at the FPGA design level[31, 36, 37].

## 2.3 Mitigation Techniques

## 2.3.1 Classical Approaches: TMR and ECC

The primary mitigation techniques discussed in the literature include the following:

- Triple Modular Redundancy (TMR);

- Error Correction Code (ECC).

TMR is a fault-tolerant approach based on **N-Modular Redundancy**, in which three identical logic circuits are used to compute a specified Boolean function. Each circuit receives the same input data, and their outputs are compared through a majority-voting mechanism. In this way, even if one of the three circuits produces an incorrect result, the other two can correct it, ensuring that the fault is effectively masked. TMR technique is particularly effective in protecting against errors and introduces a small delay in the circuit. However, its main drawback is that it requires triplicate logic and additional circuitry, which results in more than three

times the original area [38].

ECC represents a set of techniques for detecting and correcting errors: the detection is enabled by adding redundant parity bits to the data. One of the most well-known examples is the family of Hamming Codes, which belongs to the linear error-correcting codes. The standard Hamming code can only detect and correct a single-bit error. Still, there are more powerful versions in which additional parity bits are added, a technique known as *Single Error Correction/Double Error Detection* (SECDED). ECC RAM commonly uses Hamming codes with SECDED to automatically correct single-bit errors and raise an alert when double-bit errors occur [39, 40].

#### 2.3.2 AI-Based Detection

More recently, AI-based approaches have been explored to enhance fault detection and prediction. Machine learning models trained on historical data have shown promising results in identifying patterns associated with potential failures, thereby improving the reliability and resilience of SACRES [41, 42].

## 2.4 Fault Injections Techniques

Different fault injection techniques have been introduced in the literature. The following sections analyze the most common approaches [43].

## 2.4.1 Hardware Fault Injection

Hardware Fault Injection involves techniques that deliberately introduce faults into the physical components of an electronic system to study their effects on system behavior. Several surveys and experimental studies [44, 45] group HFI methods into two broad categories:

• Contact (direct) HFI: the injector physically interfaces with the target to perturb its electrical conditions (e.g., via pin-level probes or by inserting the device into a manipulable socket); such methods enable relatively precise timing control but often require physical access to the target.

• Non-contact (indirect) HFI: the injector acts from outside the package using external stimuli—such as heavy-ion radiation or electromagnetic fields—to provoke faults without direct electrical contact.

Another common classification in the literature distinguishes techniques by their invasiveness, defined as the degree of physical alteration or risk of damage to the target: non-invasive, semi-invasive, and invasive. The following list summarizes the most common HFI techniques, with all information sourced from [46]:

- Clock glitching (non-invasive): the system clock is disturbed to create timing violations that may cause registers to capture incorrect values. Effects are typically non-deterministic, making it challenging to target precise internal locations.

- Voltage glitching (non-invasive): the supply voltage is momentarily perturbed (spikes or drops), altering logic timing and potentially inducing incorrect computations. As with clock glitching, reproducibility and spatial targeting are limited.

- Electromagnetic Fault Injection (non-invasive): focused electromagnetic pulses are applied externally to induce currents or voltage transients in on-chip circuits. EMFI can produce effects similar to voltage glitches, but, due to field dispersion, precise spatial targeting is challenging.

- Laser Fault Injection (semi-invasive): a laser beam is employed to inject localized energy into the die (after decapsulation or package thinning), producing controlled bit flips or timing faults. LFI enables finer spatial targeting compared to non-invasive techniques while remaining less destructive than invasive editing.

- Focused Ion Beam editing (invasive): semiconductor-editing equipment is used to physically modify the chip (e.g., cut/add interconnects) to create permanent alterations or to expose internal nodes for probing. FIB is highly targeted and powerful, but destructive and complex to perform.

Each technique represents a trade-off between cost, potential damage to the target system and the reliability of the obtained results. Non-invasive methods are generally easier to deploy and less destructive, but they provide limited spatial precision. Semi-invasive and invasive techniques, on the other hand, enable higher targeting accuracy at the expense of greater complexity, higher costs, and an increased risk of permanent modification.

Overall, HFI techniques yield highly reliable results because tests are conducted directly on the physical device under realistic operating conditions. This makes them particularly suitable for diagnostic purposes and for validating detection mechanisms. However, hardware-based fault injection is costly, requires specialized expertise, and carries the risk of permanently damaging the device under test. Additionally, many techniques have limited portability across different architectures, restricting their applicability in heterogeneous embedded environments.

#### 2.4.2 Software Fault Injection

SFI, on the other hand, introduces faults into a running software system. This technique is highly flexible: faults can be injected at multiple levels, including memory, registers, and even the operating system, which is otherwise difficult to analyze [43]. Although not considered intrusive, in real-time systems, where precise timing is essential for correct operation, software-level injections may disrupt normal system activity [47].

SFI techniques can be categorized by considering the trigger mechanism that produces the artificially generated fault or error, or the injection times. In this way, it is possible to distinguish according to [45, 48]:

#### • Injection Strategy

- **Time-based:** Faults are injected at predetermined time intervals. This technique is easy to implement non-intrusively, but limited in flexibility.

- Location-based: Faulty values are written into predefined memory locations. Suitable for memory corruption studies, but prevents dynamic control of the fault load.

- Execution-driven: Faults are triggered dynamically depending on the control flow. This approach allows realistic and complex fault models but does not apply to black-box applications.

#### • Injection Timing

- **Before runtime:** The program is modified before execution (e.g., source code mutation to insert software bugs).

- During runtime: Faults are injected while the program is executing.

- At loading time: Faults are introduced when external components are loaded, for example, via dynamic library binding or dependency injection.

The benefits of using software fault injection are numerous. They can be categorized as a flexible approach that enables extensive experimentation without the need for specialized hardware, eliminating the risk of damaging physical devices. Furthermore, it is cost-effective and can be easily extended to support new types of faults. The main drawbacks of software fault injection complement the strengths of hardware-based methods. Specifically, software-based approaches often offer limited observability and coverage, and it is more challenging to induce permanent faults.

#### Tools

In the literature, there are different tools that can be used to inject faults at the software level:

- BOND [49], a software-based fault injection system for COTS applications;

- **Xception** [50], a software-implemented fault injection tool for dependability analysis;

- MAFALDA [51], a fault injection environment for real-time COTS microkernel-based systems;

- DOCTOR [52], an integrated software fault injection environment.

Among the tools presented, *Xception* is the most interesting one for the thesis, because it exploits the debug unit of modern processors to inject faults. In the literature, there are few examples of SFI based on the debug unit, and a more precise approach will be presented in the next sections.

## 2.4.3 Other Categorization

The distinction between hardware-based and software-based fault injection alone is not sufficient. Fault injection techniques can also be categorized by the development phase in which they are applied [46]:

• Simulation-Based Fault Injection: faults are injected into high-level system models (often described in VHDL). This approach is particularly powerful

because it enables dependability evaluation in the early stages of development, as soon as a model is available.

- Emulation-Based Fault Injection: faults are introduced into an emulated environment rather than into real hardware. This approach relies on simulators such as QEMU or on FPGA-based platforms, and can reproduce scenarios like bit flips in memory or registers. It allows the analysis of system behavior under fault conditions without requiring a physical prototype.

- **Hybrid Fault Injection**: combines hardware and software-based techniques to leverage the advantages of both approaches.

#### 2.4.4 Classification of Faults

The observable effects of a fault can vary significantly and are typically classified as follows [53]:

- Crash: the program terminates abnormally;

- Hangs: the program enters in an unresponsive state;

- **Reboots**: the operating system reboots;

- Silent Data Corruption (SDC): the program continues to run, but the result of the computation is incorrect;

- **Benign**: the program outputs the correct result, and the fault does not affect the outcome.

Among these outcomes, detecting SDCs is particularly challenging: for this reason, different detection mechanisms have been developed and analyzed in the literature.

### 2.5 Related Works

Dependability evaluation constitutes a crucial step in the design of SACRES, as widely demonstrated in the scientific literature. Among the various approaches proposed in recent years, the framework presented in [12] is particularly relevant and forms the basis of the evaluation conducted in this thesis. The authors introduce a fault injection framework specifically designed for the reliability assessment of

SACRES. This framework aims to reproduce soft errors induced by environmental disturbances and analyze their effects through machine learning algorithms to enable the detection of malfunctions in the system's architecture.

## 2.5.1 High-Level Details

**Figure 2.4:** High-Level architecture of the fault injection framework presented in [12]

Figure 2.4 illustrates the high-level architecture of the proposed framework, which consists of two primary components: a Host PC and the embedded system under test. The framework employs a SFI mechanism based on the microprocessor's debug unit. While this method has been infrequently reported in the literature, its main advantage is the ability to inject faults at multiple levels, such as CPU registers, memory, and the operating system, with minimal overhead since execution must be halted for fault injection. In this context, the debug unit was the only viable option. In contrast to alternative techniques, this approach does not require code recompilation between executions following fault injection, as the code remains unchanged. Since the primary objective is to generate a dataset for machine learning-based assessment, this method is the most practical solution. Additionally, this approach guarantees experiment repeatability, which is critical for collecting architectural event data during execution (this requirement will be addressed in a subsequent section). The CPU debug unit operates in external mode using the JTAG protocol, which enables control of the debug phase of the target system from an external host and permits modification of CPU registers and memory.

The framework extends the traditional SBU approach introduced in [13] to support MBU. A key feature is the integration of the processor's PMU, which enables the collection of HPCs during execution. This capability allows the framework to combine functional correctness checks with a detailed analysis of micro-architectural events recorded at runtime.

The Host PC coordinates the fault injection campaigns through a Python-based script that interacts with the Xilinx Software Command Line Tool. On the target side, a Xilinx Zynq SoC running FreeRTOS executes the workload compiled into a ELF binary. The faults are injected either by selecting faults from a predefined list of location—time tuples (e.g., provided in a CSV file) or by generating them randomly at runtime. To ensure reproducible results, the random seeds used to initiate execution, as well as the golden outputs obtained in the fault-free runs are stored in the FPGA memory. Fault injection outcomes are classified according to the standard dependability taxonomies into Benign, SDCs, or crash/hangs.

## 2.5.2 Experimental Setup and Workflow

The experimental evaluation was carried out on a Pynq-Z2 board featuring a dual-core ARM Cortex-A9 and running FreeRTOS v.10. Benchmarks were selected from the MiBench suite, chosen for their diversity across application domains such as Automotive, Networking, Security, Office, Telecommunications, and Industrial Control. The subset considered includes:

- **SHA**, a hashing algorithm producing a 160-bit digest, widely used in cryptographic applications;

- Dijkstra, an implementation of the shortest-path algorithm on graphs;

- Quicksort, a sorting algorithm applied to arrays of strings;

- Rijndael, better known as AES, a block cipher for secure data encryption;

- BasicMath, which performs arithmetic operations often lacking hardware acceleration in embedded CPUs;

- Stringsearch, which performs pattern matching within a text.

These benchmarks were evaluated both individually and within multitask workloads managed by the FreeRTOS scheduler, resulting in 23 injection campaigns that covered injections into memory, CPU registers, and Program Counter.

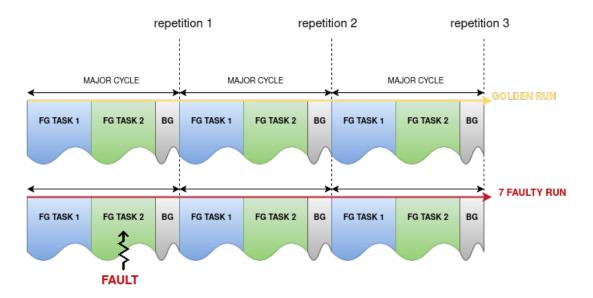

Figure 2.5: Software execution flow taken from [12]

The workflow, illustrated in Figure 2.5, is structured in two main phases. First, during the golden run, the host boots the target, supplies random input data to ensure reproducibility, and collects the golden output, used later for comparison. In the faulty run, the host activates an injection loop: for each iteration, it specifies the events to monitor, sets the injection breakpoint, and resumes execution. When the breakpoint is reached, faults are injected and execution continues until the end. The final output is then compared with the golden reference. If outputs coincide, the run is classified as Benign; if they differ, it is classified as SDC; and if execution fails to terminate within the timeout, it is labeled as Crash/Hang. The timeout is carefully calibrated to account for both OS boot and benchmark execution time, with additional margin to distinguish between minor timing deviations and genuine failures.

#### 2.5.3 Results

The main findings of the experimental campaigns can be summarized as follows:

- Faults injected into memory are mostly benign, owing to the large address space that reduces the likelihood of affecting critical regions;

- CPU register injections exhibit a higher susceptibility to *SDCs*, particularly in cryptographic workloads where intermediate values are more sensitive;

- PC injections are especially critical, frequently resulting in system crashes or significantly increasing the SDC rate.

In addition, HPC profiling demonstrated its effectiveness in distinguishing benign executions from faulty ones, thus confirming the potential of performance counters as indicators for the development of fault detection mechanisms in SACRES.

# Chapter 3

# Target Platform

This chapter introduces the platform and tools used to conduct this thesis. It opens with a description of the target system employed in the experimental work and highlights the principal features of FreeRTOS, the Real-Time Operating System under which the benchmarks are executed.

#### 3.1 Target Hardware Platform

Figure 3.1: Pynq Z2 board [54]

The target hardware platform used for the experimental setup is a Pynq-Z2[54] 3.1, which is a FPGA development board, based on ZYNQ XC7Z020. It supports Python on Zynq (PYNQ, an open-source framework from Xilinx that enables the customization of Xilinx ZYNQ SoCs without fully rely on the design programming

logic circuit. PYNQ-Z2 board integrates Ethernet, HDMI Input/Output, MIC Input, Audio Output, Arduino interface, Raspberry Pi interface, 2 Pmod, user LED, push-button and switch. It is designed to be easily extensible with Pmod, Arduino, and peripherals, as well as general purpose General-Purpose Input/Output pins.

#### 3.1.1 The Cortex-A9 processor

The processor exhibited by the board is an ARM Cortex-A9[55, 56]: it belongs to the Cortex-A series, which can support complex OS and multiple user applications, available in different smartphones and digital devices. It is effective and powerful, suitable for a large number of applications and constitutes the perfect choice for applications where energy efficiency is necessary.

ARM Cortex-A9 is a 32 bit multi-core processor, based on ARMv7 architecture and on the implementation of *Thumb-2* instruction set, which reduces the size of programs with little impact on performance. Moreover, it presents the following features:

- High-Efficiency Superscalar Pipeline;

- NEON Media Processing Engine;

- Optimized Level 1 Caches;

- Thumb-2 Technology;

- Floating-point unit.

Among these interesting characteristics, the PMU available is the most relevant one. In general, PMU is commonly used for performance analysis and debugging, providing a wide range of *events* that can be monitored for performance profiling. In general, most of the events provided are common, however, each processor can define its own specific events.

In the case of Cortex A-9, as already reported in the introductory part, according to the Technical Reference Manual [55], PMU provides six counters to gather statistics on the operation of the processor and the memory system. Counters can be accessed from the internal CP15 interface as well as from the DAP interface. A clear overview of the registers are reported in the table below:

Name Type Description PMXEVCNTR0-5 RWEvent Counter Register **PMCCNTR** RWCycle Count Register PMXEVTYPER0-5 RWEvent Type Selection Register **PMCNTENSET** RW Count Enable Set Register **PMCNTENCLR** RW Count Enable Clear Register **PMINTENSET** RW Interrupt Enable Set Register RWPMINTENCLR Interrupt Enable Clear Register **PMOVSR** RW Overflow Flag Status Register **PMSWINC** WO Software Increment Register **PMCR** RWPerformance Monitor Control Register **PMUSERENR** RWUser Enable Register

Table 3.1: Cortex-A9 PMU Registers

Among them, the most interesting ones are the following:

RW

**PMSELR**

• Performance Monitor Control Register (PMCR): which enables/disables the PMU, controls reset of counters and sets some global modes;

Event Counter Select Register

- Event Counter (PMC): a set of 32-bit counters that can be programmed to track specific event, typically we have 6 events counters and 1 cycle counter;

- Cycle Counter (CCNT): a dedicated counter for counting CPU clock cycles;

- Performance Monitors Event Type Select Register (PMXEVTYPERn): each counter has a register that defines which event it should monitor.

- PMU Interrupts: Counters can trigger an interrupt on overflow.

Event Selection Registers are very useful because they enable the selection of the Performance Monitor Count Register to Count. They can be accessed in this way:

```

MRC p15, 0,<Rd>, c9, c13, 1; Read PMXEVTYPER Register MCR p15, 0,<Rd>, c9, c13, 1; Write PMXEVTYPER Register

```

More details will be provided in the later chapters, for managing and configuring the PMU.

#### 3.2 Real-Time Operating System

RTOS is an operating system specifically designed to support real-time computing applications, where tasks must meet strict deadlines. Due to its characteristics, an RTOS is commonly used in embedded systems and automotive context where being *event-driven* and *preemptive* is important, meaning that the scheduler can assign different priorities to tasks and preempt lower-priority tasks in favor of higher-priority ones [57, 58, 59].

For the proposed framework, the choice fell on RTOS according to several factors:

- Faithfulness to the automotive context: in this scenario, RTOS are largely used and in most of the cases they represent the only choice.

- Reproducibility for profiling: an RTOS is easy and predictable, so that reproducibility can be ensured to reply the experiments and collect as much information as possible for a correct profiling.

#### 3.2.1 Tasks

Real-time applications are typically structured into *periodic tasks*, which can be defined as a sequence of instructions designed to perform specific functions. Tasks are managed and scheduled by the operating system and, depending on the criticality of the functions they implement, can be assigned different priorities: tasks with higher priority are executed before those with lower priority. In general, each task comprises an initialization phase followed by an *infinite loop*, within which the required functions are repeatedly executed.

When an operating system is capable of managing and executing multiple tasks concurrently, this capability is referred to as multitasking. In the case of a RTOS, true parallel execution of tasks on a single-core processor is not possible. Instead, the RTOS employs scheduling algorithms to allocate CPU time among the available tasks. A **schedule** specifies the strategy adopted by the operating system to assign resources and determine the execution order of tasks. Each task can exist in one of four states: **ready**, **running**, **suspended**, or **blocked**. The scheduler within the RTOS manages the transitions between these states according to the adopted scheduling policy.

Two main types of schedulers can be distinguished in RTOS: **preemptive** and **cooperative**. A preemptive scheduler allows a task to be interrupted during its execution if a task with higher priority becomes ready, ensuring that the most critical task is executed immediately. Conversely, a cooperative scheduler does not permit preemption: even if a higher-priority task is ready, it must wait until the currently running lower-priority task has completed its execution before being scheduled.

#### Scheduling Algorithms

As previously introduced, a **scheduling algorithm** is defined as a set of rules that determine, at any point in time, the order in which tasks are executed. One of the simplest approaches is *static scheduling*, where decisions are based on fixed parameters assigned to tasks prior to their activation. Other relevant examples include:

- **Timeline scheduling**: tasks are organized within a predefined timeframe, called the *major cycle*. Each task is executed during its dedicated *minor cycle*. This is one of the simplest and most deterministic scheduling strategies.

- Round-Robin scheduling: ensures fairness by allocating fixed time slices to tasks belonging to the same priority level. Once a task exhausts its time slice, the scheduler moves to the next task in the queue.

- Rate-Monotonic Scheduling: a fixed-priority scheduling algorithm in which tasks are assigned priorities based on their periods: the shorter the period, the higher the priority. It is optimal among static-priority scheduling policies.

- Earliest Deadline First: a dynamic-priority scheduling algorithm in which tasks are scheduled according to their absolute deadlines. This approach is particularly suitable for real-time systems, where meeting strict timing constraints is critical.

#### 3.2.2 FreeRTOS

FreeRTOS is a widely adopted open-source OS designed for embedded systems [60]. It is particularly suitable for microcontrollers and applications characterized by limited memory resources and constrained computational capabilities. A basic FreeRTOS application is typically structured around tasks, which represent

independent units of execution. Two types of tasks can be distinguished: the *standard tasks*, defined by the user to perform specific application functions, and the *idle task*, which is automatically created by the kernel and executed whenever no other tasks are ready to run.

In the case of standard tasks, the user must specify several parameters at creation time, including a unique name for identification, the task function to be executed, its priority, and the stack size. Task priority is expressed as a positive integer value, ranging from 0 (the lowest priority, typically reserved for the idle task) to configMAX\_PRIORITIES - 1. The constant configMAX\_PRIORITIES is defined in the configuration file FreeRTOSConfig.h and determines the maximum number of priority levels available within the system.

The scheduler of FreeRTOS supports different policies for task execution. By default, the scheduler operates in a preemptive mode with time slicing, but there is also the possibility to disable timeslicing or configure a cooperative scheduling approach. Regardless of the chosen policy, when two or more tasks share the same priority level, the *Round-Robin* mechanism is applied to determine their execution order.

```

/* FreeRTOSConfig.h */

2 #define configUSE_PREEMPTION 1 // preemption enabled

3 #define configUSE_TIME_SLICING 1 // time-slicing enabled

```

#### 3.2.3 FreeRTOS Fundamentals

FreeRTOS provides a set of primitives for synchronization and communication between tasks. These mechanisms are essential to coordinate concurrent activities, manage access to shared resources, and synchronize tasks with interrupts.

#### Binary Semaphores and Mutexes

A binary semaphore is a synchronization primitive that can assume only two values, typically 0 or 1. It is often used to signal events, for example from an Interrupt Service Routine to a task. In FreeRTOS, when multiple tasks attempt to take the same semaphore, the scheduler ensures that the highest-priority task succeeds first. The API also allows specifying a *block time*, which is the maximum number of

system ticks a task will remain in the *Blocked* state while waiting to acquire the semaphore.

A mutex (mutual exclusion object) is similar to a binary semaphore but includes a *priority inheritance* mechanism. This feature helps mitigate the problem of *priority inversion*, ensuring that lower-priority tasks holding a mutex do not unduly delay higher-priority tasks.

#### Task Notifications

In addition to semaphores, FreeRTOS provides lightweight synchronization through task notifications. A task notification can be considered as a binary or counting semaphore built directly into each TCB. This approach reduces RAM consumption and improves performance. Functions such as ulTaskNotifyTake() or ulTaskNotifyTakeIndexed() are used in place of xSemaphoreTake(), with the parameter xClearOnExit set to pdTRUE to emulate the binary semaphore behavior.

#### The RTOS Tick

When a block time is specified (for example, when a task is put to sleep), FreeRTOS measures the waiting period using the system *tick*. A timer interrupt, known as the *RTOS tick interrupt*, periodically increments the kernel tick count. This allows the kernel to measure time with a resolution determined by the tick frequency. Each time the tick count is incremented, the scheduler verifies whether it is time to unblock any tasks whose delay periods have expired.

#### The tasks.c File

The file tasks.c is the core of the FreeRTOS kernel. It implements task management and scheduling, including the creation and deletion of tasks, context switching, and state transitions. Moreover, it provides the implementation of TCB and defines the mechanisms for handling priorities and scheduling policies.

# Chapter 4

# Implementation Details

After reviewing the literature on fault injection techniques, this chapter describes the implementation of the proposed framework. It first presents the benchmarks used in the single-workload campaigns and then proceeds describing the multi-workload campaign.

## 4.1 AutoBench - Automotive Industrial Benchmarking

The benchmarks selected to carry out the experiments and ensure an environment as close as possible to the real one are provided by the *Embedded Microprocessor Benchmark Consortium* [61]. AutoBench is suite of benchmarks created to evaluate the performance of microprocessors and microcontrollers in automotive, industrial and general-purpose applications. It consists of sixteen benchmarks, including basic automotive algorithms and signal processing algorithms: a brief description of the algorithm is proposed in appendix.

The choice fell on AutoBench because it is one of the most adopted automotive benchmark suites, used in both academia and industry. It integrates a set of automotive workloads with the EEMBC Multi-Instance Test Harness, a framework designed to ensure portability across a wide range of multicore processors and operating systems. MITH employs a POSIX-compliant, thread-based API to provide a common programming model: benchmarks interact with the harness through an abstraction layer, which offers a flexible interface for testing heterogeneous,

thread-enabled workloads.

Each benchmark is composed of three main elements: **workload**, **dataset**, and a **Cyclic Redundancy Check**. The workload corresponds to the algorithm under test, which may be implemented as single-threaded or multi-threaded. The dataset consists of the input data supplied to the workload, typically available in two different sizes (4MB and 4KB). Finally, the CRC is used to verify the correctness of the computation by comparing the produced output against a reference signature.

Among the sixteen algorithms available in the EEMBC AutoBench suite, the following benchmarks were selected to be included in the framework: Angle to Time Conversion, CAN Remote Data Request, Matrix Arithmetic, and Road Speed Calculation. These benchmarks were chosen because, on one side, they reflect typical computational patterns found in automotive applications and provide sufficiently complex scenarios to emulate realistic operating conditions, including communication between interfaces. On the other, they are diverse enough to enable a comprehensive analysis of different system aspects, ranging from arithmetic-intensive workloads to communication and control-oriented tasks. Although all four benchmarks were integrated, the experiments carried out focused exclusively on a2time and rspeed01.

The selected benchmarks were integrated in two configurations: single and multi-workload setup. The single-workload campaign refers to the execution of a single workload (in our case either a2time or rspeed01); while multi-workload campaign refers to the execution of multiple workloads (both a2time and rspeed01), leveraging the FreeRTOS scheduler. For the single-workload, the existing framework was just extended to include new test cases and to enable the fault injector to target the newly added tasks. For the multi-workload configuration, it was necessary to create a scheduling infrastructure that manages the chosen benchmarks concurrently under FreeRTOS, while ensuring reproducibility and randomness typical of the existing framework. In the experiments, we considered two concurrent tasks and injected faults into one of them, but the infrastructure can easily be extended to include more than two tasks.

#### 4.1.1 Benchmark Structures

Each AutoBench benchmark follows a standardized execution flow, structured around a set of core functions. This standardization is particularly convenient because it allows to understand the workflow of data around the execution and the

basic operation performed by the algorithm. The set of core functions are provided below: the \* can be substitute with the name of the benchmark that is executed.

- define\_params\_\*: configures the general parameters of the benchmark, such as the dataset to be used and the reference CRC associated with that dataset. The input file containing the dataset is read and stored into RAM. This function is called once before any execution, regardless of the number of runs performed.

- bmark\_init\_\*: initializes the parameters for the current run, allocates the memory required for the output file, and resets all counters. This function must be called at the beginning of each new iteration.

- t\_run\_test\_\*: implements the core benchmark algorithm. It executes the workload in a loop, repeating the computations across multiple iterations without reinitializing the parameters. Results are overwritten in the output buffer at each iteration.

- bmark\_verify\_\*: computes the CRC of the output data on the fly and compares it with the reference CRC provided during parameter definition. The function returns a boolean value indicating whether the results are correct.

- bmark\_fini\_\*: finalizes the benchmark run by releasing the memory allocated for the output file, effectively performing the inverse operation of bmark\_init\_\*.

- bmark\_clean\_\*: completely clears the memory and resets the variables used by the benchmark, performing the inverse operation of define\_params\_\*.

To satisfy the requirements needed to carry out the experiments, some of the functions were slightly modified, but they do not change the overall structure.

#### 4.1.2 Benchmark Descriptions

The description of the operation performed by the algorithms integrated in the framework are reported as follows. Details are directly taken from the EEMBC AutoBench Data Book [62].

#### Angle to Time Conversion

This benchmark models an embedded automotive application in which the processor processes input from a toothed wheel mounted on the engine crankshaft. Each tooth produces a pulse, and the time interval between consecutive pulses provides a measure of the crankshaft's angular velocity (engine speed). From this information, the benchmark estimates the crankshaft position relative to the *Top Dead Center* reference, computes the instantaneous engine speed, and converts the tooth pulses into an accurate crankshaft angle expressed in linear time from TDC.

At the start of each iteration, the kernel reads a counter value from the input dataset and subtracts the previous value to obtain the elapsed time between two consecutive teeth. As long as TDC is not detected, the tooth counter is incremented to track progress through the revolution. When the counter matches the firing angle associated with a cylinder, the benchmark simulates an ignition event by generating the corresponding firing time. Upon detecting the next TDC, the tooth counter is reset and the cycle repeats.

The a2time benchmark can be classified as **CPU-centric**. Its workload is dominated by arithmetic and logical operations rather than memory accesses. The algorithm performs continuous numerical conversions from crankshaft angle to linear time, involving subtraction, multiplication, and division on a small set of variables.

#### CAN Remote Data Request

This benchmark emulates an automotive communication workload in which nodes connected through a Controller Area Network exchange messages. The scenario modeled is the reception of a Remote Data Request message, which is broadcast to all nodes. Each node inspects the message identifier to determine whether it is responsible for the requested data. If so, the node retrieves the appropriate information and places it back on the network to be received by the requester.

At the kernel level, the benchmark processes messages from a simulated receive buffer by checking their identifier fields. Messages that are not relevant are discarded, while relevant ones are either stored locally or, in the case of an RDR message, used to fetch the corresponding data. The retrieved data is then written into a simulated transmit buffer, ready to be sent back across the network to the original requester.

#### Matrix Arithmetic

This benchmark represents an automotive and industrial workload characterized by intensive matrix arithmetic. The kernel operates on  $n \times n$  input matrices, performing an Lower-Upper decomposition as its primary computation. In addition, it evaluates the determinant of the input matrix and computes a cross product with a second matrix, thereby stressing the system with a mix of linear algebra operations: these simple calculations are nowadays the basic foundations of AI.

#### Road Speed Calculation

This benchmark models an automotive workload in which the processor periodically computes vehicle speed from differences between timer counter values. To mitigate noise, the raw values are filtered, and the algorithm must also handle corner cases such as counter rollover, abrupt variations in measurements, or the absence of increments when the speed is zero (to avoid indefinite waiting).

The benchmark combines arithmetic operations with control-flow routines. The arithmetic part relies on basic operations (addition, subtraction, multiplication, and division), which may represent a performance bottleneck on low-end microcontrollers. Conversely, in more advanced processors, efficiency is influenced not only by raw arithmetic throughput but also by pipeline behavior, since a considerable number of compare and branch instructions are executed. Processors that balance both aspects tend to achieve the best performance on this workload.

# 4.2 Integration into the single workload campaigns

To correctly integrate the benchmarks into the proposed framework, both randomness and reproducibility must be ensured. Randomness permits to increase the coverage during fault-injection campaigns, while reproducibility allows replaying the same fault across iterations to collect the architectural events. In our setup, inputs are sampled uniformly using rand() and the seed is derived from the clock cycle count or Cycle Count Register value to achieve randomness. On the other side, reproducibility is ensured because each seed used for the input generation is stored in a dedicated memory region separated from the main memory, that remains intact also after the reboot. Moreover, for AutoBench benchmarks that

provide a dataset, the stored seed is also used to deterministically select dataset indices, ensuring identical elements are replayed across experiments.

The interaction and the organization between host and target is consistently divided in *golden run* and *faulty run*. The phases are reported as follows:

- The host initiates the campaign by rebooting the target system to ensure consistency and that injections begin from a clean, deterministic state. In respect to the previous framework, the boot procedure includes additional checks, since injecting faults into a corrupted environment may produce unpredictable behavior or cause crashes.

- Then, the host configures the target for the injection by generating a fault list composed of tuples that identify the injection location (address and register). Injections may target memory locations or CPU registers; each specified location also indicates the particular bit position to be flipped.

- After the execution of the workload on the target system, a final breakpoint is established, necessary to read the HPCs from the PMU.

Once the workload is completed, the resulting golden output is saved for reference. During the faulty run, the previously stored inputs are read to execute the workload under injected faults. The faulty output is compared against the golden reference and the result is classified in *benign*, *SDC* or *crash/hang*.

The integration of new benchmarks in the proposed structure was necessary to extend the dataset previously obtained with new data from the Autobench benchmarks. Only in this way, it was possible to learn about the effectiveness and usefulness of the data collected employing the new test cases. Furthermore, the inclusion of benchmarks more faithful to the automotive context has allowed us to improve some practical aspects of the implementation that in the past had not had a great influence, but which would certainly have affected the performance of multiworkload-campaigns.

#### 4.3 Multi-workload campaigns

The execution of multiple workloads within the same campaign was realized thanks to the development of a new scheduling infrastructure. The infrastructure was designed to be highly customizable, supporting more than two concurrent workloads in future tests, and to remain controllable by the fault injector even though the target is rebooted at each injected fault. Customizability is achieved through the configuration data structures MultiBenchCfg\_t and MultiBenchCfgTLS\_t (more details about the code are provided in the next chapter), which provide a convenient and extensible way to set benchmark parameters. Controllability to repeated reboots is ensured by storing runtime configuration and control data in BRAM, this enables the injector to preserve and reapply settings across iterations. Another critical requirement was randomness, achieved by extending the previously described approach to the multi-workload setting. In this case, a per-benchmark local seed is derived from the iteration number and the benchmark index, ensuring deterministic reproducibility for each benchmark, while randomness is preserved because rand() is still used.

#### 4.3.1 High-level overview of MultiBench

The main components of a MultiBench campaigns are the following:

- benchList[]: an array of pointers to benchmark wrapper functions that determines which benchmark each task executes.

- demo(int golden): the demo entry point. It initializes the MultiBenchCfg\_t parameters by reading values written by the fault injector in BRAM and then calls runMultiBenchmark(&cfg).

- runMultiBenchmark(&cfg): performs sanity checks, allocates PMU vectors, creates semaphores used to orchestrate execution, spawns the worker tasks, and iterates the campaign for the number of iterations specified by the fault injector.

- multiBenchmarkTask(): waits for a notification to start, sets the execution context, runs the assigned benchmark, reads the PMU when the task is the injection target, stores the execution result, resets the PMU buffers, and releases the semaphore.

#### Configuration structure

The infrastructure relies on several ad-hoc *structs*. The MultiBenchCfg\_t configuration structure holds the global parameters of a campaign: benchList, the number of tasks (used for sanity checks), the global seed (provided by the fault

injector and used as the source for per-task local seeds), the number of iterations (the number of golden-run repetitions; one of these is randomly chosen as the injection target), and the target injection index (which indicates whether task 1 or task 2 will be the injection target). The WorkerParam\_t structure contains each task's local parameters, including a pointer to the global configuration, the task's benchmark index, a local seed, the number of iterations already executed, a semaphore used for synchronization, and the task handle.

# 4.3.2 Global Structure for HPC collection and task management

A common feature to preserve also in the multibench campaigns is the reproducibility, which is necessary to collect HPC meaningful for the analysis. In this case, since just one workload is target of the injections, the infrastructure allows to collect just the HPC of interests. In future works, it will be possible to interconnect the execution flows of the two benchmarks to emulate a real-time scenario, and to collect the HPCs of both tasks in order to analyze how a fault in one workload affects the other and to investigate their mutual interactions. From a practical point of view, the collection of HPC and the association of the gathered data with benchmark tasks, it was necessary to define some global variables: g\_numTask (the number of tasks), g\_pcVector and g\_numTaskVector. These variables are inizialized in the multibench file, but used internally in FreeRTOS tasks.c. In the operational flow, runMultiBenchmark initializes g\_numTask and allocates g\_pcVector (one slot per task): after creating the tasks, task numbers are stored in g numTaskVector. During the execution, PMU collection is integrated into the scheduler routines: an initial PMU snapshot is taken at scheduler start using the function (readPMU(pc init state)), and on each task switch-out a final snapshot (readPMU(pc\_fin\_state)) is read and the difference is accumulated into g pcVector[index]. To quickly determine whether the current TCB corresponds to a benchmark task, the helper function check\_currentTCB\_is\_bench\_task compares uxTaskGetTaskNumber(pxCurrentTCB) against the entries in g numTaskVector if not found it returns -1 and no collection is performed.

#### Advantages

This approach is, in practice, the only workable solution, since only the operating system has precise knowledge of when context switches occur. Moreover, other advantages are reported below: