#### Politecnico di Torino

Master's degree in Cybersecurity A.y. 2024/2025 Graduation Session October 2025

# Securing Aircraft Engine Control Units: Utilizing Embedded Board Security Features for Enhanced Protection

Supervisors:

Stefano Di Carlo Alessandro Savino Luca Schena Candidate:

Niccolò Lentini

#### Abstract

In the aerospace domain, where the concept of airworthiness and ensuring its continuity is fundamental, securing Engine Control Units (ECUs) is a critical objective to prevent system compromise with potentially catastrophic consequences. This work focuses on the implementation of robust security mechanisms for embedded avionics ECUs by leveraging the advanced hardware security features available on one from the NXP S32K family of microcontrollers used in both automotive and aerospace applications.

By examining this recent Automotive General Purpose ECU, the study demonstrates how embedded system security can be significantly enhanced through the strategic utilization of built-in hardware capabilities. Special emphasis in this work is placed on securing the software image loading process with appropriate verification and authentication and enforcing strict memory protection policies to ensure both the integrity and confidentiality of system data and code exploiting the cryptographic capabilities of the board.

The study begins with the modelling of a realistic case study for an avionic ECU, establishing a foundation for subsequent security analyses. A detailed threat assessment follows, adhering to most recent aerospace standards and regulations (e.g. DO-178C, DO-356, AIR7368) and employing frameworks like the Common Attack Pattern Enumeration and Classification (CAPEC) and the Embedded System Threat Modelling and Mitigation Methodology (EMB3D) to systematically identify and categorize potential vulnerabilities. Next, a comprehensive analysis of the necessary security measures is conducted to obtain adequate countermeasures against each threat condition. The implementation part follows a configuration and deployment strategy for hardware-assisted security mechanisms such as secure boot, cryptographic validation of application image, and memory region protection, features that are not only analyzed in terms of their technical configuration but also evaluated for their effectiveness in mitigating all the threats previously identified.

Experimental results confirm that the proposed approach strengthens the ECU's security reducing the attack surface. The use of on-chip security features contributes to a substantial increase in system resilience without introducing significant performance penalties.

In conclusion, this work provides a concrete contribution toward the development of safer and more secure avionics systems by proposing an architecture that exploits the native hardware security features of modern microcontrollers underscoring the critical role of hardware-assisted security in the design of next-generation ECUs.

# Table of Contents

| 1 | Avi | o Aero                                                                            | 5  |

|---|-----|-----------------------------------------------------------------------------------|----|

|   | 1.1 | Company overview and background                                                   | 5  |

|   | 1.2 | Latest Achievements                                                               | 7  |

|   |     | 1.2.1 AMBER Hybrid-Electric Propulsion Project                                    | 7  |

|   |     | 1.2.2 Catalyst engine                                                             | 7  |

| 2 | Sec | urity Regulations in Aerospace applications                                       | 9  |

|   | 2.1 | Airworthiness & Airworthiness Security                                            | 9  |

|   | 2.2 | DO-178C (Software Considerations in Airborne Systems and Equipment Certification) | 9  |

|   | 2.3 | DO-326B (Airworthiness Security Process Specification)                            | 10 |

|   | 2.4 | DO-356 (Airworthiness Security Methods and Considerations                         | 13 |

|   | 2.5 | SAE AIR7368 (Cybersecurity for Propulsion Systems)                                | 13 |

| 3 | Sta | te of the art in avionics product security                                        | 15 |

|   | 3.1 | Nowadays proposed solutions                                                       | 15 |

|   | 3.2 | Secure Electronic Control Units (ECUs)                                            | 15 |

|   | 3.3 | Data Communication Security                                                       | 16 |

|   | 3.4 | Real-Time Monitoring and Intrustion Detection                                     | 16 |

|   | 3.5 | Hardware Security Features                                                        | 16 |

|   | 3.6 | Software Security                                                                 | 16 |

|   | 3.7 | Redundancy                                                                        | 17 |

|   | 3.8 | Is aircraft physical security really necessary?                                   | 17 |

| 4 | Pro | educt Security Assessment                                                         | 19 |

|   | 4.1 | Use Case                                                                          | 19 |

|   | 4.2 | PSA Model                                                                         | 19 |

|   | 4.3 | Threat Repositories: CAPEC & MITRE EMB3D                                          | 21 |

|   | 4.4 | Scope definition & threat identification                                          | 23 |

|   | 4.5 | High Level Requirements Definition                                                | 27 |

|   | 4.6 | Starting Project Assessment Phase                                                 | 30 |

| 5 | The | eory Background                                                                   | 33 |

|   | 5.1 | Hash Functions                                                                    | 33 |

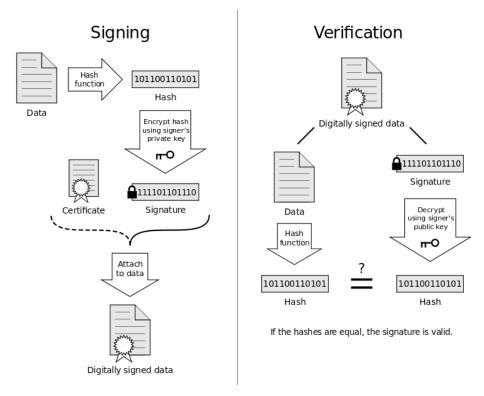

|   | 5.2 | Digital Signatures                                                                | 34 |

|   |     | 5.2.1 Elliptic Curve Digital Signature Algorithm (ECDSA)                          | 36 |

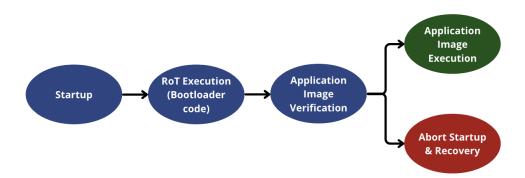

|   | 5.3 | Secure Boot                                                                       | 38 |

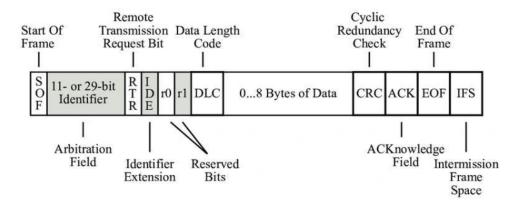

|   | 5.4 | Controller Area Network (CAN)                                                     | 39 |

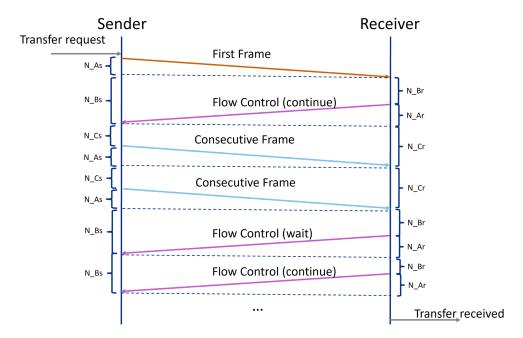

|   | 5.5 | CAN TP                                                                            | 40 |

|                 | 5.6                                    | Unified Diagnostic Services (UDS)                                                                                                                                                                                                                                                                                                                                                              | _                                      |

|-----------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 6               | <b>Lab</b> 6.1                         | Laboratory Setup Components                                                                                                                                                                                                                                                                                                                                                                    |                                        |

| 7               | <b>Pro</b> 7.1 7.2                     | gram Development         57           Project Structure         57           Execution flow         58           7.2.1 Key generation         58           7.2.2 Signature generation and Flashing Procedure Script         58           7.2.3 Signature Checking Procedure         59           7.2.4 Target Board Bootloader         62           7.2.5 Application Image Content         63 | 7<br>3<br>3<br>3<br>3<br>3<br>9        |

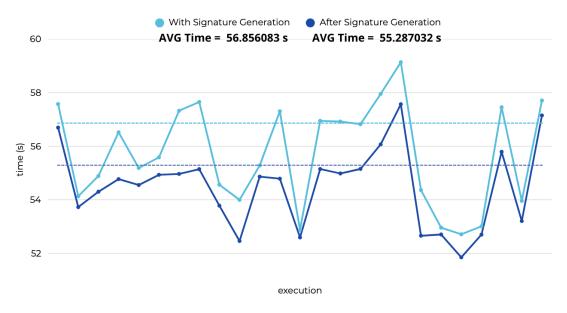

| 8               | Res<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5 | Achieved Security Improvements 65 Performance Considerations 66 Validation Outcomes 69 Impact on the Attack Surface 69 Limitations and Future Work 70                                                                                                                                                                                                                                          | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |

| 9               | Con                                    | clusions 73                                                                                                                                                                                                                                                                                                                                                                                    | 3                                      |

| List of Figures |                                        |                                                                                                                                                                                                                                                                                                                                                                                                | 5                                      |

| Bibliography    |                                        |                                                                                                                                                                                                                                                                                                                                                                                                | )                                      |

# Chapter 1

# Avio Aero

This thesis work was carried out during an internship at Avio Aero, which provided me the opportunity to work at their headquarters in Rivalta di Torino throughout the entire duration of the internship.

Figure 1.1: GE Avio Aero logo

#### 1.1 Company overview and background

Avio Aero is a GE Aerospace company that represent a global leader in the design, production, and maintenance of advanced propulsion systems for the aerospace industry. Originally established as Fiat Aviazione in 1908, the company has established itself as a key player in the development of innovative technologies for aviation, covering a significant role in the development of Italy's aviation sector during the early 20th century, contributing to both civil and military aviation programs. Avio Aero is headquartered in Turin but operates multiple facilities across Europe.

Figure 1.2: Fiat Aviazione stand at Fiera Campionaria di Milano 1952. Source https://archiviostorico.fondazionefiera.it/oggetti/10412-stand-della-fiat-aviazione-al-salone-dellauto-avio-moto-ciclo-e-accessori-sportivi-nel

In 1989 the company changed its name in Fiat Avio while in 2003, Fiat Avio underwent a major transformation when it was sold by Fiat Group to a consortium led by the Carlyle Group and Finmeccanica (now Leonardo) and was rebranded as Avio and continued to focus on aerospace propulsion systems, while also expanding into space propulsion technologies.

In 2013, Avio's aerospace division was acquired by General Electric (GE) and became part of GE Aerospace, taking on the name Avio Aero. This acquisition integrated the company into GE's global operations, providing access to GE's resources and expertise in aviation technology allowing Avio Aero to continue develop advanced propulsion systems.

Today, with more than 5,700 employees, Avio Aero is present from the product design and development phase through production and aftermarket services.

The company specializes in the design and manufacturing of critical components for aircraft engines, including turbines, gearboxes, and combustors, as well as advanced systems for both civil and military aviation. Avio Aero is renowned for its expertise in additive manufacturing, leveraging cutting-edge 3D printing technologies to produce complex engine parts with enhanced performance, reduced weight, and improved efficiency. This commitment to innovation aligns with

GE Aerospace's broader mission to deliver safer, more sustainable, and more efficient solutions for the aviation industry.

The company adheres to rigorous standards and certifications to ensure the reliability and airworthiness of its products, contributing to the success of major aerospace programs worldwide. Collaborations with leading aircraft manufacturers and research institutions gave Avio Aero a pivotal role in shaping the future of aviation through continuous technological advancements and a focus on sustainability.

As a trusted partner in the aerospace sector, Avio Aero combines decades of experience with a forward-looking approach to innovation, making it a cornerstone of GE Aerospace's global operations. The dedication to excellence and the ability to adapt to the evolving demands of the industry underscore its position as a leader in propulsion systems and aerospace technology.

#### 1.2 Latest Achievements

During its history the company has achieved several key milestones successfully leading the development o advanced technologies and taking part in international projects.

#### 1.2.1 AMBER Hybrid-Electric Propulsion Project

Avio Aero has launched a hybrid-electric technology demonstration program as part of the European Clean Aviation initiative that focuses on developing a hybrid-electric demonstrator engine that combines traditional gas turbines with electric power systems to improve fuel efficiency and reduce emissions. This effort explores the potential of hybrid-electric propulsion for regional and short-haul aircraft, using advanced technologies like electric motors, power electronics, and energy storage systems. Working in collaboration with European research institutions, universities, and industry partners, Avio Aero is contributing to the aviation industry's push toward sustainability and its goal of achieving net-zero carbon emissions by 2050.

#### 1.2.2 Catalyst engine

The Catalyst engine represents one of Avio Aero's most significant technological achievements in recent years. Developed in collaboration with GE Aerospace and entirely designed and manufactured in Europe, the Catalyst engine is the first turboprop engine of its kind in over five decades on the continent. It integrates advanced technologies such as a fully authority digital engine control (FADEC) system and extensive use of additive manufacturing that enable improved performance, reduced fuel consumption and lower emissions compared to its competitors. In early 2025 the Catalyst Engine received FAA Part 33 certification after a rigorous campaign involving over 2600 hours of testing. The Catalyst engine has also been selected to power the Eurodrone, the European Medium Altitude Long Endurance (MALE) remotely piloted aircraft system, marking a major step toward strategic autonomy in defense application.

These milestones confirm the technical maturity of the engine and demonstrate Avio Aero's capacity to deliver cutting-edge propulsion systems for both civil and military aviation.

${\bf Figure~1.3:~Catalyst~engine.~Source~https://avioaero.com/it/media/media-releases/il-catalyst-scelto-da-airbus-per-eurodrone}$

## Chapter 2

# Security Regulations in Aerospace applications

In the aerospace industry, ensuring the safety and security of systems is fundamental, as these systems operate in environments where failure or compromise can have catastrophic consequences. To address these challenges, stringent security regulations and standards have been established to guide the development, certification, and operation of aerospace systems and all the vendors (like Avio Aero) must strictly adhere to these regulations to guarantee the right level of security and safety of the systems.

#### 2.1 Airworthiness & Airworthiness Security

In the process of securing avionic system, two key terms are commonly used, Airworthiness and Airworthiness Security. The first one refers to the ability of an aircraft or its components to operate safely within the defined parameters of its design and certification, ensuring that aircraft meet strict safety standards and are fit for flight. Airworthiness is governed by regulatory authorities such as the Federal Aviation Administration (FAA) in the United States and the European Union Aviation Safety Agency (EASA) in Europe that establish certification processes, maintenance requirements, and operational guidelines to ensure the continued safety of aircraft throughout their lifecycle.

Airworthiness Security, on the other hand, focuses on protecting the airworthiness of an aircraft from intentional threats, such as cyber attacks, sabotage, or other malicious activities that comes from the increasing reliance on software, connectivity and digital systems of a modern aircraft. Airworthiness security ensures that the **confidentiality**, **integrity and availability** (CIA) of systems essential to safe flight are maintained through cybersecurity standards and certifications, threat assessment and mitigation strategies.

# 2.2 DO-178C (Software Considerations in Airborne Systems and Equipment Certification)

DO-178C is the primary standard for the development and certification of software used in airborne systems and equipment. It provides a structured framework for ensuring the safety, reliability, and airworthiness of software in aviation and defines objectives for software development processes,

including requirements capture, design, coding, testing, and verification. It introduces the concept of Design Assurance Levels (DALs), which categorize software based on its criticality to flight safety, ranging from Level A (most critical) to Level E (least critical). DO-178C also emphasizes traceability between requirements, design, and testing to ensure comprehensive validation and it includes supplements such as DO-330 (tool qualification), DO-331 (model-based development), DO-332 (object-oriented technology), and DO-333 (formal methods), which address advanced software development techniques. Compliance with DO-178C is essential for obtaining certification from aviation authorities like the FAA and EASA.

| Design Assurance<br>Level | Description                         | Target System<br>Failure Rate                       | Example System            |

|---------------------------|-------------------------------------|-----------------------------------------------------|---------------------------|

| Level A<br>(Catastrophic) | Failure causes crash, death         | <1 x 10 <sup>-9</sup> chance of failure / flight-hr | Flight controls           |

| Level B<br>(Hazardous)    | Failure may cause crash, deaths     | <1 x 10 <sup>-7</sup> chance of failure / flight-hr | Braking systems           |

| Level C<br>(Major)        | Failure may cause stress, injuries  | <1 x 10 <sup>-5</sup> chance of failure / flight-hr | Backup Systems            |

| Level D<br>(Minor)        | Failure may cause inconvenience     | No safety metric                                    | Ground navigation systems |

| Level E<br>(No Effect)    | No safety effect on passengers/crew | No safety metric                                    | Passenger entertainment   |

Figure 2.1: Design Assurance Levels (DALs). Source https://eteo.tistory.com/496.

# 2.3 DO-326B (Airworthiness Security Process Specification)

DO-326B focuses on the security aspects of airborne systems, addressing the growing concern of Intentional Unauthorized Electronic Interaction (IUEI), defined as human-initiated actions with the potential to affect the aircraft due to unauthorized access, disclosure, use, denial, modification or destruction of electronic information or electronic aircraft system interface. This document is the joint product of two industry committees, the EUROCAE Working Group WG-72 and the RTCA Special Committee SC-216 and it provides a framework for identifying, assessing, and mitigating security risks that could impact the airworthiness of an aircraft. It introduces the concept of Airworthiness Security, which ensures that security vulnerabilities do not compromise the safety and operational integrity of the aircraft. DO-326B outlines processes for threat identification, risk assessment, and the implementation of security controls that address airworthiness security during the aircraft product life cycle, from project initiation until the aircraft Type Certificate.

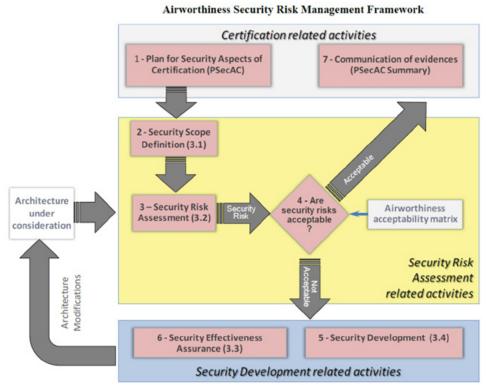

The purpose of the Airworthiness Security Process (AWSP) is to establish that when the system is subject to IUEI, it will remain in a condition for safe operation. This necessary implies the definition of an acceptability treshold and a complete and correct Risk Assessment. The AWSP

is composed of three major parts:

- Certification Activities: to manage the certification process.

- Security Risk Assessment Related Activities: to evaluate risk based on identified threat scenarios to determine acceptability and to assess the implemented security measures always considering the acceptability of the risk.

- Security Development Related Activites: this is the implementation part of the required security measures.

Figure 2.2: DO-326B Management Framework. Source https://militaryembedded.com/avionics/safety-certification/

incorporating-do-326a-security-airworthiness-into-software-development-life-cycle

DO-326B provides a structured workflow and defines the activities to be performed, organized into the following steps:

- 1. Aircraft Security Scope Definition (ASSD): Establish the aircraft's operational environment with respect to information security.

- 2. Preliminary Aircraft Security Risk Assessment (PASRA): Identify potential threat conditions and scenarios, and evaluate security risks at the aircraft level.

- 3. System Security Scope Definition (SSSD): Define the system's operational environment concerning information security.

- 4. Preliminary System Security Risk Assessment (PSSRA): Identify potential threat conditions and scenarios, and evaluate security risks at the system level.

- 5. System Security Risk Assessment (SSRA): Analyze threat conditions, scenarios, and vulnerabilities to assess the system's security risks.

- 6. Aircraft Security Risk Assessment (ASRA): Analyze threat conditions, scenarios, and vulnerabilities to assess the aircraft's security risks.

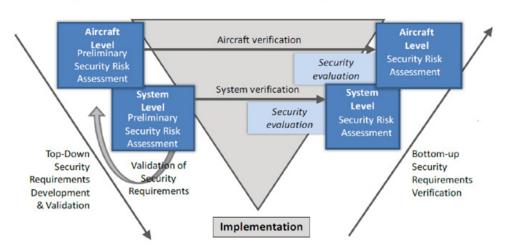

The workflow proposed by DO-326B follows a V-MODEL approach that highlights the presence of a preliminary Security Risk Assessment before the implementation, followed by another Security Risk Assessment after the implementation. The aim of the first one is to identify which part of the system is at an acceptable theoretical security risk level, identifying new security requirements when the security risk is not acceptable.

Security Risk Assessment Related Activities in the development process V-model

Figure 2.3: DO-326B Security Risk Assessment V-MODEL. Source https://militaryembedded.com/avionics/safety-certification/incorporating-do-326a-security-airworthiness-into-software-development-life-cycle.

# 2.4 DO-356 (Airworthiness Security Methods and Considerations

DO-356 is another critical guidance document, born by the joint work of RTCA Special Committee SC-216 and EUROCAE Working Group WG-72, that addresses the growing need for cybersecurity in aviation systems due to the increasingly interconnected nature and reliance on digital technologies that made the potential for cyber threats broader. DO-356 complements other aviation standards, such as DO-178C and DO-326B, by focusing specifically on the identification, assessment, and mitigation of cybersecurity risks throughout the lifecycle of an aircraft system. It provides methodologies and guidelines to be used within the airworthiness security process defined in DO-326B, for threat modeling, vulnerability analysis, and risk management, ensuring that cybersecurity measures are integrated into the design, development, operation, and maintenance phases. The document also emphasizes the importance of aligning cybersecurity efforts with safety objectives, ensuring that security measures do not inadvertently compromise the reliability or functionality of critical systems. One area for enhancement in DO-356 could involve expanding its guidance on emerging technologies, such as artificial intelligence (AI) and machine learning (ML), which are increasingly integrating into aviation systems and introduce unique cybersecurity challenges, such as adversarial attacks on AI models or data poisoning, which require specialized mitigation strategies. Additionally, DO-356 could benefit from more detailed recommendations on securing communication protocols used in connected aircraft, such as satellite links and ground-based networks, to address vulnerabilities in data transmission.

The document is organized into six chapters that are designed to be used sequentially. Starting with the first chapter, which defines key terms and acronyms that the reader is expected to be familiar with, the subsequent chapters are structured to progressively guide the reader in acquiring the necessary knowledge and methodologies to ensure airworthiness security and conduct effective security risk assessments.

It also contains several appendices that provides concrete examples on how to perform a complete security risk assessment and how to guarantee airworthiness security.

#### 2.5 SAE AIR7368 (Cybersecurity for Propulsion Systems)

The SAE Aerospace Information Report (AIR) 7368 serves as a foundational framework for establishing a common approach to cybersecurity airworthiness certification for propulsion system manufacturers. Developed through a joint effort between industry experts and regulatory members of the E-36 Cybersecurity Subcommittee, its primary purpose is to provide comprehensive guidance on cybersecurity practices. As outlined in the document, achieving compliance requires that the engine control, propeller control, monitoring systems, and all auxiliary equipment systems and networks associated with the propulsion system be safeguarded against IUEI. Such interactions could potentially compromise the safety and functionality of the propulsion system, making robust protection measures essential. This document applies to security protection of propulsion systems for which IUEI are possible when connected to:

- Aircraft Systems like air data computers, flight and trhust management computers, engine interface units.

- Equipment for field and factory loading of production software.

- Equipment for making adjustments to adjustable parameters in the embedded software.

- Equipment to download from or upload data to the propulsion control system using wired or wireless communication protocols.

- Any other systems with digital or network connectivity capability.

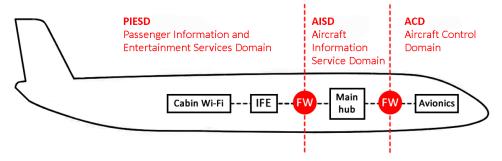

In this document is highlighted the distinction between four aviation domains. The Aircraft Control Domain (ACD) that consists of airborne systems and networks which functions are to support safe operation of the airplane. The Airline Information Services Domain (AISD) that enables operation of the airline like electronic manuals, cabin surveillance, cabin crew information access and so on. Passenger Information and Entertainment Services Domain (PIESD) that is a private unstrusted domain that informs and entertains the passengers. Passenger-Owned Devices Domain (PODD) that is the public domain external to the aircraft domain that includes all the devices that passengers may bring on board.

When performing security risk assessment is important to consider the division between these domains and how they can influence each other.

Figure 2.4: Aircraft domains. Source https://www.pentestpartners.com/security-blog/in-flight-entertainment-system-security/

## Chapter 3

# State of the art in avionics product security

Avionic product security encompasses a wide range of components, from the engine's Electronic Control Unit (ECU) and passenger entertainment systems to pilot inputs and mechanical systems. Given that Avio Aero is a leader in engine production, this analysis focuses specifically on the security aspects related to the engine.

The state of the art security measures that can be adapted from other industry sectors focus on safeguarding the confidentiality, integrity and availability (airworthiness security) of systems which increasingly rely on digital systems for control monitoring and diagnostics. For this reason advanced security measures are essential to address potential vulnerabilities.

#### 3.1 Nowadays proposed solutions

The integration of cybersecurity into aircraft engine design is a relatively recent development, driven by the need to protect critical systems from increasingly sophisticated threats. While modern aerospace engines aim to employ advanced security measures, the actual solutions adopted do not always represent the highest level of security. In fact, since Certification Authorities have only recently begun formalizing dedicated regulations (EASA started in 2021), many already certified engines lack security awareness and re-certification requires a significant effort. For example basic mechanisms like cyclic redundancy checks (CRC) are often used to verify data integrity, but they offer limited defense against more complex attacks, such as data manipulation or spoofing. Furthermore the rapid evolution of cyber threats means that even robust systems can become vulnerable without regular updates and improvements.

Although specific implementation details about proprietary engines remain confidential, the general principles and technologies that should be adopted in this sector are known.

#### 3.2 Secure Electronic Control Units (ECUs)

The ECU is the central element of an aircraft engine's digital control system, responsible for managing all the engine functions and this makes it a primary target for cybersecurity measures. Protection applied on the ECU are fundamental for the safety, operational reliability, protection against unauthorized access and information integrity of the system.

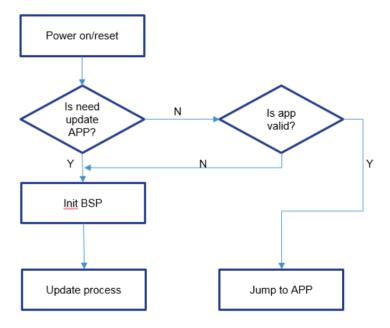

Secure Boot represents a pivotal feature to ensure that the ECU only runs software that is verified

and trusted. During the boot process the ECU perform some checks on the software components to confirm the authenticity and integrity, prevent malicious software from being executed. Cryptographic protection the main technique to safeguard data integrity and confidentiality.

Encryption can be used to protect sensitive data while digital signature further ensure that data has not been tampered with, providing a robust mechanism for verifying data authenticity.

Access Control (like role based access control RBAC) is the security measure to prevent unauthorized access to the ECU, ensuring that only authorized personnel can access or modify critical engine parameters.

#### 3.3 Data Communication Security

The communications between the engine, aircraft systems, and external entities such as ground stations are essential for operational efficiency and safety, so it is securing these communications. Encrypt communications using protocols like TLS is a common solution that ensures that any intercepted data remains untelligible to unatuhorized parties.

Authentication mechanisms are used to verify the identities of communicating parties ensuring that only legitimate systems can exchange data with the engine preventing injection of malicious commands.

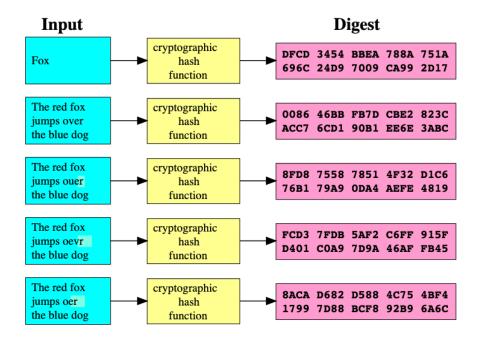

Integrity checks using hashing (e.g. SHA Algorithms) or checksum (e.g. CRC) are performed to verify that data has not been altered during transmission.

#### 3.4 Real-Time Monitoring and Intrustion Detection

Solutions like Anomaly Detection or Intrusion Detection Systems (IDS) can monitor the system for signs of malicious activity and to compare it with the expected behavior, enabling rapid response to mitigate threats before they impact the engine performance. Most recent solutions adopt new technologies like AI based Intrusion Detection System to increase the efficiency of these systems.

#### 3.5 Hardware Security Features

Physical security measures complements software-based protections to enhance the engine security. Trusted Execution Environments (TEEs) provide a secure area within the engine's hardware for executing sensitive operations, such as cryptographic functions, protecting from interference or tampering by unauthorized software.

Tamper-Resistant Components are designed to resist physical tampering, with features such as sealed enclosures and tamper-evident seals, safeguarding the engine from physical attacks.

On-chip Hardware security measures are the most studied solution as they represent the best solutions against common problems like economic constraints, security vs performance tradeoff and compliance with new regulations.

#### 3.6 Software Security

Ensuring the security of engine software is a continuous process that involves multiple layers of protection.

Engine Secure Software Development Lifecycle obtained using secure coding practices, rigorous testing, and compliance with standards making software resilient against known vulnerabilities

and compliant to industry best practices for safety and security.

Regular Updates and Patching for which engine software is regularly updated with security patches to address newly discovered vulnerabilities. These updates are carefully tested to ensure they do not compromise system functionality, maintaining the balance between security and operational reliability.

#### 3.7 Redundancy

By incorporating duplicate systems for critical functions, such as engine control and monitoring, redundancy allows the engine to continue functioning even if one component is compromised or fails. These redundant systems operate independently, providing a backup that can immediately take over in the event of an issue, not only mitigating the impact of potential cyber threats but also enhancing safety by maintaining uninterrupted engine performance during adverse conditions. Full Authority Digital Engine Control (FADEC) due to its full control on the engine operations implement redundancy as a security measure to guarantee the engine availability.

#### 3.8 Is aircraft physical security really necessary?

Although the likelihood of physical attacks on aircraft engines is extremely low, the potential consequences of such an attack could be catastrophic. This underscores the importance of proactively addressing and mitigating possible threats to ensure safety and security.

Even if for security purposes, there are no publicly known physical attacks on aircraft engines.

Even if, for security purposes, there are no publicly known physical attacks on aircraft engines, the following are examples of incidents where intruders gained access to airports and remained for sufficient time to potentially carry out serious attacks on aircraft.

- Avalon Airport, March 2025 [1]: A 17 year old boy managed to bypass airport security and board a plane by disguising himself as a staff member, wearing a security jacket and work belt, while carrying a gun.

- Mumbai Airport, 2019 [2]: A man was detained on Mumbai airport's Runway 27 after being spotted by the pilots of SpiceJet Flight SG634 who alerted airport security. The man managed to climb over the airport wall and enter the aircraft zone.

- Kano Airport, 2024 [3]: A man climbed the airport fence during the night and managed to get on an aircraft without being spotted. The cabin crew found him the next morning when they entered for a new flight.

- London, June 2024 [4]: Two elements of climate activist group Just Stop Oil breached security at a London airport in an attempt to target Taylor Swift's private jet as part of their protest against celebrity carbon emissions. The activists managed to enter the airport and remain there for some time, but ultimately failed to locate the jet.

- Bergamo Airport, July 2025 [5]: A 35-year-old man breached security at Bergamo-Orio

al Serio Airport by abandoning his car outside the terminal and running into the aircraft

parking area. He accessed the runway by opening a security door and ran toward a jet

preparing for takeoff, where he tragically lost his life after being sucked into the engine.

While the incidents described above were not aimed at performing cyberattacks, the ability of intruders to gain unauthorized access to restricted areas and remain there for extended periods demonstrates the potential for serious threats, including cyber or physical attacks on aircraft

systems. Even if these breaches were not malicious in nature, the time and access the intruders had would have been sufficient to execute harmful actions, such as tampering with critical systems or planting devices capable of compromising engine operations. These examples underscore the need for implementing physical security features alongside cybersecurity measures to ensure the safety and resilience of modern aviation systems against a wide range of threats.

# Chapter 4

# **Product Security Assessment**

This work's product security assessment (PSA) has been conducted following the guidance provided by the regulations outlined in Chapter 2. In a company like Avio Aero PSAs are initiated to ensure that avionic products (as the one in this work) meet customer product security requirements, adhere to GE product security standards, and comply with applicable regulatory certification requirements.

The PSA described in this chapter has been developed to align with industry-standard guidelines and regulations.

#### 4.1 Use Case

The use case considered in this work focuses on an engine designed for civil aircraft, so it is an highly complex systems that must meet stringent safety, reliability, and performance standards. These engines are responsible for providing thrust to propel the aircraft and maintaining operational stability under various environmental conditions, additionally, they must comply with regulatory requirements such as those set by aviation authorities like the FAA and EASA.

The real case reference is a GE engine designed for civil aviation which integrates advanced digital systems to work, in fact, as modern engines increasingly rely on digital systems, the potential for cyber vulnerabilities grows and without strong security measures, critical systems could be exposed to risks such as unauthorized access, data manipulation, or system disruption. This highlights the need for enhanced cybersecurity protocols to safeguard the engine's digital components and ensure resilience against emerging threats in the aviation industry.

#### 4.2 PSA Model

PSA process follows the guidelines from DO326B and V-model approach and is composed of different phases that include system design and verification activities. Moreover for each phase is expected the production of an artifact that provide evidence of work done in that phase.

#### Aircraft Aircraft Aircraft verification Level Security Risk Security Security Risk Assessment evaluation Assessment System verification System Level Preliminary Security Security Risk evaluation Security Risk Assessment Top-Down Bottom-up Validation of Security Security Security Requirements Requirements Requirements Development Verification & Validation Implementation

#### Security Risk Assessment Related Activities in the development process V-model

Figure 4.1: DO326 V-model approach

This is a process that aim to identifying, analyzing, and mitigating cybersecurity risks in the system. It is designed to ensure that security considerations are integrated into the system lifecycle from the earliest stages of development thanks to the various phases:

- Planning and scope definition phase: it is the foundation of the Security Assessment process, where the objectives, scope, and boundaries of the cybersecurity effort are defined. This phase begins with identifying the systems, components, and interfaces that require protection (assets). Risk identification is also initiated, focusing on potential vulnerabilities and areas of concern. During this phase it is developed a high-level understanding of the system architecture and its operational environment including identifying external interfaces, data flows, and dependencies that could introduce security risks. This phase sets the stage for a targeted and efficient security assessment.

- Security Assessment phase: it focuses on evaluating the system's current security posture and identifying risks and vulnerabilities conducting a detailed analysis of the system's architecture using techniques such as threat modeling, risk analysis, and vulnerability scanning. The goal of this phase is to prioritize security concerns based on their likelihood and impact, for example risks that could compromise safety-critical systems or sensitive data are given higher priority. The findings from the assessment phase provide the foundation for defining security requirements in the next phase.

- Security Requirements phase: translate the findings from the assessment phase into actionable security measures by defining specific security requirements that address identified risks

and vulnerabilities. These requirements may include technical measures, such as encryption protocols or access controls, as well as procedural measures, such as incident response plans or training programs. During this phase, the team also develops security specifications and design criteria to ensure that the system meets regulatory standards and industry best practices.

- Security Verification phase: ensure that the implemented security measures meet the defined requirements and effectively mitigate identified risks by developing test plans, executing test procedures, and documenting results. Verification activities may include penetration testing, vulnerability scanning, and functional testing of security features with the goal of validating the system's security posture and ensure compliance with regulatory standards. Any issues identified during testing are addressed through iterative improvements (iterative process).

- Final Reporting phase: it finalizes the Security Assessment process and documents the outcomes by summarizing the security measures implemented, the results of verification, and any residual risks. During this phase, recommendations for ongoing security monitoring and maintenance are developed to ensure that the system remains resilient against emerging threats throughout its lifecycle.

#### 4.3 Threat Repositories: CAPEC & MITRE EMB3D

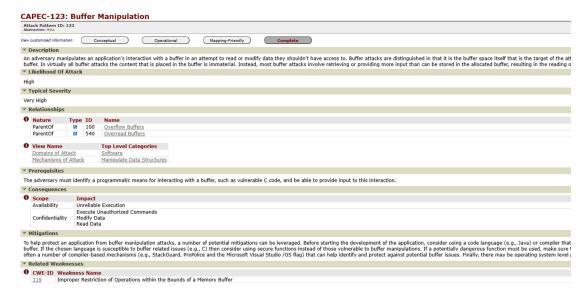

Threat assessment in this work has been conducted using two widely recognized resources to provide a thorough evaluation of potential cybersecurity risks and vulnerabilities. The first resource, Common Attack Pattern Enumeration and Classification (CAPEC), is a catalog maintained by MITRE that provides a comprehensive repository of common attack patterns, detailing the methods, techniques, and strategies adversaries use to exploit system vulnerabilities. Each attack pattern is described in terms of its characteristics, prerequisites, and potential impacts enabling security professionals to identify weaknesses in system architecture and operational processes, in fact, CAPEC is particularly valuable for mapping attack patterns to specific system features, allowing for the development of targeted mitigation strategies that address the most relevant threats.

Figure 4.2: CAPEC Vulnerability Example

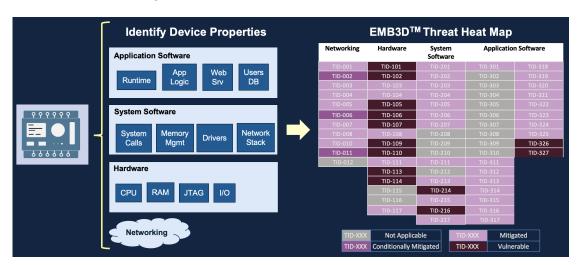

The second resource, MITRE EMB3D, is a knowledge base of cyber threats created by MITRE to enhance the security of embedded devices focusing on the unique challenges associated specifically with them, which often have constrained resources and critical functions. The framework maps known cyber threats to specific features of embedded devices, such as communication interfaces, memory management, or control mechanisms and for each identified threat, it provides corresponding mitigation strategies, offering actionable guidance to reduce vulnerabilities and improve system resilience. This framework has been used only as support for threat enumeration using CAPEC.

Figure 4.3: EMB3D threat domains. Source https://emb3d.mitre.org/

Together, CAPEC and EMB3D provide a robust foundation for threat assessment, combining a broad understanding of attack patterns with a specialized focus on embedded systems. This

dual approach enables the identification of risks in the system and supports the development of effective security measures tailored to the system's unique needs. By utilizing these resources, the threat assessment process can achieve a high level of precision and reliability.

#### 4.4 Scope definition & threat identification

Before conducting threat assessment it is required to define the **Security Environment and System Security Scope** to be analyzed. Since the work is done on the Engine ECS, the domain to be analyzed is the **Aircraft Control Domain (ACD)**, that is the network responsible for the internal communication of the aircraft related to flight and operational control of the aircraft. The **Security Environment** is defined by all the connection that interact with the ECS. These connections are called *Security Vectors* and their presence must be analyzed to spot potential vulnerabilities.

In our study the connection between the ECS and the ADC are represented by:

- ARINC 429: standardized data bus protocol used for communication of avionic information.

- PCAN with the host PC that loads the application image.

- Analog connections: direct analog signal interfaces for specific data or control.

The roles and entities interacting with the aircraft engine:

- Flight Crew: People who fly the plane and have unescorted access to the flight deck with the potential risk to inflict catastrophic loss upon the aircraft.

- Aircraft/Engine Maintainer: People retained by the airframer and subsequent operators

who are responsible for the required maintenance operations required by the aricraft with

the potential risk to inflict catastrophic loss upon the aircraft and provide unauthorized

aircraft access to external parties.

- General Population: People with no responsibility to the engine that can potentially perform attacks if the system is not secured.

After the environment analysis, it is possible to identify possible threats that could harm our system between the ones reported in the threat repositories.

Threat assessment results, reported below, is a list of threat conditions that could potentially harm the system.

| CAPEC-ID | Threat Scenario                                         | Threat Category          |

|----------|---------------------------------------------------------|--------------------------|

| 21       | Take advantage of input validation and authentication   | Bypass authentication    |

|          | to attack session IDs and resource IDs to gain access   | mechanism                |

|          | to EEPC.                                                |                          |

| 22       | Leverage implicit trust EEPC server places on a client, | API/Interface abuse      |

|          | or what the server believes to be the client.           |                          |

| 25       | Forced Deadlock.                                        | Race conditions or Dead- |

|          |                                                         | locks                    |

| 26       | Manipulate EEPC to run multiple processes concur-       | Race conditions or Dead- |

|          | rently to create a race condition.                      | locks                    |

| 28  | Fuzzing, manipulate input validation by feeding random input to ECS.                                                                                                                                  | Manipulate input/parameter/buffer or Inject Traffic |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 74  | Modify state information.                                                                                                                                                                             | Manipulate state/environ-<br>ment/configuration     |

| 94  | Adversary in the middle, an attacker can probe the line to place in the middle of a communication and steal information.                                                                              | Intercept or Eavesdrop                              |

| 112 | Brute forcing, even if adopting adequate solutions, the probability is never zero.                                                                                                                    | Bypass authentication mechanism                     |

| 113 | An adversary manipulates API to impact the security of the system executing functionality not intended by the API.                                                                                    | API/Interface abuse                                 |

| 114 | Exploit flaws in authentication mechanism to gain access to sensitive information and functionalities.                                                                                                | Bypass authentication mechanism                     |

| 115 | Authentication bypass.                                                                                                                                                                                | Bypass authentication mechanism                     |

| 116 | Excavation, probe the system by using valid interactions but in a wrong way or with wrong arguments to produce errors that leak information.                                                          | Manipulate input/parameter/buffer                   |

| 117 | Interception, monitor messages that go from or to the ECS.                                                                                                                                            | Intercept or Eavesdrop                              |

| 122 | Privilege abuse, exploit features of ECS reserved for privileged users.                                                                                                                               | Privilege Escalation                                |

| 123 | Buffer manipulation, create buffer overflows or similar.                                                                                                                                              | Manipulate input/parameter/buffer                   |

| 124 | Manipulation of resources shared between ECS and other systems.                                                                                                                                       | API/Interface abuse                                 |

| 125 | Message flooding, DoS.                                                                                                                                                                                | Resource attacks or DoS                             |

| 129 | Pointer manipulation.                                                                                                                                                                                 | Manipulate input/parameter/buffer                   |

| 130 | Excessive allocation, force the allocation of excessive EEPC resources via crafted messages.                                                                                                          | Resource attacks or DoS                             |

| 131 | Deplete system resources.                                                                                                                                                                             | Resource attacks or DoS                             |

| 137 | Parameter injection, need proper input validation.                                                                                                                                                    | Manipulate input/parameter/bufferor Inject Traffic  |

| 148 | Content spoofing, adversary modifies content to make<br>it contain something other than what the original<br>content producer intended while keeping the apparent<br>source of the content unchanged. | API/Interface abuse or<br>Spoofing                  |

| 151 | Identity spoofing, adversary may craft messages that appear to come from a different principle or use stolen/spoofed authentication credentials.                                                      | Bypass authentication<br>mechanism or Spoofing      |

| 153 | Input data manipulation, exploiting weakness in input validation.                                                                                                                                     | Manipulate input/parameter/buffer                   |

| 154 | Spoof the location of available resources to leverage an alternate resource.                                                                                                                          | API/Interface abuse or<br>Spoofing                  |

| 161 | Infrastructure manipulation, manipulate the routing                                                                                                                                  | Manipulate state/environ-                           |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|     | of messages to extract information.                                                                                                                                                  | ment/configuration                                  |

| 165 | Modify file contents to cause incorrect processing.                                                                                                                                  | Manipulate state/environ-<br>ment/configuration     |

| 169 | Footprinting, the attacker uses tools to gather as much information as possible about services and mechanisms of the system.                                                         | Footprinting/Fingerprinting                         |

| 173 | Action spoofing, adversary is able to disguise one action for another and trick a user into initiating one type of action when they intend to initiate a different action.           | API/Interface abuse or<br>Spoofing                  |

| 175 | Code inclusion, adversary exploits a weakness on the target to force arbitrary code to be retrieved locally or from a remote location and executed.                                  | Execute Arbitrary Code                              |

| 176 | Configuration/environment manipulation, attacker manipulates files or settings external to a target application which affect the behavior of that application.                       | Manipulate state/environ-<br>ment/configuration     |

| 184 | Software integrity attack, attacker initiates a series of events to cause a user, program, server, or device to perform actions which undermine the integrity of software code.      | Execute Arbitrary Code                              |

| 188 | Reverse engineer the ECS to gain system and security information.                                                                                                                    | Reverse engineering or<br>Elicitation               |

| 212 | Functionality misuse, adversary leverages legitimate capabilities to achieve negative impacts.                                                                                       | Manipulate state/environment/configuration          |

| 224 | Fingerprinting, adversary compares output from a target system to known indicators that uniquely identify specific details about the target.                                         | Footprinting/Fingerprinting                         |

| 227 | Adversary attempts to deny legitimate user access to<br>a resource by continually engaging a specific resource<br>in an attempt to keep the resource tied up as long as<br>possible. | Resource attacks or DoS                             |

| 233 | Privilege escalation by exploiting system weaknesses.                                                                                                                                | Privilege Escalation                                |

| 240 | Resource injection, change resource identifiers to enable unintended modification of EEPC resources.                                                                                 | Manipulate input/parameter/buffer or Inject Traffic |

| 242 | Code injection exploiting improper input validation.                                                                                                                                 | Execute Arbitrary Code /<br>Inject Traffic          |

| 248 | Command injection, adversary looking to execute a command of their choosing, injects new items into an existing command thus modifying interpretation away from what was intended.   | Execute Arbitrary Code / Inject Traffic             |

| 272 | Protocol manipulation, manipulate the communication protocols through known security vulnerabilities.                                                                                | Intercept or Eavesdrop                              |

| 390 | bypass physical security.                                                                                                                                                            | Physical Unauthorized Access                        |

| 410 | Information elicitation, engage individual from the company to gain information about the system.                                                                                    | Reverse engineering or<br>Elicitation, 10           |

|     |                                                                                                                                                                                      |                                                     |

| 438 | Modification during manufacture, supply chain attack.                                                                                                             | Compromise during manufacturing                                   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 439 | An attacker undermines the integrity of a product, software, or technology at some stage of the distribution channel.                                             | Compromise during manufacturing                                   |

| 440 | HW integrity attack, adversary exploits a weakness in the system maintenance process                                                                              | Compromise during manufacturing                                   |

| 441 | Insert malicious logic into the system.                                                                                                                           | Execute Arbitrary Code or<br>Compromise during manu-<br>facturing |

| 507 | Physical Theft.                                                                                                                                                   | Physical Unauthorized Access                                      |

| 548 | Contaminate resource, contaminate ECS information system causing it to handle unauthorized information resulting in unavailability while the problem is resolved. | Resource attacks or DoS                                           |

| 549 | Local execution of code, adversary installs and executes malicious code on the target system in an effort to achieve a negative technical impact.                 | Execute Arbitrary Code                                            |

| 560 | Adversary guesses or obtains legitimate credentials to achieve authentication and perform authorized actions under the guise of an authenticated user or service. | Bypass authentication mechanism                                   |

| 594 | Traffic injection, adversary injects traffic to degrade or disrupt connection.                                                                                    | Intercept or Eavesdrop                                            |

| 607 | Obstruction.                                                                                                                                                      | Resource attacks or DoS                                           |

| 624 | HW Fault Injection.                                                                                                                                               | Fault injection or Physical signal manipulation                   |

Table 4.1: Mapping of identified threat conditions to CAPEC entries

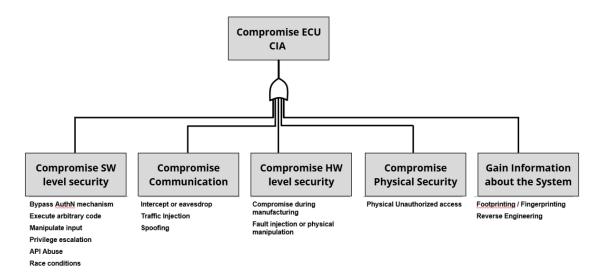

All the threat conditions have been grouped into five different categories based on the domain of the possible attacks with all of them pointing to a "Top-Event" which is the compromise of the ECU Confidentiality, Integrity or Availability as shown in the figure below.

Figure 4.4: Threat condition categories

#### 4.5 High Level Requirements Definition

Each threat condition shapes the creation of High-Level Requirements, each of which defines the necessary system characteristics and safeguards to mitigate the corresponding threat. After having analyzed and grouped the threat conditions, the resulting High Level Requirements are the following:

| Requirement ID | Description                                           | CAPEC Threat ID                                       |

|----------------|-------------------------------------------------------|-------------------------------------------------------|

| R1             | The product shall be developed in a secure environ-   | 404, 410, 416                                         |

|                | ment to protect intellectual property and prevent     |                                                       |

|                | unauthorized access to design data.                   |                                                       |

| R2             | The product shall validate data communications in ac- | 116, 130, 227, 490, 137,                              |

|                | cordance with the interface control document (ICD).   | 175, 242, 248, 624, 126,                              |

|                |                                                       | 148, 151, 184, 216, 28, 21,                           |

|                |                                                       | 114, 123, 153, 161, 272,                              |

|                |                                                       | 548, 607, 441                                         |

| R3             | Unused I/O interfaces, including reserved and manu-   | 116, 117, 169, 224, 125,                              |

|                | facturing interfaces, shall be disabled.              | 130, 131, 227, 490, 137,                              |

|                |                                                       | 175, 240, 242, 248, 624,                              |

|                |                                                       | 126, 148, 151, 154, 173,                              |

|                |                                                       | 184, 440, 25, 26, 29, 74,                             |

|                |                                                       | 462, 113, 212, 216, 554,                              |

|                |                                                       | 28, 39, 112, 155, 21, 114,                            |

|                |                                                       | 115, 22, 69, 122, 233, 234,                           |

|                |                                                       | 30, 123, 124, 128, 129, 153,                          |

|                |                                                       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

|                |                                                       | 271, 272, 548, 607, 97, 542,                          |

|                |                                                       | 438, 439, 441                                         |

| R4  | Clearly defined access controls shall be required for untrusted humans and automated access requests.                      | 126, 173, 74, 28, 112, 155, 21, 114, 115, 122, 233, 234, 30, 129, 390, 507                                                                                                                                                                                                        |

|-----|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R5  | Write protection shall be provided for executables and images to ensure integrity.                                         | 137, 175, 240, 242, 248, 184, 155, 129, 165, 171, 542, 441                                                                                                                                                                                                                        |

| R6  | Data segment execution protection shall be implemented to prevent unauthorized code execution.                             | 137, 175, 240, 242, 248, 184, 74, 28, 124, 129, 153, 165, 171, 542, 441                                                                                                                                                                                                           |

| R7  | Shared system resources shall be protected to prevent unauthorized or unintended information transfer.                     | 126, 148, 151, 154, 173, 74, 161, 410                                                                                                                                                                                                                                             |

| R8  | The integrity of items executed during operation shall be confirmed, and modification shall be prevented.                  | 175, 240, 28, 124, 153, 165, 171, 268, 548, 542                                                                                                                                                                                                                                   |

| R9  | Improper configuration during startup or operation shall be recorded, and normal operations shall be limited or prevented. | 175, 126, 113, 212, 155, 176, 268, 272, 548, 542, 441                                                                                                                                                                                                                             |

| R10 | Data loads and their sources crossing trust boundaries shall be validated and authenticated prior to activation.           | 116, 125, 130, 227, 490, 137, 175, 240, 242, 126, 148, 151, 154, 173, 28, 28, 112, 114, 124, 128, 153, 171, 548, 542, 441                                                                                                                                                         |

| R11 | Test/debug interfaces, ports, protocols, and facilities shall be protected against unauthorized usage.                     | 116, 117, 169, 224, 125, 130, 131, 227, 490, 137, 175, 240, 242, 248, 126, 148, 151, 154, 173, 184, 25, 26, 74, 462, 113, 216, 554, 28, 28, 112, 155, 21, 114, 115, 22, 69, 122, 233, 234, 30, 123, 124, 128, 129, 153, 161, 165, 171, 176, 268, 271, 272, 548, 607, 97, 542, 441 |

| R12 | Third-party components shall be analyzed for vulnerabilities and malware.                                                  | 624, 440, 212, 554, 115, 124, 542, 441                                                                                                                                                                                                                                            |

| R13 | Third-party components included in the product shall be tested to ensure they perform only intended functionalities.       | 624, 440, 212, 554, 115, 124, 542, 441                                                                                                                                                                                                                                            |

| R14 | Resource usage shall be controlled appropriately for the product.                                                          | 130, 131, 227, 490, 240, 154, 74, 21                                                                                                                                                                                                                                              |

| R15 | A documented approach shall be implemented to detect, mitigate, and recover from flooding DoS attacks.                     | 125, 490, 607                                                                                                                                                                                                                                                                     |

| R16 | Users or processes acting on behalf of users shall be uniquely identified and authenticated.                               | 22                                                                                                                                                                                                                                                                                |

| R17 | The product shall include a vulnerability applicability matrix to identify known vulnerabilities.                          | All                                                                                                                                                                                                                                                                               |

| R18 | The vulnerability applicability matrix shall be updated within the last three months.                                      | All                                                                                                                                                                                                                                                                               |

| R19 | Each product version shall be tested for applicable vulnerabilities prior to release.                                           | 116                                                                                                                      |

|-----|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| R20 | Software within the product shall comply with secure coding practices.                                                          | 137, 242, 248, 126, 184, 25,<br>26, 74, 28, 113, 554, 28, 21,<br>114, 115, 69, 233, 123, 124,<br>129, 153, 171, 542, 441 |

| R21 | All network interfaces shall be scanned and passively monitored for unexpected services or events.                              | 169, 125, 131, 227, 490, 184, 462, 216, 22, 161, 272, 607                                                                |

| R22 | Services responding on network interfaces shall be verified to be necessary per requirements.                                   | 169, 125, 131, 227, 490, 184, 462, 216, 22, 161, 272, 607                                                                |

| R23 | Interface responses shall provide necessary identification information for the overall product version.                         | 116, 224, 28, 97                                                                                                         |

| R24 | Identification information from autonomous responses shall be verified.                                                         | 116, 224, 28, 97                                                                                                         |

| R25 | The operational load image shall be validated prior to execution.                                                               | 542                                                                                                                      |

| R26 | The integrity of the load image shall be maintained during transfer from the originating source.                                | 542                                                                                                                      |

| R27 | Validation mechanisms shall minimize the likelihood of operational load image modification.                                     | 542                                                                                                                      |

| R28 | The operational load image shall include metadata containing version, integrity, and security information.                      | 542                                                                                                                      |

| R29 | Integrity measures shall be sufficiently complex to uniquely validate the operational load image.                               | 542                                                                                                                      |

| R30 | Invalid operational load images shall be rejected and not stored in non-volatile memory.                                        | 542                                                                                                                      |

| R31 | The product shall determine the operational load image is invalid if the integrity check fails.                                 | 542                                                                                                                      |

| R32 | Error handling, logging, and recovery mechanisms shall be implemented and clearly defined.                                      | 175, 624, 440, 25, 212, 28, 123, 607, 542, 441                                                                           |

| R33 | All data from outside the security perimeter shall be validated prior to transmission and use.                                  | 125, 130, 490, 137, 175,<br>242, 248, 126, 28, 21, 123,<br>128, 153, 441                                                 |

| R34 | Input that fails validation shall be immediately deleted.                                                                       | 137, 175, 242, 248, 126, 28, 21, 153, 441                                                                                |

| R35 | Privilege levels shall remain fixed once established.                                                                           | 74, 69, 233, 234, 30                                                                                                     |

| R36 | Credential storage and handling shall prevent theft<br>or leakage, and critical operations shall require re-<br>authentication. | 112, 114, 115, 560                                                                                                       |

| R37 | Users shall be authenticated to enable remote access to files, resources, and log data.                                         | 22                                                                                                                       |

| R38 | The supply chain shall be secured through authentication, validation, and tamper-evident mechanisms.                            | 438, 439, 440                                                                                                            |

| R39 | Secure communication protocols shall be implemented | 94, 216, 272 |

|-----|-----------------------------------------------------|--------------|

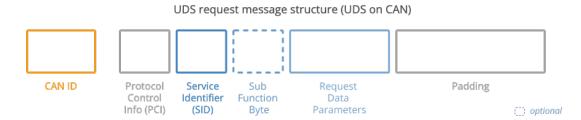

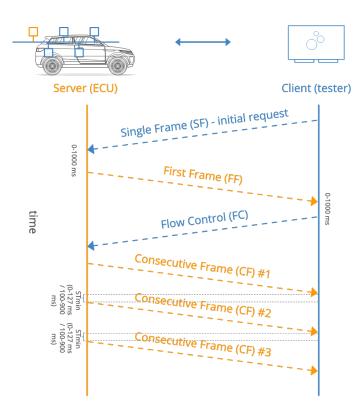

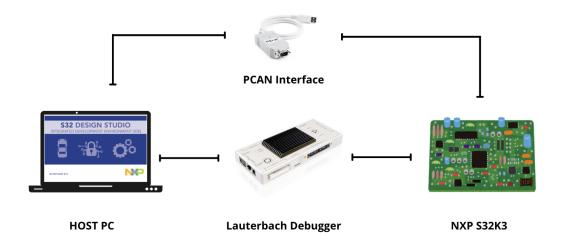

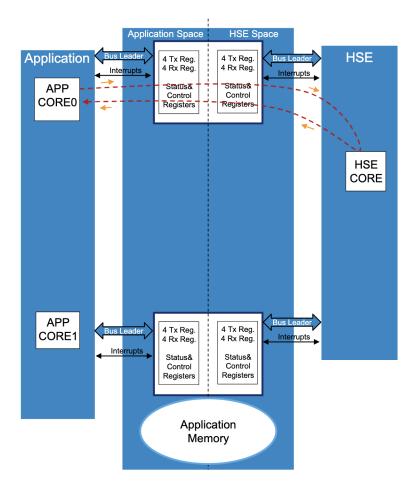

|     | to prevent MITM attacks.                            |              |