# Politecnico di Torino

Corso di Laurea Magistrale in Ingegneria Informatica (Computer Engineering)

A.A. 2024/2025

Sessione di Laurea Ottobre 2025

# Performance Optimization of a CAN Data Server on a Heterogeneous Automotive Embedded System

Design, implementation, and optimization of embedded firmware for efficient CAN data handling in automotive cluster and infotainment systems.

Master's Thesis developed at Iveco S.p.A. in collaboration with Politecnico di Torino

Relatore: Luciano Lavagno Candidato: Gabriele Russo

## **Abstract**

#### English

The rapid evolution of automotive electronic architectures, driven by the increasing adoption of infotainment and digital cluster systems, has led to a significant growth in the amount of data exchanged among Electronic Control Units (ECUs) and the transition towards more powerful hardware, such as High-Performance Computers (HPCs). Despite the introduction of new technologies, the Controller Area Network (CAN) remains the predominant communication protocol, requiring efficient firmware solutions to guarantee low latency and reliable performance.

This thesis presents the design, implementation, and optimization of embedded firmware for CAN data handling on heterogeneous automotive platforms, composed of microcontrollers running hard real-time operating systems and microprocessors running general-purpose automotive operating systems. The work includes the development of a CAN codec, the integration of the firmware with higher-level applications through efficient data serialization, and the evaluation of performance across different hardware platforms.

The analysis highlights typical bottlenecks such as dynamic memory allocation, shared-memory communication, and debugging overhead. Optimization strategies were applied, leading to reduced execution times, improved stability, and more efficient resource usage, as demonstrated through illustrative performance results.

The conclusions outline the contribution of this work in enhancing the reliability and scalability of in-vehicle communication systems and discuss potential future developments.

# Sommario

#### Italiano

La rapida evoluzione delle architetture elettroniche automobilistiche, guidata dalla crescente diffusione dei sistemi di infotainment e dei cruscotti digitali, ha portato a un significativo aumento della quantità di dati scambiati tra le Electronic Control Units (ECU) e alla transizione verso hardware più potenti, come gli High Performance Computers (HPC). Nonostante l'introduzione di nuove tecnologie, il Controller Area Network (CAN) rimane il protocollo di comunicazione predominante, richiedendo soluzioni firmware efficienti per garantire bassa latenza e prestazioni affidabili.

La presente tesi descrive la progettazione, l'implementazione e l'ottimizzazione di firmware embedded per la gestione dei dati CAN su piattaforme automotive eterogenee, composte da microcontrollori con sistemi operativi real-time hard e microprocessori con sistemi operativi automotive di tipo general-purpose. Il lavoro comprende lo sviluppo di un codec CAN, l'integrazione del firmware con applicazioni di più alto livello tramite meccanismi efficienti di serializzazione dei dati e la valutazione delle prestazioni su diverse piattaforme hardware.

L'analisi mette in evidenza i principali colli di bottiglia, come l'allocazione dinamica della memoria, la comunicazione tramite memoria condivisa e l'overhead dovuto alle attività di debug. Sono state applicate strategie di ottimizzazione che hanno portato a una riduzione dei tempi di esecuzione, a una maggiore stabilità e a un utilizzo più efficiente delle risorse, come dimostrato attraverso risultati prestazionali esemplificativi.

Le conclusioni delineano il contributo di questo lavoro nel migliorare l'affidabilità e la scalabilità dei sistemi di comunicazione veicolari e discutono i possibili sviluppi futuri.

# Ringraziamenti

Ringrazio innanzitutto la mia famiglia, che mi ha accompagnato con pazienza, fiducia e generosità lungo tutto il percorso accademico. Il loro sostegno, umano ed economico, è stato determinante per affrontare con equilibrio le sfide di questi anni.

Un grazie sentito va anche agli amici, per l'affetto, l'ironia e la comprensione con cui mi hanno accompagnato, rendendo più umano e leggero un percorso spesso rigoroso. Estendo il mio ringraziamento a coloro che, per ragioni diverse, non sono più presenti nella mia vita ma che hanno avuto un ruolo significativo nella mia crescita personale e accademica.

Infine, ringrazio i docenti, tutor aziendale e colleghi incontrati lungo la strada per gli stimoli ricevuti, le discussioni costruttive e le opportunità di sviluppo tecnico e professionale. Il confronto con loro ha contribuito in modo concreto alla qualità del lavoro qui presentato e al mio metodo di studio e di ricerca.

Desidero dedicare questa tesi a mio padre, che purtroppo non ha potuto assistere alla conclusione di questo cammino. Il suo esempio e il suo incoraggiamento, presenti anche nei momenti più difficili, sono stati una guida silenziosa che mi ha sostenuto fino a questo traguardo. Questo lavoro è per lui.

# **Indice**

| Ab  | stra  | ct    |                                                         | i   |

|-----|-------|-------|---------------------------------------------------------|-----|

| Soı | ηm    | aric  | )                                                       | iii |

| Rin | gra   | ziar  | nenti                                                   | V   |

| Ind | lice. |       |                                                         | vii |

| Ind | lice  | dell  | e figure                                                | xi  |

| 1   | Int   | rod   | uzione                                                  | 1   |

| 1.  | .1    | lved  | CO                                                      | 1   |

| 1.  | .2    | Cor   | ntesto                                                  | 2   |

| 1.  | .3    | Sta   | to dell'arte                                            | 3   |

| 1.  | 4     | Rias  | ssunto capitoli                                         | 5   |

|     | 1.4.  | .1    | Reti veicolari e veicoli moderni                        | 5   |

|     | 1.4.  | .2    | Piattaforme hardware                                    | 5   |

|     | 1.4.  | .3    | Organizzazione software                                 | 5   |

|     | 1.4.  | .4    | Implementazione software                                | 5   |

|     | 1.4.  | .5    | Integrazione con sistema Host                           | 6   |

|     | 1.4.  | .6    | Ottimizzazione e performance                            | 6   |

|     | 1.4.  | .7    | Testing e validazione                                   | 6   |

|     | 1.4.  | .8    | Conclusioni                                             | 7   |

| 2   | Re    | ti ve | eicolari e veicoli moderni                              | 8   |

| 2   | 2.1   | Evo   | luzione delle architetture elettroniche a bordo veicolo | 8   |

| 2   | 2.2   | S     | oftware-defined vehicle e implicazioni                  | 10  |

| 2   | 2.3   |       | e reti di comunicazione                                 |     |

| 2   | 2.4   | II    | protocollo CAN (Controller Area Network)                |     |

|     | 2.4   | l.1   | Architettura del bus CAN                                | 11  |

|     | 2.4   | 1.2   | Struttura del frame CAN                                 |     |

|     | 2.4   | 1.3   | Funzionamento ed arbitraggio                            |     |

|     | 2.4   | l.4   | Tipologie di frame nel protocollo CAN                   |     |

|     | 2.4   | l.5   | Rilevamento degli errori nel protocollo CAN             |     |

|     | 2.4   | l.6   | Svantaggi del protocollo CAN                            | 16  |

| 3   | Pio   | ntta  | forme hardware                                          | 17  |

| 3.1 Mic | rocontroller Unit e Microprocessor Unit       | 17 |

|---------|-----------------------------------------------|----|

| 3.1.1   | Componenti principali di un microcontrollore  | 17 |

| 3.1.2   | Tipologie di microcontrollori                 | 18 |

| 3.1.3   | Microprocessor Unit (MPU)                     | 18 |

| 3.2 E   | oard utilizzate                               | 20 |

| 3.2.1   | NXP i.MX8QM MEK                               | 20 |

| 3.2.2   | NXP S32K312 EVB                               | 22 |

| 3.2.3   | RT1064                                        | 23 |

| 3.3 P   | orting                                        | 24 |

| 3.4 P   | roblemi collegati all'hardware                | 25 |

| 4 Orgar | nizzazione software                           | 26 |

| 4.1 Mo  | delli architetturali                          | 26 |

| 4.2 F   | lardware Abstraction Layer                    | 26 |

| 4.2.1   | Cos'è realmente l'HAL                         | 26 |

| 4.2.2   | Progettazione modulare ed impatto sul porting | 28 |

| 4.3 A   | rchitettura esagonale                         | 28 |

| 4.4 F   | lexCAN                                        | 29 |

| 4.4.1   | Architettura funzionale essenziale            | 29 |

| 4.4.2   | Pattern operativo adottato nel progetto       | 30 |

| 4.4.3   | Vantaggi di questo approccio                  | 31 |

| 4.5 R   | TOS su MCU                                    | 32 |

| 4.5.1   | FreeRTOS                                      | 32 |

| 4.5.2   | Perché scegliere FreeRTOS                     | 34 |

| 4.5.3   | AUTOSAR Classic                               | 34 |

| 4.5.3.1 | Architettura a strati                         | 34 |

| 4.5.3.2 | 2 Vantaggi e limiti                           | 34 |

| 4.5.4   | AUTOSAR e FreeRTOS a confronto                | 35 |

| 4.6     | NX ed AUTOSAR Adaptive                        | 35 |

| 4.6.1   | QNX                                           | 35 |

| 4.6.2   | AUTOSAR Adaptive                              | 36 |

| 5 Imple | mentazione software                           | 38 |

| 5.1 Red | quisiti del sistema                           | 38 |

| 5.1.1  | I requisiti del progetto                                     | 38 |

|--------|--------------------------------------------------------------|----|

| 5.1.2  | Esempio di requisiti                                         | 39 |

| 5.2    | Ambienti di sviluppo e Software Development KitKit           | 40 |

| 5.2.1  | IDE                                                          | 40 |

| 5.2.2  | SDK                                                          | 40 |

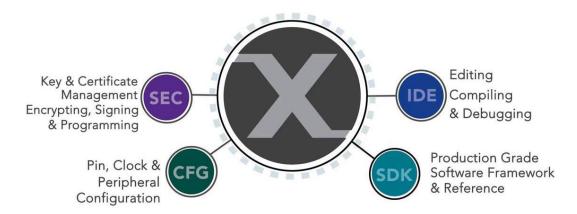

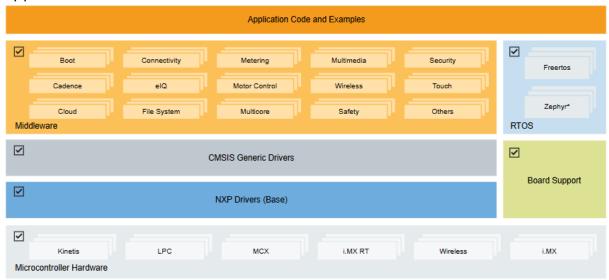

| 5.2.3  | MCUXpresso strumenti e software                              | 41 |

| 5.2.3. | MCUXpresso IDE                                               | 41 |

| 5.2.3. | 2 MCUXpresso SDK                                             | 41 |

| 5.2.3. | 3 I vantaggi dell'ambiente NXP                               | 42 |

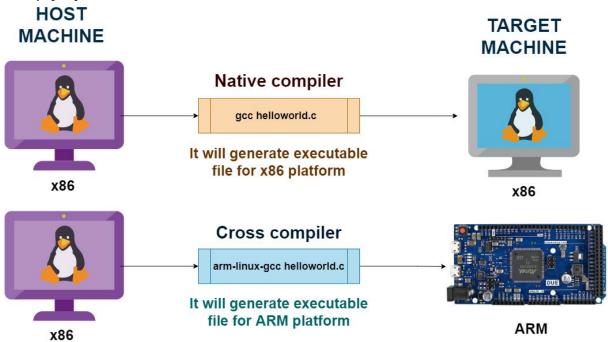

| 5.3    | Cross-compilazione                                           | 43 |

| 5.3.1  | GCC Arm Embedded (arm-none-eabi)                             | 43 |

| 5.3.2  | QCC / Q++ per QNX                                            | 43 |

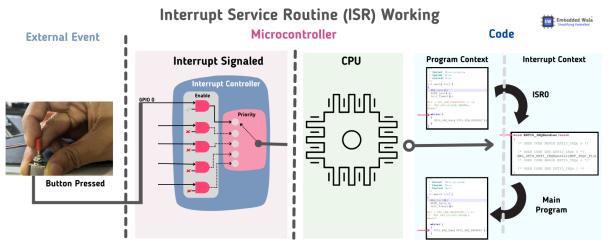

| 5.4 I  | nterrupt: principi, scelte progettuali e uso nel firmware    | 44 |

| 5.4.1  | Concetti chiave                                              | 44 |

| 5.4.2  | Sorgenti d'interrupt nel progetto                            | 44 |

| 5.4.3  | Politica adottata con gli Interrupt                          | 45 |

| 5.5 I  | mplementazione degli HAL                                     | 45 |

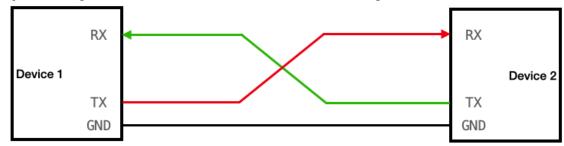

| 5.5.1  | HAL UART                                                     | 46 |

| 5.5.2  | HAL CAN                                                      | 47 |

| 5.5.3  | HAL SPI                                                      | 47 |

| 5.5.4  | HAL Watchdog                                                 | 48 |

| 5.5.5  | HAL GPT (General Purpose Timer)                              | 48 |

| 5.5.6  | HAL Codec                                                    | 48 |

| 5.6    | CoderDBC                                                     | 49 |

| 5.6.1  | Che cos'è un file DBC                                        | 49 |

| 5.6.2  | Dal DBC al codice con CoderDBC                               | 49 |

| Integ  | razione con sistema host                                     | 50 |

| 6.1 Co | municazione tra livelli di processo: applicativo e real-time | 50 |

| 6.1.1  | Comunicazione interna su SoC eterogenei                      | 50 |

| 6.1.2  | Transizione verso comunicazione fisica                       | 52 |

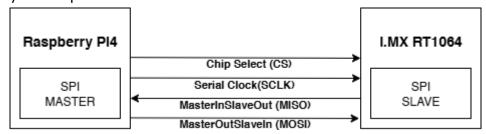

| 6.1.3  | Implementazione e problematiche SPI                          | 52 |

| 6.2    | Serializzazione dati per SPI                                 | 54 |

6

|    | 6.  | 2.1  | Redundant checks                                               | 55 |

|----|-----|------|----------------------------------------------------------------|----|

| 7  | 0   | ttir | nizzazione e performance                                       | 56 |

|    | 7.1 | St   | rumenti di Misura                                              | 56 |

|    | 7.2 |      | Metriche Principali                                            | 57 |

|    | 7.3 |      | Individuazione dei problemi                                    | 57 |

|    | 7.4 |      | Interventi di ottimizzazione                                   | 58 |

|    | 7.  | 4.1  | Architettura: eliminazione dell'IPC e autonomia del controllo  | 58 |

|    | 7.  | 4.2  | Codec e serializzazione: generazione mirata e formati compatti | 58 |

|    | 7.  | 4.3  | Zone di codice critiche e gestione risorse                     | 59 |

|    | 7.5 |      | Inoltro del frame CAN su SPI                                   | 60 |

| 8  | Te  | esti | ing e validazione                                              | 62 |

|    | 8.1 | М    | etodologia di test                                             | 62 |

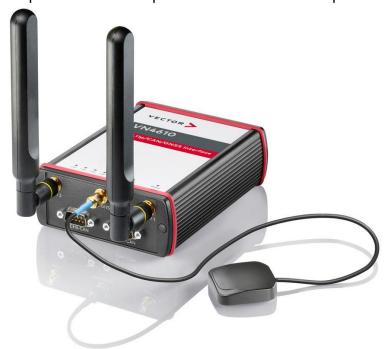

|    | 8.  | 1.1  | Banco e simulazioni: CANcase + CANalyzer                       | 62 |

|    | 8.  | 1.2  | Strumentazione e raccolta dati                                 | 63 |

|    | 8.  | 1.3  | In veicolo                                                     | 63 |

|    | 8.2 |      | Risultati sintetici                                            | 63 |

| 9  | С   | on   | clusioni                                                       | 64 |

|    | 9.1 | V    | alutazione critica                                             | 64 |

| 10 |     | Bi   | bliografia                                                     | 65 |

# Indice delle figure

| Figura 1  | Cluster, infotainment ed indicatori/comandi vari di un trattore strado | ıle  |

|-----------|------------------------------------------------------------------------|------|

| Iveco S-\ | Way                                                                    | 3    |

| Figura 2  | Slide from a 2020 presentation by Herbert Diess highlights the VW      |      |

| Group's s | software ambitions                                                     | 8    |

| •         | NXP illustration on vehicle architecture distribution [4][4]           |      |

|           | Architettura tipica di una rete CAN [5]                                |      |

| Figura 5  | Struttura di un frame CAN standard [5]                                 | 12   |

| Figura 6  | Esempio di arbitraggio di priorità nel bus CAN [5]                     | 13   |

|           | comparazione di diversi frame classici ed FD [7]                       |      |

| _         | MCU, MPU, SoC                                                          |      |

|           | i.MX 8QM MEK [9]                                                       |      |

| Figura 10 | i.MX8 SoC structure [10]                                               | 21   |

|           | SCU [11]                                                               |      |

| Figura 12 | S32k312 [12]                                                           | 22   |

| Figura 13 | i.MX RT1064 Evaluation Kit [13]                                        | 23   |

| Figura 14 | esempio di HAL                                                         | 27   |

| Figura 15 | FlexCAN block diagram [27]                                             | 30   |

| Figura 16 | Multi tasking on single core applications [16][16]                     | 32   |

| Figura 17 | FreeRTOS architecture example                                          | 33   |

| Figura 18 | Rappresentazione grafica di ciò che costituisce un SDK (fonte:         |      |

| cleverta  | o.com)                                                                 | 40   |

| Figura 19 | MCUXpresso SDK High-Level Block Diagram [22][22]                       | 42   |

| Figura 20 | Rappresentazione grafica di compilazione nativa e cross-compilaz       | ione |

| [23]      |                                                                        | 43   |

| Figura 21 | Rappresentazione grafica del funzionamento di un ISR [24]              | 44   |

| Figura 22 | 2 Esempio di connessione UART [25]                                     | 46   |

| Figura 23 | 3 i.MX8QM software architecture [10]                                   | 50   |

| Figura 24 | i.MXRT1064 SPI pins connector schematics                               | 53   |

|           | 5 Immagine del PCB con i ponti in rame – Sulla destra un ingrandime    |      |

| del PCB   |                                                                        | 54   |

| Figura 26 | S Vector CANcase VN4610                                                | 62   |

# 1 Introduzione

Negli ultimi anni il settore automotive ha attraversato una profonda trasformazione tecnologica, guidata dall'introduzione di sistemi avanzati di infotainment, assistenza alla guida e connettività veicolo-utente. Le moderne vetture integrano un numero crescente di schermi e interfacce — dal cruscotto digitale (cluster) ai display touch di grandi dimensioni — che offrono funzionalità evolute come mappe di navigazione in tempo reale, integrazione con smartphone tramite Android Auto e Apple CarPlay, streaming multimediale e assistenti vocali.

Sebbene in precedenza molti sensori o attuatori erano cablati in maniera diretta adesso sono quasi tutti interfacciati tramite bus dati, principali o secondari, che comunicano con due o più centraline per permettere all'intero veicolo di operare in sincronia ed avere una serie di automatismi tali da richiedere un elevata complessità anche per le funzioni più semplici come alzare un finestrino.

Questa evoluzione ha comportato un aumento esponenziale della quantità di dati che devono essere scambiati in tempo reale tra le centraline elettroniche di controllo (ECU) di un veicolo. Il Controller Area Network (CAN) rimane il protocollo di comunicazione predominante in ambito automotive per la sua affidabilità, robustezza e capacità di operare in ambienti gravosi. Tuttavia, il crescente numero di sensori, attuatori e dispositivi di visualizzazione comporta un incremento del traffico dati sulla rete, rendendo sempre più necessarie ottimizzazioni lato firmware e architettura di sistema per garantire prestazioni stabili e tempi di risposta compatibili con i requisiti di sicurezza.

#### 1.1 Iveco

Iveco Group è uno dei principali costruttori mondiali di veicoli industriali, con una gamma che spazia dai veicoli leggeri per il trasporto urbano e regionale fino ai mezzi pesanti per il lungo raggio, oltre a veicoli speciali per applicazioni difensive, antincendio e fuoristrada. Con sede centrale a Torino e una presenza globale attraverso stabilimenti produttivi e centri di ricerca e sviluppo, Iveco rappresenta un attore chiave nel settore della mobilità commerciale, con una forte attenzione all'innovazione tecnologica e alla sostenibilità.

Negli ultimi anni l'azienda ha investito significativamente nello sviluppo di soluzioni a basse e zero emissioni, includendo veicoli alimentati a gas naturale e veicoli elettrici. Parallelamente, Iveco ha intrapreso una profonda trasformazione digitale, riconoscendo l'importanza crescente del software nella gestione dei veicoli moderni, sia per i sistemi di controllo e diagnostica sia per le interfacce avanzate di

infotainment e HMI (Human Machine Interface).

In questo contesto si inserisce la creazione della nuova Software House Iveco, inaugurata a fine 2024 presso la sede di Lungo Stura Lazio 49 a Torino. Questa struttura, progettata come hub centrale per lo sviluppo software, concentra competenze in ambiti quali firmware embedded, architetture di comunicazione veicolare, infotainment e HMI. L'obiettivo è accelerare lo sviluppo di soluzioni software proprietarie e ottimizzate per la nuova generazione di veicoli Iveco, garantendo affidabilità, scalabilità e prestazioni in linea con le esigenze dei sistemi automotive moderni.

Il team specifico in cui è stato sviluppato il presente lavoro di tesi è il team HMI, dedicato allo sviluppo delle interfacce uomo-macchina dei veicoli Iveco. Il gruppo si occupa della progettazione, implementazione e ottimizzazione del software necessario per la visualizzazione di informazioni critiche sul veicolo, gestione dei dati di sensori e attuatori, e interazione con sistemi di infotainment avanzati. In questo contesto, l'ottimizzazione delle prestazioni di un CAN Data Server rappresenta un caso concreto di come il team HMI lavori per garantire tempi di risposta rapidi, affidabilità dei dati e fluidità nell'interazione utente, elementi fondamentali per un'esperienza di guida sicura e moderna

#### 1.2 Contesto

L'architettura elettronica dei veicoli moderni è caratterizzata da una rete distribuita di ECU interconnesse tramite bus di comunicazione standard come CAN, LIN ed Ethernet automotive. Tra queste, il CAN continua a essere largamente utilizzato per la trasmissione di dati critici a bassa e media velocità, come informazioni di sensori, comandi di attuatori e segnali diagnostici.

La crescente complessità delle funzioni implementate a bordo veicolo ha introdotto nuove sfide:

- Aumento della densità di informazioni: i sistemi devono gestire simultaneamente dati provenienti da decine di sensori, telecamere, radar e moduli di infotainment.

- **Requisiti di tempo reale**: molte informazioni devono essere elaborate e visualizzate entro tempi molto ridotti per garantire la sicurezza e la reattività del sistema.

- **Interfacciamento eterogeneo**: i microcontrollori dedicati alle funzioni di basso livello devono comunicare in modo efficiente con processori ad alte prestazioni che gestiscono applicazioni grafiche complesse.

In questo scenario, l'ottimizzazione del firmware che gestisce i flussi di dati CAN diventa cruciale per garantire la stabilità e la scalabilità delle architetture elettroniche veicolari.

Quanto detto è fondamentale per l'**Human-Machine Interface (HMI)**, comprendente tutti i sistemi e le interfacce che permettono al conducente di interagire con il veicolo, come cruscotti digitali, display infotainment, pannelli touch, comandi vocali e feedback tattile. Lo scopo principale dell'HMI è fornire informazioni critiche in modo chiaro e sicuro, supportando il conducente nelle decisioni e nella gestione del veicolo.

Figura 1 Cluster, infotainment ed indicatori/comandi vari di un trattore stradale Iveco S-Way

Nel contesto del team HMI di Iveco, l'obiettivo era sviluppare un cluster ed infotainment completamente funzionante, integrando la raccolta dati dai sensori e dalle ECU con la visualizzazione e l'interazione dell'utente, garantendo al contempo prestazioni ottimali e tempi di risposta real-time.

#### 1.3 Stato dell'arte

Negli ultimi decenni, l'elettronica e il software hanno progressivamente assunto un ruolo predominante nello sviluppo dei veicoli, trasformando l'architettura interna da un insieme di sistemi isolati a una rete interconnessa di **Electronic Control Unit** (**ECU**). Queste centraline, dedicate a funzioni specifiche come il controllo motore, la sicurezza attiva, il comfort e l'infotainment, devono comunicare tra loro in tempo reale per garantire funzionalità affidabili e integrate.

Lo standard **CAN** (**Controller Area Network**), introdotto da Bosch negli anni '80 [1] e successivamente normato da ISO 11898, si è affermato come punto forte della comunicazione a bordo veicolo grazie a robustezza, tolleranza ai disturbi e determinismo nella gestione delle priorità dei messaggi. La sua architettura multimaster e l'efficiente arbitraggio dei pacchetti lo rendono adatto a scenari critici, dove la latenza deve rimanere bassa anche in condizioni di traffico intenso.

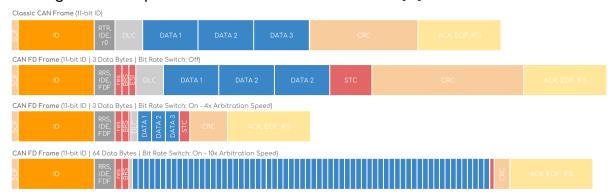

L'evoluzione delle esigenze ha portato allo sviluppo del CAN FD (Flexible Data-rate), che aumenta la dimensione massima del payload (fino a 64 byte) e supporta velocità di trasmissione più elevate nella fase dati, mantenendo retrocompatibilità con il CAN tradizionale. Questa tecnologia si è rivelata cruciale per ridurre l'overhead e migliorare l'efficienza nelle comunicazioni a elevata densità di dati, ad esempio nei sistemi ADAS o nei moduli di diagnostica avanzata.

Parallelamente, l'adozione di Automotive Ethernet sta guadagnando terreno per applicazioni che richiedono larghezza di banda molto superiore, come la gestione di flussi video per telecamere a 360°, sensori Lidar o Radar ad alta risoluzione. Standard come 100BASE-T1 e 1000BASE-T1, progettati specificamente per l'ambiente automotive, offrono velocità fino a 1 Gbps su singolo doppino schermato, mantenendo requisiti di peso e ingombro compatibili con il cablaggio veicolare [2]. Oltre ai protocolli di comunicazione fisica, negli ultimi anni si è assistito alla diffusione di middleware e standard software come AUTOSAR (Automotive Open System Architecture), che fornisce un'astrazione hardware e un'architettura modulare per lo sviluppo di applicazioni automotive, facilitando la portabilità del software e la gestione delle risorse. AUTOSAR, nelle sue versioni Classic e Adaptive, è ormai un riferimento per la gestione di sistemi real-time e di applicazioni ad alte prestazioni, rispettivamente.

La crescente complessità delle architetture ha portato anche alla separazione fisica delle funzioni: sistemi con architetture di dominio o le più recenti architetture zonali integrano più funzioni in unità di calcolo centralizzate. In particolare, si tende a ridurre il numero di ECU sostituendole con **High Performance Computer** (**HPC**), capaci di gestire più funzioni simultaneamente, dalla grafica e infotainment fino al controllo real-time dei sistemi critici.

In questi scenari, la comunicazione tra domini (ad esempio, tra la parte di alto livello grafico/infotainment e il controllo real-time delle funzioni critiche) deve essere gestita con protocolli ottimizzati, come SPI o Shared-Memory, quando possibile, per minimizzare latenza e jitter.

Infine, il tema della sicurezza è diventato centrale: l'interconnessione dei veicoli con infrastrutture esterne (V2X) e servizi cloud espone i sistemi embedded a nuove minacce. Gli standard come ISO/SAE 21434 e regolamenti UNECE (WP.29 R155) impongono requisiti stringenti per la sicurezza del software e delle comunicazioni interne, influenzando la progettazione dei protocolli e delle architetture hardware. In sintesi, lo stato dell'arte delle comunicazioni automotive è caratterizzato da:

- consolidamento del CAN e transizione verso CAN FD;

- crescente adozione di Automotive Ethernet per applicazioni ad alta banda;

- uso di middleware standardizzati come AUTOSAR;

- uso di sistemi operativi real-time;

- tendenza verso architetture centralizzate e zonali;

- attenzione crescente a cybersecurity e diagnostica avanzata.

Questi elementi, con alcune esclusioni dovute ai tempi ristretti ed alle finalità del

progetto svolto nel tirocinio, costituiscono il contesto tecnologico in cui si inserisce il presente lavoro di tesi, volto a sviluppare e ottimizzare un sistema firmware per la gestione e la trasmissione efficiente di dati su piattaforme embedded eterogenee.

# 1.4 Riassunto capitoli

#### 1.4.1 Reti veicolari e veicoli moderni

Analizza l'evoluzione delle architetture elettroniche a bordo veicolo, mettendo in evidenza il ruolo delle reti di comunicazione nella gestione della crescente complessità funzionale. Dopo una panoramica sull'aumento del numero di ECU e della mole di software necessaria nei veicoli moderni, vengono discusse le principali tipologie di architetture (distribuite, a dominio e zonali) e le relative implicazioni in termini di scalabilità e manutenzione. Infine, il capitolo descrive come la crescente centralità del software abbia portato alla nascita del paradigma dei software-defined vehicles, in cui le funzionalità del veicolo sono sempre più determinate dallo stack software e dalla capacità di gestire in modo efficiente i flussi di dati tra le diverse ECU.

#### 1.4.2 Piattaforme hardware

Si introducono le piattaforme hardware utilizzate nello sviluppo del progetto, con particolare attenzione alle differenze tra microcontrollori e microprocessori in ambito automotive. Dopo aver presentato le principali caratteristiche delle schede impiegate, vengono discusse le problematiche incontrate durante le attività di porting del firmware su diverse MCU e MPU, con riferimento alle differenze nei driver, nei kit di sviluppo e nelle periferiche disponibili. Il capitolo affronta inoltre le sfide legate a compatibilità hardware, mancanza di componenti o SDK incompleti, illustrando le soluzioni adottate per garantire la portabilità e la stabilità del codice.

# 1.4.3 Organizzazione software

Viene descritta l'organizzazione del software sviluppato, analizzandone sia gli aspetti architetturali sia quelli operativi. Dopo un'introduzione ai modelli utilizzati per garantire modularità e portabilità, come l'Hardware Abstraction Layer e l'architettura esagonale, il capitolo affronta la gestione della comunicazione CAN a livello di driver e codec. Viene inoltre presentato un approfondimento sui sistemi operativi più diffusi in ambito automotive: FreeRTOS e AUTOSAR Classic per i microcontrollori, QNX e AUTOSAR Adaptive per i microprocessori. L'obiettivo è fornire una panoramica delle soluzioni software adottate e del loro ruolo nell'assicurare affidabilità, determinismo e integrazione tra piattaforme eterogenee.

# 1.4.4 Implementazione software

Qui si entra nel dettaglio dell'implementazione del firmware, descrivendo lo stack software e gli strumenti di sviluppo utilizzati, tra cui IDE, SDK e interfacce di debug.

Vengono illustrati i principali componenti del codice e le tecniche adottate per la gestione delle periferiche, degli interrupt e della logica di codifica/decodifica dei messaggi CAN. Per chiarezza espositiva, gli algoritmi e le soluzioni più rilevanti sono presentati tramite esempi di pubblico dominio, come i buffer di tipo ping-pong, senza riportare materiale proprietario. Il capitolo evidenzia così le scelte implementative alla base del funzionamento del firmware e le metodologie applicate per garantire robustezza ed efficienza.

### 1.4.5 Integrazione con sistema Host

Analizza il processo di integrazione del firmware con i sistemi host di più alto livello. Viene descritto il ruolo dei codec CAN come interfaccia tra microcontrollori e applicazioni, con particolare attenzione all'utilizzo di formati efficienti per la serializzazione dei dati, come FlatBuffers. Sono inoltre illustrate le modalità di comunicazione tra MCU e host, implementate attraverso diversi protocolli e meccanismi, tra cui SPI, UART, Ethernet e shared memory, in ambienti operativi come Linux, QNX o AUTOSAR. Il capitolo mostra come tali soluzioni permettano di garantire interoperabilità e affidabilità nello scambio di dati tra componenti eterogenei del sistema.

### 1.4.6 Ottimizzazione e performance

Questo capitolo è dedicato alle attività di analisi e ottimizzazione delle prestazioni del firmware. Dopo aver introdotto le metriche e gli strumenti utilizzati, come contatori hardware e timer, vengono esaminati i principali colli di bottiglia individuati, tra cui l'uso di allocazioni dinamiche, la gestione della memoria condivisa e l'impatto delle routine di debug. Vengono quindi presentate le soluzioni implementate per migliorare l'efficienza, tra cui la ristrutturazione di algoritmi, l'adozione di strutture dati più leggere e la riduzione della complessità nel codec CAN. Il capitolo si conclude mostrando i benefici ottenuti in termini di latenza, utilizzo delle risorse e stabilità complessiva del sistema.

# 1.4.7 Testing e validazione

Vengono illustrate le metodologie adottate per la verifica e la validazione del firmware sviluppato. Sono presentati i test condotti su banco e in scenari simulati, con l'obiettivo di riprodurre condizioni realistiche senza riportare dati sensibili. I risultati discussi, pur basati su valori esemplificativi, permettono di evidenziare i miglioramenti ottenuti dopo le attività di ottimizzazione, in termini di tempi di risposta, stabilità e affidabilità. Inoltre, il capitolo descrive le strategie di gestione degli errori, l'implementazione di watchdog hardware e software e le procedure di logging utilizzate per monitorare il comportamento del sistema e rilevare eventuali anomalie.

#### 1.4.8 Conclusioni

Il nono capitolo raccoglie le conclusioni del lavoro di tesi, presentando una sintesi dei risultati ottenuti e delle principali ottimizzazioni introdotte nel firmware. Viene proposta una valutazione critica delle soluzioni adottate, evidenziandone i punti di forza e i limiti riscontrati durante lo sviluppo e i test. Infine, il capitolo offre una panoramica delle possibili evoluzioni future, come l'adozione dello standard CAN FD, l'implementazione di SAE J1939 e l'integrazione di meccanismi avanzati di sicurezza e diagnostica, delineando le prospettive per lo sviluppo di sistemi embedded automotive sempre più efficienti e affidabili.

# 2 Reti veicolari e veicoli moderni

# 2.1 Evoluzione delle architetture elettroniche a bordo veicolo

Come anticipato nei paragrafi precedenti, tutti i veicoli moderni sono dotati di una o più reti veicolari, necessarie per gestire l'elevata complessità elettronica a bordo. Oggi, un veicolo integra fra **70 e 100 ECU (Electronic Control Units)** — per funzioni che spaziano dal controllo motore e frenata ai sistemi di climatizzazione — rispetto a poche centraline presenti in passato, e ciò comporta una gestione dei dati molto più sofisticata.

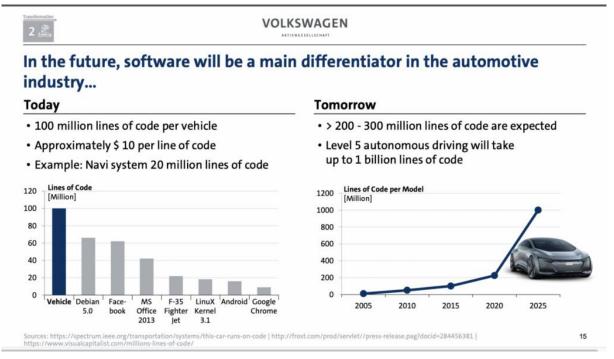

L'altra dimensione della complessità è data dal software: un'auto moderna, secondo Porsche Engineering [3], contiene circa **100 milioni di linee di codice**, una cifra sorprendente se si considera che un Boeing 787 ne include "solo" circa 14 milioni.

In un articolo di NXP [4] si parla addirittura di "centinaia di milioni di linee di codice" necessarie per far funzionare sistemi di infotainment, parcheggio automatico, telecamere surround e radar, con un impatto crescente man mano che si evolvono connettività, elettrificazione e autonomia (intesa come l'avvento di automatismi) dei veicoli.

Figura 2 Slide from a 2020 presentation by Herbert Diess highlights the VW Group's software ambitions

Questa complessità non riguarda solo il numero di nodi e la dimensione del software, ma anche la **topologia dell'architettura elettronica**. Le prime generazioni di veicoli avevano un'**architettura distribuita**, con ECU dedicate a singole funzioni

e cablaggi estesi e complessi. Questa soluzione, pur semplice da sviluppare inizialmente, si è rivelata inefficiente e poco scalabile: con l'aumento delle funzioni, il cablaggio è diventato eccessivamente pesante e costoso, e la gestione dei segnali sempre più complessa.

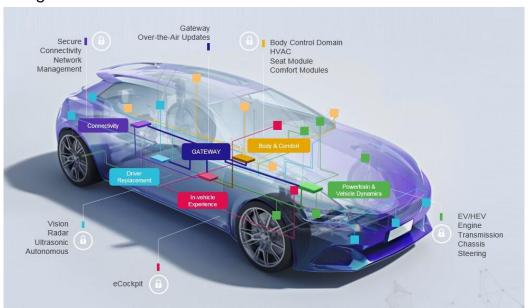

Per superare questi limiti, si è progressivamente passati ad **architetture a dominio**, in cui le ECU vengono raggruppate in base alla funzione (es. powertrain, chassis, infotainment, ADAS, body control). Ogni dominio è gestito da un controller centrale che raccoglie e coordina i dati delle ECU locali.

Figura 3 NXP illustration on vehicle architecture distribution [4]

Tale passaggio è motivato da esigenze operative precise: i veicoli moderni devono gestire non soltanto un'enorme mole di dati, ma anche garantirne la trasmissione in modo tempestivo e affidabile. Oggi, la tendenza più recente è quella verso **architetture zonali**, in cui le funzioni non sono più raggruppate per tipologia ma per posizione fisica nel veicolo (zona anteriore, posteriore, laterale, cabina, ecc.). Ogni Zonal ECU raccoglie i segnali dei dispositivi situati nella propria area e li inoltra a un **High Performance Computer (HPC)** centrale, responsabile dell'elaborazione ad alto livello e della gestione del software applicativo.

Questo approccio consente:

- riduzione significativa del cablaggio (meno cavi, meno peso);

- maggiore modularità (facilità di manutenzione e aggiornamento);

- **scalabilità** migliorata, poiché nuovi moduli possono essere aggiunti con minori modifiche all'architettura esistente;

- gestione più **efficiente** del software, grazie alla centralizzazione su piattaforme di calcolo più potenti.

# 2.2 Software-defined vehicle e implicazioni

Con la crescente complessità del software e l'introduzione di HPC, si sta affermando il concetto di **Software-Defined Vehicle (SDV)**, in cui le funzionalità del veicolo non sono più determinate dall'hardware, ma dallo *stack software* installato. Gli aggiornamenti possono così introdurre nuove funzioni senza modificare l'hardware di base, abilitando modelli di business come *feature on demand* o aggiornamenti OTA continui.

Questa evoluzione implica:

- adozione di **sistemi operativi real-time (RTOS)** sui microcontrollori e di sistemi multitasking su processori ad alte prestazioni;

- utilizzo di middleware standardizzati come AUTOSAR Classic e AUTOSAR Adaptive, per gestire la complessità e garantire portabilità;

- necessità di **ottimizzare i flussi dati tra i vari livelli**, dal firmware embedded ai processi di alto livello, come nel caso del lavoro oggetto di questa tesi.

## 2.3 Le reti di comunicazione

Il passaggio verso architetture più centralizzate non sarebbe possibile senza reti di comunicazione affidabili e deterministiche. Le reti veicolari permettono alle diverse ECU di scambiarsi informazioni in tempo reale e coordinare le funzioni del veicolo. I principali protocolli in uso sono:

- **CAN** (Controller Area Network): lo standard più diffuso, robusto e adatto a segnali critici in tempo reale (motore, freni, trasmissione).

- **Automotive Ethernet**: introdotto per funzioni ad alto volume di dati, come telecamere, radar, sistemi ADAS e infotainment, sta man mano diventando sempre più di largo utilizzo.

- **LIN** (Local Interconnect Network): usato per sottosistemi meno critici, come la regolazione dei sedili o l'illuminazione interna.

- **FlexRay**: protocollo ad alta affidabilità per funzioni di sicurezza, oggi *in parziale declino* a favore di Ethernet.

Ogni rete ha caratteristiche specifiche in termini di velocità, priorità dei messaggi, costo e robustezza.

Nel caso del CAN, ad esempio, la comunicazione è basata su un bus multi-master con arbitraggio a priorità, in cui i messaggi con identificatore più basso hanno precedenza. La velocità tipica varia da 125 kbps a 1 Mbps, mentre la variante CAN FD (Flexible Data-rate) consente di arrivare fino a 8 Mbps e di trasmettere frame fino a 64 byte, riducendo l'overhead e aumentando l'efficienza del bus.

L'introduzione di Automotive Ethernet (100BASE-T1, 1000BASE-T1) ha aperto la strada a un nuovo paradigma, in cui il veicolo diventa una vera e propria rete IP interna, capace di gestire simultaneamente streaming video, diagnostica remota e aggiornamenti OTA (Over-The-Air). Tuttavia, la coesistenza di reti eterogenee rende necessaria una gestione accurata della gateway architecture, ovvero delle ECU che traducono e instradano i messaggi tra protocolli diversi.

# 2.4 Il protocollo CAN (Controller Area Network)

Il **Controller Area Network (CAN)** è lo standard di comunicazione più diffuso nei sistemi embedded automotive. Sviluppato da Bosch nel 1986 e formalizzato come ISO 11898, è stato progettato per consentire la comunicazione affidabile fra più centraline elettroniche (ECU) senza la necessità di una topologia master-slave.

Il CAN è un **bus seriale multi-master e message-oriented**, dove ogni nodo può trasmettere e ricevere messaggi in modo asincrono, condividendo lo stesso mezzo trasmissivo. La sua robustezza, affidabilità e basso costo hanno reso questa tecnologia lo standard de facto per la comunicazione veicolare.

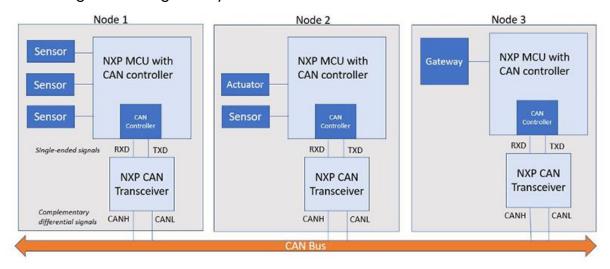

#### 2.4.1 Architettura del bus CAN

Tutti i nodi di una rete CAN sono collegati tra loro tramite un bus differenziale a **due fili intrecciati**, denominati **CAN High (CANH)** e **CAN Low (CANL)**. Proprio la comunicazione differenziale fornisce un'alta resistenza a disturbi elettrici esterni, fondamentali su un autoveicolo.

Ogni nodo è costituito da tre componenti principali:

- un microcontrollore (MCU), che gestisce la logica applicativa;

- un controller CAN, spesso integrato nel microcontrollore stesso, che si occupa della codifica/decodifica dei frame;

- un **transceiver**, che converte i segnali logici (TXD/RXD) in segnali differenziali su CANH e CANL.

Questa architettura consente di collegare nodi di complessità molto variabile – da sensori digitali fino a gateway di rete o centraline di calcolo avanzato.

Figura 4 Architettura tipica di una rete CAN [5]

#### 2.4.2 Struttura del frame CAN

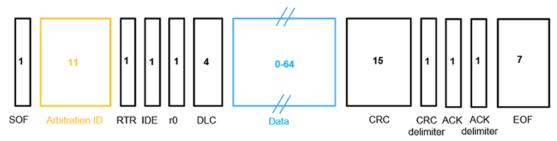

Un **frame CAN** è l'unità base di comunicazione sul bus. Tutti i nodi ascoltano costantemente il bus e, quando il mezzo è libero, uno di essi può iniziare una trasmissione. Ogni frame contiene diversi campi funzionali, come mostrato in Figura 5

Figura 5 Struttura di un frame CAN standard [5]

| Campo    | Descrizione                                                                    | Note                              |

|----------|--------------------------------------------------------------------------------|-----------------------------------|

| SOF      | Start of Frame – bit dominante che segnala l'inizio<br>del messaggio           | 1 bit                             |

| ID       | ldentifica il messaggio e la sua priorità                                      | 11 o 29 bit                       |

| RTR      | Remote Transmission Request – bit recessivo se il<br>frame è di richiesta dati | 1 bit                             |

| IDE      | Indica formato standard (11 bit) o esteso (29 bit)                             | 1 bit                             |

| r0 / FDF | Riservato; indica un frame CAN-FD                                              | 1 bit                             |

| DLC      | Data Length Code – numero di byte nel campo dati                               | 4 bit                             |

| DATA     | II )ati ettettivi                                                              | 0–8 byte (fino a 64 in<br>CAN FD) |

| CRC      | Cyclic Redundancy Check – controllo d'errore                                   | 15 + 1 bit                        |

| ACK      | Bit di conferma dai nodi riceventi                                             | 1+1 bit                           |

| EOF      | End of Frame – 7 bit recessivi                                                 | 7 bit                             |

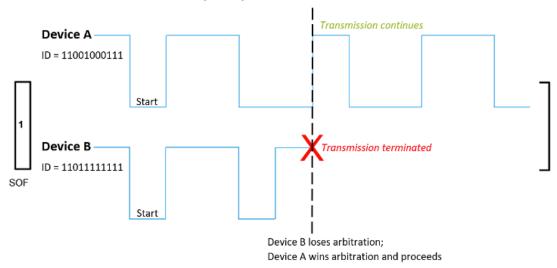

# 2.4.3 Funzionamento ed arbitraggio

Il protocollo CAN utilizza un meccanismo denominato arbitraggio non distruttivo a livello di bit (**lossless bitwise arbitration**) per determinare la priorità dei messaggi. Ogni nodo della rete è in grado sia di trasmettere sia di ricevere messaggi; tuttavia, **solo un messaggio alla volta può occupare il bus**.

L'accesso al mezzo è di tipo **event-driven**, per cui può accadere che più nodi tentino di iniziare una trasmissione nello stesso istante.

In tali casi, il protocollo stabilisce automaticamente quale messaggio debba avere la precedenza: il messaggio con priorità più alta "vince" l'arbitraggio e ottiene il controllo del bus. La priorità è determinata confrontando i bit dell'identificativo del messaggio (Arbitration ID) uno alla volta (bitwise):

un valore binario più basso corrisponde a priorità più alta, poiché il bit logico '0' (detto dominante) prevale sul bit logico '1' (detto recessivo).

Il nodo che "vince" l'arbitraggio prosegue la trasmissione senza ritardi, perdita o corruzione del messaggio, mentre il nodo che trasmetteva un messaggio a priorità inferiore interrompe immediatamente l'invio. Una volta che il bus torna libero, quest'ultimo tenterà nuovamente la trasmissione.

Per chiarire il principio, si considerino due dispositivi che iniziano a trasmettere simultaneamente sul bus CAN.

Il Dispositivo A ha un identificativo di arbitraggio pari a 11001000111, mentre il Dispositivo B ha un identificativo 11011111111.

Poiché il quarto bit del messaggio di A è 0 (dominante), mentre quello di B è '1' (recessivo), il messaggio di A prevale e ottiene il controllo del bus.

Il dispositivo A quindi completa la trasmissione, mentre il dispositivo B attende che la linea sia nuovamente libera per ripetere il tentativo.

Figura 6 Esempio di arbitraggio di priorità nel bus CAN [5]

In aggiunta, oltre a identificare univocamente il messaggio, il campo di arbitraggio (ID) definisce anche la priorità con cui esso può accedere al bus: ID più basso → priorità più alta.

Quando più nodi trasmettono contemporaneamente, il protocollo assicura che solo il messaggio con priorità maggiore proceda, garantendo un accesso ordinato, deterministico (latenza massima prevedibile in base ai messaggi con priorità superiore già presenti sulla rete) e privo di collisioni distruttive. [5]

# 2.4.4 Tipologie di frame nel protocollo CAN

Un messaggio trasmesso sulla rete CAN (Controller Area Network) è denominato frame. Il protocollo definisce quattro tipologie principali di frame, ciascuna con una funzione specifica all'interno della comunicazione tra nodi.

- Data frame: rappresenta la tipologia più comune e costituisce l'unico frame contenente dati effettivi. La sua struttura comprende:

- o Arbitration ID, che identifica la priorità del messaggio;

- o Campo dati, contenente le informazioni da trasmettere;

- o CRC, utilizzato per il rilevamento degli errori;

- ACK, che conferma la corretta ricezione del messaggio da parte dei nodi.

- Remote Frame: consente a un nodo di richiedere dati specifici a un altro nodo della rete. Le differenze principali rispetto al Data frame sono due:

- la presenza di un bit RTR recessivo all'interno del campo di arbitraggio, che identifica esplicitamente il frame come richiesta;

- l'assenza del campo dati, poiché il frame non trasporta informazioni ma funge esclusivamente da richiesta.

- Error Frame: Quando un nodo rileva un'anomalia, trasmette un Error frame a tutti gli altri nodi della rete. Questi, a loro volta, propagano lo stesso frame, garantendo che l'errore venga riconosciuto globalmente.

Per evitare un ciclo infinito di messaggi di errore (bus flooding), i transceiver CAN implementano contatori hardware di errore, che limitano la ritrasmissione automatica di tali frame.

- Overload Frame: ha la funzione di introdurre un ritardo tra un Data o

Remote frame e il successivo, richiedendo implicitamente la

ritrasmissione del messaggio in un secondo momento. Tuttavia, con

l'evoluzione dei controller CAN, questa tipologia è stata progressivamente

abbandonata: i dispositivi moderni sono infatti in grado di gestire

autonomamente i tempi di elaborazione, evitando così un traffico

superfluo sul bus.

#### 2.4.5 Rilevamento degli errori nel protocollo CAN

La robustezza del bus CAN deriva in larga parte dall'ampia gamma di meccanismi di rilevamento degli errori che esso implementa. In particolare, il protocollo CAN integra cinque metodi di controllo, di cui **tre a livello di messaggio** e **due a livello di bit**. Qualora un messaggio non superi anche solo uno di questi controlli, esso viene scartato e il nodo ricevente genera un **Error frame**.

#### • Controlli a livello di messaggio

- CRC e ACK: i campi Cyclic Redundancy Check e Acknowledgement includono rispettivamente un checksum e bit delimitatori, che consentono di verificare l'integrità del messaggio e la corretta ricezione da parte dei nodi.

- Form check: alcuni campi del messaggio devono obbligatoriamente contenere bit recessivi. Tra questi rientrano l'End of Frame (EOF), il delimitatore dell'ACK e quello del CRC. L'eventuale rilevamento di un bit dominante in tali posizioni genera un errore.

#### · Controlli a livello di bit

- Bit monitoring: i trasmettitori monitorano i propri messaggi bit per bit.

Se il valore scritto sul bus non coincide con quello letto, viene generato un errore.

- Bit stuffing: per garantire la sincronizzazione della rete, dopo cinque bit consecutivi dello stesso livello logico viene inserito automaticamente un bit di livello opposto. I nodi riceventi provvedono poi a rimuovere i bit "stuffed". Questa regola si applica a tutti i campi del frame, ad eccezione del delimitatore CRC, del campo ACK e dell'EOF. La presenza di sei bit consecutivi della stessa polarità costituisce una violazione della regola di bit stuffing e determina la generazione di un errore.

#### 2.4.6 Svantaggi del protocollo CAN

Nonostante la sua ampia diffusione e i numerosi punti di forza, il **CAN classico** presenta alcune limitazioni che ne riducono l'efficienza in applicazioni moderne e ad alta intensità di dati.

- Overhead significativo: uno dei principali svantaggi del CAN classico è l'elevato rapporto tra bit di controllo e bit utili. A fronte di un payload massimo di soli 8 byte, la struttura del frame include numerosi campi di arbitraggio, controllo e delimitazione. Questo comporta un overhead proporzionalmente molto alto, che riduce l'efficienza della trasmissione, soprattutto quando i messaggi devono essere inviati con elevata frequenza o contengono informazioni numericamente consistenti.

- Larghezza di banda limitata: la velocità massima di trasmissione è pari a 1

Mbps, un valore adeguato a molte applicazioni tradizionali, ma insufficiente per sistemi avanzati che richiedono throughput più elevati.

- Scarsa scalabilità: all'aumentare del numero di nodi e del traffico sul bus, cresce la probabilità di ritardi dovuti all'arbitraggio delle priorità, con possibili conseguenze negative sulla prevedibilità temporale in applicazioni realtime.

- **Assenza di meccanismi di sicurezza nativi**: il protocollo non integra funzioni di autenticazione o crittografia, rendendo necessarie soluzioni esterne per garantire la protezione da attacchi informatici. [6]

Figura 7 comparazione di diversi frame classici ed FD [7]

Nel contesto specifico delle **attività di tirocinio e della presente tesi**, è importante sottolineare che non è stato adottato il **CAN FD (Flexible Data Rate)**, il quale avrebbe permesso di estendere il payload fino a **64 byte** e di incrementare la velocità di trasmissione. A mio avviso, questa scelta ha rappresentato una **limitazione significativa**, poiché l'uso del CAN classico ha imposto vincoli stringenti in termini di efficienza e capacità di trasferimento dati, influenzando direttamente le possibilità di ottimizzazione del sistema sviluppato.

# 3 Piattaforme hardware

Nei veicoli moderni, il software e l'elettronica hanno un ruolo centrale, e la scelta della piattaforma hardware è determinante per le prestazioni e l'affidabilità del sistema. In questo contesto, due categorie principali di dispositivi emergono: microcontrollori (MCU) e microprocessori (MPU/CPU) anche se molto spesso vedremo come gli MPU in ambito automotive siano realmente dei System on Chip (SoC).

# 3.1 Microcontroller Unit e Microprocessor Unit

Un **microcontrollore (MCU, MicroController Unit)** è un circuito integrato che combina al suo interno CPU, memoria e periferiche di input/output ed è progettato per controllare dispositivi elettronici in modo autonomo e deterministico. A differenza dei microprocessori, le MCU sono pensate per applicazioni embedded, dove il controllo diretto di sensori, attuatori e altri moduli elettronici è fondamentale, con vincoli stringenti su tempi di risposta, consumi energetici e spazio fisico.

Figura 8 MCU, MPU, SoC

# 3.1.1 Componenti principali di un microcontrollore

Secondo la classificazione proposta da IBM [8], i microcontrollori possono essere descritti attraverso i sequenti blocchi funzionali:

• **Unità di elaborazione (CPU)**: esegue le istruzioni del programma e coordina le operazioni interne.

#### • Memoria:

- o RAM per i dati temporanei,

- Flash/EEPROM per il firmware, che rimane memorizzato anche senza alimentazione.

- **Periferiche integrate**: moduli hardware che permettono l'interazione diretta con il mondo esterno, come convertitori analogico/digitali, timer, contatori, interfacce seriali UART ed altri protocolli di comunicazione come SPI e CAN.

- **Moduli ausiliari**: in alcune MCU avanzate possono essere presenti controller per display LCD, Ethernet, USB, ecc.

### 3.1.2 Tipologie di microcontrollori

L'evoluzione tecnologica ha portato alla nascita di diverse famiglie di MCU, differenziate per architettura e capacità [8]:

- **8-bit**: soluzioni semplici, a basso costo, usate in piccoli elettrodomestici, giocattoli e telecomandi.

- **16-bit**: più potenti, adatte a dispositivi medicali, sistemi industriali e applicazioni automotive di medio livello.

- 32-bit: le più diffuse oggi, basate principalmente su architetture ARM

Cortex-M, utilizzate in robotica, automotive, IoT e sistemi industriali avanzati.

- RISC (Reduced Instruction Set Computer): architetture semplificate che eseguono istruzioni più velocemente, come gli ARM (Advanced RISC Machines), oggi standard de facto nel settore.

- **PIC (Peripheral Interface Controller)**: microcontrollori compatti e versatili, molto usati in automazione e robotica.

- **DSP/FPGA-based MCU**: soluzioni ibride per applicazioni che richiedono elaborazione di segnali, video processing o networking ad alta velocità.

# 3.1.3 Microprocessor Unit (MPU)

Tradizionalmente, un MPU viene definito come un'unità di calcolo pura, progettata per eseguire istruzioni e coordinare le operazioni logiche e aritmetiche di un sistema. In questa concezione classica, il microprocessore non integra né memoria né periferiche: per funzionare necessita di componenti esterni, come RAM, memoria non volatile e controller di I/O. Questa architettura modulare è tipica dei computer general-purpose, dove la CPU è separata dagli altri sottosistemi e si limita a svolgere il ruolo di "cervello" centrale.

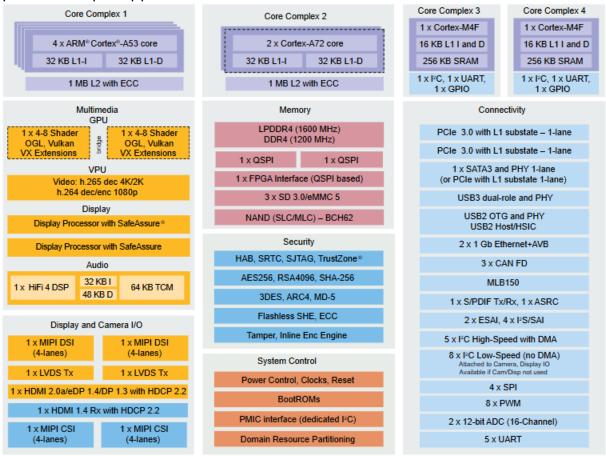

Tuttavia, nel mondo **embedded** e in particolare in ambito automotive, questa distinzione netta tende a sfumare. Le esigenze di riduzione dei costi, dei consumi energetici e della complessità di integrazione hanno portato all'evoluzione verso **System-on-Chip (SoC)**, in cui anche i microprocessori includono al loro interno blocchi funzionali che un tempo erano esclusivamente appannaggio delle MCU.

Oggi molte MPU destinate all'automotive integrano:

- **memorie on-chip** (cache di grandi dimensioni, RAM integrata, talvolta anche Flash),

- periferiche di comunicazione (CAN, Ethernet automotive, USB, PCIe),

- moduli grafici o DSP dedicati per l'elaborazione di segnali e immagini,

- **core eterogenei**: accanto ai core ad alte prestazioni (ARM Cortex-A, tipici delle MPU) vengono spesso affiancati core a basso consumo e deterministici (ARM Cortex-M), che svolgono il ruolo di microcontrollori integrati.

Questa architettura eterogenea consente di combinare in un unico dispositivo la **potenza di calcolo elevata** necessaria per applicazioni complesse (infotainment, ADAS, sensor fusion) con la **deterministicità real-time** tipica delle MCU, indispensabile per la gestione di periferiche critiche e funzioni di sicurezza.

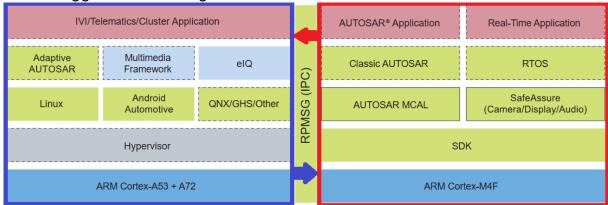

In ambito automotive, tali soluzioni vengono spesso utilizzate come **piattaforme centralizzate**: la parte "MPU" esegue sistemi operativi complessi (Linux, QNX, AUTOSAR Adaptive) e gestisce applicazioni ad alto livello, mentre i core "MCU-like" integrati si occupano di attività a bassa latenza, come la gestione del bus CAN o il monitoraggio di funzioni di sicurezza.

In questo modo, anche se per definizione un microprocessore dovrebbe essere un sistema privo di periferiche e memoria, nella pratica delle applicazioni embedded moderne si tende a **integrare tutto su un singolo chip**, dando vita a soluzioni ibride che uniscono i vantaggi di MCU e MPU in un'unica piattaforma. Vedi la Figura 8 per avere un paragone visuale di queste 3 strutture.

#### 3.2 Board utilizzate

Dopo aver introdotto le differenze concettuali tra microcontrollori e microprocessori, è utile descrivere le piattaforme hardware concretamente impiegate nello sviluppo del progetto. L'attività, infatti, si è articolata in più fasi, ciascuna caratterizzata dall'uso di una scheda differente, scelta in base alle esigenze di sperimentazione, budget e portabilità del firmware.

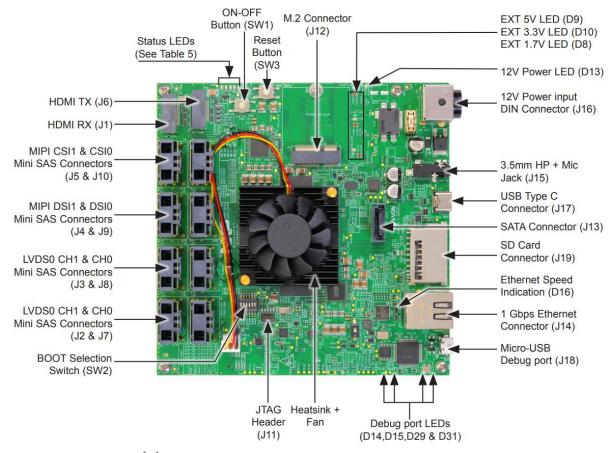

#### 3.2.1 NXP i.MX8QM MEK

Figura 9 i.MX 8QM MEK [9]

La prima piattaforma utilizzata è stata la NXP i.MX8QM Multisensory Enablement Kit (MEK), una scheda di sviluppo basata su un SoC eterogeneo con core ARM Cortex-A ad alte prestazioni e core Cortex-M integrati. Questa board rappresentava l'hardware originale del progetto e costituiva il punto di partenza per la mia attività di sviluppo. Il lavoro iniziale ha riguardato la modifica e l'adattamento del firmware esistente, con l'obiettivo di comprenderne la struttura, studiarne i punti forti/deboli e di predisporre il codice per una successiva portabilità su diverse piattaforme. La scheda è stata utilizzata in abbinamento a un modulo di espansione per il CAN bus, necessaria per la comunicazione con altri dispositivi non avendo nativamente i transceiver CAN integrati.

Per una descrizione più dettagliata è più intuitivo con attenzione la struttura interna dell'i.MX 8 rappresentata in Figura 10, dove possiamo notare la presenza di 6 core

ad alte prestazioni (4+2) designati al livello applicativo e 2 core a "basse prestazioni" per applicazioni Real Time.

Figura 10 i.MX8 SoC structure [10]

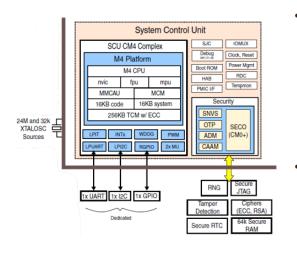

Inoltre, anche se poco documentato e non presente nell'immagine appena vista l'i.MX8 presenta un terzo cortex-M4 ed un cortex-M0 "non utilizzabile" [11].

- System Controller Unit subsystem is comprised of

- 1x Cortex-M4 processor

- A set of peripherals

- 1x TPM, 1x UART, 1x I2C, 8x GPIOs, 4x MUs

- This is the first processor to boot in the design

- Security subsystem is made of

- 1x Cortex-M0 processor running at 133MHz

- Handles security services for other processors

- A set of cryptographic related hardware accelerators

- RSA, ECC, AES, DES/3DES, SHA-1, SHA-2, MD5, HMAC, RNG

Figura 11 SCU [11]

L'M4 svolge esclusivamente il ruolo di **System Control Unit (SCU)** con il suo relativo

**System Control Unit Firmware (SCFW)**, firmware non completamente disponibile ma di cui è possibile modificare alcune parti e ricompilarle per personalizzare leggermente il comportamento della board.

Ulteriori approfondimenti verranno trattati nel capitolo dedicato ai problemi riscontrati e allo sviluppo del software; per una trattazione completa, comprendente gli aspetti hardware e software di SCU ed SCFW, si rimanda al documento [11].

#### 3.2.2 NXP S32K312 EVB

Figura 12 S32k312 [12]

La **\$32K312EVB-Q172** è una scheda di valutazione sviluppata da NXP per applicazioni automotive basate sulla famiglia di microcontrollori **\$32K3**. A differenza di piattaforme più complesse come la i.MX8, questa board non integra processori a livello applicativo (ad esempio core ARM Cortex-A), ma si basa esclusivamente su un **ARM Cortex-M7 a 32 bit**, progettato per garantire affidabilità, basso consumo e capacità di elaborazione real-time.

Questa caratteristica la colloca pienamente nella categoria delle **MCU automotive**, pensate per il controllo diretto di periferiche e la gestione deterministica di segnali e comunicazioni, piuttosto che per l'esecuzione di sistemi operativi complessi. Dal punto di vista hardware, la scheda offre:

- alimentazione flessibile 12-48V certificata per sicurezza funzionale;

- interfacce di comunicazione tipiche del settore automotive, come CAN FD e LIN;

- periferiche di test a bordo (LED, pulsanti, potenziometro ADC, pad capacitivi);

- slot compatibile Arduino UNO per l'espansione con shield esterni.

Sul piano software, la board è supportata da driver **AUTOSAR e non-AUTOSAR**, librerie di sicurezza e tool di sviluppo integrati nell'ambiente **S32 Design Studio**, con estensioni per MATLAB/Simulink.

Nel contesto del progetto, la **\$32K312EVB** era stata inizialmente selezionata come piattaforma di migrazione del firmware, con l'obiettivo di verificare la portabilità del codice da un ambiente basato su MPU (i.MX8) a un microcontrollore puro. Sono stati avviate le prime fasi del porting, ma la scheda è stata **abbandonata in una fase precoce**, principalmente per concentrare gli sforzi su una piattaforma più adatta all'integrazione finale e per altri motivi interni all'azienda.

Il suo ruolo, quindi, è rimasto marginale: utile come fase esplorativa per valutare le differenze tra un sistema eterogeneo ibrido ed uno puramente real-time.

#### 3.2.3 RT1064

Figura 13 i.MX RT1064 Evaluation Kit [13]

La piattaforma che ha avuto un ruolo centrale nello sviluppo del progetto è stata la NXP MIMXRT1064-EVK, scheda di valutazione basata sul microcontrollore i.MX RT1064, appartenente alla famiglia delle cosiddette crossover MCU. Questi dispositivi rappresentano una categoria intermedia tra microcontrollori e microprocessori: pur mantenendo le caratteristiche tipiche delle MCU (architettura deterministica, basso consumo, periferiche integrate), offrono frequenze di clock e capacità di memoria paragonabili a quelle di sistemi più complessi.

Il cuore della scheda è un **ARM Cortex-M7** operante fino a **600 MHz**, che la colloca tra le MCU a più alte prestazioni disponibili sul mercato. Il microcontrollore integra **4 MB di Flash on-chip** e **1 MB di RAM interna**, di cui una parte configurabile come **TCM (Tightly Coupled Memory)** per garantire latenze estremamente ridotte nelle applicazioni real-time. Questa caratteristica ha reso la piattaforma

particolarmente adatta al porting del firmware, riducendo la dipendenza da memorie esterne e semplificando la gestione del codice.

Dal punto di vista delle periferiche, la MIMXRT1064 offre un set molto ricco:

- 2 interfacce Ethernet 10/100 con supporto IEEE 1588,

- 2 controller USB 2.0 OTG con PHY integrato,

- fino a 8 UART, 4 I<sup>2</sup>C, 4 SPI,

- 2 moduli FlexCAN con supporto CAN FD,

- interfacce per memoria esterna (SDRAM, NAND, NOR, eMMC, QuadSPI),

- moduli audio e grafici (SAI, SPDIF, LCD controller, 2D graphics engine),

- convertitori ADC a 12 bit e comparatori analogici.

La scheda di valutazione **MIMXRT1064-EVK** integra inoltre:

- 256 Mb di SDRAM esterna,

- 512 Mb di HyperFlash e 64 Mb di QSPI Flash,

- connettori per LCD parallelo, camera, audio codec e CAN transceiver,

- compatibilità con lo **standard Arduino UNO pinout**, che ne facilita l'espandibilità.

## 3.3 Porting

Nel contesto dello sviluppo software per sistemi embedded, il termine **porting** indica il processo di **trasferimento e adattamento di un'applicazione o di un firmware da una piattaforma hardware a un'altra**, mantenendone il comportamento funzionale e le prestazioni attese. Questo processo non si limita alla semplice ricompilazione del codice sorgente, ma richiede una **revisione approfondita dell'interazione tra software e hardware**, in particolare per quanto riguarda la gestione delle periferiche, dei driver e delle risorse di sistema.

Il porting diventa necessario quando si cambia architettura (ad esempio da una MPU a una MCU), si sostituisce la scheda di sviluppo, oppure si desidera rendere il software compatibile con più target hardware. In ambito embedded, dove il software è spesso strettamente legato all'hardware sottostante, il porting può comportare modifiche significative a livello di:

- driver di basso livello,

- configurazione dei registri e delle periferiche,

- allocazione della memoria,

- gestione del clock e delle interruzioni,

- compatibilità con toolchain e ambienti di sviluppo differenti.

Nel settore automotive, il porting assume un ruolo strategico: consente di riutilizzare codice già validato su nuove piattaforme, riducendo i tempi di sviluppo e facilitando la scalabilità del software tra diverse ECU. Tuttavia, comporta anche sfide legate alla sicurezza funzionale e alla gestione di ambienti eterogenei, come nel caso di SoC che integrano core di tipo MPU e MCU.

Nel progetto descritto in questa tesi, il porting ha rappresentato una fase cruciale: partendo da un firmware originariamente sviluppato per una piattaforma MPU/SoC

(i.MX8), si è proceduto alla sua migrazione verso microcontrollori più leggeri (S32K312, i.MX RT1064), affrontando le problematiche legate alla compatibilità, alla disponibilità dei driver e alla gestione delle periferiche. Le soluzioni adottate e le scelte architetturali saranno descritte nei paragrafi successivi.

## 3.4 Problemi collegati all'hardware

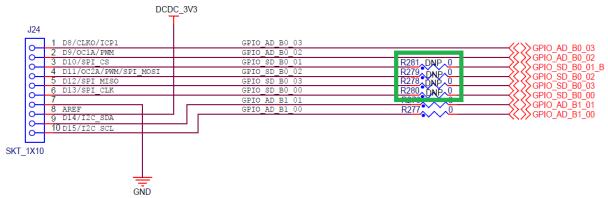

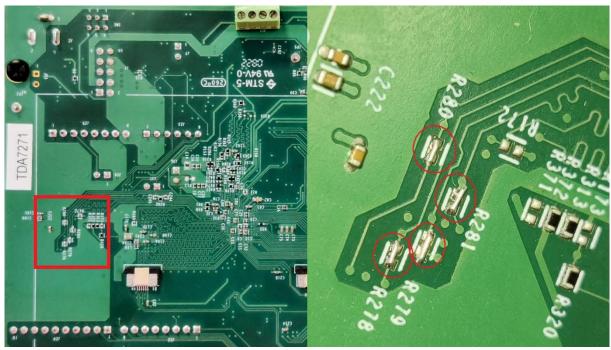

Durante l'integrazione della **MIMXRT1064-EVK** con il **Raspberry Pi 4** sono emerse due principali criticità. Da un lato, sul piano hardware, la comunicazione SPI non funzionava inizialmente perché gli header della scheda non erano collegati ai pin dell'MCU: nello schematico erano infatti presenti resistenze da 0  $\Omega$  marcate come *DNP* (Do Not Place).

Dall'altro lato, sul piano software, è stato riscontrato che nel **BSP di QNX per Raspberry Pi** il driver SPI era implementato solo in modalità **master**, mentre anche la RT1064 era stata configurata come master. È stato quindi necessario **invertire i ruoli**, mantenendo il Raspberry Pi come master e riconfigurando la RT1064 come slave, così da rendere possibile la comunicazione.

I dettagli tecnici e le implicazioni di queste scelte verranno approfonditi nel Capitolo 6.

## 4 Organizzazione software

#### 4.1 Modelli architetturali

Nello sviluppo di sistemi embedded complessi, la scelta di un modello architetturale adeguato è fondamentale per garantire **scalabilità**, **manutenibilità e portabilità** del codice.

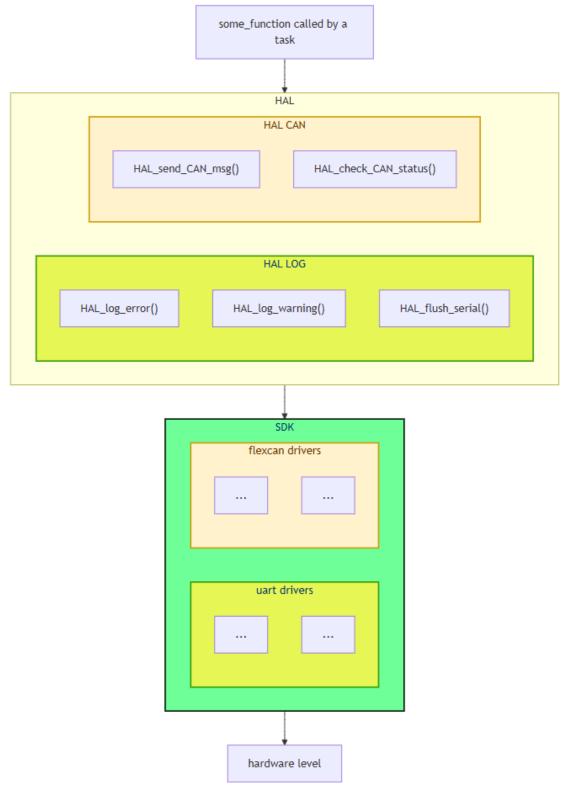

Due approcci particolarmente rilevanti sono:

- Hardware Abstraction Layer (HAL), che fornisce un'interfaccia uniforme tra

hardware e software applicativo, molto usata durante lo svolgimento di

questa tesi nello sviluppo del firmware;

- pattern architetturali a strati (come l'adapter pattern o l'architettura esagonale), che separano la logica di business dalla gestione delle periferiche e dei servizi esterni. Usata principalmente dal team per lo sviluppo a livello applicativo.

Questi modelli hanno lo scopo comune di ridurre le dipendenze dal sistema ospitante e di rendere il software più robusto ai cambiamenti di piattaforma.

## 4.2 Hardware Abstraction Layer

L'adozione di modelli architetturali orientati alla separazione delle responsabilità è stata determinante per garantire portabilità e manutenibilità del firmware. Tra questi, l'Hardware Abstraction Layer (HAL) ha svolto un ruolo centrale, consentendo di disaccoppiare in modo sistematico la logica applicativa dai driver specifici di piattaforma (SDK). L'impiego dell'HAL fin dalle fasi iniziali di sviluppo ha reso possibile un percorso di migrazione ordinato tra piattaforme eterogenee, riducendo lo sforzo necessario al minimo a fronte di uno sforzo maggiore per lo sviluppo del firmware originario.

#### 4.2.1 Cos'è realmente l'HAL

L'HAL è uno strato software intermedio che espone all'applicazione interfacce stabili (API) per l'accesso alle periferiche e ai servizi di base (ad esempio SPI, CAN, GPIO, timer, watchdog), nascondendo driver, il pin multiplexing, la configurazione dei clock e la gestione degli interrupt specifici di ciascun dispositivo.

In questo modo, il codice applicativo dipende da contratti funzionali chiari, anziché da implementazioni concrete.

Ne discende un duplice beneficio:

- da un lato si ottiene portabilità, perché l'implementazione dell'HAL può essere sostituita al variare della piattaforma;

- dall'altro si migliora la manutenibilità, perché la correzione di anomalie o l'ottimizzazione delle prestazioni resta confinata nello strato di astrazione, preservando l'integrità della logica superiore.

Figura 14 esempio di HAL

Nella Figura 14 è riportato un esempio di una possibile struttura di HAL. In questo schema, la funzione *some\_function>* — invocata da un task — utilizza gli HAL **CAN** e **LOG** per eseguire operazioni quali, ad esempio, l'invio di un messaggio sul bus CAN, la lettura del suo stato e la registrazione dell'evento sulla seriale, senza avere conoscenza diretta delle implementazioni sottostanti.

Se, nello stesso contesto, si volesse testare una diversa metodologia di logging, sarebbe sufficiente modificare l'HAL corrispondente, senza dover intervenire sul codice della funzione *<some\_function>* o sul task che la utilizza.

## 4.2.2 Progettazione modulare ed impatto sul porting

La scelta di strutturare fin da subito il firmware su i.MX8 intorno a interfacce HAL ha permesso di stabilire una chiara separazione tra la logica di alto livello (gestione dei messaggi, log, codifica) e i dettagli dell'SDK di piattaforma.

Il codice interagisce esclusivamente con API coerenti e documentate, evitando accessi diretti ai registri o dipendenza da nomi di funzione specifici dell'SDK sottostante.

Quando si è reso necessario migrare verso RT1064, il perimetro del cambiamento si è limitato, dove possibile, alla sostituzione dell'implementazione delle stesse interfacce: le chiamate applicative sono rimaste immutate, mentre sono stati riallineati i parametri di configurazione e i collegamenti ai driver del nuovo ambiente.

Questo ovviamente non è stato sempre possibile, ad esempio nel passaggio da un metodo di comunicazione (RPMsg) a un altro (SPI). Tuttavia, il principio resta valido: anche in questi casi l'HAL risulta utile per l'ottimizzazione e il test di differenti implementazioni, poiché è sufficiente modificare il codice sottostante al layer, senza intervenire sulla logica applicativa superiore.

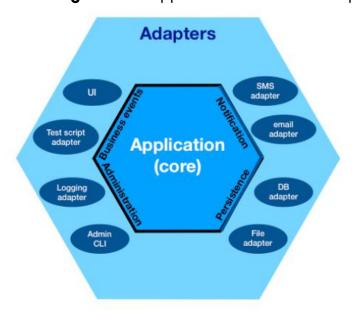

## 4.3 Architettura esagonale

L'**Architettura Esagonale** (nota anche come *Ports and Adapters*) è un pattern architetturale proposto da Alistair Cockburn nel 2005 [14] con l'obiettivo di separare il **core logico** di un'applicazione da tutte le dipendenze esterne come interfacce

utente, database. servizi esterni, protocolli di comunicazione, infrastruttura. La metafora dell'esagono serve principalmente rappresentare graficamente che il "cuore" dell'applicazione può avere più "facce" (alcune verso gli input, altre verso gli output) tramite cui interagire mondo esterno, mediante ports (interfacce astratte) adapters е (implementazioni concrete).

#### Componenti principali [14]:

- Il **core** (Dominio / Business Logic) è il centro dell'architettura. Qui risiedono gli use case, le regole di dominio, le entità (o strutture dati) centrali, insomma tutto ciò che rappresenta la logica di funzionamento indipendente dalla tecnologia. Il core **non dipende** da dettagli esterni: né driver hardware, né librerie, né protocolli di comunicazione.

- Le **porte** sono interfacce astratte esposte dal core, che definiscono i punti di ingresso e uscita per tutte le interazioni con l'esterno. Si distinguono principalmente due tipi:

- o **Inbound ports** (anche chiamati *primary* o *driving*): definiscono come il core può essere "guidato" dall'esterno (es. tramite un task, una richiesta, un interrupt, un messaggio).

- Outbound ports (o secondary / driven): definiscono come il core si aspetta di comunicare verso l'esterno per servizi che non sono implementati nel core (es. persistenza, comunicazione esterna, logging, interfacce di rete)

- Gli adapters sono le implementazioni concrete delle porte: traducono richieste verso il core o comportamenti del core verso componenti esterni. Ci sono adapter inbound (ricevono input esterno e lo adattano al formato che il core si aspetta) e adapter outbound (implementano servizi esterni su interfacce fornite dal core).

- Flusso delle dipendenze / principio di inversione

Un principio fondamentale è che le dipendenze devono andare verso l'interno, cioè il core non deve conoscere dettagli degli adapter o tecnologie concrete. Questo è strettamente legato al Dependency Inversion Principle (DIP). Le interfacce (porte) sono definite nel core, mentre gli adapter risiedono "all'esterno". In questo modo, è possibile sostituire un adapter (es. cambiare database, cambiare metodo di comunicazione) senza toccare il

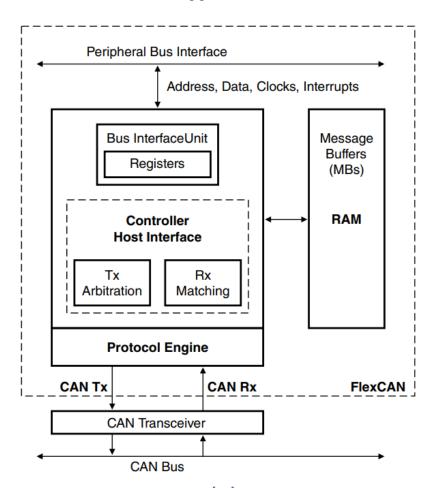

#### 4.4 FlexCAN

core.

Il controller FlexCAN è un'interfaccia CAN integrata nei SoC NXP progettata per offrire flessibilità nella gestione del traffico CAN/CAN FD pur mantenendo le garanzie di affidabilità richieste in ambito automotive. FlexCAN espone meccanismi hardware per il buffering, il filtraggio e il time-stamping dei frame, consentendo al software di delegare al controller le operazioni più onerose e di concentrare la logica applicativa sul trattamento semantico dei messaggi.

#### 4.4.1 Architettura funzionale essenziale

Message Buffers (MB): unità di memoria mappate hardware utilizzate per la trasmissione e la ricezione; ogni MB può essere configurato singolarmente come trasmettitore o ricevitore con relativo filtro/maschera.

- **Rx FIFO**: modalità alternativa di ricezione che consente di accumulare frame in coda in modo efficiente per scenari con traffico burst.

- **Filtri e maschere** hardware: permettono al controller di accettare solo gli ID di interesse, riducendo il carico della CPU.

- **Registri di stato e interrupt**: segnali dedicati per eventi di MB completato, errori di bus, wake-up e condizioni di overflow.

- **Timestamping**: marcatura temporale dei frame in ingresso, utile per analisi temporali e diagnostica.

- **Supporto CAN FD** (nelle revisioni compatibili): gestione di DLC esteso e di bit-rate differenziati tra arbitraggio e fase dati.

Figura 15 FlexCAN block diagram [27]

## 4.4.2 Pattern operativo adottato nel progetto

Nel firmware è stato realizzato un HAL specifico per FlexCAN che centralizza le operazioni di inizializzazione e gestione del controller senza esporre i dettagli dei registri al livello applicativo. Le attività principali svolte dal HAL sono: configurazione del bit timing e del pinmux, allocazione e configurazione dei Message Buffers (ruolo, filtri, DLC), abilitazione della Rx FIFO se necessaria e impostazione delle sorgenti di interrupt rilevanti.

Per minimizzare il tempo di esecuzione in interrupt e garantire determinismo, l'ISR gestita dal HAL svolge operazioni minime: riconosce l'evento sul MB o sulla FIFO, esegue una lettura rapida dello stato e delle dimensioni, e segnala l'avvenuto evento a un task dedicato tramite meccanismi RTOS (queue/semaphore). Il task di smaltimento, eseguito in contesto thread, provvede a leggere i frame completi dal driver HAL, applicare le operazioni di decodifica e parsing tramite un secondo HAL di livello superiore e inoltrare i payload alla pipeline applicativa per l'elaborazione.

## 4.4.3 Vantaggi di questo approccio

- ISR breve e prevedibile, riduzione del jitter nelle priorità real-time.

- Filtraggio precoce in hardware che riduce il carico CPU.

- Isolamento delle differenze di controller tra piattaforme: cambiando l'implementazione del HAL non cambiano le API esposte all'applicazione.

- Possibilità di ottimizzare buffering (MB vs FIFO), uso di DMA e politiche di retry senza alterare la logica di decoding.

Questa impostazione mantiene la complessità del controller confinata nello strato HAL e rende l'intera gestione CAN modulare, testabile e facilmente adattabile alle diverse revisioni hardware o ai requisiti di performance. I dettagli implementativi del driver FlexCAN e le scelte adottate saranno presentati nel capitolo 5 (Implementazione software).

Per motivi di riservatezza e in ottemperanza all'accordo di non divulgazione, i dettagli tecnici e le scelte implementative relative all'analisi e all'impiego dei Message Buffers del controller FlexCAN non sono riportati in questa sede.

Si può però affermare, senza entrare nel merito operativo, che una significativa porzione del lavoro sperimentale è stata dedicata allo studio delle politiche di buffering e allo studio delle modalità di ricezione/accodamento dei frame; tali attività hanno fornito gli elementi necessari per ottimizzare la latenza e la robustezza della catena di ricezione e decodifica.

I dettagli sperimentali, i risultati misurati e il codice sorgente relativo a queste attività non sono inclusi nella tesi per vincoli contrattuali, ma le conclusioni operative e gli effetti sul comportamento del sistema sono discussi sommariamente nei capitoli 7 e 8.

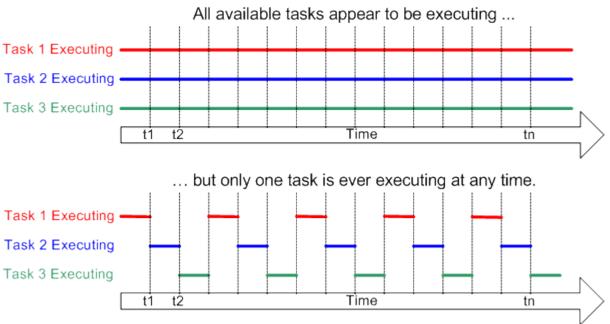

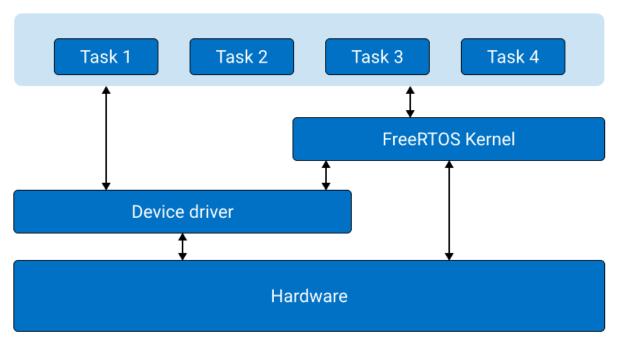

#### 4.5 RTOS su MCU