## POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

### Master's Degree Thesis

Model-Based Design and FPGA Implementation of a Pulse Detection Algorithm for Optical and RF Interrogations in Avionic application

Supervisor

Candidate

Prof. Mario Roberto CASU

Giuseppe RINALDO

Co-Supervisor

Ing. Marco AVITABILE

Ing. Riccardo STICCA

October 2025

#### Abstract

Modern airborne electronic computer implement pulse detection algorithms, that are fundamental for interpreting signals from ground station interrogations and laser-optical warning systems. These systems play a crucial role in aircraft's situational awareness and threat mitigation, in particular in complex operational environments.

These type of algorithms require efficient signal processing capabilities while maintaining high detection accuracy, in order to be capable of identifying fast and transient pulse signals while minimizing false detections. At the same time, these algorithms must maintain low latency and minimal hardware overhead, in order to ensure optimal real-time performance that are typical of modern avionics systems.

To address this challenge, the use of High-Level Synthesis (HLS) [1] tool within a model-based design framework provide a promising approach for implementing signal processing algorithms on FPGA platforms. This methodology enables a more abstract and modular design process, allowing rapid prototyping, early verification and effective design-space exploration. Moreover, it simplifies the development of optimized hardware architectures and resource utilization, computational efficiency and energy performance.

This thesis focuses on the design and implementation of a pulse detection algorithm targeting FPGA platforms through Siemens EDA Catapult HLS tool. This work includes the development, simulation and synthesis of the algorithm, with the evaluation of its hardware characteristics, including logic utilization, latency and power consumption. Furthermore, the study explores different architectural configurations and processing strategies to assess the trade-offs between performance and hardware resource overhead, offering insights into the optimal design choices for real implementation in aerospace applications.

Ai miei nonni Giuseppe e Concetta, i quali mi hanno permesso di essere l'uomo che sono oggi

# Table of Contents

| Li             | st of                         | Figure     | es                                     | VI |  |  |  |

|----------------|-------------------------------|------------|----------------------------------------|----|--|--|--|

| List of Tables |                               |            |                                        |    |  |  |  |

| A              | crony                         | $^{ m ms}$ |                                        | IX |  |  |  |

| 1              | Intr                          | oducti     | ion                                    | 1  |  |  |  |

|                | 1.1                           | Conte      | xt                                     | 1  |  |  |  |

|                | 1.2                           | High-l     | Level Synthesis Definition and History | 2  |  |  |  |

|                | 1.3                           | Object     | tives                                  | 5  |  |  |  |

|                | 1.4                           | Metho      | odology and Thesis Organization        | 6  |  |  |  |

| 2              | Imp                           | lemen      | tation in MATLAB                       | 8  |  |  |  |

|                | 2.1                           | Algori     | thm description                        | 8  |  |  |  |

|                | 2.2                           | Peaks      | and Noise Characterization             | 10 |  |  |  |

|                |                               | 2.2.1      | Effective signal power on detector     | 12 |  |  |  |

|                |                               | 2.2.2      | Noise modeling in the optical receiver | 12 |  |  |  |

|                | 2.3                           | Comp       | osite Signal Generation                | 18 |  |  |  |

|                |                               | 2.3.1      | Background noise generation            | 19 |  |  |  |

|                |                               | 2.3.2      | Pulse train generation                 | 20 |  |  |  |

|                |                               | 2.3.3      | Overall input waveform                 | 21 |  |  |  |

| 3              | Implementation in Simulink 2  |            |                                        |    |  |  |  |

|                | 3.1                           | Model      | Structure                              | 24 |  |  |  |

|                |                               | 3.1.1      | Inputs Block                           | 26 |  |  |  |

|                |                               | 3.1.2      | Opto Hybrid Block                      | 27 |  |  |  |

|                |                               | 3.1.3      | Analog To Digital Converter Block      | 32 |  |  |  |

|                |                               | 3.1.4      | FPGA Block                             | 37 |  |  |  |

|                |                               | 3.1.5      | Peaks Statistics Block                 | 40 |  |  |  |

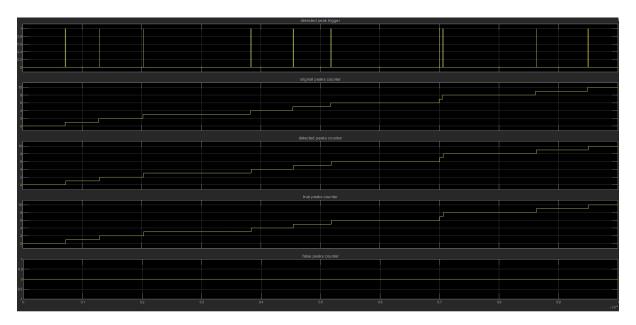

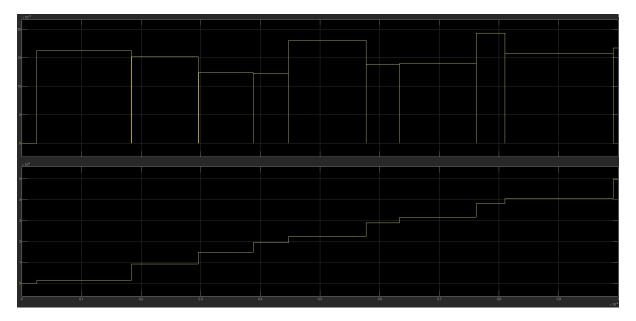

|                | 3.2                           | Simula     | ation results                          | 43 |  |  |  |

| 4              | Implementation in HDL Coder 4 |            |                                        |    |  |  |  |

|                | 4.1                           | Simuli     | ink HDL Coder                          | 44 |  |  |  |

|                | 12                            | HDI.       | Code Concretion                        | 15 |  |  |  |

#### TABLE OF CONTENTS

|         |                               | 4.2.1                 | HDL Coder suitable model                           | 46         |  |  |  |  |

|---------|-------------------------------|-----------------------|----------------------------------------------------|------------|--|--|--|--|

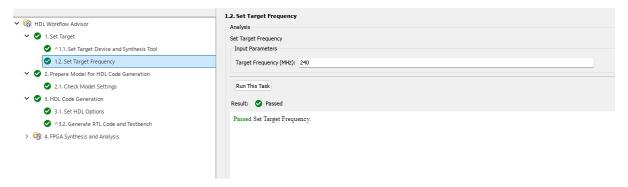

|         |                               | 4.2.2                 | HDL Coder workflow                                 | 50         |  |  |  |  |

|         | 4.3                           | Questa                | aSim Simulation                                    | 53         |  |  |  |  |

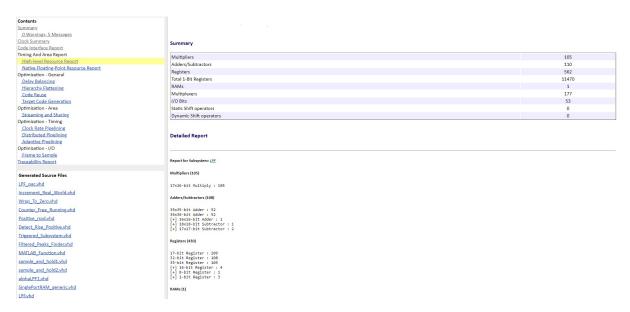

|         | 4.4                           | Vivado                | o Synthesis & Implementation                       | 55         |  |  |  |  |

| 5       | Implementation in Catapult 58 |                       |                                                    |            |  |  |  |  |

|         | 5.1                           | Catap                 | ult HLS                                            | 58         |  |  |  |  |

|         | 5.2                           | C++ .                 | Architecture & Optimization Pragmas                | 62         |  |  |  |  |

|         |                               | 5.2.1                 | Initial implementation                             | 64         |  |  |  |  |

|         |                               | 5.2.2                 | Optimized implementation                           | 72         |  |  |  |  |

|         | 5.3                           | Questa                | aSim Simulation                                    | 74         |  |  |  |  |

|         | 5.4                           | Vivado                | o Synthesis & Implementation                       | 75         |  |  |  |  |

| 6       | Res                           | ults an               | nd Reports                                         | <b>7</b> 8 |  |  |  |  |

|         | 6.1                           | Compa                 | arative Analysis of Implementations                | 78         |  |  |  |  |

|         |                               | 6.1.1                 | Implementations at $240MHz$                        | 79         |  |  |  |  |

|         |                               | 6.1.2                 | Initial implementations at $240MHz$ and $260MHz$   | 80         |  |  |  |  |

|         |                               | 6.1.3                 | Optimized implementations at $240MHz$ and $260MHz$ | 81         |  |  |  |  |

|         |                               | 6.1.4                 | Latency optimization                               | 82         |  |  |  |  |

|         |                               | 6.1.5                 | Time effort                                        | 83         |  |  |  |  |

| 7       | Con                           | clusio                | ns                                                 | <b>85</b>  |  |  |  |  |

| ${f A}$ | MA                            | $\operatorname{TLAB}$ | Source Codes                                       | 87         |  |  |  |  |

|         | A.1                           | Calcol                | lo_Vrms_noise_e_segnale_ver01.m                    | 87         |  |  |  |  |

|         | A.2                           |                       | Gim_GenData.m                                      | 90         |  |  |  |  |

| В       | HLS                           | S C++                 | - Source Codes and scripts                         | 96         |  |  |  |  |

|         | B.1                           |                       | threshold.h                                        | 96         |  |  |  |  |

|         | B.2                           |                       | n.h                                                | 97         |  |  |  |  |

|         | В.3                           |                       | h                                                  | 98         |  |  |  |  |

|         | B.4                           |                       | ence.h                                             | 98         |  |  |  |  |

|         | B.5                           |                       | effs.h                                             | 99         |  |  |  |  |

|         | B.6                           |                       |                                                    | 01         |  |  |  |  |

|         | B.7                           |                       |                                                    | 01         |  |  |  |  |

|         | B.8                           |                       | \ <del>-</del>                                     | 02         |  |  |  |  |

|         | B.9                           |                       |                                                    | 04         |  |  |  |  |

|         | B.10                          |                       |                                                    | 04         |  |  |  |  |

|         |                               |                       | — •                                                | .05        |  |  |  |  |

|         |                               | -                     | — — —                                              | 0.77       |  |  |  |  |

|         | B.12                          | 2 s_h_ r              | peak.h                                             | .07        |  |  |  |  |

|         |                               | _                     |                                                    | .07        |  |  |  |  |

### TABLE OF CONTENTS

| Bibliography    | 111 |

|-----------------|-----|

| Acknowledgments | 113 |

# List of Figures

| 1.1  | Target Pulse Identification within High-Noise Signals |

|------|-------------------------------------------------------|

| 1.2  | Design Flow                                           |

| 1.3  | Gajski-Kuhn Y-chart                                   |

| 1.4  | Tasks Timeline                                        |

| 2.1  | Block Diagram of the system                           |

| 2.2  | Measured Interferences                                |

| 2.3  | Measured Pulse                                        |

| 2.4  | Relationship with Signal Power                        |

| 2.5  | Working points                                        |

| 2.6  | MATLAB output transcript                              |

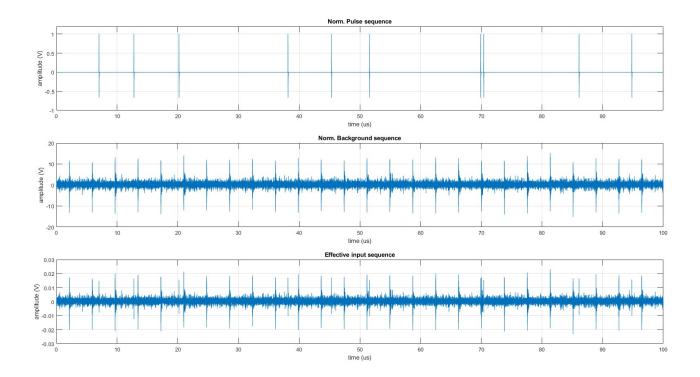

| 2.7  | Input waveforms                                       |

| 2.8  | Interference zoom                                     |

| 2.9  | Pulse zoom                                            |

| 3.1  | Simulink model                                        |

| 3.2  | Results displays                                      |

| 3.3  | Input block                                           |

| 3.4  | Opto Hybrid block                                     |

| 3.5  | Opto Hybrid - Signal Statistics sub-block             |

| 3.6  | Opto Hybrid - Original Peak Finder sub-block          |

| 3.7  | Time domain output                                    |

| 3.8  | Frequency domain output                               |

| 3.9  | Performace parameters                                 |

| 3.10 | Analog To Digital Converter block                     |

| 3.11 | Quantizer block parameters                            |

| 3.12 | Generic transfer function of an ADC                   |

| 3.13 | Quantizer2 sub-block                                  |

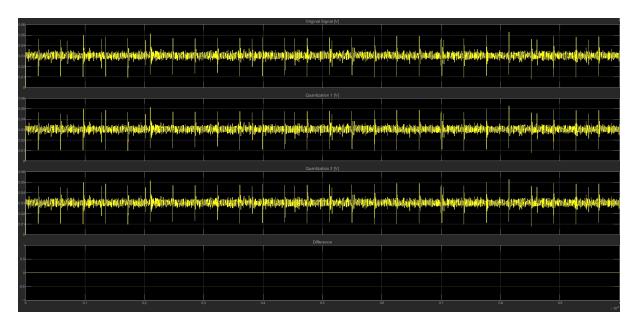

| 3.14 | ADC plots                                             |

| 3.15 | Digitalized signal zoom                               |

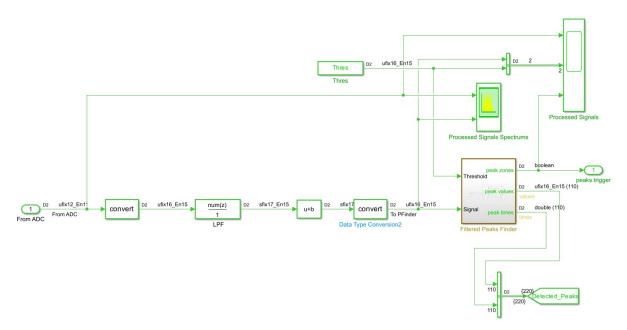

| 3.16 | FPGA block                                            |

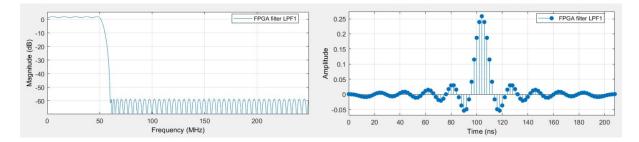

| 3.17 | FIR filter response and coefficients                  |

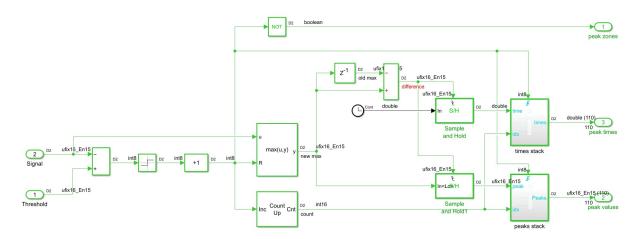

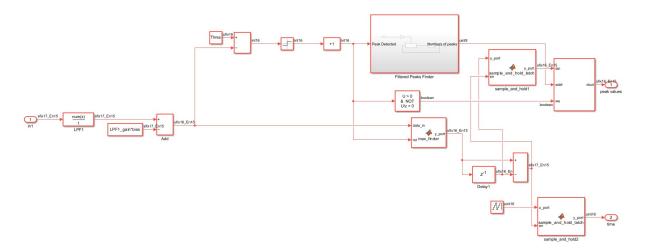

| 3.18 | FPGA-Peak finder sub-block                            |

### LIST OF FIGURES

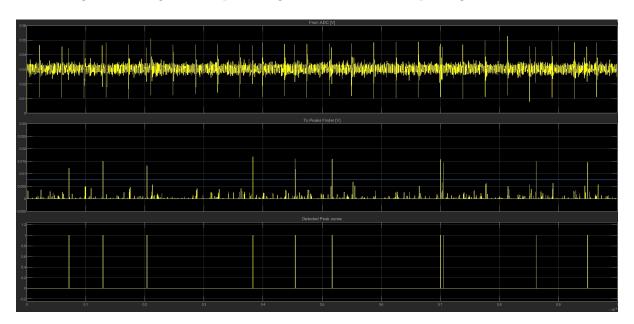

| 3.19 | FPGA results plot                                             |

|------|---------------------------------------------------------------|

| 3.20 | FPGA spectrum analyzer                                        |

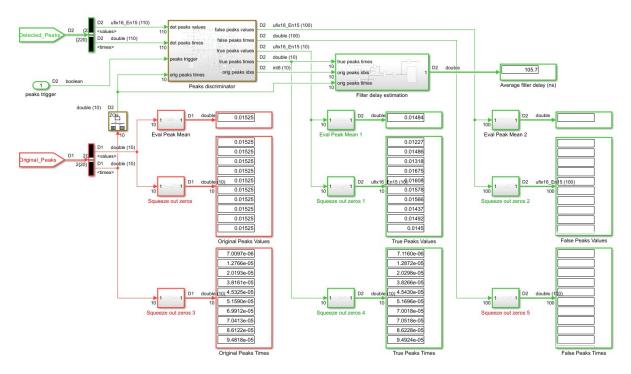

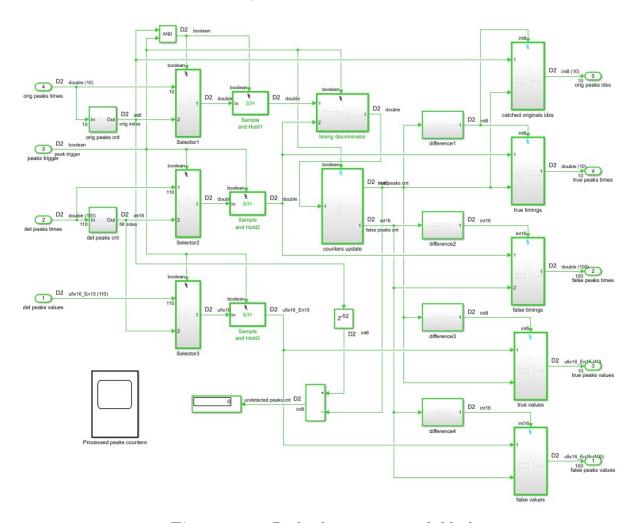

| 3.21 | Peaks Statistics block                                        |

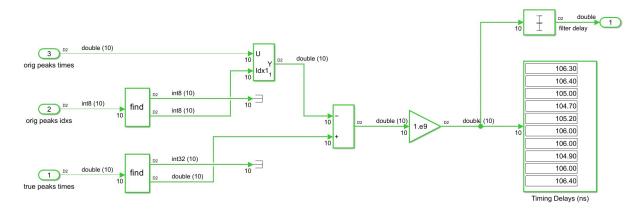

| 3.22 | Filter delay estimation sub-block                             |

| 3.23 | Peaks discriminator sub-block                                 |

| 3.24 | Peaks Statistic block - time analysis                         |

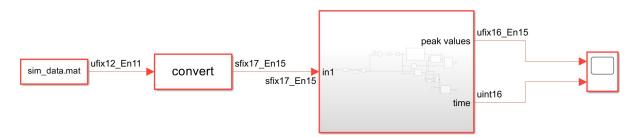

| 4.1  | Top level model-HDL Coder compatible                          |

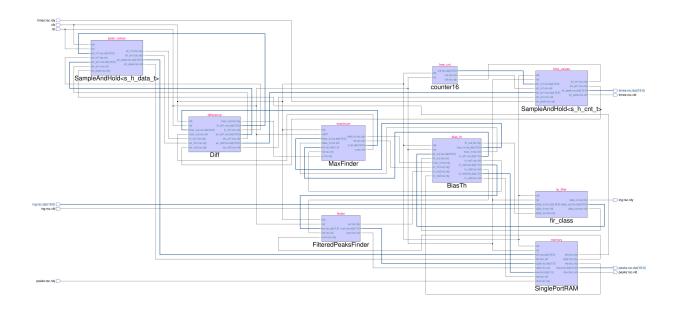

| 4.2  | FPGA sub-blocks                                               |

| 4.3  | Simulink simulation                                           |

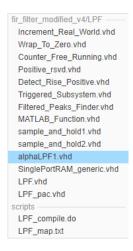

| 4.4  | Workflow Advisor Steps                                        |

| 4.5  | HDL Coder generated files                                     |

| 4.6  | Generated model                                               |

| 4.7  | Code Generation Report                                        |

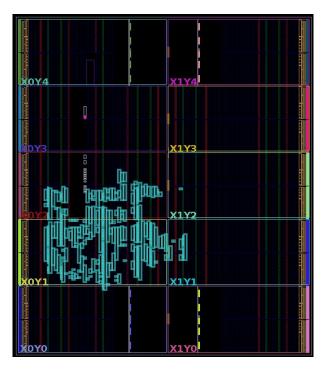

| 4.8  | Placement view of HDL Coder project on the FPGA               |

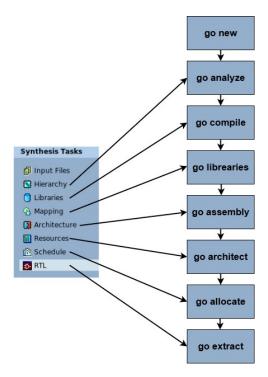

| 5.1  | Catapult HLS flow                                             |

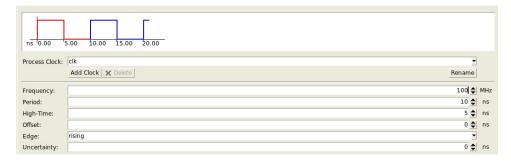

| 5.2  | Mapping-Clock frequency                                       |

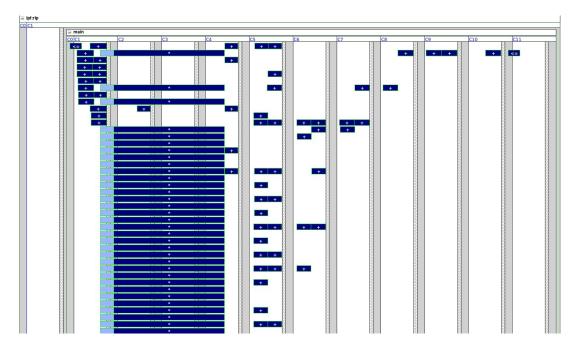

| 5.3  | Scheduling view                                               |

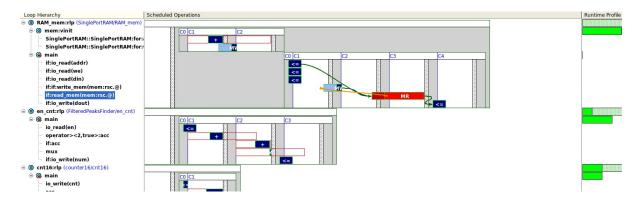

| 5.4  | Example of Table view                                         |

| 5.5  | Catapult HLS                                                  |

| 5.6  | Catapult HLS Flow-Libraries                                   |

| 5.7  | Catapult HLS Flow-Architecture                                |

| 5.8  | Catapult HLS Flow-Schedule                                    |

| 5.9  | Catapult HLS Flow-RTL                                         |

| 5.10 | MAC and SHIFT loops                                           |

| 5.11 | Optimized implementation-Scheduling                           |

| 5.12 | Optimized implementation-RTL                                  |

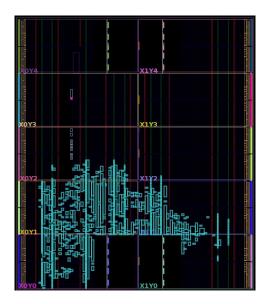

| 5.13 | Placement view of the initial implementation on the FPGA      |

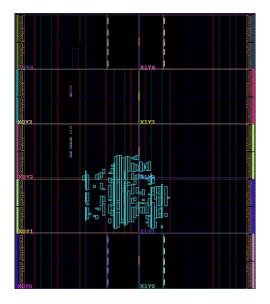

| 5.14 | Placement view of the optimized implementation on the FPGA 76 |

# List of Tables

| 3.1 | FIR vs. IIR equations                                                | 38 |

|-----|----------------------------------------------------------------------|----|

| 4.1 | QuestaSim Simulation results                                         | 54 |

| 4.2 | HDL Coder-FPGA implementation results in Vivado                      | 56 |

| 5.1 | Initial implementation-simulation results                            | 74 |

| 5.2 | Optimized implementation-simulation results                          | 75 |

| 5.3 | Catapult HLS-FPGA initial implementation results in Vivado           | 76 |

| 5.4 | Catapult HLS-FPGA optimized implementation results in Vivado         | 77 |

| 6.1 | Comparison at $240MHz$ between HDL Coder and Catapult HLS (both      |    |

|     | implementation with different Percentage Sharing Allocation)         | 79 |

| 6.2 | Comparison between initial implementations at 240MHz and 260MHz with |    |

|     | different Percentage Sharing Allocation                              | 81 |

| 6.3 | Comparison between optimized implementations at 240MHz and 260MHz    |    |

|     | with different Percentage Sharing Allocation                         | 82 |

| 6.4 | Latency optimizations                                                | 83 |

# Acronyms

HLS High-Level Synthesis.

FPGA Field-Programmable Gate Array.

MUX Multiplexer.

DSP Digital Signal Processor.

VHDL VHSIC Hardware Description Language.

HLL High-Level Language.

RTL Register-Transfer Level.

SoC System-on-Chip.

ADC Analog-To-Digital Converter.

PSU Power Supply Unit.

SNR Signal-To-Noise Ratio.

FIR Finite Impulse Response.

RMS Root-Mean-Square.

LUT Look-Up Table.

S&H Sample-And-Hold.

LSB Least-Significant Bit.

IIR Infinite Impulse Response.

WNS Worst Negative Slack.

WHS Worst Hold Slack.

WPWS Worst Pulse Width Slack.

BRAM Block Random Array Memory.

# Chapter 1

## Introduction

#### 1.1 Context

In the last years, ground station interrogation and laser-optical warning systems have been evolving, trying to obtain faster, more autonomous, and more secure airborne platforms. This phenomenon has led to a stronger focus on high-performance signal processing algorithms and architectures. In particular, the detection and analysis of impulsive signals (such as radar pulses or navigation aids) is a critical task in many on-board systems, such as military helicopters, where low-latency, real-time performance and hardware efficiency are very important in order to instantly perceive and react to the environment obstacles.

Impulsive signals in these contexts have typically low amplitude and they are characterized by a short duration in time, in the order of nanoseconds, and embedded in noisy environments. For this reason their identification requires filtering, integration, thresholding, and sometimes time-frequency or statistical processing with high precision, in order to recognize the obstacle and recalculate a safer flight path. Traditional software-based approaches may have some problems to meet the rigorous real-time constraints imposed by airborne environments, in particular when multiple channels inputs are involved.

Figure 1.1: Target Pulse Identification within High-Noise Signals

As a result to meet these challenges, programmable logic devices, in particular Field-Programmable Gate Array (FPGA [2]), are increasingly adopted due to their ability to parallelize different operations, minimize latency, and maintain real-time deterministic behavior. However, implementing this kind of algorithms on FPGA is not only such an easy task: it involves not only theoretical development and numerical validation, but also architectural consciousness of how algorithms are translated into logic blocks like MUXs (Multiplexers [3]), DSPs (Digital Signal Processors [4]), flip-flops and memory structures.

Until now many functions have been managed in an analog way but, due to the high number of operations that must be integrated in the system, a digital way is now mandatory to increase efficiency, reliability and integration. Nowadays digital design generally follows a traditional methodology based on manual HDL coding. In this approach, algorithms have been translated into low level hardware description languages such as VHSIC Hardware Description Language (VHDL [5]) or Verilog, that could be a high-time consuming process due to the increasing complexity of these algorithms.

In some cases tools like Simulink HDL Coder have been employed to partially automate and speed-up this process: algorithms are described by using High-Level Language (HLL [6]), but they still require some modeling specifics that must be compatible with the hardware synthesis. For this reason HLS is arising as an efficient alternative methodology that allows to obtain a Register-Transfer Level (RTL [7]) description starting from the behavioral description of the algorithm. HLS gives the possibility to the designer to describe the algorithm in HLL such as C++ or System C, and then automatically generate RTL reducing the effort required for the design and the verification.

### 1.2 High-Level Synthesis Definition and History

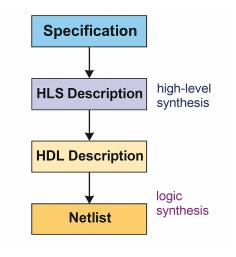

High-Level Synthesis (HLS), also known as behavioral synthesis or algorithmic synthesis, refers to the ability to generate high quality and synthesizable RTL implementations starting from an abstract. Unlike traditional design methods, HLS allows designers to realize the functionalities using HLL, like C++ or SystemC, from which the synthesis tool generates an optimized hardware architecture that meets specific design constraints such as latency, throughput, power, and area consumption.

Nowadays, most of the designs start with the specification and with an executable model that describes the behavior of the system, without any information regarding hardware details. After that, the model must be optimized and a suitable architecture must be chosen in order to realize a physical implementation of the described algorithm. But this challenge is not so easy and the problem is amplified in larger designs, due to the fact that it is more complex to realize the system without any error. This is precisely where HLS proves valuable: it ensures an error-free design flow from high-level

Figure 1.2: Design Flow

specifications, significantly reducing development time and effort.

By decoupling behavior from structure, HLS tools can explore different architectural implementations in an automatic way through design space exploration, enabling rapid prototyping, shorter verification and higher productivity. The process of HLS involves parsing a behavioral input specification, scheduling operations over clock cycles, allocating and binding operations to specific hardware resources and finally generating an RTL description that meets timing and resource constraints defined by the designer.

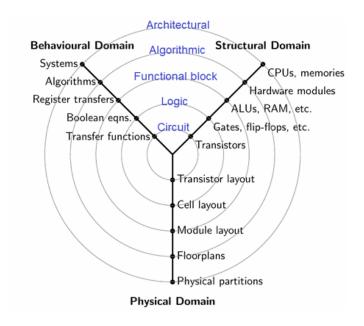

The shift of the focus of the engineer, so from the low-level control to the functionality of the algorithm, is well-represented within the Gajski-Kuhn Y-chart (Figure 1.3) made by Robert Walker and Donald Thomas in 1985 [1].

This graph models hardware design as three orthogonal views (behavioral, structural, and physical) each with increasing levels of refinement. HLS operates within the behavioral domain at higher abstraction levels, providing a structured pathway to transition into the structural domain through automatic generation of RTL. The refinement process envisioned by the Y-chart, starting from an abstract behavioral model and gradually introducing implementation details, is precisely the workflow enabled by HLS tools. The output of HLS can then undergo logic synthesis and physical design, completing the traversal of the Y-chart toward the transistor-level realization of the system.

Historically, HLS was tied to research studies in the '70s and early '80s, when the higher abstraction level was already called for by researchers and industries as an early response to increasing system complexity. The first pioneering research studies explored the mapping of behavioral specifications onto register-level hardware through structured transformations and scheduling algorithms. Experts on HLS history have recognized different generations of HLS tool [2]: the first genuine generation of HLS, between the 1980s and early 1990s, was still dominated by academia. Pioneering research by researchers like Dan Gajski, Giovanni De Micheli, and Pierre Paulin introduced seminal notions e.g.,

Figure 1.3: Gajski-Kuhn Y-chart

force-directed scheduling and architecture exploration. Although they produced many classic papers and initial tools, typically DSP domains, this generation did not achieve any industrial impact. There were many reasons: the tools took non-standard, applicationspecific input languages; the tools produced hardware results with inconsistent quality; and they were too targeted for dataflow problems, which were not on the agenda at that instant of ASIC designers, being focused on control logic and system integration. The second generation, the mid-1990s and early 2000s, is where the first serious commercial initiatives for HLS were made by big EDA firms Synopsys, Cadence, and Mentor Graphics. Some of the tools created with the goal of providing behavioral synthesis relevant for actual designs are Synopsys's Behavioral Compiler, Cadence's Visual Architect, and Mentor's Monet tool. The second generation commercially failed. These tools had the hypothesis that RTL designers would automatically migrate to HLS, which never happened. Further, inputs as behavioral HDLs restricted usage to a small number of designers. The tools also required synthesis right down to gate level without being part of the then-prevailing RTL synthesis flows at any point, rendering the workflow inefficient. The designs thus produced tough to verify, performed erratically, and were less than ideal for control-intensive logic. These, with marketing hysteria and user unfamiliarity, caused second-generation HLS tools to fail. Third generation of HLS, starting about the early 2000s, however, was far more successful and prevalent. Among the differences in features of this generation is the utilization of high-level programming languages with which computer and algorithmic C, C++, SystemC, and MATLAB. Catapult C from Mentor Graphics, Forte's Cynthesizer, Bluespec, and Cadence's C-to-Silicon compiler for application domains like DSP, multimedia, and image processing, which are dataflow-based and algorithmic in nature, belong to this category. These tools bypassed the flaws of

their forebears by targeting algorithm designers rather, enabling faster exploration of design alternatives, and yielding better quality of outcomes. Increased uses of FPGAs in hardware prototyping also played a big role, since HLS tools were superior in rapidly translating algorithms into FPGA fabrics, where fitting and timing are less important than in ASIC design. Therefore, HLS was a viable choice for specific classes of designs, especially in wireless communications, multimedia, and signal processing.

Looking ahead, there is an anticipated fourth generation of HLS. This new generation would combine the virtues of present tools by allowing synthesis across multiple domains, control- and datapath-intensive designs, and even integration with heterogeneous targets such as ASICs, FPGAs, and configurable processors. The ultimate vision for this generation is truly system-level design exploration and optimization—software that allows designers to compare trade-offs among architectures, domains, and abstraction levels effortlessly and automatically. While this vision is still a fantasy, the progress already made provides a solid foundation for making the long-awaited promise of high-level synthesis a reality: to significantly improve design productivity while retaining or improving implementation efficiency.

HLS has become a revolutionary methodology, specifically in situations where rapid prototyping, design reuse, and system-level optimization are critical. It offers a tractable path toward dealing with the growing complexity of today's hardware systems at respectable levels of design effort, correctness, and performance. As the digital design environment keeps on evolving, HLS will find itself at the center of system-on-chip (SoC [8]) and FPGA-based design approaches more and more.

### 1.3 Objectives

This work addresses the design, the simulation, and hardware implementation of a pulse detection algorithm for the recognition of impulsive signals. Two different hardware implementation flows are explored in parallel in order to compare their efficiency and effectiveness for avionic applications:

- Simulink-based flow: starting from a high-level Simulink-based model, it is possible to generate in an automatic way the HDL code thanks to Simulink HDL Coder tool. This flow has been used for many years and it exploits the model-based design principles to allow the transition from the high-level algorithm to the hardware implementation, for an easier prototyping and verification;

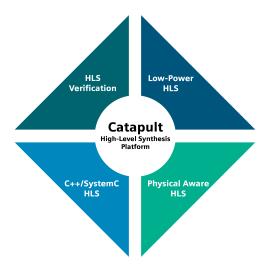

- HLS flow: this approach exploits Siemens EDA Catapult HLS tool, which is able to generate the hardware implementation starting from the C++ description of the algorithm. This strategy allows more software-centric design methodology, improving flexibility and control on hardware optimizations in terms of resources and performances.

The main objective of the thesis is to evaluate and compare these two design flows in terms of:

- **Design effort:** It includes the time needed to develop, debug, and optimize the algorithm implementation for each flow. It covers the time needed to learn how to use the tools, the development of the algorithm and its translation into hardware, its verification and its optimization in order to achieve the wanted results;

- Hardware metrics: Analysis of key hardware parameters that are resource utilization (how many logic blocks are used), latency (the time delay between the first input and the first valid output generated), working clock frequency and power consumption (so how much static and dynamic power the hardware consumes).

### 1.4 Methodology and Thesis Organization

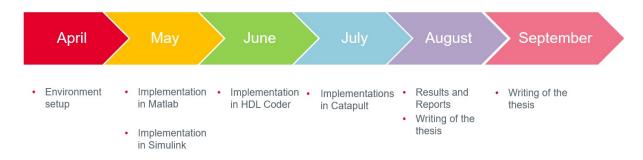

In order to achieve the objectives described in the previous section, the work has been organized according to a structured and sequential methodology, that can be observed in Figure 1.4. This kind of approach has allowed a progressive consolidation of knowledge, facilitated early-stage validation and supporting a mapping between high-level description and low-level implementations. The key activities that have been planned are summarized below, with the corresponding chapter in which they are discussed in detail:

- Environment setup and tools familiarization: this initial phase involved the study and the familiarization with the new tools used throughout the thesis (Simulink HDL Coder and Catapult HLS) (Chapter 4 and 5)

- Implementation in MATLAB: during this phase, the algorithm has been described starting from the real data acquired by the framework and the parameters and the setup for the Simulink model of the pulse detection algorithm were developed and tested using MATLAB scripts, enabling parameter tuning and mathematical correctness (Chapter 2)

Figure 1.4: Tasks Timeline

- Implementation in Simulink: a modular Simulink model of the framework representing the arrival of the pulses and their elaboration has been developed, preparing it for HDL generation and system-level simulation (Chapter 3)

- Implementation in HDL Coder: the relevant part was converted into HDL code using Simulink HDL Coder. The generated code was then optimized, synthesized and evaluated within the Vivado design suite, targeting FPGA-based deployment (Chapter 4)

- Implementation in Catapult: the algorithm and the design blocks were described by using C++ code and then thanks to this tool it was possible to obtain the RTL and the synthesizable code for Vivado (Chapter 5)

- Results and Reports: a final comparison between the two flows has been performed in order to see the differences obtained in terms of hardware implementation and time effort (Chapter 6)

# Chapter 2

# Implementation in MATLAB

### 2.1 Algorithm description

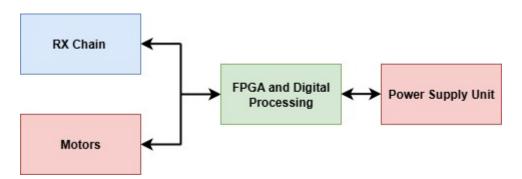

The description of a pulse detection algorithm with all its specifications has been the first key task of this work. The system operates by emitting short-time duration laser pulses in order to scan the surrounding environment and then analyzing the returned echoes to be able to identify a possible dangerous obstacle and to reconstruct the image of it. For this reason the pulse detection must be very accurate to ensure the safety of flight operations. The detection of the signal that is reflected by the target object is initially performed by an analog chain that is composed by several stages. First of all the optical signal is converted into an electronic one via an avalanche photodiode, that is know in the optoelectronics world for its high sensitivity and fast response. After that, the second step involves a signal pre-amplification in order to obtain a suitable amplitude and finally a threshold comparison, which is a function of the round-trip-delay of the transmitted pulse.

Figure 2.1: Block Diagram of the system

Once that the analog signal is acquired in the proper way, it is digitalized by an analog-to-digital converter (ADC [9]) and the resulting samples are sent to a FPGA which performs further processing. If the comparison is successful, the main information related to the detected echo is estimated: range (and so the distance from the sensor), angular coordinates (azimuth and elevation) with respect to the local reference frame and some

qualitative attributes that are related to the nature of the reflecting surface. The range is evaluated based on the time delay between the transmission and the reception of the pulse, while the angular coordinates are determined by the angular orientation of the scanner at the acquisition time. The geometry of the is evaluated from the amplitude of the returned echo.

In the overall chain of processing of the opto-electronic signal outlined above, some several disturbances occur in the analog acquisition chain: these include electromagnetic interferences generated by the motors that drive the laser beam deflection in the predetermined area and the switching noise due to the power supply unit (PSU [10]) that provides all the necessary power to allow to the device to operate properly. Although the shielding adopted to mitigate these disturbances, they are not completely eliminated and this affects the signal-to-noise ratio (SNR [11]) of the system. Moreover, the sensitivity of the device is also affected, that is the ability to detect the low-amplitude echoes that are typically related to this obstacles (for example power lines, cables) or those that are farther away from the framework (search range).

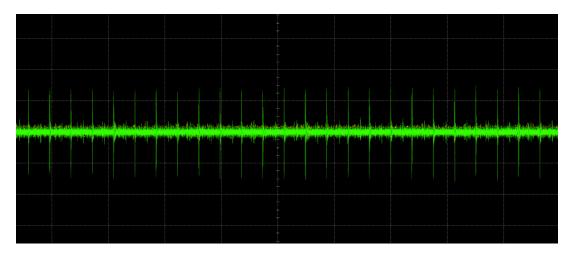

Figure 2.2: Measured Interferences

First of all, a recording of the signal without firing the laser pulse (but with the scanner in action) has been used to carry out the model in order to obtain a more realistic solution (Figure 2.2). The use of differential signaling provides only partial mitigation of the electromagnetic disturbances that affect the analog signal chain. While this approach does not reduce the amplitude of the noise, it introduces symmetry because the common mode noise appears equally on both lines and are canceled out when computing the difference between A and B. The result is an effective signal swing of about 2A (assuming A and B are perfectly complementary), which remains stable over the time, even if there are external interferences.

However, the system output shows that disturbances are still present and superimposed on the background noise of the system. The amplitude of these residual disturbances is typically in the order of 30 mV peak-to-peak. This is a critical figure, as it directly

affects the reliability of the threshold detection mechanism. In fact, for any detection threshold set at or below this level, the system becomes highly susceptible to generating false positives, i.e. spurious detections not associated with actual reflected echoes but rather with transient noise peaks or oscillatory artifacts introduced by the interference.

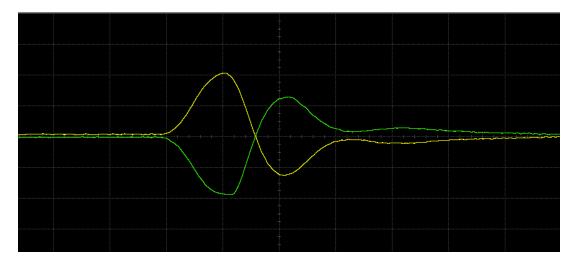

Moreover, a recording of the pulse received after the shot, with the scanner inactive, is shown in Figure 2.3.

Figure 2.3: Measured Pulse

To address this challenge a robust signal conditioning strategy is required. One possible solution to the problem could be the insertion of an appropriate filtering stage before the threshold comparison, which could further reduce or eliminate such disturbances. This solution implies two possible implementation alternatives: the first one is to insert an analog filter at the pre-amplification stage, while the second alternative is to perform the filtering directly in the digital domain downstream of the ADC. The latter approach also implies the migration of both the filtering and threshold comparison operations into the digital domain, within the FPGA itself.

This first part of the work explores a possible implementation of the second approach. The proposed digital signal processing involves a finite impulse response (FIR [12]) filter to eliminate noise and enhance valid echoes signatures. After that, there is a comparison between the signal and the threshold in order to recognize the returned echoes from some false peaks due to noise. This architecture allows to improve the detection of weak pulses and provides great flexibility and reconfigurability.

#### 2.2 Peaks and Noise Characterization

The simulator developed to evaluate the behavior of the whole signal acquisition and processing chain, from emission of the laser pulses to digital threshold detection performed

within the FPGA, was implemented in the MATLAB/Simulink environment. The simulation environment enables the architectural design and functional validity of the processing pipeline to be verified early for various operating conditions. The simulator is divided into two components: a couple of MATLAB scripts and an overall Simulink model of the signal processing chain.

The MATLAB scripts manage the definition and establishment of the simulation parameters. In particular, the scripts allow to compute the input vectors and reference values necessary for simulation initialization and generate the look-up tables that guide threshold decisions in the digital logic. Before Simulink simulation is executed, the MATLAB scripts must be executed in order to initialize all data structures and configuration parameters appropriately.

The first MATLAB script (Calcolo\_Vrms\_noise\_e\_segnale\_ver01.m, see Appendix A) is dedicated to the implementation of a detailed radiometric model, which plays a fundamental role in characterizing the expected behavior of the received signal under varying environmental and system conditions.

```

q = 1.602176634e-19;

% carica elettrone

detector_BW = 50e6;

% [Hz] detector electrical bandwidth

M_adp_gain = 9.244;

% 9.168; ADP gain, from interpolated curve

Rapd = 1.087;

% 1.09; [A/W] detector responsivity

keff = 0.45;

Tz = 34e3;

% [Ohm] detector resistance

Gain = 3.5;

% preAmp voltage Gain

eta_rx_bw = 0.4723;

% 0.45972; % Optical bandwith vs Receiver bandwith

% Band penalty due to the filter effect of the receiver

10 Pb_det_in = 2.724e-9;

% [W] con sfondo 50 W/(m2 sr um) Potenza di backgroud a

valle del filtro IF

11 Pb = Pb_det_in;

% Potenza di backgroud

12 \text{ Pb_ase} = 2.942e-10;

% 0.736e-9; % [W] Received power into RX/TX path due to

13 Ids = 3.3e-9;

% 9.702e-12; % [A] Ids := IDS(Is0) = dark due to surface

14 Idb = 3.3e-9;

% 3.465e-9; % [A] Idb := IDB(Is0) = dark due to bulk

15 in_LLAM = 0.6e-12;

% [A] in_LLAM = 0.6 pA / sqrt(Hz);

16 R = Rapd;

% responsivity

17 \mid M = M_adp_gain;

% ADP gain

18 Deltaf = detector_BW;

% detector electrical bandwidth

19 F = keff*M+(1-keff)*(2-1/M);

% Noise figure

```

More specifically, the model uses a number of significant parameters that govern the energy of the back reflection as it can be seen in the code lines above. They include:

- inherent characteristics of the outgoing pulse, like temporal profile and peak intensity;

- characteristics of the reflecting target or obstacle, i.e., its reflectivity, surface geometry, material structure, and relative position to the source;

- the characteristics of the medium of propagation, such as the attenuation effects like absorption by water vapor and particles, solar background noise, and potential optical turbulence.

These atmospheric contributions are particularly significant when measuring degradation of the signal over longer distances or for conditions of low-visibility environments.

#### 2.2.1 Effective signal power on detector

The script includes the factors shown above to compute the resulting amplitude of the received electrical pulse and the associated noise level, typically in terms of root-mean-square (RMS [13]) voltage. Regarding the evaluation of the effective signal power that arrives on the detector, that in the script is denoted as  $P_s\_det\_in$ , not all this power is effectively transformed into photocurrent in the detector. Losses and bandwidth restrictions of several types reduce the amount of the received signal that can be utilized.

```

Ps_det_in(k) = x; % vector containing the received signal power

Ps = Ps_det_in(k) * eta_rx_bw; % [W] Effective power on detector

In_signal = R * Ps; % [W] Photocurrent

```

As can be observed, the effective power received on the detector is evaluated as:

$$P_s = Ps\_det\_in \cdot \eta_{rx\ bw} \tag{2.1}$$

where the term  $\eta_{rx\_bw}$  is a coefficient representing the overall optical efficiency that includes:

- optical coupling losses;

- imperfect responsivity across the signal spectrum;

- filter and bandwidth restrictions.

This effective power is then used to compute the signal photocurrent

$$I_{n\_signal} = R \cdot P_s \tag{2.2}$$

where R is the avalanche photodiode's respositivity.

#### 2.2.2 Noise modeling in the optical receiver

The optical signal received is perturbed by several sources of noise, each one originating from distinct physical mechanisms. In order to evaluate the system's performance in terms of the SNR, it is essential to model all the most significant noise contributions. The equations used in this work are well-established equations in the photonics literature and represent the main processes responsible for degrading detection capability. The considered noise terms are:

• Shot noise: Shot noise is a fundamental type of noise that originates from the random nature of discrete charge transport events occurring independently of one another [3]. Shot noise is encountered especially in electron emission from a thermionic cathode or photocathode, carrier transport in a pn junction or current conduction in semiconductor devices, like transistors. Moreover, it is associated with the energy transitions in semiconductors such as the electron-hole pairs generation and recombination and photon emission processes in lasers. Due to their stochastic nature, the resulting current contains variability. These can be quantified in terms of the RMS value of noise current and are proportional to the mean direct current of the underlying process. The RMS value of shot noise current is given by the following formula:

$$\sqrt{\overline{i_s^2}} = \sqrt{2 \cdot q \cdot I_{dc} \cdot B} \tag{2.3}$$

where q is the electron charge,  $I_{dc}$  is the average DC current and B is the electrical bandwidth in Hz. In the case of this work, the equation to evaluate the shot noise due to the signal becomes:

```

insh_signal = sqrt(2 * q * In_signal * M^2 * F * Deltaf);

```

The signal photocurrent,  $In\_signal$ , is subject to quantum fluctuations due to the fact that photo-detection is a discrete process. For an APD, the photocurrent is further amplified by the avalanche gain M, with the multiplication process introducing statistical fluctuations that are accounted for by the excess noise factor F. Shot noise is a fundamental limit to optical detection. Under weak signal power, the photocurrent generated by the signal is low and the unpredictability of photon arrivals is the dominant noise source.

Moreover, this noise contribution must be evaluated also for the background power and the dark current:

```

insh_dark = sqrt(2 * q * (Ids + Idb * M^2 * F) * Deltaf);

```

where  $I_{ds}$   $I_{db}$  are the dark current contributions due to surface and bulk, respectively. And

```

insh_back = sqrt(2 * q * (In_background * M^2 * F) * Deltaf);

```

where  $I_n$ \_background is the current evaluated from the background power  $P_b$  as:

```

In_background = R * Pb;

```

• Johnson-Nyquist and Flicker: Johnson-Nyquist noise, also known as thermal noise, is a fundamental physical phenomenon that is due to random thermal motion of electrons within a resistor, as stated in [3]. This phenomenon is applied at the electrical terminals of the passive components, even in the absence of any applied signal or current flow. Thermal noise is present in all resistive components and is unavoidable in electronic circuits. The general equation of thermal noise is the following one:

$$\sqrt{\overline{i_j^2}} = \sqrt{\frac{4 \cdot k \cdot T \cdot B}{R_L}} \tag{2.4}$$

where k is Boltzmann's constant, T is the absolute temperature,  $R_L$  is the resistance value in ohm and B is the electrical bandwidth.

Regarding the Flicker noise, also known as 1/f noise, is a low-frequency noise component that becomes significant as the frequency is decreased. It originates mainly from semiconductor material and interface defects, like traps in MOSFET gate oxides or surface roughness [4]. Flicker noise is not white like thermal noise: its power spectral density increases as the frequency decreases, and it typically dominates the total noise spectrum at frequencies below a few kilohertz. The equation is the following one:

$$I_{nf}^2 = \frac{2 \cdot q \cdot I_{dc} \cdot f_c^m \cdot B}{f} \tag{2.5}$$

where  $f_c^m$  is the comer frequency, where m is between 1 and 2, and f is the frequency of interest.

Here the two components are summed toghether and the total noise is given by:

```

in_tia = in_LLAM * sqrt(Deltaf);

```

where in  $in_{LLAM}$  is a parameter that considers the two previous noise contributions.

• Internal background: This term explains the noise due to the internal background optical power within the system falling on the photodetector. In a real-world optical system, not every incoming light at the detector can be attributed to the desired signal. There is some residual background light present within the receiver itself due to internal reflections, non-ideal optical isolation, spurious coupling among the optical components, or other non-ideal effects of the system design. Although such background light is constant or gradually varying with time, it also generates a photocurrent in the detector. It is evaluated as:

```

insh_stray = sqrt(2 * q * (R * Pb_ase) * (M^2 * F) * Deltaf);

```

where  $P_{b\_ASE}$  is the internal background power.

All these contributions must be summed all together in order to evaluate the total noise current (in RMS value):

```

ni_tot = sqrt(insh_signal^2+insh_dark^2+insh_back^2+in_tia^2+insh_stray^2);

```

After the evaluation of the currents, the voltages of both the wanted signal and the noise are evaluated as:

```

Vnoise(k) = Gain * ni_tot * 1 * Tz; % voltage total noise

Vsignal(k) = Gain * (Ps * Rapd) * M * Tz; % voltage signal level

```

where Gain is the voltage gain and Tz is the detector impedance evaluated in Ohm. Moreover, the SNR, in linear and in dB, of each index is evaluated as the ratio of the signal and noise voltages:

```

SNR_lin(k) = Vsignal(k)/Vnoise(k);

SNR_db(k) = 20*log10(Vsignal(k)/Vnoise(k));

```

The output of the script is a look-up table (LUT [14]), which maps a series of operating points, described by output voltages between 5 mV and 3 V, to their respective pulse amplitudes, noise RMS levels and calculated SNRs. In fact a vector of discrete values of output voltages is created, converted in volts to maintain unit consistency, has been created.

The distribution of these reference values is intentionally more compact at lower voltage amplitudes, which is the region of primary interest for the analysis; this arrangement ensures higher precision in fitting simulated data to the desired levels in the most critical operating region. The number of reference levels was determined  $(Vout\_nr)$ , and for each level, the algorithm computed the absolute difference between the simulated output voltage vector (Vsignal) and the reference value. The index of the minimum difference was stored in idx, thereby determining the point in the simulated signal that best matches each given voltage level. This operation effectively maps the continuous simulated signal into discrete output levels for performance evaluation under quantized measurement constraints.

```

Vout_nr = length(Vout);

for i = 1:Vout_nr

delta = abs(Vsignal - Vout(i));

minValue = min(delta);

idx(i) = find(delta == minValue);

end

```

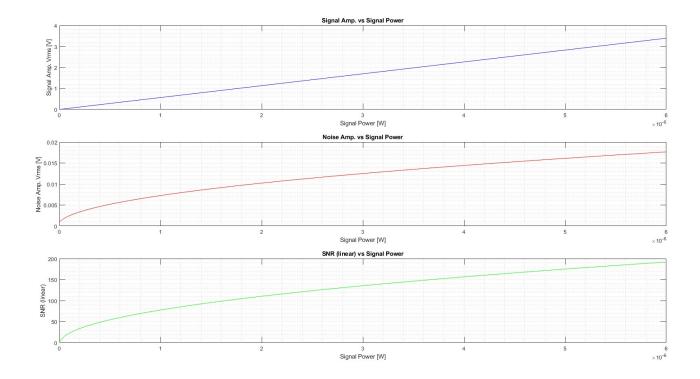

The output of the MATLAB scripts can be observed in Figure 2.4 and 2.5.

Figure 2.4: Relationship with Signal Power

The previous subplots contains the trends of signal and noise amplitudes and the linear SNR with respect to the incident signal power in the detector  $P_S\_det\_in$ . As can be expected, the signal amplitude has a linear slope with respect to optical power due to the fact that all the contributions that gives the value of the slope (responsivity, gains and so on) are linear too. Meanwhile, the noise amplitude grows as the square-root with the signal power due to the fact that it embeds all the contributions described before that grows as  $\propto \sqrt{I}$ . For this reason, the SNR follows the same trend of the noise amplitude, in fact in the low-power regime, SNR improves rapidly with increasing power because the signal grows linearly while the noise is near its floor. For higher power values the SNR continues to increase but with a lower slope due to the noise amplitude ( $\propto \sqrt{P}$ ).

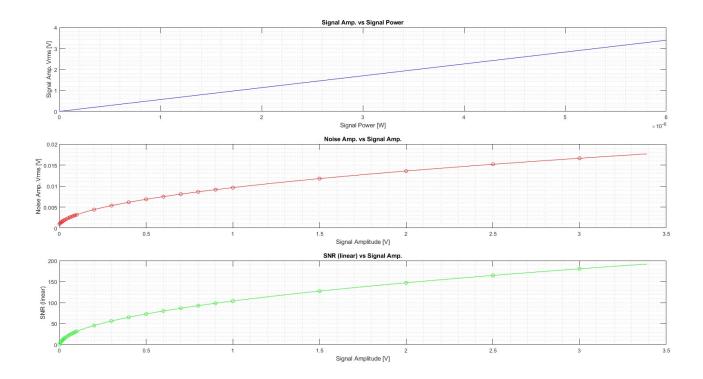

Figure 2.5: Working points

In the second Figure, there is again the same subplot of the first one (Signal amplitude vs. Signal power) and then there are the subplots of more interest that are the noise amplitude and the SNR values evaluated with respect to the signal amplitude.

- The red curve shows how total noise voltage varies with signal level. Red markers are the operating points where Vsignal is closest to each target maximum output level in Vout. This makes it easy to read off the noise level for the desired outputs.

- The last panel directly shows how SNR changes with output signal level. The green markers are the SNR achieved at the discrete output levels Vout. The arrays Vout and idx give a mapping from desired discrete output levels to the closest achievable points in the simulated signal.

The overlaid markers in Figure 2.5 enable to read off noise and SNR at exactly those operating points, which is valuable for:

- checking conformity to instrument/ADC ranges

- selecting operating points with good SNR

- measuring performance accuracy where the Vout grid is finer at low amplitudes (range of interest), thus increasing accuracy of reported metrics in the most critical range.

#### 2.3 Composite Signal Generation

This second script is executed immediately after the first one and represents a critical step in the simulation process: it translates the analytical results of levels of signal and noise previously calculated into a waveform within the real-time domain. Whereas the first script produced static plots of Vsignal, Vnoise and SNR for a large range of operating points, this step is focused on one specific working point and produces a time series reproducing the exact signal-to-noise ratio for this point. In other words, it takes a point on the SNR curve from the original script and "materializes" it into a waveform consisting of pulses and background noise that can be sampled, filtered, and processed as in the real system.

The script begins by ensuring that the simulation could be the reproducible. A seed value for the random number generator is made constant, such that in every execution, the results are identical, in order to allow comparisons among runs with different parameter settings. The general parameters are then defined: sampling frequencies for both the background and the pulse, total simulation time, number of points to be simulated and the time slot available for each pulse. A small bias term is also set for the background in the real-data mode.

```

seed = 091537;

rng_info = rng(seed,'twister');

RandomSeed = floor(rand*10000);

% general parameters

6

ideal_sig = 0;

% real or ideal data signal generation

Max_false = 100;

% maximum false peaks detectable

Fs_bkg = 10e9;

% background sampling frequency

9

Fs_{imp} = 160e9;

% pulse sampling frequency

Fs = Fs_bkg;

% output sampling frequency

Pr = 10e-6;

% time slot to receive each pulse

time_span = 100e-6;

% total duration of the simulation

Npts = round(time_span*Fs);

14

Bias_bkgd = 0.03;

dt = 1/Fs:

```

Next, the script selects the input files. The background file contains the waveform of the background noise, the other the pulse waveform, both measured from a real simulation of the framework. In particular, there are different files that can be selected but for this work the files used are:

- for the background noise, a file that contains the data collected for  $100\mu s$  with the scanner operating

- for the pulse, a registered echo with a width of 100ns

For real data, a clean time window that is not disturbed by interferences is chosen in the background file in order to determine the RMS value, which is then used for normalizing the waveform. This normalization allows that the background can be scaled precisely to the desired noise amplitude.

```

inp_file_bkgd = 'bkgd_scan_width100us_step10us_fs10ghz.mat';

t1 = 13.6e-6; t2 = 17.1e-6;

inp_file_pls = 'pulse_width100ns_step10ns_fs160ghz.mat';

```

A key step follows: choosing the operating point. The script prompts the user to choose an index corresponding to one of the discrete output voltage levels evaluated in the first script. Based on this index, it chooses the signal amplitude, noise amplitude and the corresponding SNR. This provides absolute consistency between the two scripts: the generated waveform is not random, but matches one of the analytically computed scenarios.

The index that can be selected by the user goes from 2 to 27, in the case of this work, because a index equal to 1 corresponds to a signal amplitude that is equal to 0V, and so it can not be useful to perform a suitable simulation. Moreover, based on the value of the signal amplitude, also a fixed value for the threshold is set as

$$Threshold = \frac{Signal\_Amplitude}{2} \tag{2.6}$$

that can be a reasonable average value for this parameter.

#### 2.3.1 Background noise generation

The generation of background sequences follows. In the ideal mode, so with the *ideal\_sig* parameter equal to 1, a Gaussian white noise sequence is generated and normalized to unit RMS.

```

if ideal_sig

BSequence = wgn(1,Npts,0,1,RandomSeed,'real');

rms_backg = std(BSequence);

BSequence = BSequence./rms_backg;

BackgSequence = [t; BSequence];

save(BackgSeq,'BackgSequence');

bias = 0;

```

In this case, as can be observed in the code lines, the bias is set equal to 0 due to the fact that in an ideal case there is no need to sum a bias to the background noise in order to obtain a correct simulation of the framework. Meanwhile in real-data mode, an existing background waveform from the measured background is loaded, resampled and normalized in the same way. This yields a unit-RMS background "template" that, once multiplied by the chosen noise amplitude, achieves the exact wanted RMS level.

```

else

backg = load(inp_file_bkgd,'data');

if length(backg.data)<Npts, error('La sequenza ha durata minore del tempo di

simulazione predefinito !'); end

BSequence = backg.data(1:round(Fs_bkg/Fs):end);

rms_backg = std(BSequence(round(t1*Fs):round(t2*Fs)));

BSequence = BSequence(1:Npts)./rms_backg;

BackgSequence = [t; BSequence];

save(BackgSeq,'BackgSequence');

bias = Bias_bkgd;

end</pre>

```

#### 2.3.2 Pulse train generation

After that the pulse train is created, which is the sequence of the returned echoes over the simulated time window. Even for the pulse sequence generation, depending on the value of  $ideal\_sig$ , an ideal pulse (Gaussian pulse) or the pulse collected from the real world is used to re-create the sequence for the simulation. Each pulse is placed in a random time position within the time window of  $10\mu s$ , so it ensures that the resulting sequence mimics a real-data acquisition. Then the pulse is normalized with respect to the maximum value of the peak amplitude in order to obtain a unitary peak amplitude.

```

Nimp = round(time_span/Pr);

% Pulse number to be created for the

simulation

PSequence = zeros(1,Npts);

if ideal_sig

4

Sigma = 2.5e-9;

% Gaussian pulse' sigma

tcum = 0:

for n = 1:Nimp

t0 = tcum+rand*Pr;

y = 1/sqrt(2*pi*Sigma^2).*exp(-(t-t0).^2./(2*Sigma^2));

8

PSequence = PSequence + y;

tcum = tcum + Pr;

end

Amp = max(PSequence);

PSequence = PSequence./Amp;

PulseSequence = [t; PSequence];

save(PulseSeq,'PulseSequence');

axis_range = [t(1)*1e6 t(end)*1e6 -0.2 +1.2];

str = sprintf('\nCreati %d impulsi ideali\n', Nimp);

% file degli impulsi di ingresso

inp_pulse = load(inp_file_pls,'data');

if length(inp_pulse.data)>(Pr*Fs_imp), error('La sequenza ha durata maggiore del

periodo predefinito !'); end

pulse = inp_pulse.data(1:round(Fs_imp/Fs):end);

23

npts = length(pulse);

24

dnpts = Npts-npts;

25

[max_pulse, imax] = max(pulse);

26

pulse = cat(2,pulse,zeros(1,dnpts));

tcum = 0;

for n = 1:Nimp

29

n0 = round((tcum+rand*Pr)*Fs);

```

```

PSequence = PSequence+circshift(pulse,n0-imax);

tcum = tcum + Pr;

end

PSequence = PSequence./max_pulse;

PulseSequence = [t; PSequence];

save(PulseSeq,'PulseSequence');

axis_range = [t(1)*1e6 t(end)*1e6 -1 +1.2];

str = sprintf('\nCreati %d impulsi reali\n',Nimp);

end

```

#### 2.3.3 Overall input waveform

The main part of this code is the combination of the waveforms generated before: the background noise is multiplied by the amplitude noise value, the pulse train sequence is multiplied by the pulse amplitude and then they are summed together in order to obtain the total input sequence. This sequence is characterized to have the SNR value defined by the selected working point.

```

TSequence = SignAmp*PSequence+NoiseAmp*BSequence;

```

At the end, the script generates a transcript that shows to the user some information related to the pulse at the corresponding index selected (like peak amplitude, SNR, and so on) as can be observed in Figure 2.6

```

>> Calcolo_Vrms_noise_e_segnale_ver01

>> Par_Sim_GenData

Inserisci un indice della tabella Vsignal-vs-Vnoise nel range [2, 27]

Indice : 4

Creati 10 impulsi reali

OH ampiezza segnale [V] = 0.015248

OH ampiezza rumore di fondo [Vrms] = 0.001522

OH SNR [db] = 20.015722

OH bias [V] = 0.030000

ADC numero di bits = 12

ADC range di tensione [V] = 2.000000

Seme Random = 1046

```

Figure 2.6: MATLAB output transcript

In the case of this work, an index equal to 4 has been selected because it is associated to a pulse amplitude that is almost 16mV, that is the case of interest for the framework. Moreover, a figure is created with three subplots:

- 1. the normalized pulse train sequence

- 2. the normalized background sequence

- 3. the resulting input waveform

Figure 2.7: Input waveforms

The interference is manifested basically as periodic signal distortions riding on the useful signal. Visually, in a time-domain acquisition, such distortions are of the form of spurious high-frequency 'stripes' or oscillatory patterns superimposed upon the underlying noise floor and the actual echo response. This contaminates the SNR, reducing the system's weak echo detecting ability, specifically those due to remote or low-reflectivity targets.

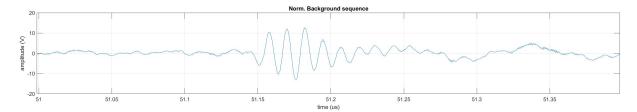

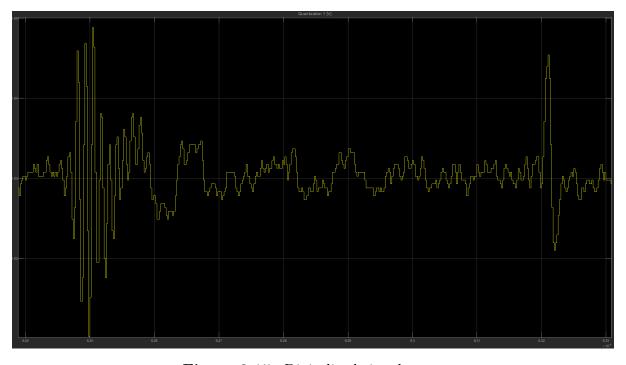

Figure 2.8 shows a zoom of a "line" of the disturbance shown in Figure 2.7; as can be seen, each line is actually a wavelet with a duration of about 100ns and a frequency of about 80MHz; these parameters will be taken into account to define the best filter to use within the FPGA.

Figure 2.8: Interference zoom

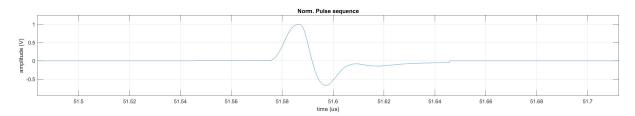

Meanwhile, the absolute pulse generated for the simulation is derived from the collected data, subsampled at 10GHz and normalized to 1; this pulse is shown in Figure 2.9.

Figure 2.9: Pulse zoom

The script also defines the ADC parameters, i.e., the sampling frequency, the number of bits of resolution and the input voltage range. As well as the ADC configuration, the script sets the FPGA filter parameters, such as the FIR filter coefficients, the associated gain, and nominal delay caused by the filter. The parameters are set to emulate the properties of the real digital processing chain and are critical for accurately modeling the system bandwidth and temporal response. These parameters are not yet applied at this stage of the simulation, but they are used as parameters of the Simulink model described in the following chapter.

# Chapter 3

# Implementation in Simulink

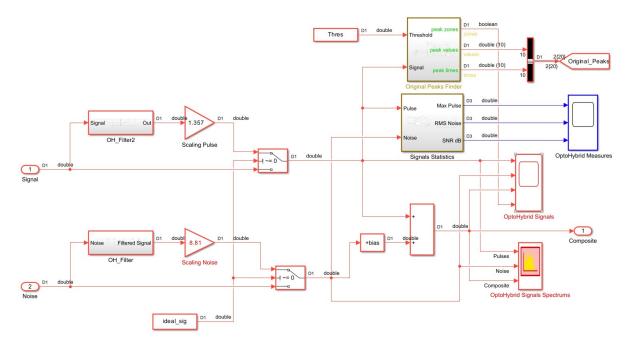

#### 3.1 Model Structure

The Simulink model is used to simulate the behavior of the opto-hybrid component, that represents the analog front-end of the framework, and the subsequent analog to digital conversion. This simulator has been enhanced in order to allow the processing of both ideal data and real recorded data including environmental interferences. Moreover, the model has been extended in order to include the signal filtering and threshold comparison carried out within the FPGA.

This model reproduces the time-domain evolution of the signals starting from the analog front-end, then through the digitization performed by an ADC and the digital logic approximating the behavior of the FPGA hardware. This digital section includes a low-pass filtering stage, a peak detection in order to correctly recognize the wanted echoes and threshold comparison blocks to determine if a returned pulse is a true echo or not. All together, they capture the behavior of the target hardware system at high algorithmic level.

The results provide an insight into the performance of the overall in terms of detection accuracy, false alarm rate and signal integrity. This modeling step is important because it allows to optimize the design before hardware synthesis, allowing design space exploration and the detection of possible architectural bottleneck. Moreover, by repeating simulations, it allows to fix all the parameters and variables, like filter coefficients, threshold value and so on, leading to a more efficient and reliable hardware implementation.

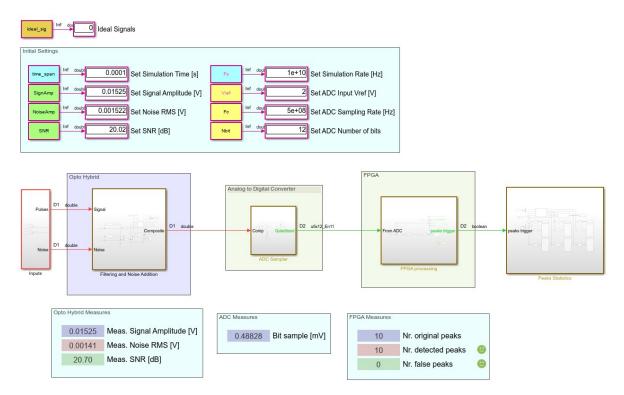

The Simulink model can be run after the execution of the previous MATLAB scripts. In this work, as previous stated, the simulation will be executed by using the working point corresponding to the index equal to 4 and a seed equal to 962247. The overall structure of the model is shown in the following Figure:

Figure 3.1: Simulink model

As can be observed, the model is based on five main macro-blocks that are modeled at high level in an algorithmic way to allow flexible testing and tuning of the parameters. The main five blocks are:

- Input block: this block is responsible to feed the processing chain with the pulse and background sequences evaluated in the MATLAB scripts

- Opto Hybrid block: this block behaves as the opto-electronic front-end component that receives the optical input signal and that converts it into an electrical one that is suitable for the following processing chain. It has to shape correctly the signal to maintain signal integrity before the digitization

- Analog To Digital Converter block: it is responsible to translate the continuous signal (both in time and amplitude) coming from the previous block into a discrete and quantized signal that is suitable for the processing that is performed in the following block

- **FPGA** block: This block performs the digital signal processing performed within the FPGA. The block implements peak detection algorithms to recognize possible returned pulses, which are those peaks that exceed a predefined detection threshold. This threshold can be tuned to optimize the detection probability and false alarm rate

- Peaks Statistics block: This block performs a post-processing analysis of the results. Each peak that is detected is classified as either a true pulse (correct identification of a

real pulse) or a false pulse (false detection due to noise or interference). Additionally, the block identifies if there are some missed detections, i.e. real pulses that were present in the input waveform but that are not detected by the digital chain

All these blocks will be described in detail in this chapter. Moreover, as can be observed in Figure 3.1, there are some displays above the blocks that show how some key parameters have been set in the scripts and that are useful to understand how the simulation will be performed (like the value of ideal\_sig, simulation time, amplitudes corresponding to the selected working point, the number of bits of the ADC and so on).

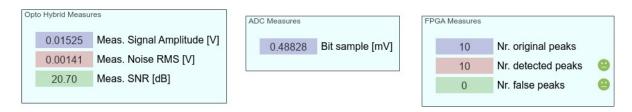

Figure 3.2: Results displays

Meanwhile in the bottom part of the Figure, there are other three displays that show to the user

- the measured values of peak amplitude, noise amplitude and respective SNR in the Opto Hybrid block, in order to evaluate how the input sequence is processed by this component

- the quantization step that comes from the ADC block

- the number of peaks that are correctly recognized and the false detected peaks

These displays are useful to understand immediately the performance of the components and the capability of the system to detect properly the peaks that must be recognized and if there are some false detections.

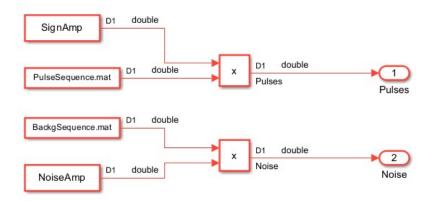

### 3.1.1 Inputs Block

The internal structure of the Inputs block, shown in Figure 3.3, represents the beginning of the overall processing chain of the framework and it is the responsible for constructing the two sequences of the input waveform: the pulse and the noise (background and interferences) sequences. Both these contributions are generated in parallel starting from the data that the MATLAB scripts have produced.

As it can be observed, the two contributions are produced into two different branches:

• in the **upper** branch, the file *PulseSequence.mat* is loaded, either with the synthetic Gaussian pulses or true measured pulses, depending on the value of the *ideal\_sig* parameter. The waveforms produced by the scripts are in a normalized form (so

unit amplitude) in order to preserve the correct behavior independently from the operating conditions. For this reason, the sequence stored in the file must be scaled by the signal amplitude (SignAmp) corresponding to the working point selected

Figure 3.3: Input block

• in the **lower** branch, *BackgSequence.mat* provides the background noise sequence, also stored in normalized form. This sequence may refer to ideal white Gaussian noise (ideal mode) or to real measured background noise (real mode), with all the perturbations from the environment. Similarly for the pulse sequence, the background is in a normalized form and so it must be multiplied by the respective noise amplitude.

The output of the two branches are kept separated in order to allow to the subsequent blocks to process them further, filter each of them in a proper way and then combine them into one input waveform. The choice to treat them as distinct allow the reusability and the flexibility of the simulation environment. In fact in this way it is possible to change one of the two amplitudes (or both) to obtain a different simulation, without the need of re-run the scripts to re-generate the input sequences.

Additionally, on an analysis level, it facilitates the downstream blocks to filter, process, and visualize each of the pulses and the noise independently before the combination takes place, which simplifies the analysis of the impact of each part on the overall system performance. So it represents a critical block in enabling the simulation to simulate a wide range of operating points while maintaining the signal definition unchanged and controlled.

### 3.1.2 Opto Hybrid Block

The Opto Hybrid block models the analog front-end of the receiver chain, including the optical-to-electrical conversion of the input sequence, its conditioning, and its preparation for the digital conversion. It contains an initial filtering and conditioning, which can represent the photodiode response, transimpedance amplification and any analog filtering

that exists in real hardware. At the beginning of the block, low-pass filtering is applied in order to limit the passband to 50MHz in the case of ideal signals. It is not performed for the real-data signals because these traces are measured downstream of this component, so they do need any other filtering process.

Figure 3.4: Opto Hybrid block

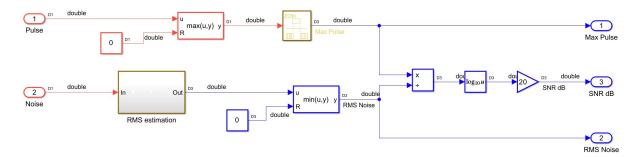

After filtering step the two components, that are still separated to keep their individual signal properties, are multiplied by a proper gain factor that is obtained from the component characterization of the opto-hybrid block and that allows to keep proper values for peak and noise amplitudes. In this way the simulation provides quantitative results that can be compared to experimental ones. After that, the two components are then summed together and a bias offset is also added to the resulting waveform. The bias is added in order to avoid that in the quantization process, performed in the following block, the negative part of the sequence is clipped (remember that the bias is applied only for measured data, while for ideal signals the bias is equal to 0). By shifting the signal, it is possible to center the waveform within the input range of the ADC appropriately. Aside from waveform conditioning, the block performs two important analysis operations that are useful for the statistics performed at the end of the chain:

• Signals Statistics: this operation analyze the input waveform in order to calculate the pulse amplitudes at the peak, the RMS background noise and the corresponding SNR in dB. In particular, the RMS background noise is superimposed with some interferences that increase the power of the noise significantly, by considering the overall trace, leading to an overestimation of the noise level. For this reason, the RMS value of the nose is estimated by using a FIR low-pass filter with moving window size  $3.3\mu s$ : this value is not a random value, but it is slightly less than

the fixed time interval between two consecutive disturbances. Then, by selecting the lowest output value of this filter over time, the estimation process mitigate the transient disturbances contribution to end up with an accurate representation of the true noise floor

Figure 3.5: Opto Hybrid - Signal Statistics sub-block

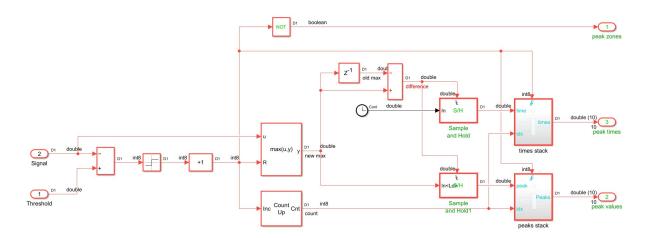

Peaks Finder: this sub-block, as can be observed in Figure 3.6, identifies the pulses that are present in the overall trace. This sub-block always monitors the input signal and, whenever the threshold level is reached by the waveform, it increments a peak counter and starts a run-time search for the peak amplitude in the current peak. During this time, the system analyze the evolution of the peak and it updates the stored value of the peak encountered. Once this peak reaches a stable value, so no higher values of the peak are reached, it is associated to the time of occurrence are captured in a sample-and-hold (S&H [15]) circuit. In this way both amplitude and time-arrival information are preserved with accuracy. As soon as the signal falls below the threshold again, the detection cycle is considered completed and the peak level and time value are stored and into the output registers ("peaks stack" and "times stack") in order to save all the detected peaks. In parallel, the boolean output "peak zones" is generated and it is asserted for the entire duration of the signal when it is above the threshold. All the peak levels, times, and zone info are then added to the "Original\_Peaks" data bus for further processing later. This sub-block will be encountered also in the FPGA block and it allows to perform a comparison between analog and digital analysis in the last block of the chain.

Figure 3.6: Opto Hybrid - Original Peak Finder sub-block

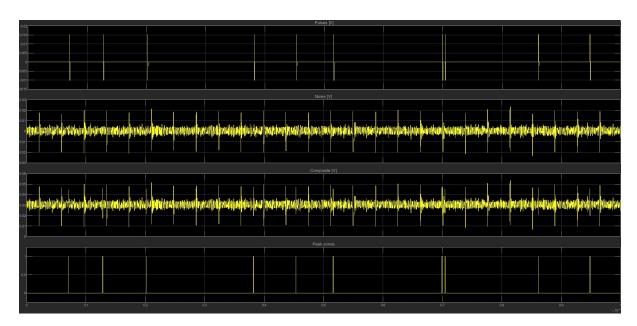

The internal processed signals of the block can be represented both in the time domain and in the frequency domain, providing complementary views of the simulated waveforms' behavior. The time domain representation (Figure 3.7) shows how the signals evolve with respect to time. This Figure displays four different traces:

- The first trace, labeled "Pulses", is the isolated series of received pulses, already normalized and shaped as specified by the input

- Trace "Noise" is the background signal with the periodic interferences, normalized to its RMS, to provide a standard reference against which SNR can be calculated

- The "Composite" waveform is obtained by adding the pulse sequence on top of the background noise and adding the bias offset to avoid clipping. This is the actual signal that will be used as input to the ADC

- A fourth trace is also plotted: the boolean "peak zone" flag, in order to better show when a wanted echo arrives during the simulation.

This representation is extremely useful in understanding the quality of the detector logic to map onto the actual waveform and to check for the consistency of the thresholding approach with noisy inputs. It can be also useful to perform a graphical comparison with digital processed signals to see if any kind of distortion or delay is applied after filtering operation.

Figure 3.7: Time domain output

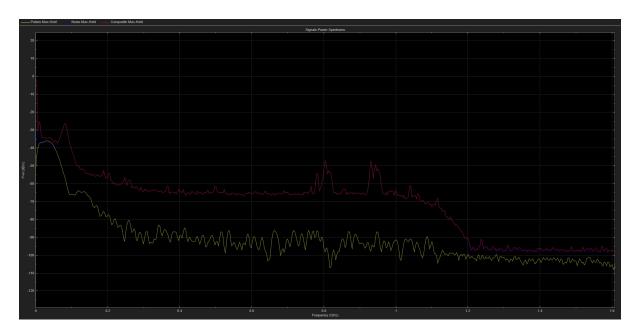

In the frequency domain (Figure 3.8), the same signals are shown in the spectrum analyzer in order to obtain information about their distribution. The background noise has a broad spectrum due to its stochastic nature, while the pulses have a more concentrated spectral content that depends on their width and shape. For this reason, the resulting signal has contributions from both sections. By comparing all the spectra, it is possible to see the success of the filtering process. In particular, the low-pass filter in the block limits the passband to 50 MHz and it attenuates high frequency content.

Figure 3.8: Frequency domain output

Both the time- and frequency-domain analyses provide a full view of the behavior of the analyzed block. The former allows to show how the pulses are superimposed with the background noise, how the bias allows to suppress clipping and how the detection logic senses the true echoes in real time. Meanwhile, latter focuses on the spectral distribution of the signals and very shows the effect of the filter on the overall waveform. This analysis is useful to understand which digital processing method can be implemented in the FPGA.

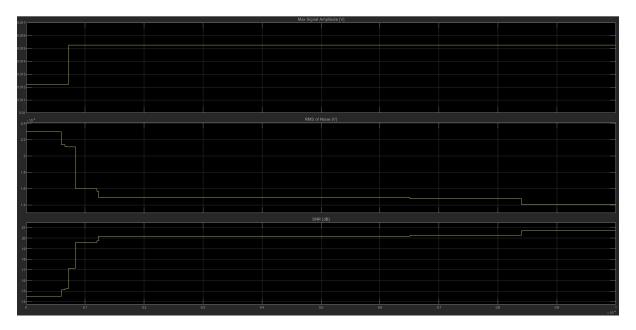

Figure 3.9: Performace parameters

Figure 3.9 plots how the three performance parameters that are always monitored by the Opto Hybrid block change: the maximum pulse amplitude detected, the minimum RMS value of the background noise, and the maximum achieved SNR. These parameters provide a direct feedback of how the analog part of the system can preserve signal integrity in an environment full of noise and disturbances. From peak amplitude and RMS noise values the block can compute the highest detected SNR to quantify the detection ability of the system.

These outcomes are then automatically passed back to the high-level simulation measurements (see Figure 3.2), where they are merged with the result of the subsequent processing steps. By going through this, it is possible to relate front-end behavior to the performance of the system itself, perhaps even seeing where there may be potential bottle-necks or room for optimization. By quantifying the changes over time of pulse amplitude, background noise, and SNR, the Opto Hybrid block provides essential information about the strength of the analog section before digitization, such that the ADC's input is not only appropriately scaled and conditioned but also optimized for trustworthy downstream digital processing.

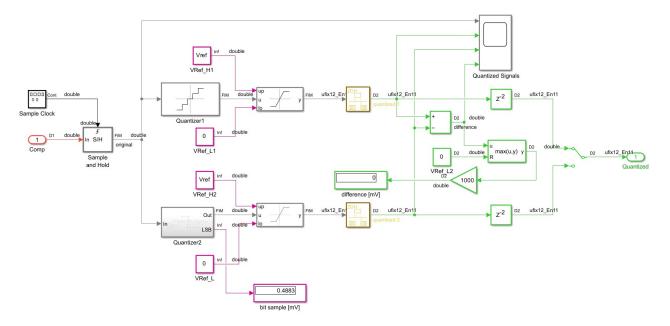

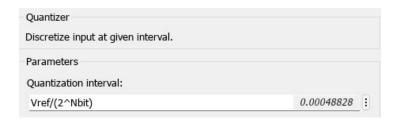

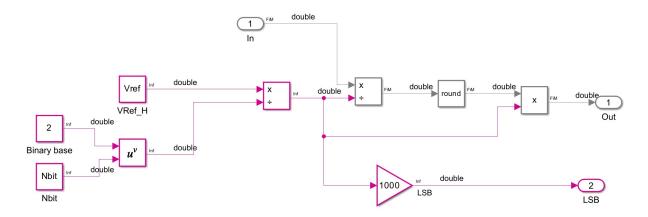

#### 3.1.3 Analog To Digital Converter Block

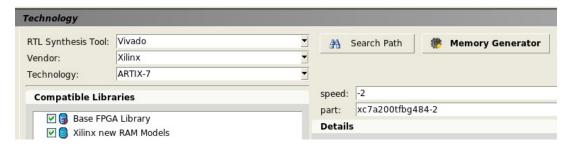

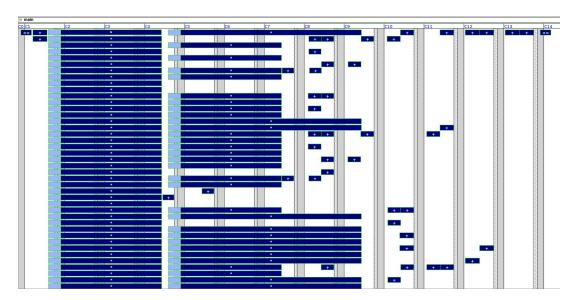

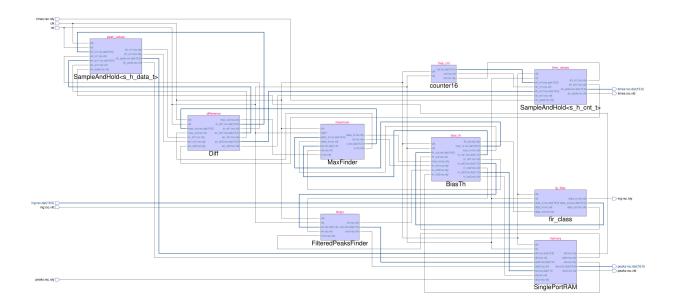

The Analog-to-Digital Converter (ADC) block then acts as the interface between the analog front-end described in the previous paragraph and the sequence of digital processing.