Master Degree Thesis

# Design and Implementation of an Embedded Board for Vehicular Connectivity

#### Supervisors

Prof. Massimo Ruo Roch

Prof. Claudio Ettore CASETTI

Prof. Guido Masera

Candidate

Sofia GIANNOCCARO

OCTOBER 2025

#### Abstract

Vehicular connectivity serves as a cornerstone in the rapid diffusion of intelligent transport systems and smart mobility. By rendering information exchange feasible between vehicles and networked devices, a shift towards more reliable, resource efficient and environmentally conscious traffic interactions is possible. Versatile, reliable hardware platforms supporting various interfaces play a pivotal role in the ongoing deployment of Vehicle-to-Everything (V2X) communication protocols. To provide the physical infrastructure able to integrate different communication standards and allow for interoperability, a compact, custom, open source hardware platform has been tailored for this application.

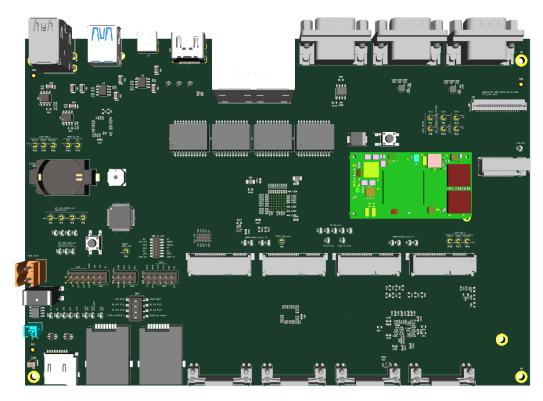

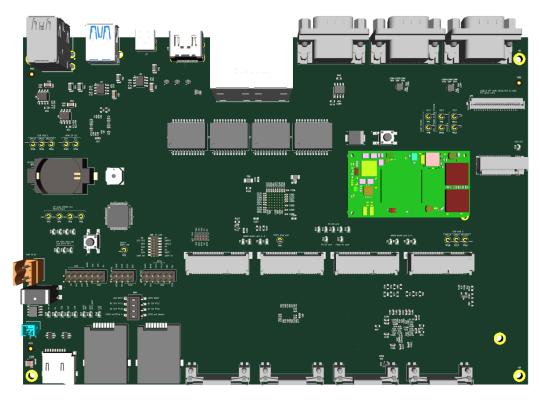

Starting from a set of initial specifications in terms of interfaces, storage, and physical dimensions, an embedded board has been designed to accommodate off-the-shelf modules and support wireless connectivity between vehicles and networked devices in general. The design revolves around a System-on-Module by Variscite (DART series) which functions as a core processing module equipped with interfaces for a standard V2X On-Board-Unit. The board includes multiple miniPCIe slots supporting Wi-Fi and cellular modules, ports for serial communication, CAN, Gigabit Ethernet and Automotive Ethernet, USB and several GPIOs to grant flexibility, in addition to multiple storage solutions.

This thesis describes the board design process up to component placement. The work covers the specification refinement, schematic design, PCB stack-up and component placement, taking into account automotive environmental constraints such as power supply and thermal management. The electronic design has been implemented using KiCad EDA tools. Completion of signal routing and PCB manufacturing files for final prototype development will be carried out in future work.

### Summary

Safe interactions, improved mobility, reduced pollution and energy saving are driving factors for the development of connected vehicles systems. The primary aim is to create a system that goes beyond traditional sensors, laying the foundation for better decision-making and predictive safety insights, as well as improving traffic management with dynamic route adjustment to reduce congestion and minimize emissions associated to fuel consumption.

Consequently, this leads to the necessity of open source embedded hardware for Vehicle-to-Everything (V2X) communication, essential to effortlessly integrate a reliable, powerful, low latency platform in existing vehicles.

Therefore, a solution to lack of customization, limited number of connectors and plug-in slots for connectivity modules on commercial platforms is proposed, while also safeguarding open source compatibility and ensuring interoperability. This thesis outlines the design methodology and implementation of an embedded board for vehicular connectivity, starting from a set of specifications, moving on to hardware components selection and printed circuit board layout up to component placement.

Once the concept was drafted and the initial requirements were refined, the core processing module was selected. The DART-MX8M-PLUS System-on-Module by Variscite based on the NXP i.MX 8M Plus processor was chosen due to its longevity support, small form factor, and most importantly, its capability to operate with Yocto built distributions. The Yocto project is an open source collaboration that provides tools and processes to create custom Linux-based systems in the embedded and IoT sector, regardless of the hardware architecture.

The design process proceeded with the switches and hubs selection, employed to adapt the SoM interfaces to the number of connectors requested by the end user. As for storage solutions, the board features a microSD card slot and an SSD slot compliant with PCIe standard for high speed event logging, in addition to the embedded Multi Media Card (eMMC) integrated on the SoM. Several Gigabit Ethernet ports are incorporated, as well as one Automotive Ethernet port which allows for precise synchronization and timestamp control in high-precision communication. The board is also equipped with multiple USB connectors of different form factors, a couple of serial debug ports and a display output. The Controlled Area Network (CAN) interface is included for robust and low cost data exchange and miniPCIe slots supporting Wi-Fi and cellular modules are incorporated for wireless connectivity.

On board power monitoring, fault detection and recovery is coordinated with the use of a microcontroller which handles the start-up routine and supplies additional interfaces for expandability. Component selection was conducted preferring widely available products with industrial temperature range, to ensure ease of replacement and scalability for future requirements. Board mounted connectors were chosen for enhanced stability due to their resilience to mechanical stress that is caused by frequent attaching and detaching in harsh environments. Furthermore, visual LED signaling for user ease of use and debugging purposes, such as real time monitoring of systems activity and quick fault identification, was incorporated. Integration of additional modules and support for optional peripherals

is ensured via export of interfaces and power lines, granting expandability and flexibility. The thermal management strategy adopted revolves around conductive cooling which, in conjunction with an aluminum case that also grants high grade shielding, help improve system reliability. A power supply with a wide input voltage range is used to step down the voltage and supply the board, facilitating system operation across multiple vehicle types such as passenger vehicles and heavy duty vehicles (trucks, buses, construction machinery).

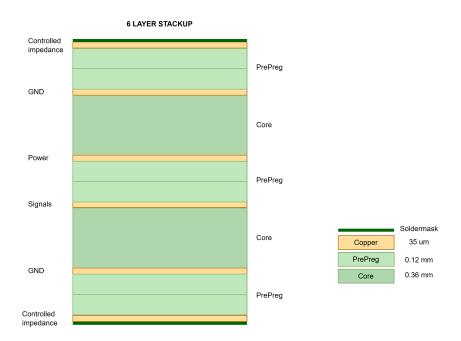

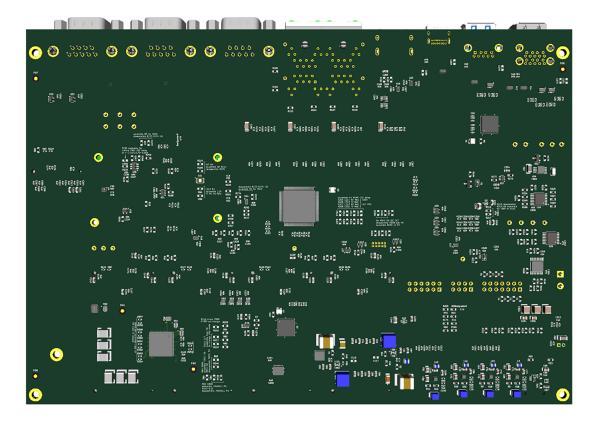

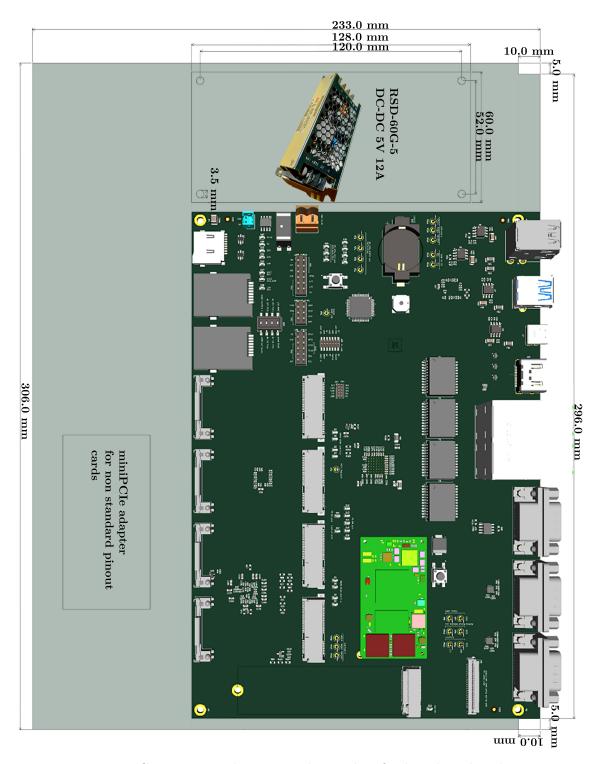

Finally, the design was implemented using KiCad EDA tools. The schematic meets all the requirements specified by the interface standards integrated on the board in question and the PCB stack-up was chosen with the aim of reducing interference, optimize layer count and reliability. The final step ultimately involved careful component placement to ease routing and trace management, while maintaining functional grouping of components, also taking into account mechanical constraints and accessibility.

Further development of the project is planned as part of future work which will include routing completion, the generation of PCB manufacturing files for prototype fabrication and firmware design.

On Board Unit top view

### Contents

| Li | st of | Tables                                                            | 6  |

|----|-------|-------------------------------------------------------------------|----|

| Li | st of | Figures                                                           | 7  |

| 1  | Inti  | roduction                                                         | 8  |

|    | 1.1   | Vehicular communications                                          | 8  |

|    |       | 1.1.1 Regulatory Bodies, Standards and Protocols                  | 10 |

|    | 1.2   | On Board Units                                                    | 12 |

|    |       | 1.2.1 Commercial OBUs                                             | 12 |

|    |       | 1.2.2 Challenges and Gaps                                         | 15 |

|    | 1.3   | Thesis objective                                                  | 15 |

|    | 1.4   | Document structure                                                | 16 |

| 2  | Cor   | ncept to hardware architecture definition                         | 17 |

|    | 2.1   | Specification Refinement                                          | 17 |

|    |       | 2.1.1 Core processing module: SoM selection                       | 19 |

|    | 2.2   | Architecture Draft                                                | 20 |

|    |       | 2.2.1 Interfaces                                                  | 20 |

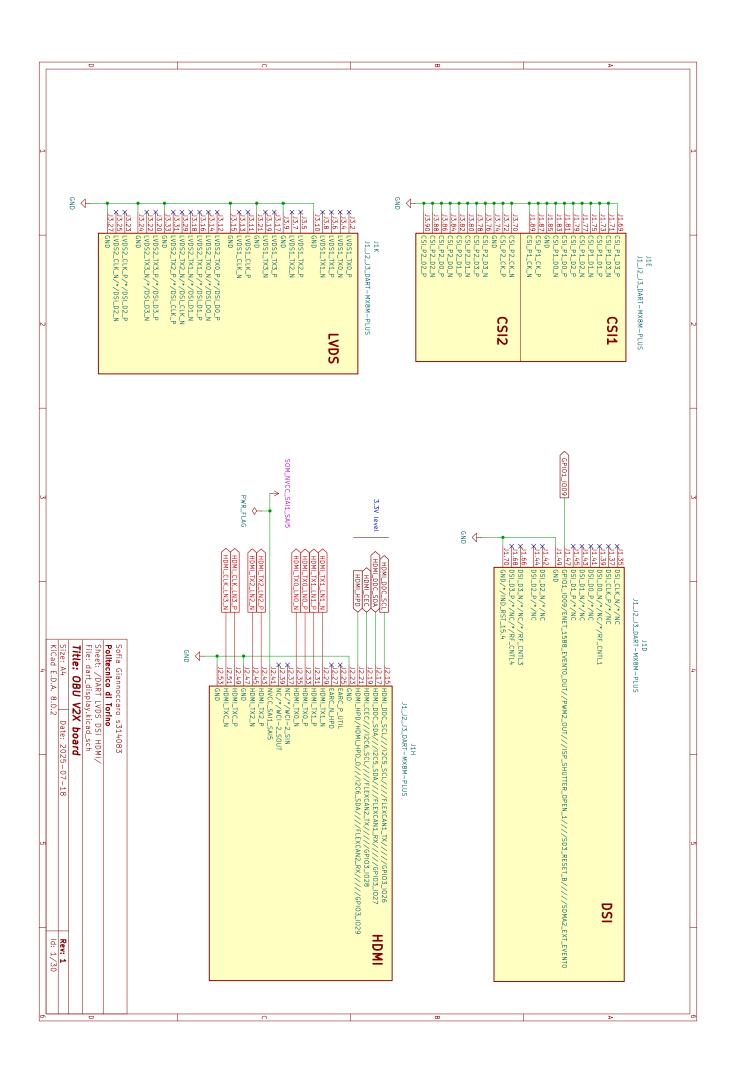

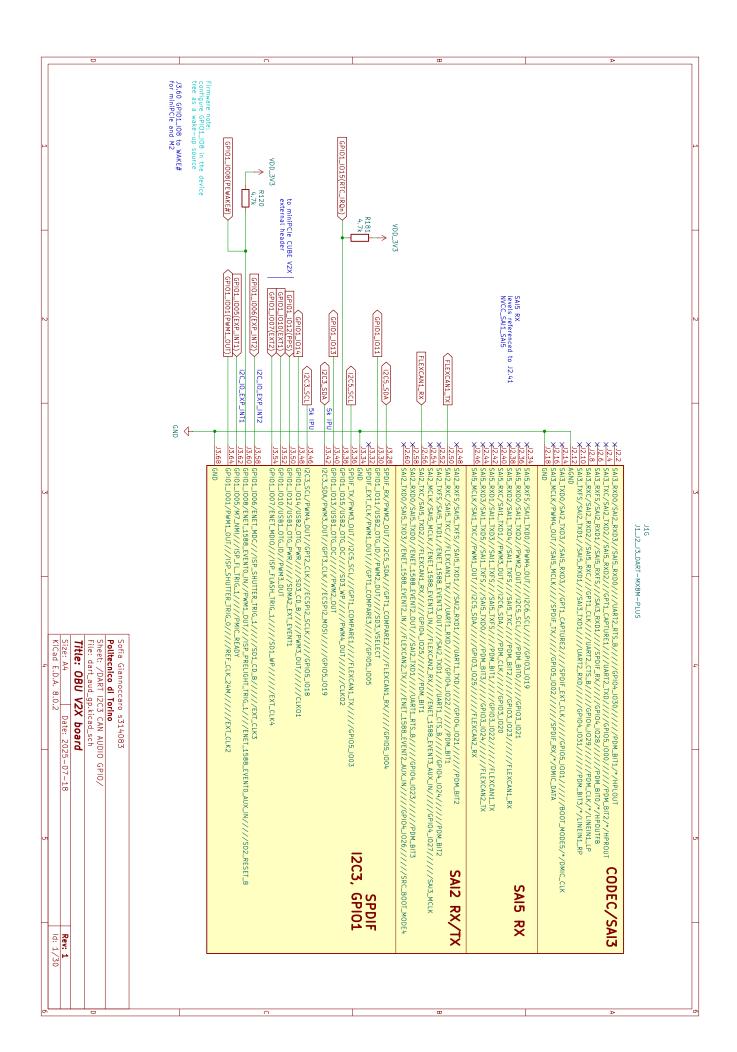

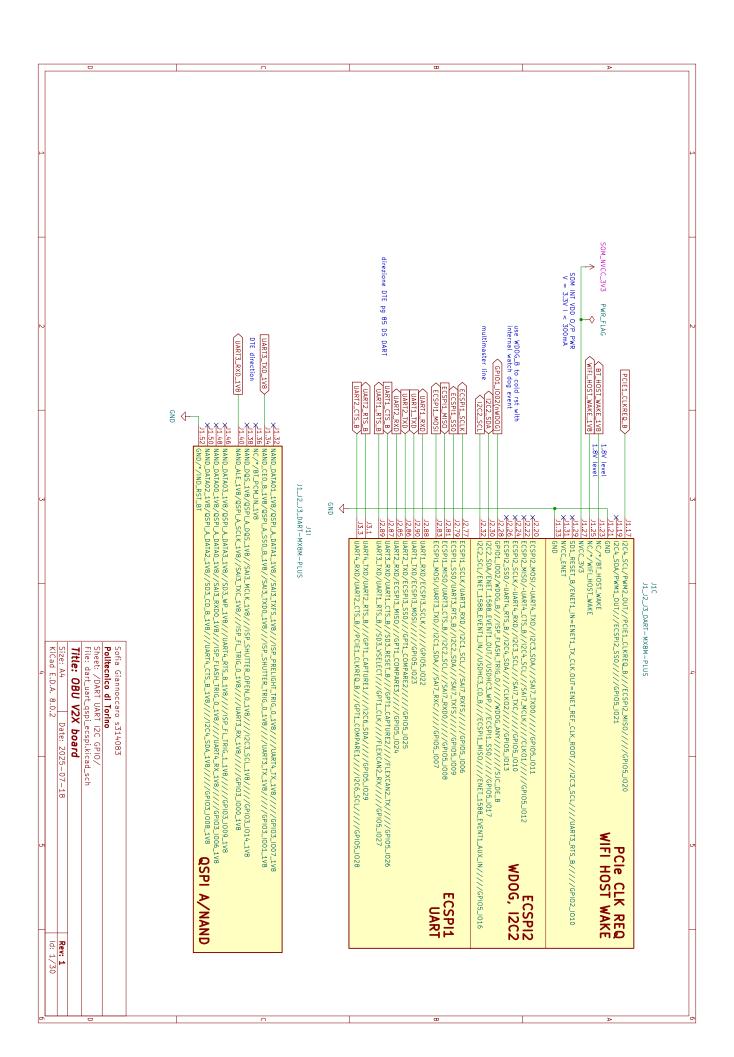

|    |       | 2.2.2 DART SoM pinout mapping                                     | 26 |

|    | 2.3   | Components selection                                              | 27 |

|    | 2.4   | Power distribution and step down converters                       | 27 |

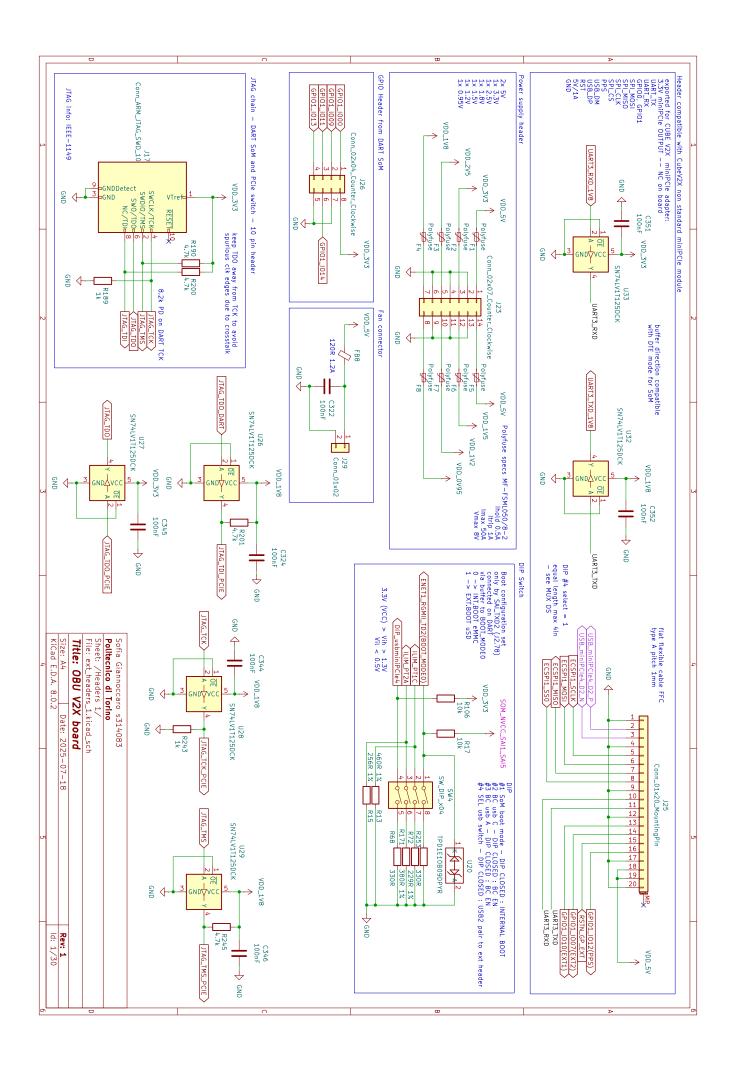

|    |       | 2.4.1 Microcontroller as power supply supervisor                  | 31 |

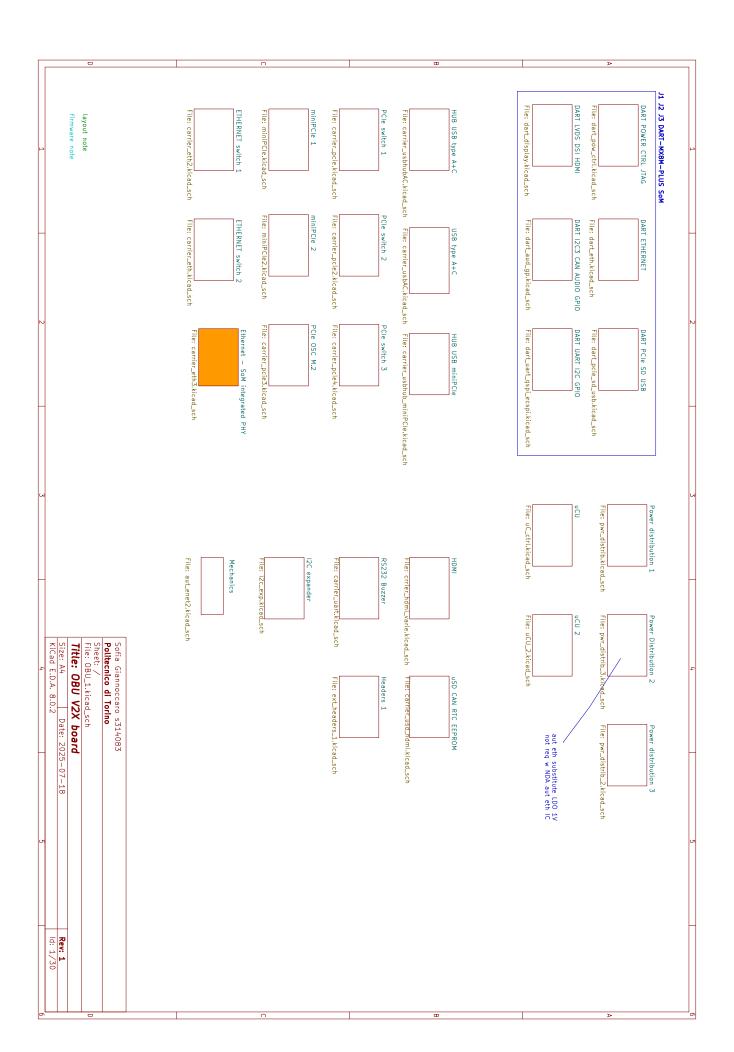

|    | 2.5   | Board I/Os summary and block diagram                              | 32 |

| 3  | Sch   | ematic design                                                     | 35 |

|    | 3.1   | Library setup and symbols adjustment                              | 35 |

|    | 3.2   | Highlights of design choices                                      | 35 |

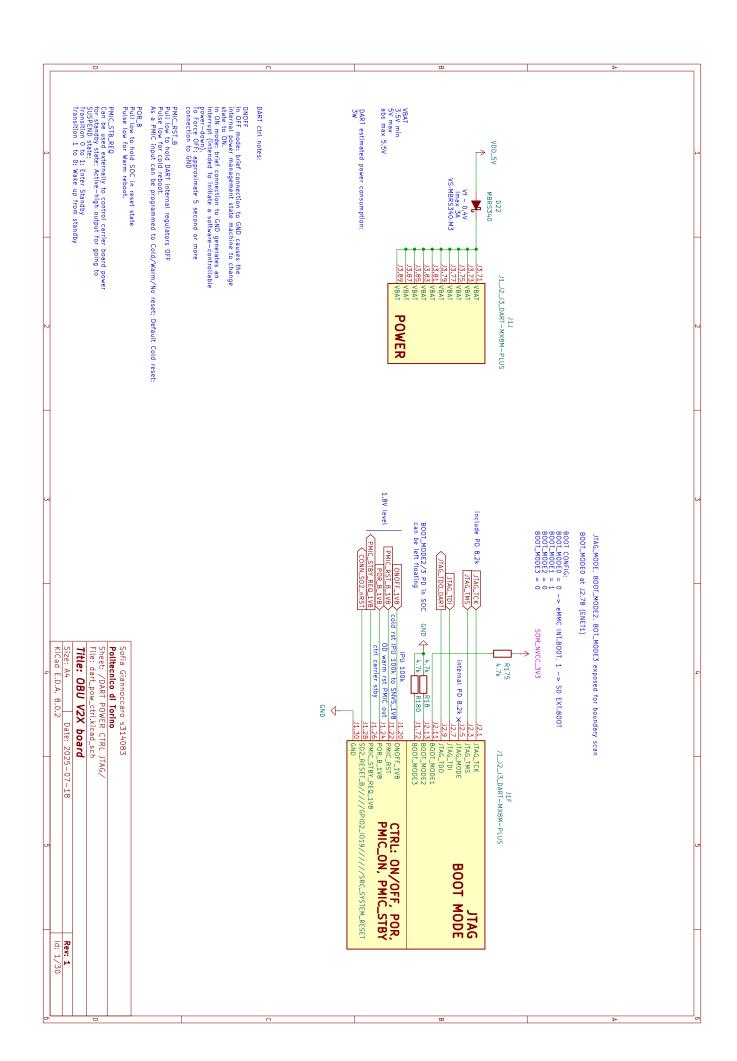

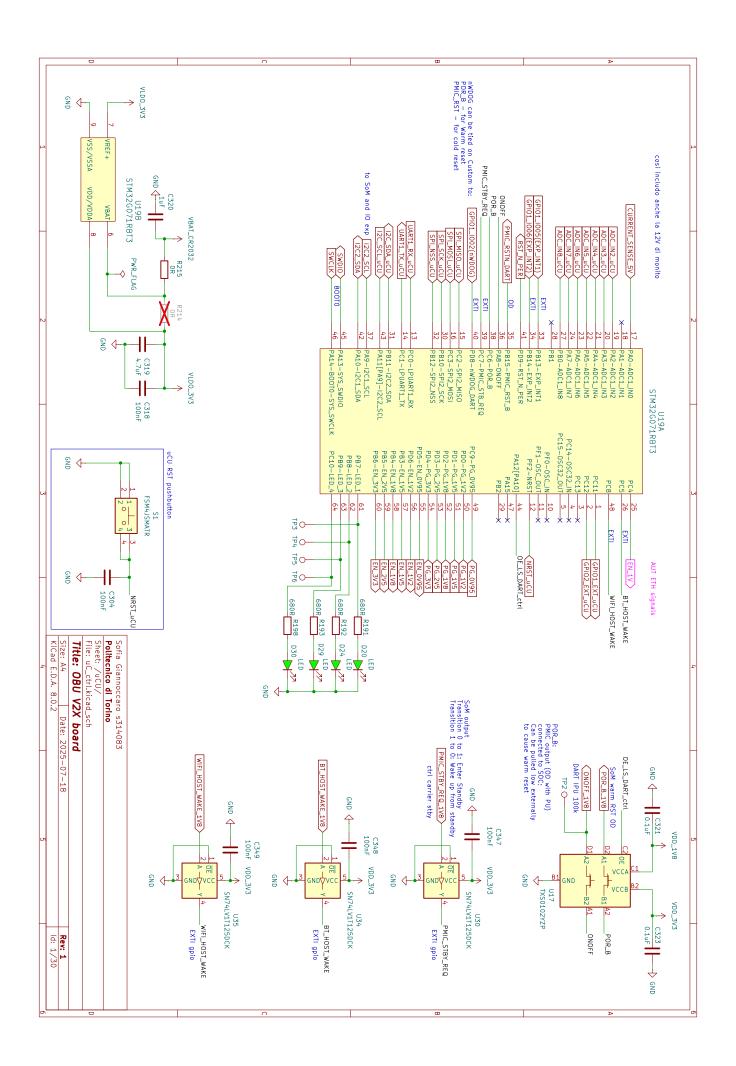

|    |       | 3.2.1 DART-MX8M-PLUS                                              | 35 |

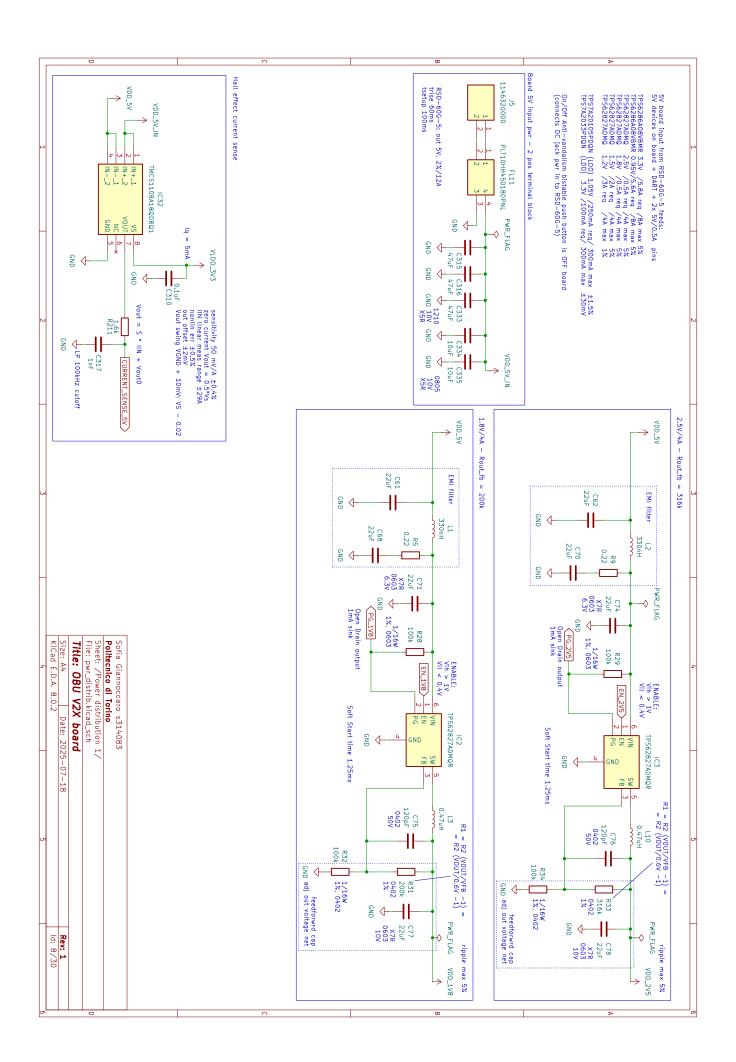

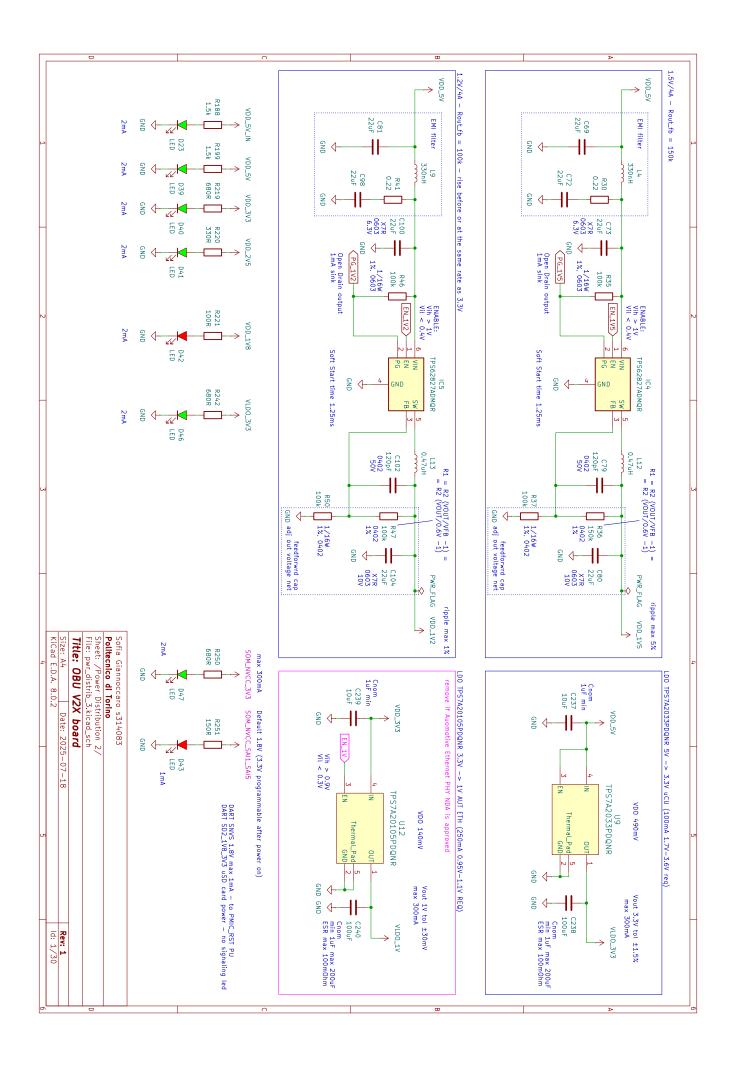

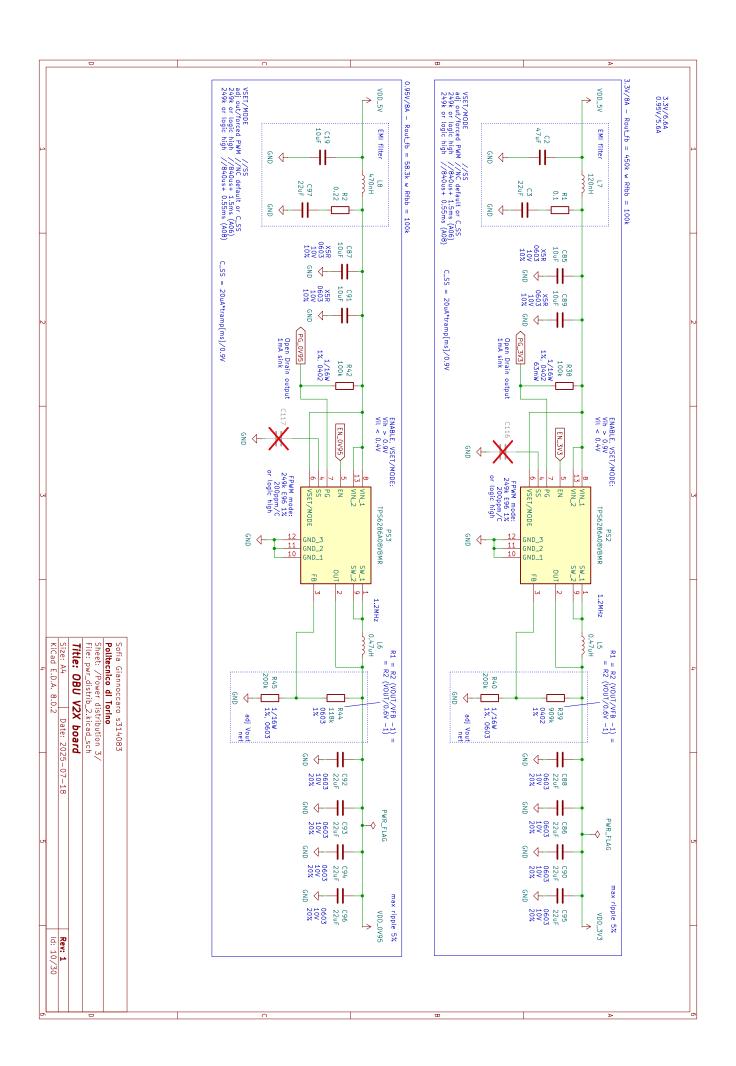

|    |       | 3.2.2 Power distribution and current sensing                      | 37 |

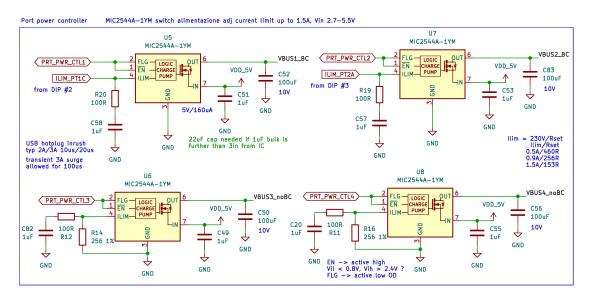

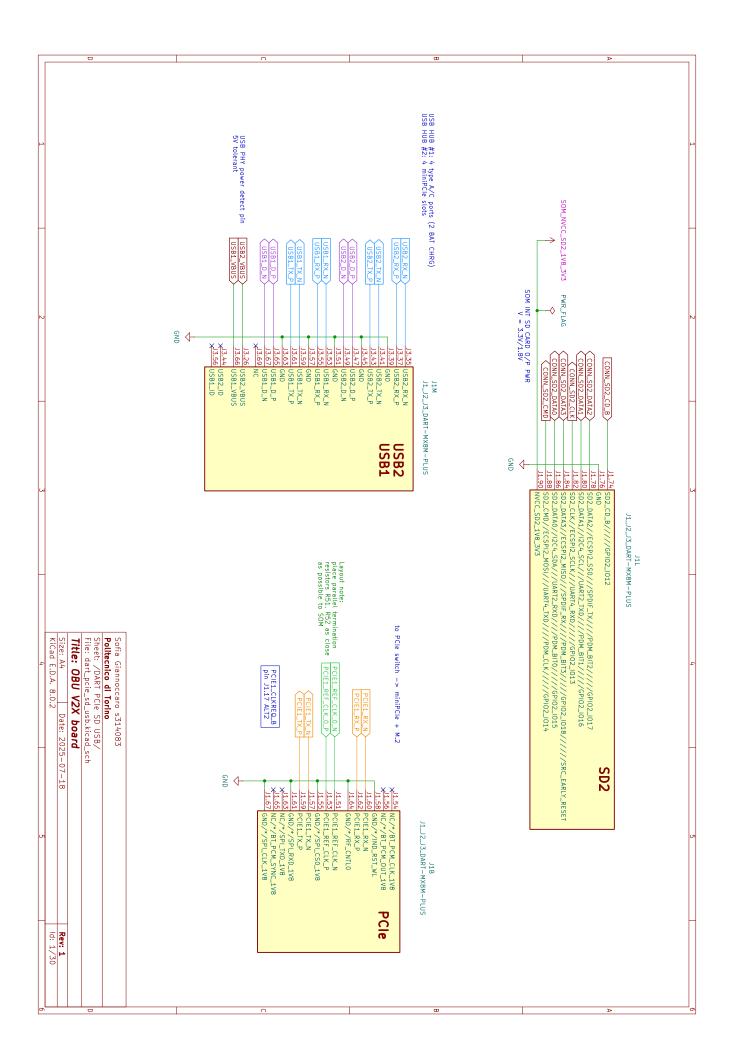

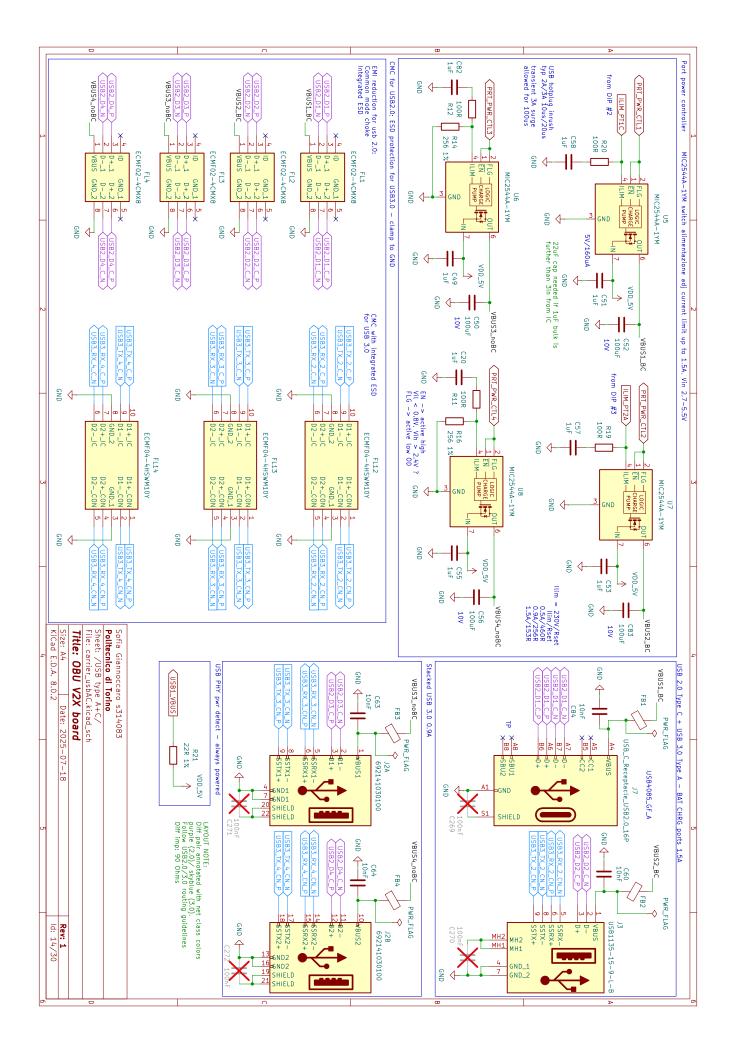

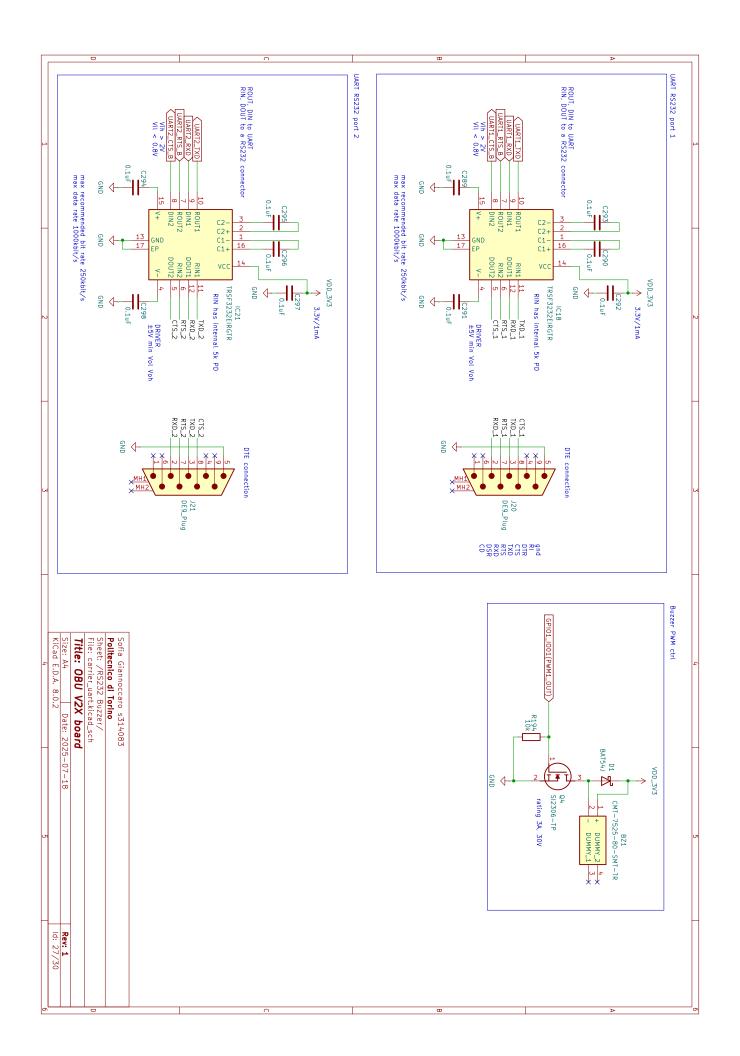

|    |       | 3.2.3 USB port power controller and current limit                 | 38 |

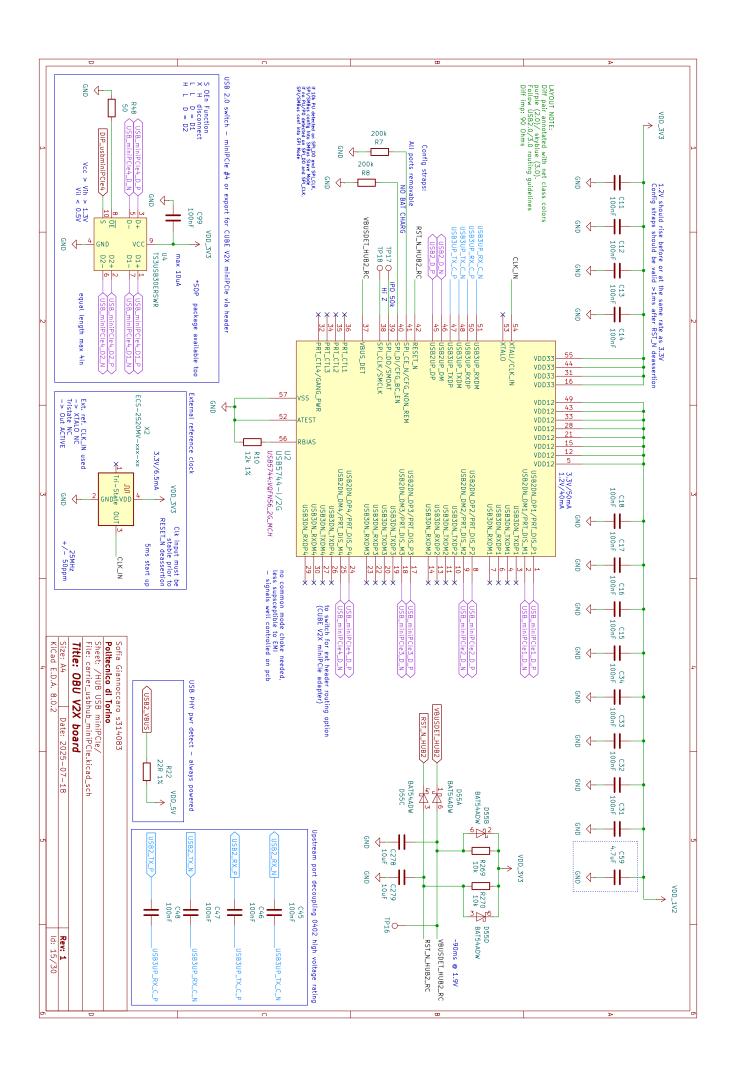

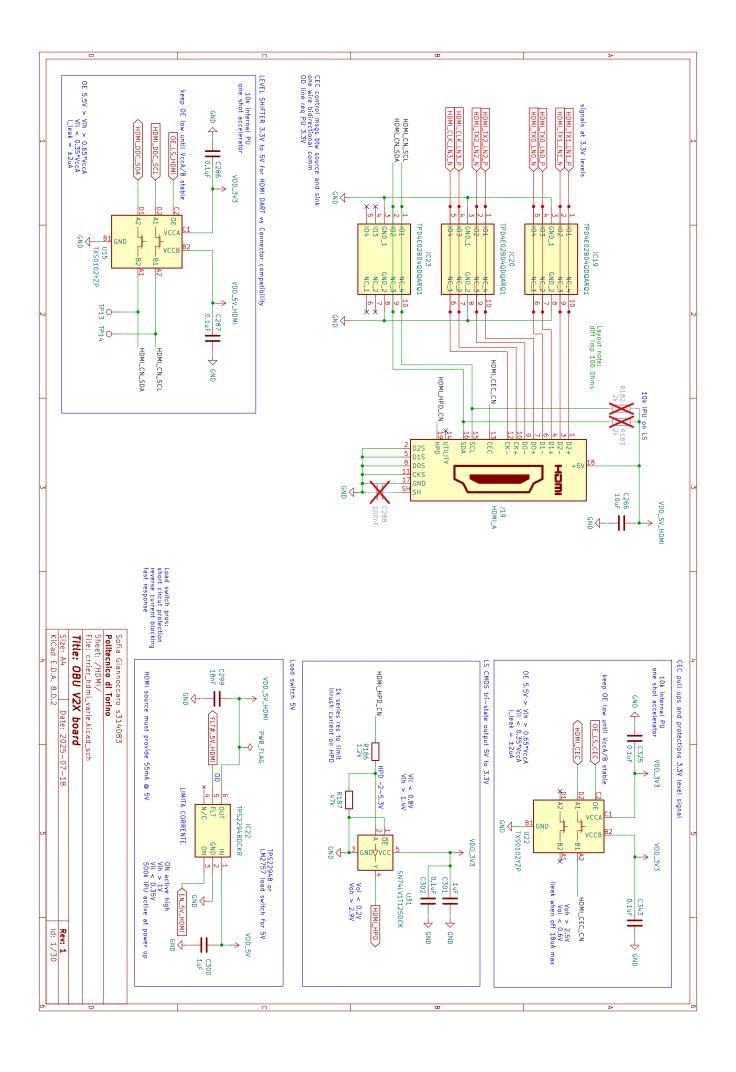

|    |       | 3.2.4 USB 2.0 multiplexer/demultiplexer switch and 20-pin FFC-FPC |    |

|    |       | connector                                                         | 39 |

|    |       | 3.2.5 EEPROM for Board ID                                         | 40 |

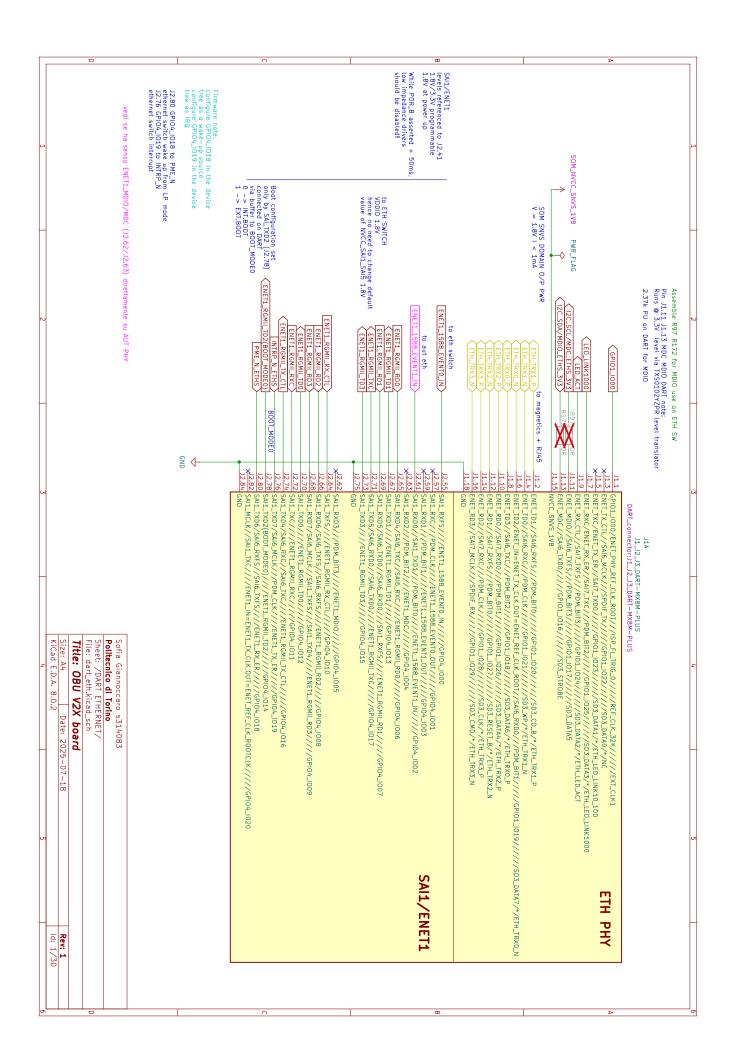

|    |       | 3.2.6 RGMII clock delay                                           | 41 |

|    |       | 3.2.7 Ethernet switch management interface                        | 42 |

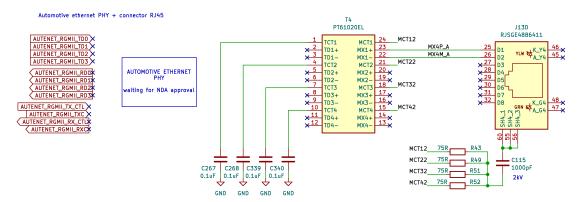

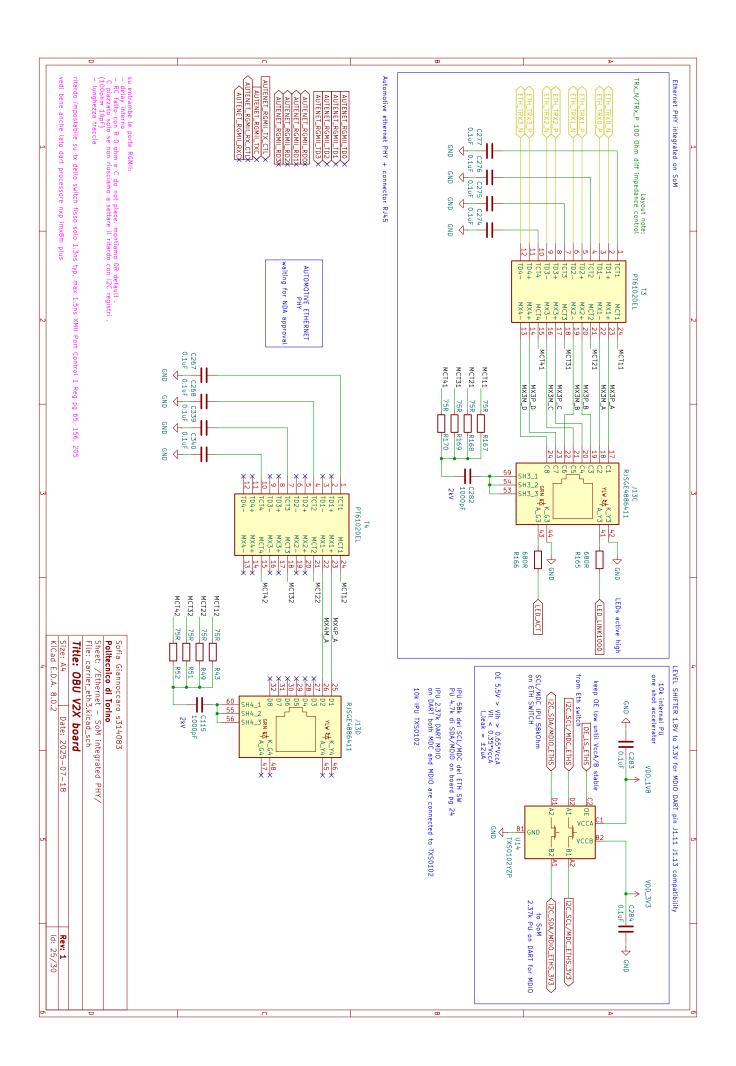

|    |       | 3.2.8 Automotive Ethernet                                         | 43 |

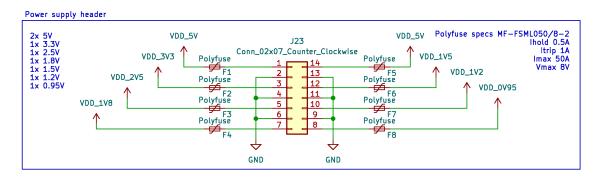

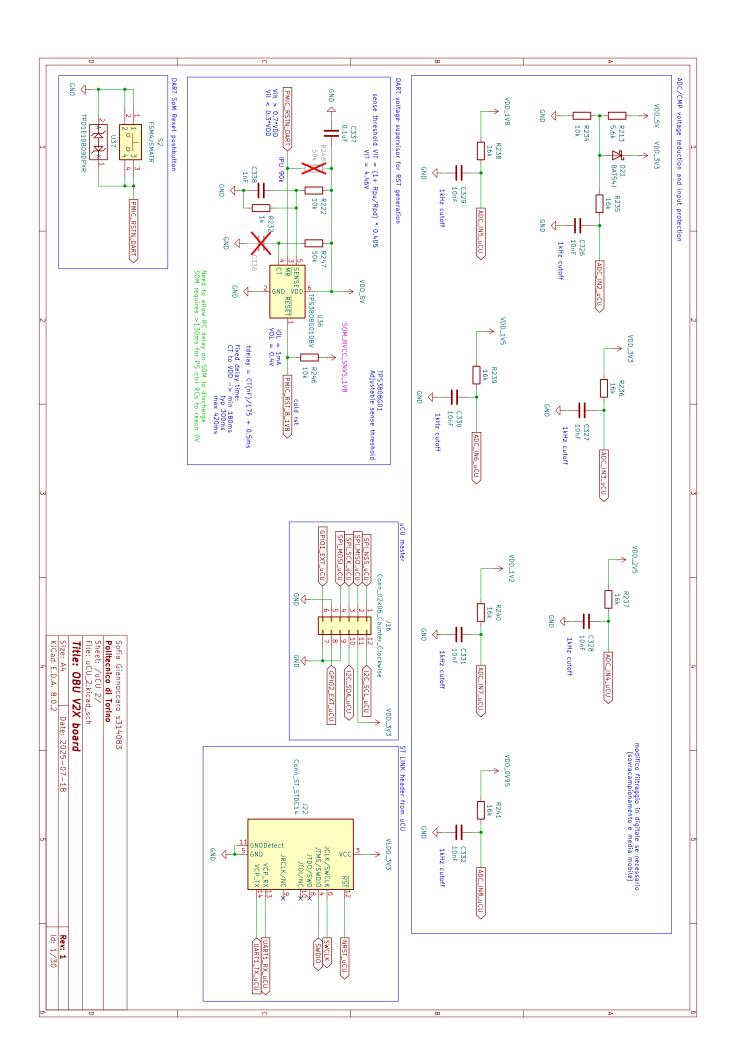

|    |       | 3.2.9 Polyfuses on voltage supply header                          | 43 |

|    |       | 3.2.10 DIP switch                                                 | 44 |

|    |       | 3.2.11 I2C                                                        | 45 |

|    |       | 3.2.12 JTAG chain                                                 | 46 |

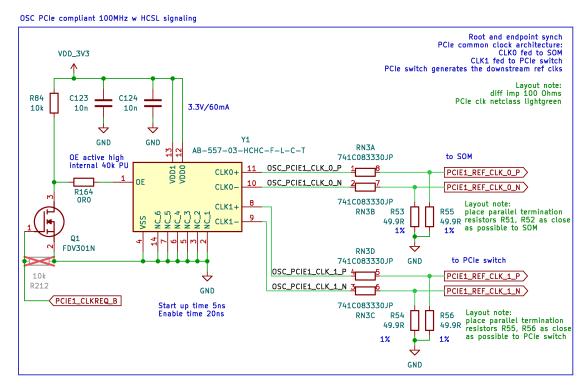

|    |       | 3.2.13 PCIe clock                                                 | 46 |

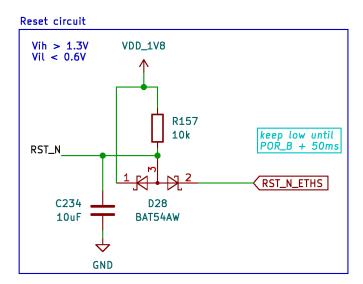

|    |       | 3.2.14 IC reset circuit                                           | 48 |

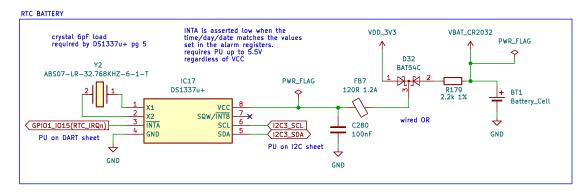

|    |            | 3.2.15 RTC OR circuit                  | 49                   |

|----|------------|----------------------------------------|----------------------|

|    | 3.3        |                                        | 49                   |

|    |            | 3.3.1 Resistors and capacitors         | 49                   |

|    |            | 3.3.2 ESD                              | 50                   |

|    |            | 3.3.3 Ferrite Beads                    | 50                   |

|    |            | 3.3.4 Ethernet magnetics               | 51                   |

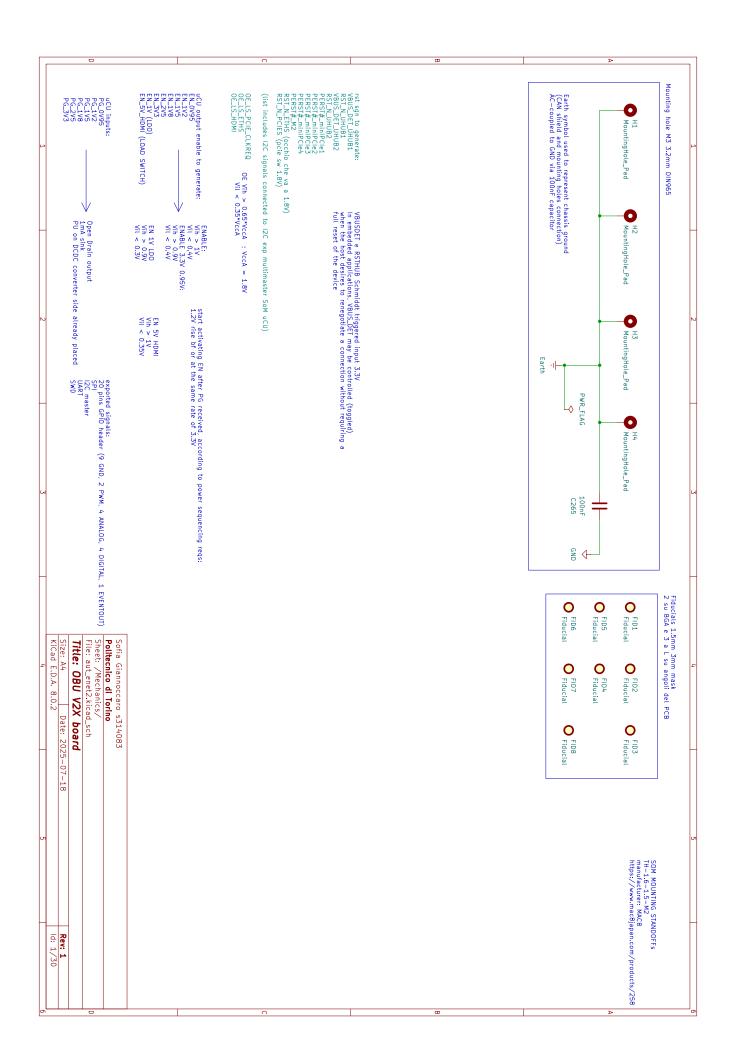

|    | 3.4        | Mechanics                              | 52                   |

| 4  | 4.1<br>4.2 | B design PCB Stack-up and design rules | 54<br>54<br>54<br>57 |

| 5  | Con        | nclusions                              | 60                   |

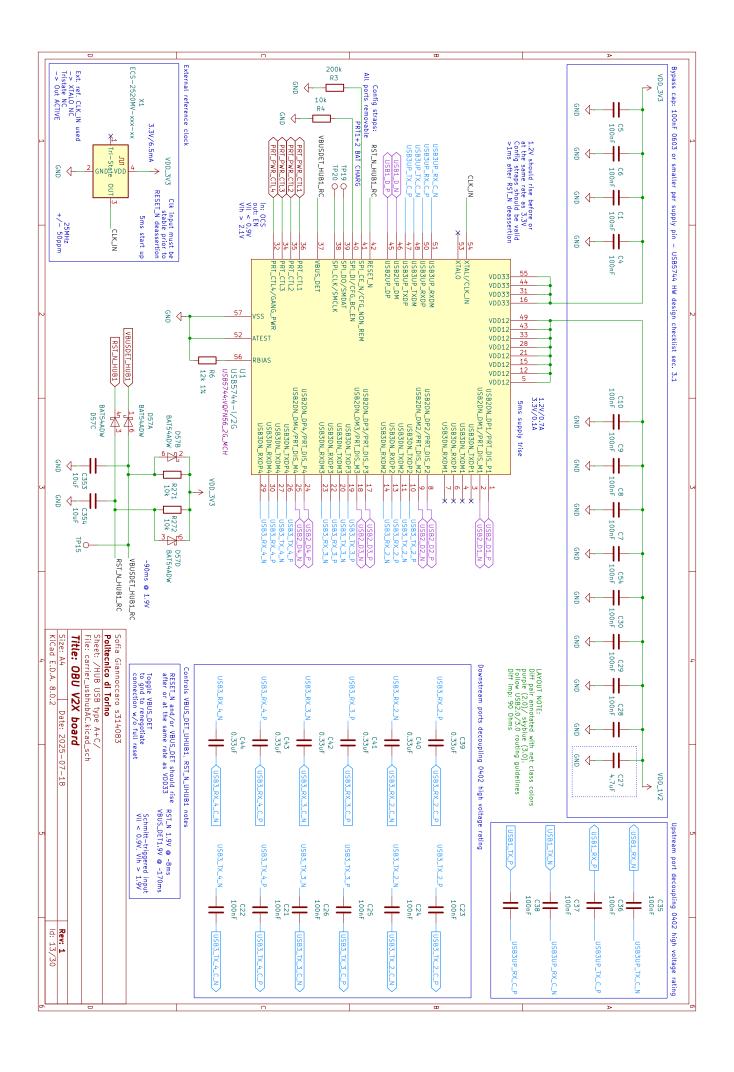

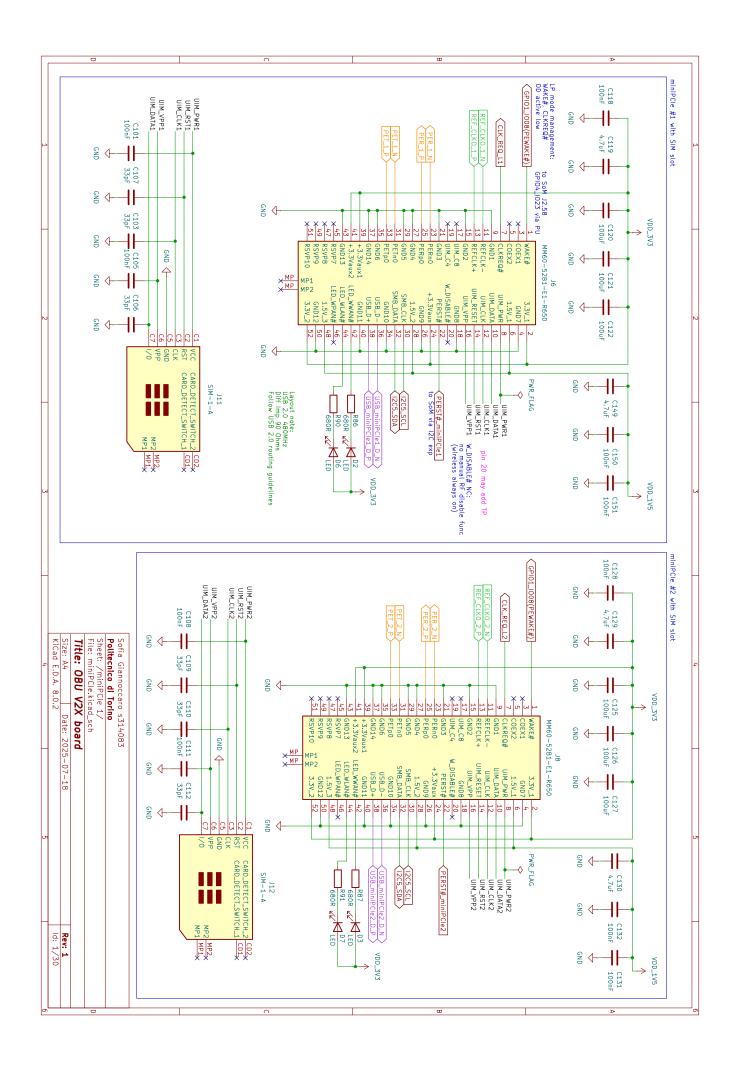

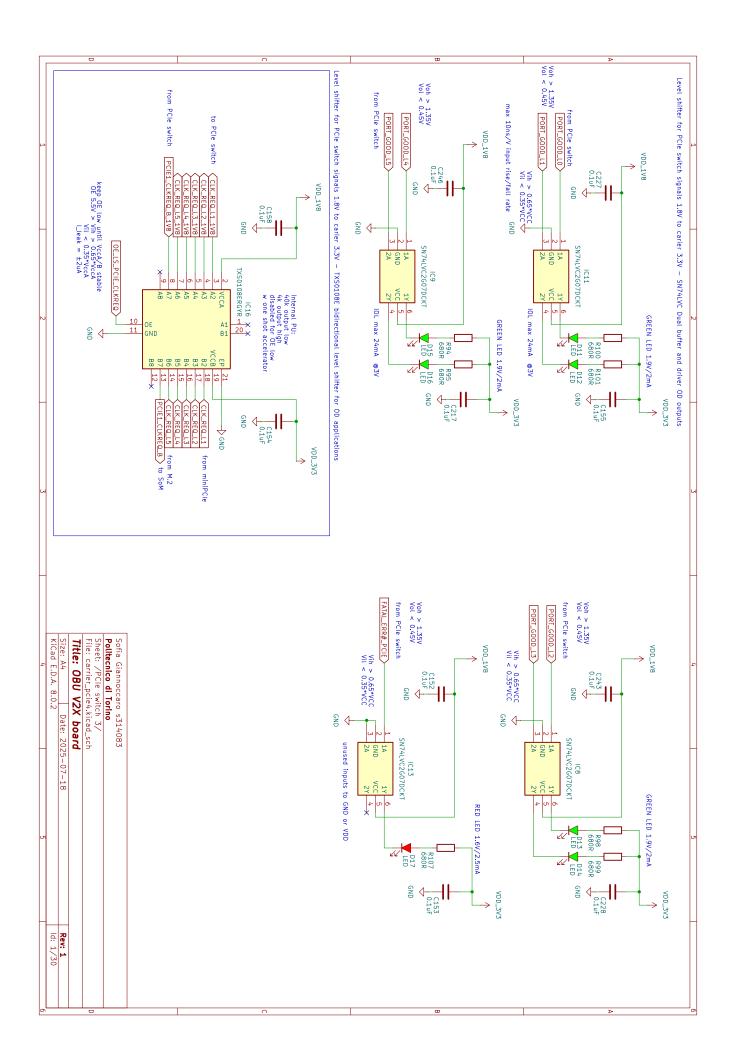

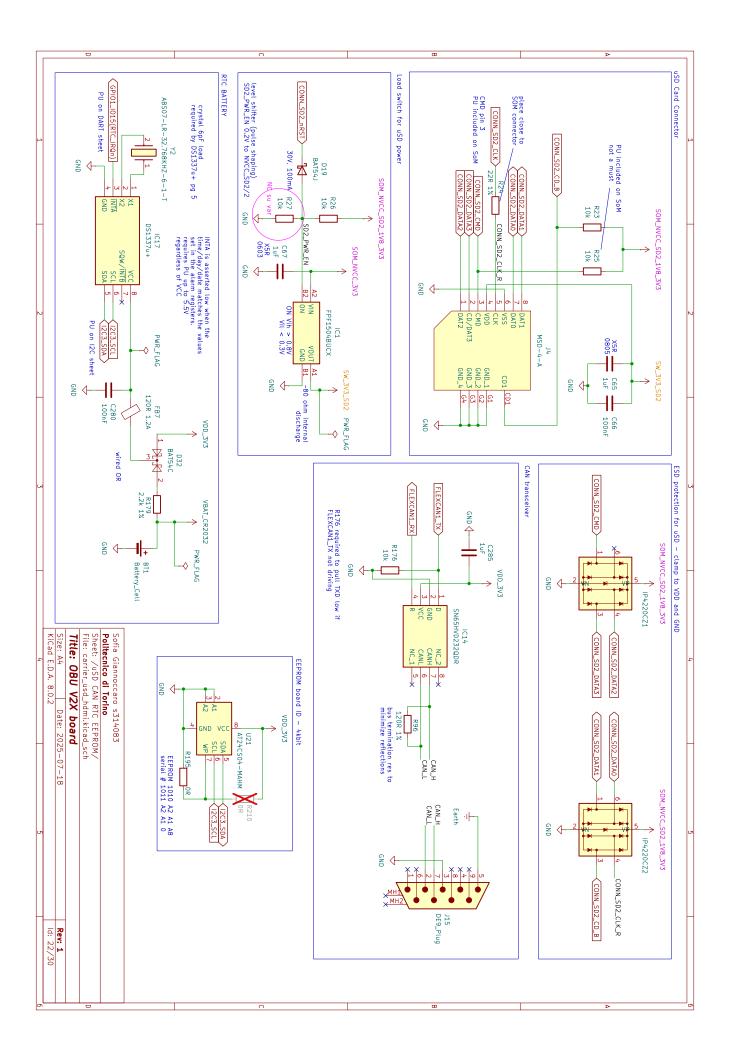

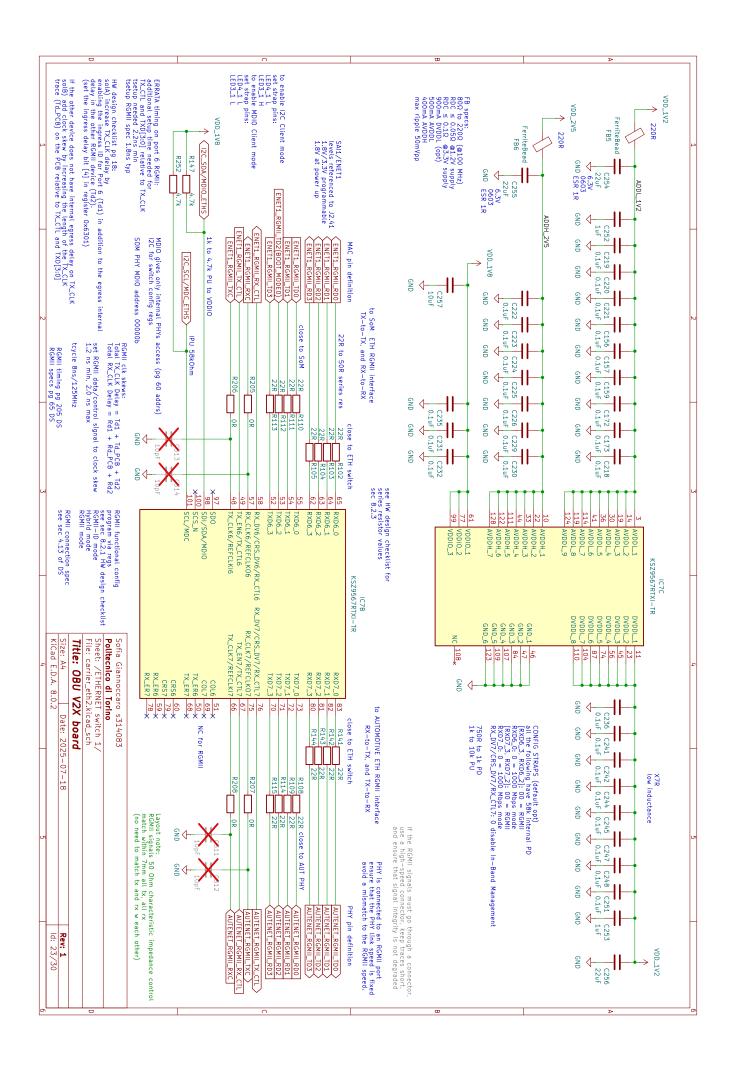

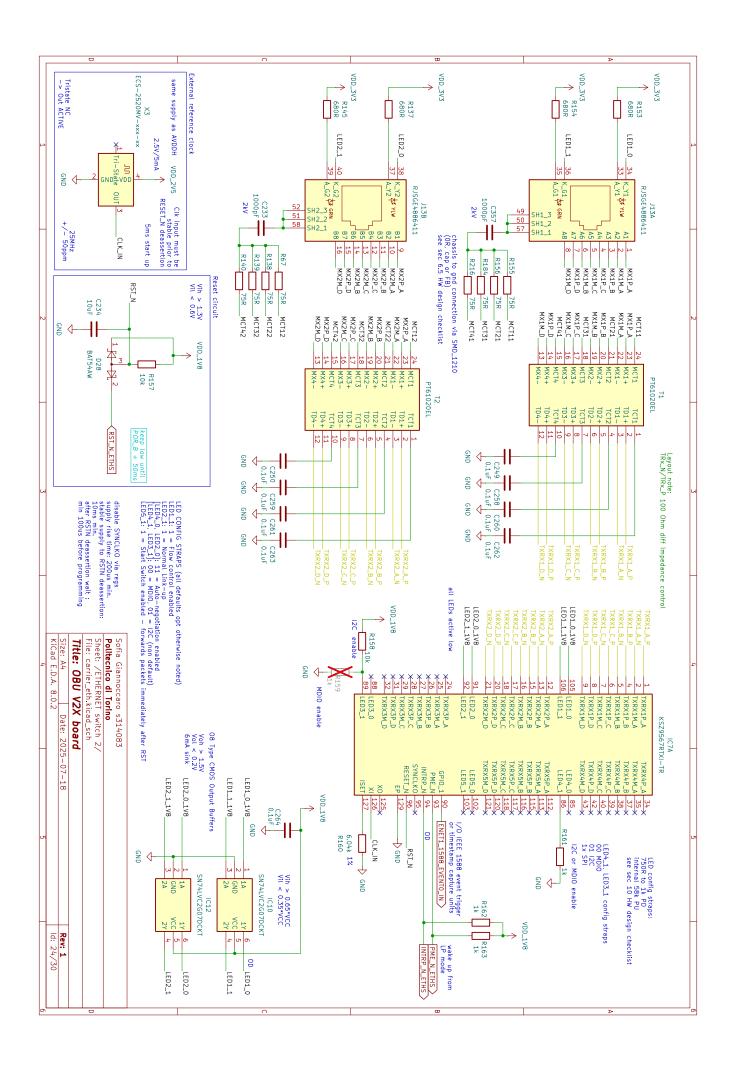

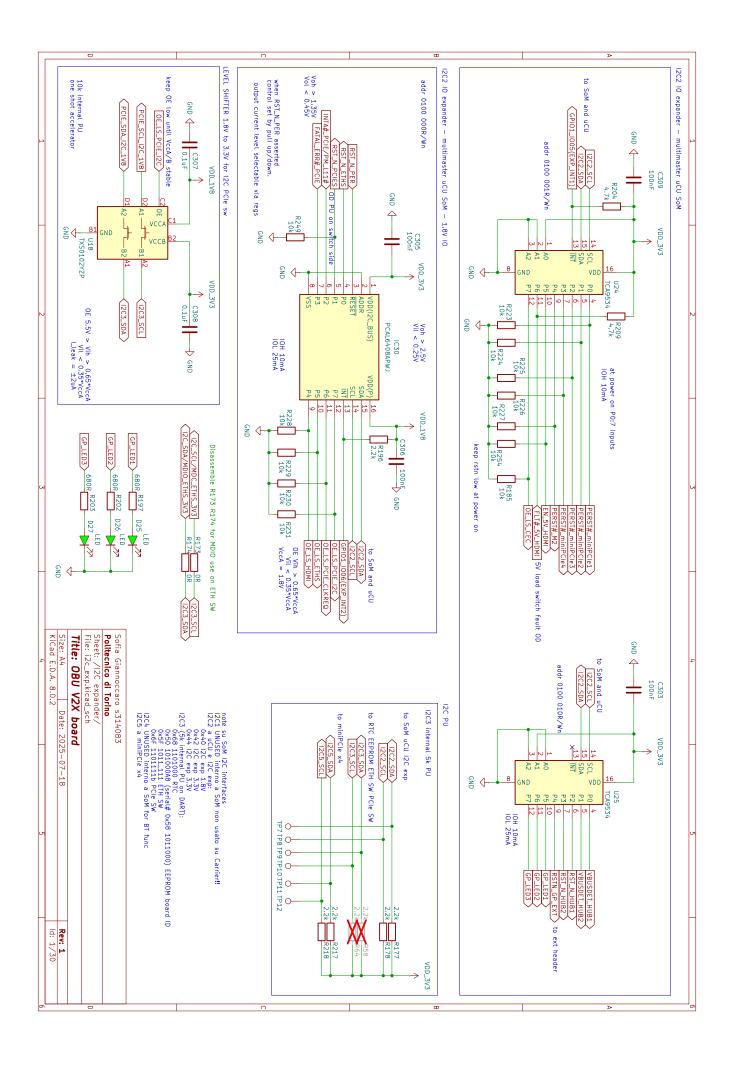

| A  | Scho       | ematic                                 | 61                   |

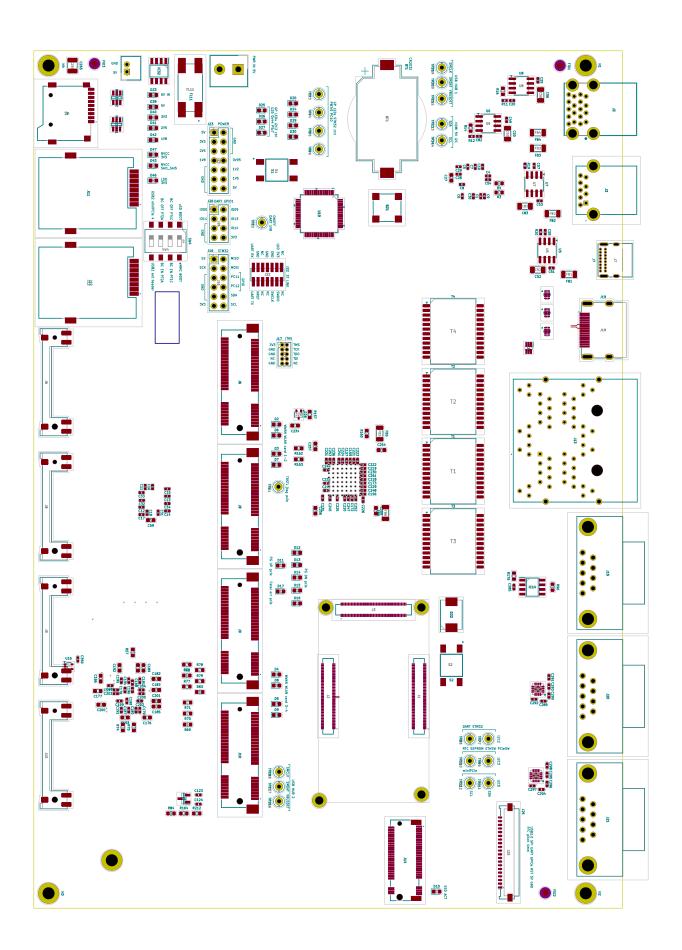

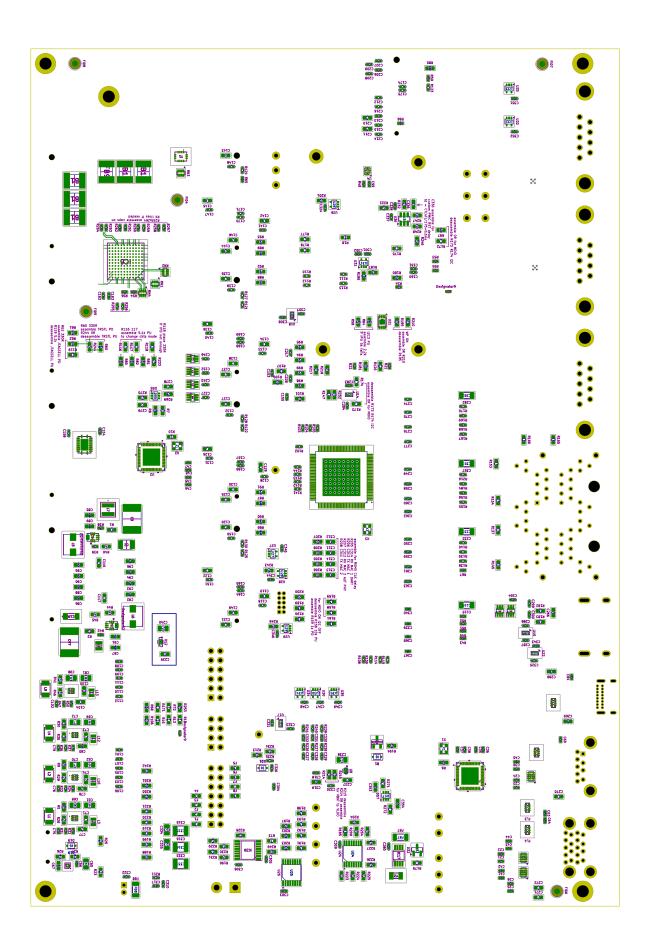

| В  | PCI        | B layout view                          | 92                   |

| Bi | bliog      | graphy                                 | 95                   |

## List of Tables

| 1.1 | Conceptual overview of C-ITS ecosystem                                    | 8  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | V2X protocol stacks and access layers                                     | 11 |

| 1.3 | Widely known embedded solutions for V2X applications                      | 13 |

| 1.4 | Hardware comparison of commercial OBUs with accessible documentation      | 14 |

| 2.1 | DART-MX8M-PLUS V2 ready for purchase hardware configuration               | 20 |

| 2.2 | SoM and ICs: typical operating voltage and current supply. Operating      |    |

|     | mode selected is the one that requires higher supply values               | 28 |

| 2.3 | Peripherals: typical operating voltage and current supply. Operating mode |    |

|     | selected is the one that requires higher supply values                    | 29 |

| 2.4 | Board current drawn per power supply and step down converters             | 29 |

| 2.5 | User accessible connectors, controls and status indicators                | 33 |

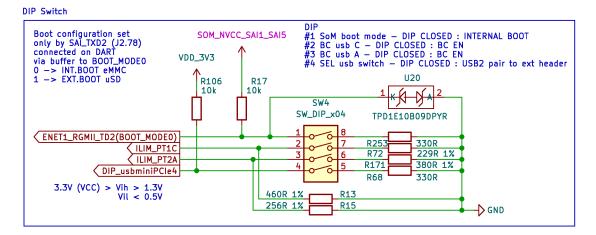

| 3.1 | DIP switch functions selection                                            | 45 |

| 3.2 | DART SoM I2C addressing                                                   | 46 |

| 3.3 | Ethernet magnetics to RJ45 mapping                                        | 51 |

| 4.1 | Enclosure dimensions                                                      | 58 |

| 4.2 | RSD-60G-5 enclosed converter and Double Eurocard dimensions               | 58 |

## List of Figures

| 1.1  | Sketch of a V2X system. Adapted from <i>Phenikaa X Joint Stock Company</i> . | 9  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | Several V2X use cases. Adapted from Nexus Group                              | 10 |

| 2.1  | Board draft conceptual diagram with minimum requirements                     | 18 |

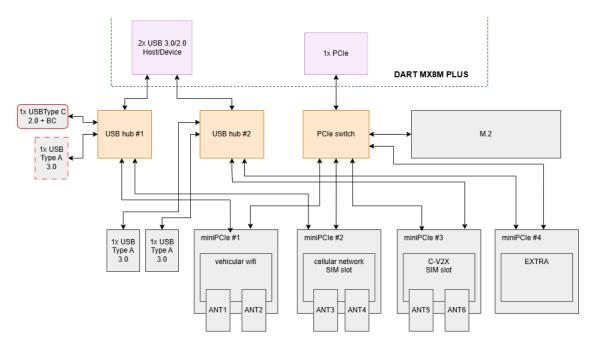

| 2.2  | Block diagram detail: USB and PCIe interfaces                                | 22 |

| 2.3  | PCI Express link concept. Adapted from Board Design guidelines for PCI       |    |

|      | Express interconnect, PCI-SIG Developers Conference                          | 23 |

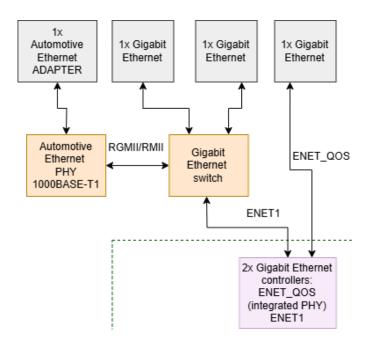

| 2.4  | Block diagram detail: Ethernet interface                                     | 25 |

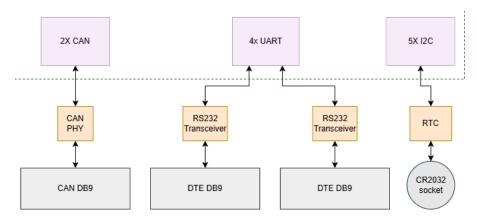

| 2.5  | Block diagram detail: CAN, RS232 interfaces                                  | 26 |

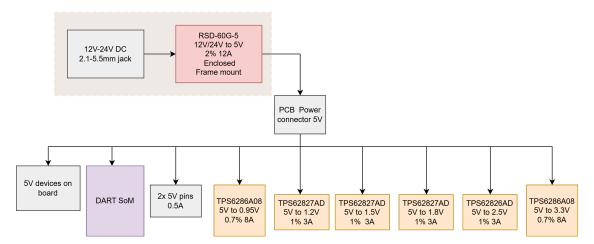

| 2.6  | Block diagram detail: power distribution                                     | 30 |

| 2.7  | RSD-60G-5 Enclosed DC-DC converter by MEAN WELL                              | 31 |

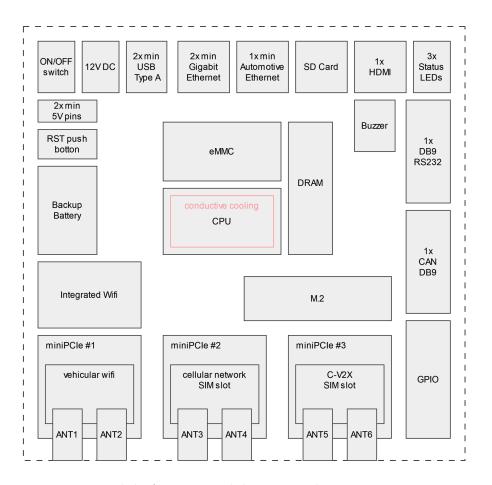

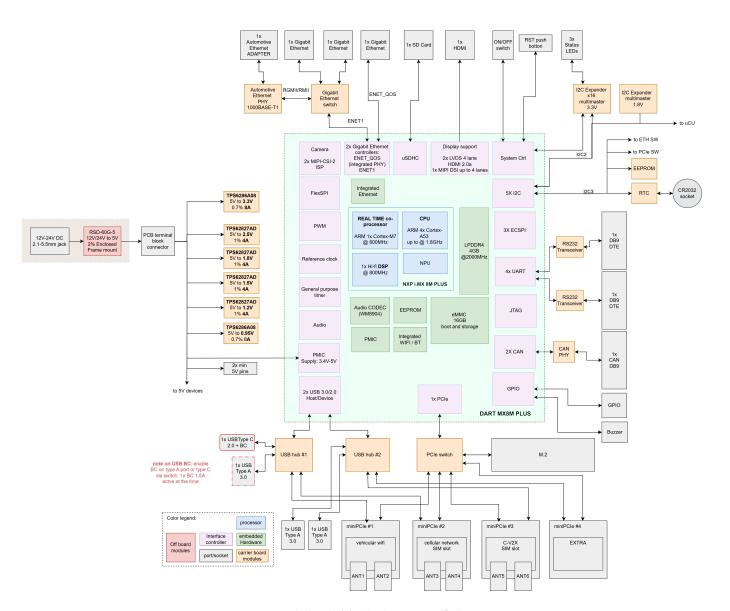

| 2.8  | High level block diagram of the system                                       | 34 |

| 3.1  | Schematic capture: SoM reset circuit                                         | 36 |

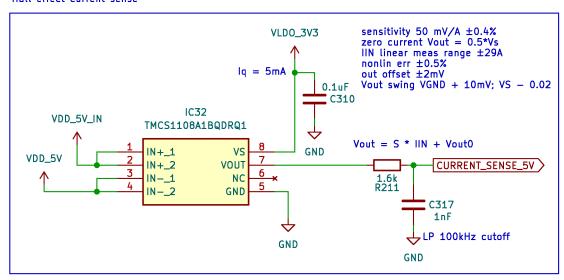

| 3.2  | Schematic capture: Hall effect sensor for current sensing on the main power  |    |

|      | rail                                                                         | 37 |

| 3.3  | Schematic capture: USB Port power controller                                 | 39 |

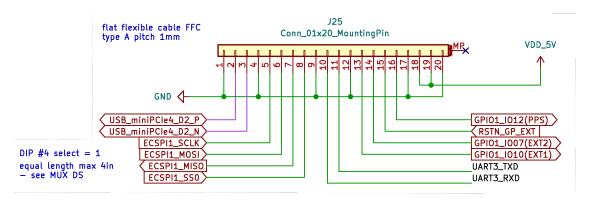

| 3.4  | Schematic capture: USB 2.0 Mux/Demux switch                                  | 40 |

| 3.5  | Schematic capture: 20-pin FFC-FPC connector for non standard pinout          |    |

|      | miniPCIe adapter                                                             | 40 |

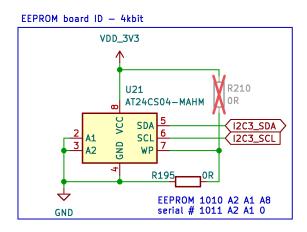

| 3.6  | Schematic capture: EEPROM                                                    | 41 |

| 3.7  | Schematic capture: Automotive Ethernet                                       | 43 |

| 3.8  | Schematic capture: Power supply header                                       | 44 |

| 3.9  | Schematic capture: DIP switch                                                | 45 |

| 3.10 | Schematic capture: PCIe 100 MHz HCSL oscillator                              | 47 |

| 3.11 | *                                                                            | 48 |

| 3.12 | Schematic capture: Real Time Clock                                           | 49 |

| 4.1  | PCB Stack-up                                                                 | 55 |

| 4.2  | Board 3D view: Top                                                           | 56 |

| 4.3  | Board 3D view: Bottom                                                        | 57 |

| 4.4  | Board 3D view: Front panel                                                   | 57 |

| 4.5  | PCB top view: dimensions designed to fit the selected enclosure              | 59 |

## Chapter 1 Introduction

Over the past decade a worldwide effort has been invested towards implementing Intelligent Transport Systems (ITS) solutions, primarily addressing safety and traffic congestion concerns. ITS relies on vehicular connectivity and consists in monitoring, evaluating and managing transportation networks.

Many benefits derive from its deployment. Using real-time traffic data, it's possible to provide several services aimed at improving road safety, traffic efficiency and energy saving altogether. To illustrate some, it features hazards warning systems designed to reduce accidents, built upon predictive safety insights that extend beyond traditional sensors, and dynamic route adjustment to optimize course and maintain efficient movement, thereby minimizing the resulting emissions. Being applicable to both passenger and freight transport, a cohesive network for data exchange is formed, leading to smart mobility.

In recent developments, ITS solutions have evolved towards Cooperative Intelligent Transport Systems (C-ITS), focused on direct communication between entities that enables cooperation and lays the foundation for connected automated mobility (CCAM) [1]. Real-time data is exchanged via Vehicle-to-Everything (V2X) communication technology which allows vehicles to connect to each other, to road infrastructure and other users, thus to coordinate their actions.

| Concept | Role                           | Example scenario                 |

|---------|--------------------------------|----------------------------------|

| C-ITS   | System level coordination      | Traffic management               |

| CCAM    | Automated mobility application | Self driving car                 |

| V2X     | Communication technology       | Shared messages between entities |

Table 1.1: Conceptual overview of C-ITS ecosystem

Successful outcome of C-ITS integration strongly depends on the number of vehicles and objects equipped with units featuring interfaces compatible with vehicular communications. To achieve this, organizations adopt cooperative strategies to ensure coherent and coordinated deployment [2]. Different funding programs are currently active in Europe [3], targeting both infrastructure improvements and research breakthroughs.

#### 1.1 Vehicular communications

Vehicular communications refer to information exchange involving vehicles. They include both in-vehicle interactions and external communications enabled by V2X technologies.

Vehicle-to-Everything (V2X) describes a subset of vehicular communications implemented via wireless connection. Its purpose is to allow interactions between the vehicle and the surrounding environment; meaning among any entity that may affect or may be affected by the vehicle. This technology is developed as part of C-ITS and relies on WLAN and cellular networks infrastructure.

As a result, vehicles can interact with other vehicles, infrastructure, people, bicycles and networks, acquiring so the capability to know ahead even without visibility. This implies that means of transport equipped with V2X can see around corners and beyond any obstruction across a one mile radius; it constitutes a significant technological breakthrough.

Applications for connected vehicles consist of data acquisition from sensors, information transfer and processing, as well as end-user interface aspects. Focusing on the information transfer component, different communication modes of V2X exist and are classified according to the target entity participating in the interaction.

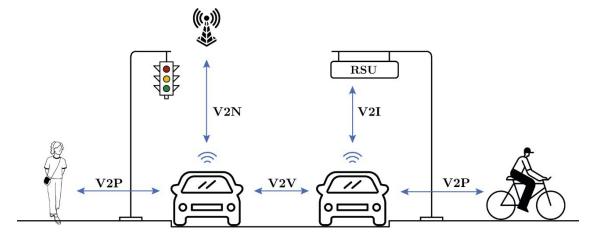

Some types of communication involved in V2X applications are listed below:

- Vehicle-to-Vehicle (V2V): vehicles send messages to other vehicles via On-Board-Units (OBUs);

- Vehicle-to-Infrastructure (V2I): vehicles send messages to the infrastructure and vice-versa, specifically to Road-Side-Units (RSUs);

- Vehicle-to-Pedestrian (V2P): vehicles send messages to pedestrians or bicycles, i.e., Vulnerable Road Users (VRUs), and vice-versa;

- Vehicle-to-Network (V2N): vehicles exchange messages with an application server in the network.

Vehicle interactions with road infrastructure are enabled by the use of Road-Side-Units (RSUs), identified as communicating nodes in the connected vehicles environment. The RSU is a transceiver that links vehicles to infrastructure. It is installed in designated areas alongside roads, collects traffic data and transmits information to a local server. Meanwhile, vehicle to vehicle communication is carried out by means of On-Board-Units (OBUs) installed on vehicles. The OBU is a hardware platforms that implements wireless connectivity and handles signaling, providing interfaces and processing power to let the vehicle engage in V2X communications.

Figure 1.1: Sketch of a V2X system. Adapted from Phenikaa X Joint Stock Company.

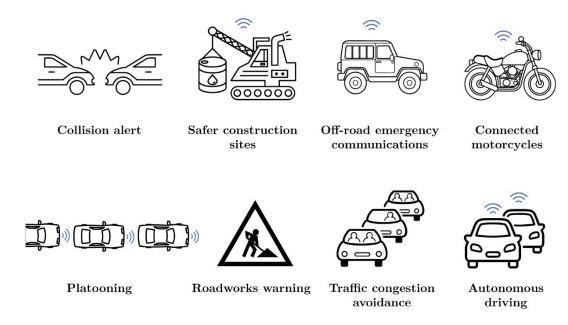

It follows that V2X sets out to resolve two main problems: safety and mobility. Secure exchange of speed, position, acceleration and travel direction data, provides the

means to create applications, such as collision alert, hazards warning, and to notify the driver of any other danger in the path. Therefore, accidents can be dramatically reduced. Risk associated to heavy machinery use in construction sites is mitigated, motorcyclists are safeguarded with prompt warnings of nearby hazards and off-road drivers rescue operations are facilitated, despite being in rough terrain areas where cellular service is often not available. Furthermore, exploiting V2X to control the vehicle's speed, mobile nodes can coordinate their maneuvers as to avoid traffic jams and synchronize themselves to drive through a green wave. Moreover, V2X is essential for large scale deployment of autonomous vehicles since it extends the limited perception of onboard sensors. It is of utmost importance in poor lighting conditions and rough weather, complementing information coming from line-of-sight sensors.

Figure 1.2: Several V2X use cases. Adapted from Nexus Group.

#### 1.1.1 Regulatory Bodies, Standards and Protocols

The aforementioned communication types of V2X, rely on standards and protocols developed by international organizations. These include the European Telecommunications Standards Institute (ETSI) [4], the Institute of Electrical and Electronics Engineers (IEEE) and the 3rd Generation Partnership Project (3GPP) [5]. They provide guidelines to implement the underlying technology and define message format in order to support interoperability across devices.

On the other hand, regulatory bodies such as the European Commission and the Federal Communications Commission (FFC) in the United States, hold legal authority and enforce rules related to operational conditions such as defining spectrum allocations.

Dedicated Short Range Communications Early V2X communication used only Wireless Local Area Network (WLAN) technology, forming a vehicular ad hoc network based on V2V and V2I information sharing, once two senders are in range. This ensures communication in remote areas where no platforms other than the vehicles' OBUs and infrastructure RSUs are present. Standardization at the physical level of WLAN based V2X was handled by IEEE who first published 802.11p, an amendment of 802.11 [6] that adapts the wireless standards to vehicular communications. It operates in the licenced ITS band of 5.9GHz, referred to as the Dedicated Short Range Communications (DSRC) band. Higher layers definition differs according to region, resulting in specific stacks built on the same underlying access technology defined by IEEE. In Europe, the ITS protocol stack with ITS-G5 access [7], specified by ETSI, is adopted; meanwhile, Wireless Access in Vehicular Environments (WAVE) is its counterpart in the United States, which incorporates IEEE 802.11p for the physical layer and IEEE 1609.x protocols for higher layers.

Cellular V2X As commitment towards innovation of ITS solutions grew, V2X started evolving into Cellular V2X (C-V2X), a technological branch that leans on the existing cellular infrastructure. It faces the drawbacks encountered in 802.11p commercial deployment since it did not progress as expected. C-V2X is defined by 3GPP in Release 14/15 as LTE-V2X and was later upgraded to 5G-V2X, from Release 16 onward [8]. The second generation version offers higher speed and lower latency, as it is based on 5th generation New Radio (5G NR) technology. It's important to specify that two cellular communications interfaces are defined for C-V2X. Both of them can be employed for communications based on either LTE or 5G technologies. The interfaces in question are the PC5 for direct communications and the Uu for mobile networks communications. The PC5, also known as sidelink, uses device-to-device communications without requiring the presence of a base station. It enables V2V, V2I, V2P communication, and it's ideal for low latency and safety critical applications. On the other hand, the Uu interface relies on the cellular network infrastructure to connect end users and vehicles to base stations, providing V2N services over a wide range. Hence, the two interfaces complement each other and address the trade off between maximum communications range and response time.

The two implementations are not interoperable at the access layer and are used in conjunction to augment V2X capabilities. Aside from this, they have identical application layers and use cases. The standardization efforts and resulting protocol stacks, are summarized in Table 1.2.

| Communication type | Region | Protocol Stack | Access Layer | Standardization Body |

|--------------------|--------|----------------|--------------|----------------------|

| DSRC               | Europe | ITS-G5         | 802.11p      | ETSI / IEEE          |

| Done               | U.S.   | 1609.x         | 802.11p      | $_{ m IEEE}$         |

| Cellular V2X       | Global | C-V2X          | LTE/5GNR     | 3GPP                 |

Table 1.2: V2X protocol stacks and access layers

#### 1.2 On Board Units

As mentioned before, V2X communication, on the vehicle side, relies on specific hardware platforms that provide the necessary interfaces and processing power to enable vehicular connectivity. On-Board-Units are developed for this purpose.

These units manage both internal and external vehicle communications: once a message is received through a V2X link, the OBU acts as an actuator and notifies the vehicle's internal Electronic Control Unit (ECU). For instance, upon receiving a collision alert via V2X data exchange, the OBU transmits this information to the ECU which will trigger the braking system and prevent impact.

Hence, they are built for transmitting, collecting and storing data. Additionally, they often rely on external hardware components to enhance connectivity, such as cellular modems (usually connected through a miniPCIe adapter), GPS/GNSS receiver for real time positioning and CAN bus for interfacing various sensors and ECUs.

#### 1.2.1 Commercial OBUs

With the intention of understanding technological and functional challenges of OBU devices, available solutions in the commercial market are briefly analyzed. Table 1.3 displays some V2X products listed by companies. Most of these manufacturers offer multiple solutions in the vehicular communications sector, spanning from chipsets and modules to standalone hardware platforms such as OBUs and RSUs.

The product list showed, is based on a cross reference of the latest technical report of C-V2X devices by 5GAA Automotive Association [9], its marketplace website [10] and online research. The 5GAA Automotive Association is an organization of companies in the automotive and telecommunications industries that contributes to the development of ITS solutions.

For simplicity, the table does not distinguish between products supporting PC5 sidelink and Uu connection types, hence the reader is advised that the classification is more complex than illustrated, since the aim is to give a brief overview of commercial products.

Moreover, only products supporting DSRC 802.11p at the physical layer are marked as DSRC compliant, given that it's important to differentiate between devices able to process direct messages using 802.11p radio and the ones that support only the 1609.x protocol stack for DSRC but use Cellular V2X LTE or 5G as underlying technology. In particular, the MobiQ 5931 OBU features this characteristic.

Although the solutions hereby outlined are commercial products, it is worth mentioning a platform developed for research purposes in this field: the LINKS V2X OBU [11]. It is used for advanced CCAM applications testing and supports both DSRC and C-V2X connectivity.

Table 1.4 presents a hardware comparison of products with accessible documentation listed in table 1.3. Fields are left empty if no information is provided. Available solutions proposed by manufacturers in this sector are rapidly evolving, companies are acquired (Cohda Wireless is now part of Danlaw [12]; Lacroix has been incorporated by the Austrian company Swarco [13]), some products are phased out and replaced by more

profitable solutions (Harman Savari mobiWAVE OBU has been superseded by Ready Connect Telematics Control Unit [14]).

| Company        | OBU                 | Market     | DSRC   | C-V2X<br>LTE | C-V2X<br>5G |

|----------------|---------------------|------------|--------|--------------|-------------|

| Cohda Wireless | MK5 [15]            | Global     | ✓      | Х            | Х           |

| Conda wheless  | MK6 [16]            | Global     | ✓      | ✓            | ✓           |

| Commsignia     | ITS-OB4 [17]        | EU/US      | ✓      | ✓            | ✓           |

| Chemtronics    | Hybrid OBU [18]     | US/KOR/CHN | ✓      | ✓            | X           |

| Danlaw         | AutoLink [19]       | US         | ✓<br>X | X<br>J       | X<br>X      |

| CICTCI         | VU4105 [20]         | CHN        | X      | <b>✓</b>     | 1           |

| Cradlepoint    | Ericsson R1900 [21] | Global     | X      | ✓            | ✓           |

| DENSO          | MobiQ [22]          | Global     | X      | ✓            | X           |

| Ettifos        | THEUS OBU [23]      | Global     | ✓      | ✓            | X           |

| RANiX          | RXV200 [24]         | Global     | ✓      | ✓            | X           |

| Askley         | 5G OBU [25]         | EU/US/CHN  | X      | ✓            | ✓           |

| CTAG           | HMCU-OBU [25]       | EU         | ✓      | ✓            | X           |

| Company        | Chipset             | Market     | DSRC   | C-V2X<br>LTE | C-V2X<br>5G |

| Qualcomm       | C-V2X 9150 [26]     | Global     | Х      | <b>√</b>     | Х           |

| A 4 4 11       | CRATON2 [27]        | Global     | ✓      | ✓            | X           |

| Autotalks      | TEKTON3 [28]        | Global     | ✓      | ✓            | ✓           |

| Company        | Module              | Market     | DSRC   | C-V2X<br>LTE | C-V2X<br>5G |

| Unex           | SOM-301 [29]        | Global     | 1      | <b>√</b>     | Х           |

Table 1.3: Widely known embedded solutions for V2X applications

Essential hardware features that allow classification of an embedded board as OBU are V2X radio, Global Navigation Satellite System (GNSS) and in-vehicle communications (Controller Area Network and Automotive Ethernet) interfaces. Most of the listed boards come with a rugged enclosure, which is critical in automotive environments where dust, vibrations and extreme temperatures must be withstood. The core processor adopted is common to all cases, manufacturers opt for either a NXP System-on-Chip based on the ARM Cortex or simply a standalone ARM CPU. It is worth noting that platforms which employ the NXP processor use Linux as operating system, while the ARM based systems rely on proprietary software. Storage is often limited to the embedded Multi Media Card (eMMC), though sometimes external storage solutions are supported such as microSD slots or USB flash drives. Ethernet ports are a must, in fact they provide a high speed, reliable connection for both in-vehicle and external communications. Additional interfaces are Wi-Fi, Bluetooth, USB and serial, which complete the connectivity of the

board. Some OBUs are equipped with audio inputs and HDMI video output, as well as additional GPIOs for expansion. Power input to the board always complies with automotive applications, the voltage range is often wide or simply matches the common 12V supply of standard vehicles. Multiple antennas connectors are always present, seeing as they are necessary to reliably send and receive wireless signals for Wi-Fi, Bluetooth, V2X radio and GNSS.

|                        | MK5           | MK6           | ITS-OB4      | Hybrid OBU | AutoLink | R1900     | MobiQ | THEUS                | RXV200    | 5G OBU   | HMCU-OBU     |

|------------------------|---------------|---------------|--------------|------------|----------|-----------|-------|----------------------|-----------|----------|--------------|

| Core                   | NXP<br>i.MX6  | NXP<br>i.MX8  | NXP<br>i.MX6 | ARM<br>A9  | -        | ARM<br>v8 | ARM   | NXP<br>i.MX8<br>Plus | ARM<br>A7 | -        | NXP<br>i.MX6 |

| OS                     | Ubuntu        | Debian        | Linux        | Prop.      | Prop.    | Prop.     | Prop. | Linux                | Linux     | -        | Linux        |

| RAM                    | 1G            | 1G            | 2G           | 1G         | 1G       | 1.8G      | -     | 4G                   | 1G        | 2G       | 1G           |

| eMMC                   | 4G            | 16G           | 4G           | 8G         | 8G       | 6G        | -     | 16G                  | 8G        | 16G      | 4G           |

| Storage                | 4G            | uSD           | uSD          | uSD        | -        | -         | -     | -                    | -         | -        | -            |

| Ethernet [bps]         | 100M          | 1G            | 1G           | 1G         | 1        | 1G        | 1     | <b>✓</b>             | 1G        | 1G       | 1G           |

| Power [V]              | 7-36          | 7-36          | -            | 12/24      | 12/24    | 9-36      | 12    | 7-36                 | 12        | 1        | 8-16         |

| GNSS                   | ✓             | ✓             | 1            | 1          | 1        | 1         | 1     | ✓                    | ✓         | /        | ✓            |

| Wi-Fi                  | Х             | ✓             | ✓            | -          | 1        | 1         | -     | ✓                    | ✓         | 1        | <b>√</b>     |

| Bluetooth              | X             | ✓             | X            | -          | 1        | 1         | -     | ✓                    | X         | <b>✓</b> | ✓            |

| DSRC chip              | NXP           | NXP           | -            | -          | -        | -         | -     | -                    | -         | -        | -            |

|                        | Road-<br>link | Road-<br>link |              |            |          |           |       |                      |           |          |              |

| C-V2X chip             | Х             | SA515         | -            | -          | -        | -         | -     | SA515M               | CX1860    | -        | -            |

| USB                    | Х             | ✓             | ✓            | ✓          | 1        | ✓         | 1     | ✓                    | ✓         | X        | ✓            |

| CAN                    | Х             | ✓             | 1            | ✓          | 1        | Х         | ✓     | ✓                    | X         | <b>\</b> | ✓            |

| Automotive<br>Ethernet | X             | 1             | X            | X          | X        | X         | X     | X                    | X         | Х        | X            |

| Serial                 | X             | X             | X            | 1          | ✓        | ✓         | ✓     | ✓                    | ✓         | X        | X            |

Table 1.4: Hardware comparison of commercial OBUs with accessible documentation

Security and certification is a key aspect in OBU design. When handling safety critical data it is essential to certify the board to ensure automotive standards and V2X radio specifications are met. This is quite expensive, since hardware, software and radio interfaces must all be tested for standard conformance.

Adopting standalone pre-certified chips or modules is an important breakthrough for OBU design: it allows seamless integration of security and radio compliant, ready to use devices in the hardware platform. Doing so, time and costs associated with obtaining the

certification are dramatically reduced, focus is shifted on the actual board design neglecting the V2X radio interfaces and lastly, automotive and V2X compliance is guaranteed due to the integration of an already certified module.

These modules are extremely versatile and can be exploited as self-contained V2X SoM in OBUs as well as RSUs, Telematics Boxes and Network Access Devices.

An example is the Unex SOM-301 module that integrates the Autotalks CRATON2 communication processor and the PLUTON2 V2X/WLAN transceiver. It is designed to specifically address the rising demand for easy to use V2X units in connected vehicles. The form factor matches the PCI Express Mini Card (miniPCIe) standard and the host interface required is the USB 2.0 interface. The module relies on Linux operating system and requires both 3.3 V and 5 V voltages to function (compliant with the supply defined by miniPCIe standards).

These V2X System on Modules with miniPCIe form factor confer remarkable architectural flexibility and interoperability. They can be easily swapped with other modules to expand the board's functionality or support different communication standards, thus leading to a scalable and future proof final platform.

#### 1.2.2 Challenges and Gaps

A binding disadvantage of commercial V2X hardware solutions proposed by industries, is the non disclosure of information related to both hardware and software employed. As a consequence, customization efforts are vain since proprietary designs defy any modification and must be used as is. In addition to this, high costs are a major factor, especially when taking into account the limited customization options and the rapidly evolving market where a product could be easily discontinued and its software support may be ceased.

Open source platforms, not only allow a high degree of customization, transparency and community support, but also facilitate the adoption of V2X devices improving inter-operability. More connected devices across the network grant V2X applications access to larger amounts of real time information, thereby reaching higher success rate, accuracy and efficiency.

Taking this into consideration, the connected vehicle ecosystem demands for a low cost, open source hardware platform, interoperable, reliable, with low latency and multiple interfaces support.

#### 1.3 Thesis objective

This thesis outlines the design methodology and implementation of an embedded board for vehicular connectivity that can easily be installed on non-connected vehicles. The aim is to propose an open source OBU that answers to the lack of customization, limited number of connectors and plug-in slots for connectivity modules on commercial platforms. The board is compatible with Linux-based systems filling the gaps illustrated in the previous section. Radio interfaces are supported arranging multiple miniPCIe slots that will accommodate self contained V2X System on Modules, thus avoiding complex

certification requirements, granting flexibility and adaptability with respect to evolving standards.

#### 1.4 Document structure

A brief overview of the contents discussed in this documents is provided below. The aim is to guide the reader through the understanding of all design choices that were made to accommodate specific needs and how the final platform was implemented, starting from a set of specifications, moving on to hardware components selection and printed circuit board layout up to component placement.

- Chapter 2: focuses on pen and paper design which consists in refining the specifications, drafting the system architecture and selecting components;

- Chapter 3: schematic implementation is described and main design choices are thoroughly investigated;

- Chapter 4: covers the PCB aspects, stack-up and design rules, footprint layout, enclosure selection and details on the complete platform.

### Chapter 2

## Concept to hardware architecture definition

First and foremost, it is essential to lay out the groundwork for board development using a pen and paper approach. This chapter covers the description of several steps that led from the initial concept to the architecture of the hardware system.

A substantial part of the design process thus includes specification refinement, high level architecture draft and components selection. Ultimately, the components list and final block diagram are obtained, which serve as foundation to set up the schematic design in KiCad.

#### 2.1 Specification Refinement

The initial concept is built on a set of specifications pertaining processor performance, storage, connectivity, power supply and thermal management. Acting as a starting point for drafting the design, these features are not definite at this time, thus they are considered minimum requirements that should be met to attain performance levels demanded by the end user.

Raw specifications are summarized as follows:

- **Processor:** embedded CPU, quad-core 1 GHz equivalent or better, Linux compatible;

- Memory: 2 GB minimum, 4,8 GB of RAM is preferred;

- Storage: either SD card or SSD (SATA or PCIe interface);

- I/O two USB 3.0 connectors, one DB9 serial port (for debug and installation purposes), optional video output, multiple GPIOs (for additional sensors), three LED (status indicators and debug diagnostics), power on bi-stable switch, optional programmable buzzer;

- Power supply 12 V (passenger vehicles) or 24 V (heavy duty vehicles) DC input voltage, coin cell battery and at least two exposed 5 V power pins;

- Connectivity minimum two Gigabit Ethernet RJ45 connectors, one Automotive Ethernet 1000BASE-T1, a CAN transceiver, Integrated Wi-Fi chip supporting up to IEEE802.11ac (Wi-Fi 5) or IEEE802.11ax (Wi-Fi 6), three miniPCIe or PCIe slots (for expansion cards: vehicular Wi-Fi without SIM slot, cellular network mandatory SIM slot, C-V2X optional SIM slot);

- Thermal management and cooling system: passive cooling strategy (avoid dust, less susceptible to vibrations).

The first task involves polishing these specifications, in particular the ones regarding connector types and their respective interfaces. To illustrate, at this stage Type-A

connectors for USB interfaces and a DB9 connector for the Controlled Area Network transceiver are chosen, while the DB9 debug port is set to support UART communications over RS232 interface. The selected storage solutions include the embedded Multi Media Card, an SD card slot and an M.2 Next Generation Form Factor (NGFF) slot for an SSD with PCIe interface. Featured video output type is the High Definition Multimedia Interface (HDMI), aimed at being mostly used in a lab setup environment. All optional specifications are implemented to grant more flexibility. In addition, a reset pushbutton is included as well as SMA antenna connectors, mounted on the enclosure and connected via cable to the U.FL coaxial connector on miniPCIe radio modules fastened to their dedicated slot.

A sketch is drawn to help visualize the board concept, figure 2.1.

Figure 2.1: Board draft conceptual diagram with minimum requirements

Once this minimum requirements conceptual draft is completed, focus is shifted to the core processing element and memory subsystem.

#### 2.1.1 Core processing module: SoM selection

To simplify the design and maintain high reliability, a System on Module is adopted as embedded processing unit. Doing so, design complexity and error probability are dramatically reduced. Intricate high speed routing for DDR memory and CPU interface is avoided in conjunction with signal integrity challenges. Moreover, System on Modules help minimize development efforts thanks to pre-installed boot loaders and drivers on top of vast OS support resources. Moreover, they often embed components and subsystems such as eMMC, Wi-Fi chipsets and power management circuitry, in addition to CPU and RAM. The compact form factor makes system integration effortless and having an already validated and certified module, stability is already guaranteed under operating conditions.

Considering the previously listed requirements and application conditions, the module selected for this role is the DART-MX8M-PLUS by Variscite [30], which relies on the NXP i.MX 8M Plus System on Chip (SoC). It is worth noting that this specific SoC, as well as others from the same family, are employed in several commercial OBUs as highlighted in table 1.4.

The DART-MX8M-PLUS module is built to provide high performance while maintaining power consumption low. The set of NXP products family is the first with machine learning and artificial intelligent accelerators, making it ideal for security and time critical tasks. Product longevity is guaranteed for a 15 year period until 2036, with continuous software updates and support. Among other OSs, the module can also operate with Yocto built distributions. The Yocto project is an open source collaboration that provides tools and processes to create custom Linux-based systems in the embedded and IoT sector, regardless of the hardware architecture. The module is available in both commercial and industrial temperature range versions and Linux OS support is widely accessible through the dedicated development wiki page [31].

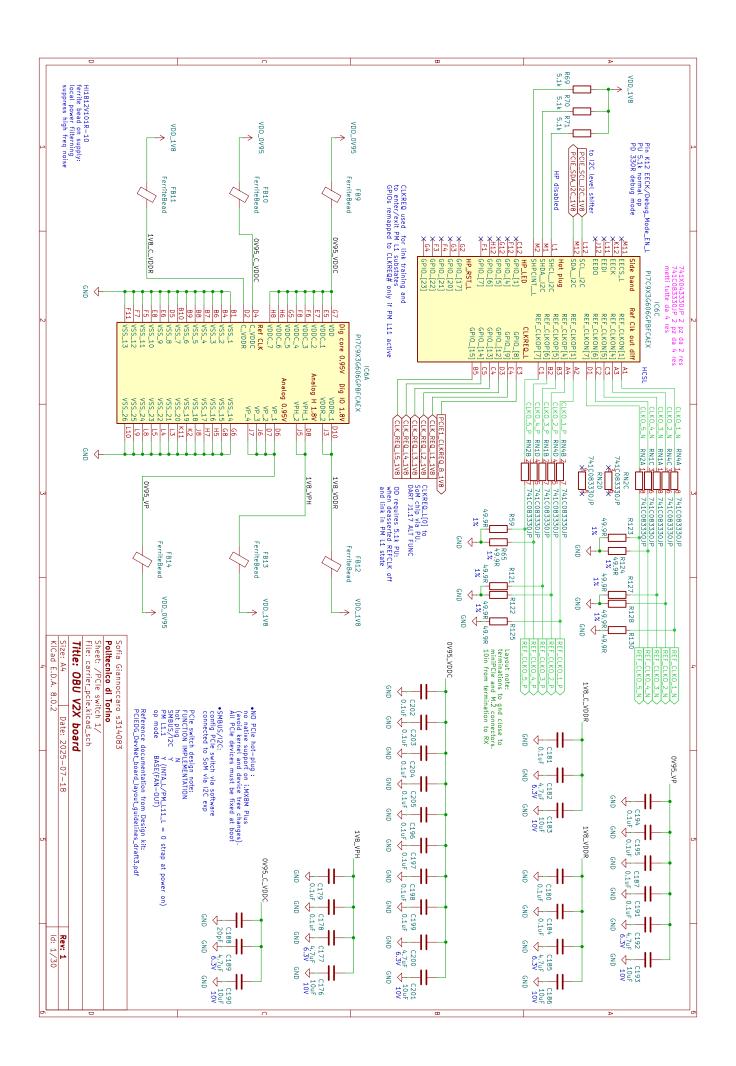

Main Features of the DART-MX8M-PLUS SoM are briefly mentioned in the following:

- NXP SoC: i.MX 8M Plus Quad core Cortex-A53 and Real Time 800 MHz Cortex-M7 co-processor;

- **Memory and storage:** configurable up to 8 GB RAM, 128 GB eMMC for high volume orders;

- Embedded subsystems: Dual band Wi-Fi 5 and Bluetooth/BLE 5.2 or Wi-Fi 6 and Bluetooth/BLE 5.4 (V2), Ethernet, Audio Codec;

- Interfaces: Display (LVDS, HDMI, MIPI DSI), Ethernet, Camera, Audio, PCIe, USB, serial (ECSPI, FlexSPI, I2C, UART, CAN, JTAG), SDIO/MMC, GPIO, PWM, timers;

- Supply voltage: 3.4 V 5 V;

- Boot loader and OS: module comes preloaded with Linux U-boot, compatible with Yocto build distributions.

Variscite also offers a specific heat sink [32] tailored for the DART SoM family, which is consistent with the passive cooling strategy adopted in the current design.

Four hardware configuration options are selectable for single unit purchase. These include version 1 or version 2 of the SoM respectively with Wi-Fi 5 and Wi-Fi 6, both available in commercial and industrial temperature range. The configuration chosen for this design is version 2 with industrial temperature range. Table 2.1 shows the selected SoM ready for purchase set up.

| DART-MX8M-PLUS V2 SoM   |                                                         |  |  |  |  |

|-------------------------|---------------------------------------------------------|--|--|--|--|

| CPU NXP i.MX 8M Plus    | CPU NXP i.MX 8M Plus   1.6 GHz Quad core Cortex-A53     |  |  |  |  |

| Real Time co-processor  | 800 MHz Cortex-M7                                       |  |  |  |  |

| RAM                     | 4 GB                                                    |  |  |  |  |

| Storage                 | 16 GB eMMC                                              |  |  |  |  |

| Integrated Wi-Fi and BT | V2: Wi-Fi 6 802.11ax, 5.4 BT (V1: Wi-Fi 5 802.11ac, 5.2 |  |  |  |  |

|                         | BT)                                                     |  |  |  |  |

| Boot loader             | SoM preloaded with Linux U-Boot                         |  |  |  |  |

| OS support              | Yocto, Debian, Boot2Qt; Android; FreeRTOS; QNX          |  |  |  |  |

| Boot sources            | Internal: eMMC; External: SD card                       |  |  |  |  |

| Temperature range       | Industrial: $-40^{\circ}C$ to $85^{\circ}C$             |  |  |  |  |

| Dimensions              | $55.0 \times 30.0 \text{ mm}$                           |  |  |  |  |

| Cost                    | 169\$                                                   |  |  |  |  |

Table 2.1: DART-MX8M-PLUS V2 ready for purchase hardware configuration

#### 2.2 Architecture Draft

Having established the minimum system requirements and chosen the core processing unit, the design is carried out analyzing how to combine the downstream connectors to the upstream SoM interfaces. The aim is to identify any mismatch in number between the upstream SoM interface outputs and downstream ports required by the specifications. When mismatch is found, it is addressed with the insertion of a Hub or switch Integrated Circuit (IC) so as to adapt the number of data interfaces to the number of available connectors on the board.

Furthermore, a DC-DC converter is picked out to step down the 12 V - 24 V input supply to 5 V and, once all the main ICs are selected, the power distribution is drafted and on board buck converters are identified. Final specifications, block diagram, a list of ICs and passive components are ultimately extracted as they define the baseline for schematic design. It should be noted that during the schematic implementation, minor adjustments will be made.

#### 2.2.1 Interfaces

Integrated Circuits selection is described in this section. Only interfaces that do need a PHY or a switch are highlighted, further information will be provided in the next chapter. In Ethernet communications, the physical layer transceiver is often referred to as PHY, it is a dedicated IC that converts data from the Media Access Control (MAC) interface into

electrical signals, matching the transmission requirements that suit the physical medium. MAC and PHY are part of the data link layer and are typical in communications interfaces such as Ethernet. Hence, the MAC is tasked with managing access to the communication medium (frame transmission, addressing and error detection), while the PHY takes care of signal conversion at the electrical level. This terminology is typically used specifically for Ethernet, other communications interfaces still employ a physical transceiver but the second layer in the structure is referred to as a controller.

Some physical transceivers and controllers are already embedded in the SoM, namely one Ethernet PHY, USB and PCIe.

#### USB

The Universal Serial Bus is serial communication standard [33] that enables data exchange between host controller and peripherals. The latest generation of the standard is the fourth, while the SoM integrates generation 3.0 and 2.0 controllers. Each one supports a different signaling rate, 5 Gbit/s Super Speed for the USB 3.0 controller and 480 Mbit/s High Speed for USB 2.0. The interface signals consist in one bidirectional differential pair of data lines (High Speed), one transmit and one receive unidirectional differential pairs (Super Speed).

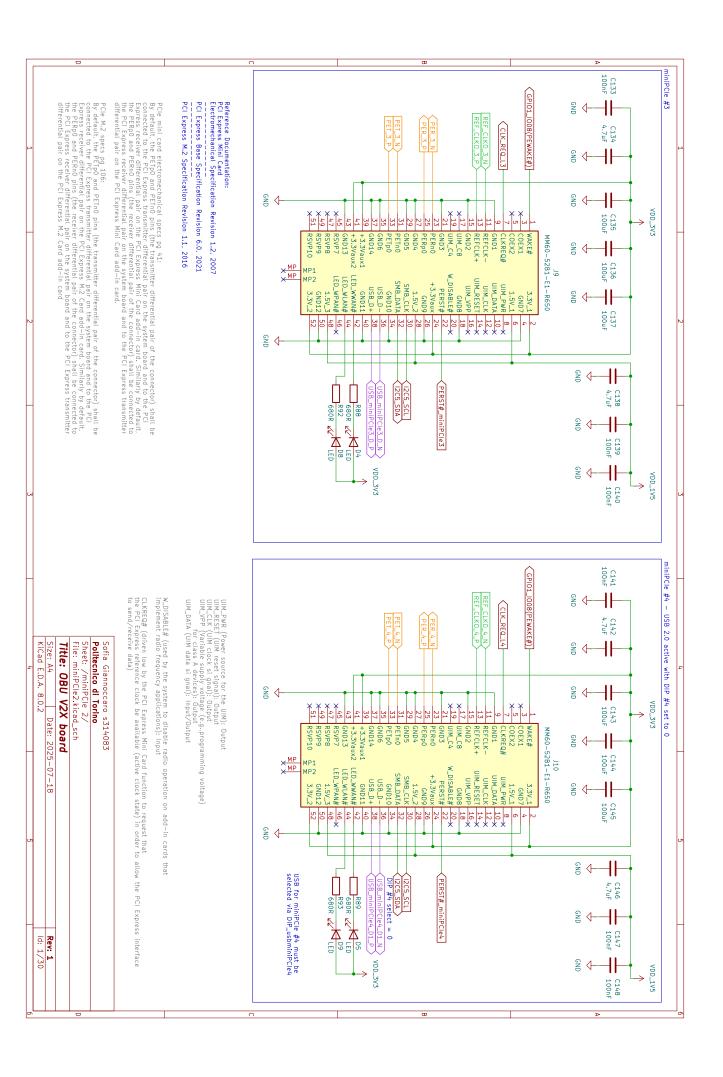

The SoM supports only two controllers with PHYs, thus a Hub IC is selected to adapt the host interface to the downstream ports needed. Two USB Hubs are employed to support eight different PHYs for four USB ports and four miniPCIe slots, starting from two host controllers on the SoM, as depicted in figure 2.2.

The four miniPCIe slots provide both USB 2.0 and PCIe buses to the add-in modules, in accordance with the miniPCIe standard [34]. Most Wi-Fi miniPCIe modules require USB 2.0 interface, as they employ Wi-Fi chipsets originally developed for USB dongles. For basic Wi-Fi 5 connectivity, the data rate theoretical speed does not exceed the 480 Mbit/s USB 2.0 speed limit, hence PCIe high speed interface is not necessary. To guarantee flexibility, all four miniPCIe slots on board support both interfaces. In order to accommodate a specific miniPCIe module with non standard pinout, USB 2.0 signals routed to the fourth miniPCIe slot are deviated to a 20-pin header meant for Flat Flexible Cable (FFC) connection, using a multiplexer picked out from a family made especially for this application, thus granting bandwidth compatibility and signal regeneration. Doing so, the integration of a non standard miniPCIe slot is avoided, while having the possibility to operate the module through the use of a dedicated adapter.

As for USB connectors instead, three USB Type A up to 5 Gbit/s and one USB Type C up to 480 Mbit/s ports are included. Battery charging (BC) capability is featured by only two ports, one Type A and one Type C. This functionality can be activated on a single port at the time using a DIP switch, preventing current overload.

The selected USB Hub is the USB5744 [35], High speed 4 ports Hub controller IC by Microchip. It supports both USB 3.0 and 2.0 signaling speeds at the same time, in addition to port power controllers. Customization is possible through bus communications or simply via resistor straps. Industrial temperature range version is available and it comes in a 56-pin Very thin Quad Flat No-lead (VQFN) package. This package type has a low profile and good thermal performance due to the exposed thermal pad underneath the

IC, that allows for direct heat transfer to the printed circuit board. Pin pads are on the bottom side of the package, which results in improved signal integrity on account of lower parasitic resistance and inductance with respect to package types where traces from pins to PCB are longer.

Figure 2.2: Block diagram detail: USB and PCIe interfaces

#### PCIe

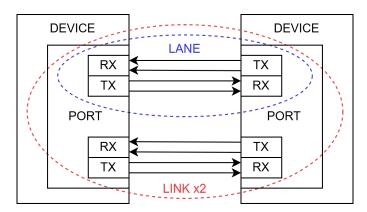

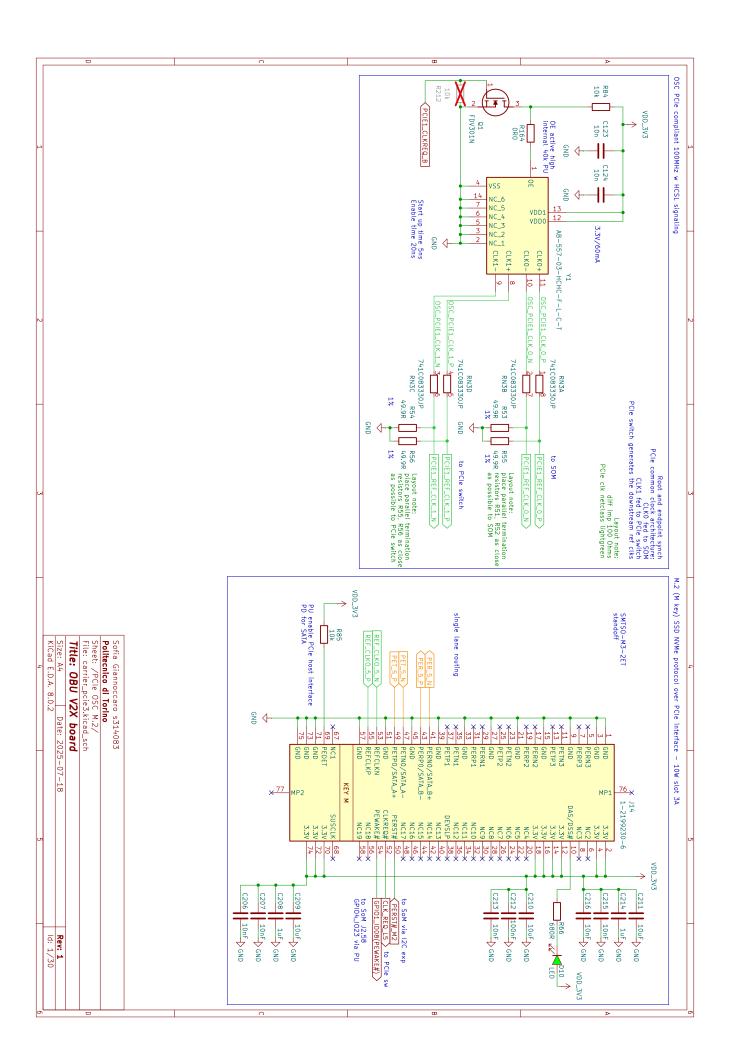

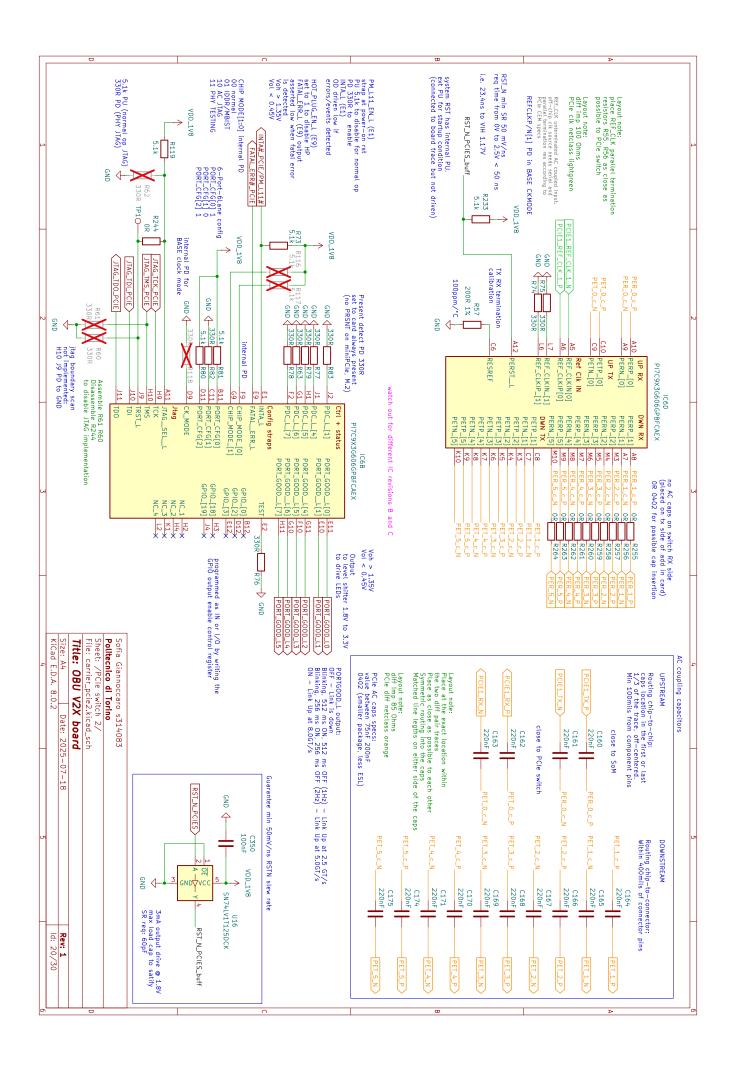

Peripheral Component Interconnect Express (PCIe) is an industrial standard for high speed communication of hardware components inside a computer. It replaces the old PCI bus interface and it's developed by PCI Special Interest Group (PCI-SIG) [36]. Each device has a dedicated connection to the host (point-to-point), data transmission is serial and is implemented with two complementary signals: when the voltage difference between the two crosses zero, data is detected, enabling precise timing even at high speeds. The topology consists of a differential pair interconnect between two devices, with a transmitter on one side and a receiver on the other. Each connection is based on two differential pairs, one intended for transmitting data and the other dedicated to its reception; this couple of differential pairs is identified as lane. Multiple lanes grouped together and connected to a single port are referred to as link, figure 2.3. Links may have different width based on the number of parallel lanes they consist in. Synchronization between transmitter and receiver is enabled by sharing the 100 MHz differential reference clock between devices.

The DART SoM supports a single lane Gen 3.0 8 Gb/s interface, including three differential pairs (transmission, reception and reference clock). The board accommodates 5 connectors supporting PCIe interface, hence a switch is employed to adapt the single

Figure 2.3: PCI Express link concept. Adapted from Board Design guidelines for PCI Express interconnect, PCI-SIG Developers Conference.

upstream lane to five downstream ports, each with single lane routing. A 6-port, 6-lane, PCIe 3.0 Packet switch by Diodes Inc. [37] is selected, it manages the reference clock integrating buffers for all downstream ports as well as PHYs. Is is programmable via several interfaces and it comes in a 144-pin Ball Grid Array package (with ball pitch 0.8 mm which allows enough routing clearance).

The system then comprises four miniPCIe slots and one M.2 slot all equipped with single lane routing, all interfacing the same switch figure 2.2. The M.2 slot is reserved for an SSD which will be mostly used for data logging, hence no bandwidth limitations are expected even in the worst case scenario where all links are active. The M.2 card follows a different set of specifications with respect to the miniPCIe modules, though still developed by the same organization [38].

The switch employed does support module hot plugging, but the option has not been enabled. Consequently, the user must restart the board to reestablish the connection once the add-in cards are swapped.

#### Ethernet

Ethernet is a wired computer networking technology frequently used in Local Area Networks (LAN) and Wide Area Networks (WAN). It is implemented in the data link and physical layers (layer 1 and 2 of the Open Systems Interconnection model [39]) and defined by the IEEE 802.3 specification [40]. With this technology data rates up to the gigabit range can be achieved over a distance of 100 m or even more if fiber optic cables are used as physical medium. Several transmission speeds and physical media interfaces exist, Ethernet families are thus identified according to the following naming convention:

$$< BitRate > < Signaling > - < Medium > < PCSEncoding > < \#Lanes >$$

To illustrate, the 1000BASE-T family name indicates a 1000 Mb/s interface with base-band signaling over twisted pair medium and blocked encoding as bit encoding scheme. This family type requires a 4-pair Category 5 unshielded twisted copper pair cable and is the one implemented in the designed board.

Ethernet PHY is divided into two main domains: Medium Independent Interface (MII) and Medium Dependent Interface (MDI). The MII comes in different variants according to speed and pin count supported, it interfaces directly with the MAC of the host device. On the other hand, the MDI connects two devices over a physical media and it is considered as the analog section of the PHY, in contrast with the MII that works in the digital domain.

The MAC to PHY connections in this design are done exploiting the Reduced Gigabit MII (RGMII) which supports speeds up to 1000 Mb/s and has a low pin count.

The DART SoM supports two controllers capable of simultaneous operation, one of which comes with an integrated PHY. The MAC interface corresponding to the integrated PHY supports both Time Sensitive Networking (TSN) and Energy Efficient Ethernet (EEE), as well as Audio Video Bridging (AVB) and the IEEE 1588 time stamping module for clock synchronization, in addition to Quality of Service (traffic prioritization), after which is labeled. Thus, the ENET\_QOS RGMII signals are connected internally on the SoM while magnetics and connectors are implemented on the carrier board. The second MAC, labeled as ENET1 in figure 2.4, is directly exposed on the SoM connectors. The corresponding RGMII signals are routed to a switch equipped with an additional RGMII interface, essential for implementing the Automotive PHY connection. Selecting an appropriate switch for this application, not only allows integration of additional Gigabit Ethernet ports with respect to the ones supported by the SoM, but also simplifies integration of the Automotive PHY.

The KSZ9567 7-Port Gigabit Ethernet Switch [41] by Microchip with five integrated PHYs and two MACs, was chosen for this design. In order to accommodate a second RGMII interface, this 7-Port switch is adopted and additional unused ports are left unconnected. It supports all features previously listed, hence its performance easily matches the one of the SoM integrated PHY.

#### **Automotive Ethernet**

Automotive Ethernet is used for in-vehicle communications, specifically to connect different ECUs. It was initially introduced to address the requirements increase both for infotainment and multimedia applications as well as higher data rates of sophisticated sensors and actuators for autonomous driving. Being a subset of Ethernet systems, it's standardized by the same IEEE 802.3 [40] specifications, though anther organization comes into play to promote its widespread adoption in the automotive industry: OPEN Alliance [42], a collaboration of mainly automotive industry that encourages adoption of Ethernet as a standard in networking applications. Automotive Ethernet follows a point-to-point topology approach, hence only two devices can be connected with a single cable. The aim is to keep the vehicle as light as possible, since multiple cables are needed to connect different sensors and ECUs. For this purpose Automotive Ethernet uses only a single twisted pair with respect to the four pairs used in standard Ethernet. They implement the same higher layer protocols but are not interchangeable at the physical level. Moreover, the communication distance is far lower than the one supported by standard Ethernet (around 15 m for passenger vehicles and 40 m for heavy duty ones).

As previously mentioned, the Automotive PHY is connected to the Ethernet switch via

Figure 2.4: Block diagram detail: Ethernet interface

RGMII interface. The selected PHY is the DP83TG721R-Q1 [43] by Texas Instruments. It supports the technology family 1000BASE-T1, requiring only a single twisted pair. Its distinctive features are 802.1AS [44] support and AVB Clock generation. The first is an adaptation of IEEE 1588 Precision Time Protocol (PTP) for real time communications and allows highly precise time synchronization between the connected devices. It is essential for Advanced Driver Assistance Systems (ADAS) and V2X critical applications, since it guarantees deterministic latency and time synchronization. On the contrary, AVB alone is suited for multimedia and infotainment systems as well as basic communications.

Regarding the Automotive Ethernet port, several connectors types can be found in the commercial market; most manufacturers offer their own proprietary solution like the H-MTD by Rosenberger [45] and MATEnet by TE Connectivity [46]. Compatibility between these connectors it not at all guaranteed; as a consequence, designing a board interoperable with devices developed by different vendors is extremely challenging. To address this problem, a common RJ45 connector is used as Automotive Ethernet port, leaving unconnected the pins reserved for the 3 twisted pairs not used by the Automotive standard. Doing so, flexibility is maintained and if a connector is standardized in the future a simple adapter to the RJ45 will grant compatibility.

#### CAN

The high speed serial communications international standard for using the Controller Area Network bus protocol is the ISO 11898 [47]. Supporting programmable data rates up to 1 Mbps, real time control and multimaster operation, it is well suited for sensors and actuators in rugged electrical environment as the automotive one.

The DART SoM includes a Flexible Controller Area Network (FLEXCAN) supporting

both CAN-FD (flexible data rate) and CAN 2.0B. An external transceiver is integrated on the carrier board, figure 2.5. The SN65HVD232 [48] operates in the common mode range of -2 V - 7 V and common mode transients are withstood up to  $\pm 25$  V. Signals interfacing with the CAN bus transceiver are only two, one for transmission and the other for reception. The transceiver output is attached to the bus lines CANH and CANL through the DB9 port with the insertion of a 120  $\Omega$  termination resistance to comply with the standard and minimize signal reflections.

Figure 2.5: Block diagram detail: CAN, RS232 interfaces

#### **RS232**

RS232 is a point-to-point communication interface that enables communication between a host and a peripheral. The bus is full duplex, meaning that it receives and transmits data at the same time. The transmitter logic level ranges from -15 V to -5 V for a logic one and from +5 V to +15 V for a logic zero. On the other hand, the receiver sensitivity is  $\pm 3$  V. The standard defines a Data Terminal Equipment (DTE) and a Data Communication Equipment (DCE). Devices in DTE configuration act as host and controller while in DCE they would be considered as peripherals. The four signals involved in the communication are labeled as TXD (from DTE to DCE) and RXD (from DCE to DTE) for data signals, RTS (Ready to Send) and CTS (Clear to Send) for control signals.

As illustrated in figure 2.5, two DB9 ports are dedicated to RS232 communication, this way one port is always available to engage in serial communications while the other is tasked with debugging. The TRSF3232E [49] is picked out as transceiver converting the UART signals outputted by the SoM into ones compliant with electrical levels specified by the RS232 standard.

#### 2.2.2 DART SoM pinout mapping

Ultimately, the SoM pinout and pinmux table attached to the documentation provided by its manufacturer, are analyzed. In particular, having selected the interfaces required on the carrier board, the corresponding SoM pins that provide these functions are identified. Most controller signals are mapped onto multiple pins and can be selected by a corresponding alternative function number with proper firmware setup. To reduce the probability of having firmware configuration issues related to signals allocation, assignment priority is given to signals mapped on pins with alternative function 0. If conflicts arise, pins are assigned to signals with higher number alternative functions.

Signal mapping onto pins is a delicate process. Thorough review is essential to avoid mistakes and obtain a balanced and coherent configuration in terms of both functional requirements and hardware constraints, while keeping peripherals configuration and initialization as simple as possible.

#### 2.3 Components selection

Component selection was conducted preferring widely available products with industrial temperature range, to ensure ease of replacement and scalability for future requirements. Board mounted connectors were chosen for enhanced stability due to their resilience to mechanical stress that is caused by frequent attaching and detaching in harsh environments.

#### 2.4 Power distribution and step down converters

Having selected the main ICs, they can now be sorted into categories with respect to the voltage supply range they require, based on the data extracted from their datasheet summarized in table 2.2. The ICs grouping depends on the required maximum tolerance on a specific supply, which is identified during this step and the maximum acceptable tolerance of the several buck converters is thus obtained. To illustrate, the USB Hub, Ethernet switch and Automotive PHY supply voltages intersect in the range 1.14 V - 1.21 V, thus, in order to have a common supply rail to all three of them, the respective step down converter must be very accurate. A DC-DC with 1% output accuracy is indeed chosen. In addition to the modules listed in table 2.2, plug-in cards must also be taken into account. These include four miniPCIe modules, two SIM cards and one M.2 SSD. Their contribution is reported in table 2.3. The SD card voltage is instead provided by the SoM directly, hence its contribution is not relevant in this context.

Once the modules are properly categorized and the final supply voltages that need to be derived on the carrier board are determined, the total current per supply is evaluated. The aim is to extract from this data a rough estimate of the worst case current that a voltage supply must be able to provide during typical operating conditions. Knowing the required current, suitable buck converters can then be picked out; refer to table 2.4. Further ICs and components are added later on during the schematic design stage but since their current draw is minimal, they have negligible impact on the overall current required on a specific voltage rail and are thereby omitted in the calculation.

Power distribution is shown in figure 2.6. The main supply rail is the 5 V, from which all other voltages are derived. This rail feeds all 5 V devices on board, the DART SoM and the buck converters. However, it is important to recall that the input voltage required by the specifications denoted in section 2.1 is 12 V - 24 V. The strategy chosen then involves using an external enclosed DC-DC converter to step down the voltage

| SoM                                         | Voltage supply [V]                                                                                     | Current supply [A]                                                                                                         | Notes                                                               | Qty |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|

| DART-MX8M-<br>PLUS V2                       | 3.5-5                                                                                                  | 0.73 @ 3.826 V,<br>0.56 @ 5 V                                                                                              | 2.79 W @<br>3.826 V                                                 | 1   |

| Embedded<br>module                          | Voltage supply [V]                                                                                     | Current supply [A]                                                                                                         | Notes                                                               | Qty |

| RTC<br>DS1337U+                             | 1.8-5.5, typical 3.3                                                                                   | $150~\mu$                                                                                                                  | draws from external battery                                         | 1   |

| CAN Transceiver<br>SN65HVD232QDR            | 3-3.6 (3.3±10%)                                                                                        | maximum 17 m,<br>typ. 10 m @ 3.3 V                                                                                         | x2 driver and<br>receiver                                           | 1   |

| I2C Expander<br>PCAL6408APWJ                | 1.65-5.5                                                                                               | 0.75 m                                                                                                                     | with pullups<br>enabled                                             | 2   |

| USB HUB<br>USB5744-I/2G                     | 1.2 ±10% (1.08-<br>1.32),<br>3.3 ±10% (3-3.6)                                                          | 93 m @ 3.3 V<br>688 m @ 1.2 V                                                                                              | 4 SS/HS ports.<br>BC supported                                      | 2   |

| PCIe Switch<br>PI7C9X3G606GP                | VDDC: 0.95±5%;<br>CVDDC:<br>0.95±5%;<br>VDDR: 1.8±5%;<br>CVDDR: 1.8±5%;<br>VP: 0.95±5%;<br>VPH: 1.8±5% | 5 @ VDDC,<br>0.02 @ CVDDC,<br>0.02 @ VDDR,<br>0.07 @ CVDDR,<br>0.54 @ VP,<br>0.13 @ VPH                                    | worst case<br>current values,<br>highest tem-<br>perature, 5.7<br>W | 1   |

| Gigabit Ethernet<br>switch<br>KSZ9567R      | VDDIO:<br>3.3, 2.5, 1.8±5%;<br>AVDDH:<br>2.5±5%;<br>AVDDL: 1.2±5%;<br>DVDDL: 1.2±5%                    | $I_{DDAH}$ 330 m,<br>$I_{DDIO}$ 80 m,<br>$I_{DDCA}$ 460 m,<br>$I_{DDCD}$ 750 m,<br>with<br>AVDDH @ 2.5 V,<br>VDDIO @ 3.3 V | full 1 Gbps operation all ports.                                    | 1   |

| Automotive<br>Ethernet PHY<br>DP83TG721R-Q1 | VDDA3P3V: 3.3±10%; VDDIO: 3.3±5%, 2.5±10%, 1.8±10%; VSLEEP: 3.3±10%; VDD: 1.05-1.21 (1.13±7%)          | 40 m @ VDDIO<br>3.3 V,<br>89 m<br>@ VDDA3P3V,<br>1.5 m @ VSLEEP,<br>250 m @ VDD                                            | active mode @ VDDIO 3.3 V. DP83TG720R-Q1 model used as reference    | 1   |

| RS232 Transceiver<br>TRSF3232E              | $5, 3.3 \pm 10\%$                                                                                      | 1 m                                                                                                                        |                                                                     | 2   |

Table 2.2: SoM and ICs: typical operating voltage and current supply. Operating mode selected is the one that requires higher supply values.

| Peripheral/    | Voltage supply       | Current supply    | Notes          | Qty |

|----------------|----------------------|-------------------|----------------|-----|

| plug-in card   | [V]                  | [A]               |                |     |

| USB type A 3.0 | 5 V                  | 0.9 A HP SS; 150  | 1 port USB     | 4   |

|                |                      | mA LP SS; 0.5 A   | type A USB     |     |

|                |                      | USB 2.0, 1.5 A    | 3.0 BC consid- |     |

|                |                      | USB 3.0 BC        | ered           |     |

| miniPCIe       | $3.3\pm 9\%$ ,       | 1100 mA (2750     | latest is 2.1. | 4   |

|                | $1.5\pm5\%$          | mA) normal        | 7.5 W per      |     |

|                |                      | (peak) @ 3.3 V;   | slot (man-     |     |

|                |                      | 375 mA (500 mA)   | ufacturers'    |     |

|                |                      | normal (peak)     | limit)         |     |

|                |                      | @1.5 V            | ·              |     |

| SIM            | $5\pm10\%$ class A   | 60 m              | asynchronous   | 2   |

|                |                      |                   | cards (also    |     |

|                |                      |                   | class B 3 V,   |     |

|                |                      |                   | class C 1.8 V) |     |

| M.2 NVMe SSD   | $3.3\pm 9\%$ ,       | 3 A @ 3.3 V for a | latest is re-  | 1   |

|                | $3.3$ Vaux $\pm 9\%$ | 10 W slot         | vision 6.      |     |

|                |                      | estimated: 1 A (3 | Optional Vaux  |     |

|                |                      | W)                | is needed for  |     |

|                |                      |                   | wake signal    |     |

Table 2.3: Peripherals: typical operating voltage and current supply. Operating mode selected is the one that requires higher supply values.

| Voltage    | Current    | Total power              | DC-DC      | Specs    |

|------------|------------|--------------------------|------------|----------|

| supply [V] | supply [A] | $\mid [\mathbf{W}] \mid$ | converter  |          |

| 5          | 4.8        | 24                       | RSD-60G-5  | 2%, 12A  |

| 3.3        | 5.8        | 19                       | TPS6286A08 | 0.7%, 8A |

| 2.5        | 330m       | 0.83                     | TPS62827AD | 1%, 4A   |

| 1.8        | 0.22       | 0.4                      | TPS62827AD | 1%, 4A   |

| 1.5        | 1.5        | 2.25                     | TPS62827AD | 1%, 4A   |

| 1.2        | 2.8        | 3.4                      | TPS62827AD | 1%, 4A   |

| 0.95       | 5.56       | 5.3                      | TPS6286A08 | 0.7%, 8A |

Table 2.4: Board current drawn per power supply and step down converters

and feed 5 V to the board while providing all the necessary protections for automotive applications. Therefore, a DC jack is mounted on the enclosure and it accepts a voltage in the range defined by the enclosed DC-DC converter input. An anti-vandal pushbutton with integrated LED is used to disconnect the converter from the input power acting as a power on switch for the board. On the other side, the DC-DC output is attached to wires terminated with a connector that mates with the one on the PCB. On the board, a simple two terminal block header able to withstand the needed current is used, thus

providing a secure and easily pluggable interface between the  $5~\mathrm{V}$  rail on the PCB and the wiring of the external DC-DC converter.

Figure 2.6: Block diagram detail: power distribution

Before focusing on the integrated DC-DC converters, let's discuss the reasons why an external enclosed DC-DC converter was chosen to provide the 5 V power to the board. Most importantly, enclosed converters often include built in protections that in solderable buck converters have to be implemented externally using additional chips or components. Robust and reliable protections are a key aspect in automotive applications in order to prevent the downstream system from being damaged. Common protection mechanisms are Under Voltage Protection (UVP), Over Voltage Protection (OVP), Over Current Protection (OCP), short circuit and reverse polarity protection. Moreover, enclosed converters are thoroughly tested for isolation, electromagnetic interference, mechanical stress and correct operation across the allowed temperature range. On top of these benefits employing an external converter brings additional flexibility to the design: it can be easily swapped in case more power is needed or replaced if damaged.

The railway-grade 60 W enclosed converter used to step down the voltage and supply the board is the RSD-60G-5 by MEAN WELL [50], figure 2.7. It is perfectly suited for this application, being specifically implemented for transportation systems. The 9 V $\rightarrow$ 36 V wide input range facilitates system operation across multiple vehicle types, such as passenger and heavy duty vehicles (trucks, buses, construction machinery). It features reinforced isolation and it can be used in environments subject to dust, vibration and strong temperature gradients thanks to the semi-potted silicone interior.