### Politecnico di Torino

A.a. 2024/2025 Graduation Session September 2025

# Accelerating the reliability assessment of hardware accelerators through emulation using hyperscale systems

Master of Science Thesis

Professors: Candidate:

Matteo Sonza Reorda Juan David Guerrero Balaguera Berkay Demir

#### Abstract

Faults within the hardware accelerators compromise the reliability of the entire system. In the case of a system failure, the more complex the system becomes, the more difficult it becomes to diagnose the origin of the faults. The location of the fault also becomes a critical issue. A fault located near or on the critical path results in a much higher divergence from the correct result and optimal performance. To analyze hardware accelerators for specialized needs, they are tested using different fault models to measure the effect on the performance of the system during the manufacturing stage.

This thesis provides a comprehensive analysis on the emulation of hardware accelerators with fault injection capabilities on an FPGA fabric. In order to increase time efficiency, the control of the fault injection campaign is done through the design of a dedicated hardware controller. The integration for fault injection is developed for fault characterization within reasonable time frames, since software control of the module spends critical execution time.

The research methodology follows a systematic approach, beginning with analysis and background research on the saboteur insertion framework within the hardware accelerators to develop fault injection capabilities. The framework of saboteur circuits is meticulously implemented in an interconnected chain architecture. This saboteur structure includes multiple fault models such as stuck-at-1, stuck-at-0 and transient faults. The configuration is made through a shift register scan chain, pushing an array of values through them inside the saboteur circuits for mode selection and bit activation.

The second contribution is the development of a fault injection controller circuit that decreases the fault emulation time. The connections for the control of the circuit are designed according to the specifics of the Wishbone B4 bus interface. The Verilog controller is developed to manage the modification and configuration of the shift registers and the activation of entire scan chains on different hardware cores, utilizing the same fault configuration of the scan chain shift registers. Through its finite-state machine, the controller handles status reporting through its bus interface, fault injection through its serial data output, and immediate and delayed fault activation for the configuration of the entire scan chain. The controller utilizes memory-mapped registers in order to program and modify different chain lengths for different hardware, making its use much more viable for hardware with the same scan chain configuration, with less memory use.

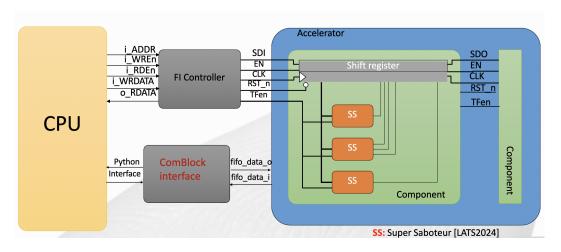

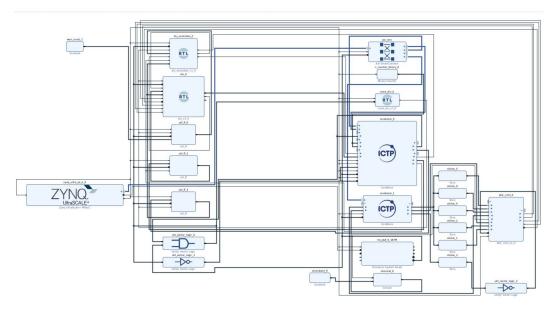

The third contribution is the integration of a hardware accelerator with an inbuilt scan chain to the saboteur control circuit and emulation on the HyperFPGA platform. The HyperFPGA system features hardware resources that are necessary

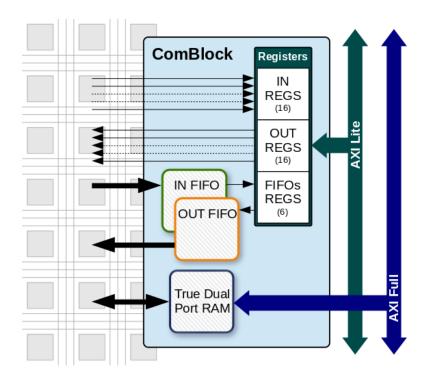

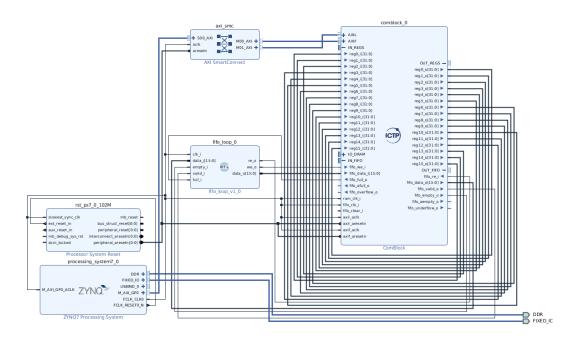

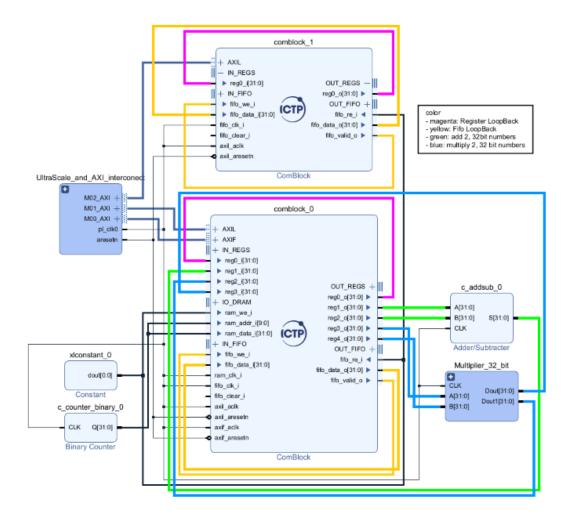

for the emulation of the system. The connection between the system and the hardware is made possible through ComBlock communication interface, an IP core that connects the gate array's server programming to the stereo-core hardware. The ComBlock provides multiple communication interfaces that include register-based, a dual port RAM and asynchronous First In, First Outs (FIFOs) for streaming data transfers.

The last contribution is to emulate 4 other hardware accelerators for evaluation of the results to be used as a benchmark. The hardware accelerators to be used in the test are a Tensor Core Unit, a Stereo Core accelerator based on census transform, a CORDIC Special Function Unit core and a Special Function Unit that calculates trigonometric functions. A brief overview of the benchmarks and results of these is analyzed, while giving specifications on which parts of the chain the faults are implemented, the difference between them and effects of different fault models on the results are evaluated. The results show a significant boost in speed compared to traditional fault injection and highlights the efficiency of the controller.

### Table of Contents

| Li | st of                  | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5           |

|----|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Li | $\operatorname{st}$ of | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7           |

| 1  | Intr<br>1.1<br>1.2     | Oduction Goal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8<br>9<br>9 |

|    | 1.2                    | Structure Of The Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Э           |

| 2  | Bac                    | ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11          |

|    | 2.1                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11          |

|    |                        | 2.1.1 Hardware Faults in Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11          |

|    | 2.2                    | Fault Emulation Using Saboteur Infrastructures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14          |

|    |                        | 2.2.1 Basic Saboteur and Scan Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14          |

|    |                        | 2.2.2 FPGA-Based Emulation Platform and Communication In-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

|    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16          |

|    |                        | 2.2.3 Integration with Hardware Accelerators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20          |

| 3  | Des                    | gn and Implementation of the Saboteur Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22          |

|    | 3.1                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22          |

|    | 3.2                    | The Wishbone BUS Protocol and Finite State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23          |

|    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23          |

|    |                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24          |

|    |                        | O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27          |

|    |                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28          |

|    |                        | 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30          |

|    |                        | O Company of the comp | 31          |

|    | 0.0                    | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33          |

|    | 3.3                    | Simulation-Based Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34          |

| 4  | Imp                    | lementation and Emulation in HyperFPGA System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36          |

|    | 4.1                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36          |

| Bi | iblios | raphy                                       | 77 |

|----|--------|---------------------------------------------|----|

|    | 6.1    | Future Work                                 | 75 |

| 6  | Cor    |                                             | 74 |

|    | 5.5    | Special Functions Unit 2                    | 68 |

|    | 5.4    | 1                                           | 63 |

|    | 5.3    | Stereo Vision Core                          | 58 |

|    | 5.2    | 1                                           | 53 |

|    | 5.1    | Introduction                                | 52 |

| 5  | Res    | ults                                        | 52 |

|    |        | 4.3.6 Summary of Findings                   | 51 |

|    |        | 4.3.5 Verification and Accuracy             | 50 |

|    |        | 4.3.4 Timing Analysis                       | 49 |

|    |        | 4.3.3 Power Consumption Analysis            | 48 |

|    |        | 4.3.2 Resource Utilization Analysis         | 47 |

|    |        |                                             | 42 |

|    | 4.3    |                                             | 42 |

|    |        | 4.2.2 Software Control Layer Implementation | 37 |

|    |        | 4.2.1 Data Flow and Control Path            |    |

|    | 4.2    | System Architecture Overview                | 36 |

### List of Tables

| 3.1  | Detailed RTL Compilation and Simulation Performance Metrics        | 34 |

|------|--------------------------------------------------------------------|----|

| 4.1  | Python configuration of pattern generation                         | 40 |

| 4.2  | JSON Structure and Hardware Hierarchy                              | 41 |

| 4.3  | Hardware Performance Comparison: Pure Execution (Posit Adder       |    |

|      | Accelerator Benchmark)                                             | 43 |

| 4.4  | Fault Injection Configuration Performance (Posit Adder, 392-bit    |    |

|      | Scan Chain)                                                        | 44 |

| 4.5  | FPGA Single Fault Injection: Detailed Time Breakdown (Posit        |    |

|      | Adder Benchmark)                                                   | 45 |

| 4.6  | Complete Fault Campaign Performance (Posit Adder, 392 Faults) .    | 45 |

| 4.7  | Optimization Potential Analysis (Based on Posit Adder Results)     | 46 |

| 4.8  | FPGA Resource Utilization Summary                                  | 47 |

| 4.9  | System Resource Utilization (Posit Adder Benchmark)                | 47 |

| 4.10 | Power Consumption Analysis (Posit Adder System)                    | 48 |

| 4.11 | Scan Chain Module Timing (Posit Adder Modules)                     | 49 |

|      | High Fan-out Net Distribution                                      | 50 |

| 4.13 | Verification Coverage (Posit Adder Benchmark)                      | 50 |

| 4.14 | Key Findings Summary                                               | 51 |

| 5.1  | FPGA Resource Utilization for TCU Implementation                   | 54 |

| 5.2  | Detailed Module-Level Resource Allocation of TCU Implementation.   | 54 |

| 5.3  | On-Chip Power Distribution Analysis of TCU Implementation          | 55 |

| 5.4  | Clock Network Utilization and Timing of TCU Implementation         | 55 |

| 5.5  | Fault Injection Performance Comparison for TCU: Bit-Banging vs     |    |

|      | Hardware Controller                                                | 56 |

| 5.6  | Timing Path Characteristics of TCU Implementation                  | 57 |

| 5.7  | FPGA Primitive Utilization Summary in TCU Implementation           | 57 |

| 5.8  | Design Complexity and Verification Coverage of TCU Implementation. | 58 |

| 5.9  | FPGA Resource Utilization for SVC Implementation                   | 59 |

| 5.10 | Detailed Module-Level Resource Allocation of SVC Implementation.   | 59 |

| 5.11 | On-Chip Power Distribution Analysis of SVC Implementation           | 60 |

|------|---------------------------------------------------------------------|----|

| 5.12 | Clock Network Utilization and Timing of SVC Implementation          | 61 |

| 5.13 | Fault Injection Performance Comparison for Stereo Vision Core:      |    |

|      | Bit-Banging vs Hardware Controller                                  | 61 |

| 5.14 | Critical Timing Path Characteristics of SVC Implementation          | 62 |

| 5.15 | FPGA Primitive Utilization Summary of SVC Implementation            | 62 |

| 5.16 | Design Complexity and Verification Coverage of SVC Implementation.  | 63 |

| 5.17 | FPGA Resource Utilization for SFU1 Implementation                   | 64 |

| 5.18 | Detailed Module-Level Resource Allocation of SFU1 Implementation.   | 64 |

| 5.19 | On-Chip Power Distribution Analysis of SFU1 Implementation          | 65 |

| 5.20 | Clock Network Utilization and Timing of SFU1 Implementation         | 65 |

| 5.21 | Fault Injection Performance Comparison for SFU-Trigonometric:       |    |

|      | Bit-Banging vs Hardware Controller                                  | 66 |

| 5.22 | Timing Path Characteristics of SFU1 Implementation                  | 66 |

| 5.23 | FPGA Primitive Utilization Summary of SFU1 Implementation           | 67 |

| 5.24 | Design Complexity and Verification Coverage of SFU1 Implementation. | 68 |

| 5.25 | FPGA Resource Utilization for SFU2 (CORDIC Core) implementation.    | 69 |

| 5.26 | Detailed Module-Level Resource Allocation of SFU2 implementation.   | 69 |

| 5.27 | On-Chip Power Distribution Analysis of SFU2 implementation          | 70 |

| 5.28 | Clock Network Utilization and Timing of SFU2 implementation         | 70 |

| 5.29 | Fault Injection Performance Comparison for SFU-CORDIC: Bit-         |    |

|      | Banging vs Hardware Controller                                      | 71 |

| 5.30 | Timing Path Characteristics (Worst Path) of SFU2 implementation.    | 72 |

| 5.31 | FPGA Primitive Utilization Summary of SFU2 implementation           | 72 |

| 5.32 | Design Complexity and Verification Coverage of SFU2 implementation. | 73 |

### List of Figures

| 2.1  | Stuck-at-0 model [1]                                              | 13 |

|------|-------------------------------------------------------------------|----|

| 2.2  | The simulation mechanism used for observing the effects of an SEU |    |

|      | bit-flip [2]                                                      | 14 |

| 2.3  | The HyperFPGA [7]                                                 | 17 |

| 2.4  | Comblock model [9]                                                | 19 |

| 2.5  | Comblock model [9]                                                | 20 |

| 2.6  | ComBlock baseline implementation                                  | 21 |

| 3.1  | Proposed design for FI controller                                 | 22 |

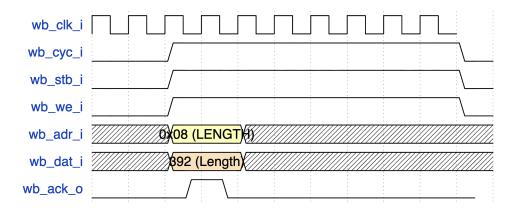

| 3.2  | Basic write operation                                             | 24 |

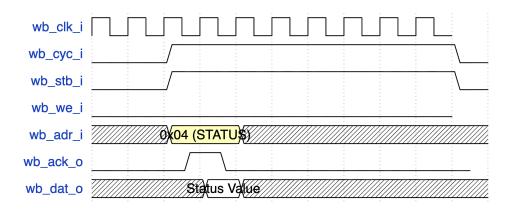

| 3.3  | Basic read operation                                              | 24 |

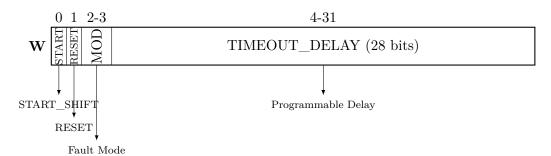

| 3.4  | Bitfield Layout of the CONTROL Register (Address 0x00)            | 25 |

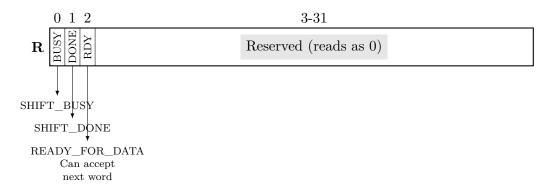

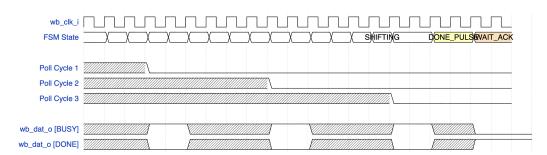

| 3.5  | Bitfield Layout of the STATUS Register (Address 0x04)             | 26 |

| 3.6  | FSM states for status polls after shifting                        | 26 |

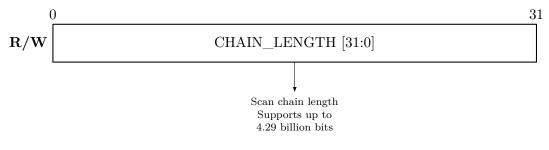

| 3.7  | Bitfield Layout of the LENGTH Register (Address 0x08)             | 26 |

| 3.8  | Bitfield Layout of the DATA Register (Address 0x0C)               | 27 |

| 3.9  | FSM design for saboteur controller                                | 28 |

| 3.10 | Configuration handshaking for data loading                        | 29 |

| 3.11 | Activate data shifting                                            | 30 |

| 3.12 | FSM state transition during partial shift                         | 31 |

| 3.13 | Synchronization for fault enable signal                           | 31 |

| 3.14 | immediate fault activation                                        | 32 |

|      | Delayed fault activation                                          | 32 |

|      | Reset operation being sent to controller                          | 33 |

| 4.1  | Hardware implementation of the test system                        | 42 |

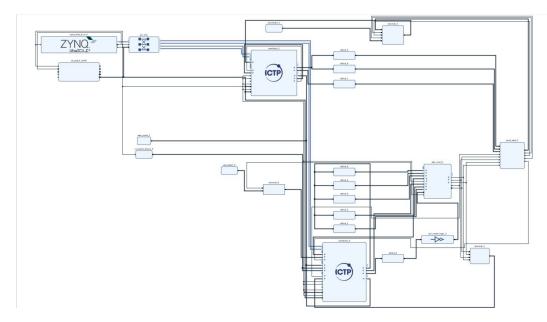

| 5.1  | Tensor Core Unit Implementation                                   | 53 |

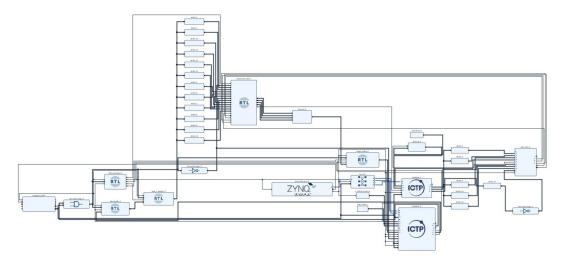

| 5.2  | Stereo Vision Core Implementation                                 | 58 |

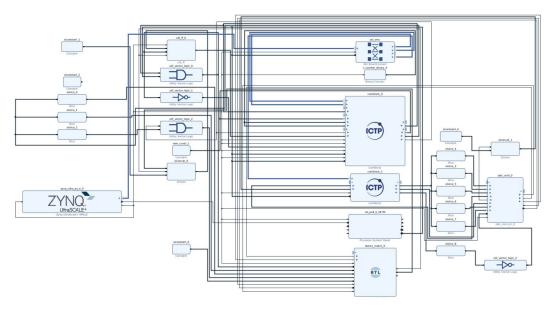

| 5.3  | Special Function Unit Implementation                              | 63 |

| 5.4  | Special Function Unit Implementation                              | 68 |

### Chapter 1

### Introduction

Ever increasing diversity within the modern computing systems took a different path from central processing units to more specialized hardware accelerators to meet the demanding performance and energy efficiency requirements of emerging applications. From autonomous vehicles processing stereo vision data in real-time to data centers accelerating machine learning workloads, hardware accelerators have become essential components of computing infrastructure. The complexity of these systems that stem from ever more advancing needs increased the need to test the reliability of these specialized circuits.

In order to understand how a system works and how reliable it would be, engineers have tried to model the defects that can arise within the systems. As more and more circuits are manufactured and used, the assessment of reliability became even more necessary. These defects would be named as faults within the hardware. Reliable operation in the presence of hardware faults has been tested in manufacturing processes for decades.

The basic way to fault models within a system would be to use software simulators running VHDL or Verilog hardware in order to evaluate the effects without going through emulation on programmable field arrays or gate arrays. This procedure provides basic observability of fault effects on the system reliability; however, the actual hardware would be more prone to fault defects as simulation works on perfect environments, not taking into account any component effects and real-life scenarios such as clock jitters or thermal effects. The second limitation on characterizing the effects of faults is the simulation speed. In a comprehensive reliability test, different fault models would be used to test out different fault injection places that can cover up to a thousand potential injection points, leading to multiple hours of simulation time. Simulation time that is not feasible in real-life scenarios where some high-level systems can reach millions.

### 1.1 Goal

This thesis establishes a practical, scalable methodology for reliability evaluation and simulation time of hardware accelerators, contributing practical hardware tools to advance the field of reliability evaluation. The developed framework enables faster transition from simulation evaluation to emulation on hyperscale FPGA systems. The goal is to accelerate the reliability assessment of hardware accelerators through newly developed hardware in emulation. In order to achieve this, a controller module has been developed. The dichotomy of slow software, fast hardware is a specific issue. Rather than the modification and activation being achieved through the software, this controller serves as a bridge in emulation timing reduction. This way, achievement of the speedup of the fault injection process increases dramatically.

### 1.2 Structure Of The Thesis

This thesis is organized in 6 chapters. The first chapter is the introduction, giving a fairly well established beginning to the thesis. This chapter also introduces the motivation, establishing the need for this work, and the general structure of this thesis.

The second chapter provides the necessary theoretical foundation needed for understanding the work done in this thesis. Starting with an explanation of faults and fault models, focusing on stuck-at-1, stuck-at-0, and bit-flip models, it further dives deep into their theoretical models to showcase how they are affecting a system in their respective models in general. Furthermore, this chapter explains the fault injection scan-chain design and the hardware for disrupting the output of basic nets. The theoretical model of the circuit is explained methodically for further understanding how fault methodology works in this thesis. Finally, this chapter dives into the hyperscale fabric we emulated our design in, the HyperFPGA design, a cloud-based FPGA infrastructure featuring Zynq UltraScale+ devices provided by Multidisciplinary Laboratory (MLAB) and the ComBlock communication infrastructure developed by MLAB/ICTP that provides register-based control for efficient software-to-FPGA communication.

The third chapter presents the design of the saboteur controller, the critical hardware module that is specialized in speeding up the fault injection and activation. The chapter provides the necessary explanations for the development of such a module, by explaining how the mechanism works with small segments of code attached to it. Utilizing the Wishbone B4 BUS interface, it implements a slave interface with a master connection coming from the software. Using continuous interaction from the software by synchronized fault injection using 32-bit registers,

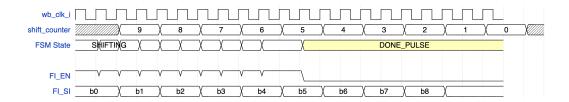

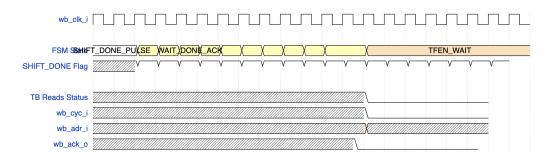

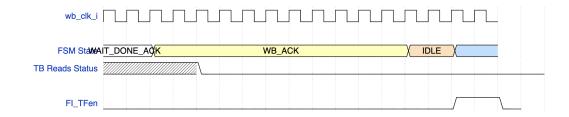

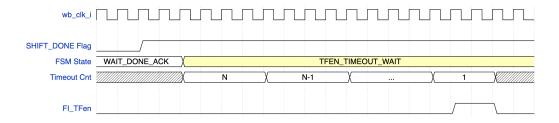

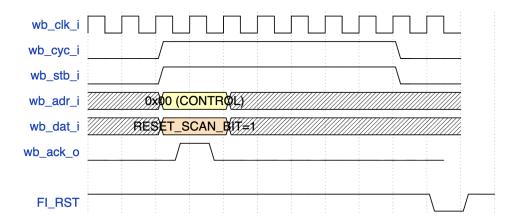

data streaming to the fault interface increases in speed because of the fast hardware clock, rather than slow software interaction. The nine state machine is thoroughly analyzed, giving the user an in-depth understanding of the algorithm behind the single cycle precision fault injection and activation. Throughout this chapter, Verilog-based timing diagrams are provided to give a better understanding to the reader.

The fourth chapter provides the entire software and hardware configuration, detailing how the FPGA frame is used in order to emulate the system. The details of the system and the methodology behind the Python scripts are explained. The integration of the system on the HyperFPGA platform is given, detailing how ComBlock and the system clock are utilized to target the accelerators on a posit adder accelerator. The Jupyter network interface is explained on how to enable the fault campaign. The results of both the software simulation and hardware emulation are presented with tables.

The fifth chapter presents the comprehensive evaluation of the results using four different hardware accelerators as benchmarks to validate the framework's efficiency. Building upon the previous chapter, the benchmark accelerators are a Tensor Core Unit, a Stereo Core accelerator based on census transform, a Special Function Unit core that calculates trigonometric functions, and a Special Function Unit core that implements the general CORDIC algorithm. The results are presented in nine tables, diving from resource allocation, power usage to timing analysis.

The sixth chapter provides the conclusion and future work of this thesis. Starting with a small summary of the problems and achievements at hand, it concludes the previous work by summarizing the key results achieved throughout the previous chapters and explaining the limitations. Finally, ideas for future work are explained, such as software and hardware optimizations.

### Chapter 2

### Background

### 2.1 Introduction

In this chapter, background research for the development of the thesis will be provided, starting with a focus on the theoretical aspects of the faults within the circuits that will be instrumental in this work. To provide a comprehensive understanding of the work done in this thesis, a deep dive into the fault mechanism, the classifications of faults and the differences between them, and modeling methods will be thoroughly explained. Secondly, to demonstrate how modern design testing works, the scan chain architecture and the basic building blocks that are used will be explained. Lastly, to give a background on the emulation fabric, the hardware ComBlock for the communication between software and the hardware HyperFPGA for emulation will be explained in an explicit way.

### 2.1.1 Hardware Faults in Digital Systems

#### **Fundamental Concepts and Classification**

The ever increasing complexity within the systems, due to the shrinking transistor sizes, resulted in the need for much heavier testing to ensure reliable operation under variable situations. The concept of fault revolves around the idea of defects in the hardware operating cycle. A fault is a defect within the system hardware that causes unwanted responses and deviations from the expected result of a digital system. Faults are classified by their duration. Three categories that this work takes into account can be classified: permanent, intermittent, and transient faults. Permanent faults are, as indicated, lasting throughout the operational lifetime of the device and require physical replacement of the part or parts. They usually stem from hardware defects during manufacturing processes such as open and short circuits in the vias. Another common occurrence in which the fault occurs is

during electromigration, where conductor atoms break apart and migrate during high-current-density scenarios.

However, an intermittent fault is classified as a malfunction that occurs at irregular intervals in a device that can function regularly. Harder to diagnose because during the testing stages, the operation can commence and end fault-free. The most prominent reason for these types of faults is environmental effects such as the variation of temperature during operation. The transistor voltages within the system can fluctuate during thermal expansion, leading to operational failures. Because of this unpredictable nature, specialization and multiple runs for testings are usually needed for full fault coverage.

A transient fault is a malfunction that is relatively short within the system operation time. It can be seen in the circuits that utilize smaller architectures with fluctuating small voltage levels in sensitive nodes, mostly from electromagnetic interference. Mostly problematic for true data transmissions, these types of fault can disrupt the normal operation of digital hardware.

#### Fault Modeling and Fault Testing

During the testing phase of many hardware, in order to simulate the defects that will inevitably arise from faults, engineers have come up with a terminology in order to model the effect to be seen. Fault modeling is the development of intentional system failure in order to simulate actual physical defects within a system as a logical model. With the exponential growth of hardware in the 21st century, this resulted in development of different abstraction levels, mainly gate-level modeling and transistor-level modeling. The reason for the development of these levels stems from the tradeoff between high accuracy and computational difficulty. Transistorlevel fault modeling has been the go-to for simulating faults within individual transistors. Stuck in a transistor model means a permanent conducting transistor or an open circuit transistor independent of the gate and drain voltage. The benefit of having a comprehensive fault analysis gives many statistics on effects of faults, however, this detailed analysis also comes at a computational expense. In order to find a medium, gate-level fault models are developed to provide a higher level of abstraction for analyzing faults on digital circuits. Rather than per transistor, the work details the logic gates and their changing responses. The most common among them is the stuck-at-fault model. During this work, this model will be extensively used to modify the circuit response to compare speed between simulation and emulation. For further analysis, the stuck-at concept will be extended to transition fault models in order to capture timing-related defects by modeling faults that prevent or delay signal transitions. Path-delay fault models consider the cumulative effect of small delays along critical paths that can cause timing violations without affecting the logical functionality.

#### Stuck-At Fault Model

The stuck-at-fault model is designed to fix a node to be permanently grounded (stuck-at-0) or supplied (stuck-at-1). It is the most common fault model to be used for it's simplicity to design and comprehensive and detailed simulation for behavioral results. In gate-level modeling, the fault is simulated to occur on the output of gates or in signal lines. In order to maintain simplicity within fault analysis, the assumption to be made is that only a single fault is active within the circuit. In a circuit with n signal lines, 2n stuck-at faults can exist. The difference between the fault-free model result and the injected fault result is then compared, giving a comparison metric that calculates the deviation from the result between all 2n faults within the system. In this way, the critical nodes that have a higher deviation rate can be observable. Thanks to modeling, in case of real-time fault, faulty gates, signal lines, transistors, and vias can be identified.

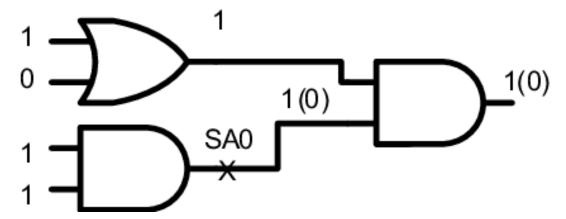

Figure 2.1: Stuck-at-0 model [1].

The current stuck-at-0 model shown in the Figure 2.1 takes the test sequence (1,0,1,1) to its ports. This results in a fault excitement on the signal. The AND gate 1 output expected to be 1, resulted in 0. The expected result on the AND gate 2 is 1, while the propagated result of the stuck-at-0 fault is observed on the output.

#### Bit-Flip Fault Model

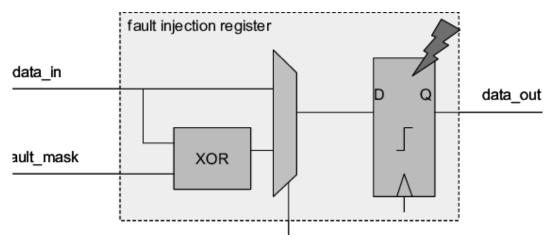

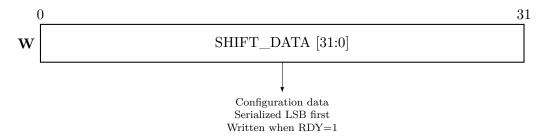

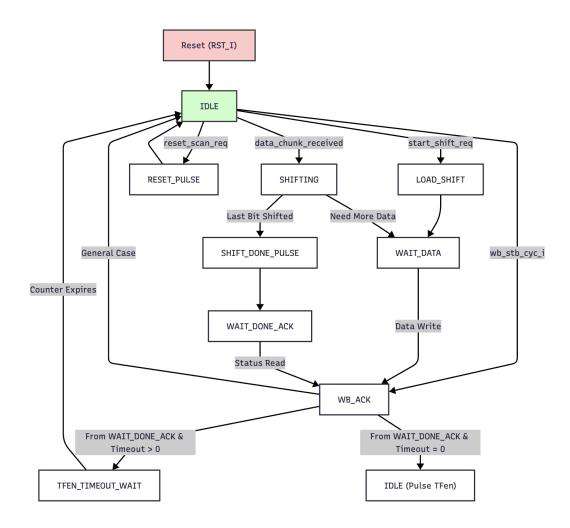

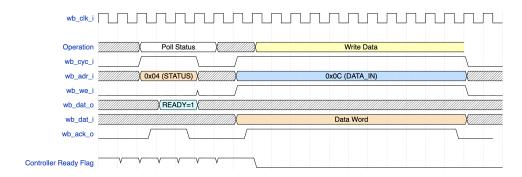

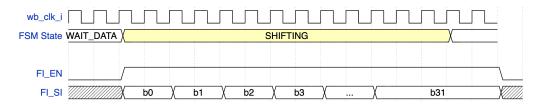

The bit-flip fault model is a type of transient fault that inverts the bit value the signal is carrying through the gate. It is especially important during operations due to environmental factors and electromagnetic interference. There are 2 Bit-flip models, **Single Event Transient (SET)**, where the fault affects the combinatorial logic, and **Single Event Upset (SEU)** fault model that affects the flip-flops,