#### Politecnico di Torino

M.Sc in ICT for Smart Societies - LM 27 A.Y. 2024/2025 July 2025

# Design and implementation of a deployment tool for modular DNN inference using ZeroMQ-based GPU-aware communication

Supervisors: Candidate:

Prof. Carla Fabiana Chiasserini Dott. Corrado Puligheddu Dario Antonio Ruta

# Summary

Deep Neural Networks (DNNs) are the fundamental structure adopted to provide smart service in a wide range of AI applications. However, DNN-based tasks have high computing requirements, posing huge challenges on their deployment on small and resource-constrained devices such as mobile phones or IoT devices. To address this issue, some solutions consider model compression techniques to limit the computational burden on the device as well as the model memory footprint. Other strategies involve partial or full task offloading towards more powerful computing platforms placed at the edge of new-generation mobile networks (5G-MEC), ensuring low latency and near-zero computing cost for the mobile device. In such context, mobile devices can consider DNN tasks as on-demand services. However, for the fact that MEC platforms are more resourceful than mobile devices, MEC radio and computing resources are limited. Therefore, it is of paramount importance to manage and optimize them to maximize the task execution rate. In this context, promising results emerge from sharing parts (blocks of layers) of DNN models among similar offloaded tasks. However, coping with parallel model execution in a scenario with high dynamism and strict latency requirements during offloading poses some challenges to be solved.

This thesis work presents BlockFlow, a high-performance deployment and management tool for modular and dynamic DNN inference. It incorporates TensorMQ, a novel contribution in GPU-aware communication for inter-block tensor forwarding at inference time based on ZeroMQ library. A detailed system design and technical motivation of the adopted choices for the practical implementation are widely discussed. BlockFlow provides a high degree of flexibility and adaptability across different computing scenarios such as single-node-single-GPU, single-node-multi-GPU, multi-node, and it can be adopted when offering DNN as service to the users. The performance of the inference pipeline has been tested under different operating conditions and for the most common object detection and object classification DNN architectures. TensorMQ addresses the ping-pong problem between CPU and GPU in single-node-single-GPU and single-node-multi-GPU setups for modular DNN architectures presenting a zero-copy solution, thus reducing the communication

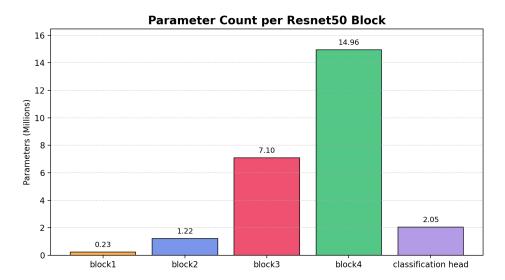

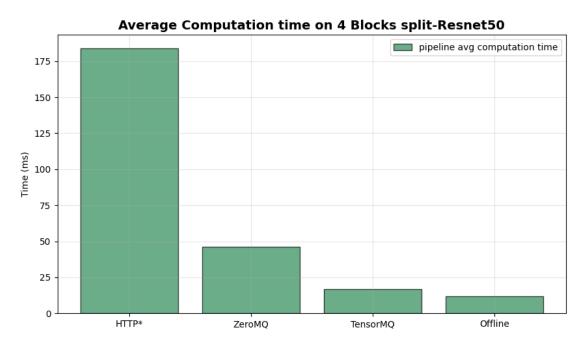

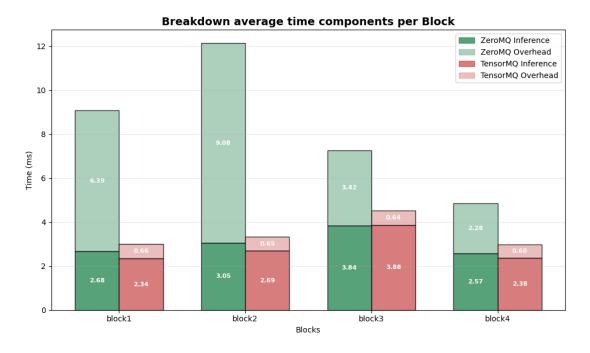

overhead, increasing the pipeline throughput and avoiding redundant data movements while still maintaining a high degree of system modularity and dynamicity. Experimental results in single-GPU setup, considering the popular Resnet50 model, demonstrate how TensorMQ outperform standard ZeroMQ, achieving up to 2.89x faster inference time, 8.30x reduction in pipeline communication overhead in ResNet50 architecture split into 4 blocks. In multi-GPU setups, it allows for up to 5.26x communication latency gains.

# Acknowledgements

I would like to express my deepest gratitude to my supervisor, Prof. Carla Fabiana Chiasserini, for giving me the opportunity to work on one of my most cherished topics. My sincere thanks also go to Dr. Corrado Puligheddu for his valuable advice and for incredible generosity with his time.

I would also like to thank all the people I have met along the way and with whom I have shared unforgettable experiences, both inside and outside the classrooms of the Politecnico. I could not name everyone, but a special mention goes to Tanucci, Nanni, Francesco, Ettore, to whom I wish all the best.

If we are reading this document today, it is undoubtedly thanks to my Papà, whom I cannot thank enough for allowing me to become who I am today.

Finally, I would like to thank Martina for being an integral part of my life.

# Table of Contents

| Li           | st of | Tables                                       | XI  |

|--------------|-------|----------------------------------------------|-----|

| Li           | st of | Figures                                      | XII |

| $\mathbf{A}$ | crony | vms                                          | XV  |

| 1            | Intr  | roduction                                    | 1   |

|              | 1.1   | Offloading Computer Vision Tasks at the Edge | 2   |

|              | 1.2   | Thesis Motivations & Objectives              | 4   |

|              |       | 1.2.1 Motivations                            | 4   |

|              |       | 1.2.2 Objectives                             | 5   |

|              | 1.3   | Thesis Contributions                         | 6   |

|              | 1.4   | Thesis structure                             | 6   |

| <b>2</b>     | Bac   | kground                                      | 9   |

|              | 2.1   | AI & Deep Neural Networks                    | 9   |

|              |       | 2.1.1 Deep Neural Networks                   | 10  |

|              |       | 2.1.2 Convolutional Neural Networks          | 12  |

|              | 2.2   | Deep Learning at scale                       | 15  |

|              | 2.3   | Inter-process Communication (IPC)            | 18  |

|              | 2.4   | Multi-access Edge Computing (MEC)            | 19  |

|              | 2.5   | OffloaDNN                                    | 21  |

| 3            | Blo   | ckFlow                                       | 27  |

|              | 3.1   | System Requirements                          | 28  |

|              | 3.2   | Technical Challenges                         | 28  |

|              | 3.3   | BlockFlow used tools                         | 30  |

|              |       | 3.3.1 ZeroMQ                                 | 30  |

|              |       | 3.3.2 PyTorch                                | 31  |

|              |       | 3.3.3 CherryPi                               |     |

|              |       | 3.3.4 Pickle                                 | 32  |

|              |       | 3.3.5   | Psutil                                                  | 33  |

|--------------|-------|---------|---------------------------------------------------------|-----|

|              |       | 3.3.6   | Python NVIDIA Management Library                        | 33  |

|              |       | 3.3.7   | Nvidia nvprof                                           | 33  |

|              |       | 3.3.8   | Taskset & Numactl                                       | 34  |

|              | 3.4   | Tensor  | MQ: tensor-aware inter-block communication via CUDA-IPC |     |

|              |       | and Ze  | $\mathrm{eroMQ}$                                        | 34  |

|              | 3.5   | Archit  | ectural Design                                          | 35  |

|              |       | 3.5.1   | Block Design                                            | 38  |

|              |       | 3.5.2   | Dispatcher Design                                       | 39  |

|              | 3.6   | System  | n Workflow                                              | 39  |

|              |       | 3.6.1   | Block workflow                                          | 40  |

|              |       | 3.6.2   | Dispatcher workflow                                     | 47  |

|              | _     | •       | 4.1.D                                                   | 4.0 |

| 4            | -     |         | ntal Results                                            | 49  |

|              | 4.1   | _       | imental setup                                           | 49  |

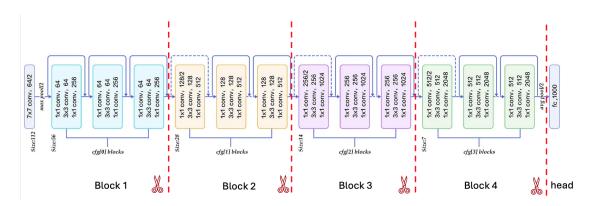

|              |       | 4.1.1   | Split-ResNet50 Offline analysis                         | 51  |

|              | 4.0   | 4.1.2   | ZeroMQ forwarding performance analysis                  | 52  |

|              | 4.2   | -       | ne performance analysis                                 | 53  |

|              |       | 4.2.1   | Mathematical model                                      | 54  |

|              |       | 4.2.2   | Single-host-single-GPU                                  | 55  |

|              | 4.0   | 4.2.3   | Single-host-Multi-GPU                                   | 64  |

|              | 4.3   |         | lar DNN deployment vs Standard Deployment               | 66  |

|              |       | 4.3.1   | Mathematical formulation                                | 66  |

|              |       | 4.3.2   | Numerical Comparison                                    | 68  |

| 5            | Con   | clusio  | ns & Future research                                    | 73  |

| Bi           | bliog | graphy  |                                                         | 75  |

| $\mathbf{A}$ | Awe   | enode ( | GPU topology                                            | 79  |

| В            | Zero  | oMQ v   | s TensorMQ time distributions per Block                 | 81  |

# List of Tables

| 2.1 | ResNet Architecture Comparison                                            | 16 |

|-----|---------------------------------------------------------------------------|----|

| 4.1 | Comparison between single-GPU-server and multi-GPU-server                 | 50 |

| 4.2 | Comparison of memory and latency metrics for scripted and traced          |    |

|     | blocks                                                                    | 51 |

| 4.3 | RTT Comparison on awenode (ms)                                            | 52 |

| 4.4 | Task distribution across different classes, for the considered scenarios. | 68 |

| 4.5 | ResNet50 modular vs traditonal deployment VRAM occupancy                  |    |

|     | analysis                                                                  | 69 |

| 4.6 | ResNet152 modular vs traditonal deployment VRAM occupancy                 |    |

|     | analysis                                                                  | 70 |

| ۸ 1 |                                                                           | 70 |

| A.1 | GPU Topology and Affinity (multi-GPU-server)                              | 79 |

# List of Figures

| 1.1  | Simple CNN structure for Handwritten Digit Recognition                                                       | 3  |

|------|--------------------------------------------------------------------------------------------------------------|----|

| 2.1  | AI, ML, DL relationship                                                                                      | 9  |

| 2.2  |                                                                                                              | 2  |

| 2.3  |                                                                                                              | .3 |

| 2.4  |                                                                                                              | 3  |

| 2.5  |                                                                                                              | 4  |

| 2.6  |                                                                                                              | .5 |

| 2.7  |                                                                                                              | 7  |

| 2.8  |                                                                                                              | 8  |

| 2.9  | MEC overview                                                                                                 | 20 |

| 2.10 | MEC platform Schema [13]                                                                                     | 1  |

| 2.11 | OffloaDNN's innovations. (fig.1, p.2 at [9])                                                                 | 3  |

| 2.12 | OffloaDNN architecture and workflow (fig.4, p.4 at [9]) 2                                                    | 4  |

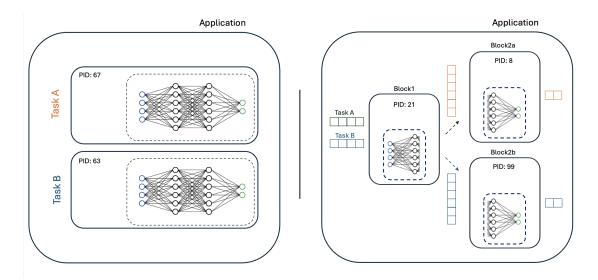

| 3.1  | (left) Traditional DNN deployment for each admitted task, (right) modular DNN architecture with shared block | 29 |

| 3.2  | Ping-pong effect between RAM and VRAM                                                                        |    |

| 3.3  | IPC handle deliver through TensorMQ                                                                          |    |

| 3.4  | BlockFlow application components                                                                             |    |

| 3.5  | BlockFlow application planes                                                                                 |    |

| 3.6  | Block Components                                                                                             |    |

| 3.7  | System Update workflow                                                                                       | 0  |

| 3.8  | Data Object in TensorMQ                                                                                      | 2  |

| 3.9  | TensorMQ Tensor transfer procedure between 2 blocks over 2 different                                         |    |

|      | GPUs                                                                                                         | 4  |

| 4.1  | ResNet50 Splitting points                                                                                    | 0  |

| 4.2  | ResNet50 Parameters (millions) per Block                                                                     | 2  |

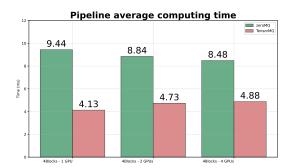

| 4.3  | 4-block pipeline average computing time                                                                      | 6  |

| 4.4  | Time components per block                                                                                    | 6  |

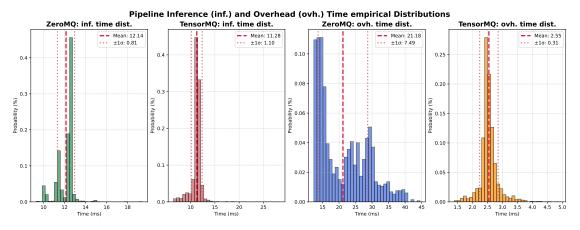

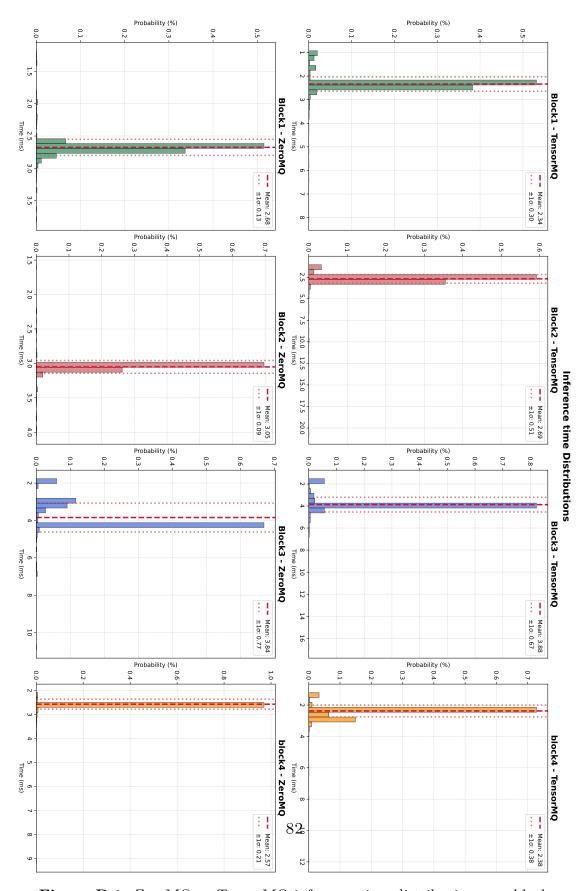

| 4.5  | Pipeline inference and overhead time distributions                        | 57  |

|------|---------------------------------------------------------------------------|-----|

| 4.6  | GPU and CPU utilization                                                   | 58  |

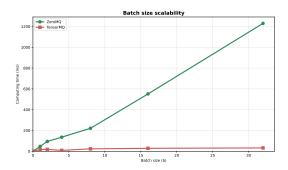

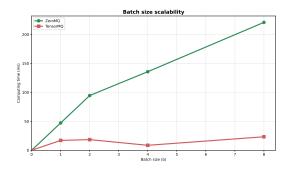

| 4.7  | Pipeline Computing time under different batch size                        | 59  |

| 4.8  | Pipeline Computing time under different batch size (zoomed)               | 59  |

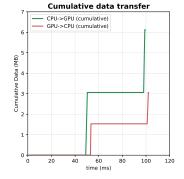

| 4.9  | Data Movement analysis with NVIDIA nvprof for 2 consecutive               |     |

|      | inferences with ZeroMQ                                                    | 59  |

| 4.10 | Energy consumption per inference                                          | 60  |

| 4.11 | Pipeline scalability in multi-client scenario                             | 61  |

| 4.12 | 4-blocks Pipeline Throughput analysis                                     | 62  |

| 4.13 | Average VRAM occupancy under different arrival rates                      | 63  |

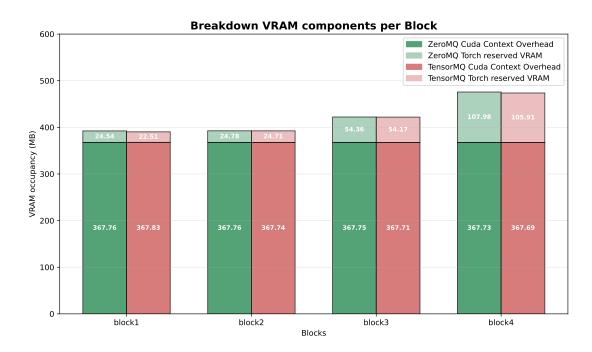

| 4.14 | Average VRAM occupancy per block                                          | 64  |

| 4.15 | Blocks average <b>computing time</b> with different deployment scenarios. | 65  |

| 4.16 | Blocks average <b>overhead time</b> with different deployment scenarios.  | 65  |

| D 1  |                                                                           | 0.0 |

| B.I  | ZeroMQ vs TensorMQ inference time distributions per block                 | 82  |

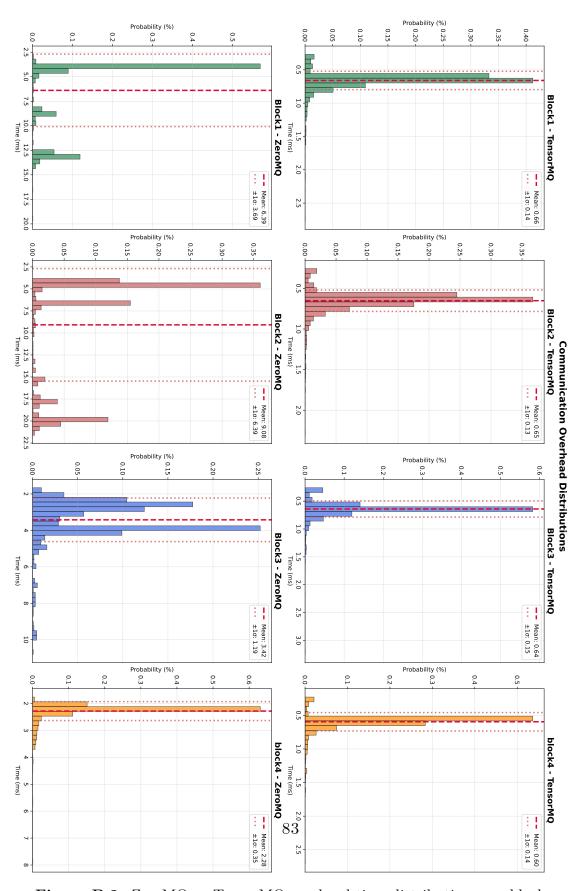

| B.2  | ZeroMQ vs TensorMQ overhead time distributions per block                  | 83  |

# Acronyms

#### SoTA

State of The Art

#### **ASIC**

Application-Specific Integrated Circuits

#### **GPU**

Graphical Processing Unit

#### CV

Computer Vision

#### DNN

Deep Neural Network

#### CNN

Convolutional Neural Network

#### LLM

Large Language model

#### **ETSI**

European Telecommunication Standard Institute

#### MEC

Mobile Edge Computing

#### DOT

DNN for scalable Offloading of Tasks

#### IPC

Inter-Process Communication

#### RTT

${\bf Round\text{-}Trip\text{-}Time}$

#### PDF

Probability density function

#### ePDF

Empirical Probability density function

#### PDI

Path Distribution Index

## Chapter 1

### Introduction

In recent years, the number of digital services based on Artificial Intelligence (AI) is growing exponentially, bringing a digital revolution of our society. In this vein, the main form of technological progress can be attributed to the large-scale deployment of services based on Deep Neural Networks (DNNs) jointly with Deep Learning (DL) algorithms.

DNNs are the essential paradigm that enabled smart use-cases in a variety of industries such as smart city, precision agriculture, smart health, autonomous-driving and many others.

One of the major factors contributing to this digital revolution has undoubtedly been the increased availability of data to be processed, available computational resources and specialized hardware like Application-Specific Integrated Circuits (ASICs) and Graphical Processing Units (GPUs), effectively enabling the creation of increasingly intelligent and, at the same time, large and complex models.

Indeed, over the past few years model sizes have grown dramatically. This rate of scaling is outpacing Moore's Law, creating a significant gap between the supply and demand for computing power. This poses a serious challenge in the deployment of DNNs in devices with small computational capabilities like IoT and Edge devices. This scenario gets even more complicated if Edge devices are battery powered.

One solution to tackle this problem lies on algorithmic procedures to reduce the computational burden and the memory footprint of the model (e.g., using pruning and quantization techniques). However, model compression techniques usually lead to a reduction in model performance (e.g., accuracy) [1]. Moreover, often the compressed model fails to provide an adequate trade-off between power consumed and required performance. Conversely, the edge device in some cases can take advantage of high-speed wide-band connectivity to offload the full computation or a part of it to a cloud server with more computational power. Nonetheless, applications with strict latency constraints fail to benefit from this solution as they experience large delays due to the network signal propagation to remote hosts

and back. To cope with these issues, the European Telecommunication Standard Institute (ETSI) introduced the concept of Multi-Access Edge Computing (MEC) [2], bringing cloud computing capabilities to the network edge thereby reducing the latency and enhance the overall performance of user applications [3].

In a scenario where AI tasks based on DNNs can be seen as services, the end user can enjoy the above benefits by offloading computer vision tasks to the edge. However it is important to ensure that certain performance levels are guaranteed while respecting systemic constraints.

# 1.1 Offloading Computer Vision Tasks at the Edge

Among the huge number of DNN based tasks, Computer Vision (CV) tasks may be a great candidate to be offloaded.

Offloading computer vision tasks at the edge-cloud is a promising approach able to reduce latency required for computation due to higher computational capabilities and reduce energy consumption due to the shorter path the data has to travel through the network to reach the remote-cloud. In particular, those who benefit most are small devices that are unable to handle the required calculations due to strict constraints on their hardware.

Offloading computer vision tasks to a Multi-Access Edge computing platform, significantly outperforms traditional remote cloud offloading schemes (more on Multi-Access Edge Computing paradigm can be found in sec. 2.4). In [4], the authors implemented an end-to-end solution, demonstrating the goodness of the 5G-MEC architecture in the context of offloading of computer vision tasks from mobile devices. Specifically, they focused on offloading emotion recognition tasks through CNNs running at the edge. They proved that 5G-MEC architecture improves the throughput of more than 250% and reduces the response time of 71.3% compared to the remote-cloud-based offloading. For small packet sizes, even to a cloud service located in the same country, the RTT could be halved.[5]. The reduction factor is due to a smaller network propagation delays (i.e. fewer number of hops to be traversed) and a more efficient radio communication under 5G-NR with respect to previous RAN generation.

Offloading to the edge-cloud implies the transmission of information over a wireless channel, thus the number of bits transmitted over the channel is a key factor that needs to be taken into account in latency constrained applications. Often, edge devices experience signal quality degradation and transmission bit-rate variability due to their relative movement with respect to the closest Base Station (BS) they are connected to.

For that reason, a variation of the Edge Computing paradigm gained attention

in recent times where the edge device does not offload the full task but only a part of it. This approach refers to split-computing, where the main actors involved (i.e edge-device, edge-cloud, cloud) are in charge of only a part of the computation. In the context of DNN based tasks like CV tasks this approach refers to the *split-DNN*.

Several works take into consideration *split-DNN* as a potential solution to jointly optimize the radio and computing resources and the total energy consumption of the inference pipeline over a multi-tiered interconnected mobile-edge-cloud system to serve multiple DNN based tasks [6]. However, the optimization problem stated above is hard to be solved also due to the *Data Amplification Effect* [7], where quite often in CNNs intermediate feature maps are bigger in size with respect to the input images.

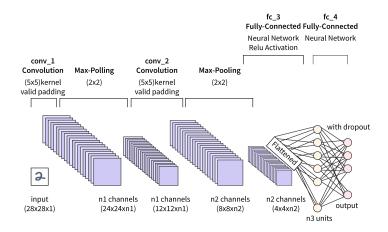

Figure 1.1: Simple CNN structure for Handwritten Digit Recognition

For example, even considering a trivial CNN as the one reported fig 1.1, one can notice that given as input an image of size [H, W, C] = [28,28,1], after the first convolutional layer with 32 filters, kernel size of [H, W] = [5,5], stride = 1 and padding = 0, the output feature map is of shape [H, W, C] = [24,24,32], increasing the size by almost 32x with respect to the input tensor. <sup>1</sup>

Solutions to these problems are linked again to model compression techniques or the use of encoders-decoders between the entities involved to shrink the amount of bits sent over the channel.

However, in a scenario where the same base model is shared to perform multiple tasks, there is a risk of irreparably compromising accuracy performance in sensitive tasks to them. A possible approach is to enrich the system with a degree of flexibility, thus making it flexible and adaptable to the required context. The

<sup>&</sup>lt;sup>1</sup>more on CNNs functional is reported in sec. 2.1.2

work at [8] perfectly marries the problem of data amplification effect. Indeed, the authors introduced *Slimmable Encoders* to cope with limited channel capacity in IoT wireless networks.

The *Data Amplification Effect* must be taken into account even in simpler contexts such as traditional Offloading to the Edge Server. There could be cases in which, the split-DNN architecture lies on a single host. In these scenarios, the inference is done by means of a DNN block's pipeline. Hence, it is of paramount importance to ensure efficient communication between the parts of the DNN structure.

Valuable research works such as OffloaDNN [9], focus on this use-case providing a framework able to increase the computing platform efficiency by minimizing the system resources (both radio and computational) in 5G-MEC infrastructure. The main idea is to share dynamically one or more DNNs blocks between one of more than one admitted task at the edge. As a result, the forward pass of a DNN is no longer a static sequence of layers belonging to the same entity but becomes a logical execution path, where different blocks are involved in the inference process depending on the active tasks.

#### 1.2 Thesis Motivations & Objectives

As discussed, OffloaDNN provides meaningful insights in the context of offloading CV tasks at the edge, demonstrating and validating the effectiveness of the proposed solution under different scenarios.

#### 1.2.1 Motivations

When adopting a modular DNN architecture it is essential to consider not only the pure computation time—represented by the cumulative time spent in each block—but also additional overhead factors such as communication latency, interblock data transfers, and serialization/deserialization operations. Furthermore, computing time itself can vary significantly depending on the current load of each block, introducing complications on accurate latency estimation. Indeed, latency depends on the processing time of each block in the pipeline and on the waiting time spent before being processed by the block.

Mathematically speaking, the average total time  $T_b$  spent by a generic tensor t in a generic block b of the pipeline depends on the block load  $\rho$  and on the device d hosting the block (e.g, GPU or CPU) and it is:

$$T_b(\rho, d) = T_w(\rho) + T_c(d) + T_{tx} + O_b$$

(1.1)

where  $T_w$  is the waiting time of the generic tensor t spent waiting to be served and it depends by the block load  $\rho$ ,  $T_c$  is the computing time and it depends on the device d that is hosting the block while  $T_{tx}$  is the inter-block transmission time. The term  $O_b$  is the overhead component of each inference and it is related to computing operations like serialization and describination etc. The load  $\rho$  is function of the tensor arrival rate at the block b and its processing time and it is:

$$\rho(\lambda, d) = \frac{\lambda}{\mu(d)}. (1.2)$$

where  $\mu$  is the average service rate of the generic block b computed as the reciprocal of the computing time.

In Eq.1.1, the inter-block transmission time  $T_{tx}$  has quite often been overlooked in the context of branchy and modularly deployed DNNs in the same computing platform. Indeed, an efficient transmission procedure between blocks is of paramount importance since it can directly impact the total computing time, the computing effort and the energy consumption of the pipeline.

Clearly, due to the DNN computation itself and by the presence of hardware accelerators, the development of efficient communication strategies between blocks poses some challenges to overcome, otherwise there could be the serious risk that the advantages in terms of memory and resource reduction would be nullified by prohibitive latency times and excessive overhead.

Moreover, the nature of a distributed application imposes a careful management and orchestration of the active entities involved in the architectural schema.

#### 1.2.2 Objectives

This thesis work has the following objectives:

- Objective 1: Analyze the intra-host modular-DNN paradigm under the scenario of minimizing computational resources given by the possibility to share blocks between different tasks;

- Objective 2: Research possible solutions related to efficient communication between DNN's blocks instantiated in a computing platform in order to achieve a good trade-off between the advantages offered by the modular architecture itself while avoiding prohibitive overhead:

- **Objective 3:** Design and realize a tool able to manage modular-DNN inference architecture applying the main concepts found as outcome of objective 2:

- Objective 4: Make the tool integrable to an optimization engine that might command the deployment of DNN modules and their connection for each offloaded task;

- **Objective 5:** Validate its reliability and performance with both single-GPU and multi-GPU setup.

#### 1.3 Thesis Contributions

This study presents **BlockFlow**, an *open-source* tool that aims to manage split-DNN architectures intra-node and inter-node providing strong flexibility on DNNs AI services.

The main features of **BlockFlow** are:

- TensorMQ: a near-zero communication overhead tensor exchanging paradigm between DNN blocks in presence of hardware acceleration devices<sup>2</sup>,

- complete life-cycle management of the Blocks instantiated in the machine,

- real-time system KPI monitoring during inference.

**BlockFlow** can be widely used in all applications that require a certain degree of flexibility, taking advantage of the possibility of having multiple shared DNN structures.

#### 1.4 Thesis structure

The presented thesis work is articulated into 5 main chapters each of them with specific goals:

Chapter 1: This is the introductory chapter, which serves to lay the foundations for the understanding of the context on which the thesis is based. It presents offloading to the edge procedures with a particular focus for DNN based tasks, discusses its advantages, but highlights some limitations. It analyzes related works on the Literature and finally, it presents the objectives and main contributions of this thesis.

<sup>&</sup>lt;sup>2</sup>Nvidia GPUs compatible with CUDA library

- Chapter 2: It it serves as a theoretical background (sec 2.1 presenting a general overview of the related concepts used in the thesis. Hence, it provide a broader overview of OffloaDNN.

- Chapter 3: It aims to present in detail the work carried out for the practical implementation of the tool, discussing the technical and implementation aspects.

- **Chapter 4:** It presents the performance results obtained by the tool and discusses its strengths.

- **Chapter 5:** It concludes the work by briefly summarizing the main answers to the research questions posed and the objectives set. Finally, it presents a brief overview of how the research may be continued.

## Chapter 2

# Background

#### 2.1 AI & Deep Neural Networks

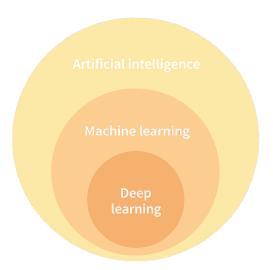

The term Artificial Intelligence (AI) refers to a set of methods and techniques used to enable machines to solve problems through the use of computer science. According to that definition, AI spans the concepts of Machine Learning (ML), Deep Learning (DL) and finally Neural Networks (NNs), as: neural networks are a type of deep learning models which are subfield of machine learning which, in turn, is a subset of AI (Figure 2.1).

Figure 2.1: AI, ML, DL relationship.

Machine Learning (ML) and Deep Learning (DL) refer to methodologies designed to train models capable of performing specific tasks effectively, thereby enabling

machines to exhibit intelligent behavior.

These methodologies are grounded in the assumption that, for a given phenomenon, there may exist an underlying mathematical relationship between a set of variables (features) and the observed outcome. In other words, given a collection of input data (features) and corresponding output values (labels or targets), a machine learning model aims to approximate the functional relationship that maps inputs to outputs. The process of developing a machine learning model typically involves three fundamental stages: **model selection**, **feature extraction**, and **decision making for prediction**. Since ML models are mathematical in nature, they rely on parameters whose values influence the model's performance. These parameters—either fully or partially—are learned through a **data-driven training process**, in which the model adjusts its internal configuration to best capture the patterns present in the data.

This introduction allow us to formulate a difference between classical machine learning and deep learning:

- Machine Learning: the model selection process encompasses the use of a statistical model to be selected among many available, the feature extraction process is handcrafted and the decision making is data-driven

- **Deep Learning**: the model selection process encompasses the use of Neural Networks, the feature extraction process is data-driven and the decision making process is data-driven.

It is important to notice that choosing the most appropriate model and selecting the right set of features can be complex for some problems.

The idea behind NNs is that if a NN is sufficiently powerful and well trained, it will be able to compute the best possible feature extraction which leads to good performance in the decision making stage.

#### 2.1.1 Deep Neural Networks

Neural networks are mathematical structures designed to mimic the human brain, whose main component is the neuron.

In the AI context, the neuron is the base component of a neural network that performs a weighted sum of several inputs and eventually the weighted sum passes through a non-linear function. The neuron's mathematical formulation is:

$$y = \phi\left(\sum_{i} w_i x_i + b\right) \tag{2.1}$$

or in matrix formulation:

$$y = \phi(w^T x + b) \tag{2.2}$$

where y is the output (scalar) of the neuron, w is the set of weights, x is the input feature vector and b is the bias. The  $\phi$  stands for the non-linearity eventually used after the weighted sum and it is chosen arbitrarily. The most common non—linear functions are: ReLU, Sigmoid, Leaky ReLU etc. each of them with a specific behavior and use case.

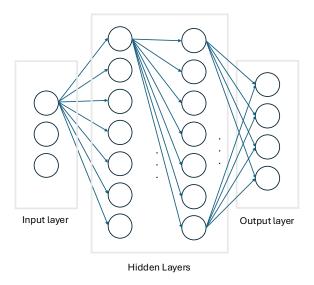

Neurons arranged in parallel create a NN layer and layers placed in a sequential way create a neural network structure.

**Deep Neural Networks** refers to a sequential composition of multiple layers, each of them composed by several neurons, able to work in a complex latent space; the first layer is also called *input layer*, the last one is known as *output layer* while the ones in the middle are called *hidden layers*. In feed-forward Neural networks, each layer takes as input the output of the previous layer. A layer whose neurons are connected with all the neurons of the next layer is called *fully connected layer* or *linear layer* whose mathematical formulation is:

$$y = \phi(Wx + b) \tag{2.3}$$

where  $y:(F_{output};1)$  is the output vector of the layer,  $x:(F_{input};1)$  is the input vector,  $W:(F_{output;F_{input}})$  is the weight matrix and  $b(F_{out};1)$  is the bias vector. The output vector of a NN  $y_{net}$  given an input vector x is given by the composition of the function f of each layer (eq.2.4 and fig. 2.2).

$$y = (f_L \circ f_{L-1} \circ \dots \circ f_1)(x) \tag{2.4}$$

As discussed in the previous section, the final goal of each machine learning model is to fit its parameters over a set of data samples and train them to learn the statistical dependency between the input provided and the output desired. In other words, given a set of observations we try to estimate a mathematical function that is able to generalize the observed phenomenon and thus, make prediction when new data are provided. Since Deep Neural networks perform feature extraction by themselves, they are universal function approximator. In practice, they are able to provide good approximation of functions in N dimensions and the accuracy of the approximation depends on: the amount and the quality of data provided, the number of parameters of the NN itself and their relative connections between them and finally the training strategy. The training process is an iterative procedure devoted to retrieve the set of optimal parameters of the NN and it is based on the backpropagation of the error that the neural network makes at each forward pass. The error made by the NN is measured by an error function known as loss function, that is chosen arbitrarily among several available based on the task the NN is going to be trained for. Afterward, the gradient of the loss function is backpropagated and finally the weights are updated according the chosen optimization logic (e.g., gradient descent, Adaptive moment estimation).

Figure 2.2: Simple Feed-Forward neural network with fully connected layers.

#### 2.1.2 Convolutional Neural Networks

Convolutional Neural networks (CNN) belong to a subset of neural networks that incorporate the convolution operation into their layers. These structures are particularly useful for all those problems whose data presents locality properties such as images, music, timeseries.

In a convolutional layer, each neuron performs convolution over a subset of output values coming from the previous layer's neurons. More generally, the idea behind convolutional layers is based on the fact that each neuron is in charge of extracting some knowledge in a specific spatial area of the data (i.e. set of adjacent pixels in an image, number of consecutive samples in a signal) through multiple filtering stages. This provides several advantages such as:

- the network can work with input data of variable size;

- reduced number of parameters due to less connections between neurons.

The portion of space over which a neuron performs convolution is called *local* receptive field and it depends by the filter size. The output of a convolutional layer

presents one or more than one feature maps that are latent representation of the input features. The number of feature maps in output of a convolutional layer depends on the number of filters used. Mathematically speaking, a generic neuron performs the following operation over a feature map:

$$y_n = w * x + b \tag{2.5}$$

where  $y_n$  is the output of the neuron, w is the filter or kernel, x is the corresponding values of the feature map in the same position of the filter and b is the bias term. A visual representation of convolution operation over a feature map is reported in Figure 2.3.

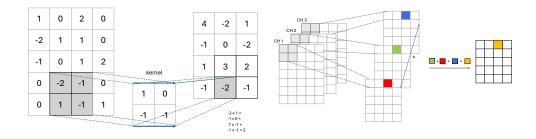

**Figure 2.3:** Convolution operation **Figure 2.4:** Generic Feature map with kernel size [2,2]. creation procedure.

The image 2.4 illustrates the main steps carried out within a convolutional layer to create a single feature map. Given an input of a generic shape with 3 channels, the filter is slid over the first input channel, creating a temporary feature map. The same operation is repeated on all input channels. Finally, the temporary feature maps are summed element-wise. The parameter that determines how many steps the filter slides is called stride. Jointly with the padding parameter and the kernel size, it determines the shape of the feature map [h, w] as output from the layer. The shape can be computed by as:

$$Output\_size = \frac{Input\_size - Kernel\_size + 2 \times Padding}{Stride} + 1$$

A set of as many filters as the number of input channels once trained allows to detect one single feature. Subsequently, for F features to be detected a number F of filters needs to be used. In case of F filters, the same set of operations is repeated for each of them. The dimensions of the feature map will therefore be [N, h, w].

In a convolutional layer i the number of learnable parameters is

$$num \quad params_i = KxKxCxF \tag{2.6}$$

where KxK is the kernel size, C is the number of input channels and F is the number of filters used.

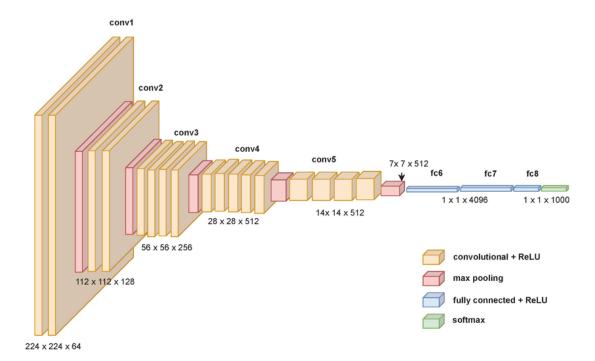

CNNs used for CV tasks are structures that employ a high number of convolutional layers, each with an adequate number of filters based on the number of features to be extracted. Figure 2.5 shows the detailed architecture of VGG-19 network for object classification.

Figure 2.5: VGG19 Architecture [10].

From a practical point of view, most CNNs reduce the spatial size of feature maps and increase their depth (or number of channels) with stride parameter larger than 1 or with pooling operations. As consequence, even in the case of small kernels (e.g.,  $3\times3$ ), the combined effect of multiple layers enlarge the field of view of the final layers over a large portion of the input image. During training, the filters of the initial layers tend to detect low-level features like angles, contours, textures, while deeper layers detect high-level features such as parts of objects, complex semantic structures. For an object classification problem, for example, the backbone of the neural network consists of a set of convolutional layers aimed at feature extraction; on top of the backbone is placed a classification head (linear

layer) preceded by a flattening of the feature maps produced by the backbone. Training of deep CNNs could suffer from the well-known phenomena of vanishing gradient and/or exploding gradient. In the first case, traditional activation functions such as sigmoid, ReLU produce derivatives in the interval (0,1), so the product of gradients across many layers tends to decrease exponentially with the depth of the network. Similarly, if the derivatives become large, gradient explosion can occur, with unstable weight updates. To mitigate these effects, modern CNN architectures introduce structural components such as residual blocks used in ResNet.

#### Resnet Architectures

ResNets were presented in 2015 for the first time in [11] as Convolutional Networks aiming to tackle the vanishing gradient problem, improve weights stability during training and allow to the creation of deeper architecture thus increasing accuracy performance on image processing tasks. Residual blocks are based on the introduction of skip connection to allow the convolutional layer to only learn a correction instead of the full transformation, leading to a reduced number of parameters used, faster convergence due to the fact that gradients are better conditioned.

Figure 2.6: ResNet50 Architecture.

The architecture of ResNet50 has **4 stages** as shown in Figure 2.6. Moving from one stage to another, the channel width is doubled and the size of the input is reduced to half. It is available in different versions with different depths: 18,34,50,101,152. The architecture of the stages is the same among all versions but the amount of residual blocks per layer changes. Table 2.1 reports a complete overview about different ResNet structures.

#### 2.2 Deep Learning at scale

Deployment of large models, particularly Large Language Models (LLMs) on a single device could be problematic due to the lack of available memory or computing

| layer name | output size | 18-layer                         | 34-layer                   | 50-layer                                | 101-layer                                                          | 152-layer                                |

|------------|-------------|----------------------------------|----------------------------|-----------------------------------------|--------------------------------------------------------------------|------------------------------------------|

| conv1      | 112×112     | $7 \times 7$ , 64, stride 2      |                            |                                         |                                                                    |                                          |

|            |             | $3\times3$ max pool, stride 2    |                            |                                         |                                                                    |                                          |

| conv2_x    | 56×56       | 3×3, 64<br>3×3, 64 ×2            | 3×3, 64<br>3×3, 64         | 1×1, 64<br>3×3, 64<br>1×1, 256<br>×3    | 1×1, 64<br>3×3, 64<br>1×1, 256<br>×3                               | 1×1, 64<br>3×3, 64<br>1×1, 256<br>×3     |

| conv3_x    | 28×28       | 3×3, 128<br>3×3, 128<br>×2       | 3×3, 128<br>3×3, 128<br>×4 | 1×1, 128<br>3×3, 128<br>1×1, 512<br>×4  | 1×1, 128<br>3×3, 128<br>1×1, 512<br>×4                             | 1×1, 128<br>3×3, 128<br>1×1, 512<br>×8   |

| conv4_x    | 14×14       | 3×3, 256<br>3×3, 256<br>×2       | 3×3, 256<br>3×3, 256<br>×6 | 1×1, 256<br>3×3, 256<br>1×1, 1024<br>×6 | $1 \times 1, 256$ $3 \times 3, 256$ $1 \times 1, 1024$ $\times 23$ | 1×1, 256<br>3×3, 256<br>1×1, 1024<br>×36 |

| conv5_x    | 7×7         | 3×3, 512<br>3×3, 512<br>×2       | 3×3, 512<br>3×3, 512<br>×3 | 1×1, 512<br>3×3, 512<br>1×1, 2048<br>×3 | 1×1, 512<br>3×3, 512<br>1×1, 2048<br>×3                            | 1×1, 512<br>3×3, 512<br>1×1, 2048<br>×3  |

|            | 1×1         | average pool, 1000-d fc, softmax |                            |                                         |                                                                    |                                          |

| FLOPs      |             | $1.8 \times 10^9$                | $3.6 \times 10^9$          | $3.8 \times 10^9$                       | $7.6 \times 10^9$                                                  | 11.3×10 <sup>9</sup>                     |

Table 2.1: ResNet Architecture Comparison.

resources. Moreover, in case it could be possible, due to the need of always-up-todate, well-performing models, the repetitive nature of the training procedure would mean that the entire training process for these structures would be very slow.

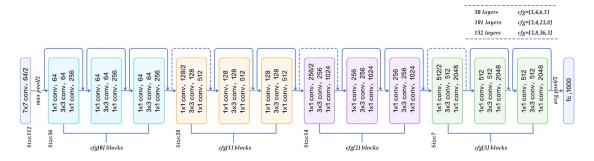

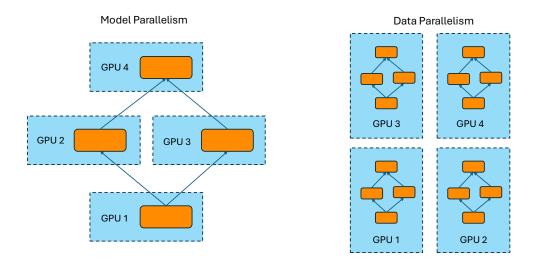

Training and deployment of deep learning models at scale present computational and architectural challenges and it necessitates distributed training and/or deployment techniques such as Data and Model Parallelism (Figure 2.7).

**Data Parallelism** is the simplest form of parallelism. It is based on the replication of the full model over multiple GPUs and dividing the training dataset into independent batches to be delivered to each model copy. Each device performs the forward and backward passes in parallel on its data shard, then they synchronize by aggregating the gradients and finally they update the shared model parameters. The main advantage is simplicity and the communication load between GPUs which is relatively low. On the other hand, there is the strict limitation that the model can fit on a single GPU.

Conversely, **model parallelism** divides the model across multiple devices. In this strategy, each GPU hosts part of the model weights rather than a complete copy. In general, this can be done in two complementary ways:

• Pipeline Parallelism: the model is divided *vertically* into sequences of layers.

Figure 2.7: Model (left) and Data (right) parallelism conceptual schema.

For example, on 4 GPUs, the first quarter of the layers could reside on GPU 1, the second quarter on GPU 2, and so on. During the forward pass, intermediate tensors are passed from one GPU to the next according to the model flow; during the backward pass, the derivatives are propagated backward along the same path. The model is therefore "pipelined" between GPUs: while one GPU calculates the initial layers for a given batch, another can calculate the subsequent layers of the same batch or a different batch. However, splitting the model into a pipeline introduces temporal inefficiencies that can reduce the total utilization of the device and thus, the system performance too; in particular, this happens when a device remains in an idle state since it is waiting for the previous block to send the intermediate tensor. In addition, overall latency can increase because each batch must go through multiple sequential stages. Efficiency is maximized when the computation times of the various segments are balanced and when optimized intermediate tensor transmission strategies are used, especially for serialization/deserialization and transfer between device memory and host memory.

• Tensor Parallelism: This method divides individual operations and tensors within layers. In tensor parallelism, a matrix or tensor is partitioned horizontally across multiple GPUs, each of which computes a portion of the operation simultaneously. For example, in a linear layer  $C = A \times B$ , the matrix B can be divided by columns into blocks and assigning each block to different GPUs, calculating  $(A \times B_i)$  in parallel. Finally, the partial results are combined to obtain the complete result.

#### 2.3 Inter-process Communication (IPC)

Inter-Process Communication (IPC) refers to a set of methods and protocols that enable data exchange between separate processes running on a computer system.

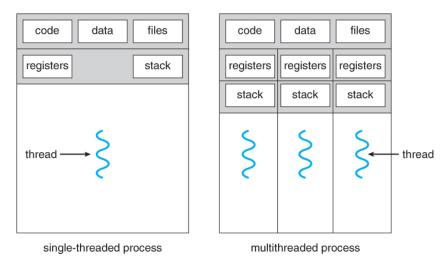

Figure 2.8: Single-threaded and multithreaded processes [12].

As the Figure 2.8 reports, each spawned process has its own address space in memory, opened files and assigned system resources, allowing it to execute instructions independently with respect to other processes. This separation ensures isolation and security: an error in one process does not directly compromise other processes, and a malfunctioning process can be terminated without causing the entire system to crash.

However, this leads to an increased overhead on the spawn of a new process with respect to the launch of a new thread.

IPC techniques can be grouped in two basic models: shared memory and message passing. Communication by means of shared memory is carried out by letting multiple processes access a common memory area and read/write over this space.

On the other hand, message passing techniques let processes communicate by sending messages through communication channels provided by the operating system.

The most common message passing techniques for IPC are:

- Pipes which are simple communication channels between two processes. There are two types of pipes: anonymous pipes and named pipes. Anonymous pipes allow one-way information exchange only for parent-child processes and follow the lifetime of the process that created them. In contrast, named pipes can also be used to communicate between unrelated processes and have two-way communication.

- Sockets, communication endpoints that can operate both locally (Unix domain sockets) and on the network (TCP/UDP). They allow for bidirectional data exchange between processes on different hosts or on the same host, using various protocols (stream-oriented such as TCP, or datagram such as UDP).

- Queues are structures managed by the operating system where processes can send or retrieve messages. The kernel is responsible for storing the messages in order; senders and receivers do not need to be directly connected, reducing the coupling between processes.

#### 2.4 Multi-access Edge Computing (MEC)

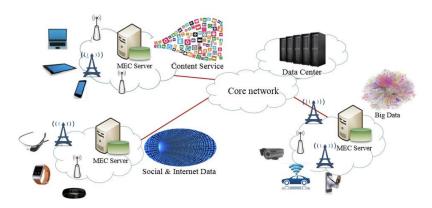

Multi-access Edge Computing (MEC) is a technology standardized by the European Telecommunication Standard Institute (ETSI) [2] in 2015 devoted to bring an IT service environment and cloud-computing capabilities at the edge of the mobile network, within the Radio Access Network (RAN) and in close proximity to mobile subscribers. As a consequence, a reduced latency, improved customer experience and a more efficient exploitation of network resources is ensured.

However, it is important to highlight the difference between Edge Computing and Multi-access Edge-Computing.

While Edge-Computing stands for a computing paradigm in which computation is performed close to the data source thus improving latency and bandwidth saving, Multi-access edge computing is a telecommunication concept; a standardized architecture to enable edge computing within mobile networks (e.g., 5G).

Since its standardization and its large-scale deployment, 5G improved end-user connectivity providing faster, more reliable and more efficient communication enabling thus economic growth and competitiveness in the creation of new use-cases in different domains such as smart cities, telemedicine, 4.0 industry etc. In addition to a better use of radio resources and the possibility of having multiple networks

Figure 2.9: MEC overview.

with different requirements coexisting within the same network, 5G leverage more programmable approaches to software networking (SDN) and use virtualization technology within the telecommunications infrastructure (NFV), functions and applications.

More in detail, NFV stands for Network function Virtualization meaning that tasks that were previously carried out exclusively by specialized hardware devices such as routers, firewalls etc. are now virtualized and executed as software components. Indeed, jointly with NFV and SDN, MEC is considered one of the key emerging technology of 5G mobile networks [2].

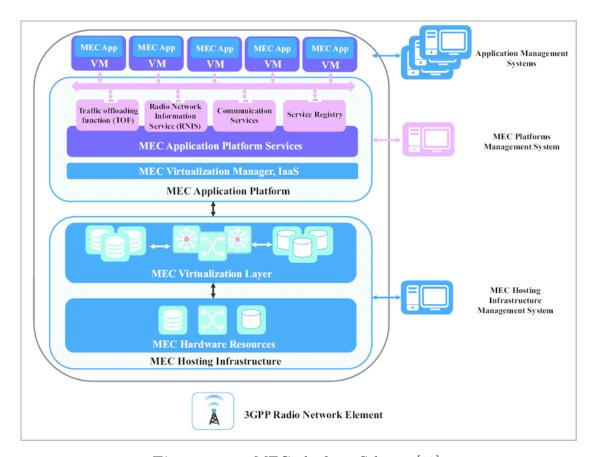

MEC is based on a virtualized platform, showing an approach that is complementary to NFV. While NFV prioritizes network functions, the MEC framework facilitates the execution of applications at the edge of the network. Each MEC server consists of a hosting infrastructure and an application platform as it is shown in fig. 2.10.

The hosting infrastructure includes the hardware resources (such as the computation, memory, and networking resources) as well as a virtualization Layer. The MEC application platform includes a MEC virtualization manager together with an Infrastructure as a Service (IaaS) controller, and provides multiple MEC application platform services. On top of the MEC application platform, the MEC applications are deployed and executed within virtual machines, which are managed by their related application management systems and agnostic to the MEC server/platform and other MEC applications.

A possible set of MEC applications includes intelligent video surveillance, dynamic traffic management, and real-time environmental monitoring. In the automotive sector, it enables V2X communications and it can support autonomous driving. Moreover, MEC allows local execution of AI models as application (e.g., CNN for computer vision) enabling also devices with limited computing power to perform tasks that they would otherwise be unable to perform.

Figure 2.10: MEC platform Schema [13].

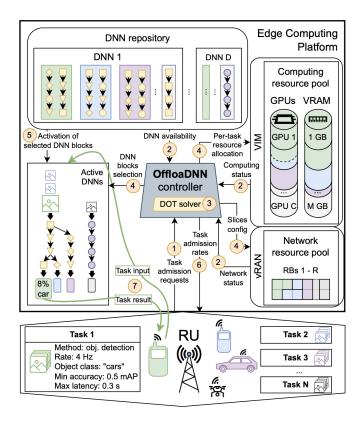

# 2.5 OffloaDNN [9]

In a 5G-MEC, end devices such as mobile phones and IoT devices can offload computationally intensive tasks, such as those related to computer vision, to nearby edge servers. This approach allows end devices to overcome hardware limitations and achieve lower latencies than the central cloud. However, it is important to consider that edge server resources are also limited. Although they offer greater computational power than end devices, edge servers must simultaneously handle several tasks from different devices.

In OffloaDNN [9], the authors formulated a weighted-tree-based heuristic to solve the DNN for scalable Offloading of Tasks (DOT problem). It provides a novel contribution on the jointly optimization of the:

- Edge-Cloud computing and radio resources,

- Offloaded task admission rate,

• Optimal structure of the DNN used to execute the offloaded task.

OffloaDNN brings a new perspective considering DNN structures serving different Computer Vision tasks as set of Blocks, each of them made by more than one original layer of the DNN. However, the main contribution lies in considering the possible structural correlations between the various DNNs required for the execution of different CV tasks.

Indeed, during training, hidden layers of a DNN get specialized into the extraction of different feature levels. Specifically, in CNNs, feature extraction process sees early layers devoted to the construction of a visual basis by learning how to detect low-level features such as corners, edges, colors etc. Final layers instead, uses the extracted information from earlier layers to perform high-level decisions such as object recognition, object classification. This hierarchical feature representation forms the foundation of transfer learning, a technique designed to accelerate the training of DNNs by leveraging pre-trained models. Specifically, the early layers of a pre-trained NN, which capture general low-level features, are retained (i.e., their weights are frozen), while only the later layers are fine-tuned on the target task. This approach not only reduces training time but also improves performance, especially when labeled data for the new task is limited [14].

OffloaDNN exploits the structural redundancy among different DNNs serving different tasks to reduce the Edge Server memory usage and increase the task admission rate to the Edge Server.

The main intuition is to leverage DNN layers that can be shared at the edge among DNNs serving different tasks.

In real-case scenarios where the edge device asks for a CV task offloading with specific requirements such as accuracy or maximum admissible round-trip-time, OffloaDNN should provide the most-valuable tradeoff that minimizes the edge server resources while meeting the constraints imposed by the end-device. In these cases, fine-tuning of task specific layers must be executed.

The second intuition is to choose which layers to share and which to fine-tune based on the task needs.

Lastly, if the structure is accurate enough, OffloaDNN allows for **structured pruning** to one or more than one block in order to reduce the model memory footprint as well as the processing time.

For a more complete understanding, the main innovations proposed are depicted fig 2.11 considering an object classification problem. In the left sub-picture, it shows how the sharing of the first 2 blocks would result advantageous, in terms of the total blocks deployed (6 total blocks vs 8 total blocks). The center sub-picture shows how to actually improve the accuracy performance for the task model train detection by fine-tuning only target specific layers. The latter (right), shows how memory footprint and latency of the structures can be further optimized relying

Figure 2.11: OffloaDNN's innovations. (fig.1, p.2 at [9])

on pruning.<sup>1</sup>

#### OffloaDNN architecture

OffloaDNN can be seen as an application running on the Edge Computing Platform, able to intelligently optimize the system resources, maximize the offloaded task admission rate while matching the task related constraints such as minimum accuracy and maximum round-trip-time.

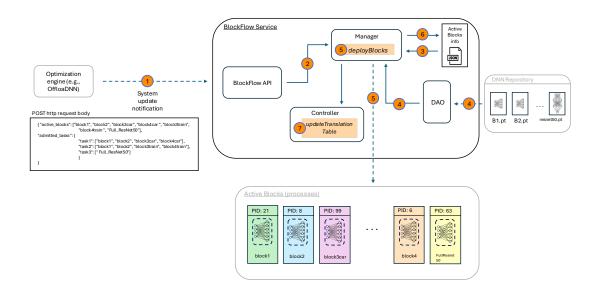

For the sake of simplicity, we skip the mathematical formulation of the DOT problem and its related heuristic (DOT solver), that the author presented in sec. IV of [9], but rather focus on the architecture and the workflow reported in fig. 2.12. The full way of functioning of OffloaDNN can be summarized into 7 main steps:

**Step 1:** Task admission request;

**Step 2:** DNN availability, network status and computing status check;

Step 3: DOT solution;

**Step 4:** Radio and computing resource allocation & DNN block selection;

**Step 5:** Activation of the selected DNN blocks;

**Step 6:** Task admission rate notification;

**Step 7:** Task result collection (end-device side);

To offload tasks, mobile devices first send a task admission request to the OffloaDNN controller (step 1). Afterwards, the controller retrieve from the Virtual

<sup>&</sup>lt;sup>1</sup>Single-Shot pruning. More on model compression techniques at ??.

Figure 2.12: OffloaDNN architecture and workflow (fig.4, p.4 at [9]).

Infrastructure Manager (VIM) and the vRAN information about the system status such as the available DNN blocks from the DNN repository and their resource requirements, as well as the current computing resource available and radio resource capacities (step 2) and then runs the DOT problem solver (step 3). Once the DOT solver finds a solution, the controller proceeds to allocate the necessary radio and computing resources (step 4) and deploys the selected DNN blocks for the tasks that are about to be admitted (step 5). After that, the controller informs the mobile device about the admitted task rates at which their tasks have been accepted (step 6). Finally, the devices can start sending input data and receiving the processed results (step 7).

#### OffloaDNN results

OffloaDNN aims to tackle the joint optimization of radio and system resources by exploiting the structural correlation about 2 or more DNN structures serving offloaded CV task at the edge. It exhibits significant gains in terms of memory resource savings when compared to previous State-of-the-Art (SoTA) optimizer such as SEM-O-RAN [15]. In particular, it reduces the computational burden of 77.3% and the average memory occupancy of 82.5% as well as the radio resources of 4.4% while increasing the offloaded tasks of 26.9%.

# Chapter 3

# **BlockFlow**

This Chapter presents **BlockFlow**, an open-source tool that aims to deploy, manage and serve modular inference pipeline intra and inter-host.

BlockFlow specifically targets application services based on DNNs, ensuring a reduced end-to-end latency between the hosting machine and the client. Moreover, it presents **TensorMQ**, a novel contribution for a low-overhead tensor transmission in modular DNN architectures (Sec. 3.4).

In the following sections are presented the System Requirements (Sec. 3.1) that **BlockFlow** has to fulfill, followed by the main Technical Challenges to be solved (Sec. 3.2).

Sec. 3.3 reports the tools used for the **BlockFlow** realization, explaining the reasons why they were chosen while sec.3.5 provides a careful and detailed explanation about the system design and the workflow.

The source code is available at https://github.com/darioruta/BlockFlow

# 3.1 System Requirements

In a context where an application needs to provide service to remote users through the network (e.g, Offloading through 5G), **BlockFlow** must be in charge of deploying and maintaining the required software infrastructure. More specifically, in a context where an application needs to fulfill DNN task based, it is fundamental that the presented tool pursues the following requirements:

- Requirement 1: receive as input the set of DNN structures to be deployed from an optimization engine (e.g., OffloaDNN) as well as the admitted tasks to be served and their optimal paths f;

- Requirement 2: selectively deploy as processes the blocks needed to respect 1-to-1 the optimal solution about DNNs structures coming from the optimization engine;

- **Requirement 3:** create logical forward passes that respect 1-to-1 the optimal paths for the admitted tasks by establishing an efficient data transmission channel between the various active blocks;

- **Requirement 4:** selectively terminate the unneeded blocks to free-up system resources;

- **Requirement 5:** monitor in real-time the system performance.

# 3.2 Technical Challenges

The realization of the tool with the requirements reported above (Sec. 3.1) includes several technical issues to be solved.

A high level idea of the thesis contribution is depicted in Figure 3.1 where in both cases, each block (right) or more generally each DNN (left) is deployed as a process.

In stark contrast to multi-threading, multiprocessing applications require Interprocess communication (IPC) techniques to let processes exchange data, usually coming with additional overheads in terms of communication latency, complexity and efficiency.

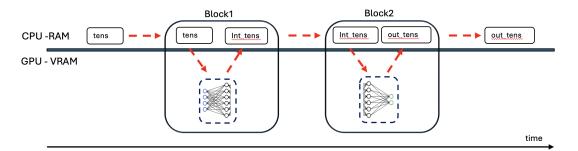

Since DNNs benefit from hardware acceleration to speed up the calculation during training and inference stages, in case of pipelined models, IPC latency overheads become even more pronounced. Without the necessary precautions, the transmission of intermediate tensors between blocks in the pipeline is CPU-bounded and could be highly inefficient both in terms of total inference latency and energy consumption. Figure 3.2 illustrates the *ping-pong* effect between RAM and VRAM during a

Figure 3.1: (left) Traditional DNN deployment for each admitted task, (right) modular DNN architecture with shared block.

generic tensor forwarding for 2 distinct processes operating on GPU. Red arrows show the data flow across the pipeline.

Figure 3.2: Ping-pong effect between RAM and VRAM.

The main challenges to solve are related to the creation of:

- a **light-weight tensor and GPU-aware IPC** to cope with the ping-pong problem improving communication efficiency and thus reducing latency;

- a modular architecture with an high degree of flexibility.

Although some existing solutions help to scale Deep Learning application they do not offer a good degree of flexibility especially during inference stages. For example, PyTorch Pipeline [16] only accepts nn.Sequential as input model and thus

the network topology becomes static: as soon as a small update in the network topology is needed the full pipeline must be turned-off and a secondary service should rewrite a new one implying service discontinuity for the clients.

As a result, use-cases with high modularity requirements must rely on general purpose communication frameworks which are known to be inefficient for tensor based communication data-flow generating the ping-pong effect in presence of hardware accelerators. In this direction, works like Pytorch RPC [17] takes into account a communication aware messaging strategy specifically targeting the DL applications. However, Pytorch RPC only provides high level APIs specifically targeted to the implementation of training applications in distributed environments. Moreover, it does not perfectly suit the goal of having a fully modular and branchy inference pipeline that can vary according to the system updated of our system optimization engine (i.e the distributed model training pipeline is created at the beginning and once interpreted, the script lives as it is until the end).

# 3.3 BlockFlow used tools

In this section, the main software tools used to develop **BlockFlow** are listed. For each tool, its main features are presented as well as the role it plays within the system.

### 3.3.1 ZeroMQ

ZeroMQ [18] is a high-performance messaging library designed for concurrent or distributed applications.

ZeroMQ enables the transmission of messages between thread or processes, in the same or even across different machines, by leveraging in-process communication mechanism (e.g., shared files) or TCP. The term "zero" is derived from the fact that communication between two entities occurs without the use of message brokers. ZeroMQ's philosophy emphasizes simplicity of the library itself; it benefits from low latency, zero licensing costs and simple administration. The added value of this library is that, through high-level calls it is possible to create different topologies between the various entities involved in a simple and efficient way and with different communication patterns, making inter-process communication as simple as inter-thread communication.

ZeroMQ provides different communication patterns:

- REQ/REP: Request/Response paradigm,

- PUSH/PULL: Producer/Consumer paradigm,

- PUB/SUB: Publisher/Subscriber paradigm,

• ROUTER/DEALER: Asynchronous Master/Slave paradigm with built-in routing capabilities.

Moreover, ZeroMQ is a multi-programming-language library, supported in C, C++,C#, Java, Python, Ruby, Dart, GO etc.

Among different general-purpose communication frameworks like gRPC, ZeroMQ

was chosen for its lightness, efficiency and flexibility to be suitable for different communication contexts, supporting different communication paradigms[19]. Several works involve the use of ZeroMQ to ensure a high-performance and light-weight communication in parallel and/or distributed applications. For example, in [20], the authors presented a novel methodology to accelerate the processing of video live stream from IP cameras offloaded to remote devices. The work enforces the use of distributed and multiprocessing architecture by using ZeroMQ as a lightweight protocol to let the remote devices communicate in pipeline. Moreover, ZeroMQ lies as high performance networking library used for the implementation of RDA3 at CERN [21]. Compared with previous versions of RDA, RDA3 scales much better and can handle high data loads and even bursts of requests.

TensorSocket [22] uses ZeroMQ as lightweight communication library in the context of multiprocessing based DNN application. However, the use-case presented in the work, takes into account the training stage. The main contribution is the reduction of the CPU usage during training by sharing the same data loader to multiple training processes (like different models or configurations) and thus reusing the same input pipeline. It uses ZeroMQ to perform Inter Process Communication.

ZeroMQ is integrated into BlockFlow to facilitate IPC. Specifically, it is employed to transmit both control and tensor-related data between distinct blocks that execute a logical forward pass.

# 3.3.2 PyTorch

PyTorch is an open source deep learning framework used to create, train and develop deep learning models. PyTorch offers a vast library of predefined modules such as tensors, network layers, optimizers and supports a wide range of use cases—from computer vision to natural language processing, from generative models to reinforcement learning. Furthermore, the official repository torchvision.models gives the possibility to download the most common neural network structures already pretrained. Among its advantages, the added value of PyTorch is its close connection to Python, allowing developers to write intuitive and readable code and simplify the prototyping and experimentation process.

PyTorch models can also be run in non-Python environments, helping to fill the gap between research prototypes and production implementation.

Indeed, TorchScript [23] allows for high model portability across different platforms. More in detail, it enables the export of trained and developed PyTorch models

from a Python environment towards environments where Python is not available, such as C++.

TorchScript facilitates three fundamental functionalities in this domain:

- optimization for production environments,

- optimized model serialization,

- Increased performance through computational graph optimization.

The creation of a TorchScript model file may be achieved through two different methods: **Tracing** (torch.jit.trace) and **Scripting** (torch.jit.script).

A Traced TorchScript model registers the operations done during a generic forward pass with an input example. Consequently, possible model dynamicity (network with more branches to be taken based on some input specific magnitudes) is lost since the export procedure depends on the input provided at that time. Conversely, a Scripted model performs a static code compilation and thus it can handle model dynamicity. This is particularly useful for those NNs structures like Recurrent Neural Networks or Branchy—Nets.

PyTorch is used in BlockFlow to export, run and deploy the Blocks.

### 3.3.3 CherryPi

CherryPi [24] is a minimalist web framework written in Python that allows the development of web applications, enabling server-side code to be written in a similar way to a normal Python program. CherryPi incorporates a thread-pool HTTP/1.1 server, handles HTTP requests in a multi-threaded manner and provides built-in tools such as flexible configuration, session management, caching and authentication. CherryPi is particularly well suited for:

- Rest API implementation, due to the ease with which URIs and various HTTP methods are handled;

- light—weight web applications realization;

In this work, CherryPi is used to create a REST API that will serve as an entry point for system updates.

#### 3.3.4 Pickle

Pickle is a Python module that implements binary protocols for the serialization and deserialization of Python object structures. Serialization (pickling), is the process of converting an object in memory into a stream of bytes that can be saved

to a file or transmitted over a network. Conversely, the deserialization (unpickling) involves the reconstruction of the original object from the byte stream. This serialization/deserialization procedure is done every time information messages are delivered through ZeroMQ.

The pickle library supports multiple versions of the protocol, numerically identified from 0 to 5 (the larger the prot. version the newer is the serialization algorithm). This thesis work used the protocol number 5.

#### 3.3.5 Psutil

Psutil [25] is a cross-platform Python library for accessing information about running processes and system resource usage.

In practice, Psutil offers the possibility to retrieve values such as CPU usage, memory usage, both at the system level and in a more fine-grained way for each individual process by providing the PID.

In this case, Psutil is used to create a resource monitoring system through the use of an entity dedicated to this purpose.

### 3.3.6 Python NVIDIA Management Library

PyNVML [26] (Python NVIDIA Management Library) is a Python module that allows to monitor NVIDIA GPUs directly from Python scripts.

In practice, it is a Python wrapper for the NVIDIA Management Library. PyNVML allows to analyze the status of all GPUs equipped on a computing platform and monitor metrics such as GPU load, memory usage, temperatures, driver status, clock levels, etc.

This has made it possible to integrate the collection of GPU's performance metrics within the application code itself for a detailed and fine-grained analysis of each component of the system (i.e., blocks, dispatchers).

PyNVML is used with the purpose to carefully assess how the various system components occupy the GPU computing resources.

# 3.3.7 Nvidia nvprof

Nvidia nvprof [27] is a command-line tool from the CUDA Toolkit that collects execution data for applications running on NVIDIA GPUs. It allows analysis of CUDA kernel performance, memory transfers between host (CPU) and device (GPU), and CUDA API calls. It offers the possibility to log or visualize the data collected during testing.

In this work, **nvprof** was of crucial importance in evaluating memory transfers between the various blocks of the pipeline for each single inference.

#### 3.3.8 Taskset & Numactl

Both of the tools presented in this section were used to ensure the reproducibility of experiments and optimize the use of computational resources in multi-core and multi-socket architectures. In practice, these tools were used to control process affinity and ensure that the tests launched actually operated in the target cores in order to provide clear explanations for the output results.

Taskset is a command available in Linux operating systems, used to set or retrieve the CPU affinity of a process. Using Taskset, it is possible to specify the set of cores on which the launched process can run.

Likewise, NUMA control (numactl) is a Linux command line tool that allows to run processes with a specific scheduling and memory allocation policy for NUMA (Non-Uniform Memory Access) architectures. In a more simplified way with respect to Taskset, numactl allows to directly bind a running program in a target NUMA node by setting the parameter cpunodebind. Moreover, for multiprocessing appplications like BlockFlow, it forces the spawn of new processes over the same NUMA node automatically.

# 3.4 TensorMQ: tensor-aware inter-block communication via CUDA-IPC and ZeroMQ

This section presents **TensorMQ**, the main contribution of this thesis work in line with **Objective 2** reported in sec 1.2.2 and in view of what has been said in the previous section (3.2).

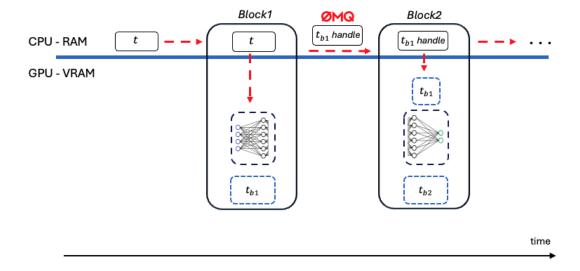

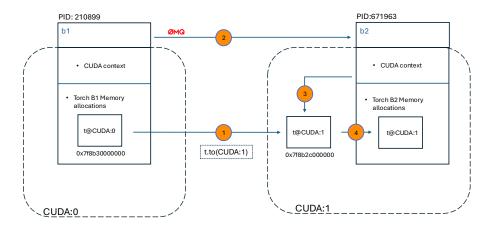

It uses ZeroMQ to deliver information-based communication messages between blocks with low overheads and good adaptability to different inference contexts. For a generic tensor t, TensorMQ exploits CUDA IPC jointly with ZeroMQ to deliver tensors between blocks. More specifically, considering 2 blocks (e.g., block1, block2) and a generic tensor  $t_{b1}$  coming out from block1, TensorMQ solves the ping-pong problem by:

- generating an *IPC handle* (i.e GPU memory region address where the tensor lives) through the cudaIpcGetMemHandle [28] enriched with some additional tensor specific meta-data

- forwarding information rich message to the next block (tensor-handle & metadata).

Upon receiving the message, *block2*, maps a new empty storage torch object and reconstruct the tensor using cudalpcOpenMemHandle.

As consequence, once the tensor enters the system, it never leaves the GPU, significantly increasing overall pipeline latency performance.

Figure 3.3 clearly shows the workflow. More detailed information about the handle creation and tensor reconstruction procedures as well as the handle structure can be found in sec.3.5.

Figure 3.3: IPC handle deliver through TensorMQ.

# 3.5 Architectural Design

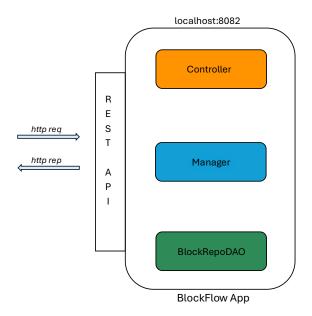

According to what presented in the system requirements in sec 3.1, BlockFlow has a modular architecture able to satisfy the system's needs. In this section the design schema is presented.

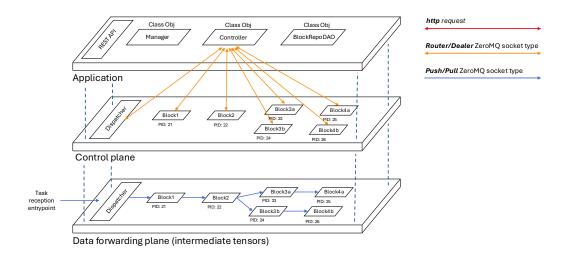

Figure 3.5 provides a visualization of the components in the system architecture. The main characters are:

- REST API,

- Manager,

- Controller,

- Block (generic),

- Dispatcher.

Figure 3.4: BlockFlow application components.

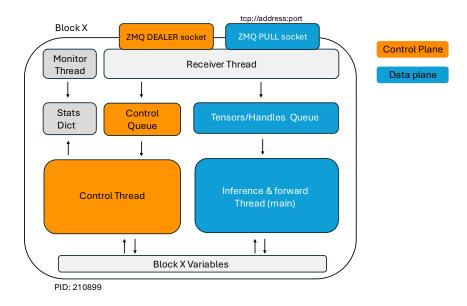

The first 3 elements of this bullet list belong to the Control Plane, responsible for managing, orchestrating, and configuring the modular DNN architecture, respecting 1-to-1 the system updates provided by the resource optimization engine.

In particular, the system control entry-point is a REST API implemented in CherryPi, exposing some CRUD methods to manage the system such as selective block pinging, system updates notification and termination of one or more blocks.

The *Manager* is a python object (class) in charge of handling the full block's life-cycle as well as keeping track about the processes alive. When a new *system update* arrives, the *manager* instance is called and it spawns as processes the set of new blocks to be deployed and selectively terminate the unneeded ones. In addition to that, it periodically performs health checks to the active blocks by sending ping messages through the controller.

The *Controller* is a python object devoted to deliver control messages with ZeroMQ to the various active blocks in the systems. It serves the needs of the manager offering the possibility to notify block specific messages such as ping, store and termination messages as well as health-status messages for monitoring purposes. It operates in a synchronous way and it incorporates a simple block fail detection

Figure 3.5: BlockFlow application planes.

#### technique.

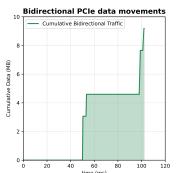

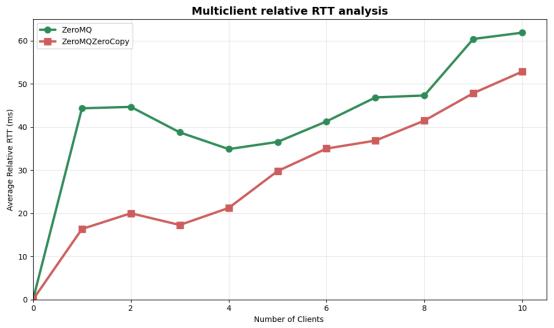

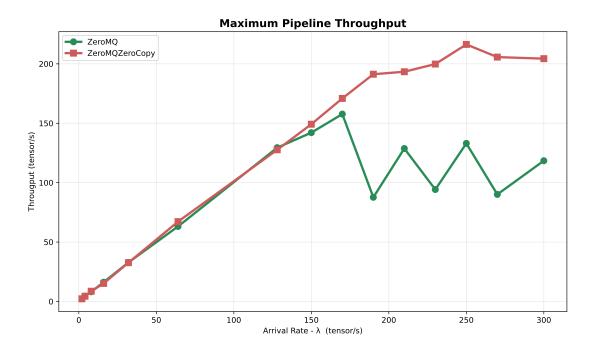

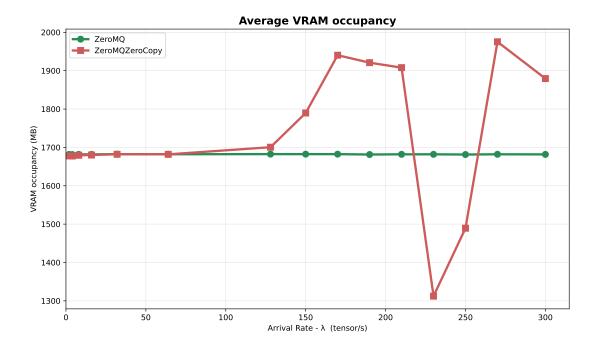

The Data Plane of BlockFlow is split into two logical topologies: one devoted to the distribution of control messages while another devoted to the distribution of intermediate results between blocks in the pipeline.