### POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

Master's Degree Thesis

## Analysis and Design of a Digital-Based Operational Transconductance Amplifier for Neural Signal Acquisition

**Supervisors**

Prof. Paolo Stefano Crovetti

Caterina Verny

Candidate

Prof. Sandro Carrara

2024/25

### Abstract

The thesis activity is in the framework of the European research project CEREBRO, which aims to develop a new non-invasive brain imaging technique with higher spatial resolution than conventional EEG, which is limited by signal attenuation through the skull. To overcome this limitation, the project proposes acquiring neural signals directly at the brain interface and transmitting them at higher frequencies, reducing the effect of signal loss through skull. This approach requires the design of tens-of-micrometer scale, remotely-powered CMOS circuits capable of detecting very low-amplitude brain signals and enabling wireless transmission.

This thesis addresses one of the main challenges of the CEREBRO system by exploring and adapting the concept of the Digital-Based Operational Transconductance Amplifier (DIGOTA) as a neural-interface amplifier. This architecture provides a promising solution to reduce both power consumption and silicon area while maintaining adequate performance for neural signal acquisition.

A key innovation of this work is also the use of the intrinsic resistive and capacitive properties of the electrodes, usually considered parasitic, as functional elements in the circuit. Instead of implementing dedicated resistors and capacitors on silicon, the characteristics of the electrode—solution interface and the coupling between electrodes are exploited as part of the circuit design. This strategy allows for a significant reduction of area.

A differential-output, fully passive-free version of DIGOTA was designed and implemented using Cadence Virtuoso. The circuit was first simulated with a simplified electrode model and later with a more detailed one, including frequency-dependent elements, to better represent real-world conditions. Simulation results show that the circuit output is a train of pulses whose amplitude depends on the input signal. This behavior allows the same circuit to be used for both signal acquisition and direct high-frequency data transmission, eliminating the need for a VCO block and thus saving additional area and power. To better control the pulse frequency and further reduce power consumption, an additional capacitance was introduced in the compensation stage.

One of the challenges was the lack of a accurate model for the electrodes to be used in the simulation. To overcome this, parameters from existing studies were

adapted, and simulations were performed across a wide range of values to ensure robustness.

The final circuit layout was designed to meet strict area constraints. Post-layout simulations, including Corner Analysis and Monte Carlo analysis, were performed and compared with schematic-level results to evaluate the effects of parasitics and process variations.

As a final step, a MATLAB script that calculates the conductance between all electrode pairs was used to explore various electrode geometries and arrangements, including both actual and floating dummy electrodes. The configuration that best matched the circuit model assumptions was selected and implemented in the final layout.

The circuit has now been sent for fabrication, and the next step is to conduct test both on the standalone amplifier and in a test setup reproducing the characteristics of the operating environment. These tests will also provide the opportunity to further refine the electrode models, improving the design and making necessary adjustments based on the measured performance.

# Table of Contents

| Li | st of | Tables                                                         | VII  |

|----|-------|----------------------------------------------------------------|------|

| Li | st of | Figures                                                        | VIII |

| 1  | Intr  | roduction                                                      | 1    |

| 2  | Elec  | ctrode Models                                                  | 3    |

|    | 2.1   | Neural Electrode Model                                         | . 4  |

|    | 2.2   | Electrochemical Electrode Model                                | . 6  |

| 3  | Dig   | ital-Based OpAmp                                               | 10   |

|    | 3.1   | Introduction and Context                                       | . 10 |

|    | 3.2   | Digital-Based OTA Behavior                                     | . 13 |

|    | 3.3   | DB-OTA circuit                                                 | . 16 |

|    | 3.4   | Digital OTA (DIGOTA) circuit                                   | . 17 |

|    | 3.5   | Time-Multiplexed Digital Differential Amplification $(TMD^2A)$ | . 20 |

|    | 3.6   | Comparison                                                     | . 24 |

| 4  | Idea  | al Behavioral Modeling of DIGOTA                               | 26   |

|    | 4.1   | Simulink Model                                                 | . 26 |

|    | 4.2   | Closed-Loop Simulations                                        | . 28 |

|    |       | 4.2.1 Closed-Loop Circuit Configuration                        | . 28 |

|    |       | 4.2.2 Parameters and Inputs                                    | . 29 |

|    |       | 4.2.3 Output $v_{out}$                                         | . 30 |

|    |       | 4.2.4 Compensation signal $v_{cmp}$                            | . 30 |

|    |       | 4.2.5 Internal signals                                         | . 32 |

|    |       | 4.2.6 Frequency analysis                                       |      |

|    | 4.3   | Bode Diagram                                                   | . 34 |

|    | 4.4   | Differential Gain                                              |      |

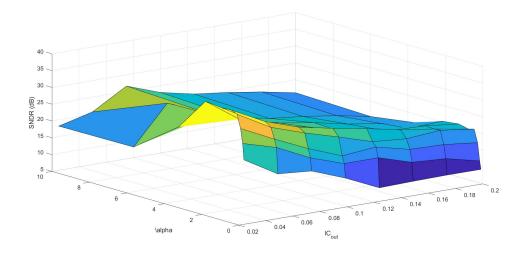

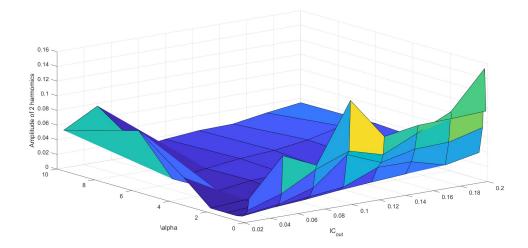

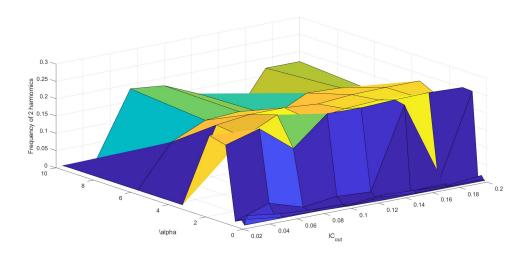

|    | 4.5   | SNDR                                                           | . 38 |

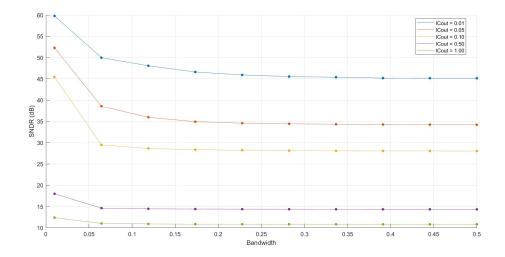

|    |       | 4.5.1 Effects of Parameter Variation                           | . 40 |

|    |       |                                                                |      |

|              | 4.6   | Parameter Dependence                          | 2 |

|--------------|-------|-----------------------------------------------|---|

| 5            | Circ  | cuit Design 5                                 | 0 |

|              | 5.1   | CEREBRO project                               | 0 |

|              | 5.2   | DIGOTA topology                               | 2 |

|              | 5.3   | Conventional configuration                    | 5 |

|              |       | 5.3.1 Circuit behavior and internal signals 5 | 5 |

|              |       | 5.3.2 Bandwidth                               | 9 |

|              |       | 5.3.3 Noise                                   | 9 |

|              | 5.4   | Simplified Electrode-Based Configuration 6    | 2 |

|              |       | 5.4.1 Circuit behavior                        | 0 |

|              | 5.5   | Enhanced Electrode-Based Configuration        | 3 |

|              | 5.6   | Layout                                        | 6 |

|              | 5.7   | Post-Layout Simulations                       | 7 |

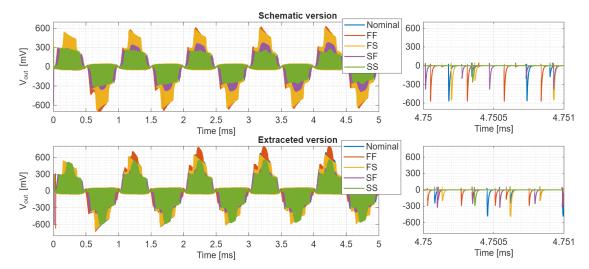

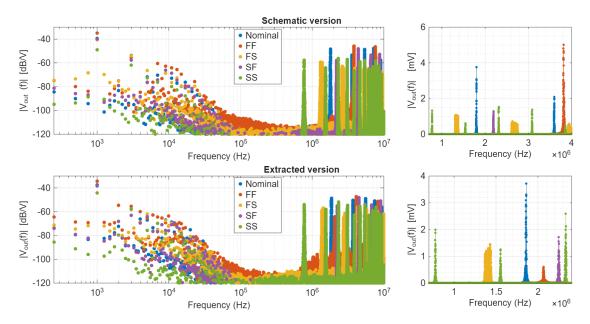

|              |       | 5.7.1 Output simulations                      | 8 |

|              |       | 5.7.2 Noise simulations                       | 9 |

|              |       | 5.7.3 Corner Analysis                         | 9 |

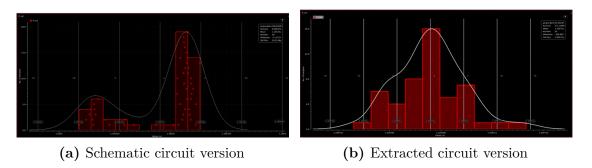

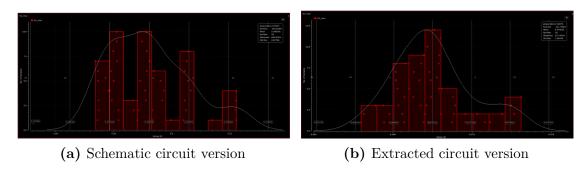

|              |       | 5.7.4 Monte Carlo Simulation                  | 2 |

|              | 5.8   | Electrode Layout                              | 3 |

| 6            | Con   | clusion and Future Work 8                     | 6 |

| $\mathbf{A}$ | Mat   | slab code 8                                   | 9 |

|              | A.1   | Bode diagram                                  | 9 |

|              |       | SNDR 9                                        | 4 |

| Bi           | bliog | craphy 9                                      | 8 |

# List of Tables

| 3.1  | Comparison between different Digital-Based OTA Implementations           | 25 |

|------|--------------------------------------------------------------------------|----|

| 5.1  | Specification for CEREBRO circuit                                        | 51 |

| 5.2  | Truth table of the DIGOTA input stage                                    | 53 |

| 5.3  | Truth table of the DIGOTA compensation stage                             | 54 |

| 5.4  | Truth table of the DIGOTA output stages                                  | 54 |

| 5.5  | Design parameters of the DIGOTA circuit                                  | 56 |

| 5.6  | Comparison for different numbers of input inverters per input branch.    | 60 |

| 5.7  | Component values of the circuit configuration considering simple         |    |

|      | electrode model                                                          | 63 |

| 5.8  | Transistor dimensions used in simulations for the output stage analysis. | 67 |

| 5.9  | Transistor dimensions used in simulations for the compensations          |    |

|      | stage analysis                                                           | 68 |

| 5.10 | Selected transistor dimensions for output and compensation stages.       | 69 |

| 5.11 | Component values of the enhanced circuit configuration                   | 74 |

# List of Figures

| 2.1  | Impedance spectra acquired in the experiment (a) modulus and (b)                                                                                                                                   | 5  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | phase [2]                                                                                                                                                                                          | 9  |

|      | b) Model for spectra acquired in the second part of the experiment [2].                                                                                                                            | 6  |

| 2.3  | Trend of the different fitting parameters derived from EEC modeling of spectra [2]                                                                                                                 | 7  |

| 2.4  | Different models for the equivalent circuit of an electrode of the electrochemical cell [3]                                                                                                        | 8  |

| 2.5  | The risk of saturation on the voltage measured at the electrode and simulated by the different models. The highlighted time interval shows the operation of the potentiostat before saturation [3] | 8  |

| 2.6  | Electrochemical impedance spectroscopy of planar Pt/Ir microelectrode and the fitted electrical models [3]                                                                                         | 9  |

| 3.1  | IRDS Roadmap                                                                                                                                                                                       | 11 |

| 3.2  | Analog differential pair                                                                                                                                                                           | 13 |

| 3.3  | Digital buffer pair                                                                                                                                                                                | 14 |

| 3.4  | Digital output configurations and implications on DM and CM input signals                                                                                                                          | 15 |

| 3.5  | DB-OTA schematic [7]                                                                                                                                                                               | 16 |

| 3.6  |                                                                                                                                                                                                    | 18 |

| 3.7  |                                                                                                                                                                                                    | 19 |

| 3.8  | DIGOTA circuit operations throughout its digital states when $v_D \geq 0$                                                                                                                          | 20 |

| 3.9  | Concept diagram of the Time-Multiplexed Digital Differential Am-                                                                                                                                   | 21 |

| 3.10 |                                                                                                                                                                                                    | 22 |

| 3.11 | State transition graph of the DB-Amp control unit [15]                                                                                                                                             | 23 |

| 3.12 | Sequence of switch configurations corresponding to the states in                                                                                                                                   |    |

|      | Fig.3.11 [15]                                                                                                                                                                                      | 24 |

| 4.1  | Simulink model of the Digital-Based OTA (DIGOTA)                                                                                        | 27 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2  | Simulink model of a feedback-configured DB-OTA                                                                                          | 29 |

| 4.3  | Behavior of $v_{in}$ and $v_{out}$ with $f_{in} = 10^{-3}$ , $\beta = 1$ , $I/C_{out} = 0.1$ ,                                          |    |

|      | $I/C_{cmp} = 0.2. \dots $         | 30 |

| 4.4  | Behavior of $v_{in}$ and $v_{out}$ with $f_{in} = 10^{-3}$ , $\beta = 0.2$ , $I/C_{out} = 0.1$ ,                                        |    |

|      | $I/C_{cmp} = 0.2. \dots $         | 31 |

| 4.5  | Behavior of $v_{in}$ , $v_{out}$ and $v_{cmp}$ with $f_{in} = 10^{-3}$ , $\beta = 1$ , $I/C_{out} = 0.1$ ,                              |    |

|      | $I/C_{cmp} = 0.2. \dots $         | 31 |

| 4.6  | Behavior of internal signals with $f_{in} = 10^{-3}$ , $\beta = 1$ , $I/C_{out} = 0.1$ ,                                                |    |

|      | $I/C_{cmp} = 0.2. \dots $         | 32 |

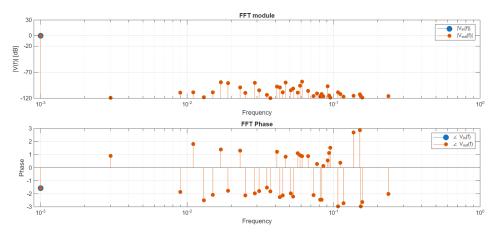

| 4.7  | FFT of $v_{in}$ and $v_{out}$ with $f_{in} = 10^{-3}$ , $\beta = 1$ , $I/C_{out} = 0.1$ , $I/C_{cmp} = 0.2$ .                           | 33 |

| 4.8  | FFT of $I_{out}$ , $I_{out,p}$ and $I_{out,n}$ with $f_{in} = 10^{-3}$ , $\beta = 1$ , $I/C_{out} = 0.1$ ,                              |    |

|      | $I/C_{cmp} = 0.2.$                                                                                                                      | 33 |

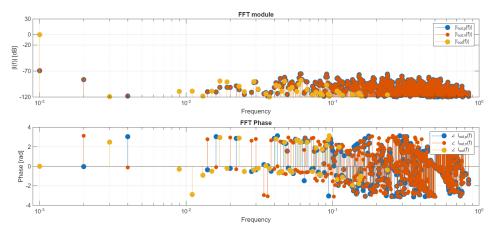

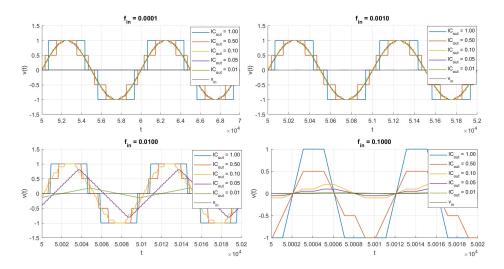

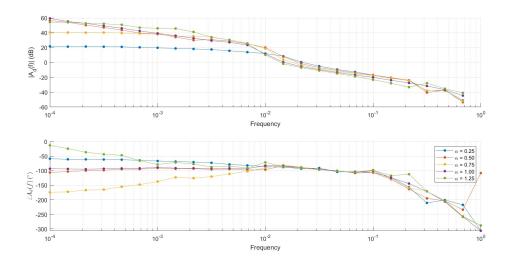

| 4.9  | Behavior of $v_{\text{out}}$ for different values of $\frac{I_{\text{out}}}{C_{\text{out}}}$ with $\beta = 1$ , $\alpha = 0.5$          | 35 |

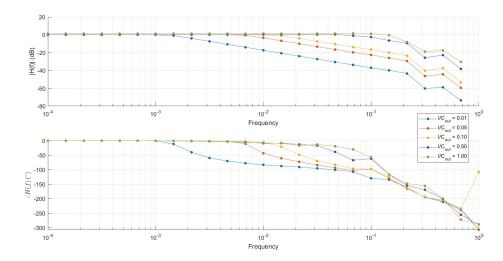

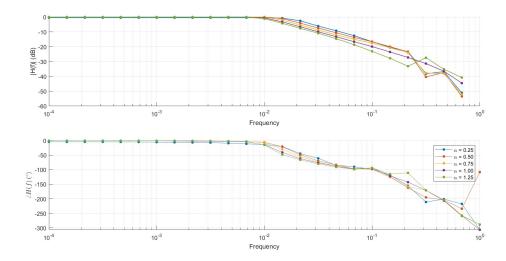

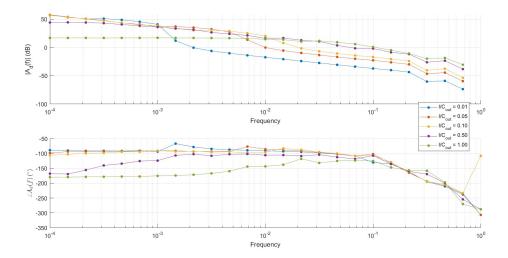

| 4.10 | Bode diagram for different values of $\frac{I_{\text{out}}}{C_{\text{out}}}$ with $\beta = 1, \alpha = 0.5$                             | 36 |

| 4.11 | Behavior of $v_{\text{out}}$ for different values of $\alpha$ with $\beta = 1$ , and constant $\frac{I_{\text{out}}}{C_{\text{out}}}$ . | 36 |

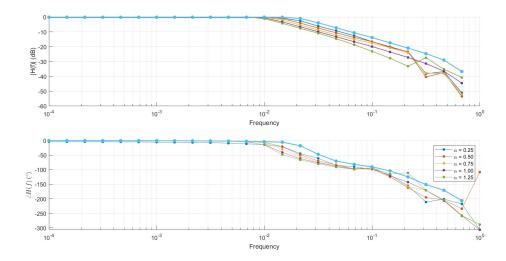

| 4.12 | Bode diagram for different values of $\alpha$ with $\beta = 1$ , and constant $\frac{I_{\text{out}}}{C_{\text{out}}}$ .                 | 37 |

|      | Behavior of $v_{\text{out}}$ for input signals with reduced amplitude ( $v_{\text{in}} =$                                               |    |

|      | $0.1 \cdot \sin(2\pi ft)$ and $\beta = 1$ , $\alpha = 0.5$                                                                              | 37 |

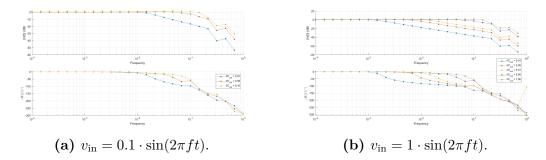

| 4.14 | Comparison of Bode diagrams for input signals with different ampli-                                                                     |    |

|      | tudes, $\beta = 1$ , $\alpha = 0.5$                                                                                                     | 38 |

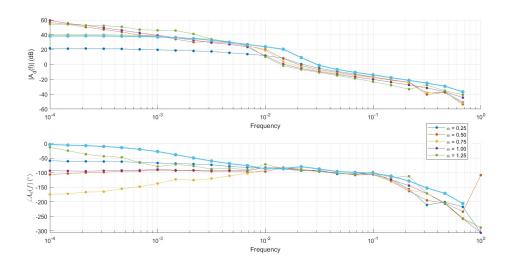

| 4.15 | Differential gain $A_d(f_{\text{in}})$ for different values of $\frac{I_{\text{out}}}{C_{\text{out}}}$ with $\beta = 1$ and             |    |

|      | $\alpha = 0.5.$                                                                                                                         | 39 |

| 4.16 | Differential gain $A_d(f_{\text{in}})$ for different values of $\frac{I_{\text{out}}}{C_{\text{out}}}$ with $\beta = 1$ and             |    |

|      | $\alpha = 0.5.$                                                                                                                         | 39 |

| 4.17 | Differential gain $A_d(f_{\rm in})$ for different values of $\alpha$ with $\beta = 1$ and                                               |    |

| 4.10 | $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.1.$                                                                                          | 40 |

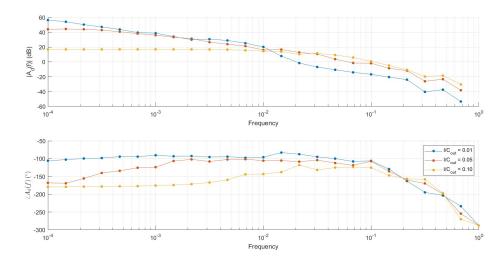

|      | SNDR for $\alpha = 0.5$ , $\beta = 1$                                                                                                   | 41 |

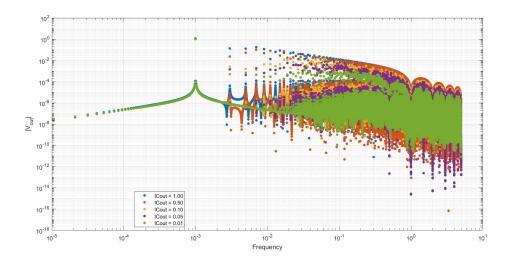

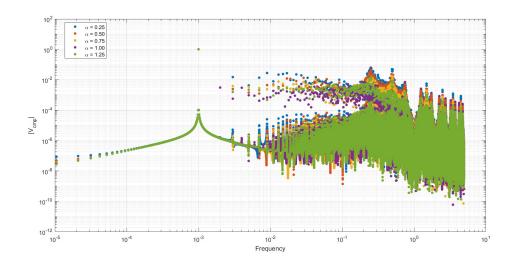

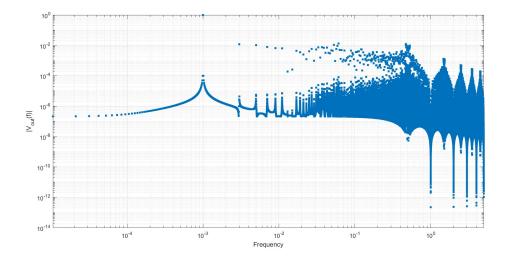

|      | FFT of $v_{\text{out}}$ for $\alpha = 0.5$ , $\beta = 1$                                                                                | 41 |

| 4.20 | FFT of $v_{\text{cmp}}$ for $\alpha = 0.5$ , $\beta = 1$                                                                                | 42 |

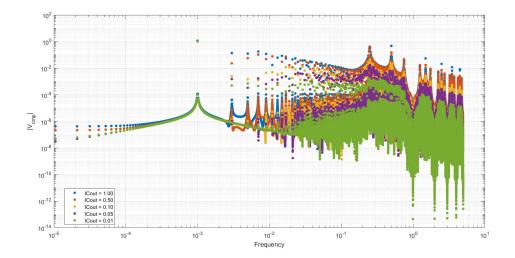

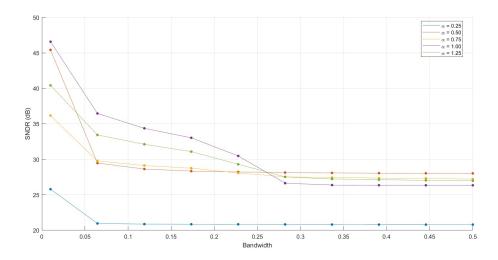

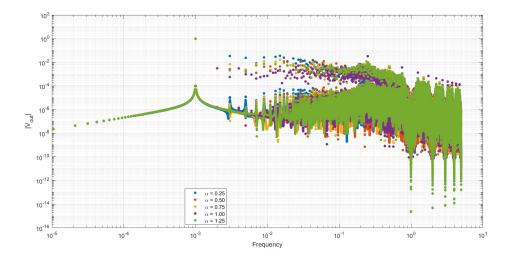

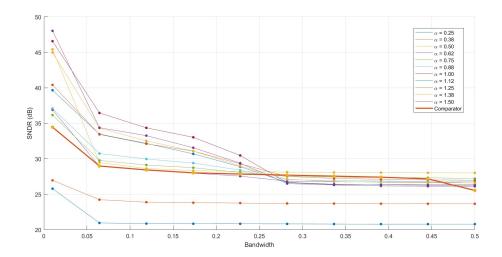

| 4.21 | SNDR for $\frac{t_{\text{out}}}{C_{\text{out}}} = 0.1$ , $\beta = 1$                                                                    | 42 |

| 4.22 | SNDR for $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.1$ , $\beta = 1$                                                                    | 43 |

| 4.23 | FFT of $v_{\rm cmp}$ for $\frac{v_{\rm cmp}}{C_{\rm out}} = 0.1$ , $\beta = 1$                                                          | 43 |

| 4.24 | Zoom of $v_{\text{out}}(t)$ for $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.1$ , $\beta = 1$                                             | 44 |

| 4.25 | Circuit diagram implemented with an ideal comparator                                                                                    | 44 |

| 4.26 | FFT of $v_{\text{out}}(t)$ calculated with an ideal comparator for $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.1$ ,                      |    |

|      | $\beta = 1.$                                                                                                                            | 45 |

| 4.27 | Bode plot comparison for DB-OTA and ideal comparator for $\frac{I_{\text{out}}}{C_{\text{out}}} =$                                      |    |

|      | $0.1, \beta = 1. \dots $          | 46 |

| 4.28 | Comparison of $A_d$ for DB-OTA and ideal comparator for $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.1$ ,                                                | 46 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.20 | $\beta=1$                                                                                                                                              | 40 |

| 4.29 | SNDR comparison for DB-OTA and ideal comparator for $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.1$ , $\beta = 1, \dots, \dots, \dots$                   | 47 |

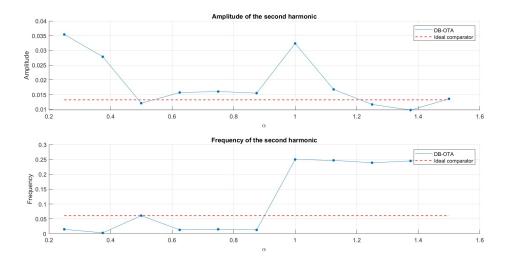

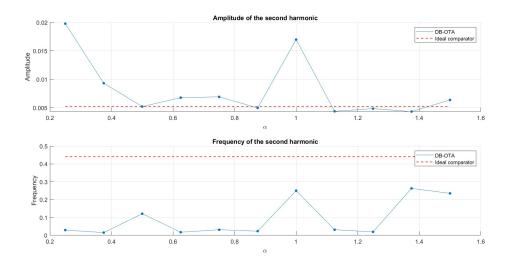

| 4.30 | Amplitude and frequency of the main harmonic following the funda-                                                                                      | 41 |

| 4.50 |                                                                                                                                                        | 47 |

| 1 21 | mental for DB-OTA and ideal comparator with $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.1$ , $\beta = 1$ .                                              | 41 |

| 4.31 | Amplitude and frequency of the main harmonic following the funda-<br>mental for DR OTA and ideal comparator with $I_{\text{out}} = 0.05$ , $\beta = 1$ | 48 |

| 4.00 | mental for DB-OTA and ideal comparator with $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.05$ , $\beta = 1$ .                                             |    |

|      | Higher SNDR $SNDR = 38$ for $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.025$ and $\alpha = 2.$                                                          | 48 |

|      | Lower amplitude of the second harmonic for $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.025$ and $\alpha = 0.75$ .                                       | 49 |

| 4.34 | Highest frequency of the second harmonic for $\frac{I_{\text{out}}}{C_{\text{out}}} = 0.17$ and $\alpha = 1.3$ .                                       | 49 |

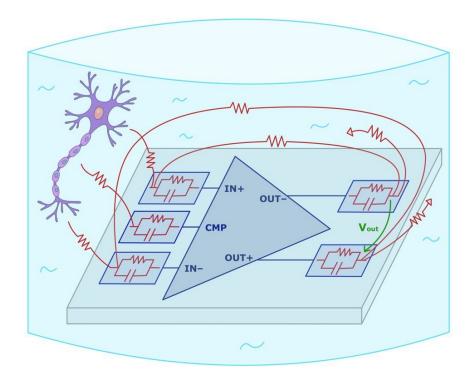

| 5.1  | Overview of the CEREBRO system                                                                                                                         | 50 |

| 5.2  | Overview of the proposed system configuration                                                                                                          | 52 |

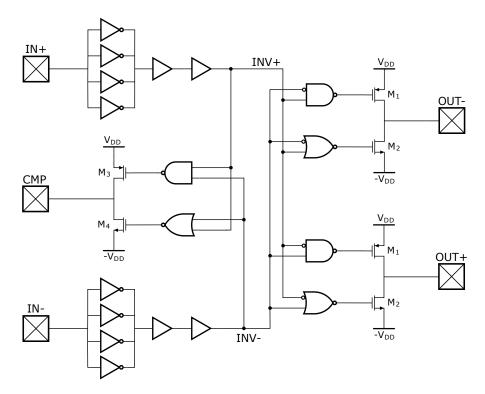

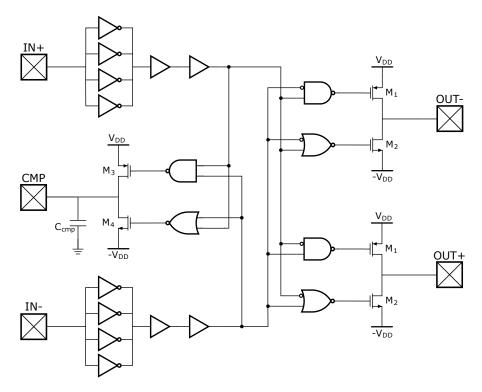

| 5.3  | DIGOTA topology                                                                                                                                        | 53 |

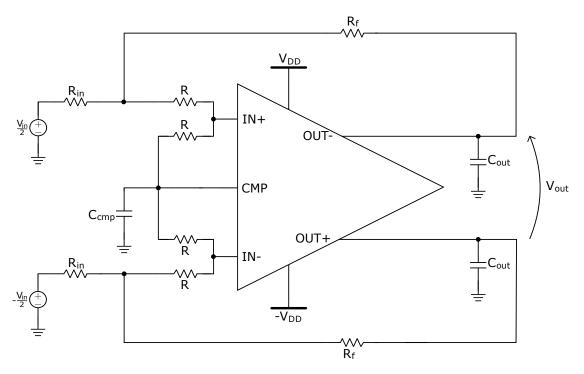

| 5.4  | Differential configuration                                                                                                                             | 55 |

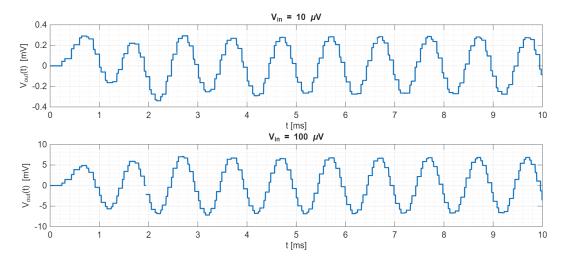

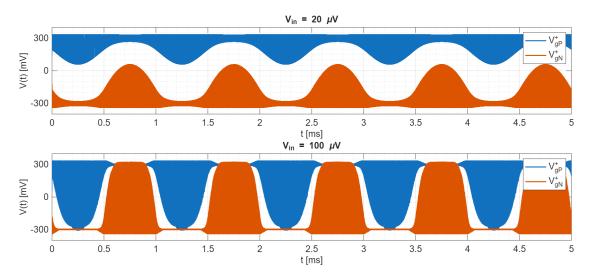

| 5.5  | Differential output $V_{out}$ for different input amplitudes                                                                                           | 56 |

| 5.6  | INV+ and INV- logic signals and gate voltage signals for output                                                                                        |    |

|      | and compensation transistors                                                                                                                           | 57 |

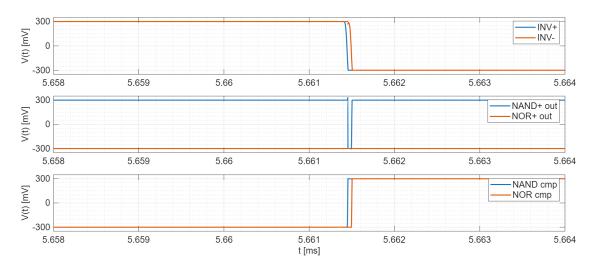

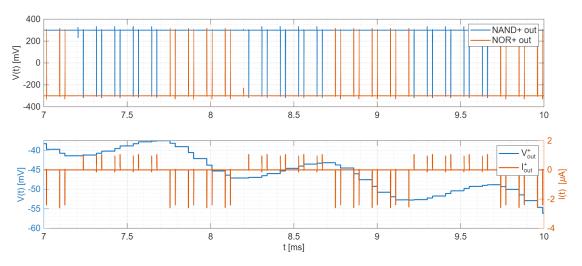

| 5.7  | Output stage logic signals and resulting $V_{out}^+$ and $I_{out}^+$ signals                                                                           | 57 |

| 5.8  | $V_{out}^+, V_{out}^-$ and $V_{out}$ signals                                                                                                           | 58 |

| 5.9  | FFT Magnitude of $V_{out}$                                                                                                                             | 58 |

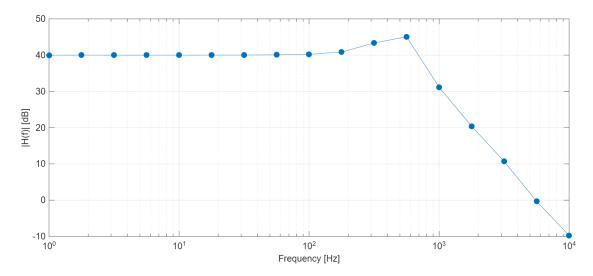

| 5.10 | Magnitude of Bode Diagram                                                                                                                              | 59 |

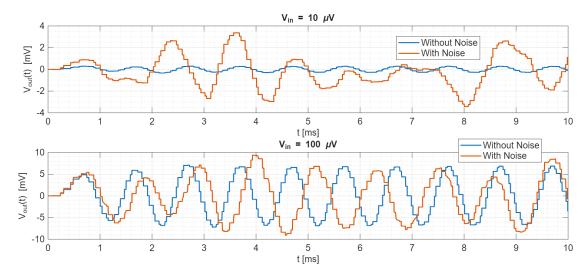

| 5.11 | Comparison between differential output with and without noise for                                                                                      |    |

|      | different input amplitudes                                                                                                                             | 61 |

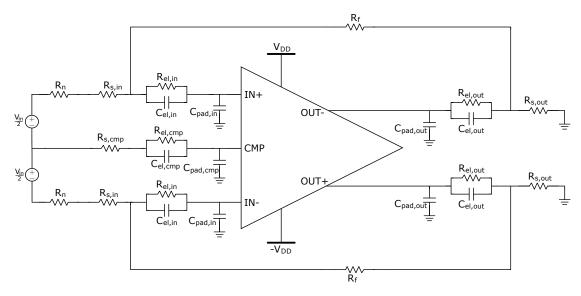

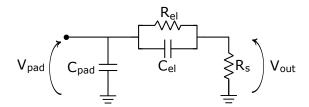

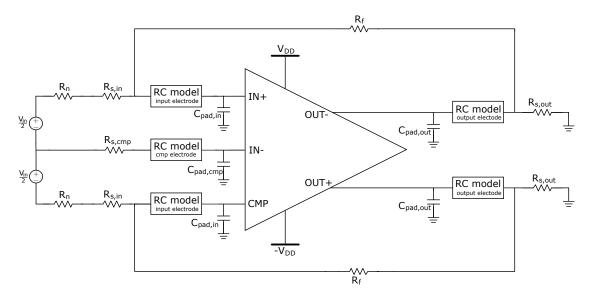

| 5.12 | DIGOTA with electrode models configuration                                                                                                             | 62 |

| 5.13 | Differential output $V_{out}$ and its zoom view for different input ampli-                                                                             |    |

|      | tudes                                                                                                                                                  | 64 |

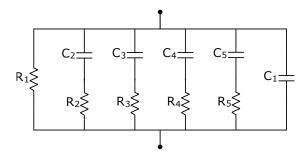

| 5.14 | Equivalent electrical model of an output electrode                                                                                                     | 64 |

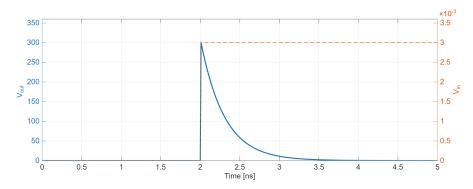

| 5.15 | Step response of the output electrode's transfer function                                                                                              | 64 |

| 5.16 | Zoom of $V_{out}^+$ , $V_{out}^-$ and $V_{out}$                                                                                                        | 65 |

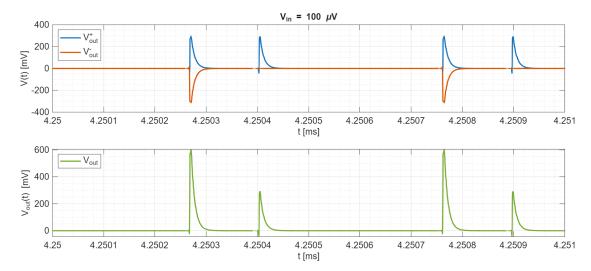

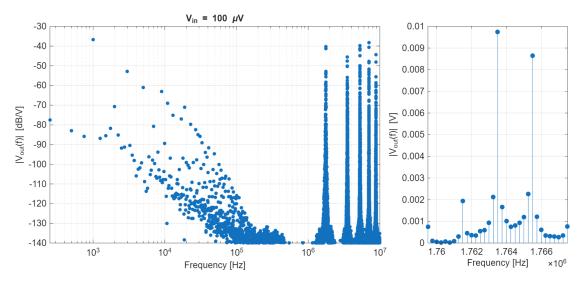

|      | DFT magnitude of $V_{out}$ and zoomed view around the spike repetition                                                                                 |    |

|      | frequency                                                                                                                                              | 65 |

| 5.18 | DIGOTA schematic with the compensation capacitor                                                                                                       | 66 |

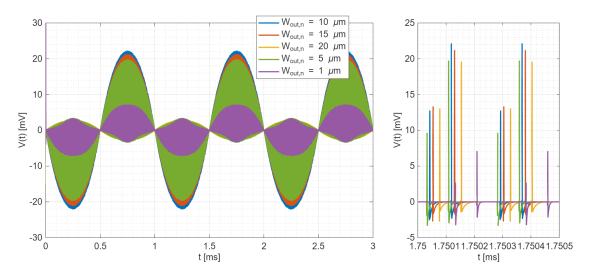

| 5.19 | Comparison of $V_{out}$ for different $W_{out}$ values                                                                                                 | 67 |

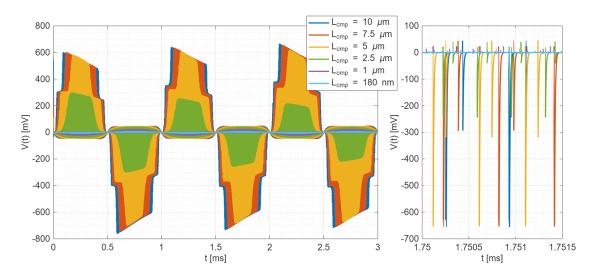

| 5.20 | Comparison of $V_{out}$ for different $L_{cmp}$ values                                                                                                 | 68 |

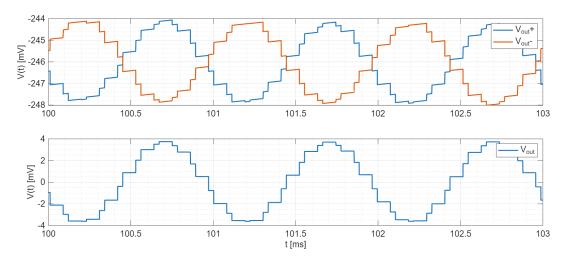

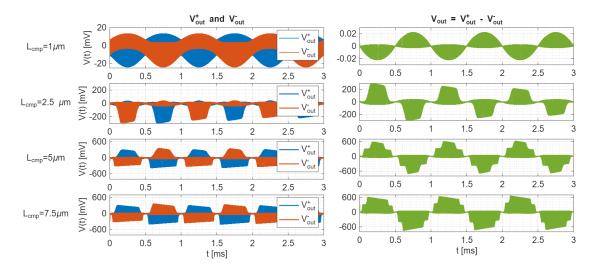

|      | Plot of $V_{out}^+$ , $V_{out}^-$ and $V_{out}$ for different $L_{cmp}$ values                                                                         | 69 |

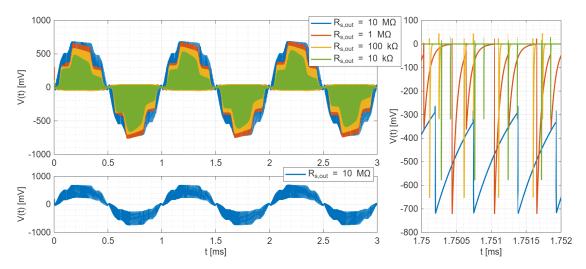

|      | Comparison of $V_{out}$ for different $R_s$ values                                                                                                     | 70 |

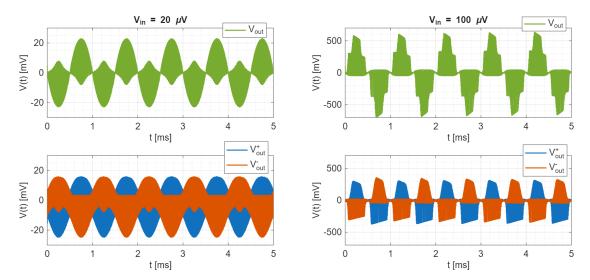

| 5.23 | Differential output $V_{out}$ and single-ended output $V_{out}^+$ and $V_{out}^-$ for                                                                  |    |

|      | different input amplitudes                                                                                                                             | 71 |

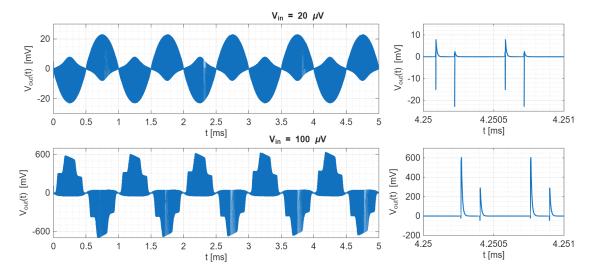

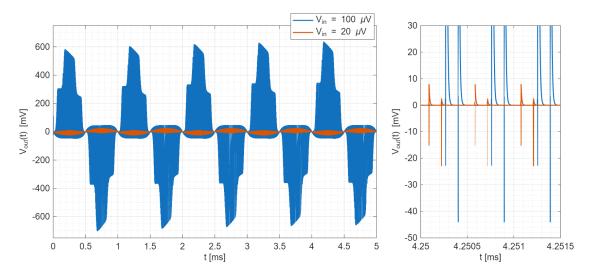

| 5.24        | Comparison between differential output $V_{out}$ for different input amplitudes and zoom on thier undesired spikes | 7             |

|-------------|--------------------------------------------------------------------------------------------------------------------|---------------|

| 5 25        |                                                                                                                    | 1.            |

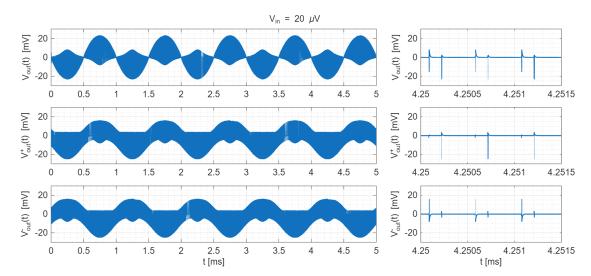

| 5.25        | Differential output $V_{out}$ and single-ended output $V_{out}^+$ and $V_{out}^-$ for $V_{out}^- = 20 \text{ eV}$  | 7:            |

| 5 26        | $V_{in} = 20 \mu\text{V}.$ Gate control signals $V_{aP}^+$ and $V_{aN}^+$ (outputs of the NAND and NOR             | 1.            |

| 5.20        |                                                                                                                    | 7:            |

| 5 27        | gates, respectively) for different input amplitudes                                                                | 7:            |

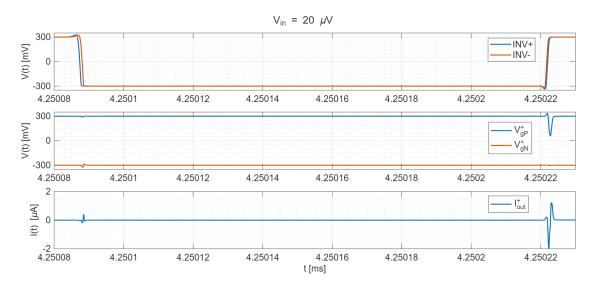

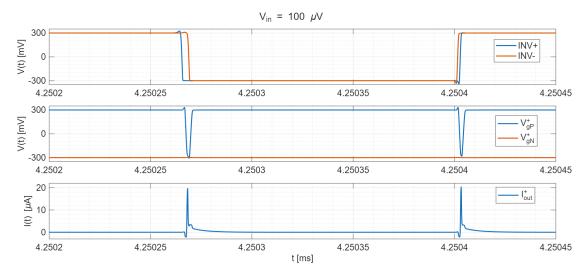

| 5.21        | Zoom of INV+, INV-, $V_{gP}^+$ , $V_{gN}^+$ and $I_{out}^+$ signals for $V_{in} = 20 \mu\text{V}$                  | 7             |

|             | Zoom of INV+, INV-, $V_{gP}^+$ , $V_{gN}^+$ , and $I_{out}^+$ signals for $V_{in}=100\mu\text{V}$ .                | $7^{\prime}$  |

|             | Enhanced electrode model                                                                                           | 7!            |

|             | DIGOTA schematic including the enhanced electrode model                                                            |               |

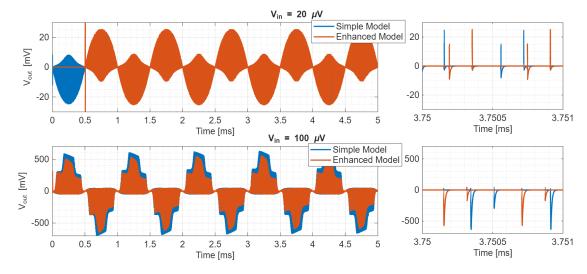

|             | Comparison of $V_{out}$ for different models                                                                       | $\frac{7}{7}$ |

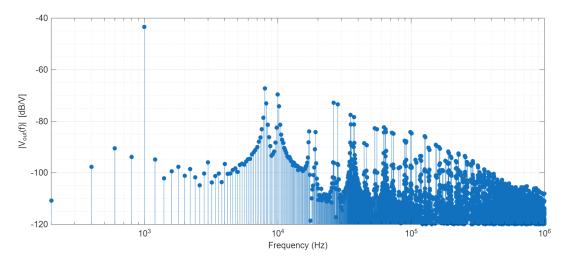

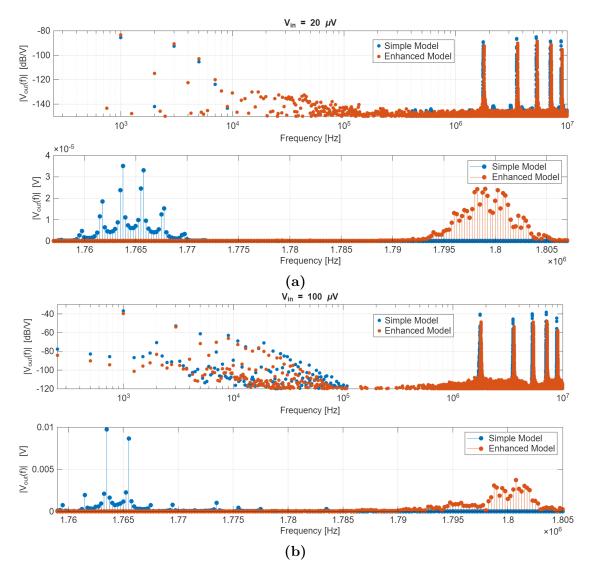

|             | DFT magnitude of $V_{out}$ and zoomed view around pulse frequency .                                                | 70            |

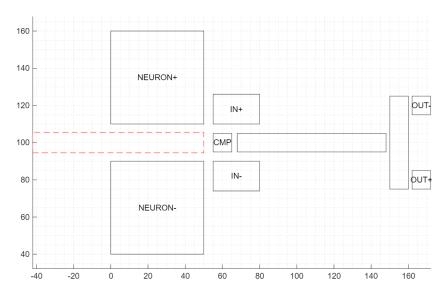

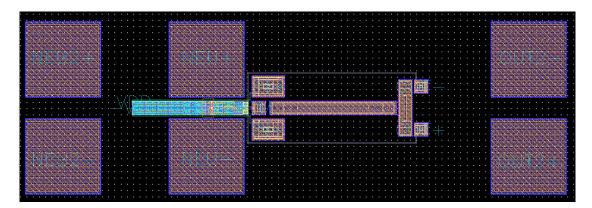

|             | DIGOTA layout                                                                                                      | 7             |

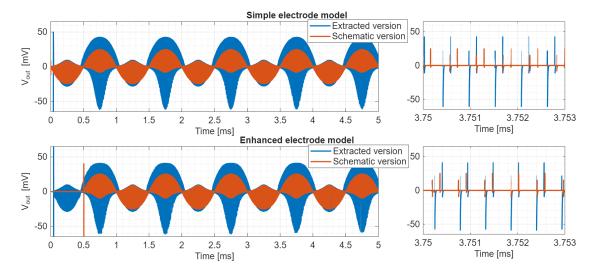

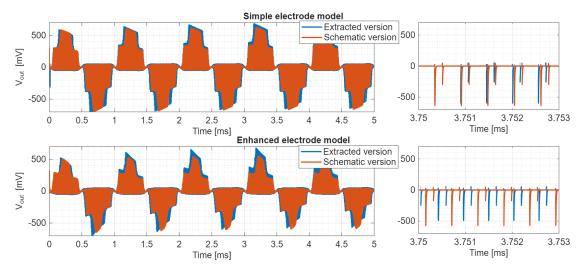

| 0.34        | $V_{out}(t)$ comparison between schematic and extracted simulations                                                | 7             |

| r 2r        | using both electrode models, with $V_{in} = 20 \mu\text{V}$                                                        | 7             |

| 5.35        | $V_{out}(t)$ comparison between schematic and extracted simulations                                                | 7             |

| T 0.0       | using both electrode models, with $V_{in} = 100 \mathrm{pV}.$                                                      | 7             |

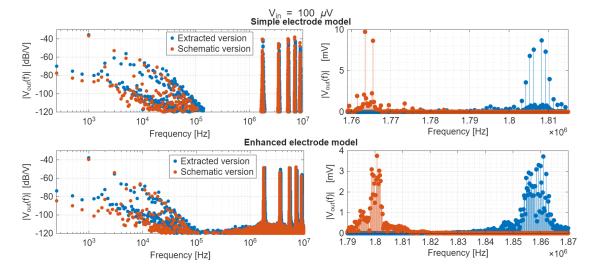

| 5.30        | FFT magnitude $ V_{out}(f) $ comparison between schematic and ex-                                                  | _             |

| r 97        | tracted simulations for both electrode models, with $V_{in} = 100 \mu\text{V}$ .                                   | 7             |

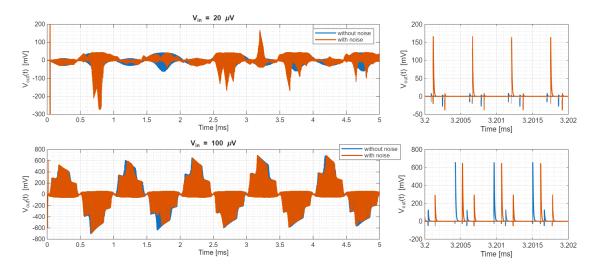

| 5.37        | Comparison between $V_{out}(t)$ with and without noise, considering                                                | 0             |

| <b>F</b> 00 | extracted layout circuit and with different input amplitudes                                                       | 8             |

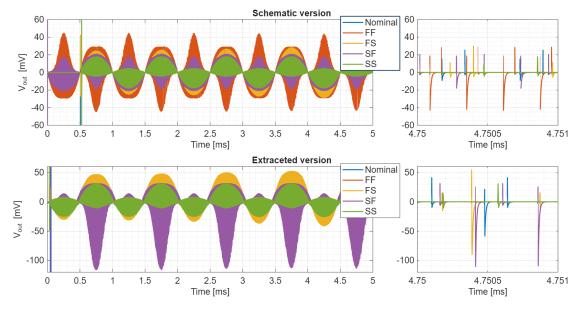

| 5.38        | Corner analysis of $V_{out}$ , schematic and extracted layout version, with                                        | 0             |

| - 00        | $V_{in} = 20 \mathrm{pV}.$                                                                                         | 8             |

| 5.39        | Corner analysis of $V_{out}$ , schematic and extracted layout version, with                                        | _             |

|             | $V_{in} = 100 \mathrm{\mu V}.$                                                                                     | 8             |

| 5.40        | Corner analysis of $V_{out}$ FFT, schematic and extracted layout version,                                          |               |

|             | with $V_{in} = 100 \mu\text{V}$                                                                                    | 8             |

|             | Monte Carlo simulation results of power consumption                                                                | 8             |

|             | Monte Carlo simulation results of the gain                                                                         | 8             |

| 5.43        | Electrode configuration used in Matlab code                                                                        | 8             |

| 5 44        | Complete circuit layout                                                                                            | 8             |

### Chapter 1

### Introduction

Electroencephalography (EEG) is one of the main techniques used to study brain activity in both scientific research and medical diagnostics. It is a non-invasive method that measures the electrical potentials generated by neurons using electrodes placed on the scalp. However, these signals are significantly attenuated by the human skull, which limits the spatial resolution.

To overcome this limitation, more precise but invasive techniques such as electrocorticography (ECoG) and stereo-EEG (sEEG) can be used, but these require skull trepanation to implant electrodes under the skull or directly into the brain cortex, respectively, and these can only image restricted regions of the brain.

The EIC Pathfinder EU project CEREBRO [1] (an electric Contrast medium for computationally intensive Electroencephalographies for high REsolution BRain imaging withOut skull trepanation) aims to address this gap by developing the first EEG contrast medium, enabling non-invasive imaging of the entire brain. The long-term goal is to achieve the spatial resolution of invasive methods without the need for surgery.

The idea of this project is to create micro-scale circuits capable of detecting neuronal signals close to neurons and transmitting them to external electrodes. By shifting the frequency of the signal to higher frequencies before transmission, attenuation due to skull can be reduced, leading to more accurate readings of neural activity.

To be suitable for such applications, these circuits must be extremely compact and capable of self-powering through energy harvesting. While future versions will need to meet strict constraints in terms of power consumption and area, the prototype explored in this thesis assumes relaxed conditions: the circuit is externally powered via wires, and its shape is designed to be narrow and long, allowing manual placement near the target neuron. In conventional designs, a typical approach would involve an analog front-end amplifier that senses the potential generated by the neuron through input electrodes. This signal is then amplified and sent to a voltage-controlled oscillator (VCO), which modulates it into a frequency signal. The resulting signal is passed to a digital buffer and finally transmitted to external electrodes for further processing.

However, this thesis investigates an alternative and more innovative approach based on a Digital-Based Operational Transconductance Amplifier (DIGOTA). Previous studies have already highlighted DIGOTA's advantages in terms of lower area and power consumption, making it a candidate for this type of application.

What makes the use of DIGOTA in this work even more innovative and challenging is the use of the parasitic properties of the electrodes as functional circuit elements. The electrodes and their mutual coupling are modeled using resistances and capacitances. Instead of being considered unwanted effects, these parasitic elements are intentionally integrated into the feedback and summing network, replacing traditional passive components usually implemented on silicon. This approach allows for a further reduction in circuit area and simplifies the overall layout.

Another significant advantage of this configuration is that it removes the need for a VCO block. In fact, the DIGOTA circuit naturally produces an output train of pulses whose amplitude is directly modulated by the input signal. This modulation allows the neural signal to be transmitted at a much higher frequency than its original frequency, without requiring an additional frequency-shifting stage. As a result, the system benefits from lower area and power consumption.

This thesis presents the design, simulation, and layout of such a DIGOTA-based circuit, developed with custom-shaped electrodes and integrated in the framework of the CEREBRO project.

The work includes a brief review of existing literature on electrode modeling, with particular attention to the electrical equivalent circuits of electrodes in organic solutions, in order to approximate their behavior for CMOS-compatible simulations.

In addiction, the concept of digitally based analog amplifiers is explored, with analysis and comparison of different DIGOTA topologies.

Behavioral simulations using MATLAB and Simulink are also performed to better understand the operating principles of the architecture and to evaluate its theoretical performance before schematic-level implementation.

### Chapter 2

### Electrode Models

Recent technological progress have enabled significant miniaturization of both electrodes, such as penetrating microelectrodes that are now preferred over planar ones for higher specificity, and electronic front-end circuits. CMOS technology is the predominant choice for electronic front-ends that are integrated with electrodes, especially for the development of the next generation of miniaturized, wireless, and ultra-low-power biosensors. These integrated devices play a crucial role in monitoring chemical and biological processes, enabling real-time acquisition and processing of vital data. Their applications are broad and include monitoring neural activity, electrochemical biosensing, and the detection of specific analytes such as dopamine. They can be used in a wide range of critical applications, with particular emphasis on medical diagnostics, continuous health monitoring, personalized medicine, and monitoring and addressing neurodegenerative diseases.

However, to ensure reliable CMOS circuit behavior and maintain system performance, the robust and effective design of these integrated devices critically depends on the availability of accurate equivalent electrical models of the interface between the electrode and the biological environment or electrolyte solution.

In the design of CMOS readouts for electrochemical sensors and biosensors, the initial step involves integrating an appropriate electrical equivalent circuit for the sensors into the CAD design tool.

Several equivalent circuits have been proposed to represent sensor behavior. The use of inaccurate models can in fact lead to fatal design errors, improper sensor operation, significant differences between simulations and actual measurements, and, consequently, severely compromise the accuracy of diagnoses.

Typically, Randles models (i.e., R-RC circuits) are used to characterize electrode impedance. The parameters of these models are calculated by solving equations, by fitting experimental data, or even estimated using numerical analysis approaches.

However, this conventional model has substantial limitations and is often considered too simple, failing to accurately represent the complex electrochemical phenomena occurring at the electrode interface.

Following are some models that go to realize a more accurate model that considers phenomena more suitable to modern microelectrodes.

#### 2.1 Neural Electrode Model

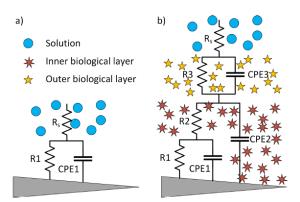

The aim of this study [2] is to monitor the impedance changes occurring on Pt/Ir penetrating microelectrodes inserted in ex-vivo porcine brains to derive an opportune electrode/brain model describing the system and its evolution in time. In particular, impedance spectroscopy measurements have been performed for 144 hours to characterise the evolution of the electrochemical behaviour. The experiments were performed using 2-inch monopolar microelectrodes coated with a 3  $\mu$ m layer of Parylene-C and with a 25  $\mu$ m exposed tip. The diameter of the microelectrode is 81  $\mu$ m at the shaft and 3  $\mu$ m at the tip, which has a taper ratio of about 25:1 and an area of 275  $\mu$ m<sup>2</sup>.

The electrode/brain interfacial impedance varies simultaneously in frequency and in time after implantation.

From the experimental results, shown in Figure 2.1, two equivalent electrical circuit (EEC) models were derived to describe the impedance variation of the microelectrode in different phase of the experiment.

- 1. For measurements acquired up to 48 hours after electrode insertion, the system was modeled using a Single Time Constant (TC) circuit. This model is illustrated in Figure 2.2a and consists of:

- a series resistance  $(R_s)$ , representing the resistance of the electrolyte (the artificial cerebrospinal fluid).

- a charge transfer resistance (R1),

- a capacitance (CPE), which represent the double-layer capacitance at the interface. It modeled as Constant Phase Elements (CPE) instead of ideal capacitors, to account for surface roughness and heterogeneity of biological samples, so that:

$$Z_{CPE} = \frac{1}{(j\omega)^{\alpha}Q} \tag{2.1}$$

where j is the imaginary number,  $\omega$  is the angular frequency, and Q and  $\alpha$  are the CPE parameters.

**Figure 2.1:** Impedance spectra acquired in the experiment (a) modulus and (b) phase [2].

- 2. After 48 hours, a more complex model is needed because two additional time constants appear in the spectra. This is related to the biological material attached to the surface of the microelectrode, that is not homogeneous and it has a variable thickness. This biofilm alters the transport phenomena close to the electrode and, promotes charge transfer from the solution to the metal. To model this heterogeneous layer covering the microelectrode, two time constants (TCs) are added at this model, as shown in Figure 2.2b:

- the branch  $R2 \parallel CPE2$  describes an internal layer of biological material, closer to the electrode surface.

- the branch  $R3 \parallel CPE3$  describes an external layer covering the first one.

The parameters of these EEC models (resistances R1, R2, R3 and parameters Q and  $\alpha$  of CPEs (Q1, Q2, Q3) vary considerably over time, Unlike the stationary

**Figure 2.2:** EEC of the electrode. a) Model for spectra acquired up to 48 hours. b) Model for spectra acquired in the second part of the experiment [2].

Randles model, Figure 2.3 shows the trend of these parameters, highlighting in particular a significant decrease of the charge transfer resistance (R1) in the first 72 hours, attributed to the attachment of the biofilm that improves the charge transfer mechanism.

#### 2.2 Electrochemical Electrode Model

Another approach to consider and model the layering phenomena occurring at the electrode-solution interface is presented in the paper [3], which analyses Pt/Ir planar microelectrodes used in a digital potentiostat.

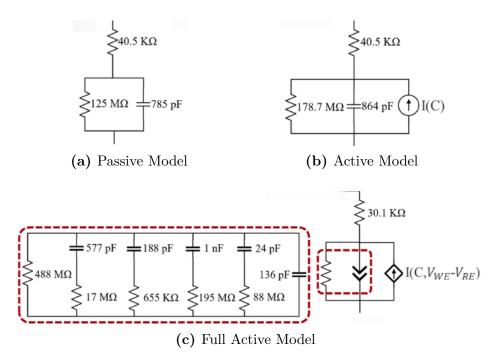

One of the main problems with traditional models for electrochemical sensors, such as the Passive Model (Figure 2.4a) and the Active Model (Figure 2.4b), is how they represent the capacitance at the interface between the electrode and the electrolyte.

These models use fixed values for this equivalent capacitance. However, in reality, because of the layering phenomema that happen at this interface, the capacitance of a metal electrode changes with the frequency of the input signal. So, it cannot be accurately described with a constant value.

Moreover, the Passive Model does not correctly model the faradaic current (the current linked to redox reactions at the electrode interface, which depends on the analyte concentration). While the Active Model adds a current source to represent the faradaic current, but it only considers the expected current range for a given analyte concentration. It does not take into account changes in the faradaic current caused by variations in the bias voltage (for example, due to CMOS process variations or thermal drift).

**Figure 2.3:** Trend of the different fitting parameters derived from EEC modeling of spectra [2].

As a result, these models do not correctly represent how the sensor interface behaves at different frequencies and conditions. In particular, they either fail to predict or wrongly predict when the potentiostat reaches saturation. This can lead to unrealistic CMOS simulation results and possibly critical design mistakes.

This paper introduces a new model called the Full Active Model (Figure 2.4c), which is a more accurate, robust, and complete equivalent circuit for electrochemical sensors than traditional models. In particular:

- It includes Constant Phase Elements (CPEs) to model the frequency-dependent capacitance at the electrode interface caused by layering phenomena. It uses multiple RC branches (the number depends on the sensor's complexity) to accurately match the behaviour of a CPE, as seen in experimental impedance measurements. This makes the model reliable for a wide range of applications.

- It models the faradaic current using a voltage-controlled current source, which reflects its (often nonlinear) dependence on the potential difference between two electrodes.

**Figure 2.4:** Different models for the equivalent circuit of an electrode of the electrochemical cell [3].

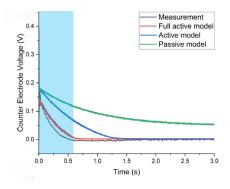

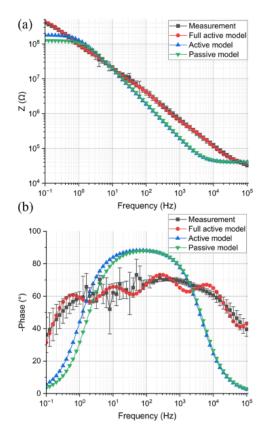

By comparing different models with experimental data, it is demonstrated that the new model provides the best match. As seen in Figure 2.6, which presents electrochemical impedance spectroscopy (EIS) measurements, the "full active model" closely fits both the magnitude and phase of the measured impedance across a wide frequency range. Figure 2.5 further confirms that the new model accurately predicts the risk of potentiostat saturation.

**Figure 2.5:** The risk of saturation on the voltage measured at the electrode and simulated by the different models. The highlighted time interval shows the operation of the potentiostat before saturation [3].

Figure 2.6: Electrochemical impedance spectroscopy of planar Pt/Ir microelectrode and the fitted electrical models [3].

### Chapter 3

## Digital-Based OpAmp

#### 3.1 Introduction and Context

#### Roadmap

Moore's Law, formulated by Gordon Moore in the 1965, described an empirical observation: the number of transistors integrated on a chip tended to double every 1.5 to 2 years, leading to increased performance and reduced costs. For nearly fifty years, this exponential trend was a fundamental reference for the development of the semiconductor industry.

To support and guide this technological evolution, global roadmapping efforts were established, initially through the International Technology Roadmap for Semi-conductors (ITRS) and currently through the International Roadmap for Devices and Systems (IRDS).

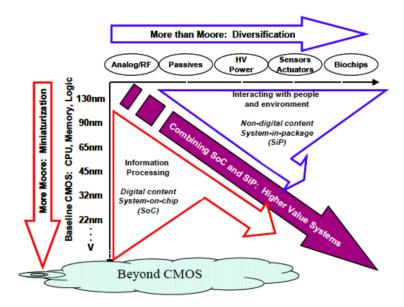

The IRDS aims to identify key directions for the future of microelectronics and *More Moore* and *More-than-Moore* are two of the strategies that continue and extend Moore's law [4].

- More Moore refers to continued shrinking of physical feature sizes of digital functionalities (logic and memory storage) in order to improve density (reducing cost per function) and performance (in terms of speed and power consumption) [5].

- More-than-Moore refers to the integration of functionalities into devices that do not necessarily scale according to Moore's Law but provide added value in other ways. The More-than-Moore approach enables non-digital functionalities (e.g., RF communication, power management, passive components, sensors, actuators) to move from the system board level into the package (System-in-Package, SiP) or directly onto the chip (System-on-Chip, SoC) [6].

This evolution of semiconductor technology, due to scaling, is visually represented in Figure 3.1.

Figure 3.1: IRDS Roadmap

Advancements in fabrication technologies now allow the co-integration of analog components on the same chip with scaled digital logic, enabling the realization of complex mixed-signal systems. However, the aggressive scaling of digital logic associated with *More Moore* imposes significant limitations and challenges on analog/mixed-signal circuit design and integration, such as reliability and matching issues introduced by improved process variability due to scaling [6].

#### Re-Thinking Analog Integrated Circuits in Digital Terms

As explained above, while modern CMOS technologies have significantly improved the performance of digital integrated circuits thanks to geometric and supply voltage scalability, analog ICs benefit less from these advances. In fact, reduced power levels, short-channel effects, and increased process variability make the integration of analog blocks into System-on-a-Chip designs increasingly difficult [7].

The limitations of analog circuits fabricated in today's digital processes have been addressed through new topologies and design techniques. Many of these solutions mitigate specific technological drawbacks at the cost of increased design complexity and/or degraded performance. State-of-the-art analog circuits typically operate above 1V, have power consumption limited by bias currents, and occupy significant silicon area. Sub-0.5V approaches using analog techniques often exhibit

degraded energy efficiency, larger area, and increased complexity [8].

An alternative approach is to rethink analog functions in digital terms. This allows them to be implemented using circuits and design methodologies that are as close as possible to the digital domain. This approach aims to overcome the limitations of traditional analog circuits in modern low-voltage digital technologies by exploiting the strengths of the digital domain implemented for analog functions [9], [10].

For this reason the DB-OTA circuit has been proposed as a digital-based implementation of an analog differential circuit to fill this gap. The idea is to implement the function of a standard differential circuit (such as a CMOS differential pair) by describing it in digital terms [7], [11].

The main advantages of these digital-based OpAmps are:

• Ultra-Low Power Consumption: They can operate with ultra-low supply voltages, even below 0.5 V (down to 0.25/0.3 V), enabling direct powering from energy harvesters or micro-batteries—ideal for energy-autonomous systems. Unlike analog sub-systems, which suffer from degraded transistor performance, reduction in signal swing and reduced SNR at low voltages, digital-based architectures eliminate bias currents and can function deep in the sub-threshold regime.

As a consequence power consumption is reduced to the nanoWatt range, overcoming the inherent power limitations of conventional analog designs [12], [8].

- **High Area Efficiency:** They are very compact. The implementation based on standard digital cells allows area scaling similar to that of digital circuits and significantly reduces area compared to traditional analog solutions (up to 2–85 times smaller [8]).

- Reduced Design and Integration Effort: These circuits take advantage of standard digital design tools, such as computer-aided design (CAD), verification, and testing techniques. Their behavior can be described using hardware description languages (HDLs), allowing for fully automated implementation through digital design flows. This significantly simplifies both the design and integration processes [7], [8].

These features make them particularly suitable for energy- and area-constrained systems, such as sensor nodes for the Internet of Things (IoT) [13] or "Body Dust" [14] applications, which require low-frequency analog interfaces powered directly from energy harvesting.

#### 3.2 Digital-Based OTA Behavior

The Digital-Based Operational Transconductance Amplifier (DB-GOTA) is a mixed-signal circuit that uses standard digital logic elements to replicate the functionality of a differential amplifier, typically implemented with analog circuitry. Its core operation is based on detecting the polarity of a differential input and encoding it into a digital signal, which is subsequently integrated to generate an analog-like output current.

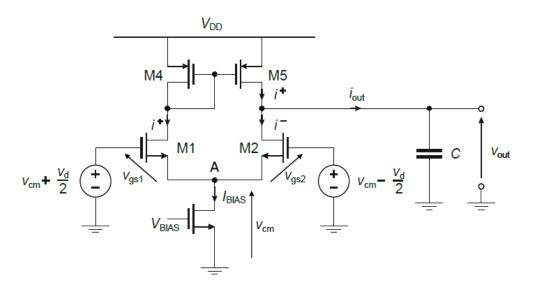

A differential stage produces an output that depends on the difference between two input signals, i.e., the differential-mode signal  $v_D = v^+ - v^-$ , and ideally rejects any signal common to both inputs, i.e., the common-mode signal  $v_{CM} = \frac{v^+ + v^-}{2}$ .

In analog CMOS implementations, this function is typically realized by a differential pair (Figure 3.2) composed of two MOS transistors biased in saturation and sharing a common source node. In such configurations, the source node voltage ideally tracks the common-mode input and is subtracted from the gate voltages. This ensures that the gate-source voltages of the transistors depend only on the differential input, enabling effective common-mode rejection. However, in modern digital CMOS technologies, this approach presents several limitations, including a narrow input common-mode range, a relatively high minimum supply voltage, and a limited output swing.

Figure 3.2: Analog differential pair.

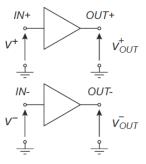

DB-OTA addresses these limitations by using digital circuits to sense the differential input. In particular, it employs a pair of non-inverting digital buffers, as shown in Figure 3.3. Each buffer operates as a comparator with a switching threshold  $V_T$ :

- When  $v_{\text{IN}} > V_T \Rightarrow v_{\text{OUT}} = V_{OH} > V_T \Rightarrow \text{OUT} = 1$

- When  $v_{\text{IN}} < V_T \Rightarrow v_{\text{OUT}} = V_{OL} < V_T \Rightarrow \text{OUT} = 0$

Figure 3.3: Digital buffer pair.

By applying this logic to both inputs, two key conditions can be identified:

- When  $v^+ > V_T$  and  $v^- < V_T$ , the output becomes  $(OUT^+, OUT^-) = (1, 0)$ , which implies a positive differential voltage, i.e.,  $v_D > 0$ .

- Conversely, when  $v^+ < V_T$  and  $v^- > V_T$ , the output is  $(OUT^+, OUT^-) = (0, 1)$ , indicating a negative differential voltage, i.e.,  $v_D < 0$ .

In these cases, the differential voltage is correctly detected, and its polarity is captured by the digital outputs.

However, when both the inputs are on the same side of the threshold (i.e., either  $v^+ > V_T$  and  $v^- > V_T$ , or  $v^+ < V_T$  and  $v^- < V_T$ ), the outputs are (1, 1) or (0, 0), respectively. In these situations, the digital outputs do not reflect the differential input but instead indicate the common-mode level:

- If  $v^+ > V_T$  and  $v^- > V_T$ , then  $(OUT^+, OUT^-) = (1, 1)$ . This implies that the average of the two signals exceeds the threshold, i.e.,  $v^+ + v^- > 2V_T$ , which means  $v_{CM} > V_T$ .

- If  $v^+ < V_T$  and  $v^- < V_T$ , then  $(OUT^+, OUT^-) = (0,0)$ . In this case, both signals are below the threshold, so  $v^+ + v^- < 2V_T$ , which implies  $v_{CM} < V_T$ .

To transform a simple pair of digital buffers into a true differential structure, it is necessary to implement a compensation feedback, as illustrated in Figure 3.5, that rejects the common-mode component of the input. This compensation is performed in real time and ensures that the effective inputs to the buffers are always driven toward a (1, 0) or (0, 1) configuration, independently of the actual common-mode voltage applied at the inputs. As a result, the output of the buffer pair remains exclusively sensitive to the differential input voltage.

|                  | OUT+                               | OUT-             | OUT+                                                  | OUT-                        | OUT+                             | OUT-      | OUT+                                                      | OUT-           |

|------------------|------------------------------------|------------------|-------------------------------------------------------|-----------------------------|----------------------------------|-----------|-----------------------------------------------------------|----------------|

| $V_{\mathrm{T}}$ | 1                                  | 1                | 0                                                     | 0                           | 1                                | 0         | 0                                                         | 1              |

|                  | v <sup>+</sup>                     | v -<br>          | ν <sup>+</sup><br>~~^><br>ν <sub>(</sub>              | ν−<br>• <sup>-0</sup><br>εм | ν <sup>+</sup>                   | ( ( ) v - | ν <sub>CM</sub> <sub>γ</sub><br>/-<br>σ<br>ν <sup>+</sup> | v <sup>-</sup> |

|                  | $v_{\mathrm{CM}} \ v_{\mathrm{I}}$ | $V_{\mathrm{T}}$ | $v_{\mathrm{CM}} < V_{\mathrm{T}} < v_{\mathrm{D}}$ ? |                             | $v_{\rm CM}$ ?<br>$v_{\rm D}$ >0 |           | ν <sub>CM</sub> ?<br>ν <sub>D</sub> <0                    |                |

**Figure 3.4:** Digital output configurations and implications on DM and CM input signals.

Figure 3.4 summarizes the output logic states of the digital buffers for all input combinations relative to the threshold  $V_T$ . When the outputs are (OUT<sup>+</sup>, OUT<sup>-</sup>) = (1,0) or (0,1), the differential input voltage  $v_D$  can be clearly determined. This situation corresponds to the condition

$$|v_{CM} - V_T| > \left| \frac{v_D}{2} \right|. \tag{3.1}$$

Conversely, when both buffer outputs are equal, i.e., (1,1) or (0,0), the differential input cannot be resolved, but the common-mode level  $v_{CM}$  relative to  $V_T$  can be inferred. This is the case when

$$|v_{CM} - V_T| < \left| \frac{v_D}{2} \right| \tag{3.2}$$

. These ambiguous cases activate the compensation mechanism, which dynamically adjusts the internal nodes to restore a valid differential interpretation.

#### 3.3 DB-OTA circuit

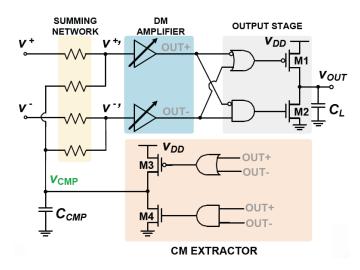

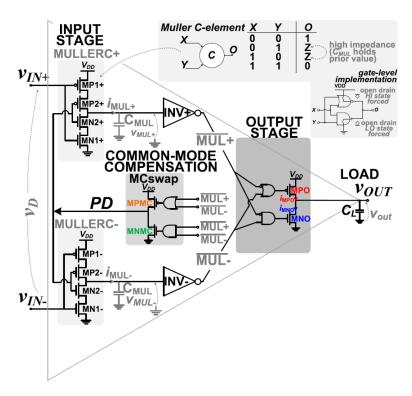

The complete digital-based OTA (DB-OTA) circuit proposed in Fig. 3.5 is describer in [7] and it consists of the following main blocks:

Figure 3.5: DB-OTA schematic [7].

1. **Digital Buffers (DM amplifier):** A pair of single-ended non-inverting digital buffers receives the internal input signals  $v'^+$  and  $v'^-$  (which are not directly the external inputs) and generate the digital output signals. These buffers are implemented as cascades of an even number of CMOS inverters.

It is essential that the two buffers have the same  $V_T$ , to ensure correct operation. To address this issue and improve robustness against process variations and mismatch, a calibration network can be introduced [12].

2. Summing Network: This block adds a "compensation" signal  $(v_{\text{cmp}})$  to the external inputs  $v^+$  and  $v^-$  to generate the effective input signals  $v'^+$  and  $v'^-$  for the digital buffers:

$$v'^{+} = \frac{v^{+} + v_{cmp}}{2}, \qquad v'^{-} = \frac{v^{-} + v_{cmp}}{2}.$$

(3.3)

It can be implemented using a resistive network or, more conveniently in CMOS technology, using quasi-floating gate (QFG) techniques.

3. CM Extractor: This stage controls the common-mode (CM) level. It receives the digital outputs (OUT<sup>+</sup> and OUT<sup>-</sup>) of the buffers and generates the compensation signal  $v_{\rm cmp}$ . It includes a tri-state inverter (transistors

M1–M2 driven by logic AND and OR gates) loaded by a capacitor ( $C_{\rm cmp}$ ). Its goal is to keep the internal CM voltage ( $v_{\rm CM}$ ) close to the threshold voltage of the digital buffers, regardless of the external CM voltage, therefore:

- when  $(OUT^+, OUT^-) = (0, 0)$ , the pMOS transistor M1 is active, injecting current into the capacitor to increase  $v_{cmp}$  (to correct CM);

- when  $(OUT^+, OUT^-) = (1, 1)$ , the nMOS transistor M2 is active, discharging the capacitor to decrease  $v_{\text{comp}}$ .

- in the (1,0) or (0,1) configurations, both M1 and M2 are turned off, and  $v_{\text{comp}}$  is held constant.

- 4. **Output Stage:** This block receives the digital outputs (OUT<sup>+</sup> and OUT<sup>-</sup>) of the buffers and generates the single-ended analog output signal  $v_{\text{out}}$ . It includes another tri-state inverter (transistors M3–M4) loaded by an output capacitor ( $C_{\text{out}}$ ).

- If the buffer output is (0,1), M4 is active to decrease  $v_{\text{out}}$ .

- If the output is (1,0), M3 is active to increase  $v_{\text{out}}$ .

- When the output configuration is (1,1) or (0,0) (i.e., when CM control is active), both M3 and M4 are turned off, and the output is held constant.

#### 3.4 Digital OTA (DIGOTA) circuit

In the paper [8], the previous DB-OTA topology has been modified replacing the resistive summing network used for CM compensation with two Muller C-elements, as presented in Figure 3.6.

In prior digital-based OTAs, the common-mode compensation signal was added to the primary inputs via a passive summing network based on on-chip resistors, pseudo-resistors, or quasi-floating gate transistors, at the cost of substantial area overhead and voltage gain degradation. By eliminating the resistive summing network, this technique results in a fully-synthesizable design that is compatible with a digital standard cell flow. Furthermore, it exhibits reduced input-referred noise and improved resilience against mismatch and process variations, while maintaining a low power consumption in the nW range and a supply voltage of 300 mV.

In this circuit, the inputs of the Muller C-elements are connected both to the external inputs of the OTA and to the output of the common-mode compensation network. The outputs of the Muller C-elements,  $v_{\rm MUL+}$  and  $v_{\rm MUL-}$ , drive a pair of digital inverters similar to the digital buffers in the DB-OTA.

Figure 3.6: DIGOTA schematic [8].

The CM compensation and output stages, as in the DB-OTA, work based on the digital outputs of the inverters,  $\overline{\text{MUL}+}$  and  $\overline{\text{MUL}-}$ , and apply negative-feedback compensation to enforce the condition  $v_{CM}=V_T$ .

so that when  $v_{CM} < V_T$  or  $v_{CM} > V_T$ , the condition  $v_{CM} = V_T$  is enforced with a negative-feedback compensation. The compensation circuit implements a passive-less, self-oscillating loop dynamically tracking the effect of the common-mode input on  $v_{\text{MUL}+}$  and  $v_{\text{MUL}-}$ , as needed by INV+ and INV- to sense the differential input.

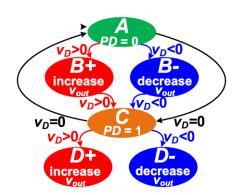

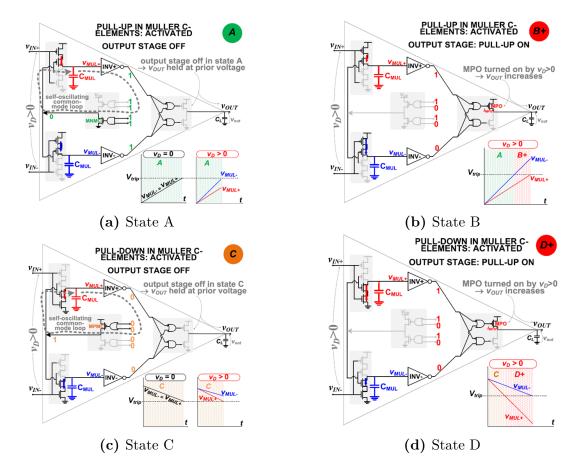

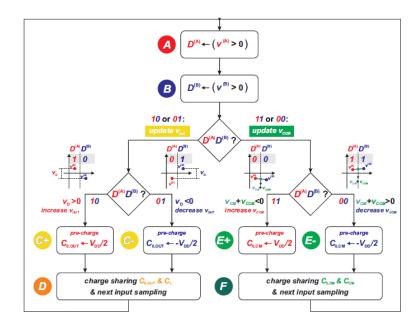

The overall DIGOTA state transition graph is summarized in Figure 3.7 and it can be described as follow:

• State A: When both voltages  $v_{MUL+}$  and  $v_{MUL-}$  are lower than the threshold  $V_T$ , we have  $(\overline{\text{MUL+}}, \overline{\text{MUL-}}) = (1,1)$ . As a result, the output stage is turned OFF, while the nMOS of the CM stage is ON, leading to PD = 0. Consequently, the pull-up networks of the Muller C-elements are enabled, allowing the capacitor  $C_{MUL}$  to charge. This causes both  $v_{MUL+}$  and  $v_{MUL-}$  to increase until the common-mode voltage  $v_{CM}$  approaches  $V_T$ , as shown in Figure 3.8a.

– If  $v_D > 0$  (i.e.,  $v_{IN+} > v_{IN-}$ ), then  $i_{MUL+} < i_{MUL-}$ , leading to State B+.

Figure 3.7: Logic states graph [8].

- If  $v_D < 0$  (i.e.,  $v_{IN+} < v_{IN-}$ ), then  $i_{MUL+} > i_{MUL-}$ , leading to State B-.

- If  $v_D = 0$  (i.e.,  $v_{IN+} = v_{IN-}$ ), then  $i_{MUL+} = i_{MUL-}$ , leading to State C.

- State B+: When  $v_{MUL+} < V_T$  and  $v_{MUL-} > V_T$ , the logic outputs are  $(\overline{\text{MUL+}}, \overline{\text{MUL-}}) = (1,0)$ , therefore the common-mode compensation stage is OFF, and output stage pMOS is ON. As a result, the output capacitor  $C_{OUT}$  is charged, causing  $v_{OUT}$  to increase, as can be observed in Figure 3.8b.

- State B-: When  $v_{MUL+} > V_T$  and  $v_{MUL-} < V_T$ , we obtain  $(\overline{\text{MUL+}}, \overline{\text{MUL-}}) = (0,1)$  and so the CM stage is OFF andoutput stage pMOS is ON. This leads to the discharge of  $C_{OUT}$ , causing  $v_{OUT}$  to decrease.

- State C: When both  $v_{MUL+}$  and  $v_{MUL-}$  are higher than  $V_T$ , then  $(\overline{\text{MUL+}}, \overline{\text{MUL-}}) = (0,0)$ . As a result, the output stage is OFF, and the CM stage nMOS is ON, which implies PD = 1. The pull-down networks of the Muller C-elements are now activated, discharging  $C_{MUL}$ . Consequently,  $v_{MUL+}$  and  $v_{MUL-}$  decrease, and the common-mode voltage  $v_{CM}$  approaches  $V_T$ , as illustrated in Figure 3.8c.

- If  $v_D > 0$  (i.e.,  $v_{IN+} > v_{IN-}$ ), then  $i_{MUL+} > i_{MUL-}$ , leading to State D+.

- If  $v_D < 0$  (i.e.,  $v_{IN+} < v_{IN-}$ ), then  $i_{MUL+} < i_{MUL-}$ , leading to State D-.

- If  $v_D = 0$  (i.e.,  $v_{IN+} = v_{IN-}$ ), then  $i_{MUL+} = i_{MUL-}$ , returning to State A.

- State D+: When  $v_{MUL+} < V_T$  and  $v_{MUL-} > V_T$ , the condition becomes  $(\overline{\text{MUL+}}, \overline{\text{MUL-}}) = (1,0)$ . In this state, the CM stage is OFF and output stage pMOS is ON. Therefore,  $C_{OUT}$  is charged and  $v_{OUT}$  increases, as can be noticed in Figure 3.8d.

- State D-: When  $v_{MUL+} > V_T$  and  $v_{MUL-} < V_T$ , the system is in the condition  $(\overline{\text{MUL+}}, \overline{\text{MUL-}}) = (0,1)$ . Here, the common-mode compensation stage is OFF

and output stage nMOS is ON. As a result,  $C_{OUT}$  is discharged, and  $v_{OUT}$  decreases.

Figure 3.8: DIGOTA circuit operations throughout its digital states when  $v_D \ge 0$  [8].

# 3.5 Time-Multiplexed Digital Differential Amplification (TMD $^{2}$ A)

The TMD<sup>2</sup>A (Time-Multiplexed Digital Differential Amplifier), presented in [15], uses a single buffer operating in a time-multiplexed way, unlike the DB-OTA architecture, which employs two matched digital buffers to compare the non-inverting and inverting input voltages. This approach eliminates the need for buffer matching by sequentially comparing both input voltages against a shared trip point.

It has been proposed to design a low frequency, nW power Digital-based Acquisition Front-End (DAFE).

The operation of the circuit is schematically illustrated in Figure 3.9.

Figure 3.9: Concept diagram of the Time-Multiplexed Digital Differential Amplification principle [15].

The the non-inverting  $(v^+)$  and inverting  $(v^-)$  input voltages are sampled simultaneously and stored on their respective input capacitors. Then the single-ended comparator is used to process both inputs sequentially (time-multiplexing):

• In phase A, the sampled  $v^+$  is connected in series with the common-mode compensating voltage  $v_{CCM}$  at the input of the buffer:

$$v^{(A)} = v^{+} + v_{CCM} = \frac{v_D}{2} + v_{CM} + v_{CCM}$$

(3.4)

The buffer output is stored in a D flip-flop  $D^{(A)}$ :

$$\begin{cases} v^{(A)} > 0 \Rightarrow D^{(A)} = 1\\ v^{(A)} < 0 \Rightarrow D^{(A)} = 0 \end{cases}$$

• In phase B, similarly,  $v^-$  is now connected in series with  $v_{CCM}$ :

$$v^{(B)} = v^{-} + v_{CCM} = -\frac{v_D}{2} + v_{CM} + v_{CCM}$$

(3.5)

The result is stored in  $D^{(B)}$ :

$$\begin{cases} v^{(B)} > 0 \Rightarrow D^{(B)} = 1\\ v^{(B)} < 0 \Rightarrow D^{(B)} = 0 \end{cases}$$

Depending on the digital outputs  $(D^{(A)}, D^{(B)})$ , either the output voltage  $v_{OUT}$  or the common-mode compensation voltage  $v_{CCM}$  is updated as detailed below:

- If  $(D^{(A)}, D^{(B)}) = (1,0)$ , meaning that  $v_D > 0$ , the output voltage  $v_{OUT}$  is increased, while  $v_{CCM}$  remains unchanged.

- If  $(D^{(A)}, D^{(B)}) = (0,1)$ , corresponding to  $v_D < 0$ , the output voltage  $v_{OUT}$  is decreased, with  $v_{CCM}$  again kept constant.

- If  $(D^{(A)}, D^{(B)}) = (1,1)$ , the compensation voltage  $v_{CCM}$  is decreased in order to satisfy the condition  $|v_{CM} + v_{CCM}| < \left|\frac{v_D}{2}\right|$ . In this case,  $v_{OUT}$  is held.

- If  $(D^{(A)}, D^{(B)}) = (0,0)$ , the compensation voltage  $v_{CCM}$  is increased to meet the same condition as above, while  $v_{OUT}$  remains unchanged.

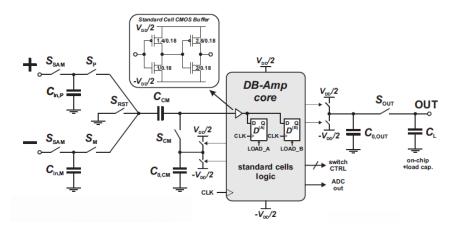

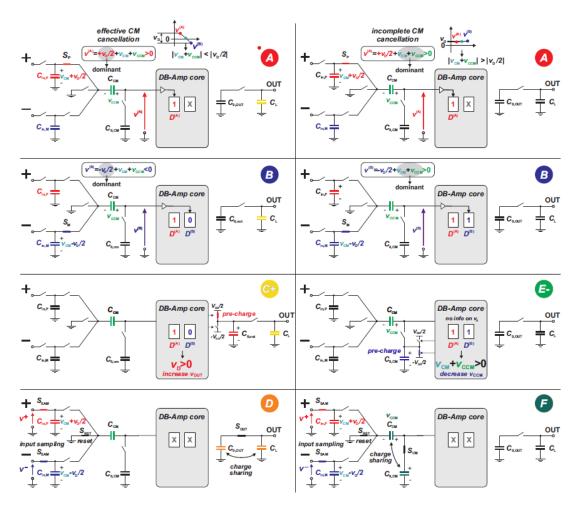

The circuit schematic is presented in Figure 3.10. Its operation is governed by the finite state machine (FSM) in Figure 3.11, and the corresponding switch configurations are illustrated in Figure 3.12. The main steps of the operating sequence are described below:

Figure 3.10: Schematic of TMD2A DAFE [15].

• In states A and B, the input capacitors  $C_{in,P}$  and  $C_{in,M}$ , previously charged with  $v^+$  and  $v^-$  respectively, are sequentially connected in series with  $C_{CM}$  at

Figure 3.11: State transition graph of the DB-Amp control unit [15].

the buffer input. The corresponding digital outputs are stored in the D-Flip Flops D(A) and D(B) at the next clock edge. Based on their values, the FSM transitions to either states C+/C- (to update the output voltage) or E+/E-(to adjust the common-mode voltage  $v_{CM}$ ), as shown in Figure ??.

- In states C+ and C-, the capacitor  $C_{0,OUT}$  is respectively charged or discharge to  $\pm \frac{V_{DD}}{2}$ .

- In state D,  $C_{0,OUT}$  is connected in parallel with  $C_L$ , resulting in:

$$\Delta v_{OUT} = \frac{C_{0,OUT}}{C_L + C_{0,OUT}} \left( \pm \frac{V_{DD}}{2} - v_{OUT} \right)$$

(3.6)

Therefore depending on whether the condition is (0,1) or (1,0), the output voltage is respectively increased or decreased. At the same time, both  $v^+$  and  $v^-$  are sampled and stored again on  $C_{in,P}$  and  $C_{in,M}$ .

- In states E+ and E-, the capacitor  $C_{0,CM}$  is pre-charged to  $\pm \frac{V_{DD}}{2}$ , similarly to state C+/C-.

- In state F,  $C_{0,CM}$  is connected to  $C_{CM}$  to update  $v_{CM}$ , thus compensating for common-mode variations. Input voltages are sampled in the same way as in state D.

**Figure 3.12:** Sequence of switch configurations corresponding to the states in Fig.3.11 [15].

# 3.6 Comparison

Table 3.1 reports the performance of several DB-OTA-based amplifiers.

These implementations show good performance, especially in terms of area and power consumption. This demonstrates that DB-OTA-based amplifiers can meet the energy self-sufficiency requirements of IoT sensor nodes and emerging biosensing applications [11].

|                                     | <b>DB-OTA</b> [12] |       | DIGOTA [8] |                     | TMT2A [16] |  |

|-------------------------------------|--------------------|-------|------------|---------------------|------------|--|

|                                     | Min                | Max   | < 500mV    | $> 500 \mathrm{mV}$ |            |  |

| Technology (nm)                     | 1                  | .80   | 180        |                     | 180        |  |

| $V_{DD}$ [V]                        | (                  | ).3   | 0.3        |                     | 0.4        |  |

| Area $[\mu m^2]$                    | 1.                 | 426   | 982        |                     | 9450       |  |

| Cap Load $C_L$ [pF]                 | 80                 |       | 150        |                     | -          |  |

| Power [nW]                          | 0.407              | 0.591 | 2.4        | 107.5               | 4.5        |  |

| DC Gain [dB]                        | 31                 | 29    | 30         | 73                  | 39.6       |  |

| GBW [kHz]                           | 0.229 0.518        |       | 0.250      | 57.5                | -          |  |

| Slew Rate [V/ms]                    | 0.097 0.264        |       | 0.085      | 0.019               | -          |  |

| In-band Input Noise $[\mu V_{rms}]$ | -                  | -     | 21         | 122                 | 11.3       |  |

| THD [%]                             | 1.26               | 2.82  | 2.0        | 1.0                 | 1.3        |  |

| CMRR [dB]                           |                    |       | 41         | 65                  | 63.8       |  |

Table 3.1: Comparison between different Digital-Based OTA Implementations

# Chapter 4

# Ideal Behavioral Modeling of DIGOTA

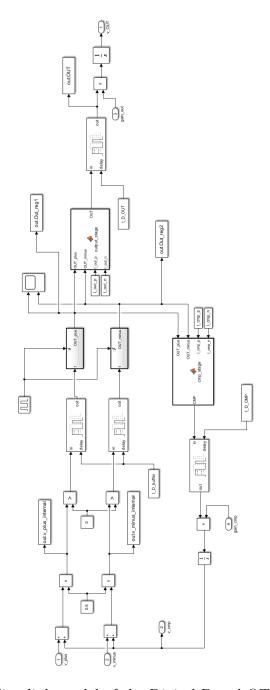

To gain deeper insight into the operation of the proposed DB-OTA circuit and validate the expected behavior of its functional blocks, an ideal behavioral model has been implemented using MATLAB and Simulink. This model, based on the architecture described in the previous section, allows for controlled simulation and analysis under idealized conditions, thus isolating the fundamental mechanisms of operation from non-idealities such as noise, parasitics, and mismatches.

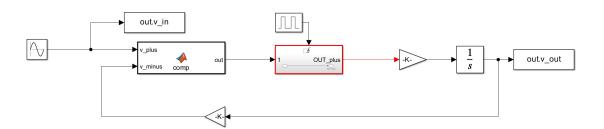

#### 4.1 Simulink Model

To analyze the ideal behavior of the Digital-Based OTA (DIGOTA), the architecture shown in Figure 3.5 has been implemented in Simulink, as illustrated in Figure 4.1. The model includes all key functional blocks and two registers to synchronize the circuit with the clock.

The circuit is composed of the following main components:

• Summing Network: Modeled using sum and product blocks. It combines the external differential inputs  $(v^+ \text{ and } v^-)$  with the compensation voltage  $(v_{cmp})$ , producing the actual inputs to the digital buffers:

$$v'^{+} = \frac{v^{+} + v_{cmp}}{2}, \qquad v'^{-} = \frac{v^{-} + v_{cmp}}{2}.$$

• Non-inverting Digital Buffers: Modeled using comparator and delay blocks to include the propagation delay  $t_D$ . It generate the digital output signals

Figure 4.1: Simulink model of the Digital-Based OTA (DIGOTA).

according to the following relations:

$$OUT^{+} = \begin{cases} 1 & \text{if } v'^{+} > 0, \\ 0 & \text{if } v'^{+} \le 0, \end{cases} \qquad OUT^{-} = \begin{cases} 1 & \text{if } v'^{-} > 0, \\ 0 & \text{if } v'^{-} \le 0. \end{cases}$$

- Registers: They synchronize the circuit with the clock frequency  $f_{clk}$ .

- Compensation Stage: Controls the common-mode level via a tri-state inverter that charges or discharges a capacitor  $C_{cmp}$  based on the digital outputs. The current is modeled using a MATLAB Function block that implements the following equation:

$$I_{cmp} = \begin{cases} |I_{cmp,p}| & \text{if } (\text{OUT}^+, \text{OUT}^-) = (0,0) \\ -|I_{cmp,n}| & \text{if } (\text{OUT}^+, \text{OUT}^-) = (1,1) \\ 0 & \text{otherwise.} \end{cases}$$

The capacitor behavior is simulated using a gain block  $1/C_{cmp}$  followed by an integrator, so that the compensation voltage  $v_{cmp}$  is described by the capacitor equation:

$$\frac{dv_{cmp}}{dt} = \frac{I_{cmp}}{C_{cmp}}.$$

• Output Stage: Converts the differential digital signals into an analog output  $v_{out}$  via a tri-state inverter charging a capacitor  $C_{out}$ :

$$I_{out} = \begin{cases} |I_{out,p}| & \text{if } (\text{OUT}^+, \text{OUT}^-) = (1,0) \\ -|I_{out,n}| & \text{if } (\text{OUT}^+, \text{OUT}^-) = (0,1) \\ 0 & \text{otherwise.} \end{cases}$$

Again, the capacitor is simulated using a gain block  $1/C_{out}$  followed by an integrator, and the output voltage is described by the equation:

$$\frac{dv_{out}}{dt} = \frac{I_{out}}{C_{out}}.$$

#### 4.2 Closed-Loop Simulations

## 4.2.1 Closed-Loop Circuit Configuration

The digital-based differential circuit can be configured in negative feedback to operate as an operational amplifier. In this configuration, the output of the circuit  $(v_{out})$  is connected to the inverting input  $(v'^-)$  through a voltage divider, represented by the factor  $\beta$ , while the input signal is applied to the non-inverting input  $(v'^+)$ . This leads to:

$$v^+ = v_{in}, \qquad v^- = \beta v_{out}.$$

Negative feedback forces the differential input  $v_d$  to zero, which implies:

$$v_d = v^+ - v^- = v_{in} - \beta v_{out} = 0 \Rightarrow v_{out} = \frac{1}{\beta} v_{in}.$$

This relationship shows that the circuit provides amplification with a gain determined by the feedback network  $(1/\beta)$ .

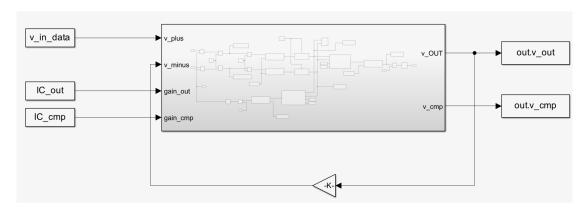

The Simulink model of this configuration is illustrated in Figure 4.2.

Figure 4.2: Simulink model of a feedback-configured DB-OTA.

#### 4.2.2 Parameters and Inputs

To study the behavior of the circuit in the feedback configuration, simulations were carried out by varying certain parameters to analyze how these changes affect the properties and performance of the circuit.

The main parameters and signals defined in MATLAB are:

- Feedback gain  $\beta$ : Often set to  $\beta = 1$  for simplicity.

- Clock period:  $T_{clk} = 1$ .

- Logic gate delay:  $t_D = 0.1 \cdot T_{clk}$ .

- Input signal: Unit-amplitude sine wave with frequency  $f_{in} \gg f_{clk}$ :

$$v_{in} = \sin(2\pi f_{in}t).$$

- Parameters  $\frac{I_{out}}{C_{out}}$  and  $\frac{I_{cmp}}{C_{cmp}}$ : Some assumptions were made regarding the transistor currents:

- The pMOS and nMOS transistor currents have equal magnitude.

- The currents are identical for both the compensation and output stages,

i.e.:

$$I_{out,p} = I_{cmp,p}, \quad I_{out,n} = I_{cmp,n}, \quad |I_{out,p}| = |I_{out,n}|, \quad |I_{cmp,p}| = |I_{cmp,n}|.$$

To explore the effect of varying  $\frac{I_{out}}{C_{out}}$  and  $\frac{I_{cmp}}{C_{cmp}}$ , the parameter  $\alpha$  was defined to relate these two terms:

$$\alpha = \frac{\frac{I_{out}}{C_{out}}}{\frac{I_{cmp}}{C_{cmn}}} = \frac{I_{out}}{C_{out}} \cdot \frac{C_{cmp}}{I_{cmp}}.$$

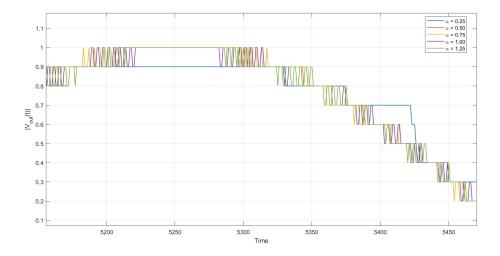

#### 4.2.3 Output $v_{out}$

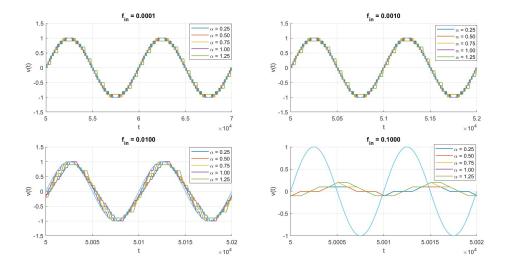

The circuit was simulated for different values of  $\beta$ . The results for  $\beta = 1$  (voltage follower configuration) and  $\beta = 0.2$  are shown in Figure 4.3 and 4.4, respectively.

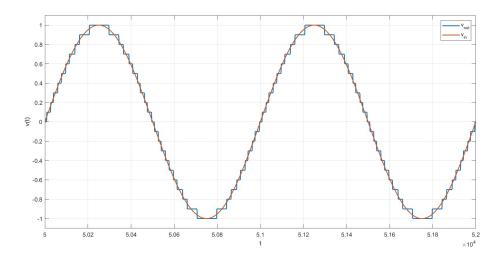

**Figure 4.3:** Behavior of  $v_{in}$  and  $v_{out}$  with  $f_{in} = 10^{-3}$ ,  $\beta = 1$ ,  $I/C_{out} = 0.1$ ,  $I/C_{cmp} = 0.2$ .

In both configurations, the circuit is able to reconstruct the input sinewave with a gain equal to  $1/\beta$ , showing that the differential voltage  $v_d = v^+ - v^- = v_{in} - \beta v_{out}$  is kept close to zero, as expected in a negative feedback system.

## 4.2.4 Compensation signal $v_{cmp}$

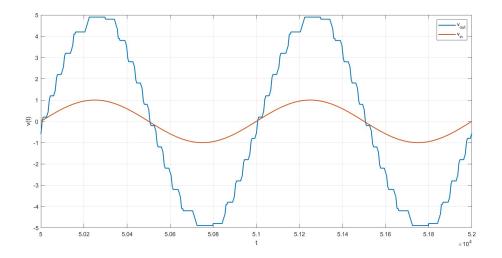

The compensation signal  $v_{cmp}$  is generated to maintain the internal common-mode voltage  $v'_{CM} = \frac{v'^+ + v'^-}{2}$  close to the threshold voltage  $V_T = 0$ , regardless of the external input signal. Figure 4.5 shows the behavior of  $v_{cmp}$ .

It can be observed that the output and compensation stages operate alternately: when  $v_{out}$  changes,  $v_{cmp}$  remains constant, and vice versa.

The variations of  $v_{out}$  and  $v_{cmp}$  at each clock cycle depend on the parameters  $I/C_{out}$  and  $I/C_{cmp}$ . Specifically, for each clock pulse, the capacitors  $C_{out}$  and  $C_{cmp}$  can be

**Figure 4.4:** Behavior of  $v_{in}$  and  $v_{out}$  with  $f_{in} = 10^{-3}$ ,  $\beta = 0.2$ ,  $I/C_{out} = 0.1$ ,  $I/C_{cmp} = 0.2$ .

**Figure 4.5:** Behavior of  $v_{in}$ ,  $v_{out}$  and  $v_{cmp}$  with  $f_{in} = 10^{-3}$ ,  $\beta = 1$ ,  $I/C_{out} = 0.1$ ,  $I/C_{cmp} = 0.2$ .

charged or discharged with a current  $I_{out} = I_{cmp}$ . Consequently, the voltage across the capacitors may vary as follows:

$$\pm \Delta v_{out} = \frac{I_{out}}{C_{out}} T_{clk}, \qquad \pm \Delta v_{cmp} = \frac{I_{cmp}}{C_{cmp}} T_{clk}.$$

#### 4.2.5 Internal signals

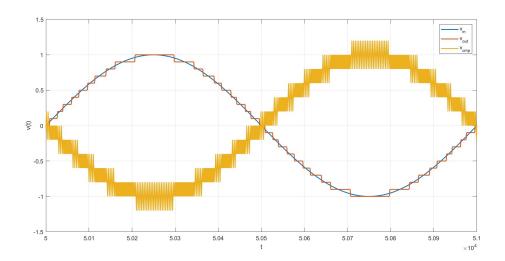

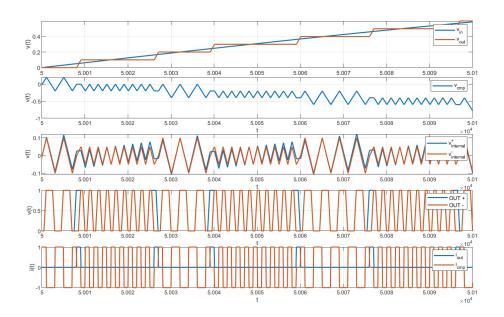

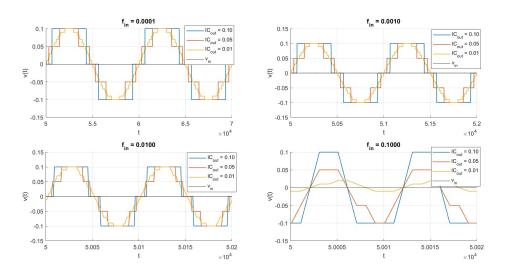

Further insights into the circuit's operation can be obtained by analyzing the waveforms of internal signals on a magnified time scale.

For example, Figure 4.6 shows the behavior of both digital and analog signals in relation to the circuit states.