### POLITECNICO DI TORINO

### MASTER's Degree in COMPUTER ENGINEERING

### MASTER's Degree Thesis

## Porting FreeRTOS Symmetric Multiprocessing support to the Zynq-7000 SoC

Supervisors

Prof. STEFANO DI CARLO

Prof. ALESSANDRO SAVINO

Doctor. ENRICO MAGLIANO

Doctor. ALESSIO CARPEGNA

Candidate

MATTEO FRAGASSI

**JULY 2025**

# Summary

Real-Time Operating Systems (RTOSs) are widely employed in time-sensitive applications. However, since keeping costs low is crucial, the adopted hardware is usually not state-of-the-art, even though safety and responsiveness are often among the requirements of the system. Therefore, it is important to exploit all the resources the hardware has to offer. From the perspective of an Operating System (OS), it has become almost imperative to be able to support multi-core processing with a single instance of the OS. In this context, the thesis focuses on porting the Symmetric Multiprocessing (SMP) functionality of FreeRTOS, a popular open-source RTOS, on the multi-core processor embedded in the Zynq-7000 System-on-Chip (SoC). The process is detailed in both the hardware-dependent and hardware-independent steps and the result is compared to other existing multiprocessing options.

# Acknowledgements

I would like to thank all my professors for the knowledge and guidance they have provided during my academic journey. A special mention goes to the supervisors and co-supervisors who supported me throughout the development of this thesis.

Un grazie speciale va poi alla mia famiglia, senza la quale non avrei affrontato questo percorso con la serenità e la consapevolezza che lo hanno contraddistinto.

Un pensiero va anche a nuovi e vecchi amici, che hanno saputo rendere leggeri e spensierati i momenti più duri, a prescindere dalla distanza che ci separava.

Infine, un ringraziamento particolare va a Michela, la mia ragazza, che ha contribuito a rendere questo viaggio un ricordo indelebile.

# Table of Contents

| Li | st of | Table  | es                                            | VI   |

|----|-------|--------|-----------------------------------------------|------|

| Li | st of | Figur  | es                                            | VIII |

| Li | st of | Listin | ıgs                                           | IX   |

| 1  | Intr  | roduct | ion                                           | 1    |

| 2  | Bac   | kgrou  | nd                                            | 3    |

|    | 2.1   | Multi  | processing                                    | 3    |

|    | 2.2   |        | 7000 SoC                                      | 5    |

|    |       | 2.2.1  | PS Software Boot Process                      | 8    |

|    |       | 2.2.2  | Application Processing Unit Modules           | 8    |

|    | 2.3   | ARM    | Cortex-A9                                     | 9    |

|    |       | 2.3.1  | Relevant features in the ARMv7-A architecture | 10   |

|    |       | 2.3.2  | Memory Management Unit                        | 12   |

|    |       | 2.3.3  | Exclusive Access                              | 13   |

|    |       | 2.3.4  | Global and Private Timers                     | 14   |

|    | 2.4   | FreeR  | TOS                                           | 15   |

|    |       | 2.4.1  | Symmetric Multiprocessing in FreeRTOS         | 15   |

|    |       | 2.4.2  | FreeRTOS on ARM Cortex-A9                     | 16   |

|    | 2.5   | Devel  | opment Tools                                  | 17   |

|    |       | 2.5.1  | Hardware-Software Design Platforms            | 17   |

|    |       | 2.5.2  | Xilinx Software Libraries                     | 19   |

|    |       | 2.5.3  | Trace and Debug                               | 20   |

| 3  | Imp   | olemen | ntation                                       | 22   |

|    | 3.1   | Devel  | opment Environment                            | 22   |

|    | 3.2   |        | TOS Port Update                               |      |

|    | 3.3   | Secon  | dary Core Bring-up Procedure                  | 25   |

|    |       | 3.3.1  | Dual-Core Boot on the Zynq-7000 SoC           |      |

|    |       |        |                                               |      |

|              |      | 3.3.2 Secondary Core Setup in FreeRTOS                 | 27 |

|--------------|------|--------------------------------------------------------|----|

|              | 3.4  | Symmetric Multiprocessing Port Upgrade                 | 29 |

|              |      | 3.4.1 Primary Core Setup in FreeRTOS                   | 29 |

|              |      | 3.4.2 Multi-core Interrupt Management                  | 30 |

|              |      | 3.4.3 Recursive Spinlocks                              | 32 |

|              | 3.5  | FreeRTOS SMP Port Trace and Debug                      | 36 |

|              |      | 3.5.1 Trace Macros                                     | 38 |

|              |      | 3.5.2 Percepio View                                    | 38 |

|              | 3.6  | FreeRTOS SMP Port Test Demo                            | 39 |

| 4            | Res  | ults                                                   | 42 |

| 5            | Con  | nclusion                                               | 47 |

| $\mathbf{A}$ | Refe | erence Manuals                                         | 49 |

| В            | Imp  | elementation Details                                   | 51 |

|              | В.1  |                                                        | 51 |

|              | B.2  | CPU1 BootROM Code                                      | 51 |

|              | B.3  | MMU Configuration for SMP                              | 53 |

|              | B.4  | Acknowledge CPU1 Boot End from CPU0                    | 53 |

|              | B.5  | Core Yield's Integration in FreeRTOS Interrupt Handler | 56 |

|              | B.6  | Cortex-A9 Nested Interrupt Handling in FreeRTOS        | 57 |

|              | B.7  | Exclusive Access Tests on the Zynq-7000 SoC            | 57 |

|              | B.8  | Floating Point Operations within Interrupt Handlers    | 60 |

| $\mathbf{C}$ | Ben  | chmark Program                                         | 62 |

|              | C.1  | AMP Configuration                                      | 62 |

|              |      | ranhy                                                  | 70 |

# List of Tables

| 4.1 | Program size comparison                                         | 44 |

|-----|-----------------------------------------------------------------|----|

| 4.2 | AMP benchmark execution times                                   | 44 |

| 4.3 | SMP benchmark execution times                                   | 45 |

| 4.4 | Impact of benchmark program's setup on the final execution time |    |

|     | for different MP configurations                                 | 45 |

| 4.5 | Benchmark execution time with 10000 items and additional high-  |    |

|     | priority task                                                   | 46 |

| Δ 1 | Zynq-7000 SoC: Reference manuals                                | 49 |

|     | v -                                                             |    |

|     | Zynq-7000 SoC: Third-party IP and standards documents           |    |

| A.3 | Reference manuals: Miscellaneous                                | 50 |

# List of Figures

| 2.1 | Comparison of SMP and AMP systems                                   | 6  |

|-----|---------------------------------------------------------------------|----|

| 2.2 | Zynq-7000 SoC Processing System internal view (Vivado)              | 7  |

| 2.3 | Hardware-software design flow                                       | 18 |

|     |                                                                     |    |

| 3.1 | Block Design view of the smallest design that includes a Processing |    |

|     | System (Vivado)                                                     | 23 |

# List of Listings

| 3.1 | CPU1 wake-up process                                              | 28 |

|-----|-------------------------------------------------------------------|----|

| 3.2 | Recursive locks variables and macros                              | 33 |

| 3.3 | FreeRTOS spinlock interface                                       | 34 |

| 3.4 | Recursive spinlock acquisition function v1                        | 36 |

| 3.5 | Recursive spinlock release function                               | 37 |

| B.1 | Memory dump of CPU1 boot instructions                             | 52 |

| B.2 | ARMv7-A instructions decoded from Listing B.1                     | 52 |

| В.3 | Core takes part in the SCU cache coherency protocol               | 53 |

| B.4 | Page table configuration for DDR memory                           | 54 |

| B.5 | Alternative CPU1 wake-up process                                  | 56 |

| B.6 | Macro to select the FreeRTOS_IRQ_Handler version                  | 57 |

| B.7 | Section of FreeRTOS_IRQ_Handler that could be optimized to handle |    |

|     | external yield requests                                           | 58 |

| B.8 | Usage of memcpy() within an interrupt handler                     | 61 |

| C.1 | Memory layout of the benchmark program in AMP configuration .     | 64 |

| C.2 | Shared memory section definition in AMP configuration             | 64 |

| C.3 | Benchmark program for CPU0 in AMP                                 | 67 |

| C.4 | Benchmark program for CPU1 in AMP                                 | 69 |

# Acronyms

#### **AAPCS**

ARM Architecture Procedure Call Standard.

#### AMP

Asymmetric Multiprocessing.

#### $\mathbf{AP}$

Application Project.

#### API

Application Programming Interface.

#### APU

Application Processing Unit.

#### BSP

Board Support Package.

#### CA9

Cortex-A9.

#### CPSR

Current Program Status Register.

#### CPU

Central Processing Unit.

#### $\mathbf{C}\mathbf{U}$

Computational Unit.

#### DDR

Double Data Rate.

#### DMB

Data Memory Barrier.

#### DSB

Data Synchronization Barrier.

#### **EABI**

Embedded Application Binary Interface.

#### $\mathbf{E}\mathbf{S}$

Embedded System.

#### $\mathbf{FP}$

Floating Point.

#### **FPGA**

Field Programmable Gate Array.

#### **FSBL**

First Stage Boot Loader.

#### GIC

Generic Interrupt Controller.

#### $\mathbf{GUI}$

Graphical User Interface.

#### HDL

Hardware Description Language.

#### ISB

Instruction Synchronization Barrier.

#### L1

Level 1.

```

L2

Level 2.

MCU

```

Microcontroller Unit.

$\mathbf{MMU}$

Memory Management Unit.

MP

Multiprocessing.

MPU

Microprocessor Unit.

os

Operating System.

PL

Programmable Logic.

PoC

Point of Coherency.

$\mathbf{PoU}$

Point of Unification.

PP

Platform Project.

PPI

Private Peripheral Interrupt.

PS

Processing System.

RTOS

Real-Time Operating System.

#### SCU

Snoop Control Unit.

#### SDT

System Device Tree.

#### SEV

Send Event.

#### SGI

Software Generated Interrupt.

#### SMP

Symmetric Multiprocessing.

#### SoC

System-on-Chip.

#### $\mathbf{SP}$

Stack Pointer.

#### $\mathbf{SPI}$

Shared Peripheral Interrupt.

#### SPSR

Special Program Status Register.

#### TMR

Technical Reference Manual.

#### TTC

Triple Timer Counter.

#### **UART**

Universal Asynchronous Receiver-Transmitter.

#### $\mathbf{WFE}$

Wait For Event.

## Chapter 1

## Introduction

In the last decades, the number of devices surrounding everyone has drastically increased, along with their complexity. These devices are usually designed to perform a few specific functions, and they are referred to as Embedded Systems (ESs). Technological improvements have made the definition of ES increasingly vague. For example, a smartphone is usually considered an ES, but today its functionality makes it more similar to a general-purpose computer. Even if this is less noticeable in other devices (e.g., appliances, cars), everything has become so smart that it contains at least a Microcontroller Unit (MCU) or/and a Microprocessor Unit (MPU). Obviously, the hardware still has a non-negligible cost, so an ES is rarely implemented with state-of-the-art technology. Because of this, exploiting all the available resources becomes crucial.

The software design of simple systems can be coded in bare metal to optimize resource usage, thus saving on hardware costs. However, as the complexity of the applications grows, the required effort increases drastically. In this scenario, having a software layer that manages the underlying hardware is useful so programs can be more easily developed and ported to other devices. In the embedded domain, as many applications are time-sensitive or need to be predictable, the most common intermediate layer is a Real-Time Operating System (RTOS).

For many years, creating devices with multiple instances of a Computational Unit (CU) has been the main strategy to overcome the performance barrier imposed by the limits of single-core processors. Systems that can manage many CUs support some form of Multiprocessing (MP), but how this is exploited by the software directly depends on the target hardware. The most common approaches are known as Symmetric Multiprocessing (SMP) and Asymmetric Multiprocessing (AMP). Historically, the latter has been more widely used in the embedded domain because it can manage heterogeneous groups of processors, thus allowing better allocation of a device's resources to specific parts of an application. SMP can, in principle, provide better performance. Still, its design is less flexible than AMP,

since the processors must comply with the same architecture and the software has inherently more dependencies. Moreover, because supporting SMP on a processor introduces some overhead, developing multi-core processors for ESs has encountered some difficulties. Despite these initial problems, many embedded devices are now equipped with multiple CU [1] to meet the requirements of modern applications.

This thesis faces the problem of porting the SMP support of an RTOS to hardware that is equipped with symmetric CUs. The scope is to show that even older platforms can benefit from improved software support, leading to better utilization of the systems' resources. Nevertheless, the process is not straightforward, since the code created for a single-core device cannot run on multiple cores without being modified. If more than one CU is considered, the software structure must be enhanced with appropriate synchronization mechanisms to ensure that no race condition can disrupt the correct execution of an application.

More specifically, the thesis illustrates the process of adapting the SMP functionality of FreeRTOS, a popular open-source RTOS, to Zynq-7000 System-on-Chips (SoCs), a family of devices released in 2011. This part is preceded by general concepts, which provide the theoretical knowledge required to understand the porting procedure. The description of the Zynq-7000 SoC, the Cortex-A9 (CA9) processor that powers it, and the tools used during the development are only some of the treated arguments. Furthermore, the steps that lead to the final implementation of the SMP port for the Zynq-7000 SoC are presented in a way that eases the comprehension, since the discussion is divided into topics rather than being a mere changelog. As a result, the focus is placed on the hardware-software dual-core configuration and the changes that address it. Some time will also be spent to describe the additional primitives that enable the execution in SMP mode. Finally, the leveraged testing tools and programs are presented, before briefly showcasing the achieved performance of the SMP port compared to an AMP configuration.

## Chapter 2

# Background

This chapter provides the foundation for the port implementation described in Chapter 3. Initially, an overview of the multiprocessing techniques considered in this document is included, followed by a brief comparison. Afterwards, both the RTOS and the SoC are presented in depth so that the reader can grasp more easily the porting process. In this sense, the architecture of the SoC, its components, and the software that powers them are detailed more than FreeRTOS itself. Indeed, while the internal functioning of the RTOS constrains the structure of the low-level code, there are often several ways to implement a port function given a specific hardware. Nevertheless, in case a non-trivial concept was inadvertently overlooked, FreeRTOS provides complete documentation [2]. The chapter concludes with a description of the development environment.

### 2.1 Multiprocessing

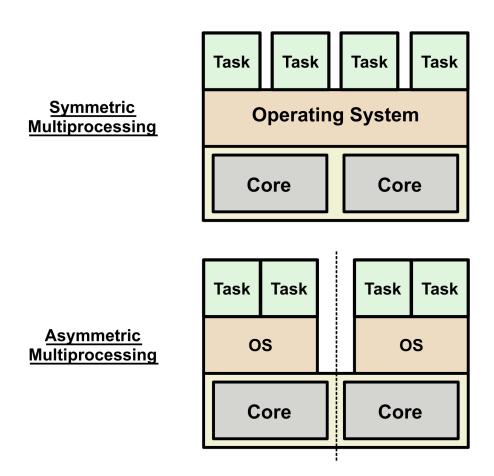

The term Multiprocessing commonly refers to the ability of a system to simultaneously use more than one Central Processing Unit (CPU) to perform the required computation. The definition can be further adapted to a specific context, since it is functional to describe the possible interactions between the different CU of a system. Multiple CPUs on many interconnected printed circuit boards, multiple cores of a single CPU, and different processors with specialized architectures (e.g., graphic and neural processing units) on an SoC are only some of the possible configurations that can be observed in modern devices. For this thesis, a CU is identified either as a core or a processor, and MP is defined as the ability of a CU to coordinate with other CUs to fulfill the function of a system. Different MP solutions can be implemented on a single device depending on the symmetry of the CUs. Some of the most common approaches are described below, other than being pictured in Figure 2.1:

#### • Asymmetric Multiprocessing

In an AMP system, the CUs are typically heterogeneous at both the hardware and software levels. The processors have distinct architectures and mostly separate memory address spaces while the programs they run can be completely different (e.g., bare-metal code and an Operating System). The CUs communicate with each other through shared memories and interrupt-driven messaging mechanisms (e.g., hardware mailbox), which can be abstracted by using proper frameworks (e.g., OpenAMP) or ad hoc software solutions.

A device that integrates an MCU to deal with sensors and other peripherals and an MPU to run a lightweight Operating System (OS) is a classic AMP system. The strength of such designs lies in their flexibility and adaptability to a wide range of requirements. In the previous example, the MPU-MCU pairing may be a low-power solution for an application that needs to fetch and label data before transmitting it to the cloud for further processing.

#### • Symmetric Multiprocessing

An SMP system is equipped with CUs that are homogeneous in terms of hardware and software. The architectural uniformity ensures that the entire set of CUs can be managed by a single instance of an OS and most of the address space is shared, or at least coherent, to ease the interaction of the CUs. When it comes to software design, it is still possible to assign additional tasks to each CU, but, compared to the whole application code, the exclusive code a CU has to execute is generally a small fraction. This approach ensures that the OS can effectively distribute the system's workload on all the provided units. However, the fact that CUs share most of the data structures is also a disadvantage because the skills and effort required to produce functionally correct SMP software are much higher than the ones needed to code an application for a single CU.

A multi-core MPU is the most obvious example of SMP system, even though devices equipped with multiple instances of a single-core processor can be found in the embedded domain.

SMP can potentially achieve higher performance than AMP because the homogeneous architecture enables designers to tightly couple the CUs [3]. Faster inter-core communication mechanisms and workload distribution across the CUs are only some of the advantages SMP offers. However, there are some significant drawbacks, as the additional complexity needed to realize such systems must be addressed in hardware and software. The architecture becomes more elaborate in terms of area and power consumption, due to the CUs' duplication and the supplementary units that provide the actual SMP support. For example, ARM Cortex-A MPUs integrate a module called Snoop Control Unit (SCU) that maintains the L1-cache

coherence for the cores participating in this process. From a software perspective, especially when the hardware support is not enabled, the application writer has numerous restrictions that would not be present with a single CU. In general, the higher the number of CUs that interact with the same data structures, the higher the sections of code that need proper synchronization mechanisms to preserve the application logic. Furthermore, as hinted before, if SMP is not properly supported at the hardware layer, the software may need to deal with several other hardware-related issues (e.g., memory coherency). Because of these problems, AMP has been historically more popular than SMP in ESs. AMP also has the advantage of better fitting the needs of many embedded applications, since it allows to assign a separate part of the application to each part of the system. This characteristic can be beneficial in mixed-criticality systems as every domain can be certified separately.

Despite their advantages and disadvantages, AMP and SMP are rarely interchangeable. Instead, they are usually employed to face different problems. For this reason, in some systems, selecting one of the two approaches would not benefit the application as much as combining them in a hybrid form of MP, which can be referred to as hybrid multiprocessing. This choice is particularly convenient when clusters of symmetric processors can be managed asymmetrically so that each cluster can be specialized in a task (AMP) and completely exploit the resources of the processors within the cluster to efficiently execute the task (SMP).

### 2.2 Zynq-7000 SoC

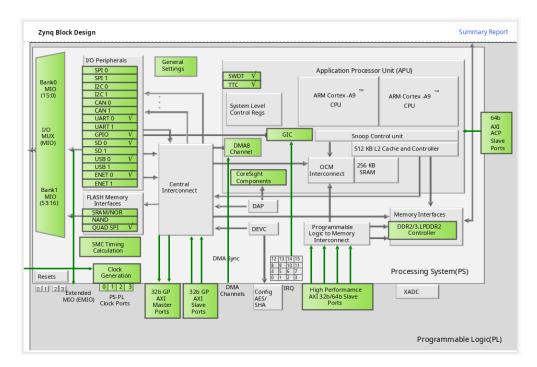

The Zynq-7000 SoC is a family of devices developed by Xilinx, now part of AMD, offering hardware and software programmability on a single chip. These features are achieved through the integration of a Processing System (PS), which embeds an ARM-based processor, and a Programmable Logic (PL), which provides the functionality of a Field Programmable Gate Array (FPGA). The heterogeneous architecture is especially suited for applications that need a compromise between hardware acceleration and the flexibility of a powerful processor.

SoCs in this family are divided into two series: Zynq-7000 and Zynq-7000S. This thesis focuses on the former architecture, as all the PSs feature an Application Processing Unit (APU) equipped with a dual-core ARM CA9 processor. Zynq-7000S SoCs are not considered, since the PS embeds a single-core CA9. Aside from the PS, the hardware configuration of both the board and the PL is not relevant to the thesis' objectives, so it will be presented in detail during the dissertation if deemed necessary. For reference, an internal view of the PS is depicted in Figure 2.2.

The cores in the APU are connected in an MP configuration, sharing a unified

Figure 2.1: Comparison of SMP and AMP systems  $\,$

Figure 2.2: Zynq-7000 SoC Processing System internal view (Vivado)

512 kB L2-cache and an SCU, which is responsible for maintaining the L1-cache coherency. Despite the architectural symmetry, the CUs can assume separate roles, as reported in Section 2.1. For example, the system boot is usually executed on one of the available cores (i.e., the primary core). In contrast, the others (i.e., the secondary cores) are started from the primary core after the system has been initialized. Therefore, for clarity, the two cores will hereafter be referred to as CPU0 and CPU1.

#### 2.2.1 PS Software Boot Process

The complete Zynq-7000 SoC boot is a complex process that involves several hardware and software passages [4, ch. 6]. However, the stages required to boot the PS are sufficient to understand the arguments exposed in the following chapters.

The Zynq-7000 SoC PS boot [5, ch. 3] is a process divided into a maximum of three steps: stage-0 boot, First Stage Boot Loader (FSBL), and, optionally, second stage boot loader. The stage-0 code stored in the on-chip ROM is the first software to be executed on the PS and it also known as BootROM code. Among its tasks, this program sets up the APU, configures the system peripherals according to the selected boot mode (e.g., JTAG, Quad-SPI, and SD memory card), and moves the FSBL from the boot device to the on-chip memory. The FSBL continues the PS' setup and eventually programs the PL before loading a second stage boot loader (e.g., U-Boot) or a bare-metal application in Double Data Rate (DDR) memory. The FSBL that is executed after the BootROM phase can be entirely customized depending on the user's needs, but AMD provides an example, which is enough for most applications.

### 2.2.2 Application Processing Unit Modules

Besides the CA9 processor, the APU includes several hardware units that provide core functionalities of the system. Among them, two modules are particularly relevant for the work presented in this thesis: Generic Interrupt Controller (GIC) and Triple Timer Counters (TTCs).

A TTC comprises three independent 16-bit timers, each equipped with a 16-bit prescaler, whose input clock can be selected from the available sources. Every counter can generate an output waveform (e.g., Pulse Width Modulation) and a periodic interrupt. Such action is triggered by an overflow, either on the entire counting range, a shorter interval, or a match with a configurable value. The APU features two TTCs for a total of six timers.

The interrupt controller incorporated in the APU is a PrimeCell GIC (PL390), based on the non-vectored ARM GIC Architecture version 1.0. The GIC is logically divided into a global Distributor and a series of local CPU interfaces.

The Distributor centralizes the interrupt sources and delivers the highest-priority pending interrupt to each interface. In contrast, the CPU interfaces allow cores to manage the interrupts routed through the GIC. When active, a CPU interface evaluates the associated core's priority mask and preemption policy to determine whether to signal the interrupt delivered by the Distributor. The interface is also used to acknowledge an interrupt and notify of its completion after it has been handled.

The GIC supports the configuration of security state, priority level, and target processor for an interrupt, as well as their activation and deactivation. Furthermore, the managed interrupts are classified in three groups: Software Generated Interrupts (SGIs), Private Peripheral Interrupts (PPIs), and Shared Peripheral Interrupts (SPIs). The GIC integrated in the Zynq-7000 SoC accepts signals coming from PL, I/O peripherals, and CA9 cores and routes the resulting interrupts to PL and CA9 cores.

On the Zynq-7000 SoC, each core has 16 private interrupt sources to generate an SGI, which can target itself and/or other cores, and some PPIs. Private peripheral sources are the CPU private timer and watchdogs, the global timer, and an IRQ and a FIQ, both coming from the PL. Moreover, since SPIs and PPIs are private, the Distributor registers associated with them are banked. In contrast, SPIs are a group of signals produced by several modules that the GIC delivers to CPU and PL, even though it does not manage reception and prioritization for the latter. An SPI can be assigned to multiple cores, but only one really handles it, and its sensitivity might also be configurable (e.g., rising-edge or high-level).

The Zynq-7000 SoC Technical Reference Manual (TMR) offers further information on both TTC [4, pp. 253-257] and GIC [4, ch. 7]. The GIC is also extensively described in the ARM manuals [6] [7].

#### 2.3 ARM Cortex-A9

The ARM CA9 is a highly configurable processor optimized for power and performance, part of the Cortex-A series. The processor is implemented with the ARMv7-A architecture, but besides the ARMv7-A instruction set, it supports Thumb and Thumb-2 and can be extended with Floating Point (FP) and single instruction multiple data support. A single MPU can host a maximum of 4 cores, each provided with a Memory Management Unit (MMU); however, as already stated in Section 2.2, the CA9 processor embedded in the Zynq-7000 SoC integrates only two cores. The following subsections discuss significant CA9-related concepts, which are helpful to understand the work presented in this thesis.

#### 2.3.1 Relevant features in the ARMv7-A architecture

The ARMv7-A architecture defines several features that enable software and hardware designers to create complex yet well-structured systems. The most significant concepts are briefly introduced in this subsection to facilitate the reading of Chapter 3.

#### **Cache Maintenance Operations**

In a memory hierarchy that employs cache memories, maintenance operations might be required to ensure that caches do not hold stale data due to changes in external levels of memory or activity in the MMU (e.g., modification of memory attributes). This function is provided through the "clean" and "invalidate" CP15 operations, which respectively write dirty lines to more external levels of memory and remove data from the cache. Nevertheless, these maintenance steps are not always necessary. For example, cleaning a cache line is only relevant for data caches that use a write-back policy.

Both clean and invalidate can be performed with cache set, way, or virtual address granularity. However, while set/way based operations target a specific level of cache, for virtual addresses two points are defined: the Point of Coherency (PoC) and the Point of Unification (PoU). The former is the point that allows all units that can access memory (e.g., direct memory access and cores) to have a coherent memory view. The PoU is the point where the data and instruction caches of a core can observe the same copy of a memory location. The concepts of PoC and PoU are equivalent for the CA9, as they both correspond to the Level 2 (L2) interface [6, ch. 8, pp. 19-20] because the processor does not incorporate an L2 cache. For more information on cache maintenance operations, refer to the ARM documentation [8, sec. B2.2.7] [6, ch. 8, pp. 17-21].

#### **Processor Modes**

The ARM architecture provides multiple processor modes to handle different scenarios that can occur during the operation of a system. These modes are classified as either Privileged or Unprivileged, and aside from User mode, all modes are privileged, so their ability to perform certain operations is not restricted. An essential aspect of processor modes is that some of the provided 16 32-bit general-purpose registers and the Current Program Status Register (CPSR) are shared across modes. Therefore, registers may need to be saved before being used. Nevertheless, some modes (e.g., FIQ) still have banked registers, meaning the software might access different physical locations depending on the active mode. Stack Pointer (SP) and Special Program Status Register (SPSR) are the only registers banked in all modes, except User and System mode, which share the

same set of registers. Since some processor modes are associated to exception events, the SPSR is used by the processor to automatically save the CPSR of the mode that was active before the arrival of an exception, while banked SPs allow to allocate separate stacks for each mode. The topic becomes even more complex when additional architectural extensions, like the Virtualization Extensions, are introduced. These cases are beyond the scope of this thesis, but they can be explored further in the ARM manuals [8, sec. B1.3] [6, ch. 3].

#### **Exception Handling**

According to ARM's definition [8, sec. B1.8-B1.9] [6, ch. 11], an exception is a condition that disrupts the normal execution of a program due to an external event. When the processor receives such a signal, it immediately manages the request by executing the handler associated with the exception in the vector table. This step is preceded by other operations, which ensure the correct resumption of normal execution after the event [6, sec. 11.2]. Among the different types of exceptions, interrupts are particularly meaningful to understand some of the topics presented in this thesis. ARMv7-A divides interrupts into "IRQ" and "FIQ", so that, when triggered, all exceptions disable IRQ, but only FIQ and reset disable FIQ.

Since ESs often execute code in response to interrupts, the speed at which the processor reacts to external events is a crucial factor, referred to as interrupt latency. Consequently, other than the classic exception management, the software can define a reentrant interrupt handler to support nested interrupts [6, sec. 12.1]. This feature allows to prioritize interrupts, reducing latency for higher priority events.

#### **Memory Barriers**

Memory barriers are instructions that generate synchronization events to constrain the execution of memory operations that appear before and after the barrier. ARM provides three instructions of this kind to support its memory ordering model: Data Synchronization Barrier (DSB), Data Memory Barrier (DMB), and Instruction Synchronization Barrier (ISB). DSB and DMB can be applied to different "shareability domains" and only affect memory accesses generated by load/store instructions and cache maintenance operations. However, the CA9 support exclusively system-wide DSBs [9, sec. 7.5]. DMB ensures that any explicit memory access preceding it is observed before any subsequent memory access. DSB imposes the same conditions of DMB, but it also enforces the completion of memory operations that appear before the barrier. Finally, ISB flushes the pipeline, forcing it to freshly fetch the following instructions. This is especially useful when context-altering operations (e.g., translation lookaside buffer or branch predictor operations) before ISB must be visible to instructions executed after the barrier.

Additional information is reported in the ARM documentation [8, sec. A3.8.3] [6, sec. 10.2].

#### ARM Architecture Procedure Call Standard

As applications are composed of multiple code modules, often written in different languages, a standard set of rules is required to ensure interoperability in ARM executables. For ESs, these rules are collected under the ARM Embedded Application Binary Interface (EABI). However, since the comprehension of the next chapter does not need such extensive knowledge, the attention can be solely focused on the ARM Architecture Procedure Call Standard (AAPCS). This is a part of the EABI that defines conventions on registers and stack usage, which must be respected by compilers and routine calls to guarantee the correct execution of a program. Key concepts are the relation between stack organization and function calls and the classification of registers in three functional groups: argument or caller-saved, callee-saved, and special registers. In particular, the rules related to memory organization specify the layout of data in memory and argument registers for function parameters, and that 64-bit types must be aligned to 8-byte boundaries. More details are discussed in the ARM Cortex-A Series Programmer's Guide [6, ch. 15].

#### 2.3.2 Memory Management Unit

An MMU is a hardware unit that acts as an interface between the processor and the memory system to manage memory accesses. This task is primarily fulfilled by denying illegal memory operations and translating the virtual addresses from the processor domain into physical addresses, which are used to access memory locations. For these reasons, the MMU can operate in conjunction with various levels of cache (e.g., Level 1 (L1) and L2), other than external memory. The MMU integrated in the CA9 is compatible with the Virtual Memory System Architecture version 7; therefore, it supports a variety of features, as described in the ARM Architecture Reference Manual (ARMv7-A) [8].

To understand the configuration of an MMU in an SMP system, examining how the address translation is performed is essential. However, the project developed in this thesis uses a 1:1 mapping, so there is no distinction between virtual and physical addresses. The process is based on hardware structures, called translation tables or page tables, which host a series of entries whose primary function is to transform a virtual address into a physical address. Attributes related to memory sections and access permissions are also encoded together. Each entry refers to a portion of the system's memory, but the actual size of such a block, also called page, depends on the specific architecture. This parameter is critical, since the

correct sizing can drastically influence the performance of memory accesses. The CA9 MMU supports 4 kB, 64 kB, 1 MB, and 16 MB pages, as well as two-levels page tables.

Memory types and attributes are concepts strictly tied to the managed memory section of a memory map [8, sec. A3.5] [4, pp. 59-62]. Three mutually exclusive memory types exist: Normal, Device, and Strongly-ordered. Memory that stores data and programs (e.g., DRAM, SRAM, ROM, and flash) is generally marked as Normal. Differently, I/O peripherals are tagged as Device or Strongly-ordered memory because they need to comply with more restrictive access rules. The "shareability" and "cacheability" attributes also affect the memory access order of the types that define them. The former divides the system into different domains, each with specific features related to the predictability and coherence of the memory operations. In the Zyng-7000 SoC, the inner shareable domain ensures coherency between the CA9 L1 caches. In contrast, the outer shareable domain provides the exact property to CPU, L2 cache, and other peripherals (e.g., direct memory access) which may access a shared memory. Cacheability is somewhat linked to shareability, since it allows to control the coherency of observers that are not part of the shareability domain of a memory region. In the Zynq-7000 SoC, memory regions marked as inner cacheable can be fetched in both L1 and L2 cache, while the ones tagged as outer cacheable can reach only the L2 cache.

#### 2.3.3 Exclusive Access

As explained in Section 2.1, SMP systems require a non-negligible software development effort. Hardware cannot always guarantee the functional correctness of application-level logic, which typically follows a hardware-independent design model. A concurrent access to the same resource by multiple CUs defines a region of code referred to as critical section and is a primary example of this concept.

The solution to such an issue is mutual exclusion. However, while in single-core systems mutual exclusion can often be achieved by disabling interrupts, in a multi-core device this is not possible because other CUs might still use the shared resource. Instead, these systems resort to hardware-software mechanisms named spinlocks.

ARMv7-A provides three basic instructions to implement mutual exclusion: LDREX (Load-Exclusive), STREX (Store-Exclusive), and CLREX (Clear-Exclusive). These primitives rely on the ability of exclusive access monitors to track the accessed memory addresses. Furthermore, the specific monitor used in a particular scenario depends on the shareability attribute that marks the tagged address. Non-shareable memory regions are only tracked with the local monitor of a core, while shareable sections are additionally checked by a global monitor, which also considers other observers' activity in the shareability domain. Monitors can assume

either the "open access" or the "exclusive access" state and can transition between these states in response to exclusive access instructions. The CA9 includes a local monitor in each L1 cache [9, ch. 7, p. 8], whereas the presence of a global monitor is never explicitly mentioned. This is consistent with the possibility of integrating both local and global monitors into a single unit [8, ch. A3, p. 116]. Furthermore, the Zynq-7000 SoC provides two additional monitors in the DDR Controller [4, pp. 142-145].

LDREX performs a load and tags the address in the exclusive monitor, while STREX conditionally executes a store when the location is marked as exclusively monitored by the core. Therefore, LDREX and STREX must be used as a pair. CLREX clears the state of a monitor; thus, it can be employed to ensure that an STREX-LDREX pair does not depend on the result of previous exclusive accesses. Naturally, the behavior of these instructions and their variants is slightly different depending on the shareability attribute of the target memory. Moreover, the number of bits for a tag is implementation-defined, but always limited between 29 and 21 bits. The size of the tagged memory block, known as Exclusives Reservation Granule, is equal to 8 words, aligned on an 8-word boundary, for the CA9 [9, ch. 7, p. 8], and can be retrieved in the CP15 Cache Type Register (c0) [8, sec. B4.1.42] as  $\log_2 \text{ERG}$ .

Further information on the topic can be retrieved from the ARM documentation [6, sec. 18.8] [8, sec. A3.4.1-A3.4.5].

#### 2.3.4 Global and Private Timers

Hardware timers are essential components that enable designers to implement time-related functions in their applications. The CA9 integrates a private timer and watchdog block per core, in addition to a global timer accessible by all cores. The private timers and watchdogs are 32-bit decrementing counters capable of generating interrupts when the count reaches zero. The counting mode is set to single-shot or auto-reload, and both prescaler and initial value can be configured via software. In contrast, the global timer is a 64-bit incrementing counter, split into two separately accessed 32-bit registers, that can generate interrupts with an interval shorter than its counting period. Although the global timer is shared, the registers to configure this feature are banked, making the interrupt private to each core. All these modules are clocked by the PERIPHCLK signal, which corresponds to half the CPU frequency on the Zynq-7000 SoC [4, p. 245]. More details on the timers' registers can be found on the CA9 MPCore TMR [10, ch. 4].

#### 2.4 FreeRTOS

FreeRTOS is a market-leading open-source RTOS developed by Real Time Engineers Ltd., now maintained by Amazon Web Services as part of the AWS FreeRTOS project [11]. It stands out from other competitors (e.g., ThreadX and Zephyr) thanks to its small memory footprint and simplicity without giving up the numerous features of the kernel. This is reflected by the variety of supported task scheduling strategies (preemptive, cooperative, and hybrid), inter-task communication (queues, task-notifications, event groups, stream, and message buffers), and synchronization primitives (mutexes and semaphores). Reliable time-sensitive applications can be implemented thanks to the deterministic real-time scheduler, the software timer Application Programming Interface (API), and the deferred interrupt handling, all while maintaining a low power consumption in tickless idle mode. The memory management is highly flexible, providing both static and dynamic approaches. This allows various design choices tailored to the specific application and target device.

FreeRTOS features a layered architecture, which separates hardware-dependent components, commonly referred to as port layer or port, from hardware-independent code. Combined with its well-structured design, it helps the kernel to be highly portable and support a broad range of architectures: ARM Cortex-M/A/R, RISC-V, and many others.

FreeRTOS is mainly present in Internet of things, industrial automation, and automotive domains where real-time performance and reliability are essential. Its adoption is backed up by many libraries, which extend the basic functions of the kernel (FreeRTOS-Plus) and allow a deep integration with the AWS cloud environment.

### 2.4.1 Symmetric Multiprocessing in FreeRTOS

Since 2003, FreeRTOS has been developed as a single-core RTOS. This was reasonable in the project's early days because ESs were not equipped with symmetric CUs. However, AMP still enabled to achieve a certain degree of MP in the developed systems. Following the design improvements in the embedded domain, FreeRTOS has been upgraded to officially support SMP in its kernel. Therefore, starting from version 11.0.0, along with the options already available, the FreeRTOS configuration file FreeRTOSConfig.h also provides SMP-related macros: configNUMBER\_OF\_CORES, configRUN\_MULTIPLE\_PRIORITIES, configUSE\_CORE\_AFFINITY, etc.

The design of the new features is coherent with the description of SMP provided in Section 2.1, but it also integrates some additional options, as hinted by the names of the listed macros. In fact, while the traditional definition of SMP implies that each core can execute every task, FreeRTOS can be configured to bind some tasks to specific cores or, if preemptive scheduling is active, to prevent tasks with

different priorities from running on multiple cores simultaneously. Furthermore, the SMP kernel enables individual tasks to be configured either in preemptive or cooperative mode, leading to hybrid forms of MP even within a symmetric set of CUs. Although the listed features introduce some variations to the original concept of SMP, they are not uncommon in modern OSs. In the context of ESs, they are instrumental when an application is migrated from a single-core to a multi-core environment because they allow the restriction of the software-level symmetry.

The FreeRTOS ports that have already been upgraded to integrate SMP are located in the portable/ThirdParty/ directory of the FreeRTOS-Kernel repository [12]. However, these ports are not always developed by the FreeRTOS team, as partners and community members can also undergo the contribution process. Among the available ports, the most notable are the XCORE AI and Raspberry Pi Pico (FreeRTOS Team Supported), the Texas Instruments Cortex-A53 (Partner Supported), and the Zynq UltraScale+ MPSoC Cortex-A53 (Community Supported).

Despite the popularity of FreeRTOS and the significant potential of using SMP in embedded devices that support it, the number of ports that implement this form of MP remains limited. Many factors contribute to the problem, such as limited documentation, the required development effort, and the availability of more mature alternatives (e.g., Zephyr).

About the documentation, aside from the numerous individual posts on the FreeRTOS forum, the two primary sources of information are the XMOS SMP design guide [13] and a popular thread discussing the Cortex-A53 SMP port [14]. It is important to note that these resources contain conflicting guidelines due to the evolution of some constraints over time. The forum post should be trusted in such cases, as it is more recent than the design document.

#### 2.4.2 FreeRTOS on ARM Cortex-A9

The FreeRTOS documentation provides a dedicated page to illustrate the characteristics of the CA9 port for devices that incorporate a GIC [15]. The most relevant features of this port are the hardware FP support and the implementation of the interrupt nesting model.

The context-switch logic can be configured to save the FP registers for all tasks or only when explicitly enabled by calling vPortTaskUsesFPU() within a task. Furthermore, FP operations cannot be used by default inside interrupt handlers. This functionality must be manually set up by modifying the FreeRTOS handler associated with the IRQ exception in the vector table (FreeRTOS\_IRQ\_Handler), so that vApplicationFPUSafeIRQHandler is called instead of vApplicationIRQ-Handler. Additionally, care must be taken to avoid the usage of functions such as memcpy() and memset(), as well as any FreeRTOS API that may rely on them

(e.g., xQueueSend()), inside both tasks and interrupt handlers. In fact, compilers may exploit FP registers to optimize these functions. The kernel also enables the definition of a maximum priority that allows interrupts to call faster interrupt-safe APIs, whose name ends with fromISR.

The implementation of nested interrupt handling is analyzed in Section B.6, while further details on the configuration and customization of the CA9 port can be found in the FreeRTOS documentation [15].

### 2.5 Development Tools

The development of modern applications for ESs often requires the assistance of an environment that automates and simplifies some steps of the design flow. Being equipped with both a PS and a PL, Xilinx devices are no exception to this rule, as they require a hardware-software co-design platform. Moreover, in case the application is designed to run with the support of an OS, debugging it becomes challenging, especially if the software is executed on multiple CUs. In this scenario, an additional OS-aware trace tool may be needed to capture the application's behavior at runtime.

#### 2.5.1 Hardware-Software Design Platforms

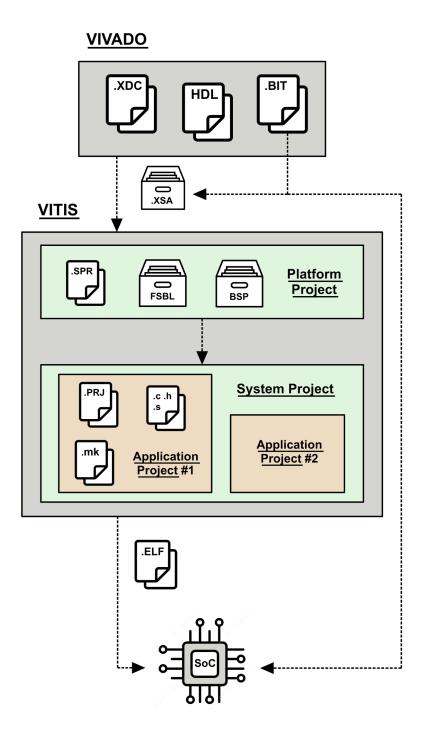

Vitis and Vivado are development platforms that support the design and implementation of hardware and software designs on Xilinx FPGAs and SoCs.

Vivado offers a comprehensive tool suite covering the entire hardware development workflow. The design begins with the description of a circuit using an Hardware Description Language (HDL), such as Verilog and VHDL, or by connecting various intellectual properties and custom blocks, which Vivado can group into an HDL wrapper. The flow proceeds through synthesis, place, and route, which can be automated to streamline the design iterations. In the end, a bitstream is generated before programming the target FPGA or exporting the generated hardware.

Vitis is a software platform that provides end users with several tools to integrate their designs on Xilinx devices. To start building an application, a target system must be selected to create a Board Support Package (BSP). Vitis comes with various predefined devices, but it is also possible to create and import one from Vivado. An application can then be developed in bare metal or on top of an OS, as both FreeRTOS and Linux are supported. The designed software can finally be cross-compiled, using one of the preinstalled toolchains, and debugged, resorting to GDB or the Eclipse TCF Agent. Vitis also handles deployment by loading the produced binary on the PS and programming the PL with a bitstream.

Figure 2.3 visually represents the aforementioned co-design flow.

Figure 2.3: Hardware-software design flow

#### 2.5.2 Xilinx Software Libraries

Most of the software components that power the design experience offered by Vitis are sourced from the Xilinx "embeddedsw" software library [16]. This open-source repository contains a collection of libraries and drivers that provide essential code to build BSPs and ease the interaction with various hardware modules.

The BSP configuration changes according to the available hardware and the abstraction level of the designed application. When the latter aspect is considered, the most relevant packages for the scope of this work are the "standalone" and "FreeRTOS" BSPs. The standalone BSP is a low-level software library exploited in bare-metal designs to manage the PS and its hardware modules (e.g., caches and timers). On the other hand, the latest version of the Xilinx FreeRTOS BSP includes both the APIs of the standalone BSP and the features of release 10.6.1 of the FreeRTOS kernel [12, tag V10.6.1], adequately adapted to the MPUs embedded in the supplied SoCs.

The drivers included in the BSPs facilitate the interaction between the application code and the modules in the PS. Obviously, each hardware unit is used to an extent that depends on the characteristics of system and application. For this reason, some modules have more optimized APIs (e.g., GIC and private timer) while others may not even need a driver (e.g., ). Additionally, as explained in Section 2.1, despite the presence of symmetric CUs, ESs are frequently configured in single-core or AMP. This often leads designers to ignore issues strictly related to SMP during the engineering of the driver.

The FreeRTOS portable code for the Zynq-7000 SoC uses substantially two drivers: scugic and scutimer. The latter supports the CA9 private timers, together with its features (e.g., hardware interrupts), whereas the former provides an interface to interact with the GIC. Although it is not present in the hardware-dependent layer, the ttcps driver is also relevant in this thesis, as it has been employed in the test demo to control the TTC module.

#### ScuGic driver

This subsection details the design of the scugic driver, as a solid knowledge of such library is essential to understand the design choices described in Subsection 3.4.2.

The scugic library is based on three main data structures, declared in xscu-gic.h: XScuGic, XScuGic\_Config and XScuGic\_VectorTableEntry. Each structure contains the preceding one as a member in the listed order. An XScuGic\_Config instance stores information on the device managed by the driver. More precisely, it holds the ID assigned to the GIC in the BSP, the base address of Distributor and CPU interface, and an array of XScuGic\_VectorTableEntry, named HandlerTable, which records the key-value pairs (Interrupt ID, Handler Address).

The library allocates a single XScuGic\_Config variable in xscugic\_g.c, which is referenced through a pointer whenever the GIC configuration is retrieved with a call to XScuGic\_LookupConfig(). The execution of this preliminary step is essential, as the function XScuGic\_CfgInitialize() assigns the XScuGic\_Config\* pointer to a XScuGic instance during its initialization. Once configured, each XScuGic variable can be used by a core as an interface to interact with the selected GIC through the scugic driver.

The library also includes logic to handle multi-core scenarios, since it defines the internal variable CpuId to identify the target core and guards the GIC shared registers, which are part of the Distributor, using the spinlock API contained in the standalone BSP.

Further information can be found in the library's source code inside the directory XilinxProcessorIPLib/drivers/scugic of the embeddedsw repository [16].

#### Xilinx spinlock API

The standalone BSP provides a simple spinlock for CA9 processors to deal with critical sections in developed applications. However, the implementation is limited to a single non-recursive spinlock, making it suitable primarily for Xilinx APIs that can leverage it and for elemental bare-metal designs.

The library declares the internal variables Xil\_Spinlock\_Addr, which stores the address of the spinlock, and Xil\_Spinlock\_Flag\_Addr, which holds the address of the spinlock's status. The flag is set to either XIL\_SPINLOCK\_ENABLED or 0, depending on whether the lock has been initialized. Such action is performed by calling Xil\_InitializeSpinLock(), while to release a spinlock, the function Xil\_ReleaseSpinLock() is used. An important detail is that the lock and its status can reside within the same 32-byte memory region because the flag is not accessed using the exclusive operations described in Subsection 2.3.3.

After being initialized, the spinlock can be claimed with Xil\_SpinLock() and unlocked with Xil\_SpinUnlock(). As the lock does not support recursive acquisitions, it cannot be claimed multiple times by its owner; hence, a Xil\_SpinLock() must always be followed by a Xil SpinUnlock().

For a more detailed description of the API's usage, refer to the files lib/bsp/standalone/src/arm/common/xil\_spinlock.\* provided with the Xilinx embeddedsw library [16].

### 2.5.3 Trace and Debug

Vitis provides native OS-aware debug options, but only Linux is entirely supported. Nevertheless, FreeRTOS can be debugged by other means, as it integrates numerous trace macros in the kernel that the user can selectively implement to extract

relevant runtime information (e.g., context-switch actors). Furthermore, Percepio Tracealyzer and its free version, Percepio View, can exploit these trace macros to collect statistics during the execution of a program and analyze them through a practical Graphical User Interface (GUI). More specifically, trace data is stored inside a static buffer in either "Snapshot" or "Streaming" mode. Unfortunately, Percepio View offers only a subset of the features available in Tracealyzer. Despite its limitations, for the aims of this thesis, Percepio View has been revealed to be a valuable tool for achieving observability in a system running FreeRTOS in SMP mode.

Despite the availability of trace tools, debugging must also be supported by a well-designed set of tests to be effective. FreeRTOS provides a variety of predefined demos, each targeting a specific device, along with a template to create new demos, respectively located under Demo/ and Demo/ThirdParty/Template in the FreeRTOS Github repository [17].

## Chapter 3

## Implementation

This chapter details the process of porting the FreeRTOS kernel's SMP support to the Zynq-7000 SoC. The discussion begins with the setup of hardware and software environments, followed by the analysis and update of the existing port for Zynq-7000 SoC from version 10.6.1 to version 11.1.0 of the kernel. After this initial phase, which focuses purely on the single-core functions, the implementation of the SMP port is presented. More specifically, the description starts by explaining the dual-core boot process of the Zynq-7000 SoC, immediately followed by the multi-core configuration of FreeRTOS, to provide a complete picture of the CPU1's bring-up procedure. Ultimately, the main changes introduced in the port are illustrated, before showing the debug tools and the demo application exploited to validate the final implementation.

It is essential to underline that although this chapter includes some configuration steps when the discussion requires them, its objective is to explain the design choices behind the implementation of the SMP port and its test demo. Detailed guides to achieve functioning projects based on the Zynq-7000 SMP port [18] and the related test demo [19] can be found in the README.md files published on the "FreeRTOS Community Supported" repositories.

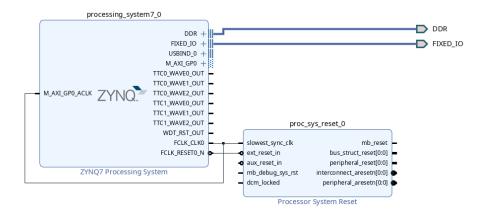

### 3.1 Development Environment

The hardware provided for developing the FreeRTOS SMP port is a TUL PYNQ-Z2, which integrates a Zynq-7020 SoC. As discussed in Section 2.2, this chip is part of the Zynq-7000 series and is equipped with a dual-core ARM CA9.

As for the development platforms, general concepts about the tools adopted to manage the hardware and software layers, which serve as the foundation of the entire project, have been introduced in Section 2.5. The specific version used for both Vitis and Vivado is 2021.1, as it is more lightweight than newer releases

but still provides the needed development features. However, concerning Vitis, the "Classic" edition does not integrate the System Device Tree (SDT) flow as the "Unified" one. Consequently, the parts that support the SDT flow have not been upgraded with the rest of the single-core port and are thus overlooked in the following discussion. Furthermore, Vitis uses a version of the embeddedsw library aligned to its release. This introduces the risk of working with outdated BSPs and drivers. The release tagged xilinx\_v2024.1 [16] was preferred to address this issue. Compared to the library bundled with Vitis 2021.1, the standalone BSP contains more useful drivers to interact with the Zynq-7000 SoC and fixes for specific CA9 operations.

Creating a hardware design for the PYNQ-Z2 in Vivado is thoroughly documented online [20]. It is therefore not presented here, as it does not influence any of the topics discussed in this thesis. For reference, Figure 3.1 shows the minimal set of hardware modules required to work with the PS. The generation of Platform Project (PP) and Application Project (AP) in Vitis is omitted as well, as this process is documented both in the README.md file provided with the SMP port [18] and in the official Vitis manual [21, pp. 24–69]. Nevertheless, it should be underlined that FreeRTOS is included as an external resource in an AP based on the standalone BSP. This choice stems from the impossibility of integrating BSPs with custom names and structures into the Vitis GUI without editing its back-end scripts. In conclusion, the cross-compilation is handled using the arm-none-eabitoolchain shipped with Vitis, so, unless explicitly stated, it is implied that the referenced FreeRTOS ports are compiled with version 10.2.0 of the GNU compiler (GCC) [22].

**Figure 3.1:** Block Design view of the smallest design that includes a Processing System (Vivado)

### 3.2 FreeRTOS Port Update

Updating the official FreeRTOS BSP for Zynq-7000 SoCs requires modifying the hardware-dependent layer. Considering that, as stated in Subsection 2.5.2, the latest available release of the Xilinx FreeRTOS BSP is based on version 10.6.1 of the kernel [12, tag V10.6.1], the official CA9 portable files of such version have been compared with the portable layer of the FreeRTOS BSP to discover potential differences. The analysis led to a better understanding of the changes performed on the basic CA9 port to adapt it to the Zynq-7000 SoC and on the degree of integration the BSP has with the Vitis back-end. The most notable aspects are listed below, grouped by file:

- port.c implements the port functions that interface FreeRTOS with the host hardware. Compared to the CA9 template in the original kernel, the management of the runtime statistics, enabled by setting configGENERATE\_-RUN\_TIME\_STATS to 1, is embedded in the port layer and causes the system tick to be generated ten times faster. Furthermore, additional functions have been defined to ease the interrupt management in the application code, preventing the direct usage of xInterruptController, the driver's instance used to configure the GIC. Finally, prvTaskExitError, assigned to configTASK\_-RETURN\_ADDRESS inside FreeRTOSConfig.h, has been redefined to terminate a task instead of triggering an assertion when it attempts to return.

- portmacro.h defines macros employed across the entire portable layer. In the FreeRTOS BSP, they have been moved in FreeRTOSConfig.h to better integrate the FreeRTOS configuration into the Vitis GUI.

The BSP is also supplied with two auxiliary files, which ease the setup steps needed by FreeRTOS to correctly interact with both the Zynq-7000 SoC and the user-defined application:

- portZynq7000.c provides the application interrupt handler vApplication—IRQHandler, the functions used to set up the interrupt that periodically invokes the scheduler, referred to as "system tick" or "SysTick", and a weak definition of the FreeRTOS hooks to prevent possible linker errors.

- port\_asm\_vectors.S overrides the definition of the CA9 vector table and of the exception handlers provided by the standalone BSP file asm\_vectors.S. Even though \_vector\_table is defined multiple times, the linker does not produce any error and resolves the symbol to the one in port\_asm\_vectors.S. Moreover, both files are linked inside the executable, as the handlers in port\_asm\_vectors.S wrap the ones in asm\_vectors.S. The function vPort\_InstallFreeRTOSVectorTable is still present in port\_asm\_vectors.S to set

the Vector Base Address Register to the correct address, but it is not used in the current port.

The FreeRTOS configuration file FreeRTOSConfig.h has been analyzed alongside the port layer because, as explained before, its generation is deeply integrated in the Vitis environment. Unfortunately, FreeRTOS 10.6.1 did not include a template to perform a proper comparison. Moreover, the back-end script that manages FreeRTOSConfig.h selectively includes definitions according to the features enabled in the BSP configuration. Therefore, the template located under examples/template\_configuration in the FreeRTOS-Kernel repository [12, tag V11.1.0] has been preferred over the configuration file provided in the FreeRTOS BSP as a starting point for future applications.

Updating the port to version 11.1.0 did not require any particular effort, since the basic functions needed to execute FreeRTOS in single-core remained consistent across the two releases. The only significant contributions have been the relocation of some macros from the BSP FreeRTOSConfig.h to portmacro.h and the addition of vApplicationDaemonTaskStartupHook inside portZynq7000.c. The SoC-specific sections of FreeRTOSConfig.h have also been added at the end of the template.

#### 3.3 Secondary Core Bring-up Procedure

This section presents the steps required to boot the dual-core CA9 embedded in the Zynq-7000 SoC. The parts concerning the Xilinx BSP and FreeRTOS are discussed separately to improve the clarity.

#### 3.3.1 Dual-Core Boot on the Zynq-7000 SoC

The PS's boot process, presented in broad terms in Subsection 2.2.1, needs to be discussed in more detail, since understanding the role of each core is essential to achieve a multi-core boot.

In a dual-core Zynq-7000 SoC, the BootROM code begins at address 0x0 on both cores [4, pp. 151-152]. Nevertheless, while CPU0 performs the boot procedure, CPU1 parks itself in a low-power state using the Wait For Event (WFE) instruction. Therefore, to start executing code on CPU1 after the stage-0 boot, it is necessary to write the application's entry point at address 0xFFFFFFF0 and awaken the core with a Send Event (SEV) instruction [4, p. 160]. As a safety measure, even if a SEV is mistakenly issued before the content of 0xFFFFFFF0 is overwritten, CPU1 remains blocked in the same section of code. Section B.2 provides more details in this regard.

After the FSBL hands off control to the bare-metal application, the standalone BSP code in boot. S is executed by the core domain selected during the creation

of the AP. For instance, choosing CPU1 as the AP domain leaves CPU0 in a low-power state. The second-stage boot sets up numerous modules of the APU (e.g., SCU, cache, MMU, and processor registers) to initialize the primary core. This procedure is outlined in the Zynq-7000 SoC TMR [4, p. 104] and in the ARM Cortex-A Series Programmer's Guide [6, ch. 13, p. 2]. From now on, APs will have CPU0 as a domain, unless specified otherwise.

The primary core's setup sequence in **boot**. S contains sections of code that ease the configuration of the APU in SMP, even though, by default, the standalone BSP can exploit only one core. In particular, the primary core is set in SMP mode and the MMU can be configured to coherently access memory with multiple symmetric cores by defining the preprocessor directive SHAREABLE\_DDR.

To achieve coherency at the core level, the developed SMP system must properly set the DDR memory's attributes in the MMU, since it is the only external memory accessed by both cores. As hinted in Subsection 2.3.2, this can be done by tagging as "shareable" the page table entries that perform address translation for the DDR. Failing to do so forces to manage coherency with explicit software operations [6, ch. 10, pp. 4-5]. Enabling the S bit of an MMU descriptor is a necessary step [4, ch. 3, p. 74], but it is not enough to achieve memory coherency, as the cores need to actively participate in the process by informing the SCU. For this reason, they have to set the SMP bit in the Auxiliary Control Register [9, ch. 4, pp. 27-29]. Listings B.3 and B.4 show the relevant code in boot.S, while Section B.3 further analyzes the DDR configuration inside the MMU.

At the end of the bare-metal boot, the execution proceeds with the C startup code in xil-crt0.s, where the application is finally started. The FreeRTOS documentation on CA9-based systems [15] suggests calling the main() function in supervisor mode, but the processor mode is set to system mode.

The boot process provided by the standalone BSP concludes with CPU1 stuck in WFE and, by default, the code to manage the wake-up mechanism of the secondary core is not implemented in bare metal. Using the FreeRTOS BSP, the result would be the same, since, as described in Subsection 2.5.2, the library is based on the standalone BSP. It is possible to unlock a domain that configures the CA9 APU in SMP mode without user intervention, but it is required to select the Linux OS during the creation of a PP.

The only way to wake up CPU1 with the adopted AP structure is to follow the steps mentioned earlier in this subsection. However, since the FreeRTOS scheduler must be started inside xPortStartScheduler() on all the cores that run the application [13, p. 2], it does not make sense to wake up CPU1 in any of the BSP files. This consideration aligns with a key decision that will influence many design choices: to modify and exploit the BSP code as little as possible to minimize the effort required to execute the port on future BSP releases. The new port file smpPortZynq7000.S implements the process to boot CPU1 along with

other functions required to operate in SMP.

#### 3.3.2 Secondary Core Setup in FreeRTOS

The FreeRTOS kernel provides vTaskStartScheduler() to start the scheduler after configuring the application inside the main() function. This API initializes several kernel objects (e.g., idle task) and ultimately calls xPortStartScheduler(), which performs architecture-specific steps before restoring the context of the first task. However, as explained in Section 2.1, when SMP is adopted, the symmetry that characterizes this MP paradigm does not inherently apply to the entire kernel structure. Therefore, in FreeRTOS, the setup of the primary core differs from that of the secondary cores, as observed in Subsection 3.4.1.

Nevertheless, in SMP mode, xPortStartScheduler() must start the scheduler on all the available cores. In the Zynq-7000 SoC SMP port, the wake-up process of the secondary core begins with a call to vPortLaunchSecondaryCore, whose code is reported in Listing 3.1 for clarity. In this function, CPU0 stores the entry point of CPU1 at address 0xFFFFFF0 and then manually cleans the dirty line of its L1 data cache to prevent the presence of stale data in CPU1's L1 data cache. As a result, since DDR addresses are marked with a write-back cache policy and CPU1 did not take part in hardware coherency yet, the memory views of the two cores differ. The cache line is cleaned by explicitly writing to the CP15 because the DCCMVAC pseudo-instruction [8, ch. B3, p. 1491] is not supported by the assembler. Moreover, as stated in Subsection 2.3.1, PoC and PoU are equivalent for the CA9, since the cache maintenance operations end in L2 cache or, in case it was inactive, in main memory. The instruction is guarded with two DSBs; the first makes sure that all prior operations are complete before proceeding, while the second forces the line clean to conclude before the execution of SEV. No other barrier is required in this case, as DMB only constraints the ordering of memory instructions without guaranteeing their completion [23], and ISB does not affect the visibility of data [8, ch. A3, pp. 148-152].

In the second part of vPortLaunchSecondaryCore, CPU0 continuously polls the shared variable ulSecondaryCoreAwakeConst to determine when it can stop issuing SEV instructions. The variable is updated once CPU1 has been completely configured, so the primary core does not start executing the application before the secondary core is ready. Alternative designs for the code are possible, as explained in Section B.4.

The entry point of CPU1 is the address associated with the symbol \_boot\_core1. This label is defined in smpPortZynq7000.S and marks the beginning of a section of code that replicates the boot of the primary core in boot.S, following the ARM's guidelines [24, ch. 5, pp. 10-11]. Naturally, the initialization procedures for the SCU and L2 cache are skipped, as they are shared resources. Another substantial

```

1 .type vPortLaunchSecondaryCore, %function

vPortLaunchSecondaryCore:

/* Write the start address of CPU1 */

mov r0, #CORE1_START_VECTOR

ldr r1, =_boot_core1

str r1, [r0]

dsb

mcr p15, 0, r0, c7, c10, 1 /* Clean address to PoC */

10

/* Wake up CPU1 and wait for it to be ready */

11

ldr r2, ulSecondaryCoreAwakeConst

pollForCore:

sev

ldr r1, [r2]

15

cmp r1, #0

16

beq pollForCore

17

18

bx lr

19

```

Listing 3.1: CPU1 wake-up process

distinction can be observed in the definition of the labels that identify the processor mode stacks, as they are different from the ones used in boot.S. This is necessary because both cores operate concurrently, so the stack would be corrupted if they happened to be in the same processor mode simultaneously. For this reason, the linker script lscript.ld, which is automatically generated during the creation of an AP, has been modified to allocate .stack1. This additional memory section hosts the processor modes' stack of CPU1. In the entire project, this is the only scenario in which the user is obliged to substitute or modify a BSP file.

After the initial boot phase, CPU1 must be properly set up to work under FreeRTOS. Therefore, before signaling to CPU0 that the core is ready to execute the application, CPU1 configures the GIC interface by jumping to vPortInit-CoreInterruptController(). This function is defined in portZynq7000.c and, other than initializing the scugic driver instance of CPU1, links prvYieldCore-Handler() to the SGI with number portSGI\_ID. As explained in Subsection 2.2.2, SGIs allow the cores connected to the GIC to communicate with each other. In the FreeRTOS SMP port, this feature is exploited by defining the macro port-YIELD\_CORE(x) as the scugic function XScuGic\_SoftwareIntr(); its objective is to notify another core that it needs to yield the task it is currently executing. The operation is performed inside prvYieldCoreHandler() by setting the variable ulPortYieldRequired[xCoreID] for the running core. Since this is a frequent operation, one could consider integrating it in the FreeRTOS\_IRQ\_Handler, as discussed in Section B.5.

Although the end of the code section that starts with \_boot\_core1 features several calls to C functions, no further action is needed to comply with the AAPCS, since the stack pointer is always 8-byte aligned.

After the setup steps described in these sections, the scheduler can run on the secondary core, so CPU1 can finally execute its first task.

### 3.4 Symmetric Multiprocessing Port Upgrade

The previous section discussed the bring-up procedure of the Zynq-7000 SoC's secondary core without investigating the improvements introduced in the FreeRTOS port layer that enable this process. These changes are both numerous and diverse, so only the most important ones are presented in the following subsections.

#### 3.4.1 Primary Core Setup in FreeRTOS

Subsection 3.3.2 mentions that CPU0 and CPU1 have different roles during the startup of FreeRTOS. Still, it does not anticipate that the primary core executes additional setup phases both in the hardware-dependent and independent layers.

Nevertheless, the current discussion solely focuses on the port code, specifically on the operations performed inside xPortStartScheduler().

In SMP, although the scheduler is started on all the available cores, a single core must handle the system tick. This ensures the correct management of xTickCount, the variable that tracks the number of OS ticks since the start of the scheduler, and the FreeRTOS APIs that rely on it (e.g., vTaskDelay()). However, unlike in the single-core port, the installation of the SysTick interrupt in FreeRTOS\_SetupTick-Interrupt() is not followed by restoring the first task's context. Indeed, CPU0 enables the SGI that implements the inter-core communication. Nevertheless, differently from CPU1, it calls vPortSetupYieldRequestHandler(), a function defined in portZynq7000.c, since it already initialized its CPU interface before configuring the system tick. After the previous step, the primary core checks if the spinlock API presented in Subsection 2.5.2 is disabled and, eventually, sets it up. At this point, as thoroughly described in Subsection 3.3.2, CPU0 jumps to vPortLaunchSecondaryCore() and starts executing its first task, once CPU1 finishes its boot sequence.

#### 3.4.2 Multi-core Interrupt Management

The hardware-dependent layer handles the interaction between cores and GIC through the scugic driver, whose functioning is mostly described in Subsection 2.5.2. Nevertheless, its usage has not been flawless, since, even though multiple cores are supported, the driver's design is not SMP-oriented.

Subsection 2.2.2 states that the registers of the CPU interfaces are banked; hence, in principle, a single XScuGic instance could be used to set up both cores. However, upon its first call, XScuGic\_CfgInitialize() configures the passed XScuGic instance so that it cannot be used to initialize more CPU interfaces. While it would technically be possible to overcome this limitation by manually modifying the IsReady field, this approach has been discarded to avoid potential issues in future library versions. Instead, the two-element array xInterruptControllers[-configNUMBER\_OF\_CORES] has been used to allocate a separate XScuGic variable per core.