## POLITECNICO DI TORINO

${\bf Master's\ Degree} \\ {\bf in\ Nanotechnologies\ For\ ICTs} \\$

#### Master's Degree Thesis

# Process Simulation and Compact Modelling for a Vertical Junctionless Nanowire Transistor

Supervisors

prof. Gianluca Piccinini

prof. Fabrizio Mo

Candidate Alessio Grillone

Academic Year 2024-2025

$Ai\ miei\ genitori\\ \ \, \textit{†}\ A\ mio\ nonno\ Antonio$

## Summary

MOSFET have dominated the electronic industry for many years. However, the continuous dimen-sional scaling required to improve the integrated circuit's performances and reduce the fabrication costs, gives rise to a series of issues. The most relevant one is the so-called Drain-Induced-Barrier- Lowering (DIBL), which consists in a loss of the gate's control over the channel and results in an increase of the power consumption per chip. To overcome these issues, novel device architectures have been conceived. The most promising one is the Gate-All-Around (GAA) configuration. Moreover, as the gate length reaches the nanometer range, it becomes really challenging to precisely control the dopant atoms distribution and so to construct abrupt pn junctions. To this aim, the Junctionless Transistor (JNT) is an innovative device which does not rely on junctions and so greatly simplifies the fabrication process. In this work, the fabrication process of a Vertical JNT p type transistor is simulated by means of Synopsys Sentaurus Process, and the results of the electrical simulations per- formed with Synopsys Sentaurus Device are compared to the experimental data of measurements on devices fabricated at the Laboratory for Analysis and Architecture of Systems affiliated to the French National Centre for Scientific Research (LAAS-CNRS). The TCAD simulations have been tuned to obtain the experimental characteristic curves, by providing also some interesting physical insights on the functioning of the studied device. In the second part of the project, an analytical compact model of JNT, inherited from literature, has been implemented in MATLAB. The MATLAB compact model has been thus fitted and validated against the experimental data, considering three different nanowire diameters. In all the cases, an error lower than 1010Finally, the compact model parameters have been tuned based on the Sentaurus results in order to fit the simulated transcharacteristic, thus obtaining a further validation of the compact model. This physical model could be integrated into a SPICE simulator so as to simulate complex digital circuits based on the technology under study and, based on the simulation results, optimize again the device parameters, thus speeding up the production.

## Acknowledgements

Finalmente sono giunto al termine di questo lungo percorso, che è stato complicato, ma anche molto appagante e stimolante. Vorrei quindi ringraziare tutte le persone che mi sono state vicine e mi hanno supportato(e sopportato). Al primo posto metterei i miei genitori, che mi hanno sempre lodato e incoraggiato dandomi la forza di andare avanti con tenacia, come anche nonna Anna,nonno Vincenzo,nonna Ninetta, zia Marianna e zio Simone. Poi vorrei ringraziare tutti gli amici che mi sono vicini da una vita:Deni, Edo, Silvi e soprattutto Cri che ha avuto tanta pazienza in questi anni. Un grazie anche a tutti gli amici del Sabato Sera, che ho conosciuto da poco, ma che hanno avuto un impatto importantissimo. Infine, ultimi ma non ultimi, un grazie particolare al professor Gianluca Piccinini, per avermi dato l'opportunità di approfondire questo argomento particolarmente interessante e a Fabrizio Mo, per la sua gentilezza, disponibilità e i suoi consigli preziosi.

## Contents

| Li | st of            | Tables                           | 8  |

|----|------------------|----------------------------------|----|

| Li | $\mathbf{st}$ of | Figures                          | 9  |

| Ι  | Fi               | rst Part                         | 13 |

| 1  | Inti             | roduction                        | 15 |

|    | 1.1              | Scaling issues                   | 15 |

|    | 1.2              | Junctionless fet                 | 17 |

|    | 1.3              | Thesis Objectives                | 18 |

|    | 1.4              | Thesis structure                 | 18 |

| 2  | Dev              | vice under study                 | 21 |

|    | 2.1              | Introduction                     | 21 |

|    | 2.2              | Fabrication procedure            | 22 |

| 3  | Me               | thodology                        | 25 |

|    | 3.1              | DTCO loop                        | 25 |

|    | 3.2              | TCAD softwares overview          | 26 |

|    | 3.3              | FEM method overview              | 27 |

| 4  | Phy              | vsical models                    | 31 |

|    | 4.1              | Density gradient model           | 31 |

|    | 4.2              | Interface traps                  | 33 |

|    | 4.3              | Mobility models                  | 36 |

|    | 4.4              | Velocity saturation              | 42 |

|    | 4.5              | Shockley-Read-Hall recombination | 43 |

|    | 4.6              | Incomplete ionization            | 43 |

|    | 4.7              | Band-To-Band-Tunneling           | 44 |

| 5  | Pro              | cess simulations                 | 47 |

| 6  | Electrical simulations 6.1 Subthreshold slope fitting | 55 |

|----|-------------------------------------------------------|----|

| I  | I Second Part                                         | 65 |

| 7  | Compact modelling                                     | 67 |

|    | 7.1 Introduction                                      | 67 |

|    | 7.2 Model derivation                                  | 68 |

| 8  | Compact model validation                              | 75 |

|    | 8.1 Subthreshold slope investigation                  | 75 |

|    | 8.2 Fitting of the experimental data                  | 77 |

| 9  | Matching the compact model with the Sentaurus results | 85 |

|    | 9.1 Mobility and Doping extraction                    | 85 |

|    | 9.2 Fitting of the Sentaurus results                  | 88 |

| 10 | 0 Conclusions and Future perspectives                 | 93 |

| 1  | 1 Appendix                                            | 95 |

|    | 11.1 Sentaurus scripts                                | 95 |

|    | 11.1.1 SProcess                                       | 95 |

|    | 11.1.2 SDevice                                        | 96 |

|    | MATI AR scripts                                       | 00 |

## List of Tables

| 4.1  | IAL mobility model parameters for phonon scattering in Si                               | 37 |

|------|-----------------------------------------------------------------------------------------|----|

| 4.2  | Masetti model parameters                                                                | 39 |

| 4.3  | IAL mobility model parameters for surface roughness scattering                          | 41 |

| 4.4  | Canali model parameters                                                                 | 42 |

| 6.1  | Acceptor type device parameters                                                         | 53 |

| 6.2  | Simulation results for different acceptor type interface traps densities                | 54 |

| 6.3  | Simulation results for $q\Phi = 4.4 \text{ eV} \dots \dots \dots \dots \dots$           | 56 |

| 6.4  | Parameters for the device with donor type interface traps                               | 57 |

| 6.5  | Simulation results for donor type interface traps                                       | 57 |

| 6.6  | Parameters for the device with donor type interface traps,<br>after gate $q\phi$ tuning | 58 |

| 6.7  | Simulation results for donor type interface traps,<br>after gate $q\phi$ tuning         | 58 |

| 6.8  | Parameters for the device with donor type interface traps,<br>after PtSi $q\phi$ tuning | 59 |

| 6.9  | Simulation results for donor type interface traps,<br>after PtSi $q\phi$ tuning         | 59 |

| 6.10 | Final device parameters                                                                 | 60 |

| 6.11 | Simulation results of the final device                                                  | 60 |

| 9.1  | Parameters of the simulation to be fitted                                               | 86 |

## List of Figures

| 4.1  | .Comparison between classical and quantum carriers distribution adapted          |    |

|------|----------------------------------------------------------------------------------|----|

|      | L J                                                                              | 32 |

| 4.2  | •                                                                                | 38 |

| 4.3  | *                                                                                | 38 |

| 4.4  | Mean free path of the holes for a correlation length of the surface roughness    |    |

|      |                                                                                  | 40 |

| 4.5  | Mean free path of the electrons for a correlation length of the surface rough-   |    |

|      |                                                                                  | 40 |

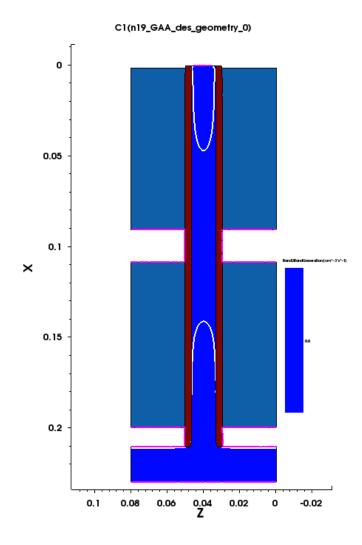

| 5.1  | 1                                                                                | 49 |

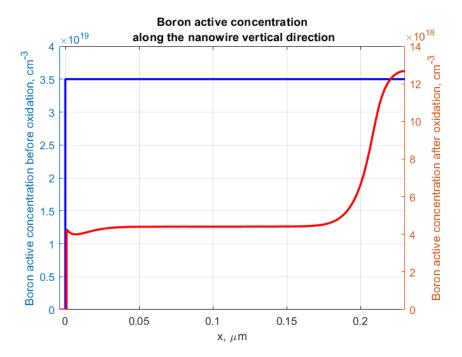

| 5.3  | .Boron active concentrations along the nanowire height direction                 | 51 |

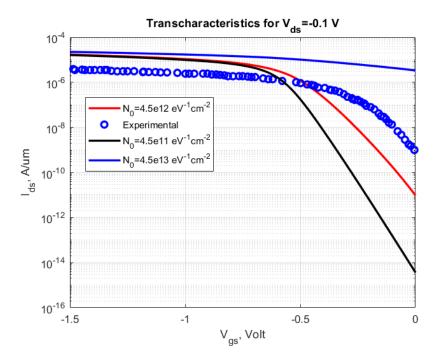

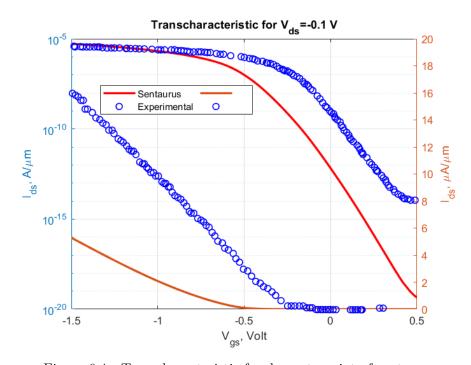

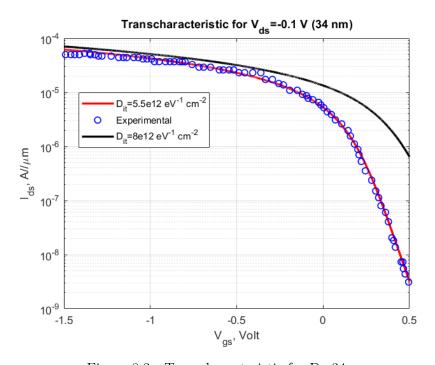

| 6.1  | .Transcharacteristics for acceptor type interface traps                          | 54 |

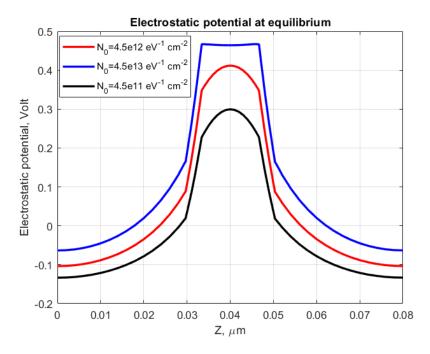

| 6.2  | . Electrostatic potential at equilibrium for different traps concentrations      | 55 |

| 6.3  | Transcharacteristic for $q\Phi=4.4~{\rm eV}$                                     | 56 |

| 6.4  | .Transcharacteristic for donor type interface traps                              | 57 |

| 6.5  | Transcharacteristic for donor type interface traps,<br>after gate $q\phi$ tuning | 58 |

| 6.6  | Transcharacteristic for donor type interface traps,<br>after PtSi $q\phi$ tuning | 59 |

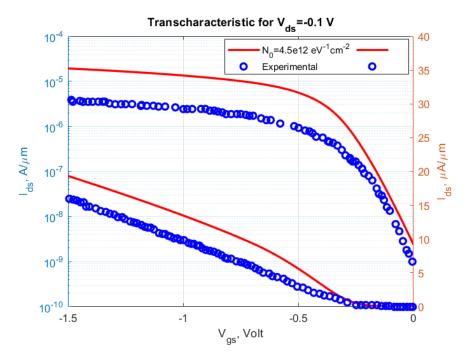

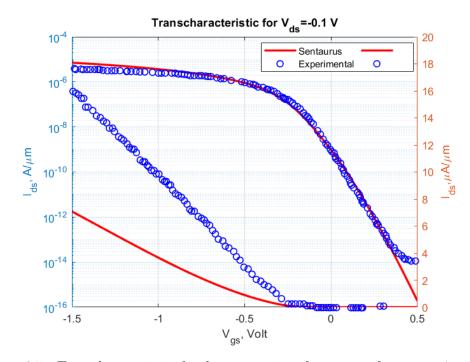

| 6.7  | .Final transcharacteristic                                                       | 60 |

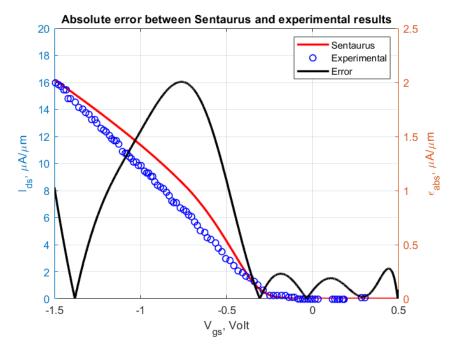

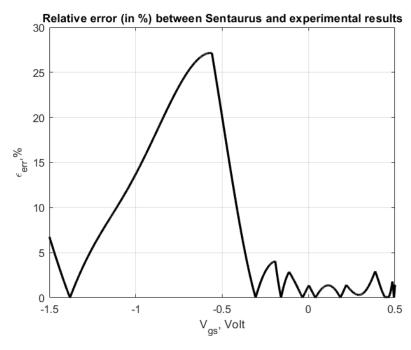

| 6.8  | .Absolute error between Sentaurus and experimental results                       | 61 |

| 6.9  | .Relative error between Sentaurus and experimental results                       | 61 |

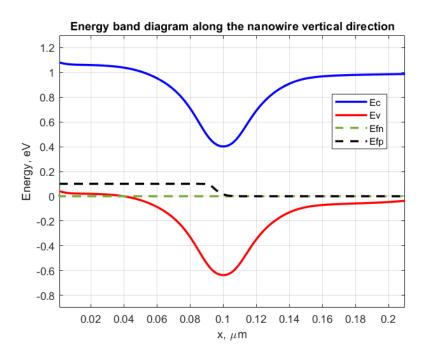

| 6.10 | .Band diagram along the nanowire vertical direction                              | 63 |

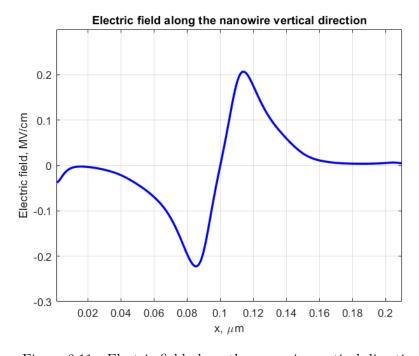

| 6.11 | Electric field along the nanowire vertical direction                             | 63 |

| 6.12 | .BTBT map along the nanowire vertical direction                                  | 64 |

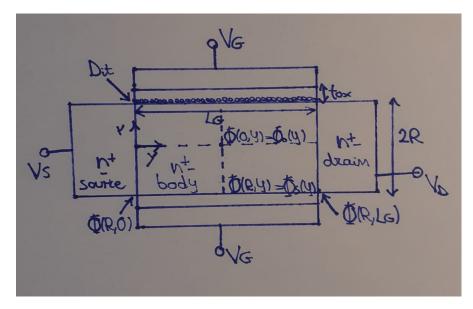

| 7.1  | Schematic diagram for the JNT                                                    | 68 |

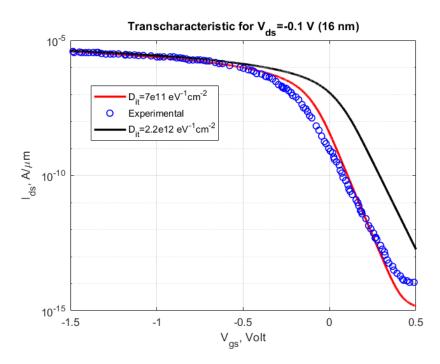

| 8.1  | .Transcharacteristic for D=16 nm                                                 | 75 |

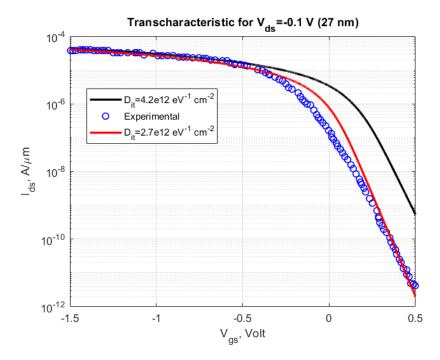

| 8.2  | .Transcharacteristic for D=27 nm                                                 | 76 |

| 8.3  |                                                                                  | 76 |

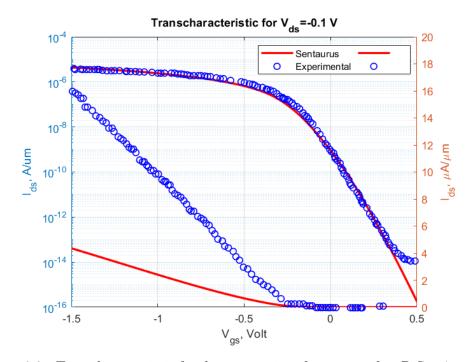

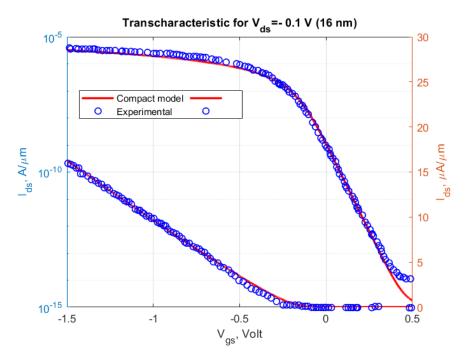

| 8.4  | .Transcharacteristic for D=16 nm with optimized fitting parameters               | 78 |

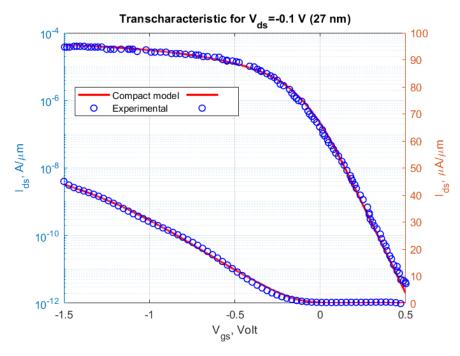

| 8.5  | .Transcharacteristic for D=27 nm with optimized fitting parameters               | 78 |

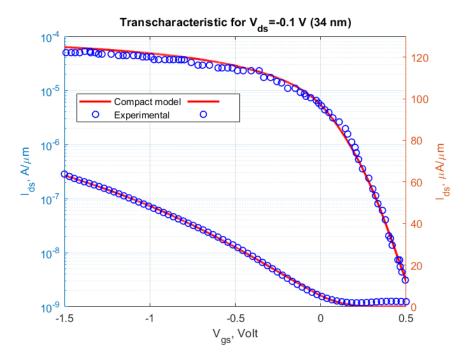

| 8.6  | .Transcharacteristic for D=34 nm with optimized fitting parameters               | 79 |

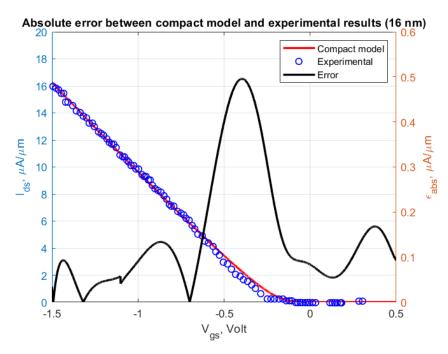

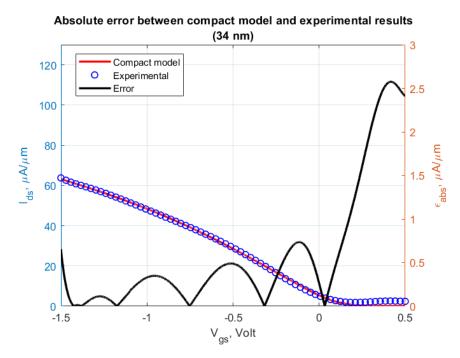

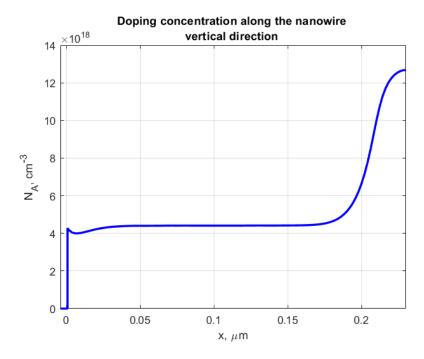

| 8.7  | .Absolute error in between the compact model and the experimental results        |    |

|      |                                                                                  | 80 |

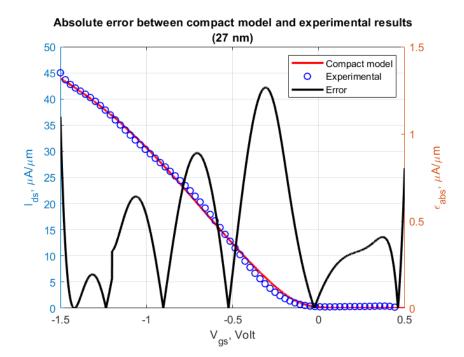

| 8.8  | .Relative error in between the compact model and the experimental results        |    |

|      |                                                                                  | 80 |

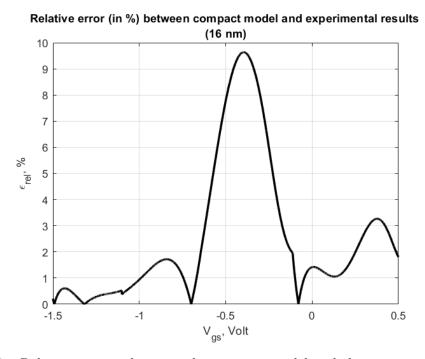

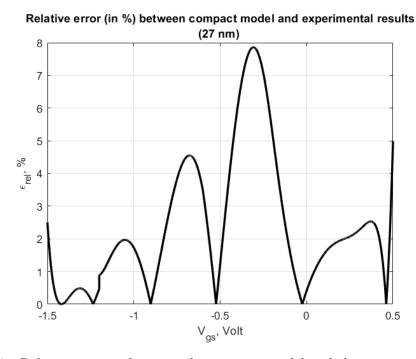

| 8.9  | .Absolute error in between the compact model and the experimental results  |

|------|----------------------------------------------------------------------------|

|      | for D=27 nm                                                                |

| 8.10 | .Relative error in between the compact model and the experimental results  |

|      | for D=27 nm                                                                |

| 8.11 | . Absolute error in between the compact model and the experimental results |

|      | for D=34 nm                                                                |

| 8.12 | .Relative error in between the compact model and the experimental results  |

|      | for D=34 nm                                                                |

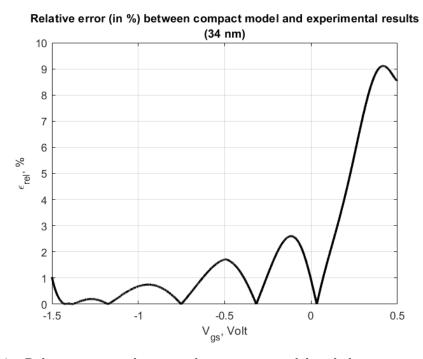

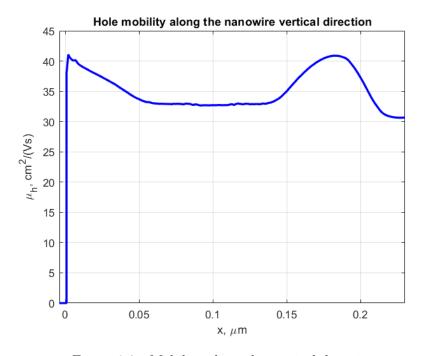

| 9.1  | Mobility and doping distributions along the vertical direction             |

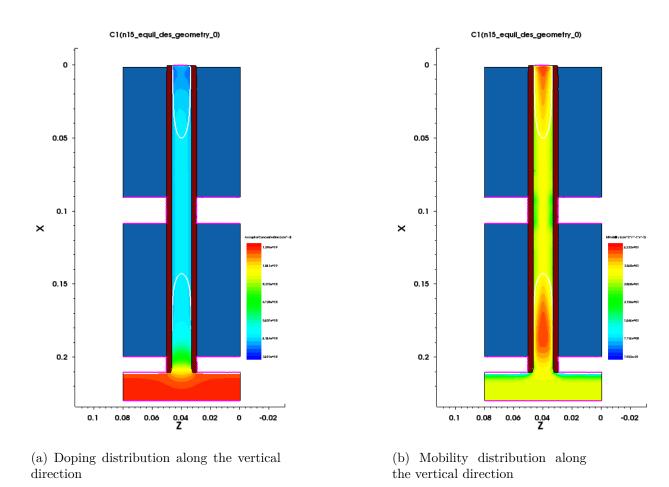

| 9.2  | .Doping concentration along the vertical direction                         |

| 9.3  | . Mobility along the vertical direction                                    |

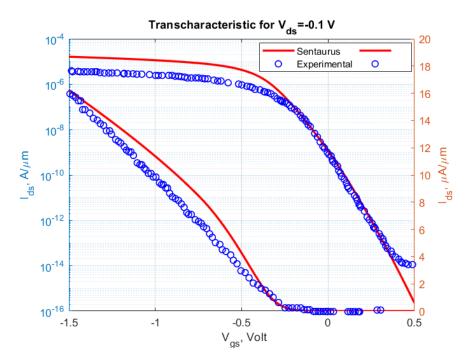

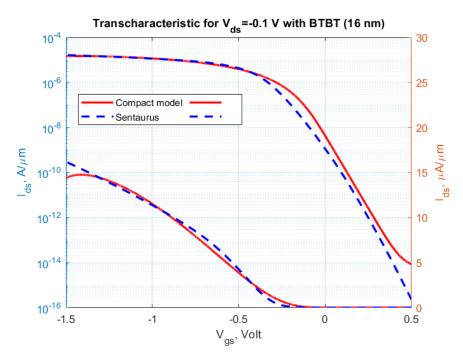

| 9.4  | .Matching of the Sentaurus results with the compact model, with BTBT       |

|      | included in the compact model                                              |

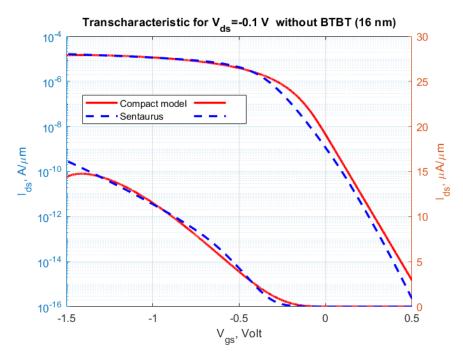

| 9.5  | .Matching of the Sentaurus results with the compact model, without BTBT    |

|      | included in the compact model                                              |

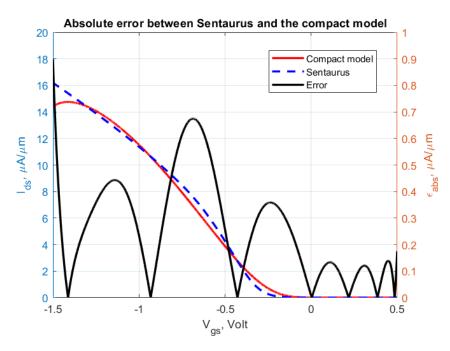

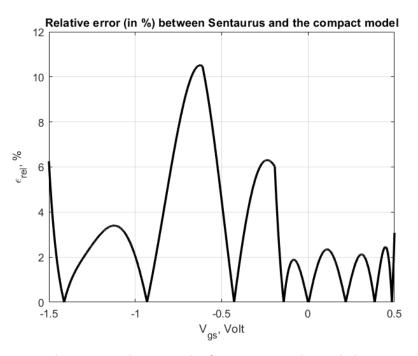

| 9.6  | .Absolute error between the Sentaurus results and the compact model        |

| 9.7  | .Relative error between the Sentaurus results and the compact model        |

If you cannot understand my argument, and declare it's Greek to me you are quoting Shakespeare.

[B. LEVIN, Quoting Shakespeare]

# Part I First Part

## Chapter 1

## Introduction

#### 1.1 Scaling issues

Nowadays MOSFET are exploited everywhere and are essential for a lot of applications such us portable electronics and telecommunications Rizvi and Jaiswal [2016]. The progress achieved over the last twenty years in the electronic industry has been possible due to the continuous dimensional scaling. This because by reducing the dimensions it's possible to ameliorate the device's performances, given that complex integrated circuits require high clock frequencies, that can be reached by decreasing the switching time, which is "the time needed by a transistor in order to make the gate of an identical transistor switching from the ground to the supply voltage" Rizvi and Jaiswal [2016].

$$\tau = \frac{Q}{I} = \frac{CV}{I} \tag{1.1}$$

Where C is the gate capacitance, V is the supply voltage and I is the transistor on state current. Therefore the best way to reduce the switching time  $\tau$  is to reduce the gate length so as to reduce the gate capacitance. The continuous dimensional scaling is also related to the fabrication costs, given that by reducing the transistor's dimensions it's possible to integrate more chips per wafer Rizvi and Jaiswal [2016]. This has lead to a huge boost of transistor's density, which was described by Moore in 1965 in the famous Moore's law, which states that "the number of devices on a chip doubles every 18 or 24 months or so as "Rizvi and Jaiswal [2016]. However, when scaling a device, there is the need to establish a sort of rule that has to be followed in order to avoid an abrupt increase of the electric field which may lead to some unwanted effects, such us oxide breakdown, drain currents uncontrolled rising due to impact ionization and electromigration, which consists in the metal wires destroying due to the atom's displacement caused by high energies electrons. To avoid all these drawbacks, a sort of "recipe" for the device scaling has been conceived. It is known as Dennard's scaling or constant-field scaling rule and it imposes three transformations so as to keep the electric field constant from one technological node to the other Dennard et al. [1974]. Firstly, the supply voltage is reduced by a scaling factor k (i.e. $V'_{ds} = \frac{V_{ds}}{k}$ ). Second, the doping is increased by the same scaling factor  $N'_A = kN_A$ . Finally, the gate oxide thickness is scaled, again using the same factor:  $t'_{ox} = \frac{t_{ox}}{k}$ . This scaling strategy has worked fine for many years but, with the further proceeding of the scaling down, it is starting to fail since the reduction of  $t_{ox}$  and the doping increase imply a threshold voltage's reduction, which can not fall below a certain limit ( $\approx 0.4~V$ ) otherwise the off current (also known as leakage current)rises too much causing power dissipation problems. As consequence, in order to allow for a large enough operating window, the supply voltage reduction has slowed down, causing an increase of the electric field. Moreover as the channel length reaches the nanometers range, a series of issues which undergo the name of short channel effects arise. They can be summarized as follow:

- drain induced barrier lowering: as the source-substrate and the drain-substrate depletion depth extensions reach the same order of magnitude of the gate length, the amount of depletion charge under the gate control diminishes Chopra and Subramaniam [2015]. This results in a lowering of the barrier in between source and drain. As a consequence the threshold voltage is reduced; moreover the barrier's height and thus the threshold voltage become affected by the drain voltage Rizvi and Jaiswal [2016]. So the barrier lowers with the drain voltage increase and this will cause an increase of the off state current of the device that on its own will cause a rising of the power dissipation.

- gate oxide tunneling: according to the constant field scaling rule, with the channel length reduction it's also necessary to reduce the gate oxide thickness. This will cause quantum mechanical tunneling that will increase the gate induced likage current.

- random doping fluctuations: by going down with dimensions becomes increasingly challenging to precisely control the dopants atoms positions, thus the effect of randomness of the dopant distribution becomes more and more pronounced.

- mobility degradation: the increase of doping concentration prescribed by the Dennard's scaling rule leads to a rising of the impurity scattering rate, which degrades the device's mobility.

- hot carriers effects: in scaled transistors, since the channel length is very short and the supply voltage can not be scaled down under a certain limit, a strong electric field arises from source to drain which accelerates carriers to very high velocities. Given that these carriers possess very high kinetic energy, they impact against the gate oxide layer, giving rise to oxide trapped charges which lead to parasitic gate currents and mobility degradation.

Therefore the integrated circuits technology is slowing down due to the increasing power dissipation, process variabilities and fabrication costs, thus novel devices able to guarantee high performances by dissipating a low amount of power are required to further proceed with the scaling down Chopra and Subramaniam [2015]. Up to the 22 nm node some change in the CMOS technology has been performed, such us replacing  $SiO_2$  with  $HfO_2$  in the gate dielectric in order to increase the gate oxide thickness without compromising the gate capacitance, or creating source and drain extensions to counteract short channel effects. However, from the 22 nm node these non ideality effects become more and more

pronounced thus new devices architectures such us Finfets or Gate All Around FET(GAA FET) should be considered in order to have a better electrostatic control over the channel and to further proceed with the technological scaling.

#### 1.2 Junctionless fet

Nowadays all the transistors exploited in the commercial electronic industries are junction based devices, which exploit junctions in order to impeed or allow the current flowing. Nevertheless, a transistor, to be defined as such, must not be necessarily based on junctions Colinge et al. [2010]. By definition, "a transistor is just a device which regulates the current flow Rongon [2022]. Infact, as explained in Colinge et al. [2010], the transistor idea was conceived for the first time in 1925, by the Austrian-Hungarian physicist Julius Edgar Lilienfield who promoted a device which consisted in a thin uniformly doped semiconductor film whose conductivity was modulated by a proper control of the voltage applied to a metal electrode deposited on it, with an insulating layer in between. However, the semiconductor technology at the time was still at the beginning, as a consequence the device's operation showed several issues. With the modern technologies the idea of a junctionless transistor was taken again in consideration and in 2010 Jean-Pierre-Colinge presented in Colinge et al. [2010] a device consisting of a uniformly doped Silicon nanowire, lying on a Silicon-On-Insulator(SOI) substrate, with a gate wrapping the channel from three sides. Then, the technology has been further refined up to arrive to a nanowire completely encircled by the gate, thus increasing the electrostatic control over the channel. Apart from the advantages in terms of reduced short channel effects, near ideal Subthreshold Slope(SS) and improved  $I_{on}/I_{off}$  ratio, this device offers a great simplification of the fabrication process, since does not rely on junctions and so does not require ultrafast annealing techniques in order to form abrupt doping profiles. This also allows to improve the electrical properties, since as soon as the channel length reaches the order of nanometers, becomes very difficult to create high quality pn junctions S.Munjal et al. [2021]. The working principle of the device S.Munjal et al. [2021] relies on the modulation of the gate voltage, which induces an electric field perpendicular to the nanowire height. If  $V_{gs}$  is small enough, the complete depletion of the silicon nanowire is achieved and the device is in the off condition. This is possible if the nanowire diameter is thin enough, otherwise is not possible to totally deplete the channel and the device can not be turned off. As the gate voltage reaches the threshold value, a small portion of neutral region appears at the center of the channel and the current starts to flow. When the gate voltage is further increased, the portion of the neutral region increases more and more and when the applied voltage is equal to the flat band one the depletion region totally disappears and the entire channel is neutral, so an high amount of current will flow. If the gate voltage increases again, then the device enters in the accumulation mode and the current slightly rises up, but the junctionless fet is often designed to operate up to the flat band condition since in the accumulation region the majority carriers accumulate at the interface between Si and  $SiO_2$  where there are interface traps which reduce the mobility, as it happens for inversion mode transistors. Moreover, since the nanowire must be thin enough to allow for the complete depletion in the off condition, the device must be highly doped in order to allow for a sufficient amount of current flowing in the on condition Colinge et al. [2010]. This means that impurity scattering dominates over phonon scattering and thus the mobility and the current are less temperature dependent with respect to a standard inversion mode device Colinge et al. [2010].

#### 1.3 Thesis Objectives

The main objectives of this thesis project are basically three. Firstly, simulating the fabrication process a novel device which is currently under study at the Laboratory for Analysis and Architecture of Systems affiliated to the French National Centre for Scientific Research(LAAS-CNRS) and obtain a good matching of the electrical characteristics with the available experimental results. Second, implementing in MATLAB an analytical compact model presented in literature which describes the physics of the device, validating the same against the experimental results. Finally, after extracting some microscopic quantities from the electrical simulations, modifying the compact model in order to obtain a good correspondence with the simulation results.

#### 1.4 Thesis structure

The structure of the project can be summarized as follows:

- in the **first chapter** the scaling issues which arise in the modern devices are described and the operational principle of the Junctionless FET is introduced, focusing on the benefits of this novel type of device with respect to the standard CMOS technologies.

- in the **second chapter** the fabrication procedure of the device which is going to be simulated is described in detail.

- in the **third chapter** the methodology currently adopted for the device optimization by the industries is presented, followed by a description of the simulation tools exploited in this project and by an overview of the Finite-Element-Method(FEM), which is used by the physics based simulator to solve partial differential equations.

- in the **fourth chapter** the physical models taken into account in the electrical simulations of the device are described.

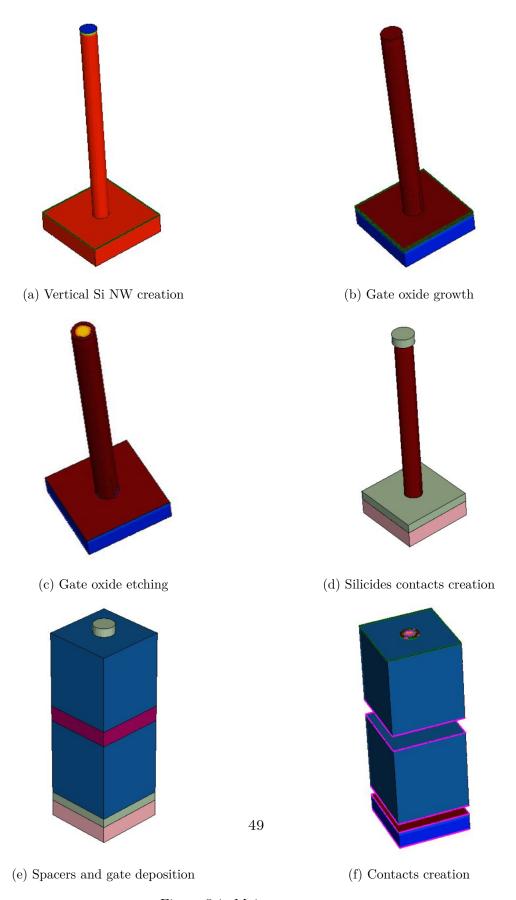

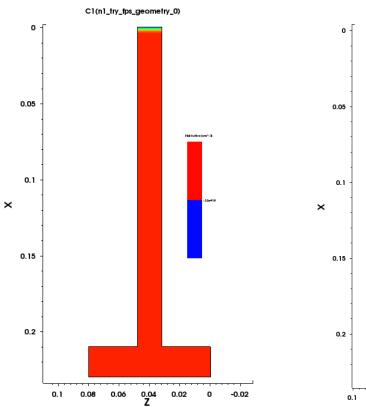

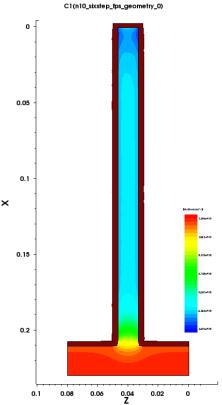

- in the **fifth chapter** the process simulation is illustrated, highlighting the differences with respect to the real process described in chapter 2.

- in the **sixth chapter** the results of the electrical simulations are presented and validated against the experimental results, reporting an analysis of the relative and absolute error.

- in the **seventh chapter** the analytical compact model presented in literature is derived.

- in the **eight chapter** the analytical compact model presented in the previous chapter is validated against the experimental results, considering three different geometries. The absolute and relative errors are reported for each case.

- in the **ninth chapter** the analytical compact model parameters are optimized so as to fit the results obtained from the electrical simulations.

- in the **tenth chapter** conclusions and future perspectives are reported.

## Chapter 2

## Device under study

#### 2.1 Introduction

As explained in the previous chapter, the modern technologies are increasingly suffering from problems related to the scaling. The most relevant one is the subthreshold leakage current, which causes an increase of the power consumption. To overcome this issue, novel CMOS architectures based on multi-gate devices have been developed, with the aim of increasing the electrostatic control over the channel. The design which allows to maximize the electrostatic control over the channel is represented by the GAA architectures. However, the amount of current flowing through a singular device is small due to the narrow nanowire's diameter, so these transistors have to be implemented on nanowires arrays so as to merge the excellent electrostatic control with high on current capability Larrieu and Han [2013], Larrieu et al. [2017]. There are two methods used to produce nanowires arrays Han et al. [2010], Larrieu and Han [2013], Guerfi and Larrieu [2016]. The first one is the so called bottom up approach, which is a chemical deposition technique which allows to sintetize nanowires on a substrate by means of a catalyst. The other one is the top down approach, consisting in the selective etching of a planar substrate. One method could be preferred to the other depending on the application: the bottom up one allows to grow nanowires using virtually any material but suffers from metallic contamination issues due to the the metallic catalyst, while the top down one is highly CMOS compatible and allows for a good control over nanowire's position, diameter and pitch. Moreover with the top down approach it's possible to construct nanowires arrays with an higher density with respect to those obtained by means of the bottom up approach. The nanowires based FET can be fabricated both horizontally and vertically Larrieu and Han [2013], Guerfi and Larrieu [2016]. From the design point of view, vertical integration can allow for a better integration density with respect to the horizontal one. Moreover, the gate length in the vertical configuration is not defined by high resolution lithographic techniques but just by the thickness of the deposited gate material Larrieu and Han [2013], Guerfi and Larrieu [2016], Larrieu et al. [2017]. Despite of these advantages, the vertical integration of nanowires transistors is not as mature as the horizontal one from a technological point of view Guerfi and Larrieu [2016], mainly because of troubles with contacts creation at the bottom of the wires and perfect control of the thickness and smoothness of the spacer layers Larrieu and Han [2013]. Thus the vertical integration architecture is not exploited at commercial level yet.

#### 2.2 Fabrication procedure

The device under study is a vertical gate all around p type junctionless transistor fabricated by the Laboratory for Analysis and Architecture of Systems affiliated to the French National Centre for Scientific Research(LAAS-CNRS). The process can be divided in the following steps:

• vertical nanowire creation: the starting point is a 4-in. Si(100) wafer, with a Boron concentration equal to  $3.5 \times 10^{19}$  atm cm<sup>-3</sup> Guerfi and Larrieu [2016], Kumar et al. [2024]. The vertical silicon nanowires are realized through a top-down approach, by exploiting plasma etching to transfer an hard mask pattern onto the silicon substrate Guerfi and Larrieu [2016]. The hard mask is realized by electron beam lithography through the patterning of an high resolution negative tone resist: Hydrogen SilsesQuioxane (HSQ) Guerfi and Larrieu [2016]. Being an inorganic resist, it is highly resistant to plasma etching and exhibits high mechanical strength Guerfi et al. [2013]. The HSQ resist is identified with the general formula of  $(HSiO_{3/2})n$ and upon e-beam exposure, there is a scission of the Si-H bonds which rearrange into Si-O-Si bonds(siloxane bonds), changing the cage like structure into a network one Guerfi et al. [2013]. Firstly, the HSQ solution is spin-coated on the Si wafer at different angular speeds so as to obtain a resist thickness ranging from 70 nm to 330 nm Han et al. [2010]. Then the sample it's baked at 80 °C for 60 s to let the solvent evaporating Han et al. [2010]. For the exposure step, it is necessary to find a proper design strategy in order to obtain circular resist nanopillars with uniform size and anisotropy Guerfi et al. [2013]. One possibility is using a design pattern based on concentric circles separated by a distance corresponding to the HSQ resolution. Unfortunately, this strategy leads to squared shaped nanostructures with bowed sidewalls and stitching defects. The proper design strategy is the so called star like design, consisting of lines starting and finishing at the center of the pattern. After the e-beam exposure, the resist is developed by manual immersion in 25% Tetramethylammonium Hydroxide(TMAH) at 20 °C for 60 s, dipped in deionized water and blown dry with nitrogen Han et al. [2010]. Then the HSQ nanopillars are transferred into the substrate by means of Reactive Ion Etching(RIE). The process parameters of this step need to be properly tailored so as to obtain anisotropy and avoid micro-trenching and under-etching effects Han et al. [2010]. After several attempts, it was discovered that the best condition is a Capacitive Coupling Plasma (CCP) chamber feeded with Chlorine  $(Cl_2)$ , biased at 80 W at a 2 mTorr pressure. The Chlorine chemistry allows to obtain sidewalls with 94% of anisotropy, whereas a low pressure chamber and an high radio-frequency power source are necessary to mitigate micro-trenching and under-etching effects. The reason behind this is that these process defects are mainly caused by specular reflections of the etching species and charging of the mask layer. At low pressures, the mean free path of the ions is long and the possibility of collisions between them is reduced, thus decreasing the specular reflections. For what concern the source, high power provides high kinetic energy to the bombarding ions which force them in a more vertical profile thus reducing the specular reflections, preventing micro-trenching. Moreover the etching time is fixed at 2 min, since over this short amount of time the charge masking is negligible. The residual resist is then removed by immersion in a diluited Fluorhydric Acid (HF) solution.

- gate oxide creation: then there is a dry oxidation step at 850 °C for 10 min, which has the purpose of reducing the nanowire's diameter and neutralize the defects present at the Si/SiO<sub>2</sub> interface. After the stripping of this sacrificial oxide layer, the gate oxide layer is realized through a wet oxidation at 725 °C for 30 min. Before the implementation of the source and drain contacts, it is necessary to etch the oxide at the top and bottom of the nanowires. This is performed by CCP using fluorine chemistry Guerfi and Larrieu [2016].

- PtSi contacts creation: then follows an anisotropic deposition of a 10 nm Platinum (Pt) layer which is annealed by a Rapid Thermal Annealing (RTA) at 500 °C for 3 min in order to form Platinum-Silicide(PtSi) Guerfi and Larrieu [2016]. The Pt contaminations on the nanowires sidewalls are removed by a selective wet etching in acqua regia solution. Acqua regia slightly oxidizes on the outer surface of the nanowires, but this is beneficial since contributes to passivate the trap states Han et al. [2012].

- source-gate spacer creation: the creation of the source-gate isolation spacer is fulfilled by spin-coating HSQ Larrieu and Han [2013], Larrieu et al. [2017], which is exploited thanks to its excellent filling properties, low viscosity and its low dielectric constant (k=2.7) which makes it compatible with CMOS processes Guerfi and Larrieu [2016]. The HSQ dielectric matrix is then etched to the proper thickness in a diluted HF solution. The HSQ etching step needs to be properly optimized so as to obtain a flat spacer surface and the desired dielectric properties Guerfi et al. [2015]. Infact, the low HSQ dielectric constant, necessary to minimize the parasitic capacitances, is achievable upon transformation of the cage like HSQ structure  $(SiO_xH_y)$ into the network like one  $(SiO_x)$ . To this aim, an annealing step is required so as to stabilize the  $SiO_x$  phase. Unfortunately, even if the annealing temperature is high, not all the  $SiO_xH_y$  phase can be transformed into the  $SiO_x$  one. The coexistence of two phases results in a inhomogeneity of the etching rate, which leads to surface holes and lack of surface smoothness. To avoid this issue, the annealing step is performed after the HSQ layer etching. However, upon the reaction between the  $SiO_xH_y$  phase and the HF present in the etchant solution, hydrogen gas can be released leading to bubble encroachments, which can increase the surface roughness of the spacer. To avoid this drawback, the HF solution is enriched by a cationic surfactant (benzalkonium chloride), whose purpose is to remove the bubbles appearing on the surface during etching.

- gate definition: the metallic gate is formed by anisotropic deposition of a 18 nm Chromium(Cr) layer Kumar et al. [2024]. As mentioned in the introduction, it is

worth to remark that the gate length is just defined by the thickness of the deposited layer and not by the lithography resolution Larrieu and Han [2013], Guerfi and Larrieu [2016], Larrieu et al. [2017], which is a great advantage for the scaling.

- gate-drain spacer creation: the procedure for the creation of the gate-drain spacer is exactly equal to the one for the source-gate spacer, the only difference is the etching rate of the HSQ layer, which is tailored so as to cover the structure up to the drain terminations.

- contacts creation: lastly, two via-holes are created by etching the HSQ layer up to the source PtSi termination and the gate layer. Then the contact pads are created by depositing and etching a 400 nm Aluminum(Al) layer Kumar et al. [2024]. Finally, there is a gas annealing process in a  $N_2/H_2$  atmosphere whose aim is to passivate the defects present at both the Si/SiO<sub>2</sub> interface and at the Pt/PtSi contacts interface Han et al. [2012], Guerfi and Larrieu [2016].

.

## Chapter 3

## Methodology

#### 3.1 DTCO loop

In the past devices optimization and system level studies were conducted independently one with respect to the other, but with the further evolution of the scaling, a strong interaction among process engineers and system designers has become mandatory in order to reduce the costs and speed up the production Asenov et al. [2015], Ma et al. [2024]. This is related to the fact that the novel technological nodes require expensive fabrication techniques(e.g. EUV lithography) and often innovative materials that are still under study, so is not feasible to produce a device without knowing its reliability at circuit level. This cooperation among different groups of experts of the semiconductor industry is known as Design-Technology Co-Optimization(DTCO) and its aim is to optimize a device and its fabrication process in order to fulfil specific requirements at system level in terms of power consumption, performances and area. It can be summarized in three steps O'Connor et al. [2024]:

- TCAD simulation at device level: given that with the current technological nodes dimensions the devices variabilities (such us metal gate's granularity, oxide traps and random doping fluctuations) play an important role, a preliminary optimization of the process at device level is needed and it is obtained by combining experimental data with TCAD simulations. By studying the simulations results, it is possible to figure out which are the variability sources that most affect the device performances and consequently optimize the fabrication process. Moreover, even if will not be part of this work, within this first step one can extract some device's parameters (e.g. capacitances, resistances) that, combined with the compact model extracted in the second step, allow to simulate cells based on the technology under study. This procedure undergoes the name of Parasitic Network Extraction (PEX).

- cells simulations: after optimizing the process at device level, more complicated circuits based on that device(i.e. cells) must be characterized. In principle, it could be possible to perform this task by means of TCAD softwares, but it would be too much computationally intensive. So a compact model suited to be integrated

in SPICE simulators must be formulated so as to conduct fast studies of the cells performances and, based on these results, optimize again the circuit at device level.

• in the last DTCO step, the cells are put together to construct more **complex circuits**(e.g.multipliers,adders) and conduct timing and power analysis.

#### 3.2 TCAD softwares overview

As mentioned in the previous section, a trail-error approach to industrial electronics is no more feasible due to the increasing process costs and complexity and necessity to reduce the products time-to market. As a consequence, industries need to rely on reliable TCAD softwares to be exploited in the DTCO loop in order to test a device before its production. In this project, the following commercial tools by Synopsys will be exploited:

- Sentaurus process: it is a TCAD software used to perform simulations of 2D or 3D semiconductor devices exploited in the field of electronics and photonics Synopsys, Inc. [2017b]. It is able to emulate the basic process steps(i.e. lithography, etching, deposition, oxidation, ion implantation, etc.) but it can not deal with more complex processes such us RIE and with rounded geometrical structures(i.e.spheres, cylinders). To this aim, more advanced tools such us Sentaurus Topography or Sentaurus Structure Editor are needed. It takes as input the so called cmd file which contains instructions related to the process to be simulated and the mesh of the structure, which is important to properly define so as to reduce the computational time of the simulation. It gives as an output the tdr file containing the structure of the device resulting from the simulation, which can be visualized with the Sentaurus Visual interface.

- Sentaurus Structure Editor: it is an editor which allows to modify or create 2D or 3D semiconductor devices by means of geometrical transformations Synopsys, Inc. [2017a]. In this work will be exploited to create the cylindrical nanowire.

- Sentaurus device: it is a physics based simulator which takes as an input the structure and the mesh generated by the Sentaurus Process tool and solves partial differential equations with the aim of extracting some microscopic quantities and the current/voltage characteristics Vallone [2020], Guerrieri and Tibaldi [2022]. As a default, it solves the drift-diffusion problem, namely the Poisson's equation coupled to the continuity equations for electrons and holes:

$$\nabla \cdot (\epsilon \nabla \phi) = -q(p - n + N_D - N_A) \tag{3.1}$$

$$\nabla \cdot \vec{j_n} = q(R_n - G_n) + q \frac{\partial n}{\partial t}$$

(3.2)

$$-\nabla \cdot \vec{j_p} = q(R_p - G_p) + q \frac{\partial p}{\partial t}$$

(3.3)

where  $\epsilon$  is the material's dielectric constant,  $\phi$  is the electrostatic potential, n and p are the electrons and holes concentrations per unit of volume,  $N_D$  and  $N_A$  are the

donors and acceptors concentrations per unit of volume,  $\vec{j_n}$  and  $\vec{j_p}$  are the electrons and holes current densities,  $R_n$  and  $R_p$  are the electrons and holes recombination rates (i.e. the variation of electrons and holes per unit of time owing to recombination mechanisms with the valence and the conduction band respectively),  $G_n$  and  $G_p$  are the generation rates (i.e. the amount of electrons and holes generated per unit of time). These equations work fine for classical devices. However, as will be shown later, as the device enters in the nm regime there is some additional effect that has to be included so as to get an accurate description of the device's electrical behaviour. The Poisson's equation coupled to the electrons and holes continuity equations forms a system of partial differential equations that can not be directly handled by the software. To this aim, the equations are discretized on the spacial domain so as to convert the partial differential equations set in a system of algebraic equations that can be easily managed by the simulator. This procedure undergoes the name of Finite-Element-Method(FEM) and will be addressed in the next section. Similarly, the voltage domain is discretized by associating to it a variable t which is ramped from 0 to 1 Synopsys, Inc. [2015]. For each time step, the corresponding voltage is computed as:

$$V(t) = V_0 + t(V_1 - V_0) (3.4)$$

where  $V_0$  and  $V_1$  are the upper and lower limits of the voltage interval respectively. The variable t is ramped from 0 to 1 and for each time step the corresponding voltage is computed according to (3.4), solving the drift-diffusion model so as to extract the current/voltage characteristics that are saved in a **plt** file, visualized by the Inspect tool.

#### 3.3 FEM method overview

As previously said, a computer can not cope with differential equations, so there is the need to convert them into a system of algebraic equations that can be easily addressed by the softwares. To this aim, the most used technique is the so-called Finite-Element-Method (FEM). The basics of this technique are now explained, taking as a reference Tibaldi et al. [2022]. As a starting point, it is useful to consider the Poisson's equation at equilibrium, since its solution is used as an initial guess to solve the drift-diffusion problem under applied bias conditions. Moreover, for the sake of simplicity, the one dimensional case is considered:

$$-\frac{d}{dz}\left[\epsilon(z)\frac{d\phi}{dz}\right] = \rho(z) \tag{3.5}$$

where  $\rho(z)$  is the semiconductor charge density. This equation exhibits two problems:

- it is differential

- it is non linear, due to the relation between charge and potential.

The first problem is overcomed by performing a discretization of the domain by choosing a mesh and writing the unknown of the problem (i.e. $\phi(z)$ ) as a linear combination of basis functions associated to each mesh node:

$$\phi(z) = \sum_{j=1}^{nn} c_j N_j(z)$$

(3.6)

where nn is the number of nodes of the discretization,  $c_j$  are coefficients and  $N_j(z)$  are the basis functions that have to be properly chosen. To this purpose, one common choice are the so-called Lagrange's polynomials, which are piece-wise functions and are basically triangles whose supports are limited to the mesh elements adiacents to the corresponding node at which the function is associated. Thus the problem is reduced to the determination of the unknown coefficients  $c_j$  which, thanks to the fact that the Lagrange's polynomials are interpolating functions (i.e.  $N_j(z_j) = 1$ ), coincide with the potential value associated to the j-th mesh node. Similarly the charge density  $\rho(z)$  is written as:

$$\rho(z) = \sum_{j=1}^{nn} \rho_j N_j(z) \tag{3.7}$$

By substituting (3.6) and (3.7) back into (3.5), after some calculation, a matrix problem is obtained:

$$[E]\{\phi\} = [M]\{\rho\}$$

(3.8)

where [E] and [M] are known matrices and  $\{\phi\}$  and  $\{\rho\}$  are vectors containing the potential and the charge values associated to each mesh node. The problem has been simplified with respect to the initial one, since the differential equation has been converted into a set of algebraic equations. However, due to the relation between charge and potential, the problem is not linear, so can not be directly handled by the software. To overcome this issue, the generalized Newton's method is exploited. It basically consists in approximating the root of a non-linear function f(x) with the root of its First order Taylor's expansion around a certain guess  $x_0$ :

$$x_1 = x_0 - \frac{f(x_0)}{f'(x_0)} \tag{3.9}$$

Then  $x_1$  is used as a guess for the next iteration and so on. To generalize, the solution at the (k+1)-th iteration reads as:

$$x_{k+1} = x_k + \Delta x_{k+1} \tag{3.10}$$

where  $\Delta x_{k+1} = -\frac{f(x_k)}{f'(x_k)}$  is the difference between the result of the (k+1)-th iteration and the k-th one. The procedure is repeated until  $\Delta x_{k+1}$  is smaller than a certain threshold. When dealing with a matrix problem, the method is applied for each equation composing the system so as to obtain a linearized system of algebraic equations. For the Poisson's

case, the final result of this linearization procedure is given by the following matrix equation:

which in compact form can be written as:

$$[\mathbf{j}] \{\Delta \phi\} = \{r\} \tag{3.12}$$

where  $[\mathbf{j}]$  is the Jacobian matrix,  $\{\Delta\phi\}$  is a vector containing the difference between the potential of the current iteration and the previous one, evaluated for each mesh node.  $\{r\} = [E]\{\phi\} - [M]\{\rho\}$  is the residual vector, which is different from zero due to the non-self-consistency of the problem. This linearized system is assembled for each iteration of the generalized Newton's loop until a certain convergence criteria is satisfied, which could be requiring that the residual vector  $\{r\}$  does not exceed a certain threshold.

## Chapter 4

## Physical models

#### 4.1 Density gradient model

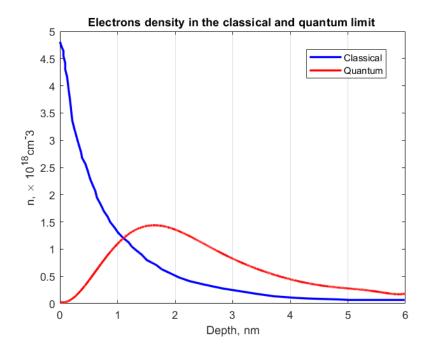

As a default, Sentaurus Device exploits the drift-diffusion model to perform the electrical simulations Synopsys, Inc. [2015] but, as the device enters in the nanometers regime, the quantum effects start to become relevant and this approach fails, leading to a wrong prediction of the device's performances. This is due to the fact that for small dimensions carriers undergo the so called "quantum smearing effect", which is a sort of redistribution of the carriers along the transverse direction of the device. This effect does not occur in classical devices since, for standard dimensions, carriers are governed by the Boltzmann's statistic which predicts an exponential decay of the carriers concentration moving away from the  $Si/SiO_2$  interface. However, in the quantum limit, the particles must obey to the Heisenberg's principle, so can not be confined at the interface because this would imply a uge energy imparted to them. Thus, in order to minimize their energy, instead of being all in proximity of the semiconductor's oxide interface, they tend to distribute in a more uniform way, with the maximum of the distribution displaced with respect to the interface, as shown in Fig. (4.1). This effect is reflected in a lower on-state current, since carriers flow in a region which is not affected by the maximum possible field. Moreover, at such small dimensions, quantization of the energy levels occurs. These quantized levels are characterized by higher energies with respect to the classical ones, thus becomes increasingly difficult for carriers to possess an energy high enough to populate the levels which participate to the conduction. So in order to have a faithful prediction of the device's performances, quantum effects have to be included in the device simulator Lyumkis et al. [2002]. To this aim, the standard choices are the Poisson-Schrödinger loop or the Non-Equilibrium-Green-Functions (NEGF) approach. These models are physically accurate but are very computationally intensive. Moreover, even if they provide an excellent description of quantum mechanics, they still have to be ameliorated under certain aspects Ancona et al. [2009]: for example they describe the scattering events by means of a simple relaxation time, they suffer from a poor knowledge of real devices and materials so fail to predict some effects (such us scattering events which occur deep in the band, the degree of strain relaxation or the exact impurity profile). Additionally, they can not describe

Figure 4.1: .Comparison between classical and quantum carriers distribution adapted from Guerrieri [2022]

devices in which the quantum effects are relevant only in a small portion of the device. To overcome all these drawbacks and find a balance between accuracy and computational cost, an alternative approach to treat the quantum effects has to be found. The most used one in the so called Density Gradient model(DG), which is an extension of the standard drift-diffusion approach to make it suited for quantum devices. It consists in modifying the Poisson's equation by adding an extra term to the carriers densities Han et al. [2013], Synopsys, Inc. [2015]:

$$\Lambda_n = -\frac{\gamma \hbar^2}{12m_n} \left\{ \nabla^2 lnn + \frac{1}{2} (\nabla lnn)^2 \right\} = -\frac{\gamma \hbar^2}{6m_n} \frac{\nabla^2 \sqrt{n}}{\sqrt{n}}$$

$$(4.1)$$

$$\Lambda_p = -\frac{\gamma \hbar^2}{12m_p} \left\{ \nabla^2 lnp + \frac{1}{2} (\nabla lnp)^2 \right\} = -\frac{\gamma \hbar^2}{6m_p} \frac{\nabla^2 \sqrt{p}}{\sqrt{p}}$$

(4.2)

$$n = N_C F_{\frac{1}{2}} \left( \frac{Ec - E_{F,n} - \Lambda_n}{K_b T} \right) \tag{4.3}$$

$$p = N_V F_{\frac{1}{2}} \left( \frac{E_{F,p} - E_V - \Lambda_p}{K_b T} \right) \tag{4.4}$$

where n and p are the electrons and holes densities respectively,  $\gamma$  is a fitting factor,  $\hbar$  is the reduced Plank's constant(1.054 × 10<sup>-34</sup>Js),  $m_{n,p}$  are the electrons and holes

effective masses,  $N_c$  is the effective density of states of the conduction band,  $N_V$  is the effective density of states of the valence band,  $F_{\frac{1}{2}}$  is the Fermi integral,  $E_C$  and  $E_V$  are the conduction and valence band edges respectively,  $E_{fn}$  and  $E_{fp}$  are the electrons and holes quasi Fermi levels. The quantum corrections  $\Lambda_n$  and  $\Lambda_p$  represent an apparent band edge shift which leads to a quantum mechanical modification of the density of states so as to take into account of the quantum smearing effect Lyumkis et al. [2002]. Eq.(4.3) and (4.4) are substituted in the Poisson's equation, leading to:

$$\nabla(\epsilon \nabla \phi) = -q \left( N_C F_{\frac{1}{2}} \left( \frac{Ec - E_{F,n} - \Lambda_n}{K_b T} \right) - N_V F_{\frac{1}{2}} \left( \frac{E_{F,p} - E_V - \Lambda_p}{K_b T} \right) + N_D^+ - N_A^- \right)$$

(4.5)

This modified Poisson's equation, solved self-consistently with the electrons and holes continuity equations, gives a result which is pretty much coherent with the one obtained with the Poisson-Schrödinger method, but with a much lower computational cost.

#### 4.2 Interface traps

With the continuous scaling down, the fabrication process variabilities are becoming more and more important and must be included in the SDevice simulator in order to have a correct prediction of the device's electrical characteristics. One of these variability issues is the presence of interface traps at the  $Si/SiO_2$  interface, which can lead to a degradation of the device's performances (i.e. threshold voltage shift, mobility degradation, leakage currents increase and SS increase). There are mainly four types of interface traps:

- process induced traps: some process steps, especially oxidation, induce some damage in the device's characteristics. The most relevant problem which arises from the oxidation step is the presence of dangling bonds, which are silicon atoms at the the interface with unpaired electrons. To overcome this issue, a passivation step in a  $H_2$  atmosphere is performed at the end of the process so as to saturate the dangling bonds formed at the interface. However, the  $Si H_2$  bond is very unstable and, as will be shown later, under annealing and irradiation can easily dissociate giving rise to other type of interface defects Zhang et al. [2024].

- irradiation induced traps: irradiation is a common source of damage in electronic devices. It derives from different sources (i.e.x-rays, heavy ions, electron beams, neutrons etc.) which are exploited in the lithographic and characterizations steps Zhang et al. [2024]. Moreover, as the device leaves the factory, it can be further subjected to the damage coming from other sources such us radioisotopes and cosmic rays Zhang et al. [2024]. There are two effects which can take place in a device depending on the radiation dose Zhang et al. [2024]: the Enhanced Low Dose Rate Sensitivity (ELDRS) and the Total Ionization Dose Effect (TID). The former is responsible for the creation of the so called  $E'_{\gamma}$  centers, the latter of the Pb centers and oxygen vacancies.  $E'_{\gamma}$  and Pb centers are formed in four steps Song et al. [2022]: firstly, electrons and holes pairs are generated in the  $SiO_2$  layer due to the ionizing irradiation. Second, holes travel via hopping through the oxygen vacancies ( $V_{o\gamma}$ ) up to arrive in proximity of

the  $Si/SiO_2$  interface, generating  $E'_{\gamma}$  centers, which are basically positively charged oxigen vacancies:

$$V_{o\gamma} + h^+ \to E'_{\gamma} \tag{4.6}$$

Third, thanks to its positive charge, the  $E'_{\gamma}$  center dissociate a nearby  $H_2$  molecule by breaking the H-H bond. The result of this process is an H-passivated oxygen vacancy  $(V_O H)$  and the release of a proton $(H^+)$ :

$$E_{\gamma}' + H_2 \longleftrightarrow V_O H + H^+ \tag{4.7}$$

Last, the generated proton  $H^+$  de-passivates a surface dangling bond by destroying a Pb-H bond, thus creating a Pb center and releasing a proton  $(H^+)$  which reacts with the previous one forming an  $H_2$  molecule.

$$H^+ + PbH \to H_2 + Pb \tag{4.8}$$

Another source of interface defects comes from the oxygen vacancies. They are created under the action of high energy irradiated particles (i.e. TID effect), which break the Si-O bond leaving a Si dangling bond (which on its own increases the interface traps density) and an oxygen vacancy. This kind of trap increases the leakage current through the gate, since the oxygen atom acts as a barrier preventing the carriers tunneling but, as the vacancy is created, the barrier diminishes thus facilitating the leakage current mechanism Zhang et al. [2024].

• stress induced traps: another source of traps comes from the mechanical stress which arises at the  $Si/SiO_2$  interface, for instance due to the oxidation step. Infact, differently with respect to the concave nanostructures where the oxidation phenomena is limited by the hydrostatic pressure increase which prevents the oxidant diffusivity thus impeding the further supply of oxygen molecules at the interface, in the case of convex nanostructures the factor which limits the oxidation rate is the arising of a radial compressive stress component at the interface, defined as Krzeminski et al. [2012]:

$$\sigma_r(r) = \frac{1}{2}\sigma_c \left[ \left( ln \frac{R^2}{b^2} \right)^2 - \left( ln \frac{R^2}{r^2} \right)^2 \right] \tag{4.9}$$

where  $\sigma_c$  is the critical stress threshold at which the plasticity flow appears ( $\approx 1 \text{GPa}$ ), R is a reduced parameter,  $b=a+t_{ox}$  where a is the nanostructure radius and  $t_{ox}$  is the grown oxide thickness, r is the radius of curvature of the nanowire. This radial stress component alters the bonds angles and lengths at the Si surface thus contributing to increase the interface's traps density Zhang et al. [2024].

• hot carriers induced traps: as mentioned in chapter 1, with the continuous downsizing, the electric field inside the device is becoming more and more strong. As a consequence carriers can gain enough kinetic energy to overcome the gate oxide potential barrier, giving rise to oxide trapped charges or interface charges, which are formed when an high energy carrier breaks a Si-H bond, leaving the surface with a dangling bond which acts as a surface trap Chen [2014].

The interface traps can behave as donor or acceptor states basing on their energy position inside the energy gap Rassekh et al. [2019]. If the trap level is below the mid-gap position, it acts as a donor state which can be empty or not depending on whether its level is below or above the Fermi level. Oppositely, the acceptor states are in the upper part of the energy gap and host an electron if are below the Fermi level. Donor(acceptor) states carry a positive(negative) charge when are empty(occupied) and are neutral if occupied(empty). Moreover, the acceptor and donor states have a different impact on the device's performances depending on the doping type Han et al. [2012]. For n-type nanowires devices, the acceptor states present at the interface decrease the majority carriers concentration in the conduction band thus causing a radial depletion of the wire. The same effect is obtained for a p-type device in presence of donor states which increase the electrons concentration in the valence band, thus reducing the holes population. Due to this this traps induced depletion effect, the electronic radius  $r_{elec}$  will be smaller than the physical radius  $r_{phys}$  Han et al. [2012]:

$$r_{elec} = r_{phys} \sqrt{1 - \frac{2N_D}{r_{phys} N_A}} \tag{4.10}$$

thus the cross section available for the carriers flowing will be decreased, causing a degradation of the device current. For the smallest nanowires diameters, the entire device's volume can be fully depleted due to the presence of interface traps, thus blocking at all the current flow Han et al. [2012]. So, when dealing with very small diameters devices, there is the need to carefully model the traps contribution since they can have a detrimental effect on the device's characteristics.

In this thesis project, the interface traps Density Of States(DOS) are modelled with a Gaussian distribution Synopsys, Inc. [2015]:

$$D_{it}(E) = N_0 exp\left(-\left|\frac{E - E_0}{E_s}\right|\right) \tag{4.11}$$

where  $N_0$  is the traps concentration in  $eV^{-1} cm^{-2}$ ,  $E_s$  is the distribution standard deviation,  $E_0$  is an energy level from which the level corresponding to the maximum of the distribution  $E_{trap}^0$  can be found as:

$$E_{trap}^{0} = \frac{\left[E_C + E_V + k_b T ln\left(\frac{N_V}{N_C}\right)\right]}{2} + E_0$$

$$(4.12)$$

To obtain the total interface traps density  $Q_{it}$ , the traps density of states  $D_{it}(E)$  has to be multiplied by the Fermi-Dirac occupation probability f(E) and integrated over the energy gap Rassekh et al. [2019]:

$$Q_{it} = -q \int_{E_V}^{E_C} D_{it}(E) f(E) dE$$

(4.13)

$Q_{it}$  is inserted in the right hand side of the quantum corrected Poisson's equation, leading to:

$$\nabla(\epsilon \nabla \phi) = -q \left( N_C F_{\frac{1}{2}} \left( \frac{Ec - E_{F,n} - \Lambda_n}{K_b T} \right) - N_V F_{\frac{1}{2}} \left( \frac{E_{F,p} - E_V - \Lambda_p}{K_b T} \right) + N_D^+ - N_A^- \right) - Q_{it}$$

(4.14)

#### 4.3 Mobility models

Mobility is another important parameter which affects the device's performances. It is composed by different contributions. The ones which are taken into account in this work are:

• phonon scattering dependent mobility: in a crystal there are collective vibrations of atoms around their equilibrium positions. These quantized vibrations are called phonons and, during their oscillating motion, they may interact with electrons or holes thus degrading the mobility.

The model adopted in this project to describe the phonon scattering contribution is the so called Inversion and Accumulation Layer(IAL) mobility model Synopsys, Inc. [2015], which takes into account of both bulk phonons and surface phonons, which affect the mobility at the interface. The former are treated according to this formula:

$$\mu_{ph,3d} = \mu_{max} \left(\frac{T}{300K}\right)^{-\theta} \tag{4.15}$$

where  $\mu_{max}$  is the maximum bulk mobility ( $\mu_{max} \approx 470.5 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  for holes) and  $\theta$  is a parameter, reported in table (4.1). For what concern the contribution due to surface phonons, they are treated as follows:

$$\mu_{ph,2D} = \frac{B}{F_{\perp}} + \frac{C(\alpha_{ph,2D,A}((N_A + N_2/2)/1 \ cm^{-3})^{\lambda_{ph,2D,A}} + \alpha_{ph,2D,D}((N_D + N_2/2)/1 \ cm^{-3})^{\lambda_{ph,2D,D}})^{\lambda_{ph,2D,D}}}{F_{\perp}^{1/3}(T/300 \ K)^k}$$

(4.16)

where  $F_{\perp}$  is the field which acts normally to the  $Si/SiO_2$  interface,  $N_A$  and  $N_D$  are the acceptor and donor concentrations respectively. All the other quantities are parameters which are reported in table (4.1). The two phonon scattering mobilities are then combined together:

$$\mu_{ph} = \left[ \frac{D}{\mu_{ph,2D}} + \frac{1}{\mu_{ph,3D}} \right]^{-1} \tag{4.17}$$

$D = exp(-x/l_{crit})$ , where x is the distance from the interface and  $l_{crit}$  is another parameter reported in table (4.1).

| Parameter           | Electron value      | Hole value        | Unit                             |

|---------------------|---------------------|-------------------|----------------------------------|

| $\theta$            | 2.285               | 2.247             | 1                                |

| В                   | $9.0 \times 10^{5}$ | $9.0 \times 10^5$ | ${ m cms^{-1}}$                  |

| С                   | 4400.0              | 4400.0            | ${\rm cm}^{5/3} {\rm s/V}^{2/3}$ |

| $\alpha_{ph,2D,A}$  | 1.0                 | 1.0               | 1                                |

| $\alpha_{ph,2D,D}$  | 1.0                 | 1.0               | 1                                |

| $\lambda_{ph,2D,A}$ | 1.0                 | 1.0               | 1                                |

| $\lambda_{ph,2D,D}$ | 1.0                 | 1.0               | 1                                |

| $l_{crit}$          | $10^{3}$            | $10^{3}$          | cm                               |

| $N_2$               | 1.0.0               | 1.0               | $\mathrm{cm}^{-3}$               |

| λ                   | 0.057               | 0.057             | 1                                |

| k                   | 1                   | 1                 | 1                                |

Table 4.1: IAL mobility model parameters for phonon scattering in Si

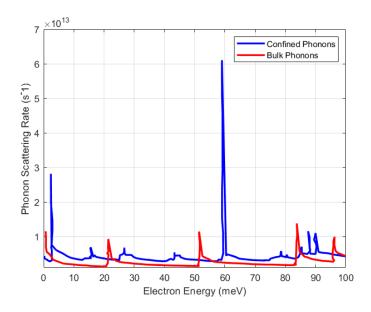

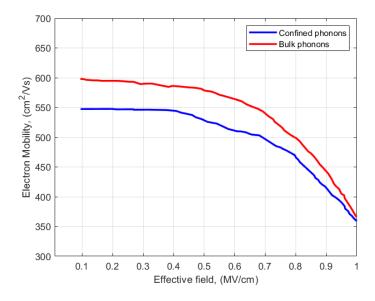

However, it should be remarked that the IAL mobility model does not take into account of an important effect which occurs in nanostructures, described in Ramayya et al. [2008] and Pokatilov et al. [2005]. Infact, as the nanowire width becomes smaller than the phonon mean free path ( $\approx 300$  nm in Si) the phonon spectrum is modified due to a mismatch of the sound velocities and the mass densities between the nanowire and the surrounding material (i.e.  $SiO_2$ ). The phonons characterized by this modified dispersion relation are called confined phonons. The origin of this change can be explained by considering the material's acoustic impedance  $\varsigma = \rho V_s$ , where  $\rho$  is the material's density and  $V_s$  is the material's sound velocity. When a soft material (i.e. low  $\varsigma$ ) surrounds an harder material (i.e. high  $\varsigma$ ) the phonon energy spectrum of the last one is compressed and its group velocity decreases. The opposite effect is obtained when an hard material surrounds a soft one. Given that Si is acoustically harder than  $SiO_2$ , its group velocity decreases and, being the electron-phonon scattering rate inversely proportional to the group velocity, it increases (Fig. 4.2) thus degrading the material mobility (Fig.4.3). To take into account of the phonon confinement effect, the scattering events among carriers and phonons should be treated within a Monte Carlo approach, solved self-consistently with the Poisson's equation. However, it is tricky to integrate the Monte Carlo solver in the Sdevice simulator, so the phonon confinement effect will be negletted.

<sup>&</sup>lt;sup>0</sup>adapted from Synopsys, Inc. [2015]

Figure 4.2: Scattering rates for confined and bulk phonons

Figure 4.3: Mobility for confined and bulk phonons

$<sup>^{0}{\</sup>rm adapted}$  from Ramayya et al. [2008]

• doping dependent mobility: dopant atoms contribute to increase the amount of carriers which contribute to the conduction, but at the same time they act as a source of impurity, perturbing the otherwise perfectly periodic potential in the lattice. This perturbation scatters the carriers during their flowing, thus degrading their mobility. The default model adopted in Sentaurus Device to treat the impurity scattering dependent mobility is the Masetti model Synopsys, Inc. [2015]:

$$\mu_{dop} = \mu_{min1} exp \left( -\frac{P_c}{N_A + N_D} \right) + \frac{\mu_{ph,3D} - \mu_{min,2}}{1 + ((N_A + N_D)/C_r)^{\alpha}} - \frac{\mu_1}{1 + (C_s/(N_A + N_D))^{\beta}}$$

(4.18)

where  $N_A$  and  $N_D$  are the acceptors and donors concentrations respectively and all the other quantities are parameters, which are listed in table (4.2).

| Parameter    | Electron value        | Hole value            | Unit                              |

|--------------|-----------------------|-----------------------|-----------------------------------|

| $\mu_{min1}$ | 52.2                  | 44.9                  | ${ m cm}^2{ m V}^{-1}{ m s}^{-1}$ |

| $\mu_{min2}$ | 52.2                  | 0                     | ${ m cm^2V^{-1}s^{-1}}$           |

| $\mu_1$      | 43.4                  | 29.0                  | $\rm cm^2  V^{-1}  s^{-1}$        |

| $P_c$        | 0                     | $9.23 \times 10^{16}$ | $\mathrm{cm}^{-3}$                |

| $C_r$        | $9.68 \times 10^{16}$ | $2.23 \times 10^{17}$ | $\mathrm{cm}^{-3}$                |

| $C_s$        | $3.43 \times 10^{20}$ | $6.10 \times 10^{20}$ | $\mathrm{cm}^{-3}$                |

| $\alpha$     | 0.680                 | 0.719                 | 1                                 |

| β            | 2.0                   | 2.0                   | 1                                 |

Table 4.2: Masetti model parameters

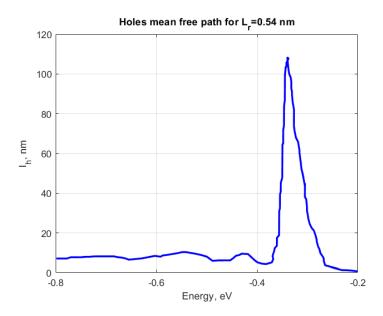

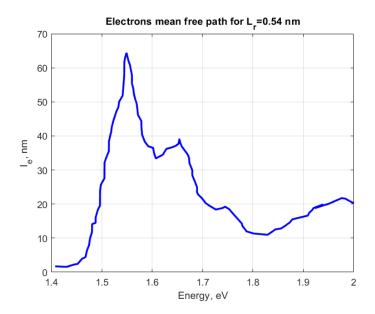

• surface roughness dependent mobility: due to the variability related to technological limitations such lithography resolution and unperfect anisotropic etching, there could be a certain surface roughness on the device sidewalls. This acts as a source of scattering for the carriers flowing near the  $Si/SiO_2$  interface. Moreover, given that the surface roughness implies a statistical fluctuation of the nanowire's radius, the average lateral confinement could increase thus causing a shifting of the electrons and holes sub-bands towards higher and lower energies respectively Lherbier et al. [2008]. As can bee seen from Fig(4.4) and (4.5), this results in a decrease of the electrons and holes mean free path that on its own causes a degradation of the carriers mobilities, given that a lower mean free path corresponds to an higher amount of scattering events.

<sup>&</sup>lt;sup>0</sup>adapted from Synopsys, Inc. [2015]

Figure 4.4: Mean free path of the holes for a correlation length of the surface roughness  $(L_r)$  equal to 0.54 nm

Figure 4.5: Mean free path of the electrons for a correlation length of the surface roughness  $(L_r)$  equal to 0.54 nm

$<sup>^0{\</sup>rm adapted}$  from Lherbier et al. [2008]

So the effect of surface roughness needs to be taken into account when dealing with a device with a large surface to volume ratio, since it affects the carriers mobility both directly through the introduction of another scattering term and indirectly, through the alteration of the electronic structure. In the IAL mobility model Synopsys, Inc. [2015], the mobility contribution due to surface roughness is given by:

$$\mu_{sr} = \frac{(\alpha_{sr,A}((N_A + N_2/2)1 \ cm^{-3})^{\lambda_{sr,A}} + \alpha_{sr,D}((N_D + N_2/2)1 \ cm^{-3})^{\lambda_{sr,D}})^{\lambda_{sr}}}{\left(\frac{(F_{\perp}/1 \ V/cm)^{A*}}{\delta} + \frac{F_{\perp}^3}{\eta}\right)}$$

(4.19)

where:

$$A* = A + \frac{\alpha_{\perp}(n+p)}{((N_A + N_D + N_1)/1 \ cm^{-3})^{\nu}}$$

(4.20)

where n and p are the electrons and holes concentrations respectively. All the other quantities are parameters listed in the following table:

| Parameter        | Electron value        | Hole value            | Unit                                 |

|------------------|-----------------------|-----------------------|--------------------------------------|

| $\alpha_{\perp}$ | 0                     | 0                     | $\mathrm{cm}^{-3}$                   |

| $\alpha_{sr,A}$  | 1.0                   | 1.0                   | 1                                    |

| $\alpha_{sr,D}$  | 1.0                   | 1.0                   | 1                                    |

| $\lambda_{sr,A}$ | 1.0                   | 1.0                   | 1                                    |

| $\lambda_{sr,D}$ | 1.0                   | 1.0                   | 1                                    |

| $\lambda_{sr}$   | 0.057                 | 0.057                 | 1                                    |

| $N_1$            | 1.0                   | 1.0                   | $\mathrm{cm}^{-3}$                   |

| $N_2$            | 1.0                   | 1.0                   | $\mathrm{cm}^{-3}$                   |

| δ                | $3.97 \times 10^{13}$ | $3.97 \times 10^{13}$ | ${\rm cm}^2{\rm V}^{-1}{\rm s}^{-1}$ |

| $\eta$           | $1.0 \times 10^{50}$  | $1.0 \times 10^{50}$  | $V^2/cm/s$                           |

| A                | 2.0                   | 2.0                   | 1                                    |

| $\nu$            | 0                     | 0                     | 1                                    |

Table 4.3: IAL mobility model parameters for surface roughness scattering

• coulomb scattering dependent mobility: a further contribution to the mobility degradation is given by Coulomb scattering, which consists in a deviation of the carriers trajectories due to the electrostatic interaction among them and the ionized impurities present in the bulk and at the surface. Also this effect is modelled by the IAL mobility model. Differently with respect to the other mobility terms, the calculations are quite long and so are omitted. Further details are reported in Synopsys, Inc. [2015].

<sup>&</sup>lt;sup>0</sup>adapted from Synopsys, Inc. [2015]

The different mobility contributions are combined together by the so called **Mathiessen's rule**, which reads as:

$$\frac{1}{\mu} = \frac{1}{\mu_{dop}} + \frac{1}{\mu_{ph}} + \frac{1}{\mu_c} + \frac{D}{\mu_{sr}} \tag{4.21}$$

#### 4.4 Velocity saturation

Another effect which is taken into account in the Sdevice simulator is the saturation of the carriers velocity which occurs at high electric fields. For low fields, the velocity increases linearly to the the applied field through a proportionality coefficient which is the low field mobility (i.e.the mobility resulting from all the contributions described in the previous section):

$$v = \mu_{low} \vec{E} \tag{4.22}$$

As the field reaches high values, the scattering rate increases more and more and at a certain point the relaxation time (i.e.the time which separates two scattering events) becomes so small that the carriers don't manage to increase their momentum in between two scattering events. As a consequence the velocity increases linearly up to a certain maximum, after which remains more or less constant. The default model adopted in Sentaurus to describe the velocity saturation effect is the Canali model Synopsys, Inc. [2015]:

$$\mu = \frac{(\alpha + 1)\mu_{low}}{\alpha + \left[1 + \left(\frac{(\alpha + 1)\mu_{low}\vec{E}}{v_{sat}}\right)^{\beta}\right]^{\frac{1}{\beta}}}$$

(4.23)

where  $\vec{E}$  is the electric field,  $v_{sat}$  is the saturation velocity,  $\alpha$  is a parameter defined in Table (4.4),  $\beta$  is an exponent given by:

$$\beta = \beta_0 \left( \frac{T}{300 \text{ K}} \right)^{\beta_{exp}} \tag{4.24}$$

where T is the lattice temperature,  $\beta_0$  and  $\beta_{exp}$  are parameters defined in the following table:

| Parameter     | Electron value | Hole value | Unit |

|---------------|----------------|------------|------|

| $\alpha$      | 0              | 0          | 1    |

| $\beta_0$     | 1.109          | 1.213      | 1    |

| $\beta_{exp}$ | 0.66           | 0.17       | 1    |

Table 4.4: Canali model parameters

<sup>&</sup>lt;sup>0</sup>adapted from Synopsys, Inc. [2015]

#### 4.5 Shockley-Read-Hall recombination

In a semiconductor there could often be some defects present inside the lattice, which originate a level  $E_T$  within the forbidden energy gap. Depending on the energy position of the level  $E_T$ , the defects can ex-change carriers with one or both the transport bands. In particular, if  $E_T$  is too close with one of the two bands then it will give rise to a simple trapping mechanism, in which electrons or holes are captured by the trapping level and then remain there or are excited back to the bands from which they have been captured. If instead the level  $E_T$  is located more or less in the middle of the energy gap, then the interaction probability with both the transport bands is maximized and so an electron can be captured by the trap level and then be relaxed in the valence band, giving rise to a complete recombination process. This kind of transition is called Shockley-Read-Hall(SRH) recombination and is characterized by the following net recombination rate Synopsys, Inc. [2015]:

$$U_{SRH} = \frac{np - n_i^2}{\tau_{n0}(p + p_1) + \tau_{p0}(n + n_1)}$$

(4.25)

where n and p are the electrons and holes concentrations respectively,  $n_i$  is the intrinsic concentration (i.e.the concentration of the intrinsic semiconductor),  $n_1$  and  $p_1$  are the electrons and holes densities that would be present in the trap level  $E_T$  if the last one would be coincident with the intrinsic Fermi level.  $\tau_{n0}$  and  $\tau_{p0}$  are the electrons and holes SRH lifetimes, defined as:

$$\tau_{n0} = \frac{1}{C_n N_T} \tag{4.26}$$

$$\tau_{p0} = \frac{1}{C_p N_T} \tag{4.27}$$

where  $N_T$  is the defects concentration per unit of volume,  $C_n$  and  $C_p$  are the capture coefficients for electrons and holes respectively, defined in cm<sup>6</sup>/s. They are related to the probability for electrons and holes to be captured by the impurity level  $E_T$ .

### 4.6 Incomplete ionization

The amount of carriers concentration in a doped semiconductor varies as a function of the temperature following three regimes:

- the frozen region: within this limit, the amount of thermal energy is not enough to allow for all the impurities present in the lattice to be ionized, releasing their extra electrons or holes to the conduction band or the valence band respectively. As a consequence, some impurity atoms remain neutral, with their extra-carrier still bounded to them.

- the saturation region: when the lattice temperature is high enough, all the impurities get ionized and over this temperature interval the majority carriers concentration is constant.

• the intrinsic region: if the temperature further increases, the thermal energy becomes so high that starts to promote transitions from the valence band to the conduction band and the amount of majority carriers concentration starts to increase again.

The simulations are performed at 300 K. This temperature should in teory fall in the saturation region. However, in practice, there could be some impurities that are not ionized yet. So, in order to have a correct prediction of the amount of majority carriers which contribute to the conduction, the incomplete ionization effect must be included in the simulations. Sentaurus Device exploits the following model to treat this effect Synopsys, Inc. [2015]:

$$N_D^+ = \frac{N_{D,0}}{1 + g_D \frac{n}{n_1}} \tag{4.28}$$

$$N_A^+ = \frac{N_{A,0}}{1 + g_A \frac{p}{p_1}} \tag{4.29}$$

where  $N_{D,0}$  and  $N_{A,0}$  are the total concentrations of donors and acceptors impurities respectively,  $g_D$  and  $g_A$  are the degeneracy factors for the impurity levels (i.e. the number of states which that level hosts),  $n_1$  and  $p_1$  are given by:

$$n_1 = N_C exp\left(-\frac{\Delta E_D}{K_b T}\right) \tag{4.30}$$

$$p_1 = N_V exp\left(-\frac{\Delta E_A}{K_b T}\right) \tag{4.31}$$