## POLITECNICO DI TORINO

Master's Degree in Electronics Engineering

Master's Degree Thesis

## ANALYSIS AND DESIGN OF A DC-DC QUADRATIC POWER CONVERTER WITH PARTIAL POWER PROCESSING ARCHITECTURE FOR PHOTOVOLTAIC APPLICATIONS

Supervisors

Candidate

Prof. Francesco MUSOLINO Prof. Paolo Stefano CROVETTI Prof. Stefano CERUTTI

Federico Emir RICCI

April 2025

#### Abstract

The increasing adoption of photovoltaic (PV) systems demands innovative DC-DC power conversion solutions. This thesis focuses particularly on micro-grid systems and standalone PV modules, where traditional array connections are unavailable, generating the need for high step-up requirements with wide input voltage variations. The analysis, design, and simulation of a novel DC-DC power converter with a Partial Power Processing (PPP) architecture is presented, designed to operate over a wide input voltage range (15–43 V) and deliver constant output voltage (350 V) across a broad power range (50–680 W), accommodating the variability of PV energy sources.

To overcome efficiency bottlenecks in DC-DC stages for single-phase grid-tied PV systems, this thesis introduces the exploitation of Partial Power Processing through a dual stage quadratic converter with Input-Parallel Output-Series (IPOS) topology, offering high performance by allowing part of the power to flow directly to the load, bypassing the converter stages. This approach achieves high efficiency, reduces component stress, and ensures reliable performance under various conditions. Simulation results reveal a California Energy Commission (CEC) weighted efficiency of 97.2% and a European (EURO) weighted efficiency of 96.8% at the rated power of 680 W.

By providing a comprehensive framework for addressing wide input voltage ranges, high step-up gains, and partial power processing, this work contributes to advancing the state of the art in PV power conversion. The methodologies and findings offer practical insights for improving efficiency in renewable energy systems while addressing challenges posed by Partial Power Processing load balancing.

Building on these innovations, this work also contributes to the DC-DC power converter design workflow by presenting developed methodologies and tools tailored to address the challenges of achieving high step-up gain values with large input voltage variation in circuit topologies highly dependent on load conditions. A detailed efficiency measurement approach, leveraging *LTSpice* and *MATLAB* integration, is introduced alongside innovative techniques for magnetic loss estimation through simulation. These contributions provide valuable insights to assist designers in optimizing converter performance for renewable energy applications.

# Acknowledgements

Prima di tutto, vorrei ringraziare ai miei relatori, Francesco Musolino, Paolo Stefano Crovetti, e Stefano Cerutti, con i quali è stato un vero piacere lavorare sin dal primo giorno, grazie alla loro costante gentilezza e disponibilità.

A mis padres, que desde el día uno me han motivado a seguir cualquier meta que me proponga, siempre acompañándome con su incondicional amor en cada proceso, hito, caída y logro que se diera. Este trabajo es la culminación de una larga etapa de mi vida, y nunca habrá palabras suficientes para expresar lo agradecido que estoy por su permanente compañía y apoyo.

A mi compañera, Giulietta, quien me ha acompañado en toda esta aventura a la distancia, pero siempre cerca, velando en todo momento por mi bienestar con un cariño inmenso.

A mi colega y amigo, Mateo, a quien hoy podría prácticamente llamar un hermano. Incontables son las experiencias, desafíos y aprendizajes que hemos compartido. Ha sido un verdadero placer vivir esta etapa junto a un gran amigo como él.

Finalmente, quisiera agradecer a todas las personas que han sido un apoyo fundamental en este camino, brindándome aliento, consejos y momentos inolvidables. A mis amigos en Torino, por hacerme sentir en casa incluso a miles de kilómetros de ella.

Un agradecimiento especial a Ivo, Celina, Lara y Agustín, quienes, con su compañerismo y amistad, han convertido el camino universitario en mucho más que una simple etapa académica.

# **Table of Contents**

| Li       | List of Tables VI    |                                                              |   |      |

|----------|----------------------|--------------------------------------------------------------|---|------|

| Li       | st of                | Figures                                                      |   | VIII |

| 1        | Intr                 | oduction                                                     |   | 1    |

|          | 1.1                  | Solar energy power systems                                   |   | 1    |

|          |                      | 1.1.1 Current trends of energy production                    |   | 1    |

|          | 1.2                  | Scope of the thesis and organization of work                 | • | 4    |

| <b>2</b> | $\mathbf{PV}$        | Power Conversion Overview                                    |   | 7    |

|          | 2.1                  | PV Sources and their Characteristics                         |   | 7    |

|          |                      | 2.1.1 Modeling of photovoltaic panels                        |   | 7    |

|          |                      | 2.1.2 Selected photovoltaic panel modeling and maximum power |   |      |

|          |                      | points                                                       |   | 10   |

|          |                      | 2.1.3 Strings configurations and micro-inverters             |   | 13   |

|          | 2.2                  | Proposed DC-DC Converter Framework                           |   | 16   |

|          |                      | 2.2.1 Partial Power Processing: advantages and limitations   |   | 16   |

|          |                      | 2.2.2 Proposed power converter                               |   | 22   |

|          |                      | 2.2.3 Equivalent stage loading and decoupling                | • | 24   |

| 3        | $\operatorname{Res}$ | onant Power Converters and the LLC topology                  |   | 29   |

|          | 3.1                  | Resonant Power Converters                                    |   | 29   |

|          |                      | 3.1.1 High-frequency power conversion                        |   | 29   |

|          |                      | 3.1.2 General architecture of resonant power converters      |   | 32   |

|          | 3.2                  | The LLC Topology                                             |   | 33   |

|          |                      | 3.2.1 Architecture structures analysis                       |   | 33   |

|          |                      | 3.2.2 First Harmonic Approximation                           |   | 41   |

|          |                      | 3.2.3 Loading limitations of the LLC topology                |   | 47   |

|          |                      | 3.2.4 Gain profiling: system gain and its effect on loading  |   | 49   |

|          |                      | 3.2.5 Zero Voltage Switching (ZVS) in the LLC topology       |   | 53   |

|          |                      |                                                              |   |      |

| 4            | Pov   | ver converter Design and Optimization                 | 59  |

|--------------|-------|-------------------------------------------------------|-----|

|              | 4.1   | Developed Design Tools                                | 59  |

|              |       | 4.1.1 Gain and load profiling tool                    | 59  |

|              |       | 4.1.2 FHA gain plotter                                | 65  |

|              |       | 4.1.3 Efficiency report tool                          | 66  |

|              | 4.2   | LLC Topology Design and Optimization                  | 69  |

|              |       | 4.2.1 Gain profiling based on architecture properties | 69  |

|              |       | 4.2.2 Design and optimization for maximum efficiency  | 71  |

|              |       | 4.2.3 Output decoupling capacitors sizing             | 81  |

| <b>5</b>     | Ma    | gnetics Modeling                                      | 89  |

|              | 5.1   | Coupled Magnetics modeling                            | 89  |

|              |       | 5.1.1 Magnetic integration in the LLC topology        | 89  |

|              |       | 5.1.2 Transformers design demo                        | 99  |

|              | 5.2   | Transformer losses                                    | 107 |

|              |       | 5.2.1 High frequency effects on copper losses         |     |

|              |       | 5.2.2 Core losses                                     | 113 |

| 6            | Sim   |                                                       | 117 |

|              | 6.1   | Simulation Settings and Data Extraction               |     |

|              |       | 6.1.1 Component sizing aided by simulation            |     |

|              |       | 6.1.2 Simulation configuration                        |     |

|              | 6.2   | Simulation Results                                    |     |

|              |       | 6.2.1 Efficiency results                              | 123 |

| 7            | Cor   | nclusions                                             | 131 |

| $\mathbf{A}$ | MA    | ATLAB code repository                                 | 133 |

|              | A.1   | Solar panel's curves extraction                       | 133 |

|              | A.2   | Gain and load profiling tool                          | 133 |

|              | A.3   | LTSpice output processing                             | 134 |

|              | A.4   | First stage output capacitor charge analysis          | 134 |

| в            | FH    | A transfer function manipulation                      | 135 |

| Bi           | bliog | graphy                                                | 139 |

# List of Tables

| 2.1          | Summary of <i>PSIM</i> Solar Module utility tool parameters 11                                                       |

|--------------|----------------------------------------------------------------------------------------------------------------------|

| $3.1 \\ 3.2$ | Half-bridge characteristics relative to Full-bridge36Full secondary winding versus center-tapped secondary winding38 |

| 4.1          | Summary of LLC topology parameters for first and second stage $77$                                                   |

| 5.1          | Transformer models parameters                                                                                        |

| 5.2          | Primary windings turns restrictions                                                                                  |

| 5.3          | Number of strands of magnetic wire for each winding 105                                                              |

| 5.4          | DC resistance value for each winding                                                                                 |

| 5.5          | Inductance measurements for first stage transformer prototype $106$                                                  |

| 5.6          | Inductance measurements for second stage transformer prototype $~$ . 107 $$                                          |

| 5.7          | Wojda modified $\Delta$ parameter per winding type                                                                   |

| 5.8          | Incremental Steinmetz equation coefficients for selected core at $T=40^{\circ}C114$                                  |

| 6.1          | Maximum voltage and current stress of inverters switches 118                                                         |

| 6.2          | Maximum voltage and current stress of output diodes                                                                  |

| 6.3          | Maximum voltage and current stress of resonating capacitors 120                                                      |

| 6.4          | Maximum voltage and current stress of output capacitors 120                                                          |

| 6.5          | Final simulation parameters values                                                                                   |

| 6.6          | Comparison of Step-up Techniques                                                                                     |

|              |                                                                                                                      |

# List of Figures

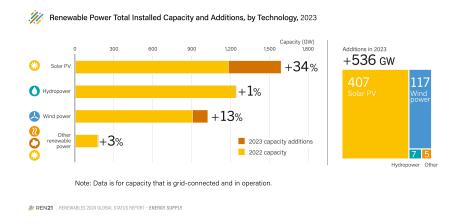

| 1.1  | Solar energy capacity addition from 2022 to 2023                      | 1  |

|------|-----------------------------------------------------------------------|----|

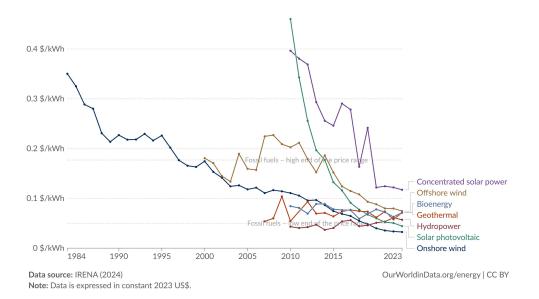

| 1.2  | Different energy sources cost per kWh evolution in time               | 2  |

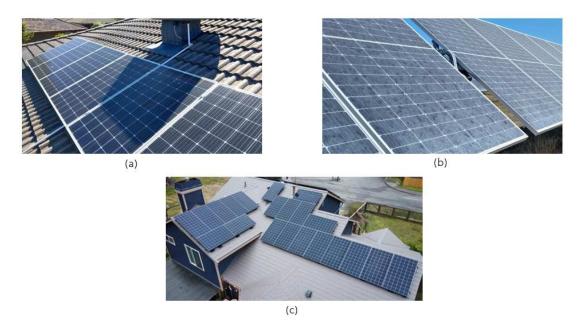

| 1.3  | Different photovoltaic panel energy production factors                | 3  |

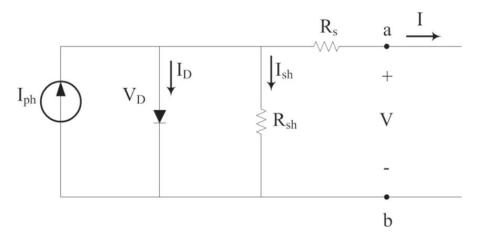

| 2.1  | Single-diode solar cell equivalent circuit                            | 8  |

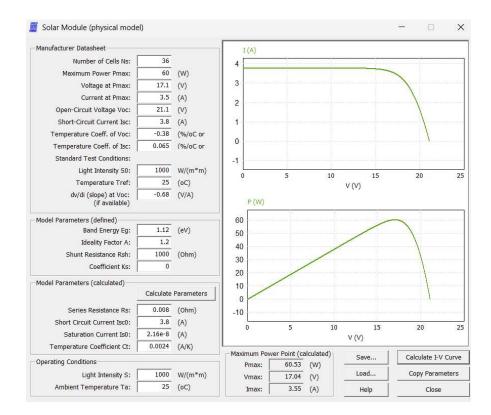

| 2.2  | <i>PSIM</i> Solar Module utility interface                            | 10 |

| 2.3  | I-V characteristic for multiple irradiance values                     | 12 |

| 2.4  | P-V characteristic for multiple irradiance values                     | 12 |

| 2.5  | Different types of photovoltaic panels connection                     | 14 |

| 2.6  | Micro-inverter topologies classification                              | 16 |

| 2.7  | General IPOS configuration overview                                   | 17 |

| 2.8  | General ISOP configuration overview                                   | 17 |

| 2.9  | Pass-through converter IPOS configuration overview                    | 18 |

| 2.10 | Reduced stress visualization of the Pass-through IPOS configuration   | 19 |

| 2.11 | System efficiency boost of the Pass-through IPOS configuration        | 20 |

| 2.12 | Power split and stage gain in the IPOS configuration                  | 21 |

| 2.13 | Short-circuit hazard in IPOS configuration                            | 22 |

| 2.14 | Proposed power converter architecture                                 | 23 |

| 2.15 | Stage equivalent load resistances                                     | 25 |

| 2.16 | First stage equivalent load resistance reduction                      | 26 |

| 2.17 | Second stage equivalent load resistance reduction                     | 27 |

| 3.1  | Hard and soft switching I-V trajectories                              | 31 |

| 3.2  | Typical hard switching waveforms                                      | 31 |

| 3.3  | Typical soft switching waveforms                                      | 31 |

| 3.4  | General architecture of a resonant power converter                    | 32 |

| 3.5  | The LLC network in the general resonant power converter architecture  | 34 |

| 3.6  | Switches technology selection based on power and frequency            | 35 |

| 3.7  | Half and full-bridge topologies                                       | 36 |

| 3.8  | Different architectures for full-wave rectification                   | 37 |

| 3.9  | Voltage and current stress across a step-up quadratic power converter | 38 |

|      |                                                                       |    |

| 3.10 | Resonant power converters in the proposed architecture                               | 39       |  |  |

|------|--------------------------------------------------------------------------------------|----------|--|--|

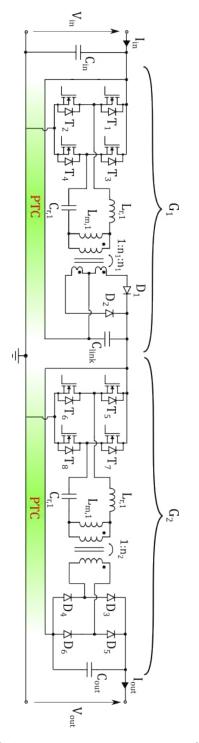

| 3.11 | Schematic of the proposed converter. PTC: Pass-through Converter.                    | 40       |  |  |

| 3.12 | 2 Typical waveforms of the non-linear rectification                                  |          |  |  |

| 3.13 | Impedance reflection in transformers                                                 | 43       |  |  |

| 3.14 | Equivalent linear circuit with FHA                                                   | 44       |  |  |

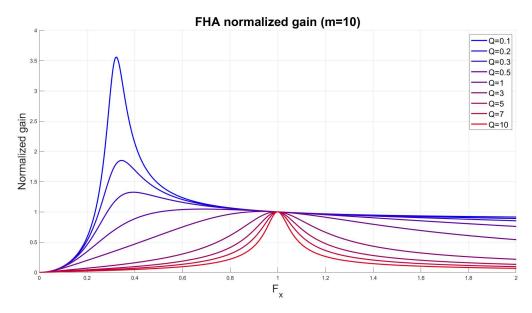

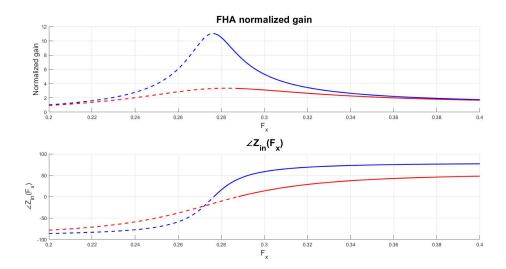

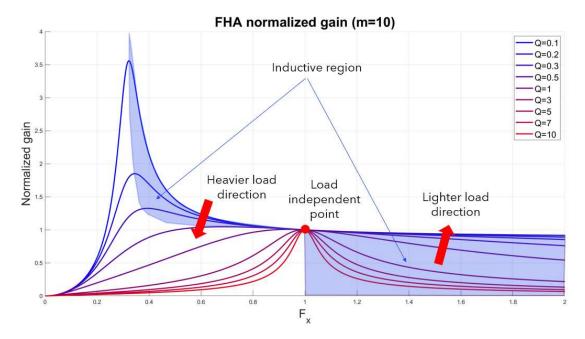

| 3.15 | FHA gain characteristic for different Q values                                       | 46       |  |  |

| 3.16 | 5 FHA gain and its relationship with impedance phase 47                              |          |  |  |

| 3.17 | LLC topology operating regions                                                       | 48       |  |  |

| 3.18 | Full-bridge inverter morphing into Half-bridge inverter                              | 49       |  |  |

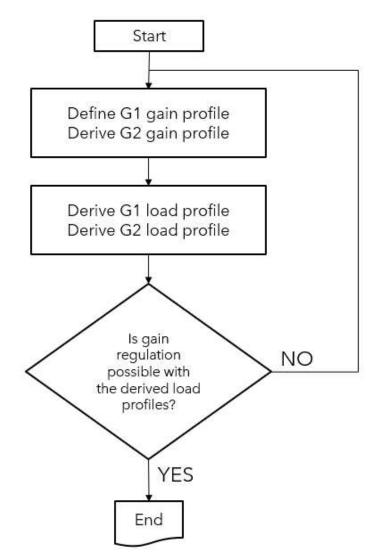

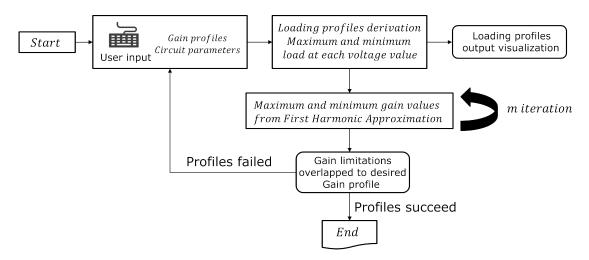

| 3.19 | Gain and load profiling design flow                                                  | 50       |  |  |

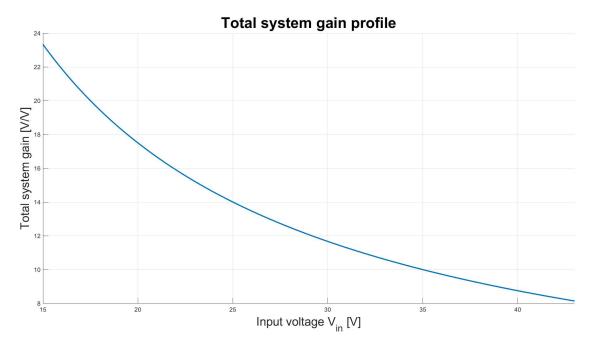

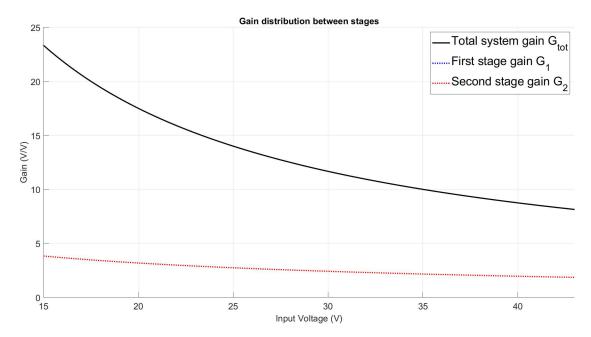

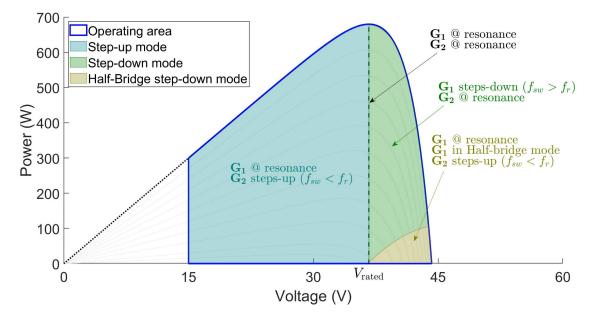

| 3.20 | Total system gain profile                                                            | 51       |  |  |

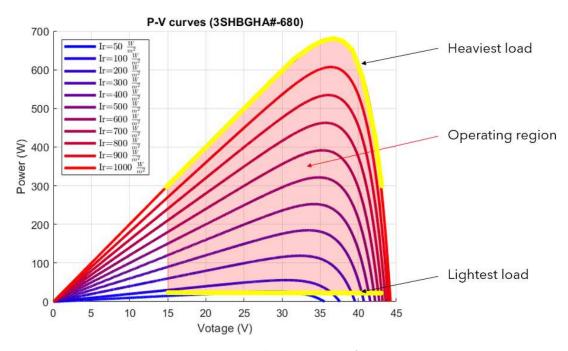

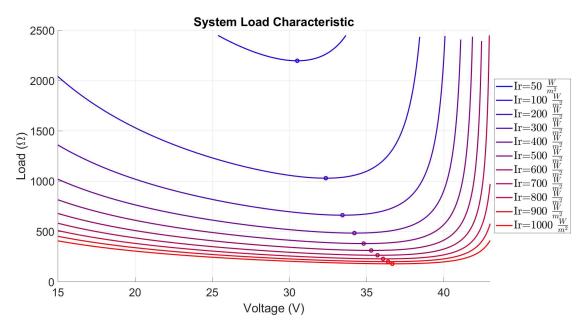

| 3.21 | Working points of the system                                                         | 52       |  |  |

| 3.22 | System load characteristic                                                           | 52       |  |  |

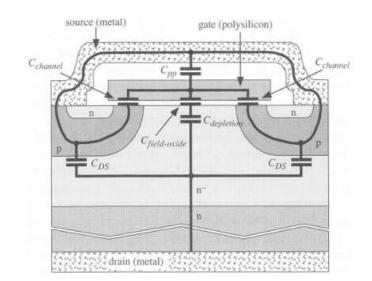

| 3.23 | MOSFET construction and the formed parasitic capacitances                            | 54       |  |  |

| 3.24 | Characterized capacitances of the MOSFET transistor                                  | 54       |  |  |

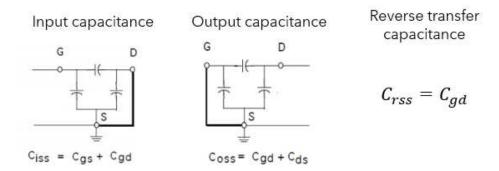

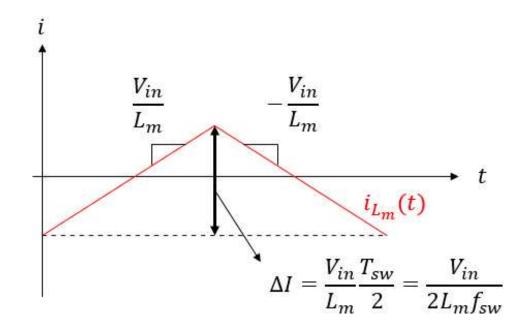

| 3.25 | Curve fit of the manufacturer $C_{oss}$ characteristic $\ldots \ldots \ldots \ldots$ | 55       |  |  |

| 3.26 | Equivalent dynamic capacitance versus static capacitance                             | 56       |  |  |

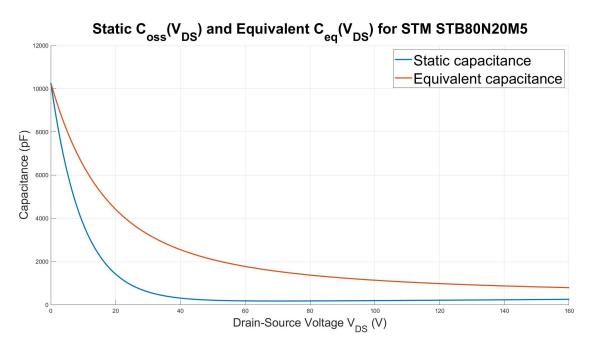

| 3.27 | Current waveform through $L_m$ at resonance $\ldots \ldots \ldots \ldots \ldots$     | 57       |  |  |

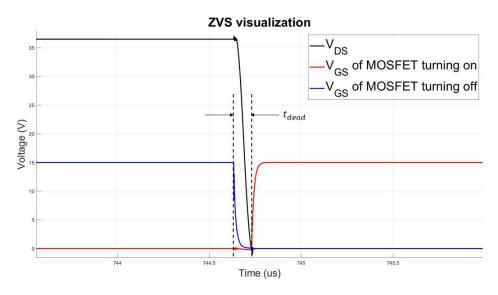

| 3.28 | ZVS visualization                                                                    | 58       |  |  |

| 4 1  | Coin on dilord muchting to all attilization                                          | co       |  |  |

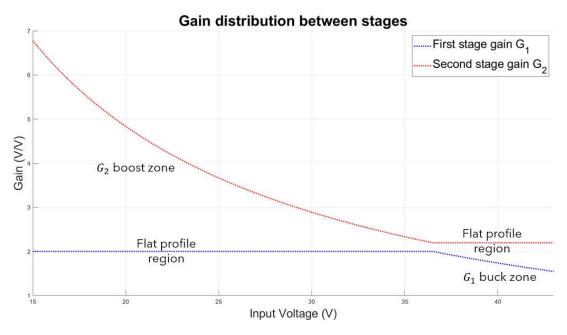

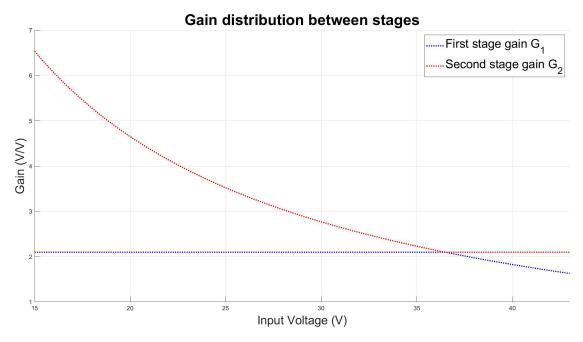

| 4.1  | Gain and load profiling tool utilization                                             | 60<br>61 |  |  |

| 4.2  | System and stages gain profiles (example)                                            | 61       |  |  |

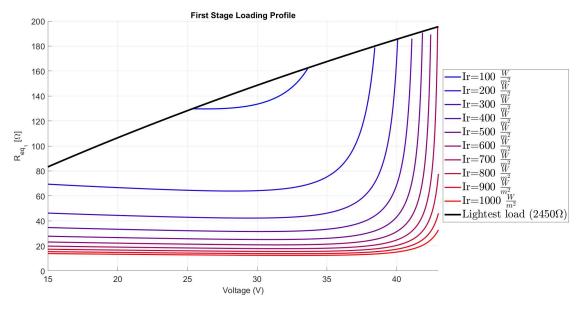

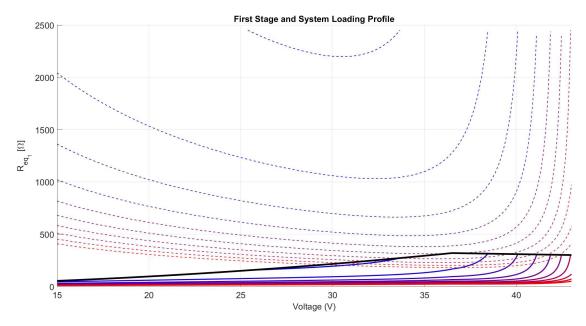

| 4.3  | First stage loading profile (example)                                                | 62       |  |  |

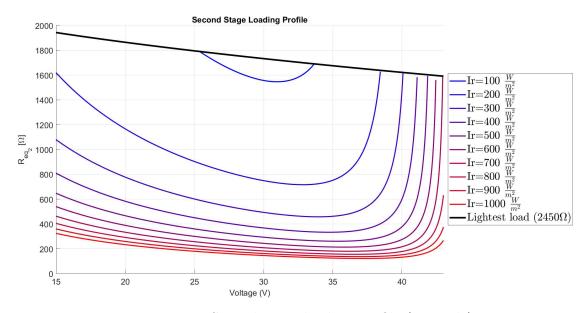

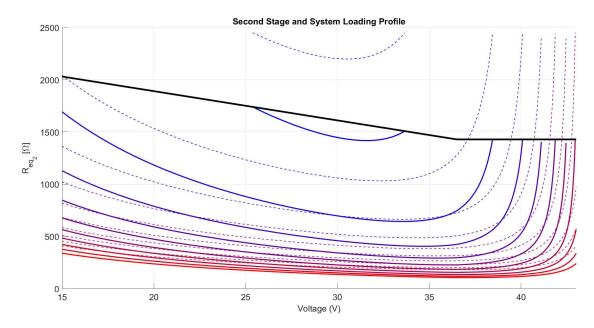

| 4.4  | Second stage loading profile (example)                                               |          |  |  |

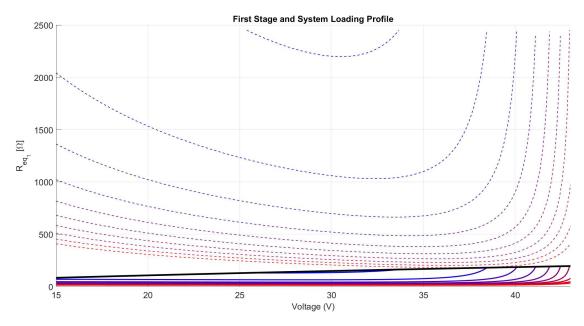

| 4.5  |                                                                                      |          |  |  |

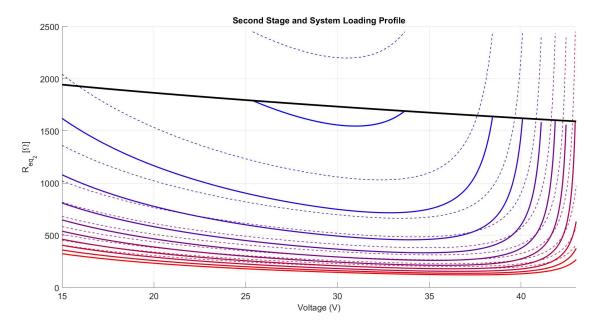

| 4.6  |                                                                                      |          |  |  |

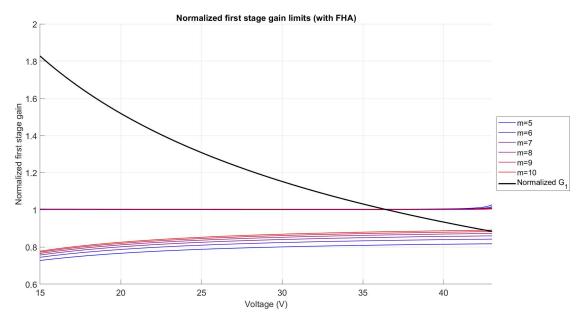

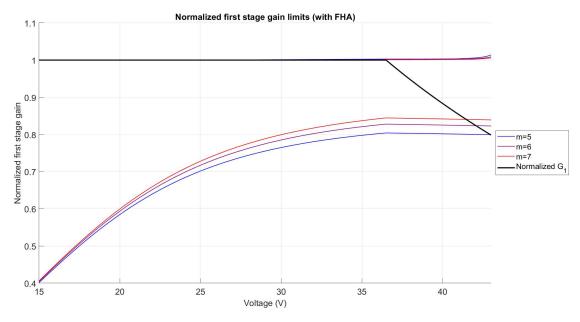

| 4.7  | First stage gain limitations (example)                                               |          |  |  |

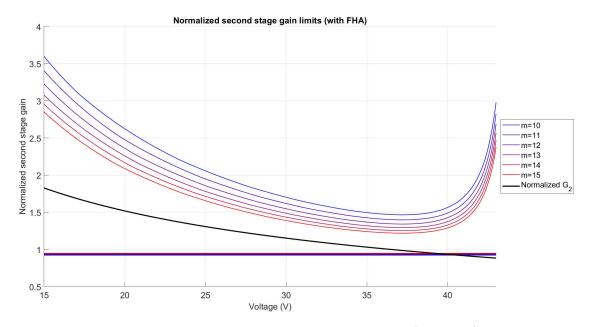

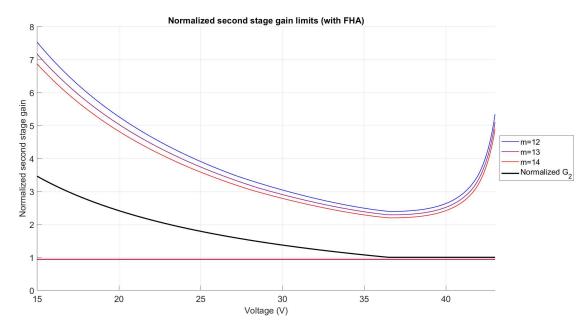

| 4.8  | Second stage gain limitations (example)                                              | 64       |  |  |

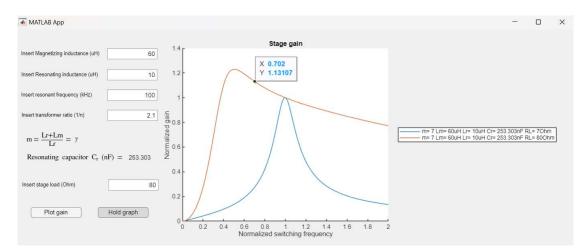

| 4.9  | FHA gain plot tool                                                                   | 65<br>67 |  |  |

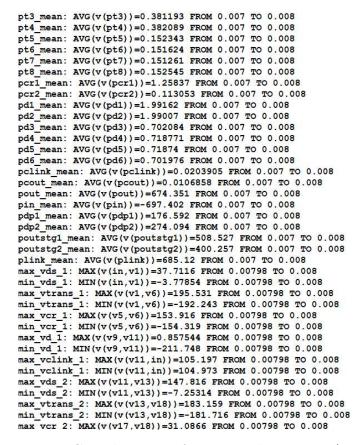

|      | Console output for one working point (example)                                       | 67<br>67 |  |  |

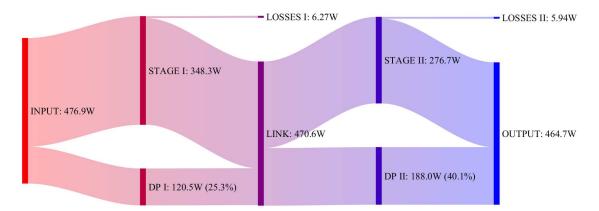

|      | Sankey diagram for power flow visualization (example)                                |          |  |  |

|      | Power budget of each architecture (example)                                          | 68       |  |  |

|      | Current and voltage stresses table (example)                                         | 68       |  |  |

| 4.14 | Graphical representation of the multi-mode approach of the proposed                  | 70       |  |  |

| 1 15 | converter in the range of target working points                                      | 70<br>71 |  |  |

|      |                                                                                      |          |  |  |

|      | 6 First proposal for the gain profiles                                               |          |  |  |

|      | First optimization action and effect                                                 | 73<br>74 |  |  |

|      | 8 Proposed gain profiles                                                             |          |  |  |

|      | Voltage stress reduction of the IPOS configurations                                  | 75       |  |  |

| 4.20 | First stage loading profile (final)                                                  | 78       |  |  |

| 4.21 | Second stage loading profile (final)                             | 78  |  |  |

|------|------------------------------------------------------------------|-----|--|--|

| 4.22 | First stage and system loading profile contrast (final)          | 79  |  |  |

| 4.23 | Second stage and system loading profile contrast (final)         | 79  |  |  |

|      | First stage gain limitations (final)                             | 80  |  |  |

|      | Second stage gain limitations (final)                            | 80  |  |  |

|      | 6 Small ripple approximation consequence on current              |     |  |  |

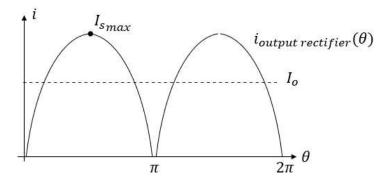

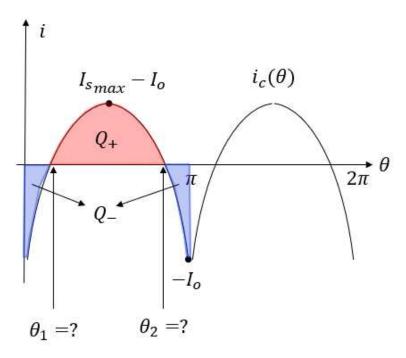

| 4.27 | Output rectifier current waveform                                | 84  |  |  |

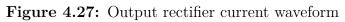

| 4.28 | Output capacitor current waveform                                | 84  |  |  |

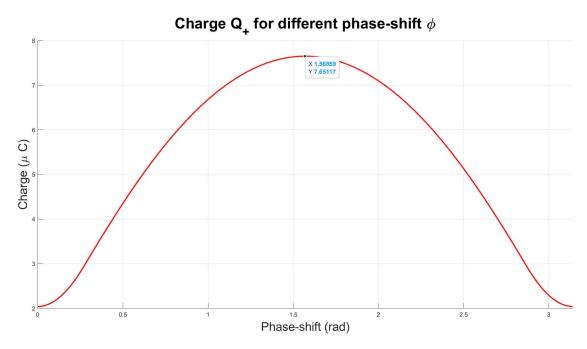

| 4.29 | Current phase-shift effect on first stage output capacitor       | 86  |  |  |

| 4.30 | Positive charge worst case scenario analysis                     | 87  |  |  |

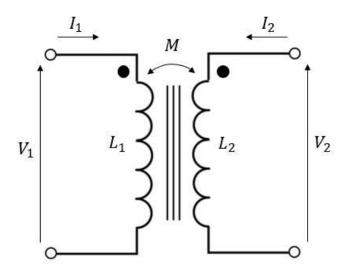

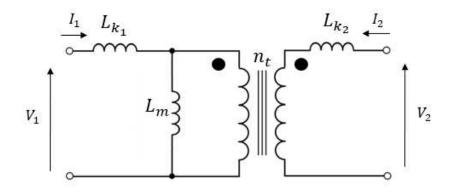

| 5.1  | Base coupled inductors model of the transformer                  | 90  |  |  |

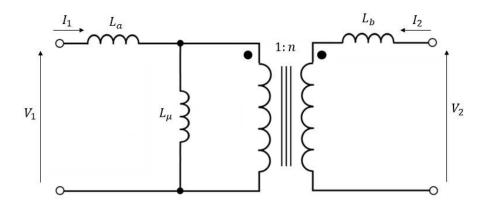

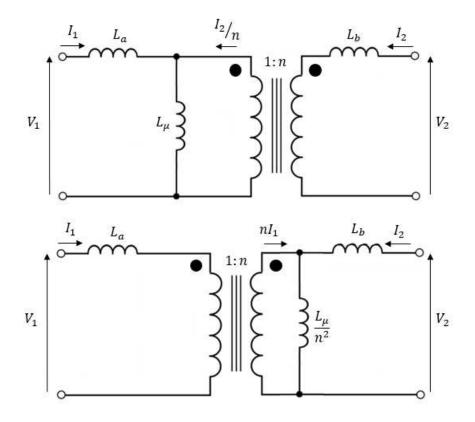

| 5.2  | Intermediate model of the transformer                            | 92  |  |  |

| 5.3  | Intermediate model analysis visualization                        | 93  |  |  |

| 5.4  | Distributed leakage transformer model                            | 94  |  |  |

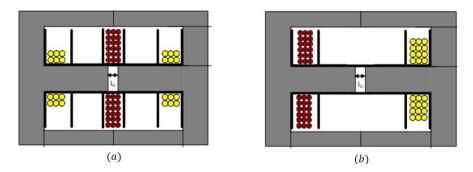

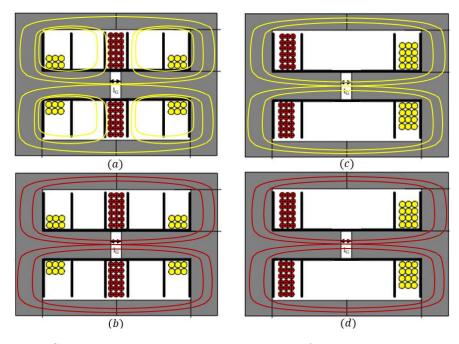

| 5.5  | Symmetrical and asymmetrical transformer architectures           | 95  |  |  |

| 5.6  | Symmetrical and asymmetrical transformer architectures magnetic  |     |  |  |

|      | flux linkage                                                     | 95  |  |  |

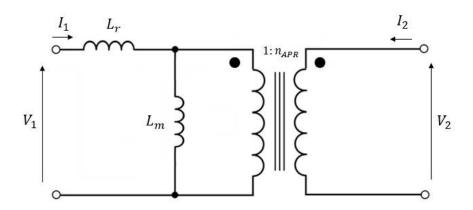

| 5.7  | All primary referred transformer model                           | 96  |  |  |

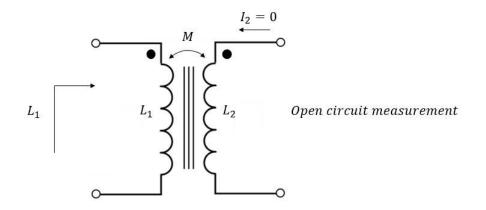

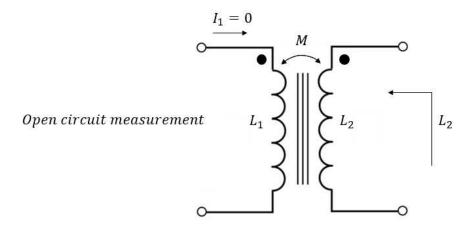

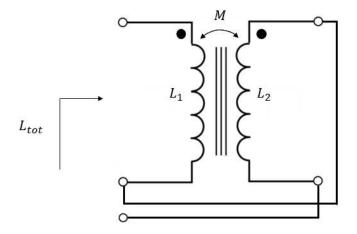

| 5.8  | Coupled inductors measurement 1, open-circuit secondary          | 97  |  |  |

| 5.9  | Coupled inductors measurement 2, open-circuit primary            | 98  |  |  |

|      | 0 Coupled inductors measurement 3, additive series connection 98 |     |  |  |

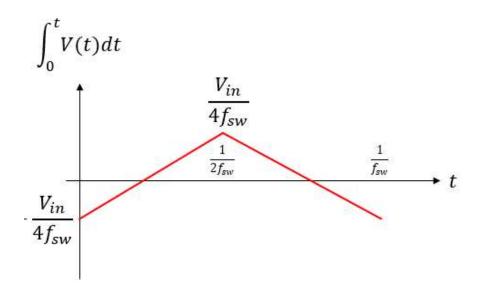

|      | Volt-second waveform at the magnetizing inductance               |     |  |  |

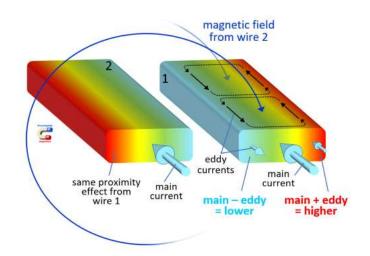

|      | Proximity effect between two conductors                          |     |  |  |

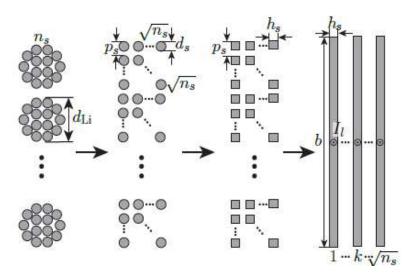

|      | Wojda method wire transformation                                 |     |  |  |

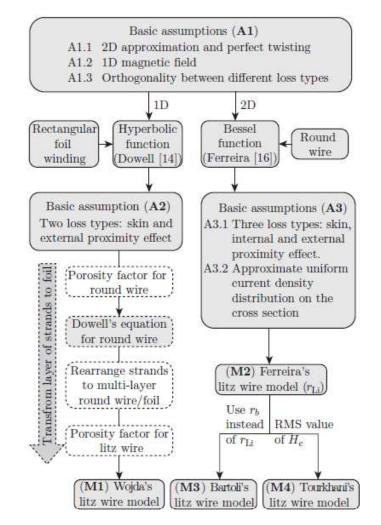

|      | Diverse Litz wire models                                         |     |  |  |

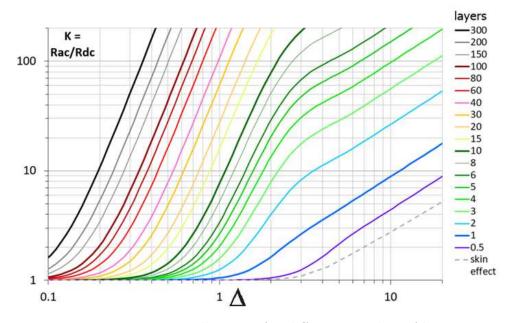

|      | Dowell curves for different number of layers                     |     |  |  |

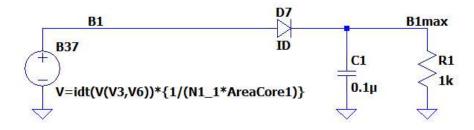

|      | LTSpice implementation of Dowell/Wojda model                     |     |  |  |

|      | Magnetic flux density peak detector in <i>LTSpice</i>            |     |  |  |

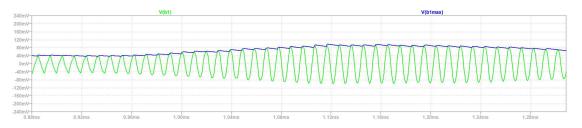

|      | Magnetic flux density peak detection showcase                    |     |  |  |

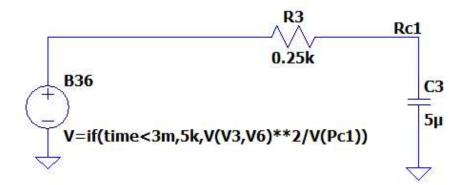

|      | Core power loss estimation in <i>LTSpice</i>                     |     |  |  |

| 5.20 | Equivalent core loss resistor filtering                          | 116 |  |  |

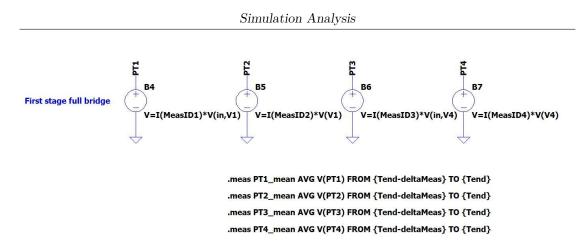

| 6.1  | First stage voltage and current stresses measuring commands      |     |  |  |

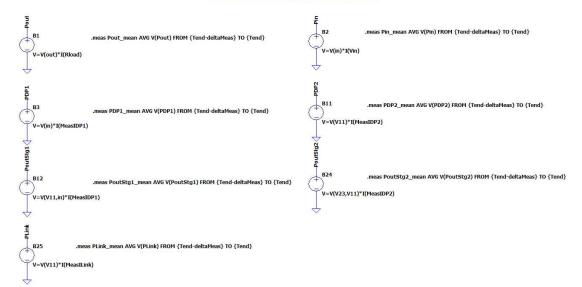

| 6.2  | Simulation accuracy controls                                     |     |  |  |

| 6.3  | Power measurement for power flow analysis                        |     |  |  |

| 6.4  | Power measurement for power losses                               |     |  |  |

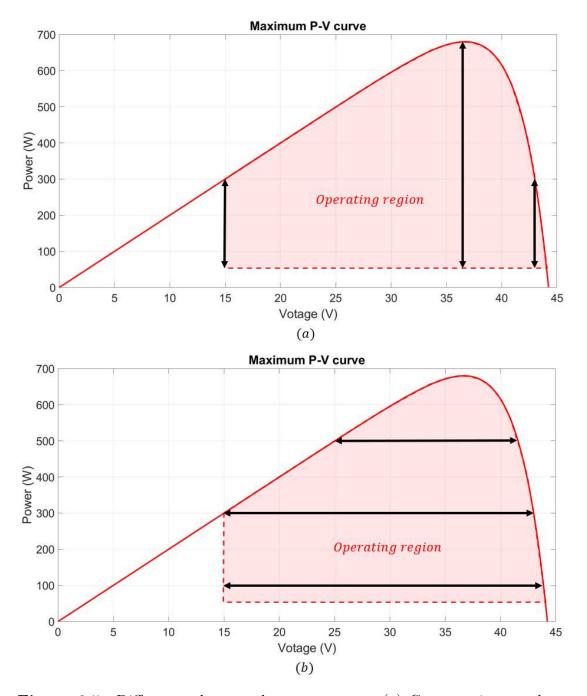

| 6.5  | Different voltage and power sweeps                               |     |  |  |

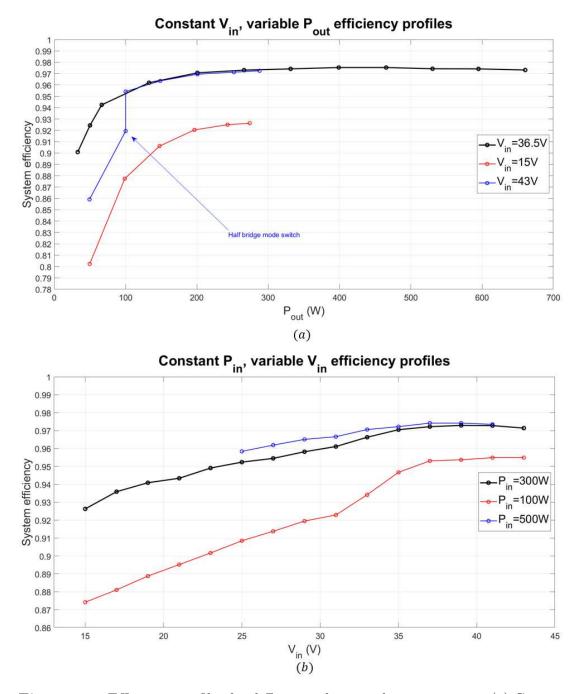

| 6.6  | Efficiency profiles for different voltage and power sweeps       |     |  |  |

| 6.7  | Pass-through power flow rise at high input voltage               | 127 |  |  |

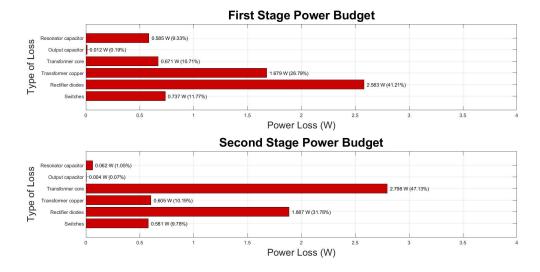

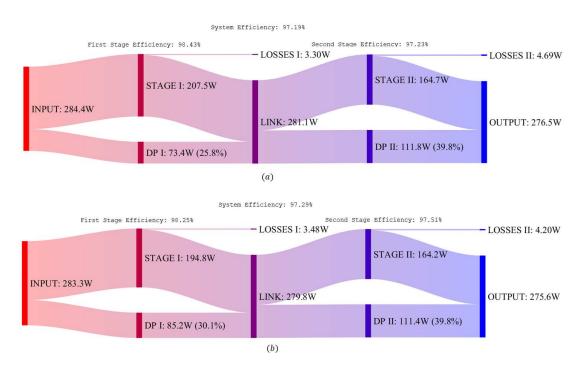

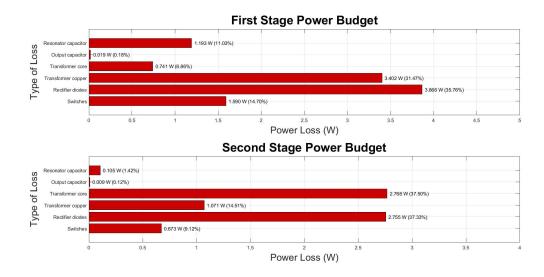

| 6.8 | Power budget for the nominal input voltage case, extracting maxi- |     |

|-----|-------------------------------------------------------------------|-----|

|     | mum power from the system                                         | 128 |

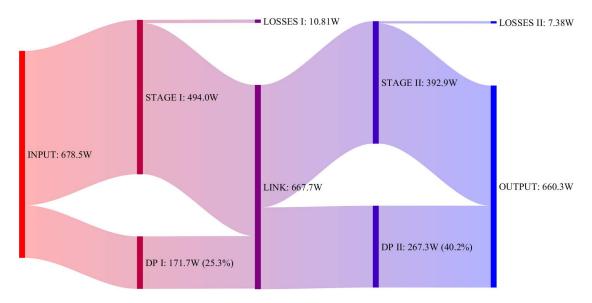

| 6.9 | Power flow diagram for the nominal input voltage case, extracting |     |

|     | maximum power from the system                                     | 128 |

## Chapter 1

## Introduction

### **1.1** Solar energy power systems

#### 1.1.1 Current trends of energy production

Solar energy has seen a major growth in the last decade, it has in fact started following an exponential tendency in terms of installed power capacity across the world. Only in 2023, the global power capacity raised 34% with respect to the total capacity in 2022 [1] as it can be seen in Fig.1.1.

Figure 1.1: Solar energy capacity addition from 2022 to 2023

The increase in the use of solar energy is mainly driven by the exponential drop in costs over the last decade, thanks to technological advancements, making it one of the lowest-cost sources of energy per kWh [2]. As shown in Fig. 1.2, prices are expressed in USD and adjusted for inflation to 2023 (levelized cost of energy). This downward trend in the cost of solar energy production is expected to continue, as this method of energy harnessing follows Wright's law [3], where prices decline exponentially as cumulative installed capacity grows.

Figure 1.2: Different energy sources cost per kWh evolution in time

To achieve a better transition to renewable energy systems, not only is technology for power generation necessary, but the interfaces to merge these varying power supplies with the infrastructure are critical.

Fossil fuels have the advantage of providing an "instantly available" energy source for grid injection. In contrast, renewable energy like wind and solar exhibit uncontrollable variability due to their dependence on environmental conditions. This introduces significant challenges for the power converter interfaces such as the capacity of operating under multiple working points while ensuring seamless grid integration while maximizing efficiency. Such converters may also manage disconnections during unfavorable conditions or integrate energy storage systems for enhanced reliability. As a result, renewable sources act as complementary sources, offsetting the use of stored energy like fossil fuels and hydroelectric power when available.

In 2023, rooftop photovoltaic modules accounted for the largest share of installations in the European Union, 33% of which are in the residential segment, mainly due to increasing cost of electricity [1]. This particular application of decentralized energy production relies on power converters designed primarily for single-phase grid-tied systems, which is the scope of this thesis.

In the context of energy production, decentralized schemes enable incremental grid capacity expansion, ensuring improved fault tolerance and scalability. Each small addition to the grid capacity, when multiplied by numerous contributions, results in a significantly larger overall capacity. This approach is more fault-tolerant, as the disconnection of one provider does not cause the entire grid to malfunction.

Several single-phase grid-tied decentralized photovoltaic system topologies exist depending on the configuration of photovoltaic panels at the input of the system [4]. The ac-module configuration uses a dedicated power converter for each photovoltaic panel connected to the grid. Having only one module presents the need for high DC voltage gains, which generates a bottleneck in the efficiency achieved by this type of system. However, they compensate their limitation in efficiency with the greatest exploitation of the maximum power that can be extracted from the photovoltaic module; they also adapt best in situations where photovoltaic panels are subject to varying conditions, such as shading, soiling, or differing orientations, as shown in Fig. 1.3, allowing each panel's power converter to adjust its control depending on the condition. In other topologies where one control scheme manages the energy extraction of numerous photovoltaic panels, the mismatch in their operating conditions leads to a reduction of the energy yield of the system.

**Figure 1.3:** Different photovoltaic panel energy production factors. (a) Shading (b) Soiling (c) Differing orientations

### **1.2** Scope of the thesis and organization of work

Photovoltaic panels present a wide input voltage range, usually low voltages for most commercial variants from 10-60 V. In the context of ac-module configuration for single-phase grid-tied systems, high step-up DC gain is needed to adapt the low voltage level of the single photovoltaic panel to the grid. Additionally, the power output of the photovoltaic panel varies significantly due to factors such as irradiance and temperature. These variations in input voltage and power present considerable challenges to the design of power converter circuits, which must operate reliably under wide input voltage and output load conditions.

Among the power conversion system between the photovoltaic panel and the grid, the high gain DC-DC converter represents the primary bottleneck in terms of efficiency. The aim of this thesis is to explore the application of Partial Power Processing (PPP) in the design of a wide-input-range DC-DC power converter stage for single-phase grid-tied ac-module photovoltaic systems. The study focuses on assessing the advantages and limitations of this technique while proposing a novel architecture based on an Input-Parallel Output-Series (IPOS) configuration to maximize the efficiency of the DC-DC stage.

The DC-AC converter, which facilitates direct grid connection, is not analyzed in depth in this work. It is treated as a simple power consumer for the sake of design of the DC-DC converter, left as a research topic for future works.

In Chapter 2, an introduction to photovoltaic energy sources is given, with the description of the state of the art connections configuration, as well as the introduction of the proposed power converter and its attributes.

In Chapter 3, a state of the art review on high-frequency power conversion is carried out, with the introduction of resonant converters as a type of highfrequency power converter, and the in-depth analysis of the particular topology used throughout this work.

In Chapter 4, the design process is explained as well as the description of the tools developed to aid this process. The optimization of the proposed architecture is performed to define and justify the selection of the necessary quantities.

In Chapter 5, an in-depth analysis on power transformers is performed, highlighting several aspects particularly important for the selected resonant topology, as well as providing the necessary models to implement power transformers and their losses in simulation environment.

In Chapter 6, device selection to implement the quantities defined in previous chapters is described, and finally the results of the analysis and design are portrayed in the characteristics retrieved from the simulation. To conclude, Chapter 7 closes this thesis with a summarized description of the results found throughout this work, as well as proposing the next challenges to continue the development of the proposed power converter.

The analysis developed in this work, with its developed tools and conclusions, relies on the use of the following software, provided by Politecnico di Torino student licensing program:

- *PSIM* for electronic circuits simulation from Altair [5]. Specially utilized for photovoltaic panel modeling.

- *MATLAB* and toolboxes from Mathworks [6]. Utilized for developing user interfaces and processing data in the design phase of this work.

- *LTSpice* for electronic circuits simulation from Analog Devices [7]. Utilized for the SPICE simulation of the final architecture and data extraction for further report generation.

## Chapter 2

# **PV Power Conversion Overview**

## 2.1 PV Sources and their Characteristics

### 2.1.1 Modeling of photovoltaic panels

Photovoltaic cells convert solar energy into electrical energy, since these cells are photocurrent generators, the most common models are obtained by superimposing the behavior of the following lumped components:

- One or more semiconductor diodes paired with a current generator, representing the recombination and generation currents of the cell

- A series resistance representing the semiconductor material resistance, the metal contacts and interconnections in the cell

- A shunt resistance representing the leakage current within the cell.

The most straightforward model is the single-diode model [8], which represents an ideal solar cell with its voltage and current losses, its circuit can be seen in Fig. 2.1. It is a simplified model that still captures the essentials of solar cells working principle.

The circuit behavior depends strongly on the environmental conditions of temperature and solar irradiance, which determine primarily the photocurrent generated

Figure 2.1: Single-diode solar cell equivalent circuit

by the cell. Usually the relationship is built in an incremental fashion, by determining certain parameters in Standard Test Conditions (STC) and incorporating them into the model.

A relationship between voltage and current is created described by applying Kirchhoff laws to the circuit model as seen in Eqs. (2.2) and (2.3). This relationship creates an IV characteristic which has the shape of a typical power supply, being able to provide a considerable current at low voltages, while dropping the ability of regulation at higher voltages. In terms of PV characteristic, this creates a point of maximum power extraction which is of interest for solar applications. By controlling the load current pulling, a controller can force the photovoltaic panel to work on this maximum power point (MPP) given a certain solar irradiance and temperature.

The current through the diode is described by Shockley equation:

$$I_D = I_S(e^{\frac{V_D}{na\frac{kT}{q}}} - 1)$$

(2.1)

Where  $V_D$  is the applied forward voltage to the diode, k is the Boltzmann constant, T is the cell temperature, q is the electron charge, n is the number of series cells, a is the ideality factor of the diode ranging from 1 to 2, and  $I_S$  is the saturation current, usually dependent in the temperature, solar irradiance and band-gap energy [9].

By applying Kirchhoff laws to the circuit model, the relationship linking the output current and the output voltage is found, as seen in Eq. (2.3).

$$I = I_{ph} - I_D - I_{sh} \tag{2.2}$$

$$I(V) = I_{ph} - I_S(e^{\frac{V + I(V)R_s}{na\frac{kT}{q}}} - 1) - \frac{V + I(V)R_s}{R_{sh}}$$

(2.3)

Although the physical model of the solar cell is not the primary focus of this thesis, it plays an important role in studying specific mission profiles and their implications for daily variations in solar irradiance and temperature based on geographic location. For the purposes of this work, however, the focus will be on utilizing empirical models derived from experimental parameters. The power converter design for this specific case will be developed in a general manner, leaving the design for a specific mission profile as a potential topic for future work.

To simplify the working behavior of a photovoltaic panel, this work will leverage a utility tool in *PSIM*, which allows the incorporation of key parameters derived from commercial photovoltaic panel datasheets. Datasheets from photovoltaic panel manufacturers typically provide parameters like open-circuit voltage, short-circuit current, and maximum power point, which are essential inputs for the *PSIM* utility tool. For working with the physical model, an inference on the circuit parameters must be done starting from the datasheet, which can be cumbersome.

By inputting parameters such as open-circuit voltage, short-circuit current, and maximum power point values, the utility tool can generate IV curves that represent the photovoltaic panel behavior under various environmental conditions. This approach enables an efficient and realistic representation of the panel electrical characteristics without delving into complex physical modeling, while still capturing the critical performance metrics required for the analysis.

The interface of the *PSIM* Solar Module utility can be seen in Fig. 2.2. Some parameters are not stated in the manufacturer datasheet but can be inferred according to the technological aspects of the photovoltaic panel such as type of semiconductor being utilized. With the initial parameters inference, small increments/decrements may be needed to fit the curve, mainly such that the maximum power point position is correct.

In the section "Operating conditions" from the interface, several curves can be extracted depending on temperature and solar irradiance. In this work, the temperature is considered to be constant  $(25^{\circ}C)$  with variable solar irradiance.

Figure 2.2: PSIM Solar Module utility interface

# 2.1.2 Selected photovoltaic panel modeling and maximum power points

The proposed photovoltaic panel for this work is the commercial model 3SHBGHA#-680 from 3SUN, which characteristics can be found in [10]. Table 2.1 summarizes the parameters used to extract the curves as well as some commentary on inferred/recommended values.

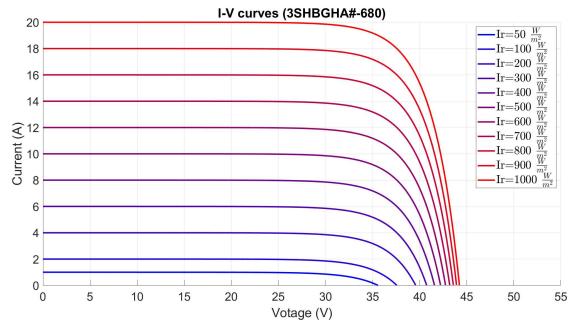

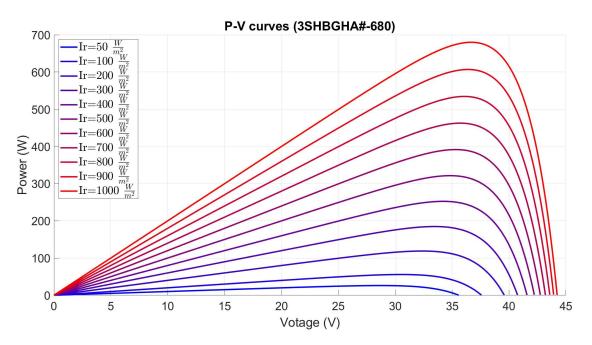

The IV curves can be extracted as a text file with the information separated in columns. This allows for then processing the information in a program like MATLAB, which will then further aid this work in the design phase. Figs. 2.3 and 2.4 show the ability to display the extracted data from PSIM in MATLAB for multiple irradiance values at a working temperature of 25°C, the code for processing the information is found in the Appendix A.1.

| Parameter                 | Value                              | Comments                                                      |

|---------------------------|------------------------------------|---------------------------------------------------------------|

| Number of Cells Ns        | 60                                 | Number of series cells                                        |

| Maximum Power Pmax        | 680 (W)                            | _                                                             |

| Voltage at Pmax           | 36.49 (V)                          | -                                                             |

| Current at Pmax           | 18.64 (A)                          | -                                                             |

| Open-Circuit Voltage Voc  | 44.2 (V)                           | -                                                             |

| Short-Circuit Current Isc | 19.78 (A)                          | -                                                             |

| Temperature Coeff. of Voc | $-0.2 \left(\frac{\%}{°C}\right)$  | -                                                             |

| Temperature Coeff. of Isc | $0.044 \ (\frac{\%}{°C})$          | -                                                             |

| Light Intensity S0        | $1000  \left(\frac{W}{m^2}\right)$ | Standart Test Conditions (STC)                                |

| Temperature Tref          | 25 (°C)                            | Standart Test Conditions (STC)                                |

| dv/di (slope) at Voc      | 0 (V/A)                            | <i>PSIM</i> docummentation<br>recommends 0 when not available |

| Band Energy Eg            | $1.12 \; (eV)$                     | Typical value for<br>Mono-crystalline n-type Si               |

| Ideality factor           | 1.87                               | Tuned value to fit the curve                                  |

| Shunt Resistance Rsh      | 1000<br>(ohm)                      | Typical value for<br>Mono-crystalline n-type Si               |

| Coefficient Ks            | 0                                  | <i>PSIM</i> docummentation<br>recommends 0 when not available |

**Table 2.1:** Summary of PSIM Solar Module utility tool parameters

Figure 2.3: I-V characteristic for multiple irradiance values

Figure 2.4: P-V characteristic for multiple irradiance values

As it can be seen in Figs. 2.3 and 2.4, the PV curves present a maximum power point (MPP) for each irradiance value. If the grid is considered as an infinite power sink, which is a reasonable assumption as renewable energy is intended for instant consumption, while other methods serve for buffering as mentioned in the introduction; it is of interest to work in the vicinities of these points, extracting the maximum power from the photovoltaic panel.

This is achieved by implementing a Maximum Power Point Tracking (MPPT) control scheme, which interacts with the driving of the power converter of the solar energy system to force this working point. There are several ways of implementing MPPT control, which are not the scope of this work, however, the concept introduces important criteria for optimization of the circuit. If the MPPs are intended to be exploited, then it is reasonable to optimize the design of the DC-DC converter so that the maximum efficiency is achieved in the input-voltage range where the MPPs happen.

#### 2.1.3 Strings configurations and micro-inverters

A photovoltaic panel is composed of multiple solar cells connected in an array fashion, series connection of cells provides a raise of the output voltage, while parallel connection of cells provides a raise of the current capability.

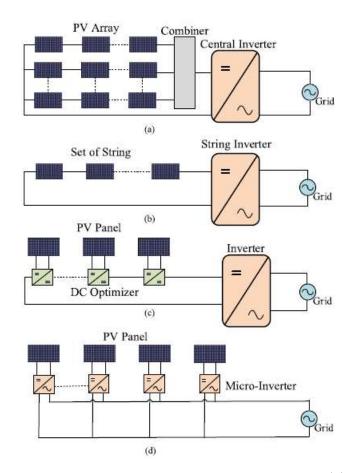

This process is also applied to photovoltaic panels as seen in Fig. 2.5 [11], a string configuration is composed of multiple panels connected in series, while a PV array is a set of strings connected in parallel. This creates a variety of alternatives which set different specifications for the power conversion systems.

Figure 2.5: Different types of photovoltaic panels connection. (a) central-inverter system, (b) string-inverter system, (c) dc optimizer, and (d) micro-inverters built into individual panels. Picture adopted from [11].

Micro-inverter systems are analyzed in this work, they are advantageous in comparison with the other alternatives [12] in the following aspects:

- They allow for a compact design where the power converter can be attached to the back of the photovoltaic panel, increasing flexibility and modularity.

- They allow for plug-and-play type of systems where complexity of installation is greatly reduced.

- Unlike string/central systems, the malfunction of one photovoltaic panel does not affect the overall performance of the system, as every photovoltaic panel behaves as a standalone system.

- Unlike string/central systems, independent MPPT control schemes over each

photovoltaic panel ensure the maximum power extraction, making them the best option in mismatch conditions between panels. In strings configurations, the distributed MPPT control along a string may not align with the MPP of all photovoltaic panels.

• Unlike DC optimizer based systems, the malfunction of the inverter does not pull off the grid the entire power generation system.

However, they have limitations which make them non-ideal in certain scenarios:

- In large power production systems, cost is a critical factor, micro-inverter systems implement one power converter for each photovoltaic panel, making them expensive in contrast with centralized schemes.

- The absence of series string connection requires high DC gain power converters to meet the voltage requirements of the grid.

Considering the actual global electricity grid, the advantages and limitations make them a great alternative for decentralized grid expansion, as mentioned in the introduction of this work.

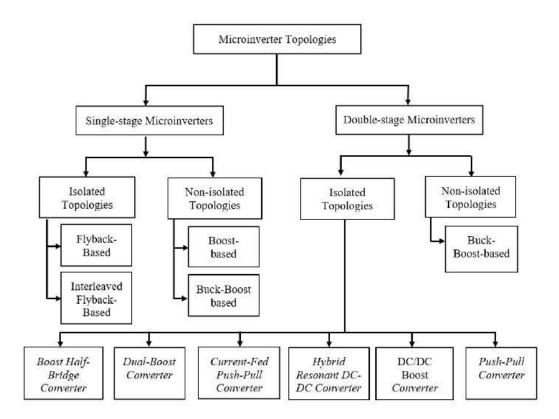

The power converters for micro-inverter systems vary topologically, in [11] and [12] the typical implemented schemes are showcased, varying mainly within single and double stages systems, with or without isolation as seen in Fig. 2.6.

The DC-DC converter proposed in this work is part of a double-stage microinverter system, where the DC-DC converter is designed to operate independently from the DC-AC inverter. The particular topology of this work is not found in Fig. 2.6 as it is a new proposal for micro-inverter topologies. The particular details of the topology implemented for this work will be expanded in the following sections.

Figure 2.6: Micro-inverter topologies classification

### 2.2 Proposed DC-DC Converter Framework

### 2.2.1 Partial Power Processing: advantages and limitations

Full power processing is the most common scenario in power conversion systems. A full power converter is the one in which power flows through the architecture at a complete rate.

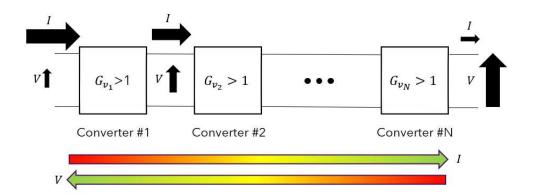

Partial Power Processing (PPP) is the power flow scheme in which one or more power converters do not process the entirety of the available power at the input to the output [13]. The power is split through different converters, reducing considerably voltage and current stress.

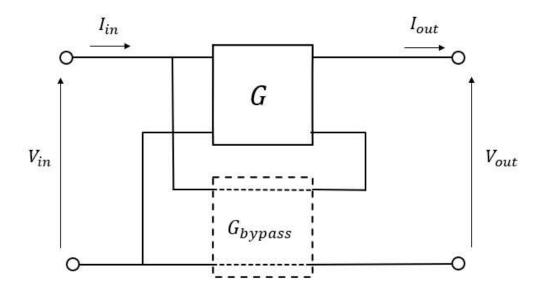

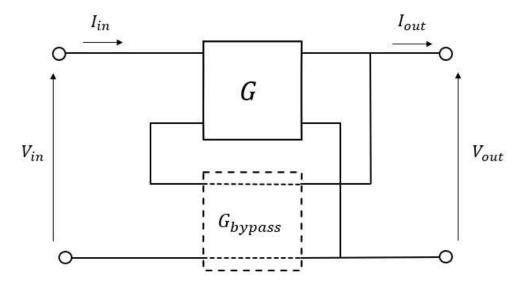

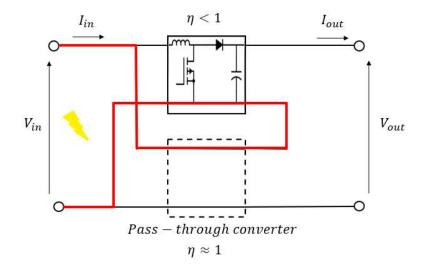

Implementations of PPP are mainly based on two different architectures, the Input-Parallel Output-Series (IPOS) configuration and the Input-Series Output-Parallel (ISOP) configuration, shown in Figs. 2.7 and 2.8. Both architectures are presented with their generalized architecture, however, in this work, the IPOS configuration is exploited with the by-pass converter in the form of a "pass-through" converter, as shown in Fig. 2.9, providing unitary voltage gain with theoretical 100% efficiency, assuming wire losses negligible. The pass-through converter concept allows for better performance, providing a boost in efficiency given the direct path of power to the load, while also reducing stresses in terms of voltage and current of the converter devices thanks to the PPP configuration, allowing for the downsizing of components [14].

Figure 2.7: General IPOS configuration overview

Figure 2.8: General ISOP configuration overview

Figure 2.9: Pass-through converter IPOS configuration overview

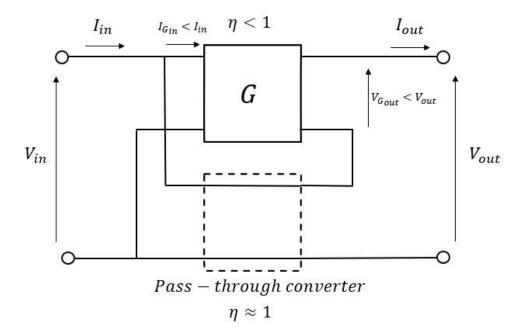

The Pass-through IPOS converter has two main advantages with respect to full power conversion, as well as two main drawbacks.

The first main advantage is the decrease in voltage and current stress in the full power converter. Considering the input port to the power converter G,  $I_{in}$  splits into a portion of current flowing into G and a portion of current flowing into the Pass-trough converter, then reduced current stress at the input is achieved compared to the full converter which would experience  $I_{in}$  entirely. In terms of voltage, the output voltage  $V_{out}$  is formed as the series connection of  $V_{in}$  and  $V_{G_{out}}$  which essentially means that  $V_{G_{out}}$  is lower than  $V_{out}$ , creating reduced voltage stress at the output of the converter. This phenomenon is highlighted in Fig. 2.10.

Figure 2.10: Reduced stress visualization of the Pass-through IPOS configuration

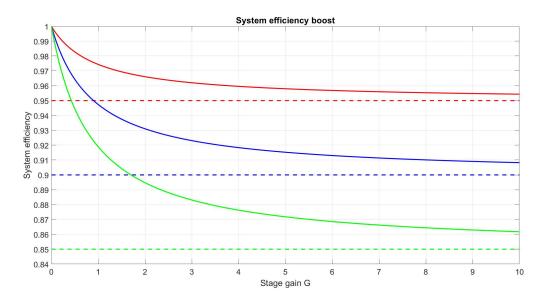

The second main advantage is the improvement in efficiency to the overall system, given that part of the power is directly transferred to the output with the theoretical 100% efficiency. The overall system efficiency can be quantized according to the power split as seen in Eq. (2.5), making use of Eq. (2.4). In Fig. 2.11, the dotted lines represent the plain efficiency values the stage could present ( $\eta_G$ ), while the solid lines represent the overall system efficiency with IPOS configuration (assuming constant efficiency through all gain values just for visualization), it can be seen how the system efficiency is always equal or greater than  $\eta_G$ .

$$\eta_G = \frac{P_{G_{out}}}{P_{G_{in}}} = \frac{V_{G_{out}}I_{out}}{V_{in}I_{G_{in}}} = G\frac{I_{out}}{I_{G_{in}}} \longrightarrow I_{G_{in}} = G\frac{I_{out}}{\eta_G}$$

(2.4)

$$\eta_{system} = \frac{P_{out}}{P_{in}} = \frac{V_{out}I_{out}}{V_{in}I_{in}} = \frac{(GV_{in} + V_{in})I_{out}}{V_{in}(I_{G_{in}} + I_{out})} = \frac{(G+1)I_{out}}{G\frac{I_{out}}{\eta_G} + I_{out}} = \left|\frac{G+1}{1 + \frac{G}{\eta_G}}\right|$$

(2.5)

The first main drawback, which can also be observed in Fig. 2.11, is the fact that the efficiency boost is greatly reduced for high gain values of the power converter. This is logical, as the more gain the converter provides, the less significant is the direct  $V_{in}$  connected in series to the converter output. It is also interesting to note

**Figure 2.11:** System efficiency boost of the Pass-through IPOS configuration. Stage simplified efficiency profiles (dotted lines) versus stage with same efficiency profile connected in IPOS configuration (solid lines)

how approaching lower gains takes more advantage of the power splitting effect, effectively adopting the direct path 100% efficiency at gain 0, which would be equivalent to having a pair of wires between input and output. This mechanic of gain dependence of the efficiency boost will be a critical factor for the proposed architecture.

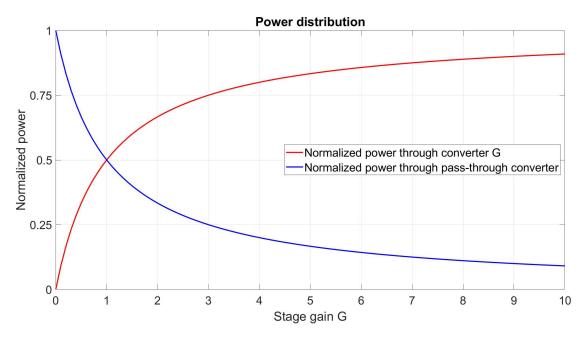

The power flow can also be quantized to understand how lower gain values create a greater amount of power flow through the more efficient direct path. In Eqs. (2.6)and (2.7), the power split can be analyzed in terms of gain of the stage, considering conservation of power, while this can be visualized in Fig. 2.12 normalized to the total power flowing through the entire IPOS configuration.

$$P_{out} = V_{out}I_{out} = (G+1)V_{in}I_{out} = V_{in}I_{out} + GV_{in}I_{out}$$

$$P_G = V_{G_{out}}I_{out} = GV_{in}I_{out}$$

Normalizing:

$$\frac{P_G}{P_{out}} = \frac{GV_{in}I_{out}}{V_{in}I_{out} + GV_{in}I_{out}} = \boxed{\frac{G}{G+1}}$$

(2.6)

$$\frac{P_{pass-through}}{P_{out}} = \frac{P_{out} - P_G}{P_{out}} = 1 - \frac{P_G}{P_{out}} = \boxed{\frac{1}{G+1}}$$

(2.7)

Figure 2.12: Power split and stage gain in the IPOS configuration

The second main drawback, and much more critical, is the fact that the possible topologies for G are greatly reduced, as to be able to apply the IPOS connection, non-commonly grounded topologies are mandatory. Commonly grounded topologies create a short-circuit hazard that can be visualized in Fig. 2.13, where a simple boost converter is employed as G. This aspect is critical for the topology selection in this work.

The non-commonly grounded topologies requirement is achieved by making use of isolation transformer based architectures. This creates a galvanic separation of the circuit, making the secondary side sector of the architecture floating with respect to the ground of the primary side sector. This second main drawback not only consists in a restricted selection of the topology, but also creates the need for isolation in a configuration that will essentially be non-isolated, as this property is lost due to the pass-through converter connection, the output and the input share the same ground, although the stage implements isolation.

The absence of isolation in a system can pose safety risks, such as ground faults and the circulation of common-mode currents through the stray capacitance of the photovoltaic panel to the ground [15]. However, it is important to notice that this work focuses on the DC-DC converter stage, several non-isolated architectures have been proposed to improve the performance of the system. Isolation is a requirement that depends on the specific application, the power converter stage proposed here is a fraction of the whole system, it could be used in scenarios where

Figure 2.13: Short-circuit hazard in IPOS configuration

isolation is not mandatory, and in the case it is, isolation could be implemented in the DC-AC stage connected to the grid in the form of an isolation transformer. Transformer-less topologies for the DC-AC converter have also been proposed to reject common-mode currents in diverse ways [16].

#### 2.2.2 Proposed power converter

In Fig. 2.4 from Section 2.1.2, it can be observed that the selected photovoltaic panel, as is generally the case, exhibits a wide input voltage range. This range needs to be stepped up to a much higher, constant voltage to feed the DC-AC converter connected to the grid. In Italy, the commercial grid operates at  $230 V_{RMS}$  and 50 Hz, corresponding to a peak sinusoidal voltage of 325.27 V. To account for AC-DC conversion losses and provide a safety margin, the proposed converter is designed to step up the voltage to  $350 V_{converter}$ .

A limitation to the input voltage range is set between reasonable values, for this particular application the range 15-43 V is considered, which categorizes this converter as a wide-input DC-DC converter. This wide input range imposes a wide range of DC gain with values between 8.14 at maximum input voltage and 23.33 at minimum input voltage for constant output voltage.

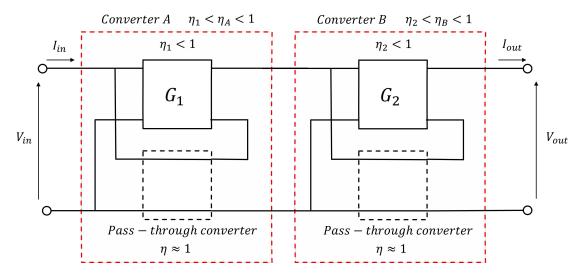

The high gain regulation scheme threatens the IPOS configuration advantage of performance boosting. As analyzed in the previous section, higher gain implies less power flow through the pass-through converter, effectively reducing the efficiency raise of this architecture. For overcoming this situation, this new proposed converter employs two IPOS configurations connected in a quadratic manner as showed in Fig. 2.14.

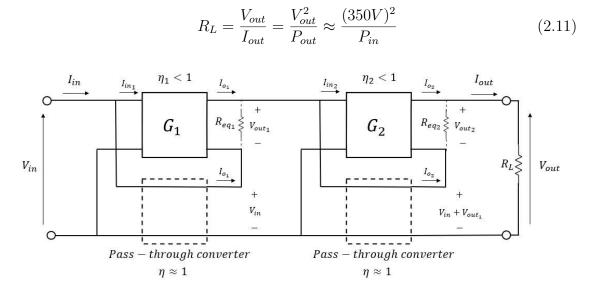

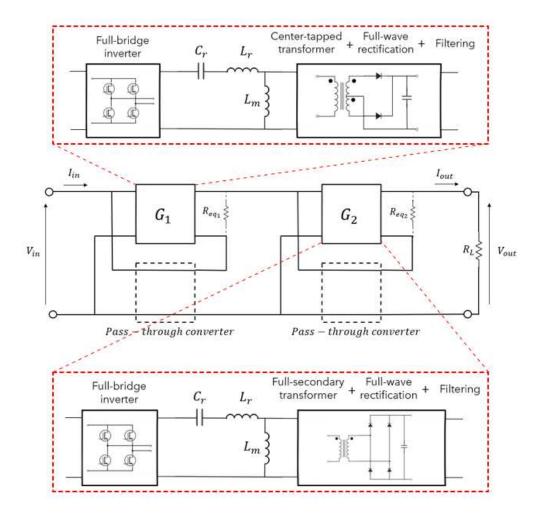

Figure 2.14: Proposed power converter architecture

In full quadratic power converters, the total system efficiency is the product of the efficiencies of each individual power converter. The proposed approach follows the same principle but offers an advantage: each stage benefits from an efficiency boost that depends on its gain. In quadratic converters, the required gain per stage can be significantly lower while still achieving a high overall gain, since the total system gain is the product of the gains of each stage, as shown in Eq. (2.8).

$$G_{total} = (G_1 + 1)(G_2 + 1) \tag{2.8}$$

The total DC-DC converter efficiency can be derived by utilizing the expression found in Eq. (2.5) considering the total efficiency as the product of both converters efficiencies, as seen in Eq. (2.9). The fact that each term is greater than the individual stage efficiency implies that this total converter efficiency with IPOS configuration is greater than the case in which the converter was only composed of the two simple stages connected in quadratic form (Eq. (2.10)).

$$\eta_{total_{proposed}} = \frac{G_1 + 1}{1 + \frac{G_1}{\eta_1}} \frac{G_2 + 1}{1 + \frac{G_2}{\eta_2}} = \eta_1 \eta_2 \frac{G_1 + 1}{G_1 + \eta_1} \frac{G_2 + 1}{G_2 + \eta_2} \equiv (<1)(<1)(>1)(>1)$$

(2.9)

$$\eta_{total_{full-power converter}} = \eta_1 \eta_2 \equiv (<1)(<1)$$

(2.10)

By modulating the gain of each stage, the whole gain range can be achieved, producing different efficiency impact depending on how the gain is distributed across both stages.

#### 2.2.3 Equivalent stage loading and decoupling

Partial power processing architectures such as the IPOS configuration make designing each stage challenging as the power split dependence on the stage gain dynamically changes the stage processed power. This relationship is even more complex in this work scheme, where a decision has to be made on how to distribute the gain between two stages with changing processed power depending on each other.

For this task, proposing a decoupling method is useful, to allow designing each stage separately, modeling the influence of the other stage in simpler manner. This can be achieved by computing an equivalent impedance at the direct output of each converter.

As previously stated, the DC-AC converter of the complete system is not of interest for this work, hence it can be modeled as a power consumer which dynamics can be decoupled from the DC-DC converter. In a solar energy production system, the DC-AC converter can be approximated as a resistive load when viewed from the perspective of the DC-DC converter, given that the dynamic behavior is correctly decoupled. This modeling assumption is justified with the filtering capacitor at the output of the DC-DC converter serving as a dynamics decoupler through energy storing, effectively decoupling the switching behavior of the DC-AC converter from the DC-DC converter output. Consequently, the DC-DC converter sees the DC-AC converter as a steady load with a resistance value determined by the power drawn, which value can be estimated from the available power at the input of the system and the output voltage, as seen in Eq. (2.11). This simplified resistive model is particularly useful for analyzing power flow and optimizing the design of the DC-DC converter.

The same concept of modeling the load as a constant resistor according to the power drawn can be applied whenever there is a capacitor large enough to decouple the high-frequency dynamics of the next stage that is being replaced by the resistor. Hence, this idea can also be applied to the first stage load, considering the second stage as a steady power consumer. This equivalent loading behavior is shown in Fig. 2.15. It can be seen in Eqs. (2.12) and (2.13) that the equivalent load resistor experienced by each stage is lower than the DC-AC load equivalent resistor, and that the reduction is highly dependent on the stages DC gain. This effect will be crucial for the design of each stage.

Figure 2.15: Stage equivalent load resistances

$$R_{eq_{2}} = \frac{V_{out_{2}}}{I_{o_{2}}} = \frac{V_{out} - (V_{out_{1}} + V_{in})}{I_{out}}$$

$$= \frac{V_{out} - (G_{1}V_{in} + V_{in})}{I_{out}} = \frac{V_{out} - V_{in}(G_{1} + 1)}{I_{out}}$$

$$= \frac{V_{out} - \frac{V_{out}}{G_{tot}}(G_{1} + 1)}{I_{out}} = \frac{V_{out}}{I_{out}}\frac{G_{tot} - (G_{1} + 1)}{G_{tot}}$$

$$= \frac{V_{out}}{I_{out}}\frac{(G_{1} + 1)(G_{2} + 1) - (G_{1} + 1)}{(G_{1} + 1)(G_{2} + 1)}$$

$$= \boxed{R_{L}\frac{G_{2}}{G_{2} + 1}} \rightarrow R_{eq_{2}} < R_{L}$$

(2.12)

$$R_{eq_{1}} = \frac{V_{out_{1}}}{I_{o_{1}}} = \frac{G_{1}V_{in}}{\frac{I_{in}}{G_{1+1}}} = \frac{V_{in}}{I_{in}}G_{1}(G_{1}+1)$$

$$= \frac{\frac{V_{out}}{G_{tot}}}{G_{tot}I_{out}}G_{1}(G_{1}+1) = \frac{V_{out}}{I_{out}}\frac{G_{1}(G_{1}+1)}{G_{tot}^{2}}$$

$$= R_{L}\frac{G_{1}(G_{1}+1)}{(G_{1}+1)^{2}(G_{2}+1)^{2}} = R_{L}\frac{G_{1}}{(G_{1}+1)(G_{2}+1)^{2}}$$

$$= \boxed{R_{L}\frac{G_{1}}{G_{1}+1}\frac{1}{(G_{2}+1)^{2}}} \rightarrow R_{eq_{2}} << R_{L}$$

(2.13)

It is worth noting that the expressions found in Eqs. (2.12) and (2.13) for the equivalent resistance values are an approximation, in the sense that for their derivation, power conservation through the stages is assumed, which is equivalent as stating that the system is lossless. With high efficient stages the discrepancy is low and the results are acceptable for the design flow.

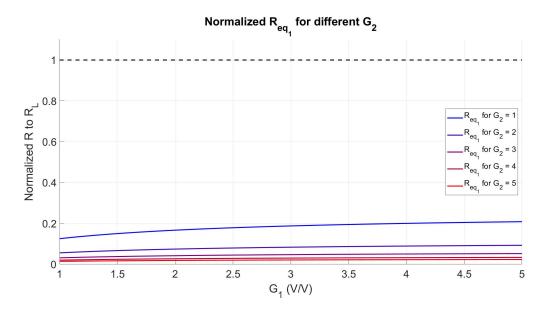

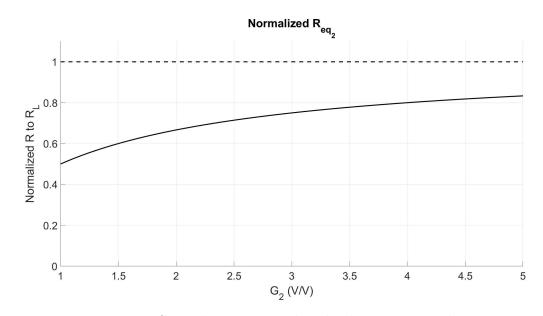

At this point, the expressions in Eqs. (2.12) and (2.13) can be graphically represented to illustrate the difference on magnitude of resistance reduction. In Figs. 2.16 and 2.17, it can be seen how the equivalent resistance at each stage normalized to the output resistance is reduced, this effect being much more pronounced for the first stage. Further into the analysis, the gain profile that will be defined for each stage will morph the system load characteristic to the equivalent resistance at the output port of each stage.

Figure 2.16: First stage equivalent load resistance reduction

Figure 2.17: Second stage equivalent load resistance reduction

# Chapter 3

# Resonant Power Converters and the LLC topology

### **3.1** Resonant Power Converters

#### 3.1.1 High-frequency power conversion

High-frequency non-linear power converters have emerged as the standard for power conversion in recent decades due to their superior performance in terms of efficiency and power density [17]. These converters are widely used in applications from renewable energy systems to consumer electronics, where minimizing energy losses and reducing size are critical design objectives.

One of the key factors contributing to their high power density is the increase in operating frequency. When rising the operating frequency, the size of passive components, such as inductors and capacitors, decreases due to the inverse relationship between component size and operating frequency. This allows for more compact designs, enabling the development of smaller and lighter systems.

In addition to power density, high efficiency is another main advantage of these converters. Efficiency is primarily achieved by carefully controlling the operation of semiconductor devices, such as MOSFETs and IGBTs, to minimize power dissipation. This involves operating the devices in specific regions of their characteristics: the saturation region (ON state) and the cut-off region (OFF state).

The amount of dissipated power in power converters is critical for designing these type of systems. Minimizing lost power not only contributes to a high-efficiency system which is capable of exploiting in the best way the available power, but it also influences the safety of the system. Due to the main power dissipation phenomenon being heat, care must be taken as how this heat is handled, if not treated correctly, the rise in temperature in the circuit can lessen the lifetime of the converter, or even its rapid malfunction by surpassing temperature limits of components.

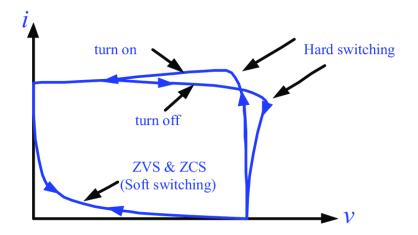

Power loss as heat dissipation in semiconductor devices is observed in two forms; the first one is the conduction loss when the device is operating in the saturation region (ON state), where the current flowing through the device will generate Joule effect losses due to the non-ideality of the channel having a non-null resistance value. This factor can be minimized in a technological approach, by selecting better devices. The second one are the switching losses, which happen at the transition between states of a semiconductor device, The ON and OFF state are low power dissipating working points, but the trajectory in the I-V characteristic of the device when transitioning from one point to the other defines the switching losses.

Implementing power conversion with high operating frequencies to enhance power density comes with its challenges, higher operating frequency introduces increased switching and magnetic losses, limiting the efficiency behavior at high frequencies.

Hard and soft switching are different techniques for going from an ON state to an OFF state and vice-versa, each one with a characteristic trajectory between the two working points. In Fig. 3.1, these different trajectories can be observed. In Figs. 3.2 and 3.3, the trajectories can be seen as a function of time for the current and voltage, and how the overlap of non-null values produce power dissipation.

The time spent during the trajectories of high dissipation is undesirable, but unavoidable due to the reactive components present in the physical architecture of power semiconductor devices, which add these disadvantageous dynamics to the device.

Figure 3.1: Hard and soft switching I-V trajectories

Figure 3.2: Typical hard switching waveforms

Figure 3.3: Typical soft switching waveforms

Another important characteristic is that, in most applications, hard switching causes rapid changes in current over short time intervals, resulting in significant Electromagnetic Interference (EMI) [18]. Soft switching techniques aim to shape the current waveform to reduce the rate of change of current  $(\frac{di}{dt})$ , thereby minimizing EMI and enabling a more robust and EMI-compliant design.

Soft-switching techniques are primarily based on shaping the current and voltage waveforms to enable smoother transitions over time. This has two main benefits: it reduces EMI by avoiding abrupt changes in current and voltage, and it intrinsically lowers switching losses. At turn-on, the current starts from or near zero and rises smoothly, while at turn-off, the current tends to decrease gradually to zero. These controlled transitions minimize the overlap between voltage and current during switching events, significantly reducing energy dissipation.

#### **3.1.2** General architecture of resonant power converters

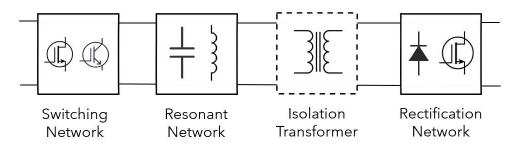

Resonant power converters are a type of high-frequency uni-directional power converter in which resonance is exploited to shape the current waveform in order to achieve soft-switching. Current shaping is achieved by employing auxiliary circuits, which are implemented as a resonant network. These circuits introduce resonance into the system, enabling smooth transitions in current and voltage. Various resonant techniques have been developed for soft switching, including quasi-resonant (QR) methods, series, parallel, and series-parallel resonance, multiresonant (MR) approaches, and resonant-transition (RT) techniques [18]. Each method is designed to address specific power and frequency ranges while optimizing switching performance.

The general architecture of a resonant power converter can be observed in Fig. 3.4. It is worth noting that architectures for resonant converters exist with and without the presence of an isolation transformer.

Figure 3.4: General architecture of a resonant power converter

Resonant techniques are particularly advantageous in high-frequency applications

where conventional hard-switching circuits would suffer from excessive switching losses and EMI. These approaches leverage the natural oscillatory behavior of LC networks to shape the circuit waveforms producing soft switching without the need for complex control schemes. Additionally, they allow designs to achieve high efficiency across a wide range of operating points [19].

While many resonant techniques exist, their applicability depends on the design goals and constraints of the power converter. For instance, quasi-resonant circuits are simpler and suitable for low-to-moderate power applications, whereas multiresonant and resonant-transition approaches can handle higher power levels with greater flexibility. The choice of topology also impacts component sizing, circuit complexity, and cost.

The LLC resonant power converter, which will be analyzed in detail in a subsequent section, exemplifies the advantages of current shaping and resonance. Its ability to achieve zero-voltage switching (ZVS) and adapt to varying load conditions has made it a popular choice for high-efficiency, high-frequency applications.

Achieving this soft-switching scheme through resonance without the need of dedicated control schemes is a great advantage in terms of ease of implementation. However, the introduction of resonance in a circuit derives three main challenges:

- Increased component stress, mainly in the resonant network components, as in a resonant circuit voltage levels can surpass the ones of the input.

- The mathematical model describing the circuit operating in several working points is complex, plenty of architectures present transcendental descriptions that have to rely in numerical analysis [20].

- Paired with the previous point, the introduction of resonance creates intricate gain relationships with the operating frequency and loading of the system. Having a wide range of working points, both in terms of gain regulation and load value create a challenging scenario for the design.

## 3.2 The LLC Topology

#### 3.2.1 Architecture structures analysis

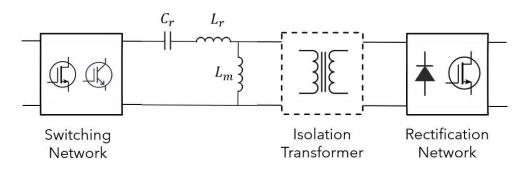

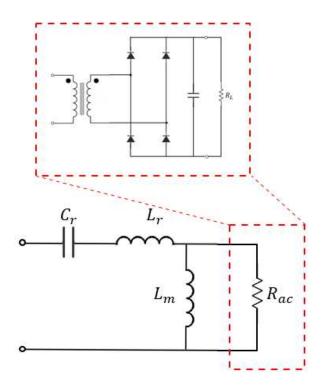

The LLC topology employs a specific resonant network which categorizes this type of resonant power converter as a multi-resonant power converter. The resonant network can be pictured in a modified version of Fig. 3.4 as seen in Fig. 3.5. It presents a series resonant tank paired with a shunt inductance; this architecture is referred as multi-resonant as the series resonance between  $L_r$  and  $C_r$  can happen, as well as the series resonance between  $L_r + L_m$  and  $C_r$  can happen, the later one being load dependent, this aspect will be covered further in this work.

Figure 3.5: The LLC network in the general resonant power converter architecture

This specific topology is commonly used from low to high power applications, it is attractive for several factors:

- Its multi-resonant behavior creates a gain characteristic capable of achieving wide gain regulation with simple frequency modulation on the switching network, depending on the loading conditions.

- When implementing the isolation transformer, it allows to integrate the inductances from the resonant network directly into the transformer. However, this comes with a much increased complexity in the design, but with the possibility to cut on costs and improve efficiency. This aspect will be deeply analyzed in Chapter 5.

- Isolation can be achieved with the implementation of the transformer, although this work will not take advantage of this feature for achieving isolation of the system, but to be able to generate the IPOS configuration.

- The ability to achieve soft-switching, in particular Zero-Voltage-Switching (ZVS) in the switches from the switching network and Zero-Current-Switching (ZCS) in the diodes from the rectification network present the possibility for a high-efficiency conversion system.

- Reduced EMI is achieved due to the sinusoidal current waveform developed by the resonant network.

The switching network sourcing the LLC network is usually implemented as a half-bridge or full-bridge square-wave inverter. The technology of the employed switches is decided according to the power to be processed by the system as well as the operating frequency and maximum reverse voltage to handle. A guideline from Infineon can be seen for selecting switches technology in Fig. 3.6.

Figure 3.6: Switches technology selection based on power and frequency

The architecture analyzed in this work is intended for power ranging from 50-680W and frequencies around 25-200kHz. Si MOSFETs are selected for this application for their capabilities for this application while maintaining an idea of cost reduction, as the other technologies are more expensive while not providing gamechanging improvements. GaN technology offers better switching performance, but the realization of soft-switching makes this characteristic not particularly interesting, as well as considering that for the most typical power extraction scenarios, the currents through the switches is considerable, making conduction losses more important than switching losses. SiC technology is intended for applications with high reverse voltages, with the disadvantage of presenting greater conduction losses.

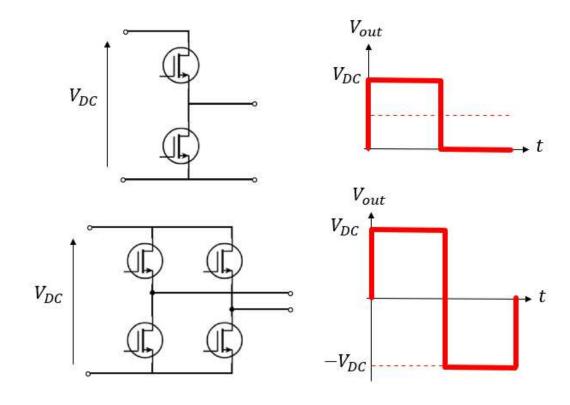

In terms of which square-wave inverter topology is chosen, a description on their main differences can be found in Table 3.1, where magnitudes are referred relative to the full-bridge variant. Each topology can be seen in Fig. 3.7. The half-bridge configuration outputs a square-wave with a DC offset of  $\frac{V_{DC}}{2}$ , in many applications this can cause problems such as core saturation of the further transformer, however, in the LLC topology this is not a problem due to the resonating capacitor also working as a DC blockage.

For this application of relatively high-power, the full-bridge configuration is chosen, primarily for the great drawback of halving the available voltage of the half-bridge configuration; having to compensate this issue with more turns in the transformer results in large losses in the copper of the winding.

The isolation transformer is of course used in this application, need for isolation in the proposed architecture has been introduced in Chapter 2, Section 2.2.1. It will also provide the ability to establish the intrinsic gain of the power converter at

Figure 3.7: Half and full-bridge topologies

| Parameter                                         | Full-bridge | Half-bridge |

|---------------------------------------------------|-------------|-------------|

| Output peak voltage                               | x1          | x0.5        |

| Number of switches                                | x1          | x0.5        |

| $I_{rms}$ through switches                        | x1          | x2          |

| Conduction losses                                 | x1          | x1          |

| Switching losses                                  | x1          | x0.5        |

| Reverse voltage                                   | x1          | x1          |

| Number of turns needed<br>(transformer secondary) | x1          | x2          |

Table 3.1: Half-bridge characteristics relative to Full-bridge

resonance, an aspect crucial for achieving the intended gain profile of the system, this will be further studied in the next sections.

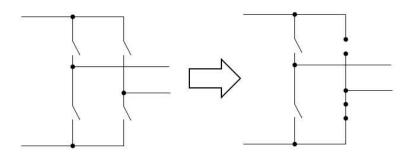

For the secondary side of the transformer and rectification network, several architectures have been proposed ranging from asynchronous to synchronous rectification, as well as different topologies for doubling and even quadrupling the voltage. Many architectures also implement topology morphing in the rectification circuit, allowing for multi-modes controlled often by the fixed state (ON/OFF) of semiconductor switches [21].

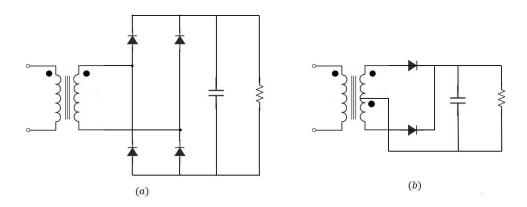

Asynchronous rectification was chosen for this work, trading-off slightly efficiency for reduction of cost and simplification of the control scheme. Approaches with full-wave rectification, both with center-tapped transformer (2 diodes) and full secondary winding (4 diodes) are showed in Fig. 3.8. An approach with topology morphing was also proposed to switch between normal rectification and a Voltage-Doubler-Rectifier (VDR) for aiding the wide gain regulation range, which was later discarded for increasing the cost and complexity of the system.

At the output of the rectification stage, a ripple filtering capacitor is introduced to smoothen the voltage waveform, this filtering effect also serves for the already mentioned decoupling purpose in the case of the first stage output capacitor, as the mismatch in operating frequency between stages will imply difference in the current waveforms. In this way, this "linking" capacitor acts as a buffer between the two stages.

Figure 3.8: Different architectures for full-wave rectification. (a) Full secondary winding, (b) Center-tapped secondary winding

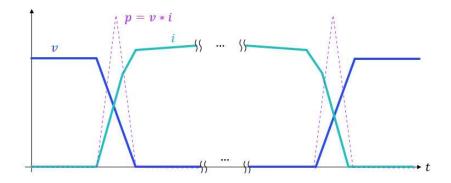

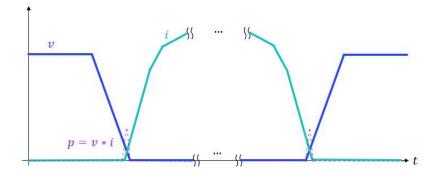

Both options with center-tapped transformer and full secondary winding transformer were employed. The criteria for the selection between both architectures can be seen in Table 3.2, where the characteristics of splitting the winding have been written relative to using the full secondary winding. When analyzing a quadratic converter like the one proposed in this work, processing a relatively constant power (ignoring for this idea the converter losses) implies that in zones where voltage is large, current should be low, and vice-versa, due to P = V \* I and power being conserved. The first converter produces the first step-up in gain, the voltage being still relatively low in this section makes the current level high, making a center-tapped approach better sparing two diode losses, and although having twice the voltage stress on the diodes, the voltage is still low in this section. This concept of different stresses sections in step-up quadratic converters is illustrated in Fig. 3.9.

| Parameter                 | Full secondary<br>winding | Center-tapped<br>secondary winding |

|---------------------------|---------------------------|------------------------------------|

| I <sub>rms</sub>          | x1                        | $X\frac{1}{\sqrt{2}}$              |

| Number of diode losses    | x1                        | x0.5                               |

| Number of secondary turns | x1                        | x2                                 |

| Diode reverse voltage     | x1                        | x2                                 |

Table 3.2: Full secondary winding versus center-tapped secondary winding

Figure 3.9: Voltage and current stress across a step-up quadratic power converter

With each block from the resonant converter with LLC network introduced, a diagram of the final circuit architecture to be studied can be presented. In Fig. 3.10, the resonant power converters are proposed in the previously described block diagram, while in Fig. 3.11, the final converter is presented in the form of the schematic, with the Pass-Through converters highlighted.

Figure 3.10: Resonant power converters in the proposed architecture

Figure 3.11: Schematic of the proposed converter. PTC: Pass-through Converter.

#### **3.2.2** First Harmonic Approximation

As mentioned in the first section of this chapter, the introduction of a resonant network creates intricate relationships between the gain regulation capabilities and the frequency of operation and load condition. The aim of this section is to propose a model that simplifies the working principle of the LLC resonant power converter to cut difficulty in the design phase, providing a mathematical tool for evaluating the gain regulation of the system.

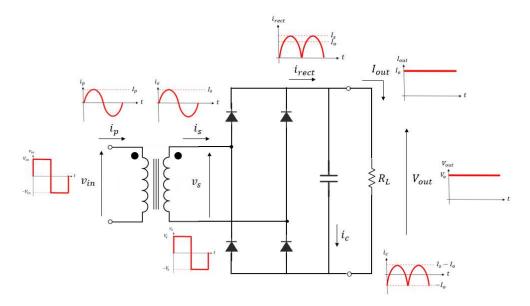

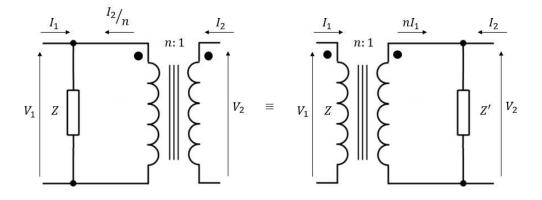

The First Harmonic Approximation (FHA) method is a widespread simplified model for analyzing resonant power converters based on the assumption that power transfer across the converter is essentially due to the fundamental Fourier series components of current and voltage [22]. This approach allows to find an equivalent simplified circuit for the resonant converter where linear AC analysis can be carried out in order to study gain at different frequencies and load scenarios, as well as to define necessary conditions in terms of impedance for achieving the desired soft-switching.

In order to derive the FHA model, the first step is to assume the full-bridge inverter as an ideal supply generating a square-wave voltage form with peak voltage  $V_{in}$  (DC input voltage) and frequency of operation  $f_{sw}$ , achieved by driving ON and OFF the MOSFETs alternately in pairs, with a 50% duty cycle without overlap. This voltage source will be the input to the final simplified network. This periodic square-wave with null average value can be represented in Fourier series as seen in Eq. (3.1).

$$v_{in}(t) = \frac{4V_{in}}{\pi} \sum_{n=1}^{\infty} \frac{1}{n} \sin(n\omega_{sw}t)$$

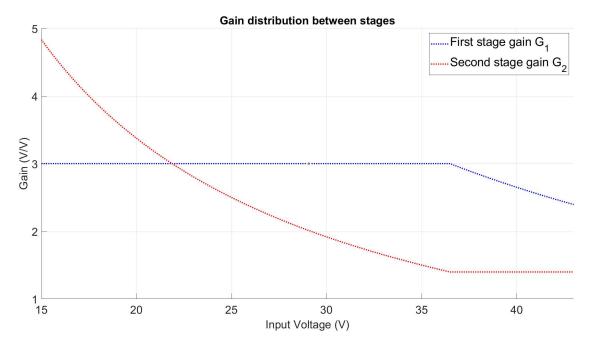

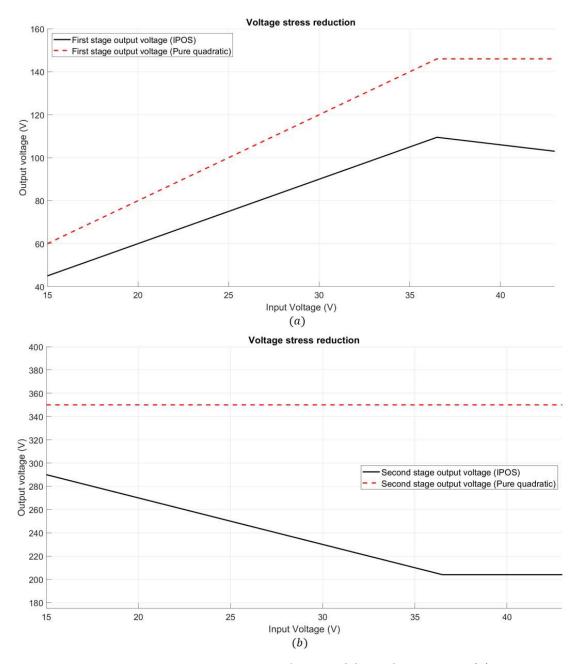

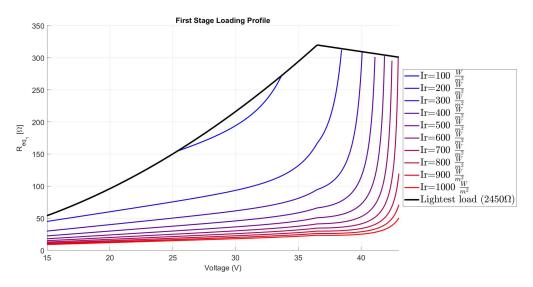

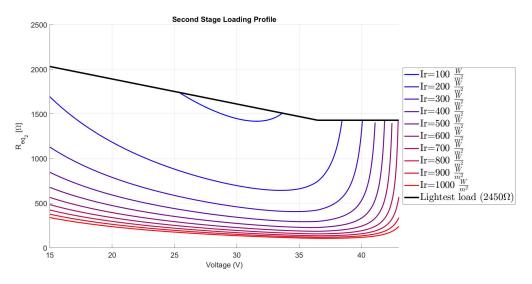

(3.1)