#### Politecnico di Torino

Corso di Laurea Magistrale in Mechatronic Engineering A.a. 2023/2024 Sessione di Laurea Dicembre 2024

## Design and characterization of a modular GaN-based power stage for automotive applications

Relatori:

Prof. Claudio Sansoè Dott. Ing. Maurizio Tranchero Candidati:

Corrado Sudano

## **Abstract**

This thesis presents the design and characterization of a modular power stage using Gallium Nitride (GaN) transistors for automotive three-phase inverter applications. The project was carried out as an internship at Ideas & Motion s.r.l, in collaboration with the Politecnico di Torino, with the aim of creating an efficient, compact and reliable inverter system suitable for high-power demands in electric vehicles. GaN technology was selected due to its high voltage capability, fast switching speed and superior efficiency compared to traditional silicon-based systems, making it ideal for the rigorous requirements of automotive power electronics. The work begins by examining the technological and environmental motivations driving the electrification of transportation, as well as the fundamental principles of power conversion and the advantages of widebandgap devices. A detailed breakdown of the GaN-based inverter follows, describing the individual subsystems and their integration within overall design. The focus then shifts to the design process, covering critical decisions in component selection, circuit architecture and PCB layout. Finally, the testing phase, where the inverter's performance is validated, is discussed to assess its operational stability, efficiency and suitability for automotive applications. This study combines theoretical analysis with practical implementation to showcase the potential of GaN technology to meet the stringent demands of automotive systems. The results highlight the inverter's capability to manage efficiently high voltage and high current levels, contributing to the broader transition towards sustainable electric mobility.

## **Contents**

| Introduct   | tion                               | 5  |

|-------------|------------------------------------|----|

| Electrifica | ation of transportation            | 9  |

| 2.1         | Motivations                        | 10 |

| 2.2         | Power conversion                   | 12 |

| 2.3         | Wide band-gap devices              | 18 |

| Study of    | a GaN-based inverter power stage   | 23 |

| 3.1         | Specifications                     | 24 |

| 3.2         | High-level partitioning            | 27 |

| 3.2.        | 1 Power Stage                      | 28 |

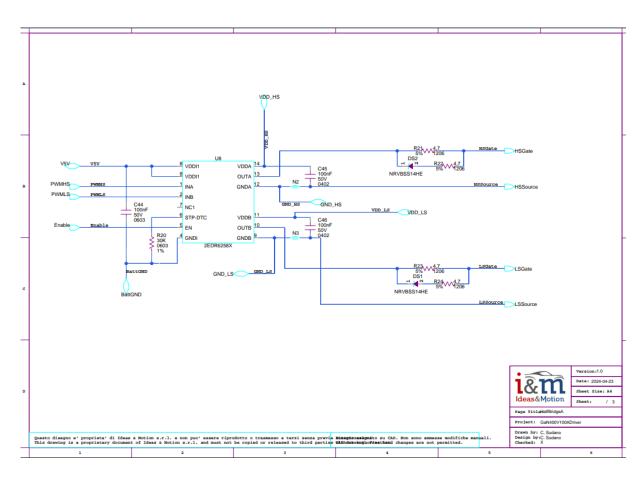

| 3.2.        | 2 Gate driving circuit             | 30 |

| 3.2.        | 3 Control system                   | 32 |

| 3.2.        | 4 Sensors                          | 33 |

| Design of   | f a GaN-based inverter power stage | 37 |

| 4.1         | Schematic                          | 37 |

| 4.1.        | 1 3-phase bridge                   | 37 |

| 4.1.        | 2 Gate driving circuit             | 41 |

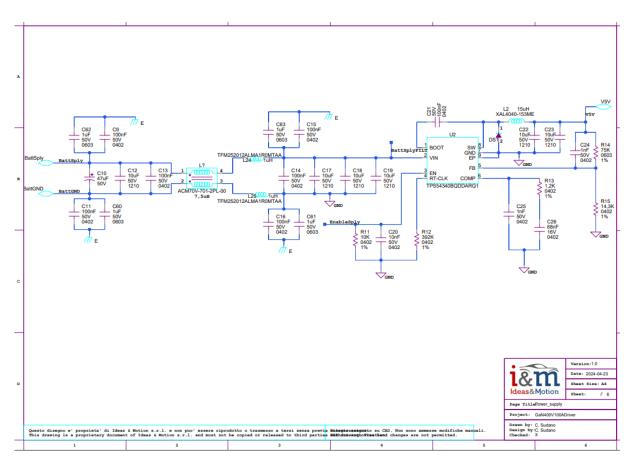

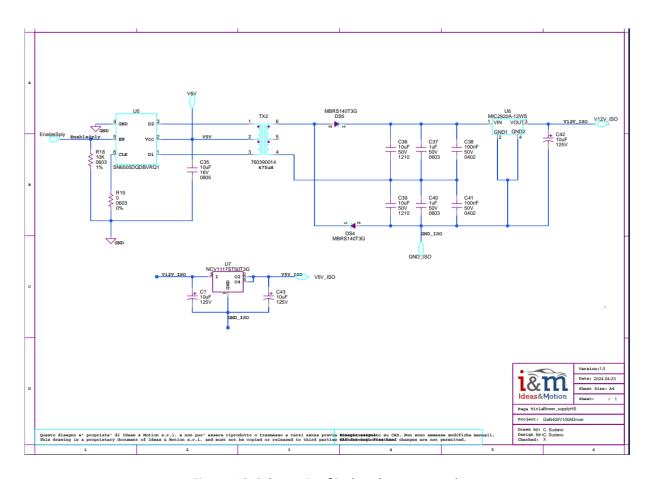

| 4.1.        | 3 Power supply                     | 46 |

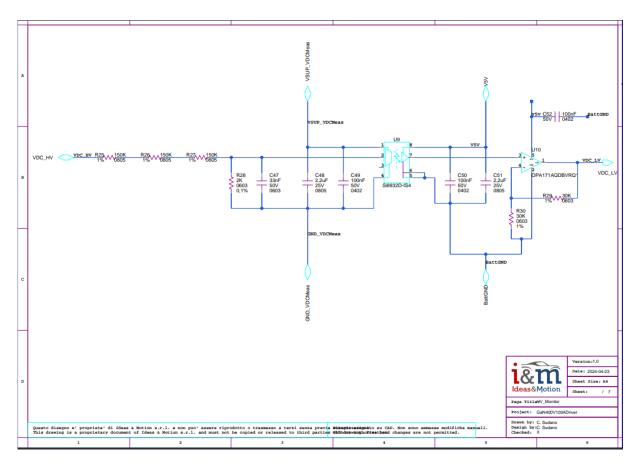

| 4.1.        | 4 High-voltage monitor             | 52 |

| 4.1.        | 5 Temperature monitor              | 54 |

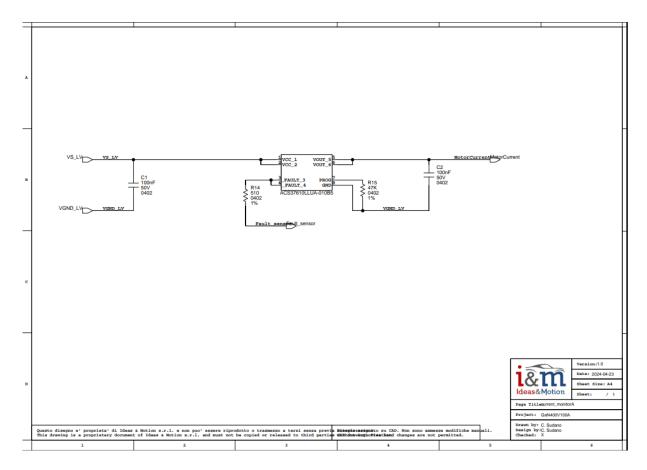

| 4.1.        | 6 Current sensor                   | 56 |

| Testing     |                                    | 59 |

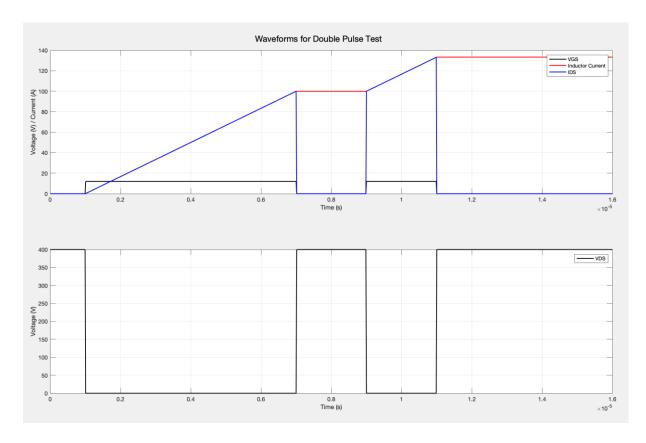

| 5.1         | Double-Pulse Test                  | 59 |

| Conclusio   | on                                 | 71 |

| Dibliogra   | nhy                                | 72 |

### Chapter 1

## Introduction

Inverters are a core technology in power electronics, as they convert direct current (DC) to alternating current (AC). This task is very important in numerous applications, including industrial power systems, and is becoming even more pertinent in the newly emerging areas of electric vehicles (EVs) and hybrid electric vehicles (HEVs). The importance of inverters has only grown in modern energy systems due to the greater emphasis on energy efficiency and the global move towards sustainable technologies. In particular, electric mobility has become a prime target for innovation, owing to the pressing need to lower greenhouse gas emissions and lessen reliance on fossil fuels. Therefore, the advancement of high-performance inverters has become a key pursuit in meeting the objectives of compactness, efficiency and reliability of electric(s) vehicle (EV) and hybrid electric vehicle (HEV) powertrains.

Inverter for EV and HEV applications must meet several demanding requirements. These consist of matching high efficiency over a wide range of loads, high energy density for the compaction of the power supply device, and safe operation under severe thermal and electrical stress. In addition, new opportunities in next-generation inverters designed with advanced semiconductor materials have been emerging. However, these benefits come with new challenges in terms of topology design, thermal management and control strategies that need to be overcome to meet their potential

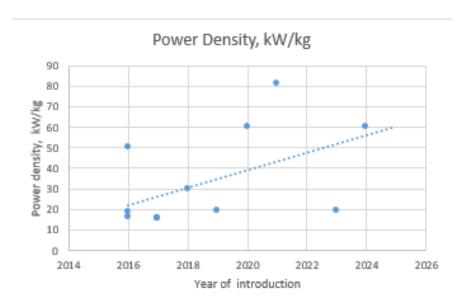

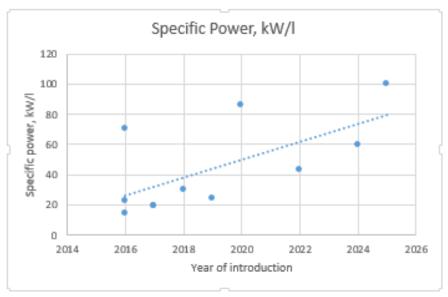

For this reason, the research community and industry standardize is focusing on Key Performance Indicators (KPIs) to evaluate and compare inverter designs. These measurements provide a consistent basis to quantify and compare the performance of inverters with respect to power, efficiency, size and reliability. Among these, the significant are: **power density** (kW/kg), which is a measurement of how much power can be delivered in relation to the physical weight of the inverter; and **specific power** (kW/l), which measures power output relative to package volume, such as when comparing designs and technologies.

Power density, measures how much power an inverter can produce compared to its mass. This is especially critical in applications like EVs and HEVs, as reducing the mass of a single component can directly improve system efficiency and range. Reducing the mass of power electronics allows manufacturers to optimize energy consumption and recover available payload volume for other key components such as batteries or structure reinforcements.

On the other hand, specific power measures the amount of power that an inverter can provide for a specific amount of physical space. This metric indicates the compactness of the design, which is a crucial aspect in automotive applications which where the space is very limited. Key to achieving these ambitious goals will be using a higher degree of specific power to allow the engineer to integrate the inverter easily into vehicle architectures without altering the design to a great extent or needing major changes to package bulky power electronics. One of the main challenges is achieving a compromise between high specific power and effective thermal management, as more compact designs can put more strain on heat dissipation.

Table 1: Timeline of inverter technologies highlighting advancements in specific power and power density [1], [2], [3], [4], [5], [6], [7], [8], [9], [10], [11]

| Year       | Author            | Title                                                        | Power    | Specific |

|------------|-------------------|--------------------------------------------------------------|----------|----------|

|            |                   |                                                              | Density, | Power,   |

| <b>↓</b> Î | ▼                 | ▼                                                            | kW/kg ▼  | kW/l ▼   |

| 2016       | Yamagichi         | Design and Evaluation of SiC-Based High Power                | 50       | 70       |

|            |                   | Density Inverter, 70kW/liter, 50kW/kg                        |          |          |

| 2016       | Cadillac CT6 PHEV | Compact and High Power Inverter for the Cadillac CT6         | 16,0     | 22,6     |

|            |                   | Rear Wheel Drive PHEV                                        |          |          |

| 2016       | BMW i3            |                                                              | 18,5     | 14,1     |

| 2017       | Opel Ampera       |                                                              | 15,6     | 19,2     |

| 2017       | Chevrolet Bolt    |                                                              | 15,6     | 19,2     |

| 2017       | Wijenayake        | Design of a 250 kW, 1200 V SiC MOSFET-Based                  | 15,6     |          |

|            |                   | Three-Phase Inverter by Considering a Subsystem              |          |          |

|            |                   | Level Design Optimization Approach                           |          |          |

| 2018       | Tesla Model 3     |                                                              | 30,0     | 30       |

| 2019       | Audi E-Tron       |                                                              | 19,0     | 24       |

| 2020       | Van Adamnson      | An 800-V High-Density Traction Inverter – Electro-Thermal    |          | 85,7     |

|            |                   | Characterization and Low-                                    |          |          |

|            |                   | Inductance PCB Bussing Design                                |          |          |

| 2020       | Wu                | An Optimized Silicon Carbide based 2×250 kW Dual             | 60       |          |

|            |                   | Inverter for Traction Applications                           |          |          |

| 2021       | Sato              | High power density inverter utilizing SiC MOSFET and         | 81       |          |

|            |                   | interstitial via hole PCB for motor drive system             |          |          |

| 2022       | Al hamoud         | A High-Density 200-kW All Silicon Carbide Three-             |          | 43,0     |

|            |                   | Phase Inverter for Traction Applications                     |          |          |

| 2023       | Zhao              | Design and Optimization of 2×211-kW SiC-Based                | 19,5     |          |

|            |                   | Aircraft Propulsion Inverter System                          |          |          |

| 2024       | Forte             | High Power-Density Design Based on WBG GaN Devices for       |          | 59,6     |

|            |                   | Three-Phase Motor Drives                                     |          |          |

| 2024 Zhen  | Zhen              | A Very High- Power Density Multilevel Inverter Using Silicon | 60,0     |          |

|            |                   | Carbide (SiC) Commercial-Off- The-Shelf (COTS) Parts         |          |          |

| 2025       | U.S DRIVE         | Electrical and electronics techical team roadmap             |          | 100,0    |

|            | Partnership       |                                                              |          |          |

These combined metrics offer a comprehensive approach to ensure that inverter designs are efficient and practical. They are important because they offer the ability to act as anchor points for literation comparison of state of the art systems and also to act as a basis for the creation of more advanced systems that are better performing and better optimizing. It is fundamentally difficult to improve both power density and specific power, as this requires a delicate balancing act between material characteristics, circuit topologies, thermal management, and system reliability. Optimizing these platforms is a truly multidisciplinary endeavor, combining improvements in wide bandgap semiconductors, cooling methods, and packaging techniques, solidifying their place in the future of power electronics.

The accompanying graphs (Figure 1 and Figure 2) illustrate the trends in literature of these key performance indicators for three-phase inverters as reported in the Table 1.

Figure 1: Power density trend of inverters

Power density has improved steadily over the years as well, with modern inverter designs now approaching 80 kW/kg. These impressive advances show that the industry can manage to substantially decrease the mass of inverter systems while keeping or raising their power output. Central to this progress has been the adoption of new semiconductor materials such as gallium nitride (GaN) and silicon carbide (SiC), which boast superior properties compared with conventional silicon-based technologies. These wide bandgap (WBG) materials permit higher efficiency, lower switching, lower conduction losses and smaller designs, resulting in lighter and more efficient inverter designs.

Figure 2: Specific power trend of inverters

Likewise, specific power has made significant strides with the most recent inverters aimed for 100 kW/l by 2025. Apart from the new materials, sophisticated cooling solutions have been crucial in reaching these specific power values. In regard to more compact designs operating on high power density, we have successfully been able to manage the added heat with the help of liquid cooling systems, integrated heat sinks, and better thermal interfaces. Through innovative thermal management strategies, inverters can be made smaller while still operating smoothly in spite of demanding conditions, which is necessarily the case with electric and hybrid vehicle applications.

In conclusion, this introduction indicates that power density and specific power are extremely important criteria to rate three-phase inverters for EV and HEV applications. The aim of this thesis is to contribute to the development of inverter technology with GaN-based designs that extend beyond conventional levels in terms of efficiency, size and reliability. The upcoming chapters are focused on the theory behind, the design and experimental implementation of the introduced inverter and will prepare the grounds for comparing it with the state of art products.

## Chapter 2

# **Electrification of transportation**

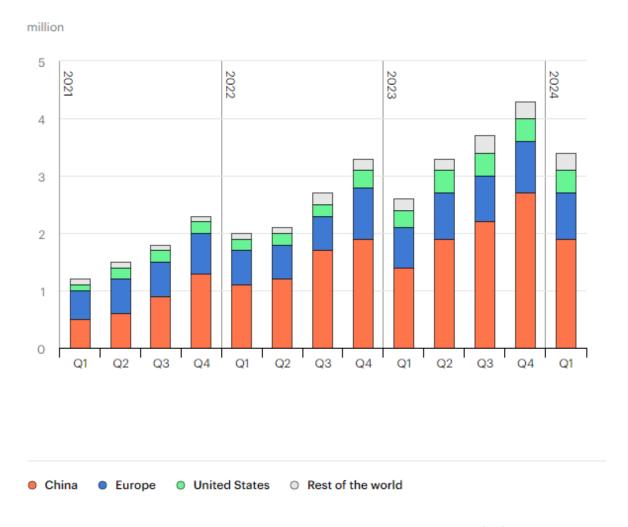

Transportation electrification has become one of the most critical elements of the global energy transition due to the requirement to decarbonize mobility, which accounts for roughly 25% of global CO<sub>2</sub> emissions. In response to this challenge, countries across the planet are implementing policies to simultaneously curb the number of internal combustion engine (ICE) vehicles on the road and bring about the adoption of EVs in the hopes of reaching climate goals. According to the International Energy Agency's Global EV Outlook 2024 report, worldwide EV sales are set to surpass 17 million units in 2024, more than 20% of total car sales. This is a major increase from earlier years, signalling that EVs are starting to transition from being niche products to something which has become more mainstream in many markets, particularly China, Europe and USA. China is the world leader in EV adoption, with more than 60% of electric car sales in 2023, thanks to strong government policies and heavy investments in EV infrastructure and manufacturing. Europe also sees strong growth, expecting electric cars to be 25% of new car sales by 2024, while the U.S. will see that number climb over 11% also in 2024. Transmission to these territories is prodded by severe CO2 outflow guidelines and systems that persuade shoppers and producers to embrace electric mobility. The European Union intends to prohibit the sale of new gasoline and diesel cars by 2035, while the U.S. Inflation Reduction Act (IRA) offers massive subsidies for EV manufacturers and buyers, driving local production and adoption. Nevertheless, growth in EVs in developing markets is slower. Although EV sales have surged in countries such as Vietnam (up 15%) and Thailand (up 10%), many developing countries still have hurdles to overcome, including inadequate charging infrastructure and high upfront costs. For this to enable global electrification to succeed, these markets will require a more targeted policy approach and investment [12].

Figure 3: Quarterly electric car sales by region, 2021-2024 [12]

#### 2.1 Motivations

Environmental, economic and technological factors all drive the switch to EVs. These factors underscore the urgent need to decarbonize transportation, improve energy efficiency, enhance energy security and generate new economic opportunities in a period of growing environmental consciousness. On the social front, electrifying the transport system, particularly in urban areas, can lead to a better quality of life, evidenced through reduced noise pollution and improved air quality. This leads to healthier living conditions and reduced public health costs related to respiratory and cardiovascular illnesses.

One of the best reasons to electrify transportation is to decrease the level of greenhouse gases, particularly carbon dioxide (CO<sub>2</sub>), and other harmful air pollutants, particularly nitrogen oxides (NOX) and particulate matter (PM10 and PM2. 5). Internal combustion engine vehicles are major contributors to these emissions, worsening climate change and contributing to poor urban air quality.

Electric vehicles, on the other hand, do not emit any tailpipe emissions, thus directly removing local air pollutants. The one caveat is the indirect emissions generated by using electricity to charge the vehicles. Where energy systems produce electricity from renewables or low-carbon sources — nuclear, wind or solar power — the emissions reduction is significant. It also widely recognised that the greater the amount of renewable energy being fed into the grid, the more the environmental benefits of EVs would increase, even in countries that rely heavily on fossil fuel generation. Another key motive is better public health: local air pollution is expected to decrease significantly when shifting to electrification, as studies indicate that poor air quality leads to millions of premature deaths each year worldwide [13].

The improvement in energy efficiency is another strong reason for the electrification of transportation. Electric vehicles are inherently more efficient than internal combustion vehicles are. ICE vehicles, on the other hand, convert less than 30% of the fuel energy in gasoline into motion [14], but electric motors can achieve efficiencies greater than 70% [14]. That inefficiency gap is what makes EVs use drastically less energy than traditional vehicles for the same distance travelled. In addition, due to regenerative braking in electric vehicles, energy that would otherwise be wasted when slowing down can instead be reclaimed, improving the efficiency of electric vehicles even more. The reduction in required energy per unit output is all pertinent in these times of rising global energy demands and an imperative to optimise available resources. In the urban areas, the replacement of ICE vehicles with electric vehicles (e.g., buses and trams) can decrease the primary energy demand drastically. The European Commission indicated that electrified public transport systems also consume 20 to 30% less energy than conventional systems [15].

Electrifying transportation is an important part of decreasing global reliance on fossil fuels. In this moment, most chime in the dynamics of global transport depends on oil, which is a finite resource, unreliable price fluctuations and geopolitical uncertainties. Such a dependency makes the economies susceptible of energy crises and trade imbalance. Electrification provides an opportunity to de-risk the energy sources used in the transportation sector by increasing reliance on renewables such as solar, wind and hydropower. This not only lessens dependence on oil but also stabilizes international energy markets. Lower oil demand also bodes well for national energy security since states do not have to rely as much on oil-exporting countries or weather the risk of conflict or political turmoil in those areas. If current trends continue, electrification could reduce global oil demand by close to 2.5 million barrels per day by 2030 [16].

In addition to environmental benefits, transportation electrification offers to unlock numerous economic and social opportunities. At a macroeconomic level, the movement towards EVs can lead to new industries and job opportunities in sectors such as EV manufacturing, battery production and charging infrastructure development. Long-term cost decreases in energy are driven by the technological innovation related to electrification, which can also help accelerate the transition toward a more green and sustainable economy. The initial costs are higher for EVs, but their operating costs are lower because of less maintenance and cheaper electricity than gas. According to a recent Gartner report, It is expected that by 2027 EVs will be cheaper to produce relative to a comparable ICE, making it even more attractive to consumers [17].

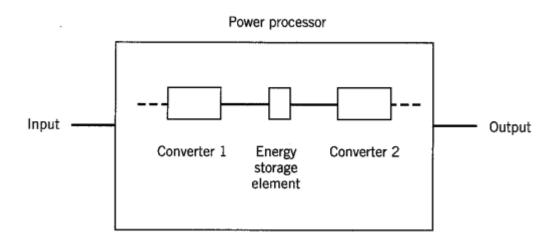

### 2.2 Power conversion

Power conversion is a necessary component of our current electronics and electrical engineering that allows electrical power to be transformed from one form to another. DC (Direct current) and AC (Alternating current) are the two basic forms of electrical power and it is through power conversion that devices are able to consume, store or generate the proper form of power when they require it. Further, the conventional power conversion devices have more than one power conversion mode, and the operation of these modes is decoupled on an instantaneous basis through storage means (capacitors and inductors). As such, a converter is the elementary building block of a power electronics system [18].

Figure 4: Power processor block diagram [18].

Power converters are broadly classified based on the types of power they convert and the techniques they use to achieve conversion. The three most common types are:

- **DC-to-DC converters**: Also known as Choppers or Chopper, are circuits that convert source direct current to a different voltage level. They are often used in applications that require a stable voltage, such as a battery-powered device, or to ensure acceptable voltage levels in renewable energy systems. There are lots of topologies but the basic are:

- 1. Step-down (Buck) converters: a Buck converter converts a higher DC input voltage to where the output is a lower DC voltage. It is frequently used in power supply unit to deliver stable voltages to microprocessor and other components. Basically, a buck converter controls the amount of energy stored in an inductor by switching a transistor ON and OFF, and then releases this power to a load at lower voltage.

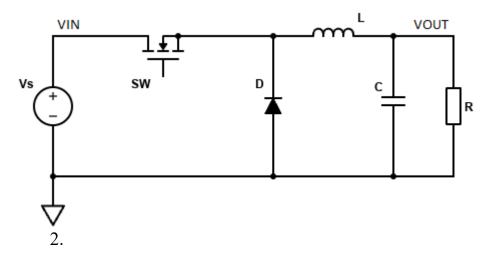

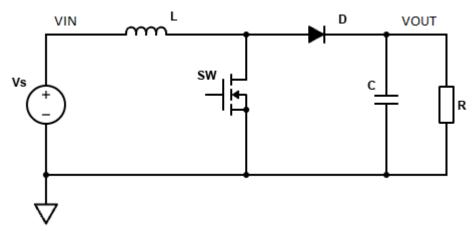

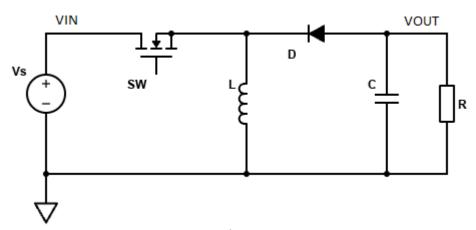

Figure 5: Buck converter

- 3. Step-up (Boost) converters: on the other hand, a Boost converter steps up a DC input voltage to a higher DC output voltage. These converters are typically used in applications such as solar power systems, where they step up the voltage from a solar panel to a level sufficient for charging batteries or being fed into the grid.

- 4. Buck-Boost converters: these converters are such type where input voltage can be increased or decreased, as per requirements. The regulator will have a DC input voltage and will output a DC voltage with an approximately equal magnitude but opposite polarity. They are flexible and serve effective in battery-operated equipment where the battery voltage changes, however, constant output voltage is required [19].

Figure 6: Boost converter

Figure 7: Buck-Boost converter

- AC-to-DC converters: Also known as Rectifiers, are used to convert alternating current into direct current. These are commonly found in power supplies for electronic devices, where AC from the grid is converted to DC for use by electronic circuits. We distinguish two basic types:

- 1. Half-Wave rectifiers: a Half-Wave rectifier passes only one half of the AC waveform and blocks the other half. This creates a pulsing DC that is usually smoothed by use of capacitors for stable operation.

- 2. Full-Wave rectifiers: a Full-Wave rectifier use both halves of the AC waveform providing a smoother DC output. These full-wave rectifiers consist of a diode bridge or center-tapped transformer. Filter circuits are widely connected to both forms of rectifiers to reduce ripple and ensure a cleaner DC output, which is a vital need for driving sensitive electronic components [20].

Circuit Configuration

Circuit Configuration

Input Voltage Waveform After Rectification

Voltage Waveform After Rectification

Voltage Waveform After Rectification Smoothing

Table 2: Full-Wave and Half-Wave rectification [20]

• DC-to-AC converters (inverters): The primary purpose of static power converters is to generate an AC output waveform from a DC power source. For sinusoidal AC outputs, it is essential to control the magnitude, frequency and phase of the waveform. Inverters are widely used in renewable energy systems, uninterruptible power supplies (UPS) and electric vehicles to convert the DC power stored in batteries into AC power suitable for driving motors or powering appliances.

Figure 8: Electrical power conversion topology [21].

They use a series of switching components and modulation methods to generate an AC waveform from a DC input. The devices with the highest incidence factor in an inverter switching are Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) and Insulated Gate Bipolar Transistors (IGBTs), which provide a variety of pros and cons in speed, efficiency and power handling.

Depending on the class of the DC input source, these converters are primarily classified into two categories as Voltage Source Inverters (VSI) and Current Source Inverters (CSI). While there are three VSI based topologies, they are the most used type since their nature is already combined as they are a voltage source, which is needed for many industrial applications. CSIs are still extensively used in medium-voltage industrial applications, especially where high-quality voltage waveform are required [21].

Inverters can be also classified based on multiple factors, including the waveform they produce, the number of phases they support and their application. For the phase, we have two main categories:

- 1. Single-Phase Inverters: Typically used in residential and light commercial applications. They convert DC into a single-phase AC output, which is suitable for powering household appliances, lighting and small loads.

- 2. Three-Phase Inverters: Commonly used in industrial applications, three-phase inverters generate AC power in three phases, which is essential for driving large motors, heavy machinery and other high-power equipment.

The output voltage can harmonics along with ripples and in best cases they are very small and hence the output waveform ideally should be a pure sine wave. DC power is drawn from the input power source by the inverter only when the load is connected to the supply. Hence, the input current is not pure DC and consists of harmonic components. Typically the performance of an inverter is evaluated on various parameters:

- 1. Harmonic factor of nth harmonic (HF $_n$ ): is a measure of individual harmonic contribution.

- 2. Total harmonic distortion (THD): is a measure of closeness in shape between a waveform and its fundamental component.

- 3. Distortion factor (DF): THD gives the total harmonic content, but it does not indicate the level of each harmonic component. If a filter is used at the output of inverters, the higher order harmonics would be attenuated more effectively. Therefore, a

knowledge of both the frequency and magnitude of each harmonic is important. The DF indicates the amount of harmonic distortion that remains in a particular waveform after the harmonics of that waveform have been subjected to a second-order attenuation. Thus, DF is a measure of effectiveness in reducing unwanted harmonics without having to specify the values of a second-order load filter.

4. Lowest order harmonic (LOH): the LOH is that harmonic component whose frequency is closest to the fundamental one, and its amplitude is greater than or equal to 3% of the fundamental component [22].

Furthermore, modulation techniques play a vital role in controlling inverter performance, demanding high efficiency and accurate and high performance output characteristics. These approaches manage the frequency, amplitude and phase of the output voltage or current by modulating the inverter's switching patterns, encapsulating the exact requirements of different applications, whether it is motor drives or renewable energy systems. Pulse Width Modulation (PWM) is one of the most commonly used modulation technique in inverter and the devices with PWM modulation are called as PWM inverters. PWM inverters removes lower order harmonics and reduce the THD content at output AC voltage. They also reduce the need for filters. The most popular modulation types used in inverters are:

- 1. Single pulse modulation: this modulation technique consists of one pulse per half-cycle, and the width of the pulse varies from 0 to  $\pi$ . By varying the pulse width, the output voltage is controlled.

- 2. Multiple pulse modulation: this modulation scheme is an extension of single pulse modulation, where several equidistant pulses are present per half cycle. The pulse width is equal in multiple pulse modulation.

- 3. Sinusoidal pulse width modulation: this is a type of multiple pulse modulation, where several pulses are present in each half-cycle. The pulse width is the sinusoidal function of the angular position of the pulse in a cycle.

- 4. Space vector modulation: the space vector modulation scheme is commonly used in inverters due to its ease of implementation. It is frequently employed in multilevel inverters [23].

## 2.3 Wide band-gap devices

A crucial step toward achieving an energy-efficient world lies in the adoption of innovative materials, such as wide band-gap (WBG) semiconductors. Energy consumption and management in buildings are heavily reliant on power electronic converters and the monitoring of indoor conditions. It is worth noting that much of the electrical power generated is eventually used only after the electrical power has been transformed several times into different currents, all of which is very wasteful and performed by power electronic converters. Semiconductors are vital for the next generation of key technologies, such as electronics, optoelectronics, communications, computing and sensing. Semiconductor device and switching frequency selection play a significant role in power converter efficiency. Semiconductor devices in power electronics converter systems play a major role in power losses during high current conduction and switching.

Considerably, high switching frequencies are required for WBG semiconductor materials to reduce switching loss and improve the power density of the converters. Therefore, power electronics innovations are crucial to minimizing the power losses in power conversion. Indeed, WBG semiconductor power devices can optimize electrical energy conversion without compromising performance and efficiency of power converters. WBG-based devices can further miniaturize power electronic components with resultant improvements in reducing system or component level costs; performance; and reliability. One of the few properties that dictate the electrical and optical behaviours of a semiconductor is the bandgap, the most important parameter when it comes to identifying a WBG semiconductor. This quantity is defined as the energy barrier which electrons have to cross to go from the valence band to the conduction band. In fact, the ferromagnetic behaviour of semiconducting materials plays an important role for the choice of power components especially in terms of energy performance, hysteresis and eddy current loss. WBG semiconductor materials have wider bandgaps (2-4 eV) compared to silicon (1-1.5 eV), offering higher power efficiency, lower overall costs, reduced size and weight, and lower energy consumption. The use of WBG material translates directly into semiconductor devices operating at high temperatures, which may cause problems for traditional silicon semiconductors with smaller bandgaps. The temperature range of semiconductor power devices is enhanced with an increased bandgap. WBG also allows electronic devices made from these materials to endure higher heat and radiation without deteriorating their electrical properties. They also show the fast switching speed, low on-state resistance, as well as higher temperature and voltage capabilities. Quicker and lower switching loss means smaller passive components and heatsinks with improved power density.

WBG semiconductor power devices outperform silicon-based devices in demanding conditions. When utilizing energy storage systems, appropriate power converters are necessary to manage energy flow during charging and discharging to maximize their full potential. Thus, the research on efficient semiconductor power electronics is of great importance to maximum energy usage of the stored energy in batteries, supercapacitors, etc [24].

Thanks to decades of developments in fabrication processes, material supply, large-scale manufacturing, and drastically reduced costs, silicon is still the element of choice for most power semiconductor device applications. It is primarily due to its technological maturity and the widespread accessibility of materials. But silicon-based devices cannot meet the advanced requirements of modern power electronics for applications with a high power density or highvoltage devices, operating at frequencies and temperatures higher than 150°C. Meanwhile, it is thought that alternatives, such as materials such as silicon carbide or gallium nitride, hold greater long term promise. Their efficiency, as well as availability of raw materials and their technologies' maturity levels, makes them attractive Contributor. Especially for power electronics, from the perspectives of device manufacturers, SiC and GaN are the most promising WBG semiconductor materials. One of the major advantages besides increasing productivity in power applications is that WBG power devices are most capable of operating at high temperatures. They provide enhanced blocking voltage, current carrying capability, and can operate at higher frequencies, power levels, and voltages. GaN-based power devices as core devices in the power conversion industry, which is essential for the operations of smartphones, computers, battery chargers, automotive systems, lighting and photovoltaics. This WBG technology provides best achievable designs for passive components, converter topologies, and thermal management when integrated into a power electronics systems. The benefits of WBG power devices make them impactful in an array of applications. So they are also good in high-power applications such as electric vehicles and other areas as they have moved beyond the limits of silicone and are designed for optimal performance in harsh environments, allowing them to be smaller, lighter, and cheaper [24].

Table 3: Material properties of Si, GaN and SiC

| Parameter                           |                        | Silicon | GaN  | SiC  |

|-------------------------------------|------------------------|---------|------|------|

| Band Gap (E <sub>g</sub> )          | [eV]                   | 1.12    | 3.39 | 3.26 |

| Critical Field (E <sub>crit</sub> ) | [MV/cm]                | 0.23    | 3.3  | 2.2  |

| Electron Mobility (μ <sub>n</sub> ) | [cm <sup>2</sup> /V·s] | 1400    | 1500 | 950  |

| Permittivity (ε <sub>r</sub> )      |                        | 11.8    | 9    | 9.7  |

| Thermal conductivity (λ)            | [W/cm·K]               | 1.5     | 1.3  | 3.8  |

Band gap of a semiconductor is related to the strength of the chemical bonds between the atoms in the lattice. These stronger bonds mean that it is harder for an electron to jump from one site to the next. Among the many consequences are lower intrinsic leakage currents and higher operating temperatures for higher band gap semiconductors. The stronger chemical bonds that cause the wider band gap also result in a higher critical electric field needed to initiate impact ionization, thus causing avalanche breakdown. The voltage at which a device breaks down can be approximated with the formula [25]:

$$V_{BR} = \frac{1}{2} w_{drift} \cdot E_{crit}$$

(1)

The breakdown voltage of a device, therefore, is proportional to the width of the drift region. In the case of SiC and GaN, the drift region can be 10 times smaller than in silicon for the same breakdown voltage. In order to support this electric field, there need to be carriers in the drift region that are depleted away at the point where the device reaches the critical field. This is where there is a huge gain in devices with high critical fields. The number of electrons (assuming an N-type semiconductor) between the two terminals can be calculated using Poison's equation [25]:

$$\mathbf{q} \cdot \mathbf{N}_{\mathrm{D}} = \varepsilon_{0} \varepsilon_{\mathrm{r}} \cdot \frac{\mathbf{E}_{\mathrm{crit}}}{\mathbf{W}_{\mathrm{drift}}} \tag{2}$$

In this equation, q is the charge of the electron,  $N_D$  is the total number of electrons in the volume,  $\varepsilon_0$  is the permittivity of a vacuum measured in farads per meter and  $\varepsilon_r$  is the relative permittivity. It can be seen that if the critical field of the crystal is 10 times higher, the electrical terminals can be 10 times closer together. Therefore, the number of electrons in the drift region can be 100 times greater. This is the basis for the ability of GaN and SiC to outperform silicon in power conversion [25].

The theoretical on-resistance of this majority-carrier device is therefore [25]:

$$R_{DS(On)} = \frac{W_{drift}}{q \cdot \mu_n \cdot N_D}$$

(3)

Combining Equation 1, Equation 2 and Equation 3, we obtain:

$$R_{DS(on)} = 4 \cdot \frac{V_{BR}^2}{\varepsilon_0 \cdot \varepsilon_r \cdot \mu_n \cdot E_{crit}^3}$$

(4)

Where  $\mu_n$  is the mobility of electrons [14]. The material dependent parameters of the Equation 4, such as relative permittivity  $\epsilon_r$ , electron mobility  $\mu_n$  and critical field  $E_{crit}$  are included into the so called Baliga's figure of merit (BFoM) for power devices. Therefore, basically the BFoM is a measure for the material dependence of the on-resistance of unipolar devices [26].

High-voltage (HV) power semiconductor switches play vital role in any power conversion system. Silicon-based insulated gate bipolar transistors (IGBTs) are widely used because they are now mature, and there is no alternative available. While incremental efficiency improvements can be made by using Si IGBTs in conjunction with SiC diodes, the resulting gains are marginal. Si IGBTs exhibit intrinsic limitations in operating frequency, switching speed, and high temperature operation, in addition to poor performance at low current. Furthermore, in high-frequency applications such as AC-to-DC power factor correction (PFC) and DC-to-DC power conversion, Si super-junction (SJ) technology is dominant. Si-based devices, on the other hand, are constrained in size or cost owing to limited material capabilities at high frequencies. This is mainly caused by switching crossover losses, conduction losses and reverse recovery losses. On the other hand, wide bandgap (WBG) materials, due to their fast turn-on and turn-off switching capabilities, and low conduction losses, help to overcome reverse recovery loss and also have low switching crossover losses. Higher critical electric fields and electron mobility in WBG materials yield lower on-state resistance for high-voltage applications, leading to superior switching performance. The WBG devices are now coming to market with great potential, addressing many of the innate limitations of Si IGBT and Si SJ devices [26].

GaN FETs come in two base configurations: enhancement mode (E-mode) or depletion mode (D-mode) devices. In power conversion applications, D-mode devices are disadvantageous since, during the start-up of a power converter, the power devices must be pre-biased negatively. Failure to apply this negative bias first will cause a short circuit. A device that was E-mode would not have this limitation. •With no bias on the gate, an E-mode will be in the OFF mode and will not conduct current until a positive voltage is applied to the gate One approach to designing a single-chip enhancement-mode GaN transistor is to stack an enhancement-mode silicon MOSFET in series with a depletion-mode HEMT (High Electron Mobility Transistor) device. The depletion-mode GaN transistor gate voltage drops to near-zero volts, and it turns on, which in this circuit turns the MOSFET on with a positive voltage on the gate. The current is able to flow

through the depletion-mode GaN HEMT and the MOSFET (in series with the GaN HEMT). The application of a negative voltage between the depletion-mode GaN transistor gate and its source electrode turns the GaN device off when the voltage on the MOS gate is removed. This kind of solution for an enhancementmode GaN system is suitable when the on-resistance of the GaN transistor is relatively higher than that of the low voltage silicon MOSFET. Because onresistance grows with device breakdown voltage, cascode solutions will work best if the GaN HEMT is high voltage and the MOSFET is quite low voltage. E-mode gates are stable, but leakage currents in E-mode gates must be analyzed carefully for better performance. E-mode devices for high-voltage, high-power applications need complex drive circuitry. These applications require high gate threshold voltage and stable gate drive to prevent gate bounce and shoot-through, conditions which cannot be achieved with current E-mode technology. The cascode architecture, as an additional precaution, also ensures that the gate structure doesn't sacrifice the level of reliability that is required by automotive applications. This dependability provides a powerful and flexible tool for the high-performance power electronics sector [27].

## **Chapter 3**

# Study of a GaN-based inverter power stage

The Introduction of Gallium Nitride transistors in power electronics has significantly changed design and characteristics of modern inverters. The electrical performance advantages of GaN-based transistors— including higher breakdown voltages, improved switching speeds, and lower conduction losses— have led to heightened market acceptance of enhancement-mode devices, which are gradually superseding conventional Silicon MOSFETs in a wide range of applications. These features make GaN transistors ideal for applications where efficiency, size, and power density are key, such as electric vehicles, renewable energy systems, telecommunications, and industrial motor drives.

One of the most significant uses of GaN technology is for the design of inverters responsible for converting DC power into AC power. Inverters design contribute to various system architectures like solar power plants, EVs, UPS, etc., demanding ever-increasing efficiency, and compactness. Si-based approaches usually have slower switching speeds and increased energy loss, especially at higher frequencies. In contrast, the fast electron mobility and wide bandgap feature of GaN transistors helps to minimize switching loss, thereby helping to either minimize loss or to increase switching frequency. Higher efficiency of GaN-based inverters also means less stringent thermal management. Si-based designs rely on bulky heat sinks and cooling systems in order to dissipate the substantial heat generated by higher losses. GaN devices, by their lower loss operation, dissipate less heat which in turn simplifies cooling solutions. Not only does this simplify the system design, but it also leads to even lower size and cost reductions. In spite of the many benefits of GaN transistors, they also introduce challenges, most notably with driving and controlling these high-performance devices. Gate control for GaN transistors is often more complex than that of MOSFETs, so they require a gate driver with integrated fast switching and high voltage / gate current drive capability under high power conditions. These drivers should also prevent the GaN transistors from overvoltage and overcurrent that could result in damage to the devices. In addition, GaN transistors do achieve better performance with higher switching frequencies, but it also means you need to pay attention to the layout and design considerations like minimising parasitic inductances and thermal management.

In this chapter, we will explore the GaN-based inverter, focusing on power stage specifications and high-level partitioning.

## 3.1 Specifications

It is important to consider the key specifications of a GaN-based inverter as all of these specifications will ultimately dictate the performance, reliability and suitability of the Galium Nitride-based inverter for the particular application. This section describes the informed spec for a GaN inverter such as input & output voltage, power, switching frequency, efficiency, thermal management and electromagnetic interference considerations. GaN-based inverters facilitate a variety of performance advantages; however, the design process comprises of a series of critical specifications, which must be calculated to ensure that the device will achieve its target operational parameters.

Ambient Temperature °C 65

Nominal Voltage V 400

Nominal Switching Frequency Hz 20000

Maximum Switching Frequency Hz 50000

Maximum Drain Current A 150

Table 4: Inverter specifications

In this specific case, the inverter is required to operate at a nominal voltage of 400 V with a frequency not exceeding 20 kHz. However, for a worst-case scenario analysis, the performance was evaluated at a 50 kHz switching frequency, taking into account various losses and thermal considerations. The nominal voltage of 400 V is typical for high-power inverters, particularly those used in industrial applications, renewable energy systems and electric vehicle powertrains. The inverter operates at this voltage level and, therefore, must be designed for large power outputs with efficiency and reliability.

In the context of the design, three Nexperia GAN039-650NTB in parallel for each leg have been selected to produce a drain current capacity of 150 A for each phase. The device is a normally-off transistor for high power and high frequency applications, merging high voltage GaN HEMT technology with low voltage silicon MOSFET technologies, delivering state-of-the-art performance and unmatched reliability. This polymer based transistor was selected as this makes the design very efficient and helps to minimise power losses and the overall

dimensions of the inverter. These capabilities clearly separate GaN devices as the inverter technology of the future for high power and high frequency, optimizing high-performance and energy-efficient designs.

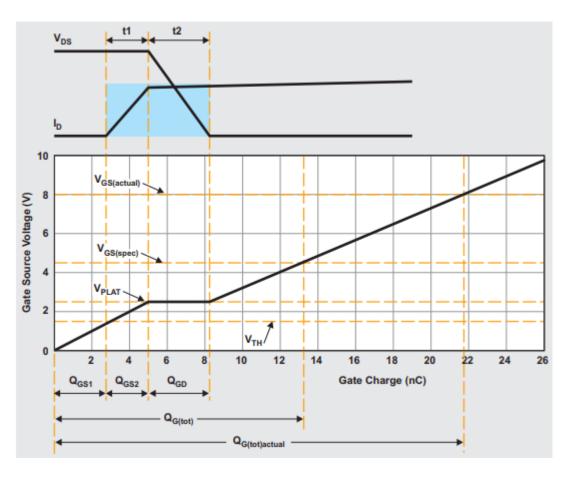

With all of these features combined with a 650 V drain-source voltage (VDS) which allows it to operate at high voltages, this device is an ideal candidate for high efficiency high voltage DC bus systems such as solar inverters or other types of industrial inverters. Maintained in high voltage at excellent performance, large voltage level is a major advantage to the high power application for this device. In addition, the low R<sub>ds(on)</sub> (typically 33 mΩ at 25 °C) offers minimized conduction losses. At higher temperatures like 150 °C, the resistance is still efficient at 73  $m\Omega$ . This low resistance help minimize energy lost during operation, making way for better overall system efficiency. The gate-source voltage (V<sub>GS</sub>) threshold is another important parameter that describes the voltage difference between the gate and source terminals when the field-effect transistor starts to conduct, allowing current to flow. In other words, it serves as the rank that signals the changeover of device state from OFF to ON. In GaN transistors, it is generally lower than conventional silicon MOSFETs, making possible fast switching speed and low power consumption. The V<sub>GS(th)</sub> is around 4 V for the GAN039-NTB: a lower V<sub>GS(th)</sub> ensures faster ON transition of the transistor, which is beneficial for devices for high frequency applications due to faster transition. Moreover, the strong gate design with ±20 V gate-source voltage (VGS) rating is a further key component of transistor reliability, especially in electrically noisy environments. This broad V<sub>GS</sub> range enables the device to withstand even sporadic, extreme over-voltage conditions without inflicting gate structure damage. This robustness is crucial to ensure stable operation in the presence of potential gate bounce, a situation that can cause undesired oscillation in the device due to rapid switching events or external electrical noise. Furthermore, the transistor's low gate charge (Q<sub>G</sub>) of 26 nC and gate-drain charge (Q<sub>GD</sub>) of just 5 nC make it ideal for fast switching transitions that minimize additional losses associated with switching. This makes it important for high frequency applications where minimal switching losses contribute to improved overall efficiency. CCPAK1212i, from its thermal component reduces hot spots and improves overall thermal performance. With a low thermal resistance, the package ensures that the device can sustain high thermal loads while still being operated at junction temperatures of up to 150 °C, a factor of paramount importance to bipolar reliability in high power applications [28].

The conduction losses in the GaN FETs are directly related to the  $R_{DS(on)}$  value and the current flowing through each device. In our case the  $R_{DS(on)}$  for each GaN FET is maximum 39 m $\Omega$  at 25 °C. For three devices in parallel, the effective  $R_{DS(on)}$  for the combined leg is reduced, which helps to lower the overall conduction losses.

The conduction losses for each leg of the inverter can be calculated as follows [29]:

$$P_{\text{COND}} = I_D^2 \cdot R_{\text{DS(on)}} = 150^2 \,\text{A} \cdot \frac{39 \,\text{m}\Omega}{3} = 292.5 \,\text{W}$$

(5)

While the inverter is designed to operate at a nominal switching frequency of 20 kHz, it is essential evaluate its performance at a worst-case switching frequency of 50 kHz. Higher switching frequencies allow for smaller passive components and reduced output filtering, but they also result in increased switching losses. Switching losses are a significant contributor to total power loss in high frequency inverters. These losses occur during the transitions between the ON and OFF states of the transistors and are directly proportional to the switching frequency.

Figure 9: Switching losses [29]

The switching losses can be estimated using the formula [30]:

$$P_{SW} = \frac{1}{2} \times V_{DS} \times I_D \times (t_{on} + t_{off}) \times f_{SW}$$

(6)

Where,  $Q_{GS2}$  and  $Q_{GD}$  depend on the time the driver gets to charge the FET and  $I_G$  is the gate current. Taking from the datasheet the values at 25 °C with  $V_{DS}$ = 400 V,  $R_{(ext)}$ = 30  $\Omega$  and  $V_{GS}$ = 10 V, we get:

$$P_{SW} = 0.5 \times 400 \text{ V} \times 150 \text{ A} \times 64 \text{ ns} \times 50 \text{ kHz} = 96 \text{ W}$$

(7)

The total losses for each leg at 50 kHz can be estimated by adding the conduction losses and the switching losses:

$$P_{TOT} = P_{COND} + P_{SW}$$

(8)

## 3.2 High-level partitioning

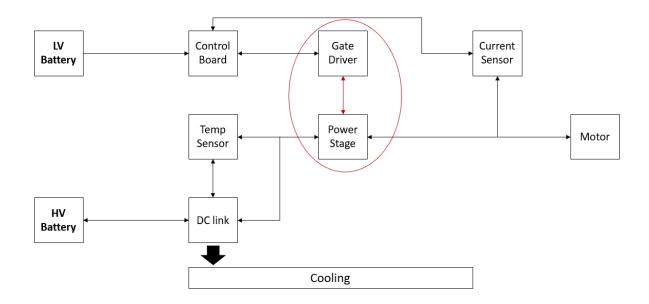

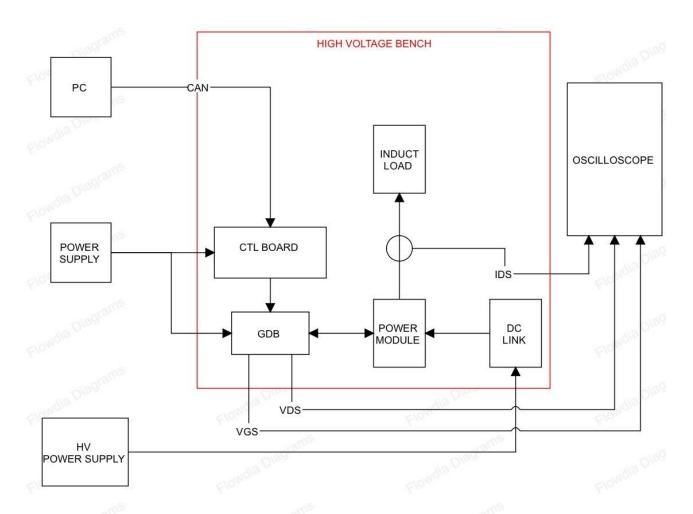

High-level partitioning is an essential step in the design of any power converter, especially a GaN-based inverter, where various functional blocks are integrated to achieve optimal performance, efficiency and scalability. In this section, the inverter design has been broken down into key blocks that play distinct role in power conversion, control and protection. Dividing the design into its functional constituents simplifies the overall design and increases the level of modularity, which are both important for prototyping as well as future development..

Figure 10: High-level partitioning of an inverter system

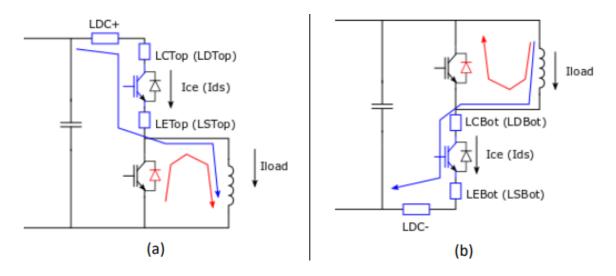

### 3.2.1 Power Stage

Of all sections of a GaN-based inverter system, the power stage may represent the most challenging and critical element, as it is responsible for performing the basic function of DC-AC power conversion. This process is accomplished using high-speed switching transistors, in this case GaN devices, that far exceed traditional silicon MOSFETs in efficiency, speed and power density. The choice of the power stage design has a big impact on the overall inverter performance: efficiency, form factor, and power capability.

The power stage of a GaN-based inverter can be divided into:

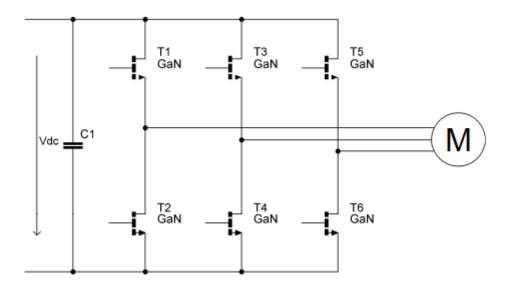

These devices are wide bandgap, and can operate at higher voltages, switch faster and create less loss than silicon-based devices. As GaN has a high electron mobility, it allows very fast switching on the order of nanoseconds — over such switching times are dominant and can significantly reduce switching loss while enhancing efficiency. GaN transistors are typically arranged in a half-bridge or full-bridge configuration during the power stage. To create a complete AC waveform, a full-bridge configuration (four transistors) is preferred. Such configuration provides output positive and negative voltage from inverter which is needed for AC load. GaN devices provide operation at higher switching frequencies in these configurations, which means smaller passive components and a smaller overall footprint.

Figure 11: Three-phase bridge GaN voltage-source inverter [31]

• DC Link: the power stage usually contains DC Link, which include the energy storage required to support the GaN transistors switching action. These capacitors play a role in smoothing the input voltage and delivering a uniform DC supply to the switching elements. In order to reduce losses and guarantee a fast transient response, low-ESR capacitors are applied due to the fast switching nature of GaN transistors. The choice of capacitors in the power stage plays a direct role in both the inverter's performance under voltage spikes and its ability to manage ripple, especially important in high-frequency designs..

The performance requirements for the inverter, coupled with the application, then determine the switching topology used in the power stage. High output power is generated using full-bridge topology. The frequency of PWM is determined by the ON and OFF sequence of each transistor in the full-bridge configuration, which is controlled using the gate driver circuit to switch ON and OFF. The filtered signal generates a clean AC output waveform.

In traditional silicon-based designs, hard-switching is commonly used, where transistors are switched on and off with significant voltage and current across them, leading to high switching losses and increased thermal stress. In contrast, soft-switching techniques greatly reduce these losses by ensuring that transistors switch when the voltage or current is minimal. This is particularly advantageous in high-frequency applications, where switching losses can become a significant portion of the total power loss. Soft-switching techniques such as ZVS and ZCS could be advantageous for enhancing the efficiency of the power stage in GaN-based inverters [32].

GaN transistors are very efficient, but power stage does emit some heat during high-power operation. Thermal management is key to prevent early failures of the inverter which is critical for performance and failure analysis. Nets And FansUnder the right conditions, GaN devices generate far less heat than their silicon counterparts, so the power stage design will usually feature heat sinks and, in some instances, active cooling (fans or liquid cooling) to dissipate the heat developed by the GaN devices. Thanks to GaN transistors' higher efficiency, GaN has significantly less demanding thermal management requirements than silicon-based systems, though thermal design is still important to avoid localized hotspots and operate safely at high power levels.

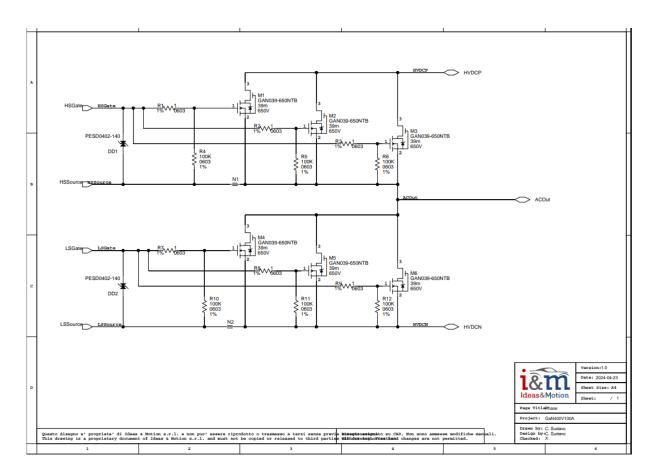

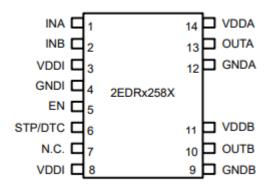

### 3.2.2 Gate driving circuit

Gate driving circuit is an important part of the power stage of an inverter, especially if GaN transistors are used in the power stage. Fast, precise, and controlled gate signals are essential to make the most of the high-speed switching and low losses that GaN transistors can deliver. A good gate driver will make sure that the transistors are turned on and off at their optimal performance scope, reducing switching losses, protecting the transistors from damage and overall improving the efficiency of the inverter.

The gate driver circuit in a GaN-based inverter is responsible for generating the appropriate signals to control the on/off states of the GaN transistors. A typical gate driver circuit can include:

- Driver IC: The driver IC is the heart of the gate driving circuit, this chip is responsible for converting control signals from the microcontroller into high-speed gate signals the gate signals needed for the operation of the GaN transistors. GaN transistors typically work at much lower gate voltages (usually 5V to 6V) than silicon MOSFETs, and the driver IC must be able to generate those exact gate voltages, with very fast rise and fall tones, to maximize the switching speed, while minimizing losses.

- Bootstrap Circuit: employed to generate the high-side gate voltage in many inverter designs, particularly those utilizing high-side and low-side switching configurations. This also allows the gate driver to float with respect to the source terminal of the high-side transistor, allowing it to control the high-side transistor properly when operating it in high-side mode. In the low-side conduction phase, the bootstrap capacitor is charged and then used to provide the gate voltage in the high-side switching phase.

- Level Shifters: For some designs where both high-side and low-side switching is required, use of level shifters are also very common in letting

control signals sent to the high-side transistors are properly referenced to the floating source potential. These results enable the gate driver to control the transistors accurately whether they are in high-side or lowside positions, and to do so without creating damaging voltage gain spikes or delaying the switching process.

• Power Supply for Gate Driver: Stability and low noise of the power supply is essential for the gate driver to operate. The power supply must produce the correct gate voltage with low enough ripple voltage that the gate circuits do not switch erroneously or produce noise. Isolated power supplies are used in many applications to provide separate biasing for the high-side and low-side gate drivers to ensure there will be no unwanted interaction between the control signals.

Although many of the fundamental principles of driving transistors are the same regardless of the underlying technology, GaN transistors do pose unique challenges compared to standard silicon MOSFETs. The cause of these challenges are the original electrical characteristic of GaN devices such as their the higher switching speeds, lower gate charge and their higher sensitivity to parasitic inductances and capacitances. The main challenge is that they can switch at very high speeds, with rising and falling times often measured in nanoseconds. This swift toggling enhances efficiency and minimizes losses but imposes on the gate driver circuit the requirement to produce clean and well-formed signals with minimum delay or distortions. Any signal distortion or delay can have a huge impact on switching losses or, even worse, lead to improper transistor switching, potentially causing devices to fail. GaN transistors also have a very low gate charge, so they can switch faster than their silicon MOSFET counterparts. This characteristic is a problem for the gate driver, though, because gate overdrive can cause overshoot, high-power dissipation, and gate oxide breakdown. This is why it means precision when it comes to voltages levels supplied by the gate driver so it doesn't get harmed. The requirements for the gate driver are also unique, as the gate threshold voltage of GaN transistors is lower than that of silicon devices. Gate voltage noise could also cause spurious switching events, leading to lost work and ultimately damaging the transistors. Moreover, the very high switching speed of GaN transistors increases their sensitivity to parasitic inductances and capacitances of the gate driver circuit. RF signal degradation, ringing, overshoot, and turn-off delay can occur from parasitic elements, particularly inductance from the gate loop, resulting in high-frequency oscillations that can damage the FET transistors in high power applications. Common-mode currents can couple through traces on a PCB that act as antennas and properly layout the PCB to keep trace lengths short and use low-inductance components. However, because GaN transistors are high performance and fast-switching transistors, protection mechanisms are an important requirement in the gate driver circuit to avoid

failures and guarantee long-term stability. Overvoltage protection: Transient over-voltages can lead to destructive breakdown of the gate oxide and thus it is necessary to protect the gate voltage such that it does not excess a safe value. The desaturation detector observes the voltage across the transistor and turns off the driver should an unusually high voltage be detected in order to indicate a possible short-circuit condition. Miller clamping also stabilizes the gate voltage during fast-train switching, preventing parasitic switching due to capacitance between gate and drain. Finally, dead time control is integral to prevention of shoot-through in inverter designs, where both high-side and low-side transistors can turn on simultaneously and cause catastrophic failures. Accurate dead time management ensures that the transistors are protected while minimizing conduction losses, thus optimizing the efficiency of the inverter system [33].

#### 3.2.3 Control system

A GaN based inverter controller is a vital element of this technology, as it directly impacts how well the inverter will function as a whole by providing power stage control and regulating switching signals and stability at different load conditions. It employs a closed-loop control system that detects changes and adapts to them, maintaining voltage and frequency regulation. The control system is also responsible for implementing protection mechanisms and responding to fault conditions, making it an essential element for the inverter's reliability and performance. The control system of an inverter typically consists of the following parts:

- Microcontroller/Digital Signal Processor (DSP): the control system consists of a microcontroller or DSP, which implements the control algorithms, generates the switching signals and reads feedback from sensors. When controlling GaN transistors (which enable fast switching), we need to make sure that any embedded control systems can cope with quick dynamic behaviors. Such real-time processing of high-frequency, complex control algorithms, like PWM, makes a DSP preferable in many applications.

- PWM Generation: One of the main methods that can be used for controlling switching of GaN transistors integrated in the power stage of a system is pulse-width modulation. The control system changes the output voltage of the inverter by modulating the duty cycle of the PWM signal. With their high-frequency switchability, GaN transistors make higher-resolution PWM possible leading to finer steps in output waveform control. These enable the control system to create a PWM signal with precise transitions to increase efficiency and minimize distortions.

- Feedback Loops: the control system focuses on feedback from voltage, current, and temperature sensors for stable operation. The controller receives this real-time data from the sensors and adjusts the PWM signals as needed. The feedback loops allow the system to adjust dynamically to variations in load conditions or changes in input voltage, keeping performance within specified limits. One such application is a voltage controller where during load condition voltage drops so control system increases duty cycle applied to PWM signal.

- Control Algorithms: There are many control algorithms that can be utilized in the control system for managing the inverter's performance. PID (proportional-integral-derivative) control is the most widely implemented control technique which modifies the output based on the difference (error) between the desired and the actual output values. PID control is simple but works well for a majority of applications. Nevertheless, advanced control methods, including model predictive control (MPC) and sliding mode control (SMC) have been developed and are being applied to GaN inverters with high efficiency. This enables improved dynamic performance compared to simpler strategies, and can better accommodate nonlinearities in the system.

GaN-based inverters utilize control strategies that allow for optimal utilization of GaN transistor's fast-switching features with reduced losses and stable operation. The two well known control strategies include voltage-oriented control (VOC) and current-oriented control (COC).

VOC is an extensively employed mechanism for PBS output voltage conversion of inverters like renewable sources and UPS. In VOC, the control system directly controls the PWM signals to keep the output voltage stable regardless of input voltage and load variations. With a feedback loop monitoring the output voltage, the PWM duty cycle is adjusted as necessary so as to minimize the difference between the output voltage and the target value. Based on its main function of output current controlling of the inverter, COC is the most widely used one in such applications requiring accurate control of the output current, most scientific of them include motor drives or gird tied inverters. In COC, the control system tracks the output current and corrects the switching signals so that the current follows the reference value. However, this method allows more precise control over the power provided to the load, making it optimal for uses with dynamic load conditions [34].

#### 3.2.4 Sensors

In Control Techniques' high performing mid-range in-vehicle current, temperature and pressure sensors are critical for GaN-based inverters to enable optimal performance and protect components of system. These sensors send signals to the control system in real-time, which uses the information to maintain power flow, prevent overloading, and avoid overheating. This information enables the inverter to dynamically adjust its operational parameters to optimise performance under varying load conditions. The total current measurement is important for controlling the power delivered, and it also provides a protection mechanism, such as overcurrent shutdown and short-circuit detection. A frequent way to measure current is with a shunt resistor. Small resistors are added in the current path and the voltage drop across those is read to know the current. Shunt resistors ensure accuracy and speed of response, parameters of great importance in a fast-switching environment like that of GaN transistors. They do produce heat that needs to be managed, especially in high-power applications. Hall-effect sensors are another common method for current sensing providing electrical isolation with the ability to measure AC and DC currents. A Hall-effect sensor is non-intrusive and adds safety by electrically isolating the measurement circuitry from the high-power components. Current transformers are often used in applications to measure high AC currents providing isolation and low power dissipation but not suitable for measures in DC current. The high-speed switching characteristics of GaN transistors make the current sensing issue in GaN inverters particularly difficult. Indeed, fast switching leads to fast changing current which is why we need sensors that suit low response time and allow us fully release those delays. The second point is that the sensors need to bear the high power levels that are characteristic of this type of inverter without saturating or heating. The output of these sensors need to be filtered for noise, and properly calibrated, as an erroneous measurement could affect the inverter performance and safety. Temperature sensing is just as important, as the high power of inverters can lead to thermal stress. GaN transistors are more sensitive to temperature extremes than traditional silicon devices, and failing to manage temperature extremes can degrade their performance, even cause failure. In comparison, stable and low-cost temperature measurement systems are usually made using thermistors, which also show high sensitivity. Negative temperature coefficient (NTC) thermistors are often used to measure the temperature of heat sinks or power devices. Thermistors, on the other hand, require calibration and can be complicated to use because the resistance is non-linear with respect to temperature. Alternatively, resistance temperature detectors (RTDs) are a more accurate and stable option, but are often more costly and may not always be necessary depending on the application. In some scenarios, GaN transistors or gate drivers may already have embedded temperature sensors, enabling direct junction temperature measurements. These combined sensors enable real-time assessment of the device's temperature, so the control system can modulate or shut down the inverter if overheating occurs. The biggest obstacle for temperature sensing used

in GaN inverters is the correct and real-time sensing of temperature variations during high-power operations where the temperature may accelerate abruptly. All the sensors need to be placed suitably near components that generate heat, and the control system needs to be able to respond quickly enough to bursts of temperature to prevent thermal damage. In such mission-critical, high-performance systems, having a sound thermal management strategy in place is essential, which goes hand in hand with how you choose a suitable sensor and ensure it's operational in the inverter's fast-moving environment. In summary, both current and temperature sensors are essential to monitor the operation of GaN-based inverters, ensuring high system performance and long-term reliability. Measurement with accuracy and timeliness perform with dynamic adjustment for system operation, ensuring safe and efficient power conversion. Through this study, by using correct sensors with careful decision, low the high power high speed switching activities risk inductor inverter design to increase risk and reliability.

#### **Chapter 4**

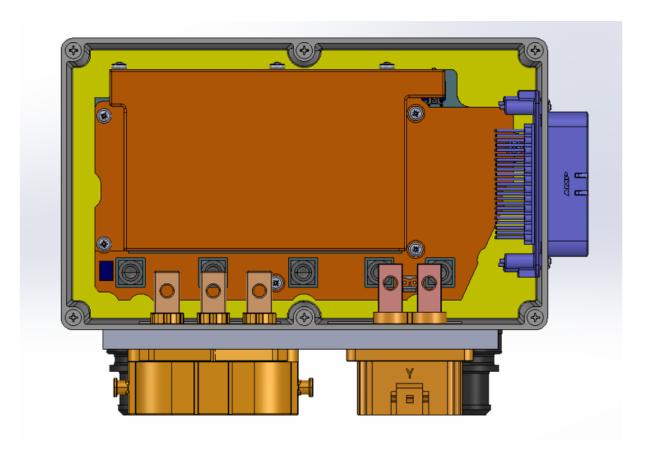

# Design of a GaN-based inverter power stage

The most important subsystem responsible for an inverter design is its power stage that encompasses several key components, which should cooperate in such a way to ensure that the conversion of dc power into ac power will be carried out effectively, confidently and by taking care with the safety issues.

This paper is methodically divided into sections scrutinizing each element that contributes to the successful shaping of the inverter system from switching frequency and efficiency to thermal management and EMI considerations & converter topology to address the technical challenges associated with their performance. This need for higher efficiency, lower losses, and room for more compact designs has driven the implementation of advanced semiconductor materials and topologies in inverter power stages. For successful implementation of these systems, the inverter must maintain the power quality, minimize the harmonic distortion, and ensure reliable operation under changing load conditions.

In this chapter, we will discuss the design and implementation of the inverter power stage, including the common components that form the overall system. The implemented design will be discussed in detail, together with relevant topics, like converter topology, gate driving circuit, power supply and sensors. Also, the layout considerations, important to minimize parasitic effects and maximize the thermal management, will be presented.

#### 4.1 Schematic

## 4.1.1 3-phase bridge

The 3-phase bridge topology is one of the main topologies for power conversion applications, such as drives, converters, inverters, and industrial equipment, where high power conversion capability is critical. It basically is a combination

of 6 switching elements, where for every phase you have one pair of switches: a high-side and a low-side switch. These switches successively connect each output phase to the positive (or negative) side of the DC bus according to a modulation strategy, often pulse-width modulation (PWM) based in order to create a sinusoidal function at the output across the load.

#### In this topology:

- Three legs are refers to the three phase of inverter output (A, B and C).

- There are two switches (high-side and low-side) in series connected to the DC bus for each leg.

- Each leg of the inverter will contain the midway point for which each phase is output.

The primary operation of the 3-phase bridge is to transform a DC input voltage into a 3-phase AC output, which is required for driving AC motors or interfacing with 3-phase power networks. Using transistors as the switches enables fast switching of ON and OFF states, thus allowing accurate output waveform control and giving benefits like high efficiency, high power handling ability and high reliability.

There are several benefits of this topology, that make it a goto topology for most high power derived applications. Here are a few of the major advantages:

- High efficiency: one of its most practical advantages is its ability to produce balanced 3-phase AC power instead of the switching losses typical of the inverter. It introduces greater overall efficiency, which is especially beneficial in applications such as electric vehicles and renewable energy systems in which energy efficiency is critical.

- Harmonics reduction: the symmetric structure of the 3-phase bridge leads to less harmonic distortion generation Harmonics are not desired because it leads to more losses and heating and therefore reduces the systems efficiency through motors, etc. This results in a smoother sinusoidal output waveform, which is better for the performance and longevity of the motor, as well as for any connected loads.

- Power is distributed evenly: in a 3-phase system, the power is delivered more uniformly across three phases, allowing the electrical load to be balanced. This balance: provides smoother operation, less stress on components, and more reliability over time.

- Compact design: 3 phase bridge topology allows compact inverter design This means the inverter can still drive high power while minimising the overall device weight and system size, perfect for space and weight critical applications [35].

As the required current to this design is quite high (150 A), using a single GAN039 would be impossible due to it's low current capacity. Achieving the 150 A current required by our system took a different direction. The current specification is high and thus parallelization technique is used to meet this. Parallelization of transistors: (a very common technique in high energy applications. This allows current to be distributed over multiple devices thus reducing stress on specific components, increase system reliability.) This is especially useful in a three phase inverter casing where it enables the inverter to process high currents while reducing the thermal loads on each transistor.

This methodology provides many advantages, especially in cases of high power density and efficiency requirements:

- Improved current handling: parallelization increases the overall current capacity available in each individual phase without stressing out any particular transistor, which means that the inverter is capable of handling more load and doing so within its safe operating area of operation.

- Less conduction loss: conduction losses in a transistor are proportional to the ON-resistance and the conduction current. The additional benefit of using the switch in parallel is that when splitting the current between multiple transistors, each individual device is able to conduct a lower amount of current, therefore reducing conduction losses and increasing efficiency.

- Enhanced thermal performance: thermal management is one particular challenge in power electronics; when using transistors, some of the input energy will always generate heat. In addition, thermal load can be shared by multiple devices by means of the parallelization method which decreases the transistors temperature rise and risk of thermal runaway [36].

Dynamic power consumption from transistors poses challenges in driving inverters, especially if the inverter drive is parquetized to withstand more current. The dynamic power is the power consumed in a transistor switching event, where the gate capacitance will charge and discharge for each cycle. In high-frequency applications, where energy must be supplied to transfer charge through the gate capacitance during each switching cycle, this power becomes much important. As with all transistors,  $C_{iss}$  adds in parallel when we parallel transistors, so the total capacitance is multiplied. The higher capacitance means that the gate requires more power to switch effectively, which in turn affects the design of the gate driver circuit and power supply

For each switching cycle, the dynamic power needed to charge and discharge the total gate capacitance is given by:

$$P_{dyn} = \frac{1}{2} \times C_{iss(tot)} \times f_{SW} \times V_{GS}^2$$

(9)

Where  $C_{iss(tot)}$  is the total input capacitance of the parallelized transistors,  $f_{SW}$  is the switching frequency and  $V_{GS}$  is the gate-source voltage, which in this case is chosen at 12 V.

Given that three transistors GAN039-650NTB in parallel have been used, each with individual input capacitance of approximately 2 nF, the total input capacitance is:

$$C_{iss(tot)} = 3 \times 2 \text{ nF} = 6 \text{ nF}$$

(10)

At a switching frequency of 50 kHz (worst-case), the total dynamic power needed to drive the gates of three parallelized GAN039-NTB650 is calculated as follows:

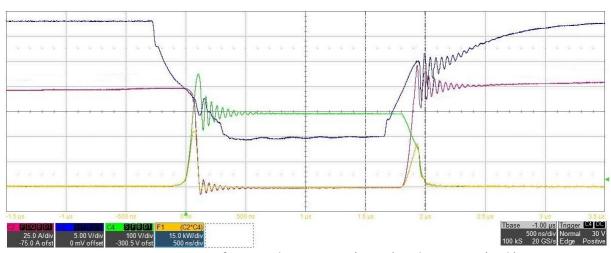

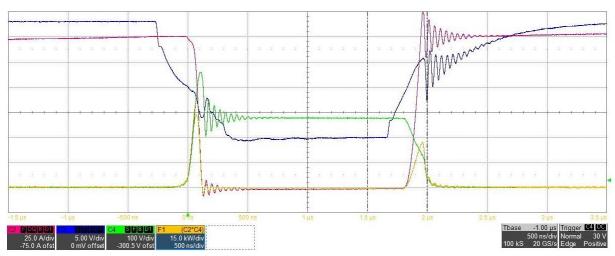

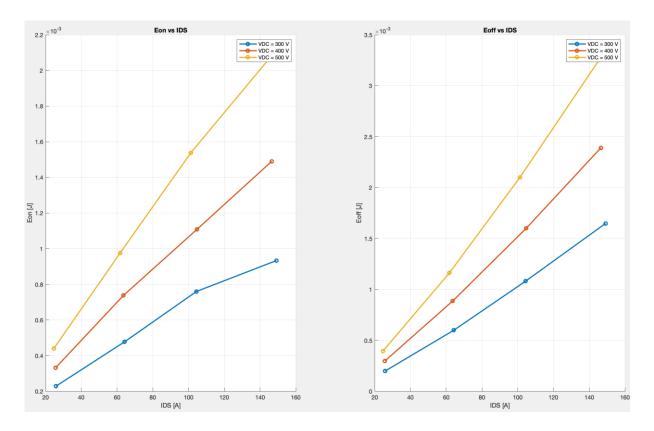

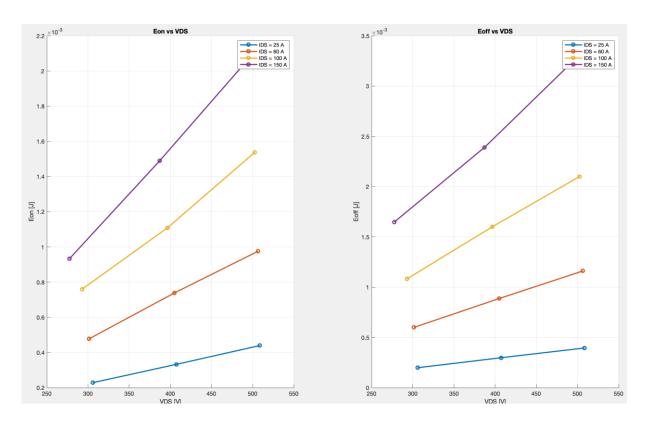

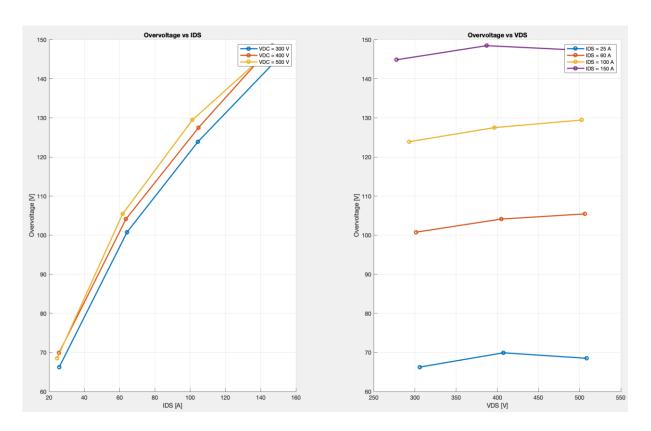

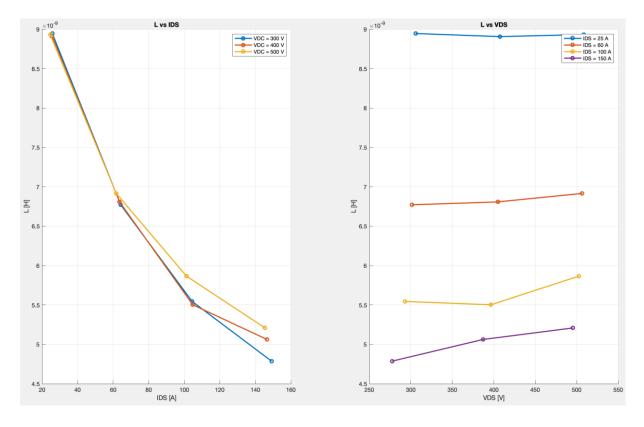

$$P_{\text{dyn}} = \frac{1}{2} \times 6 \text{ nF} \times 50 \text{ kHz} \times 12^2 \text{ V} = 21.6 \text{ mW}$$