## POLITECNICO DI TORINO

Master's Degree in Nanotechnologies for ICTs

Master's Degree Thesis

## Investigation and development of a graphene electroburning platform for reliable single-molecule electrode fabrication

Supervisors: Prof. Mariagrazia Graziano Prof. Gianluca Piccinini Ph.D. Fabrizio Mo M.Sc. Federico Ravera Candidate: SeyedBabak Esfahani

Academic Year 2023-2024

## Summary

Molecular electronics has been considered a beyond-CMOS platform to pursue the scaling of electronic devices, by pushing it to the single-molecule level, and by using the paradigm in which individual molecules constitute the active components in electronic circuits, performing a variety of functions such as transistors and sensors. For many years, molecular electronics has traditionally advanced from materials such as gold electrode with nanogap formation methods such as electromigration and mechanical break junctions. Alternatively, graphene has opened a new possibility of acting as a stable electrode at room temperature for a long period of time and its unique electronic properties have been analyzed as a possible material to be the electrode for single-molecule electronics. Since atoms in graphene are stable at room temperature owing to their sp<sup>2</sup> C-C covalent bonds, graphene can be a natural electrode for conjugated molecules, offering, at the same time, good orbital hybridization with the molecular channel and thus more natural support to transport in molecular devices.

An established method for creating nanogaps in graphene is feedback-controlled electroburning. This method can be an effective way to form nanogaps in single or few-layer graphene if certain prerequisites are met. This approach is related to the chemical reaction of carbon atoms of graphene with oxygen, and the process evolution is controllably performed using a feedback control system.

In the first part of this work, a literature review is conducted on the graphene electroburning process, with a description of the main features and reasons for employing graphene as an electrode with its key characteristics. Additionally, the potential of graphene as an electrode is investigated through a study of its physical properties.

Then, in its second part, the thesis focuses on the development of a feedback-controlled algorithm for the graphene electroburning-based nanogap formation. The algorithm is implemented in LabVIEW for an FPGA hardware platform. The system uses analog input voltage and analog output current modules with the FPGA-based controller and it is possible to achieve fast-speed feedback controlled algorithm with resolutions up to a few µs sampling rate. Then, using simulations in Synopsys' QuantumATK® software, the graphene electroburning process is analyzed in detail through the comparison of graphene nanoribbons with different atomic configurations and their properties such as current -voltage characteristics and transmission spectrum are reported to show the graphene as an electrode with different geometries and nanogap structures.

The thesis findings are consistent with literature results from other groups, confirming the potential of electro-burned graphene electrodes as a reliable electrode for singlemolecule electronics. Future works should focus on the testing and setup of the developed system on a real pre-patterned graphene sheet, addressing also higher sampling rates and time resolution.

## Acknowledgements

I would like to express my gratitude to Ph.D. F. Mo and M.Sc. F. Ravera for their valuable suggestions and guidance throughout my thesis work.

I am also deeply thankful to Prof. M. Graziano and Prof. G. Piccinini for welcoming me into their research group and providing their support.

Lastly, I wish to express my heartfelt gratitude to my parents. To my mother, for her constant and unwavering support throughout my life. To my late father, whose enduring curiosity continues to inspire me, even in his absence, as I reach this achievement.

## Contents

| List of Tables<br>List of Figures |          |                                              |    |   |                   |                                        |

|-----------------------------------|----------|----------------------------------------------|----|---|-------------------|----------------------------------------|

|                                   |          |                                              |    | 1 | <b>Int</b><br>1.1 | roduction<br>Organization of this work |

| Ι                                 | pa       | rt one                                       | 13 |   |                   |                                        |

| 2                                 | Lite     | Literature review                            |    |   |                   |                                        |

|                                   | 2.1      | Top contact junctions                        | 15 |   |                   |                                        |

|                                   |          | 2.1.1 Mechanically controlled break junction |    |   |                   |                                        |

|                                   |          | 2.1.2 Electromigration                       |    |   |                   |                                        |

|                                   | 2.2      | Carbon based electrode                       | 18 |   |                   |                                        |

|                                   | 2.3      | Electroburning                               | 19 |   |                   |                                        |

|                                   |          | 2.3.1 Fabrication                            | 19 |   |                   |                                        |

|                                   |          | 2.3.2 Feedback controlled electroburning     | 21 |   |                   |                                        |

|                                   | 2.4      | Conclusion                                   |    |   |                   |                                        |

| 3                                 | Graphene |                                              |    |   |                   |                                        |

|                                   | 3.1      | Properties                                   | 25 |   |                   |                                        |

|                                   | 3.2      | Band Structure                               |    |   |                   |                                        |

|                                   | 3.3      | Density of states                            | 28 |   |                   |                                        |

|                                   | 3.4      | Charge transport mechanism                   | 29 |   |                   |                                        |

|                                   |          | 3.4.1 Nanogap Modelling for Graphene         | 30 |   |                   |                                        |

|                                   | 3.5      | Graphene Nanoribbons                         | 31 |   |                   |                                        |

| 11                                | р        | art Two                                      | 35 |   |                   |                                        |

|                                   |          |                                              |    |   |                   |                                        |

| 4 | Simulation by QuantumATK |                       |    |  |  |

|---|--------------------------|-----------------------|----|--|--|

|   | 4.1                      | Computational methods | 37 |  |  |

|   | 4.2                      | Configuration 1       | 40 |  |  |

|   | 4.3                      | Configuration 2       | 42 |  |  |

|                                                                | 4.4    | Config   | guration $3$                                                        | 44 |

|----------------------------------------------------------------|--------|----------|---------------------------------------------------------------------|----|

|                                                                | 4.5    | Charge   | e transport comparison                                              | 47 |

|                                                                | 4.6    | Conclu   | usion                                                               | 47 |

| 5 Development of a feedback-controlled electroburning platform |        |          | 49                                                                  |    |

|                                                                | 5.1    | Hardw    | vare                                                                | 49 |

|                                                                | 5.2    | Softwa   | are                                                                 | 50 |

|                                                                | 5.3    | Electro  | oburning algorithm                                                  | 51 |

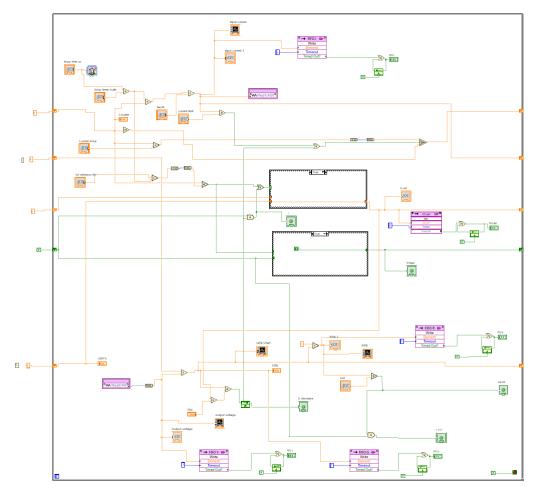

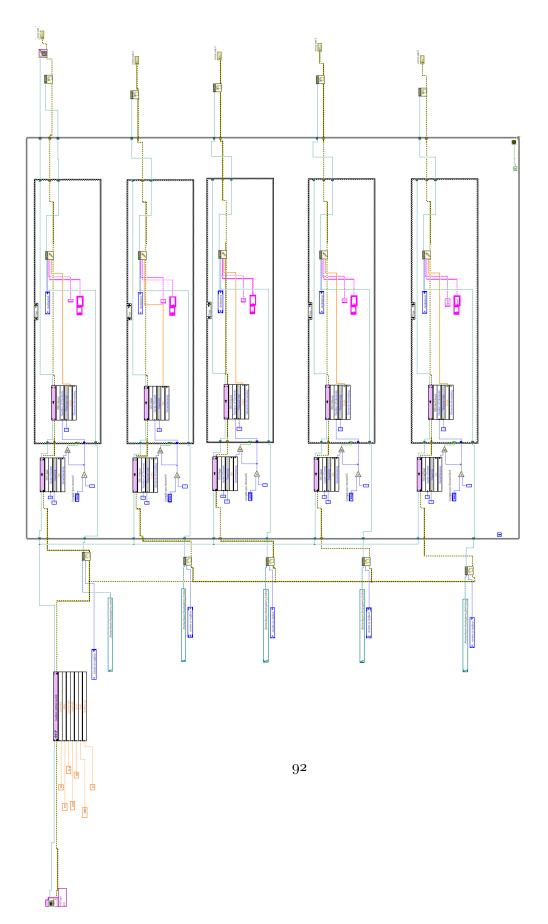

|                                                                | 5.4    | Block    | diagram                                                             | 53 |

|                                                                |        | 5.4.1    | Current generation                                                  | 53 |

|                                                                |        | 5.4.2    | Voltage reading                                                     | 54 |

|                                                                |        | 5.4.3    | Conductance and Resistance                                          | 55 |

|                                                                |        | 5.4.4    | Feedback conditions                                                 | 56 |

|                                                                |        | 5.4.5    | Loop end condition                                                  | 59 |

|                                                                | 5.5    | Transf   | fer data to the host                                                | 59 |

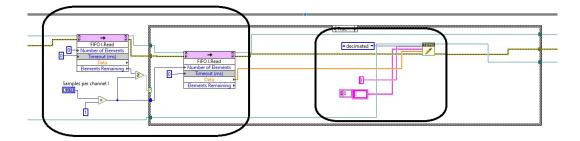

|                                                                |        | 5.5.1    | Write to FIFO in LabVIEW-FPGA                                       | 59 |

|                                                                |        | 5.5.2    | Read the data from FIFO in LabVIEW                                  | 60 |

|                                                                | 5.6    | Result   | s of feedback-controlled system                                     | 60 |

|                                                                |        | 5.6.1    | 200 µs sampling rate                                                | 61 |

|                                                                |        | 5.6.2    | 100 µs sampling rate                                                | 69 |

|                                                                |        | 5.6.3    | 20 µs sampling rate                                                 | 75 |

|                                                                | 5.7    | Conclu   | usion                                                               | 81 |

| 6                                                              | Cor    | clusio   | n                                                                   | 83 |

| Α                                                              | Pra    | ctical g | guide                                                               | 85 |

|                                                                |        | A.0.1    | Hardware                                                            | 85 |

|                                                                |        | A.0.2    | Software                                                            | 85 |

|                                                                |        | A.0.3    | Block diagram for the feedback-controlled electroburning, FPGA      |    |

|                                                                |        |          | target                                                              | 90 |

|                                                                |        | A.0.4    | Block diagram for the feedback-controlled electroburning, Host pro- |    |

|                                                                |        |          | gram                                                                | 92 |

| Bi                                                             | ibliog | graphy   |                                                                     | 95 |

## List of Tables

| QuantumATK DFT Calculator                    |

|----------------------------------------------|

| QuantumATK Transmission Spectrum settings    |

| QuantumATK Device Density of States settings |

| QuantumATK I-V curve settings                |

|                                              |

# List of Figures

| 2.1 | Schematic of the Mechanically controlled break junction.                                      | 16  |

|-----|-----------------------------------------------------------------------------------------------|-----|

| 2.2 | Conductance as a function of the bias voltage during the feedback-controlled                  |     |

|     | electromigration process.                                                                     | 18  |

| 2.3 | Schematic of the feedback-controlled electroburning process, before (top)                     |     |

|     | and after (bottom), the formation of nanometer sized gaps in few-layer                        | 00  |

| 0.4 | graphite flakes.                                                                              | 20  |

| 2.4 | Process for fabricating of graphene nanogap electrodes. (top) device fab-                     |     |

|     | rication without pre-patterning. (bottom) device fabrication with pre-                        | 21  |

| 25  | patterning                                                                                    | 21  |

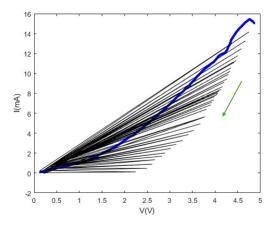

| 2.5 | electroburning process with 200 µs sampling rate. The initial I-V trace is                    |     |

|     | shown in blue                                                                                 | 22  |

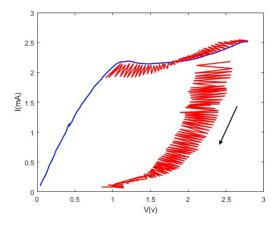

| 2.6 | I-V traces recorded during the feedback-controlled electroburning process                     | 22  |

| 2.0 | with 20 µs sampling rate. The initial I-V trace is shown in blue                              | 23  |

| 3.1 | Left: The arrangement of electrons and their relative spin in graphene.                       |     |

|     | Right: Illustration of the graphene orbitals.                                                 | 26  |

| 3.2 | Left: Honeycomb lattice structure of graphene. Right: Corresponding Bril-                     |     |

|     | louin zone with the basis vectors of the reciprocal space. The Dirac cones                    |     |

|     | are located at the K and K' points.                                                           | 26  |

| 3.3 | Left: The $\pi$ electronic band structure of graphene obtained by the nearest-                |     |

|     | neighbor tight-binding model. Right: Dirac cone                                               | 28  |

| 3.4 | Asymmetric tunnel junction with different work functions on the left and                      |     |

|     | right leads                                                                                   | 31  |

| 3.5 | Nanoribbon geometry with both zigzag and armchair edges.                                      | 32  |

| 3.6 | Graphene with armchair edge (a) and zigzag edge (b), where the carbon                         | ~ ~ |

|     | atoms belonging to sublattices are classified by labeling with A or B.                        | 33  |

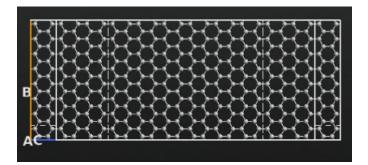

| 4.1 | Graphene Device structure without nanogap                                                     | 40  |

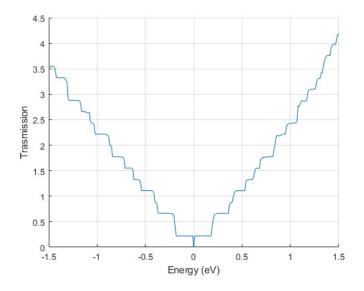

| 4.2 | Transmission Spectrum of graphene without nanogap.                                            | 41  |

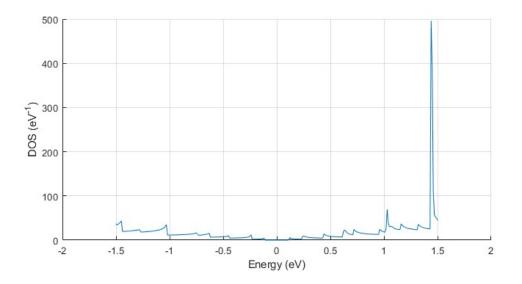

| 4.3 | Device Density of states of graphene without nanogap.                                         | 41  |

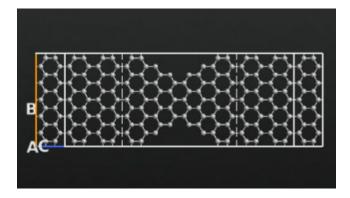

| 4.4 | Bow-tie nanogap structure of graphene with 2 carbon atoms in the center.                      | 42  |

| 4.5 | Transmission Spectrum of bow-tie nanogap graphene structure with 2 car-                       | 49  |

| 16  | bon atoms in the center.                                                                      | 43  |

| 4.6 | Density of states for bow-tie nanogap graphene structure with 2 carbon<br>atoms in the center | 43  |

|     | atoms in the center                                                                           | 45  |

| 4.7  | I-V curve for bow-tie nanogap graphene structure with 2 carbon atoms in    |    |

|------|----------------------------------------------------------------------------|----|

|      |                                                                            | 44 |

| 4.8  | Bow-tie nanogap structure of graphene with 1 carbon atom in the center     | 45 |

| 4.9  | Transmission Spectrum of bow-tie nanogap graphene with 1 central carbon    |    |

|      | atom                                                                       | 45 |

| 4.10 | Density of states for bow-tie nanogap graphene with 1 central carbon atom. | 46 |

| 4.11 | I-V curve for bow-tie nanogap graphene with 1 central carbon atom          | 46 |

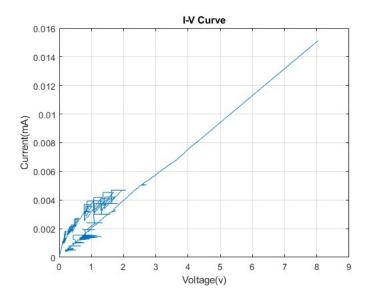

| 4.12 | I-V curve comparison for graphene with and without nanogap structures.     | 47 |

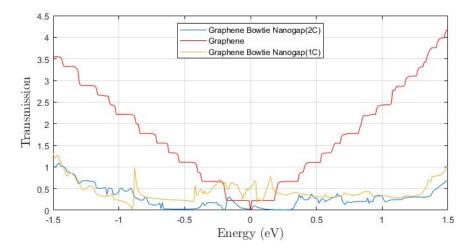

| 4.13 | Transmission Spectrum comparison for graphene with and without nanogap     |    |

|      | structures                                                                 | 48 |

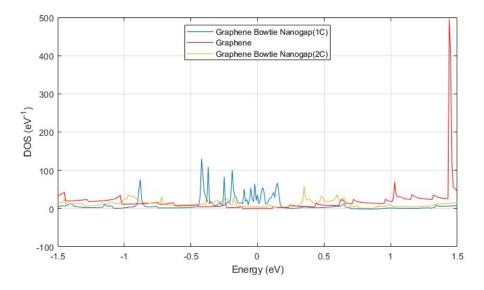

| 4.14 | Density of states comparison for graphene with and without nanogap struc-  |    |

|      | tures                                                                      | 48 |

| 5.1  | NI cRIO-9030                                                               | 49 |

| 5.2  | NI 9265                                                                    | 50 |

| 5.3  | NI 9223                                                                    | 50 |

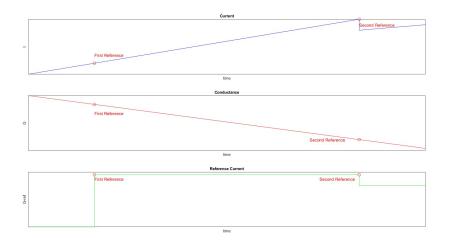

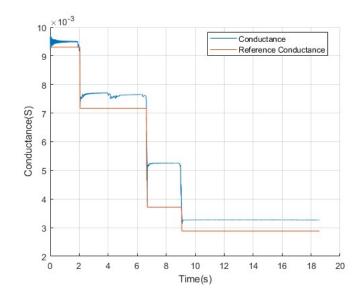

| 5.4  | Comparison of Current, Conductance, and Reference Conductance in the       |    |

|      | Algorithm.                                                                 | 51 |

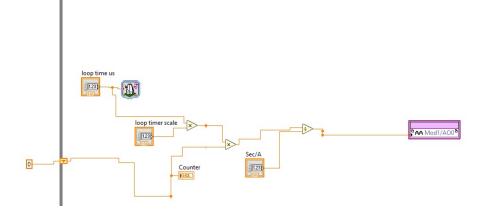

| 5.5  | LabVIEW-FPGA block diagram for loop timing and current generation.         | 53 |

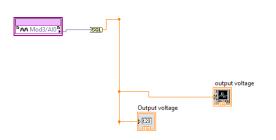

| 5.6  | LabVIEW-FPGA block diagram for output current.                             | 54 |

| 5.7  | LabVIEW-FPGA VI for output current.                                        | 54 |

| 5.8  | LabVIEW-FPGA block diagram for input voltage.                              | 55 |

| 5.9  | LabVIEW-FPGA VI for input voltage.                                         | 55 |

| 5.10 | LabVIEW-FPGA block diagram for measuring Conductance and Resistance.       | 55 |

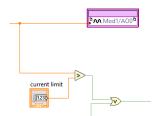

| 5.11 | LabVIEW-FPGA block diagram for Current limit.                              | 56 |

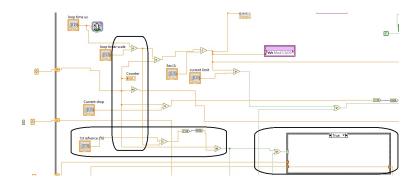

| 5.12 | LabVIEW-FPGA block diagram for 1st reference feedback condition            | 56 |

| 5.13 | LabVIEW-FPGA block diagram for triggering reference.                       | 57 |

| 5.14 | LabVIEW-FPGA block diagram for accepting reference conductance             | 57 |

| 5.15 | LabVIEW-FPGA block diagram for comparison of conductance                   | 58 |

| 5.16 | LabVIEW-FPGA block diagram for feedback selecting condition.               | 58 |

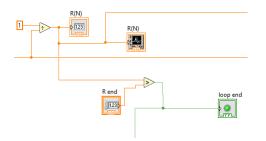

| 5.17 | LabVIEW-FPGA block diagram to stop the loop.                               | 59 |

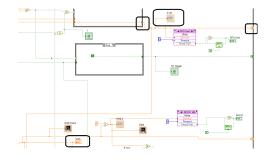

| 5.18 | LabVIEW-FPGA block diagram to write data in FIFO                           | 59 |

| 5.19 | LabVIEW block diagram to open FPGA interface and TDMS                      | 60 |

| 5.20 | LabVIEW-FPGA block diagram to read data from FIFO and write to the         |    |

|      | TDMS                                                                       | 60 |

| 5.21 |                                                                            | 61 |

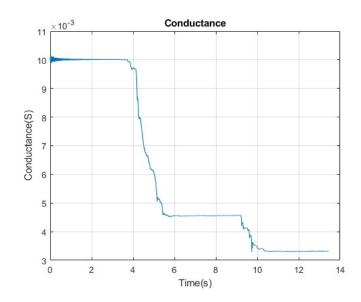

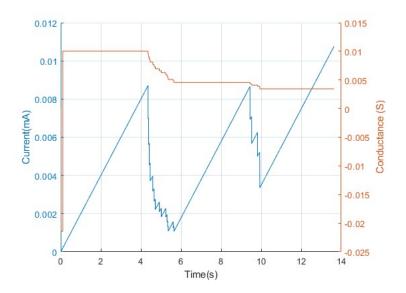

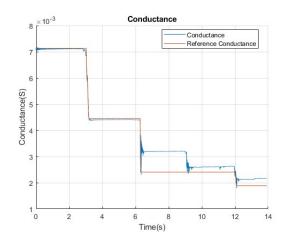

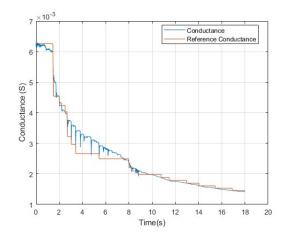

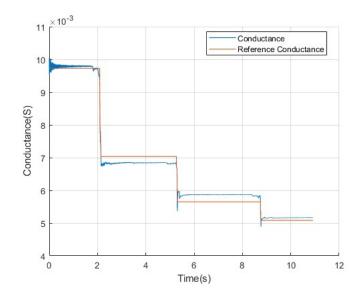

| 5.22 | Conductance vs. Time at 200 µs sampling rate (First approach)              | 62 |

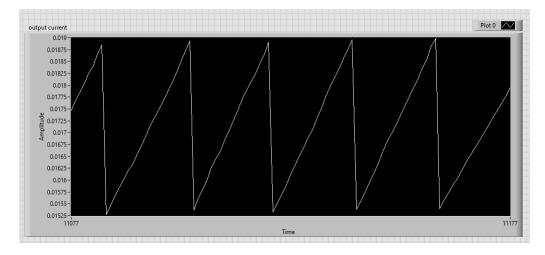

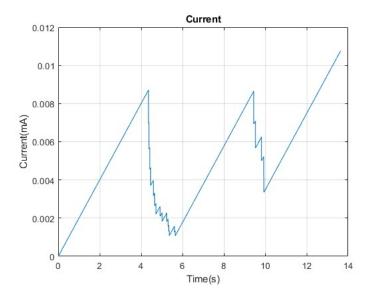

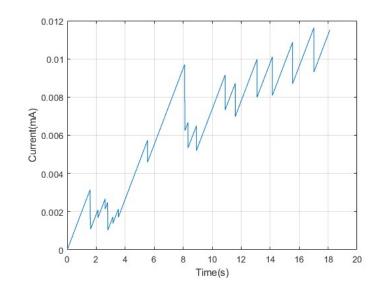

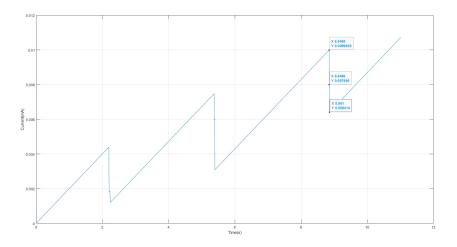

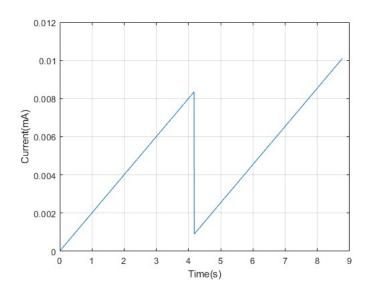

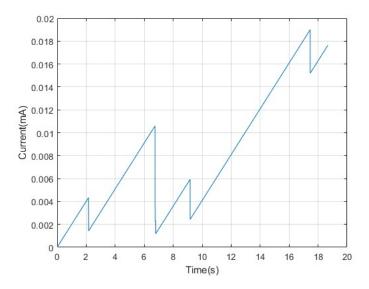

| 5.23 | Current vs. Time at 200 µs sampling rate (First approach)                  | 62 |

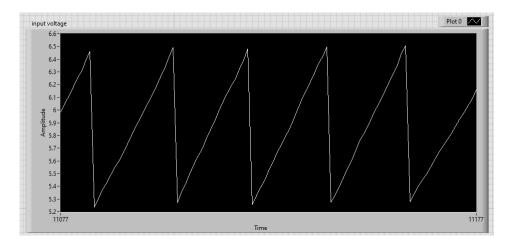

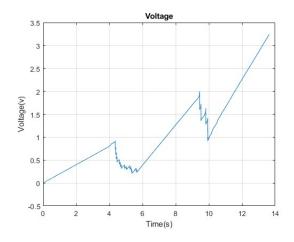

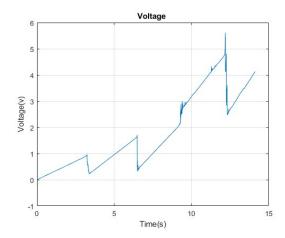

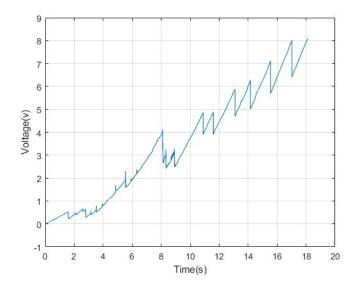

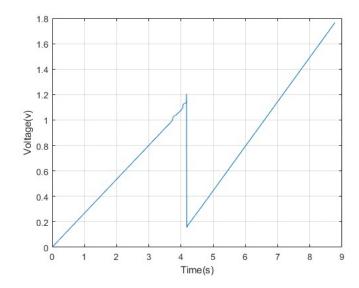

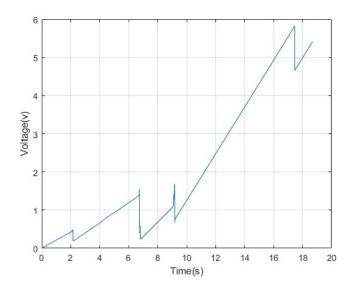

| 5.24 | Voltage vs. Time at 200 µs sampling rate (First approach)                  | 63 |

| 5.25 | Comparison of current and reference conductance at 200 µs sampling rate    |    |

|      | (First approach).                                                          | 63 |

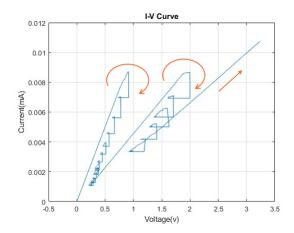

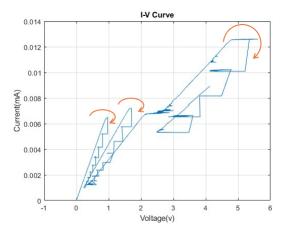

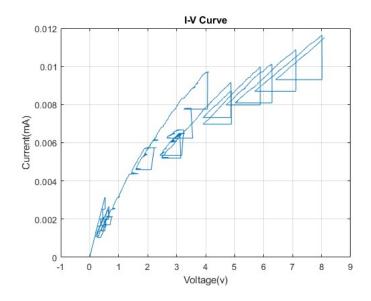

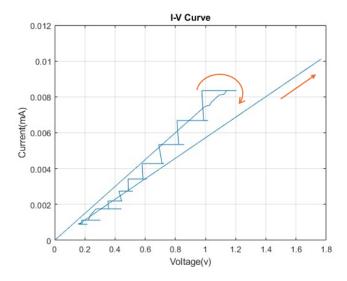

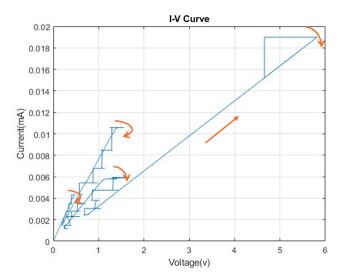

| 5.26 | I-V plot for 200 µs sampling rate (First approach).                        | 64 |

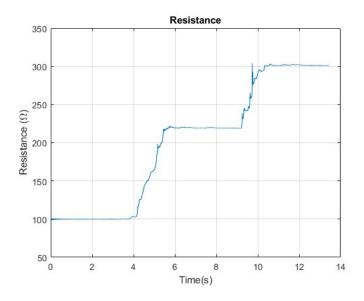

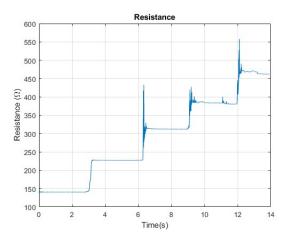

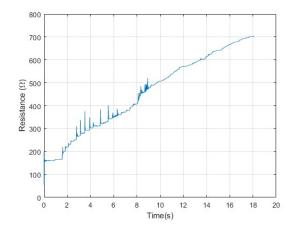

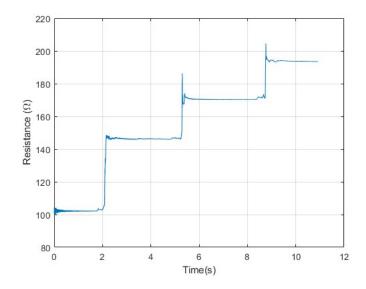

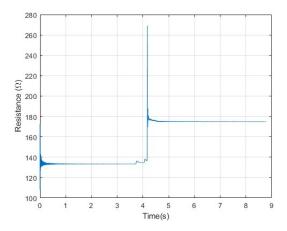

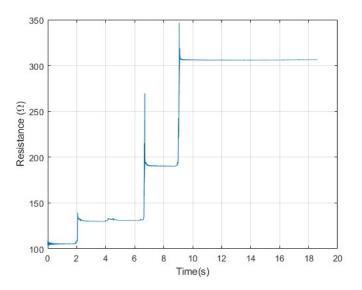

| 5.27 | Resistance vs. Time at 200 µs sampling rate (Second approach)              | 64 |

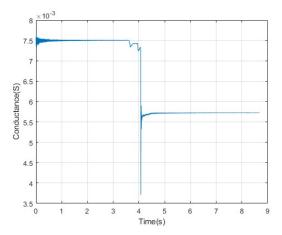

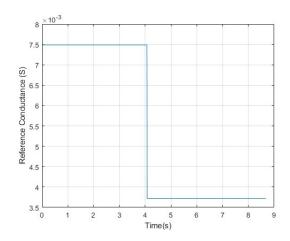

| 5.28 | Comparison of conductance and reference conductance at 200 µs sampling     |    |

|      | rate (Second approach).                                                    | 65 |

| 5.29 | Comparison of current, conductance, and reference conductance at 200 µs   |    |

|------|---------------------------------------------------------------------------|----|

|      | sampling rate (Second approach).                                          | 65 |

| 5.30 | Voltage vs. Time at 200 µs sampling rate (Second approach)                | 66 |

| 5.31 | I-V plot for 200 µs sampling rate (Second approach).                      | 66 |

| 5.32 | Resistance vs. Time at 200 µs sampling rate (Third approach)              | 67 |

| 5.33 | Comparison of conductance and reference conductance at 200 µs sampling    |    |

|      | rate (Third approach).                                                    | 67 |

| 5.34 | Current vs. Time at 200 µs sampling rate (Third approach).                | 68 |

| 5.35 | Voltage vs. Time at 200 µs sampling rate (Third approach).                | 68 |

| 5.36 | I-V plot for 200 µs sampling rate (Third approach).                       | 69 |

| 5.37 | Resistance vs. Time at 100 µs sampling rate (First approach).             | 70 |

|      | Comparison of conductance and reference conductance at 100 µs sampling    |    |

|      | rate (First approach).                                                    | 70 |

| 5.39 | Current vs. Time at 100 µs sampling rate (First approach)                 | 71 |

|      | I-V plot for 100 µs sampling rate (First approach).                       | 71 |

|      | Resistance vs. Time at 100 µs sampling rate (Second approach)             | 72 |

|      | Conductance vs. Time at 100 µs sampling rate (Second approach)            | 72 |

|      | Reference conductance vs. Time at 100 µs sampling rate (Second approach). | 73 |

|      | Current vs. Time at 100 µs sampling rate (Second approach).               | 73 |

|      | Voltage vs. Time at 100 µs sampling rate (Second approach)                | 74 |

|      | I-V plot for 100 µs sampling rate (Second approach).                      | 74 |

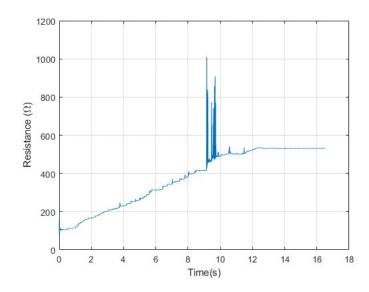

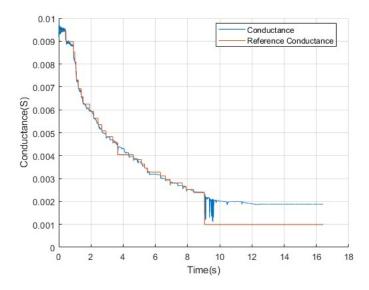

|      | Resistance vs. Time at 20 µs sampling rate (First approach)               | 75 |

|      | Comparison of conductance and reference conductance at 20 µs sampling     |    |

|      | rate (First approach).                                                    | 76 |

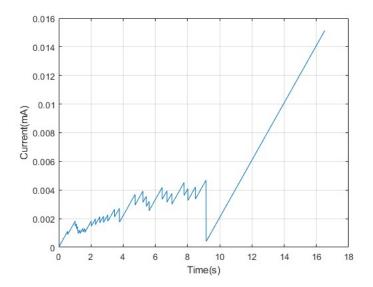

| 5.49 | Current vs. Time at 20 µs sampling rate (First approach).                 | 76 |

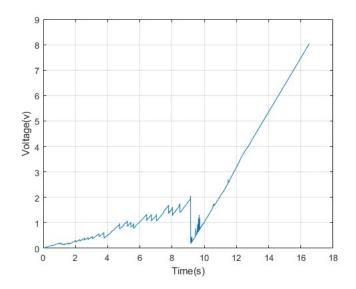

|      | Voltage vs. Time at 20 µs sampling rate (First approach).                 | 77 |

|      | I-V plot for 20 µs sampling rate (First approach).                        | 77 |

|      | Resistance vs. Time at 20 µs sampling rate (Second approach)              | 78 |

|      | Comparison of conductance and reference conductance at 20 µs sampling     |    |

|      | rate (Second approach).                                                   | 79 |

| 5.54 | Current vs. Time at 20 µs sampling rate (Second approach).                | 79 |

|      | Voltage vs. Time at 20 µs sampling rate (Second approach).                | 80 |

|      | I-V plot for 20 µs sampling rate (Second approach).                       | 80 |

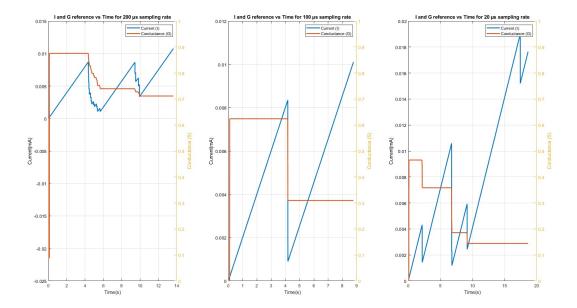

|      | Comparison of current and reference conductance at 200 µs, 100 µs and 20  |    |

|      | us sampling rates.                                                        | 81 |

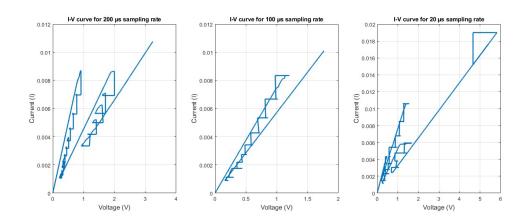

| 5.58 | I-V plots for 200µs, 100µs and 20 µs sampling rates                       | 82 |

| A.1  | LabVIEW program                                                           | 86 |

| A.2  | Measurement and Automation Explorer.                                      | 86 |

| A.3  | Remote Systems                                                            | 86 |

| A.4  | Set permissions and log in                                                | 87 |

| A.5  | LabVIEW project window                                                    | 87 |

| A.6  | LabVIEW Targets and Devices window                                        | 88 |

| A.7  | LabVIEW select programming Mode window                                    | 88 |

| A.8  | LabVIEW Project tree.                                                     | 89 |

| A.9  | Transfer data by NI MAX                                                   | 93 |

# Chapter 1 Introduction

The advancement of nanoelectronic systems and devices requires the downscaling of electronic components, such as transistors, in alignment with Moore's law. However, the miniaturization of silicon-based semiconductor devices has reached its intrinsic limitations. As a result, molecular electronics has emerged as a promising area of research. Singlemolecule electronics represent a cutting-edge field in nanoelectronics, where a molecule is positioned between source and drain contacts, functioning similarly to a transistor with a three-terminal configuration. This setup enables current flow regulated by the applied bias across a pair of terminals. Therefore, it is crucial to investigate single-molecule electrodes with a focus on electron transport mechanisms.

An important factor to consider in single-molecule electrodes is the choice of electrode material, which can be conductive, such as gold or platinum. Recently, graphene has gained attention as a semiconductive material under specific conditions, exhibiting capabilities as an electrode. To enable graphene use in single-molecule electronic devices, it is necessary to create nanogaps in the graphene electrode structure, allowing the molecule to be positioned within the nanogap between the two sides of the electrode.

The creation of nanogaps with high yield is a challenge in nanoelectronic devices, both for conductive metals and semiconductive carbon-based materials like graphene. In recent years, various techniques have been developed for nanogap formation, particularly for metal contacts such as gold, to advance nanoelectronic applications.

Electroburning is a technique used to create nanogaps in graphene by generating nanoscale separations at room temperature through the reaction of graphene's carbon atoms with oxygen. This reaction takes place in localized high-temperature regions generated by Joule heating. Compared to metals like gold, graphene demonstrates superior stability at room temperature. [1]

To control the nanogap formation process in graphene and prevent the creation of large gaps, it is required to regulate the process over time. This is achieved through the feedback-controlled electroburning technique, which uses a feedback system to make the electroburning process more precise. Another critical factor in improving the yield of nanogap fabrication in graphene is the pre-design of its shape. A well-known structure, the "bow-tie" design, has been shown to significantly enhance the efficiency of nanogap formation in graphene.[2]

## 1.1 Organization of this work

### Introduction

• Chapter 1 provided an overview of the general context of this thesis, highlighting the motivations and significance of developing a graphene electroburning platform for reliable single-molecule electrode fabrication.

### Part I

- In Chapter 2, the literature review starts by discussion on two techniques for nanogap formation in metals. Then is followed by an overview of carbon-based materials, leading to a detailed discussion of the electroburning technique for creating nanogaps in graphene. The description includes the fabrication process and an explanation of the feedback-controlled electroburning algorithm as presented in the literature.

- In Chapter 3, the theoretical physical properties of graphene are discussed. Focused on its band structure, density of states, charge transport mechanisms, and the influence of edge effects in graphene nanoribbons.

### Part II

- In Chapter 4, the transport properties of graphene, including I-V characteristics, transmission spectrum, and density of states, are analyzed. These analyses are performed using QuantumATK software to simulate three different atomic configurations, examining graphene's behavior as an electrode both with and without a bow-tie nanogap structure.

- In Chapter 5, the primary contribution of this thesis, the development of a feedbackcontrolled electroburning platform for graphene nanogap formation is presented. This involves the design of a system with an FPGA-based controller and the creation of an algorithm in the LabVIEW program, developed by the student and inspired by existing literature.

#### Conclusion

• Chapter 6 concludes the thesis by summarizing the key findings and contributions while offering recommendations for future research on this topic.

## Part I

## part one

# Chapter 2 Literature review

Electronic devices are going to be smaller and smaller; Single-molecule devices, in which individual molecules are utilized as active electronic components, have blossomed into a powerful platform for exploring novel phenomena at the molecular scale and paving the way for electronic devices downscaling to the single-molecule level. [1] In recent years, graphene has become an attractive material for research in the molecular electronic field. In experiments, gold is the most preferred electrode material in metal-molecule-metal junctions, because gold is chemically inert under ambient conditions and many anchor groups can bond to the gold surface. However, the high mobility of surface atoms of gold at room temperature leads to the instability of the molecule-gold bond in ambient conditions. The covalent bond structure gives stability to graphene at room temperature. Another advantage is that it allows for a large variety of possibilities to anchor diverse molecules as compared to metallic electrodes. While for the gold electrode, thiol and amine linkage is widely used, the carbon-based materials can not only be functionalized covalently through organic chemistry techniques but also via  $\pi$  -  $\pi$  stacking interactions of aromatic rings. Another advantage is the fact that extremely thin electrodes, ranging from (few-layer) graphene to carbon nanotubes, can be prepared. Graphene, known for its excellent stability at room temperature, can serve as an electrode in devices like transistors, sensors, and switches.

## 2.1 Top contact junctions

### 2.1.1 Mechanically controlled break junction

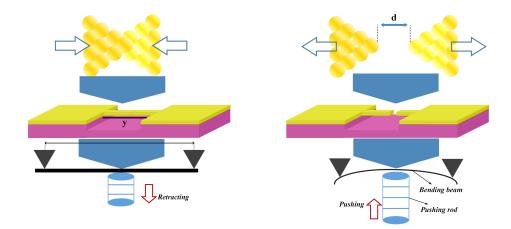

The mechanically controlled break junction (MCBJ) technique is used to fabricate electrodes with precisely adjustable separations down to a few nanometers for metal electrodes.[3] As the name implies, the distance between the electrodes is controlled by mechanical forces. the A lithographically defined metallic bridge with a notch is attached to a flexible, elastic substrate, typically made of a phosphor-bronze sheet. This substrate, serving as a bending beam, enhances flexibility and is compatible with electron beam lithography, supporting options for metal electrode deposition. A three-point bending geometry is used, where the substrate is bent by applying force at its center with a piezo-controlled pushing rod. The metallic wire is mechanically stretched until it breaks, creating a nanogap between two electrodes. This design allows for sub-picometer precision in controlling the pushing rod's displacement and controllable at the nanometer scale. [4]

Figure 2.1. Schematic of the Mechanically controlled break junction.

The MCBJ outstanding stability enables room temperature experiments to probe stability and conductance of single molecule junctions.[4] Combined with the ability to finely adjust the nano-gap without polluting the junction, this technique allows for a large number of measurements on a target molecule, enabling statistical analysis of transport measurements.[5]

A key advantage of this system is that nano-gaps form only during the experiment, making the cleanliness requirements for sample fabrication less stringent. Molecules can self-assemble onto the gold wire before the breaking process.[6] Once the nano-gap is created, the metal electrodes are coated with a monolayer of molecules. By controlling the junction, while conductance as the nano-gap size is reduced, the formation of a singlemolecule junction can be recognized. The MCBJ technique has proven useful in studying metal-molecule contact stability.[7]

Although MCBJs have led to fundamental research, they do have some limitations.<sup>[8]</sup> Developing integrated devices is challenging with MCBJs due to the constraints of bulky piezo components, which limit the larger gap size and make larger gaps difficult to create. Thermal effects are also a concern; the high electric fields applied can result in electron-phonon coupling, induce local heating, and lead to the junction instabilities.<sup>[9]</sup>

#### 2.1.2 Electromigration

Electromigration is a process in which ions are gradually transported at high electrical current densities due to the momentum transfer from conduction electrons to lattice ions. It is well studied as a major failure mode in microelectronics [10] and has now been applied

to the fabrication of nano-gap electrode.[11, 12] A voltage ramp is applied to a lithographically defined metal constriction, and electromigration of metal atoms happens, eventually leading to the breakage. This results in the formation of two nano-electrodes separated by distances as small as 1 to 2 nm. Molecules can be introduced either before or after the nano-gap is formed. Depositing molecules before the nano-gap formation is preferred, as it helps reduce contamination within the gap.[8]

The main difference of electromigrated break junctions (EBJs) compared to mechanically controlled break junctions is the solid contact between the electrodes and the substrate, offering four main advantages. First, this setup provides excellent mechanical stability, which is important for studying electron transport in molecular junctions exposed to external electromagnetic fields.[4] Second, there are no precise requisites needed for the substrate, unlike MCBJs, which require flexible substrates. Third, the planar architecture is ideal for integrating large arrays for applications. Finally, EBJs allow for the creation of three-terminal devices by using the substrate as a gate electrode. This capability enables the fabrication of devices such as single-electron transistors. [11]

A key factor in achieving high-quality junctions is controlling the local temperature in the gap, as high current densities can cause Joule heating.[13] This can result in effects such as melting, which creates large gaps, damages molecules, and forms metal debris in the gap. These metal islands interfere with the insertion of molecules and unclear the intrinsic properties of the molecules. This issue can be mitigated by reducing the total series resistance of the system and maintaining a low temperature, as demonstrated with EBJs fabricated on free-standing transparent  $SiN_x$  membranes. When the total series resistance is minimized, the resulting nano-gaps can be clean and free of debris. [14]

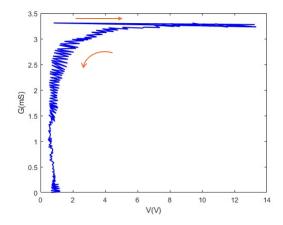

Improved yield and reproducibility have been achieved through the implementation of feedback control. Instead of relying on a single voltage ramp, the bias voltage can be adjusted by feedback control based on the junction resistance. This approach prevents thermal runaway, which could create large gaps. Feedback control has enabled the parallel fabrication of a 15-junction array in a single step by ensuring that the resistance between junctions remains lower than that of the individual junctions.[15] This method evenly distributes power dissipation across the junctions, facilitating the successful fabrication of arrays and leading to the development for integrated circuits of molecular devices.

To summarize, the limitations of using metal (gold) nano-electrodes in MCBJs and EBJs are mentioned. A significant drawback of EBJs compared to MCBJs is their inability to adjust the gap size. A combination of the two techniques can minimize this limitation, but it also restricts the range of achievable gap sizes and introduces additional challenges associated with MCBJs. The high atomic mobility of gold nano-electrodes is a significant challenge for stable room-temperature device applications.[16] Replacing gold with other metals is not ideal since many metals go to oxidation in ambient conditions. Due to these fundamental challenges, carbon-based electrodes, such as graphene, have emerged as promising alternatives for molecular electronics, which will be explored in the following section.

Figure 2.2. Conductance as a function of the bias voltage during the feedbackcontrolled electromigration process.

### 2.2 Carbon based electrode

Carbon-based electrodes exhibit several advantages over gold electrodes. CNTs offer a carrying current density up to  $10^9 \,\mathrm{A/cm^2}$ , which is 1000 times greater than that of noble metals.[17] Similarly, graphene demonstrates exceptional properties, including extraordinary thermal conductivity, high electron mobility, and impressive current density as well as the ability to support ballistic transport at room temperature [18, 19] An alternative approach for creating stable electrodes with nanometer-scale separations is the use of  $(sp^2)$  carbon-based materials. Due to their covalent bonding structure, these materials maintain stability even at high temperatures, far beyond room temperature. In contrast to more bulky metallic electrodes, these thin carbon-based electrodes minimize screening of the applied gate field, thus enhancing gate coupling. Driven by these benefits, nanogap electrodes based on carbon nanotubes have been created through oxygen-plasma etching. using a PMMA mask to define the gap, or through electrical breakdown methods. However, achieving precise control over gap sizes below 10 nm remains challenging, making it difficult to contact single molecules. Alternative methods that could lead to nanogap electrodes include atomic force microscopy (AFM), nanolithography of graphene, anisotropic etching catalyzed by nanoparticles, graphene nanogaps formed through mechanical stress, and electrical breakdown of graphene. [18]

Two main experimental techniques have been developed to create graphene nanogaps: dash-line lithographic plasma etching and feedback-controlled electroburning. The plasma etching method involves the localized cutting of graphene with oxygen plasma through an array of holes formed by dashed-line e-beam lithography in a PMMA layer. The electroburning technique, on the other hand, uses Joule heating to induce graphene breakdown in the presence of oxygen, with the process precisely controlled via a feedback system. [1]

The plasma etching approach uses chemical vapor deposition (CVD) grown graphene point contacts. By over-etching a lithographically defined pattern, this method produces nano-gaps as small as one nanometer or less. The use of large-area CVD graphene allows for the creation of nano-gap arrays across a wafer with precise positional control, however, the yield of the plasma etched devices is only 33%. [20]

The method involves the breakdown of graphene through a current-induced process, where the nano-gap size can be controlled by using Joule heating to induce graphene breakdown with partial pressure of oxygen [1] or by using feedback-controlled electroburning, a technique similar to feedback-controlled electromigration. This feedback mechanism enables precise control over the gap size, typically in the range of 1–2 nanometers. Although electroburning achieves a high fabrication yield (92% to 95%), the placement of the nanogaps is less controlled due to the random nature of the process. [20]

Despite these advancements, challenges remain in fabricating graphene nano-electrodes. One issue is the complexity and resulting low yield of device fabrication. When combined with pre-patterning, the electroburning method can achieve precise control over gap size and positioning, reaching yields as high as 95 percent. Some groups combine both techniques to enhance the yield by optimizing certain pre-patterning steps. [20] However, the electroburning process is time-consuming, especially in applications requiring large arrays of single layer graphene (SLG) junctions.

### 2.3 Electroburning

### 2.3.1 Fabrication

We begin with a brief overview of the fabrication technique that different groups have used for the fabrication of nanogap junctions in graphene electrodes. There are two types of graphene used in this approach, some groups used few-layer graphene (FLG) while others used single-layer graphene (SLG).

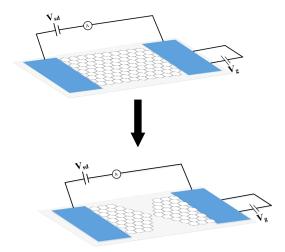

Prins et al [18], used FLG material. Few-layer graphene flakes (3–18 nm thick) are deposited onto degenerately doped silicon substrates coated with 280 nm of thermal silicon oxide, using mechanical exfoliation of kish graphite. They utilize standard wafer protection tape, which minimizes adhesive residue on the substrates. Selected few-layer graphene flakes are then patterned with Cr/Au electrodes using electron-beam lithography, followed by metal evaporation and a lift-off process in cold acetone and dichloroethane. The initial device resistances at low bias range from approximately 200  $\Omega$  to  $3k \Omega$ .

Figure 2.3. Schematic of the feedback-controlled electroburning process, before (top) and after (bottom), the formation of nanometer sized gaps in few-layer graphite flakes.

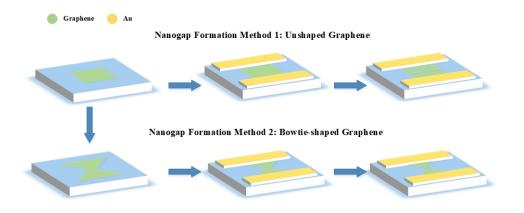

Lau et al [20], were used single layer graphene. They nano-gap fabrication approach involves a lithography process with a minimum feature size of 200 nm, followed by a feedback-controlled electroburning process that creates gaps of 0.5–2.5 nm. Out of 1079 processed devices, 776 nano-gaps were successfully formed. This study characterizes the devices before and after electroburning, examining individual nano-gap geometries through atomic force microscopy (AFM) and modeling the current density in their device structure. Graphene devices were fabricated using a passive-first, active-last process, where the graphene is transferred onto a pre-patterned silicon chip. Single-layer graphene (SLG) was grown in a chemical vapor deposition (CVD) furnace at 1090 °C, using a 1% CH4:Ar gas mixture at atmospheric pressure on a liquid copper. PMMA was spun onto the SLG/copper stack before etching away the copper with a 0.1 M ammonium persulfate solution. The PMMA/graphene stack was then rinsed in deionized water and transferred onto a pre-patterned 1 x 1 cm2 Si/SiO2 chip. Each chip contained 540 pairs of Cr/Au electrodes patterned through electron beam lithography and metal evaporation. After SLG transfer onto the metal electrodes, it was patterned into notched ribbons using electron beam lithography and oxygen plasma etching. Prior to electroburning, the devices were annealed at 350 °C for 1 hour in an Ar atmosphere to remove residual resist.

#### pre-patterning

As mentioned before, pre-patterning steps will lead to increase in the yield of nanogap formation. Xu et al [2], reported the differences in the yield with and without the pre-patterning considerations. They reported two methods in the process of fabricating graphene nanogap electrodes. In first method, devices are fabricated using exfoliated graphene flakes with typical widths ranging from 2 to 10  $\mu$ m. In the second method, exfoliated graphene flakes are first patterned into a bowtie shape through lithography and reactive ion etching. For both methods, the subsequent steps involve depositing source and drain metallic microelectrodes, followed by electroburning to create a gap in the graphene channel.

Figure 2.4. Process for fabricating of graphene nanogap electrodes. (top) device fabrication without pre-patterning. (bottom) device fabrication with pre-patterning.

Results of this group investigation[2], show that shaping a constriction in the bowtie channel dramatically increases the yield of successful nanogap formation from 30% in unshaped graphene to 80% in bowtie-shaped graphene.

#### 2.3.2 Feedback controlled electroburning

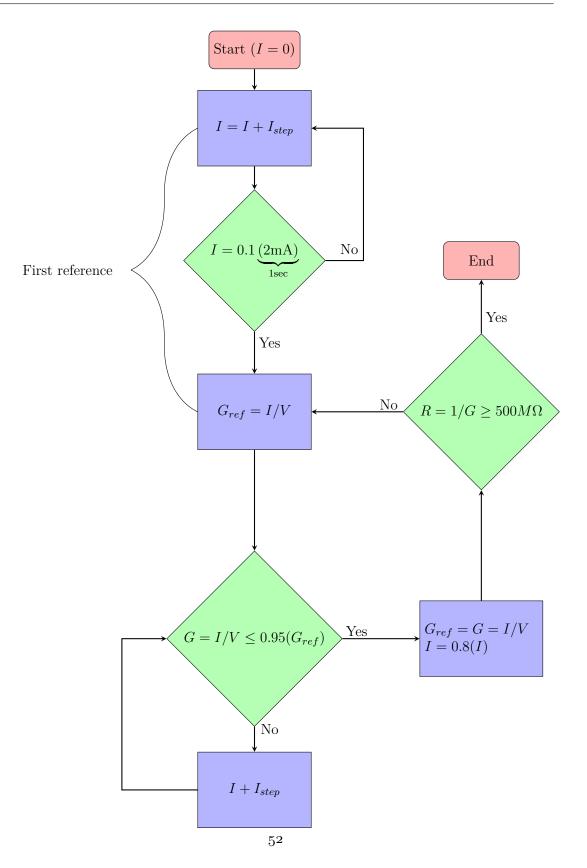

Different approaches to feedback-controlled electroburning processes exist, varying based on the sampling rates used in the system. Here, two methods reported by scientific groups are compared, the first employs a sampling rate of 200  $\mu$ s [18] while the second uses 20  $\mu$ s. [1]

#### Feedback-controlled electroburning process with 200 µs sampling rate

The feedback-controlled electroburning process is conducted in ambient air at room temperature, utilizing a control scheme similar to methods used in metallic nanowire electromigration. A voltage ramp of 1 V/s is applied to the graphite flake (FLG), with the current (I) recorded at a sampling rate of 200  $\mu$ s. Conductance ( $G = \frac{I}{V}$ ) is monitored, and the feedback is triggered if conductance drops by more than 10 percent within the last 200 mV of the ramp. Upon detecting such a drop, the voltage is immediately reduced to zero over a 10 ms interval, and a new voltage ramp is initiated. This process is repeated, gradually narrowing the graphite flake.

During the first voltage ramp (blue trace in Figure 2.5.), nonlinear I-V characteristics appear, likely due to the removal of contaminants on the flake through current annealing.

As the voltage is further increased, the initial electroburning event is observed, characterized by a downward curvature in the I-V plot, occurring here at V = 4.8 V and I = 15 mA. At this point, the feedback mechanism resets the voltage to zero, and a new ramp is applied. Throughout the electroburning progression, conductance decreases in discrete steps, and the voltage required to induce further electroburning events is reduced (indicated by the green arrow in Figure 2.5.). They conducted electroburning on 38 samples, of which 35 (92%) reached a low-bias resistance range between 500 M $\Omega$  and 10 G $\Omega$ . In the remaining cases, the feedback system was too slow to respond, resulting in gaps with infinite resistance (> 100 G $\Omega$ ). [18]

Figure 2.5. I-V traces showing the evolution (green arrow) of the feedback-controlled electroburning process with 200 µs sampling rate. The initial I-V trace is shown in blue.

#### Feedback-controlled electroburning process with 20 µs sampling rate

In this case, they employed an optimized fast-speed feedback-controlled electroburning process to create nano-gaps in graphene. The electroburning was carried out same as previous report in air at room temperature. A voltage ramp (1 V/s) was applied to the source-drain electrodes, while the corresponding source-drain current was continuously recorded at a sampling rate of 50 kHz. The conductance measured at 0.1 V was set as the reference value. When the conductance decreased by 5 percent, the applied bias was reduced by 20 percent immediately. The final conductance at the end of each cycle was used as the reference for the next cycle. This voltage ramping process was repeated until the target resistance (500 M $\Omega$  and 1 G $\Omega$ ) was achieved. [1]

The primary difference between these two methods lies in how the applied bias is adjusted. In the first method, the applied bias is reset to zero and then increased again, while in the second method, the applied bias is reduced by 20% from the previous value.

Figure 2.6. I-V traces recorded during the feedback-controlled electroburning process with 20 µs sampling rate. The initial I-V trace is shown in blue.

## 2.4 Conclusion

While feedback-controlled electroburning has demonstrated a high yield (>95%) for nanogap formation, precise control over the nanogap's location remains challenging. To address this, a constriction is introduced on the graphene, enabling nanogap fabrication with both accurate positioning and high yield due to the localized increase in current density and temperature at the constriction point. Specifically, single-layer graphene is first transferred onto a substrate and shaped into a bow-tie structure through electron beam lithography (EBL) and oxygen plasma etching. Next, feedback-controlled electroburning is applied to create a nanogap at the constriction. Statistical analysis indicates that this combined approach achieves 0.5–2.5 nm nanogaps with a fabrication yield of approximately 71 %. [20]

# Chapter 3 Graphene

## 3.1 Properties

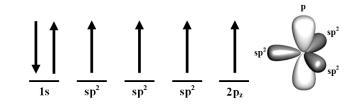

Graphene is a two-dimensional allotrope of carbon in which all carbon atoms are covalently bonded in a single plane. The structure forms a planar honeycomb lattice, characterized by a hexagonal arrangement of carbon atoms. The honeycomb lattice dedicate graphene with exceptional properties, including high electrical conductivity, mechanical strength, and thermal stability, making it a focus of extensive research in various scientific and technological fields. Graphene can transform into various forms: wrapping it into a sphere creates buckyballs, rolling it into a cylinder forms carbon nanotubes, and stacking multiple graphene layers results in graphite. Additionally, cutting graphene into narrow strips produces nanoribbons, which have become a significant focus of current research. Understanding the properties of graphene is crucial, as it provides the foundation for explaining nanoribbons' electronic behaviors. This insight is essential for exploring their potential applications in advanced materials and nanotechnology. In graphene, the 2s orbital interacts with the  $2p_x$  and  $2p_y$  orbitals to form three  $sp^2$  hybrid orbitals, as illustrated in Figure 3.1. These  $sp^2$  orbitals create three strong covalent bonds known as  $\sigma$ -bonds, which are localized along the plane connecting neighboring carbon atoms and provide graphene great mechanical strength. In addition to the  $\sigma$ -bonds,  $2p_z$  orbitals form covalent  $\pi$ -bonds. The  $\pi$ -bond electron cloud is distributed perpendicular to the plane of the carbon atoms and is relatively delocalized due to the weaker binding of  $2p_z$  electrons to the nuclei. These delocalized  $\pi$ -electrons are crucial for the unique electronic properties of graphene to understand their behavior and applications. [21]

### **3.2 Band Structure**

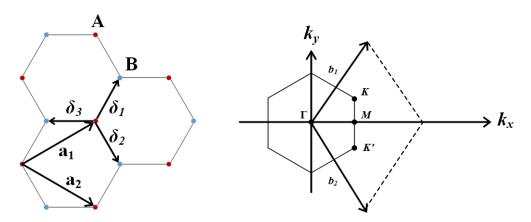

Graphene is a two-dimensional material composed of carbon atoms arranged in a hexagonal lattice. This structure can be described as a triangular lattice with a basis of two carbon atoms per unit cell. The lattice vectors are defined as :

$$\mathbf{a}_1 = \frac{a}{2}(3,\sqrt{3}), \quad \mathbf{a}_2 = \frac{a}{2}(3,-\sqrt{3}),$$

Figure 3.1. Left: The arrangement of electrons and their relative spin in graphene. Right: Illustration of the graphene orbitals.

Figure 3.2. Left: Honeycomb lattice structure of graphene. Right: Corresponding Brillouin zone with the basis vectors of the reciprocal space. The Dirac cones are located at the K and K' points.

where  $a \approx 1.42$  Å is the carbon-carbon bond length. The reciprocal lattice, critical for understanding electronic behavior, is described by the vectors:

$$\mathbf{b}_1 = \frac{2\pi}{3a}(1,\sqrt{3}), \quad \mathbf{b}_2 = \frac{2\pi}{3a}(1,-\sqrt{3}).$$

The Dirac points are particularly important, located at the corners of the graphene Brillouin zone (BZ). These points, labeled  $\mathbf{K}$  and  $\mathbf{K}'$ , are given by:

$$\mathbf{K} = \left(\frac{2\pi}{3a}, \frac{2\pi}{3\sqrt{3}a}\right), \quad \mathbf{K}' = \left(\frac{2\pi}{3a}, -\frac{2\pi}{3\sqrt{3}a}\right)$$

The three nearest-neighbor vectors in graphene's real-space lattice, denoted by  $\delta$ :

$$\boldsymbol{\delta}_1 = \frac{a}{2}(1,\sqrt{3}), \quad \boldsymbol{\delta}_2 = \frac{a}{2}(1,-\sqrt{3}), \quad \boldsymbol{\delta}_3 = -a(1,0)$$

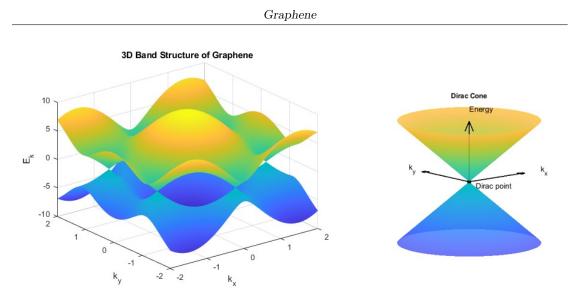

The  $\Gamma$ -point is located at the center of the Brillouin zone, while the M-points are positioned at the midpoints of the zone's edges. The K-points, including K and K', are of particular importance as they are the locations where the conduction and valence bands meet, defining the unique electronic behavior of graphene. [22]

The analytical solution for the electronic band structure of graphene can be derived using an approximation model based on the time-independent Schrödinger equation :

$$H\Psi(k,\mathbf{r}) = E(k)\Psi(k,\mathbf{r}),$$

where H is the Hamiltonian operator, representing the total energy of the system.

$$H = \frac{\hbar^2}{2m} \nabla^2 + \sum U(\mathbf{r} - \mathbf{R}),$$

The first term of the above equation corresponds to the kinetic energy, and the second term corresponds to the potential energy  $U(\mathbf{r} - \mathbf{R})$  arising from the lattice atoms. The vector  $\mathbf{R}$  corresponds to the position of a lattice point, indicating the shift from one unit cell to another in the periodic structure of the material. By substituting the Hamiltonian into the time-independent Schrödinger equation, we obtain a second-order partial differential equation that governs the behavior of the wave function  $\Psi(k, r)$  for an electron in a periodic potential. This form leads to a more complex equation that accounts for the periodicity of the lattice and determines the allowed energy states E(k) for the electron. To solve this, we must find wave function solutions that satisfy the conditions imposed by the crystal's periodic structure, involving techniques such as Bloch's theorem. Bloch's theorem states that the one-particle states in a periodic potential can be chosen so that

$$\Psi(r) = u_k(r) \exp(i\mathbf{k} \cdot \mathbf{r}),$$

where  $u_k(r)$  is a periodic function with the periodicity of the lattice, and **k** belongs to the Brillouin zone. This implies that

$$\Psi(r + \mathbf{R}) = \exp(i\mathbf{k} \cdot \mathbf{R})\Psi(r),$$

The equation shows that the wave function  $(\Psi)$  at a position **r** and at a translated position  $\mathbf{r} + \mathbf{R}$  is related by a phase factor  $e^{i\mathbf{k}\cdot\mathbf{R}}$ . [23]

The calculation of the band structure of graphene around the Fermi energy was performed using the tight-binding approximation. In the tight-binding model, only the interactions between the nearest neighbor carbon atoms are considered. Thus, taking into account that the overlap between wave functions for adjacent  $p_z$  orbitals is negligible, the energy of  $\pi$  band of graphene is obtained as:

$$E_{C,V}(k) = \pm \gamma \sqrt{1 + 4\cos\left(\frac{k_y a}{2}\right)\cos\left(\frac{\sqrt{3}k_x a}{2}\right) + 4\cos^2\left(\frac{k_y a}{2}\right)}$$

where  $\gamma$  is a parameter representing the electronic interaction between the nearest neighbor carbon atoms in graphene, and is estimated as 3.15 eV. [24]

$k_x$  and  $k_y$  are the wave number of the wave function representing an electronic state in  $\pi$  band of graphene. Positive and negative signs in above equation correspond to  $E_C$ and  $E_V$ , where C and V represent the conduction band and valence band, respectively.

Figure 3.3. Left: The  $\pi$  electronic band structure of graphene obtained by the nearest-neighbor tight-binding model. Right: Dirac cone.

#### 3.3**Density of states**

Massless particles in graphene are described using Dirac's relativistic quantum mechanical Around the Dirac points, the energy dispersion is linear and can be wave equation. expressed as :

$$E(k) = \pm \hbar v_F |k| = \pm \hbar v_F \sqrt{k_x^2 + k_y^2},$$

where  $\mathbf{k}$  is now expressed in spherical coordinates of the Dirac cone in the right part of figure 3.3.,  $\hbar$  is the reduced Planck's constant, and  $v_F$  is the Fermi velocity. The density of states (DOS), g(E), represents the number of mobile electrons or holes in a material at a given temperature. In two dimensions, the total number of states between an energy Eand a small interval dE is given by the differential area in k-space (dA), divided by the area of one k-state.

$$g(E) dE = \frac{2g_z \, dA}{(2\pi)^2 / \Omega}$$

The factor of 2 is for spin degeneracy,  $g_z$  is for cone degeneracy and  $\Omega$  is the area of lattice. There are six equivalent K-points, and each K-point is shared by three hexagons; therefore,  $g_z = 2$  for graphene. To determine dA, consider a circle of constant energy in k-space. The perimeter of the circle is  $2\pi k$ , and the differential area obtained by an incremental increase of the radius by dk is  $2\pi k dk$ . Therefore, the density of states (DOS):

$$g(E) = \frac{2|k\,dk|}{\pi|dE|}$$

where q(E) has been normalized to the  $\Omega$ . Substituting from the energy dispersion equation yields a linear density of states (DOS) appropriate for low energies:

$$g(E) = \frac{2}{\pi (\hbar v_F)^2} |E|$$

The absolute value of E is necessary because energy can be either positive (electrons) or negative (holes). At the Fermi energy ( $E_F = 0$ ), the DOS vanishes to zero even though there is no bandgap. This is the reason why graphene is considered a semi-metal in contrast to regular metals that have a large DOS at the Fermi energy. [21]

### 3.4 Charge transport mechanism

To describe the charge transport mechanisms in single-molecule devices, several theoretical models have been developed. In broad terms, coherent tunneling is explained by Landauer theory. Applying the Landauer-Büttiker theory to a nanoscale device allows expressing the steady state current as :

$$I = \frac{2q}{h} \int \gamma(E) \pi \frac{D(E)}{2} \left[ f_1(E) - f_2(E) \right] dE$$

Where, q represents the charge of an electron, h is Planck's constant, D(E) is the density of states,  $f_1(E)$  and  $f_2(E)$  are the Fermi-Dirac distribution functions corresponding to the source and drain contacts, respectively. If the channel is a single molecule,  $\gamma$  has a simple physical interpretation; it represents the "broadening" of the molecular energy levels due to the finite lifetimes of the electrons in a molecular level. The product  $\frac{\gamma \pi D}{2}$  is dimensionless and it represents the number of conducting channels at energy E. We can rewrite the last equation as:

$$I = \frac{2q}{h} \int T(E)M(E) \left[ f_1(E) - f_2(E) \right] dE$$

Where T(E) denotes the transmission probability,  $M(E) = \gamma(E)\pi \frac{D(E)}{2}$  specifies the number of conducting channels or modes available for transport.

The transmission probability T(E) can be expressed using scattering theory in terms of the mean free path for backscattering,  $\lambda(E)$ , and the channel length L as:

$$T(E) = \frac{\lambda(E)}{\lambda(E) + L}$$

This equation is derived from the principles of scattering theory, which analyzes the influence of scattering on electronic transport properties. This expression for T(E) is valid across different transport regimes:

- In the diffusive limit  $(L \gg \lambda, T \approx \lambda/L \ll 1)$ .

- In the ballistic limit  $(L \ll \lambda, T \to 1)$ .

- In the quasi-ballistic transport regime  $(L \approx \lambda, T < 1)$ .

The Fermi functions at the source and drain contacts are given by  $f_1 = f(E, E_{F1})$  and  $f_2 = f(E, E_{F2})$ , where  $E_{F1}$  and  $E_{F2}$  are the Fermi energy levels at the source and drain contacts, respectively. The Fermi function is defined as:

$$f(E, E_F) = \frac{1}{e^{(E-E_F)/k_BT} + 1}$$

where  $k_B$  is Boltzmann's constant and T is the absolute temperature. From  $\Delta E_F = -qV$ , substituting into the above equation:

$$I = \left[\frac{2q^2}{h} \int T(E)M(E)\left(-\frac{\partial f}{\partial E}\right)dE\right]V$$

And the conductance can be write as [25]:

$$G = \frac{I}{V} = \frac{2q^2}{h} \int T(E)M(E) \left(-\frac{\partial f}{\partial E}\right) dE$$

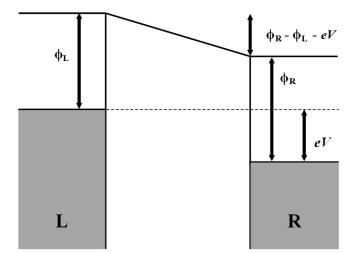

#### 3.4.1 Nanogap Modelling for Graphene

To characterize the graphene nano-gaps by measuring low-bias current-voltage (I-V) curves we can exploit the Simmons model, where the current density j in a tunnel junction with a barrier in the x-direction ( $\phi(x)$ ) is described as:

$$j = \frac{4\pi m e}{h^3} \int_0^\infty \left[ f_L(\epsilon) - f_R(\epsilon) \right] d\epsilon \int_0^\epsilon T(\epsilon_x) d\epsilon_x$$

The Fermi distribution in the leads is given by a chemical potential  $\mu$ , and  $T(\epsilon_x)$  represents the tunneling probability for an electron with kinetic energy  $\epsilon_x$  in the x-direction.

$$f(\epsilon) = \frac{1}{e^{-\frac{(\epsilon)-\mu}{k_BT}} + 1}$$

In the low-temperature limit  $(k_B T \ll \mu_L, \mu_R, f(x))$ , the Fermi distribution effectively becomes a step-function, and current density can be written as:

$$j = \frac{e4\pi m}{h^3} \int_{\mu_R}^{\mu_L} d\epsilon \int_0^\epsilon d\epsilon_x T(\epsilon_x)$$

The tunneling probability for the barrier with constant hight can be derived using the Wentzel-Kramers-Brillouin approximation, which expresses it as:

$$T(\epsilon_x) = e^{-\beta d \sqrt{\phi - \epsilon_x}}$$

Where

$$\beta = \frac{2\sqrt{2m}}{\hbar}$$

and

$$d = x_2 - x_1$$

When the work function on the left electrode,  $\phi_L$ , equals that on the right  $\phi_R$ , j becomes:

$$j \approx \frac{e}{2\pi h d^2} \left[ (\phi - \mu_L) e^{-\frac{4\pi d \sqrt{2m(\phi - \mu_L)}}{h}} - (\phi - \mu_R) e^{-\frac{4\pi d \sqrt{2m(\phi - \mu_R)}}{h}} \right]$$

This approximation can be good. [26, 18]

Figure 3.4. Asymmetric tunnel junction with different work functions on the left and right leads.

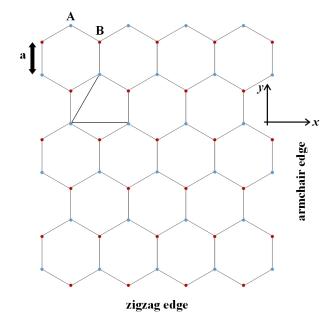

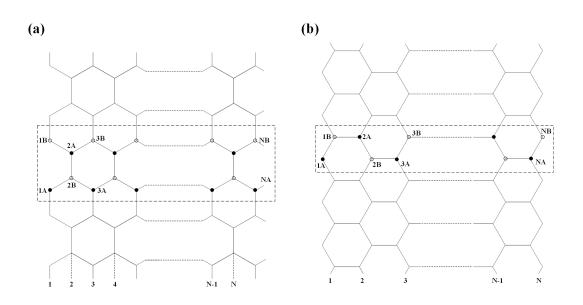

## 3.5 Graphene Nanoribbons

Graphene nanoribbons (GNRs) are narrow, rectangular structures derived from graphene sheets, with widths ranging from a few nanometers to tens of nanometers. While their lengths can extend indefinitely, their high aspect ratio classifies them as quasi-one dimensional nanomaterials. GNRs are a relatively addition to the family of nanomaterials and can exhibit either metallic or semiconducting properties.[21] The electronic structure of graphene is sensitive to structural modifications like atomic vacancies, which disrupt lattice symmetry and altering conductivity. In finite-sized graphene, edges act as onedimensional defects, significantly affecting electronic properties of graphene. Graphene edges are classified as zigzag edge or armchair edge, with arbitrary edge shapes comprising combinations of both.[24]

Its predicted that when graphene adopts a ribbon structure with infinitely extended edges, introducing zigzag edges into the honeycomb lattice leads to the emergence of nonbonding  $\pi$  electronic states, referred to as "edge states," at the Dirac point. These edge states appear alongside the  $\pi$  valence and  $\pi^*$  conduction bands inherited from the ideal graphene structure. The edge states are predominantly localized at the graphene edges and significantly influence the electronic properties of these regions. In contrast, the presence of armchair edges has a negligible effect on the electronic structure near the Dirac point. [27]

The local breaking of symmetry between A and B sites (as shown in figure 3.6) at zigzag edges plays a crucial role in graphene's electronic structure. As described by the

Figure 3.5. Nanoribbon geometry with both zigzag and armchair edges.

Hamiltonian equation, the electronic properties of graphene are governed by the interactions between wave functions of adjacent carbon atoms on A and B sites. The topology of the carbon atom network dictates the solutions to the Schrödinger equation.

When the symmetry between A and B sites is preserved, the electronic structure remains similar to that of ideal graphene, even in the presence of defects. However, breaking this symmetry due to defects significantly changes the electronic structure. This sublattice symmetry breaking is a fundamental reason for the emergence of edge states at zigzag edges.

Conversely, armchair edges maintain the symmetry between A and B sites. For ideal bulk graphene, with its infinite honeycomb lattice, the A and B sites are inherently symmetrical. Consequently, graphene with armchair edges exhibits an electronic structure like to that of ideal graphene, and defects that do not disrupt sublattice symmetry have minimal impact on its electronic properties. [24]

Figure 3.6. Graphene with armchair edge (a) and zigzag edge (b), where the carbon atoms belonging to sublattices are classified by labeling with A or B.

# Part II part Two

## Chapter 4

# Simulation by QuantumATK

In this section, we analyze the behavior of graphene as an electrode. Initially, the properties of simple graphene without a nanogap are examined, followed by an analysis of graphene with different nanogap geometries. This involves assessing the density of states (DOS), transmission spectrum, and I-V characteristics for each configuration. By comparing these results, we aim to understand how different nanogap designs impact graphene's effectiveness as an electrode in single-molecule transistors.

## 4.1 Computational methods

The software used for all simulations in this chapter is QuantumWise Atomistic ToolKit (ATK) by Synopsys, a platform that integrates various tools for atomic-scale modeling. It includes multiple simulation engines, such as those based on tight-binding Hamiltonians and density functional theory (DFT). For the simulations involving the density of states (DOS), transmission spectrum, and I-V characteristics of graphene electrodes with and without nanogaps, the parameters listed in Table below were applied to ensure consistency across analyses.

Table 1 presents the parameters used in the equilibrium simulations of graphene with and without nanogap for the LCAO calculator in QuantumATK. The Van der Waals correction and counterpoise correction are disabled in this simulation.

| LCAO CALCULATOR               |                                          |  |

|-------------------------------|------------------------------------------|--|

| LCAO Basis Set                | Exchange correlation: GGA                |  |

|                               | Functional: PBE                          |  |

|                               | Pseudopotential: PseudoDojo              |  |

|                               | Basis set: Medium                        |  |

| Numerical Accuracy            | Density mesh cut-off: Default setting    |  |

|                               | Occupation method: Fermi-Dirac           |  |

|                               | Broadening: 1000 K                       |  |

|                               | k-points: [9.0, 9.0, 201.0] Å            |  |

| Iteration Control             | Default settings                         |  |

| Algorithm                     | Default settings                         |  |

| Contour Integral<br>Parameter | Default settings                         |  |

| Poisson Solver                | Solver Type: Conjugate gradient          |  |

|                               | Boundary conditions:                     |  |

|                               | A direction: Dirichlet                   |  |

|                               | B direction: Periodic boundary condition |  |

|                               | C direction: Dirichlet                   |  |

| Electrode<br>Parameters       | Default settings                         |  |

Table 4.1.

QuantumATK DFT Calculator

The graphene layer was assumed to extend infinitely in the transverse direction, using periodic boundary conditions for the B direction in the Poisson Solver. The other boundary conditions are set to Dirichlet in the Poisson Solver to account for graphene edge passivation. Tables 2 and 3 list those applied in the transmission spectrum and device density of states calculations.

| Transmission Spectrum Analysis |                                                    |  |

|--------------------------------|----------------------------------------------------|--|

| Energy range                   | $E_0 = -1.5 \text{ eV}$                            |  |

|                                | $E_0 = -1.5 \text{ eV}$<br>$E_1 = +1.5 \text{ eV}$ |  |

|                                | Points = 301                                       |  |

| k-point sampling               | Density:                                           |  |

|                                | $K_A = 27$                                         |  |

|                                | $K_B = 27$                                         |  |

| Infinitesimal                  | 1e-06 eV                                           |  |

| Self-energy<br>calculator      | Recursion                                          |  |

| Energy zero<br>parameter       | Average Fermi level                                |  |

Table 4.2.

QuantumATK Transmission Spectrum settings

| Device Density of States Analysis |                         |  |

|-----------------------------------|-------------------------|--|

| Energy range                      | $E_0 = -1.5 \text{ eV}$ |  |

|                                   | $E_1 = +1.5 \text{ eV}$ |  |

|                                   | Points = 301            |  |

| k-point sampling                  | Density:                |  |

|                                   | $K_A = 15$              |  |

|                                   | $K_B = 15$              |  |

| Contributions                     | All                     |  |

| Infinitesimal                     | 1e-06 eV                |  |

| Self-energy<br>calculator         | Recursion               |  |

| Energy zero<br>parameter          | Average Fermi level     |  |

Table 4.3.

QuantumATK Device Density of States settings

Lastly, Table 3.4. contains the parameters used in the analysis of the I-V curves.

| IV curve Analysis         |                         |  |

|---------------------------|-------------------------|--|

| Voltage Bias              | $V_0 = 0 V$             |  |

|                           | $V_1 = 2 V$             |  |

|                           | Points = 11             |  |

| Energy range              | $E_0 = -1.5 \text{ eV}$ |  |

|                           | $E_1 = +1.5 \text{ eV}$ |  |

|                           | Points = 301            |  |

| k-point sampling          | Density:                |  |

|                           | $K_A = 15$              |  |

|                           | $K_B = 15$              |  |

| Infinitesimal             | 1e-06 eV                |  |

| Self-energy<br>calculator | Recursion               |  |

Table 4.4. QuantumATK I-V curve settings

## 4.2 Configuration 1

The first configuration involves the analysis of the transmission spectrum and device density of states properties of a graphene layer without nanogap. The graphene sample used in this study consists of 133 hexagons, with 7 arranged in the transversal direction and 19 in the transport direction.

Figure 4.1. Graphene Device structure without nanogap.

The transmission spectrum analysis shows the contributions of the transmission of charge carriers across a range of energy values. The observed symmetrical pattern in the

transmission spectrum indicates an ideal graphene layer with minimal structural defects because this configuration is done for a large graphene sheet.

Figure 4.2. Transmission Spectrum of graphene without nanogap.

The device density of states (DOS) shows a nearly flat profile near the Fermi energy and there is a sharp peak observed around 1.4 eV.

Figure 4.3. Device Density of states of graphene without nanogap.

## 4.3 Configuration 2

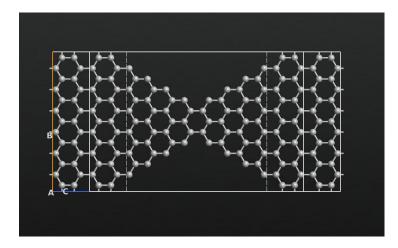

The second configuration analyzed features of a graphene nanogap in a bow-tie structure. In this structure, two central carbon atoms are retained while the atoms above and below these two are removed to form the bow-tie shape. Initially, the graphene device consisted of 75 carbon atoms, with 5 atoms along the transverse direction and 15 along the transport direction. After the removal of 9 atoms from the regions above and below the central atoms, the structure now contains a total of 66 carbon atoms.

Figure 4.4. Bow-tie nanogap structure of graphene with 2 carbon atoms in the center.

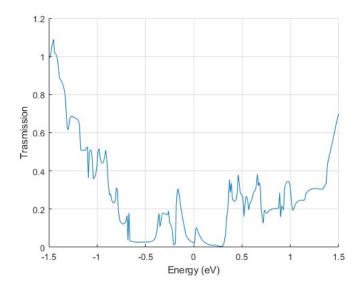

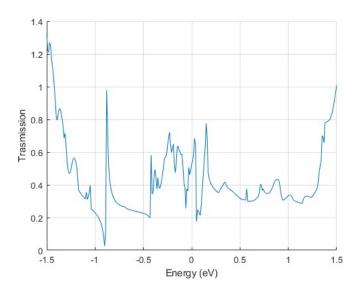

To study the graphene as an electrode with a bow-tie nanogap structure, the transmission spectrum is first analyzed. The result shows that the transmission spectrum has a low value compared to the unshaped graphene layer within the same energy range. This corresponds to the band gap of the central semiconducting armchair edge ribbon. This behavior arises due to the asymmetric alignment of the electrode Fermi levels with the band edges.

Figure 4.5. Transmission Spectrum of bow-tie nanogap graphene structure with 2 carbon atoms in the center.

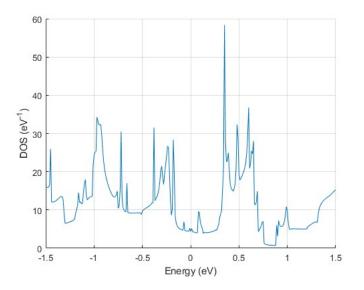

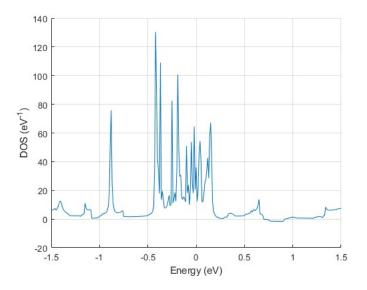

The device density of states shows sharp peaks, particularly in the range of -1 to 1 eV. As observed in this structure and the corresponding transmission spectrum results, the symmetry of graphene is broken by the creation of a bow-tie shaped nanogap. This structural modification introduces localized electronic states at the edges of the nanogap, which are responsible for the observed peaks in the device density of states.

Figure 4.6. Density of states for bow-tie nanogap graphene structure with 2 carbon atoms in the center.

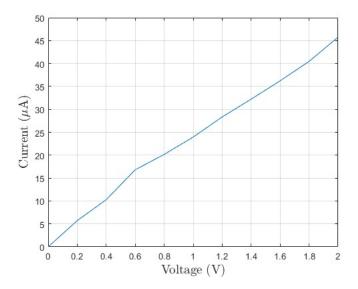

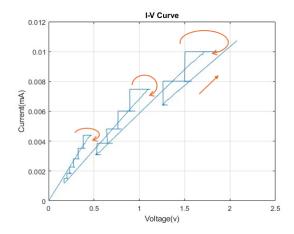

The I-V characteristics of the bow-tie nanogap graphene structure illustrate charge flow between the left and right electrodes, showing well match pattern with the I-V behavior (reported from [28]) of simple pure graphene.

Figure 4.7. I-V curve for bow-tie nanogap graphene structure with 2 carbon atoms in the center.

## 4.4 Configuration 3

Another graphene electrode structure with a bow-tie shape, featuring a single carbon atom at the center, has been simulated. Initially, the graphene device consisted of 66 carbon atoms, arranged with 6 atoms along the transverse direction and 11 atoms along the transport direction. After removing 25 atoms from the regions above and below the central atom, the resulting structure contains a total of 41 carbon atoms.

Figure 4.8. Bow-tie nanogap structure of graphene with 1 carbon atom in the center.

The transmission spectrum once again exhibits edge effects between -1 and 1 eV, corresponding to the energy range of the left and right Fermi levels, characterized by an asymmetric pattern. However, it exhibits slightly higher transmission values within the same energy range compared to the second configuration.

Figure 4.9. Transmission Spectrum of bow-tie nanogap graphene with 1 central carbon atom.

The density of states (DOS) for the structure with a single carbon atom in the center indicates that charge localization in the energy range of -0.5 to 0.5 eV is significantly more present compared to the second configuration. This can be attributed to the presence of only one carbon atom at the center of the graphene layer, which leads to reduced charge

delocalization. Consequently, the DOS becomes more concentrated in this case, reflecting the enhanced localization effects.

Figure 4.10. Density of states for bow-tie nanogap graphene with 1 central carbon atom.

The I-V characteristic for the graphene bow-tie shaped nanogap with a single central carbon atom clearly demonstrates the transfer of charge between the left and right electrodes.

Figure 4.11. I-V curve for bow-tie nanogap graphene with 1 central carbon atom.

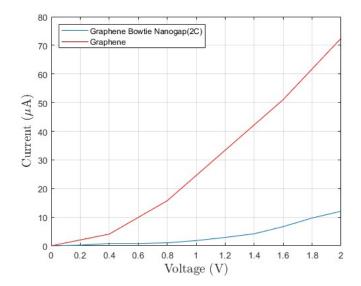

## 4.5 Charge transport comparison

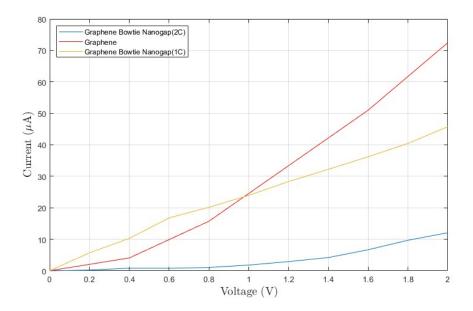

The current voltage (I-V) characteristics for all three configurations are compared. By comparing the I-V curves of the graphene bow-tie shaped nanogap with one and two central carbon atoms, and the I-V characteristic of a simple graphene layer (as reported in the study conducted by another student[28], which is not included in this thesis ), it is evident that both nanogap structures facilitate charge transport. However, the structure with a single central carbon atom exhibits a higher current flow compared to the two central carbon atoms bow tie nanogap. An interesting observation from the comparison between the single centered carbon atom bow-tie nanogap and simple graphene is that, between 0 and 1 volt, the nanogap structure shows higher current flow, indicating more conductive behavior. At 1 volt, the current for the nanogap structure with one central carbon atom and simple graphene structure without nanogap is 24  $\mu$ A, but as the voltage increases from 1 to 2 volts, the simple graphene electrode passes more current.

Figure 4.12. I-V curve comparison for graphene with and without nanogap structures.

### 4.6 Conclusion

In conclusion, the simulations show that pure graphene exhibits an ideal transmission spectrum with distinct step-like features. However, transitioning to bow-tie configurations disrupts these ideal properties. Notably, the transmission spectrum spikes observed when the graphene nanoribbon chain is opened. [29]