## **POLITECNICO DI TORINO** Master's Degree in Electronic Engineering

## Master's Degree Thesis

Implementation and validation of a hardware countermeasure against fault injection attacks

Supervisors:

Prof. Maurizio MARTINA Prof. Guido MASERA Eng. Mustapha EL MAJIHI

> Candidate: Davide MUSCIA

October 2024

If you do something and it turns out well enough, you should go ahead and do something wonderful. Steve Jobs

Se fai qualcosa e risulta abbastanza buona, dovresti andare avanti a fare qualcosa di meraviglioso. Steve Jobs

# Abstract

Data integrity in a processor is crucial to ensure that computations are processed without errors, preserving the consistency and reliability of the results. This is especially important in applications such as automotive, aerospace, and other critical sectors. Modern processor architectures have been shown to be vulnerable to fault injection attacks, which involve injecting errors into the circuit using simultaneous laser beams that target single or multiple data bits to compromise their integrity and extract sensitive information. This method has proven effective over the past decade through the observation of faulty behavior. Designing countermeasures against fault injection attacks has become essential to ensure data integrity, particularly with the increasing use of open-source implementations such as RISC-V, where the attacker has full knowledge of the architecture. This work proposes a fault detection methodology called «permutation-based homomorphic tags». It involves providing a redundant hardware implementation that computes arithmetic and logic operations in a permuted domain associated with a specific key. The permuted execution ensures that no faults have been injected into the processed data by preventing attackers from consistently targeting the same bits, as the permutation key is randomly changed. The outcome of this study is the hardware implementation of a permuted Arithmetic Logic Unit (ALU) and a permuted multiplier, where two different techniques were explored: an iterative approach aimed at low area consumption, and the 2-way Karatsuba algorithm for reducing latency. The architecture was implemented targeting the 64-bit RISC-V CVA6 application processor. The design was validated on Xilinx Artix-7-100T and Kintex-7 FPGAs and it was estimated the cost of the countermeasure resulted in a 7.67x area overhead and a 2.4x increase in the critical path for the ALU, a 0.31x area overhead and a 1.44x increase in the critical path for the iterative multiplier, and a 32.3xarea overhead and an 8.81x increase in the critical path for the Karatsuba multiplier.

*Keywords:* data integrity, fault injection attacks, countermeasure, permutationbased homomorphic tags, CVA6, RISC-V

# **Table of Contents**

| Li            | st of                           | Tables                                                                                                                                                                             | VIII                                                  |

|---------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| $\mathbf{Li}$ | st of                           | Figures                                                                                                                                                                            | IX                                                    |

| A             | crony                           | yms                                                                                                                                                                                | XII                                                   |

| 1             | Intr                            | <b>roduction</b><br>1.0.1 Thesis objectives and structure                                                                                                                          | 1                                                     |

| 2             | <b>Env</b><br>2.1<br>2.2        | vironment         SystemVerilog         CVA6         2.2.1         RISC-V                                                                                                          | 6                                                     |

| 3             | Hor<br>3.1<br>3.2<br>3.3<br>3.4 | nomorphic security tags and permutationDefinition of the countermeasurePermutationDepermutationEffectiveness countermeasure                                                        | $\begin{array}{c} 10\\12\end{array}$                  |

| 4             | Per<br>4.1<br>4.2<br>4.3<br>4.4 | muted ALU         Elementary operations         4.1.1       Extraction single bit         4.1.2       Set single bit         4.1.2       Set single bit         Boolean operations | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|          |        | 4.4.3   | Shift left by a power of $2 \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 32 |

|----------|--------|---------|--------------------------------------------------------------------------------------|----|

|          |        | 4.4.4   | Barrel shifter                                                                       | 34 |

|          | 4.5    | Count   | operations                                                                           | 36 |

|          |        | 4.5.1   | Population count                                                                     |    |

|          |        | 4.5.2   | Leading/trailing zeros count                                                         |    |

| <b>5</b> | Per    | muted   | multiplier                                                                           | 40 |

|          | 5.1    | Iterati | ve way                                                                               | 40 |

|          | 5.2    | 2-way   | Karatsuba algorithm                                                                  | 44 |

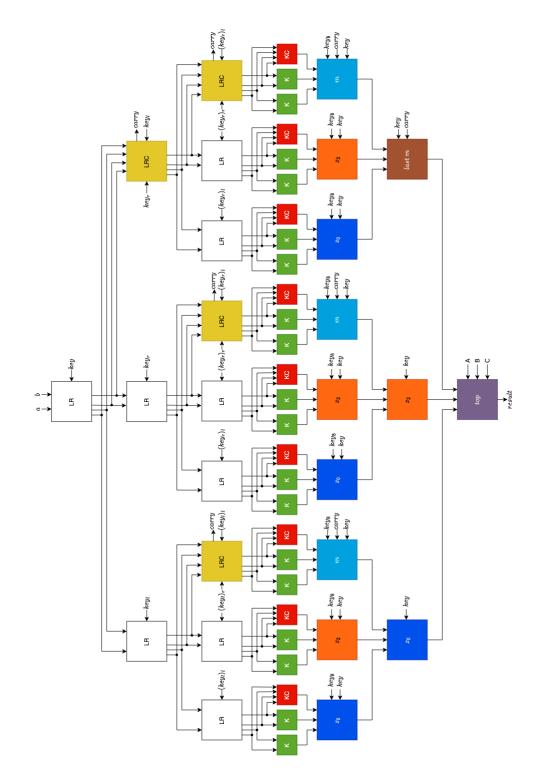

|          |        | 5.2.1   | Pre-computation tree                                                                 |    |

|          |        | 5.2.2   | Layer of multiplication                                                              |    |

|          |        | 5.2.3   | Reconstructive tree                                                                  |    |

| 6        | Vali   | dation  | process and analysis                                                                 | 56 |

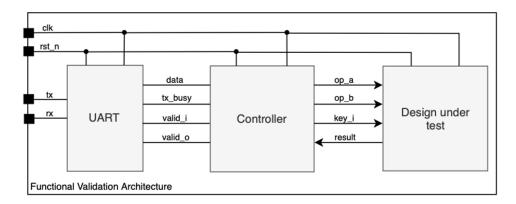

|          | 6.1    | Hardw   | vare interface                                                                       | 57 |

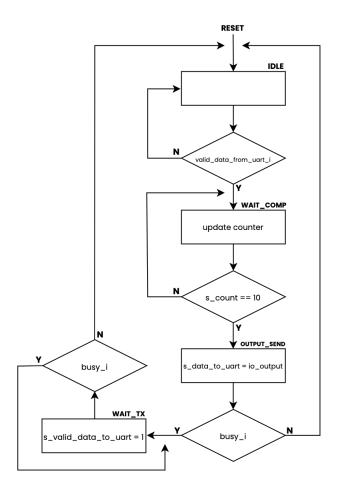

|          |        | 6.1.1   | Controller                                                                           | 58 |

|          | 6.2    |         | are interface                                                                        |    |

|          | 6.3    |         | 8                                                                                    |    |

|          |        |         | Adder and shifter comparison                                                         |    |

|          |        | 6.3.2   | ALU comparison                                                                       |    |

|          |        | 6.3.3   | Multiplier comparison                                                                |    |

| 7        | Cor    | clusio  | n                                                                                    | 66 |

|          |        |         |                                                                                      | 00 |

| Bi       | ibliog | graphy  |                                                                                      | 68 |

# List of Tables

| 3.1 | Fredkin gate truth table                                                                                                                 | 9  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | ALU operations supported by the CVA6 core Comparison cases as function of zero $bit(z)$ and carry-out $bit(carry)$                       |    |

| 6.1 | Area and critical path results for CLA, permuted CLA and permuted shifter                                                                | 61 |

| 6.2 | Area and critical path results for ALUs                                                                                                  | 62 |

| 6.3 | Area and critical path results for CVA6 multiplier, permuted Iterative<br>multiplier and 2-way Karatsuba approach in three different run |    |

|     | strategies                                                                                                                               | 63 |

| 6.4 | Possible optimizations permuted multiplier components                                                                                    | 65 |

| 7.1 | Final integration choices for the CVA6 core                                                                                              | 66 |

# List of Figures

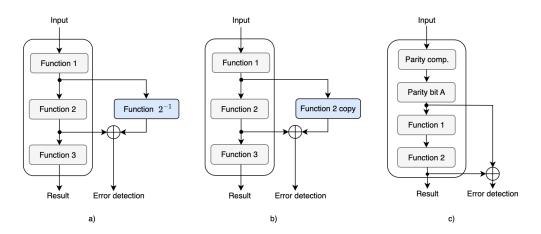

| 1.1  | Block diagram representation of redundancy techniques: a) hardware redundancy, b) temporal redundancy, c) information redundancy         | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

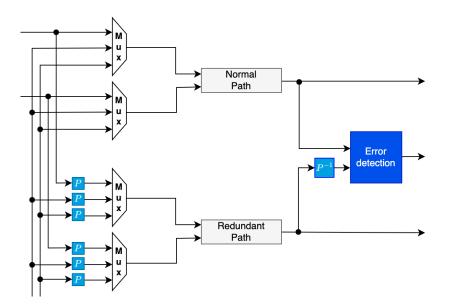

| 1.2  | Dual modular redundancy and error detection example. The Per-<br>mutation blocks( $P$ ) are stages of transformation of the operands for | 2  |

|      | the new alternative domain while the Depermutation block $(P^{-1})$ is                                                                   |    |

|      | a stage of reconstruction of the native result                                                                                           | 3  |

| 2.1  | Placement countermeasure in CVA6 pipeline                                                                                                | 7  |

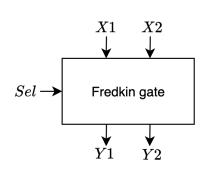

| 3.1  | Fredkin gate block                                                                                                                       | 9  |

| 3.2  | Dichotomous tree for 32-bit permutation function                                                                                         | 10 |

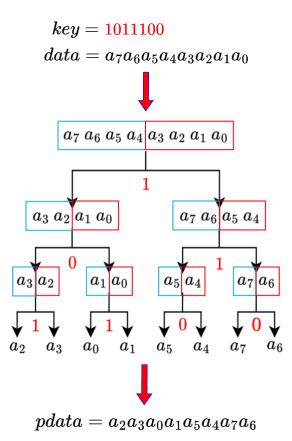

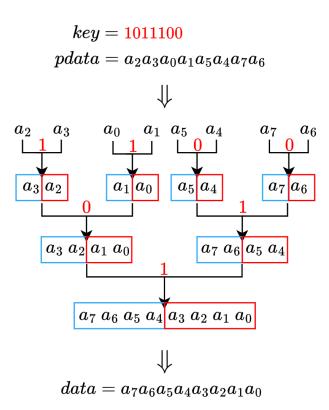

| 3.3  | Permuted dichotomous tree example for 8-bit operand                                                                                      | 11 |

| 3.4  | Depermuted dichotomous tree example for 8-bit operand                                                                                    | 12 |

| 4.1  | Extraction block                                                                                                                         | 16 |

| 4.2  | Extraction dichotomous tree example for 8-bit permuted operand .                                                                         | 17 |

| 4.3  | Set block                                                                                                                                | 18 |

| 4.4  | Set dichotomous tree example for 8-bit permuted operand $\ldots$ .                                                                       | 18 |

| 4.5  | Permuted AND logic function example for 8-bit operand                                                                                    | 19 |

| 4.6  | Full-Adder block with $sum(s)$ and $carry-out(c_o)$ generation                                                                           | 20 |

| 4.7  | Propagation problem for Ripple-Carry Adder connection typology .                                                                         | 21 |

| 4.8  | Full-Adder block with generate(g) and $propagate(p)$ generation                                                                          | 21 |

| 4.9  | Unrolling carry recurrence                                                                                                               | 22 |

|      | Propagate/generate block                                                                                                                 | 22 |

|      | Dichotomous tree example for 8-bit CLA                                                                                                   | 23 |

| 4.12 | Permuted propagate/generate block                                                                                                        | 24 |

| 4.13 | Dichotomous tree example for 8-bit permuted CLA                                                                                          | 24 |

| 4.14 | Subtracter adaptation for native and permuted domain                                                                                     | 25 |

|      | Comparison examples for $>, <, \ge, =$                                                                                                   | 26 |

|      | White block                                                                                                                              | 28 |

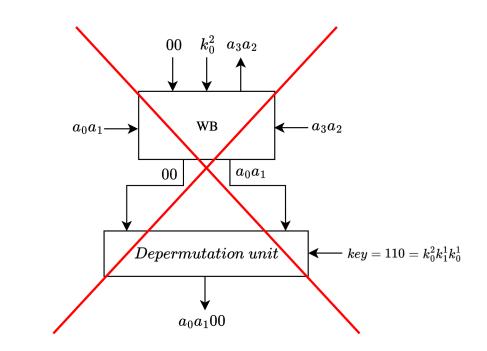

| 4.17 | Permuted shift left by 1 example with White $Block(WB)$                                                                                  | 29 |

| 4.18 | Permuted shift left by 2 example with White Block(WB)                          | 30 |

|------|--------------------------------------------------------------------------------|----|

| 4.19 | White key block                                                                | 31 |

|      | Black block                                                                    | 31 |

| 4.21 | Permuted shift left by 2 example with White Block(WB), Black                   |    |

|      | Block(BB) and White Key Block(WKB)                                             | 32 |

| 4.22 | Black block key                                                                | 33 |

| 4.23 | Permuted shift left by a power of 2 adaptation for 16-bit $K_D$ gener-         |    |

|      | ation with White Block(WB) and Black Block Key(BBK).                           | 34 |

| 4.24 | Barrel shifter configuration with multiplexer selection                        | 34 |

|      | SIMD example for 16-bit permuted operand                                       | 35 |

|      | Leading zeros example                                                          | 36 |

|      | Trailing zeros example                                                         | 36 |

|      | Population example                                                             | 36 |

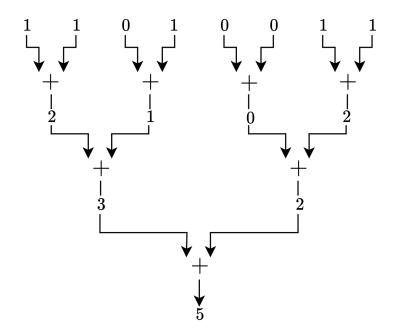

|      | Population counter example for 8-bit permuted operand                          | 37 |

|      | Leading/trailing zeros block                                                   | 38 |

|      | Leading zeros counter example for 8-bit permuted operand                       | 39 |

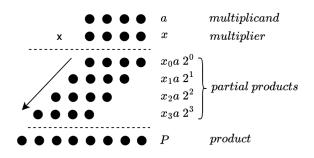

| 5.1  | 4-bit dot notation iterative approach                                          | 40 |

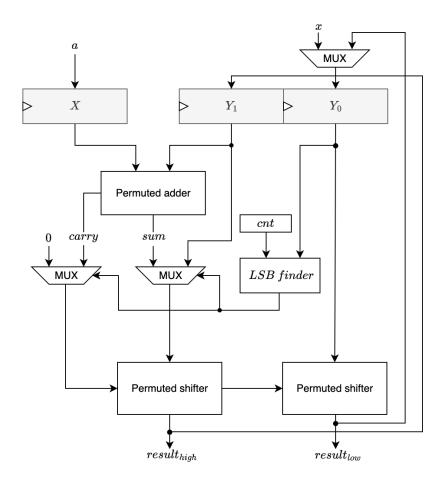

| 5.2  | Permuted iterative multiplier architecture                                     | 42 |

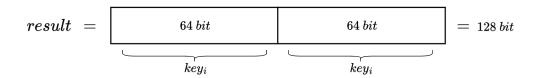

| 5.3  | 128-bit permuted product management                                            | 43 |

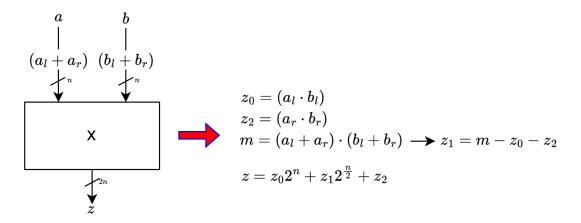

| 5.4  | Partial contribution deriving the 2-way Karatsuba algorithm                    | 44 |

| 5.5  | Trichotomous tree example for 16-bit permuted 2-way Karatsuba                  |    |

| 0.0  | multiplier                                                                     | 47 |

| 5.6  | Tree-like example structure for 16-bit parallelism reduction                   | 48 |

| 5.7  | Key-extraction example for 16-bit permuted operand                             | 49 |

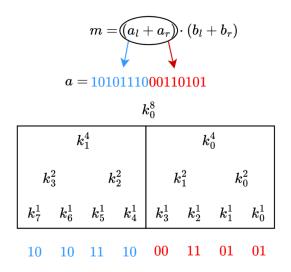

| 5.8  | Carry decomposition formulas for $m$ computation $\ldots \ldots \ldots \ldots$ | 50 |

| 5.9  | Carry decomposition example for $m$ computation with 8-bit operand             | 51 |

| 5.10 | Key extension example from 4-bit operand to 8-bit                              | 52 |

| 5.11 | Key misalignment example with difference in the MSB position                   | 53 |

|      | Reorder example with difference in the MSB-1 position                          | 54 |

|      | Adaptation process from $key_1$ to $key_2$ example                             | 55 |

|      | Key misalignment example in m computation                                      | 55 |

| 0.14 |                                                                                | 00 |

| 6.1  | Functional validation architecture                                             | 57 |

| 6.2  | Functional Controller graph                                                    | 58 |

|      |                                                                                |    |

# Acronyms

#### ALU

Arithmetic Logic Unit

#### ASIC

Application Specific Integrated Circuit

#### AXI

Advanced eXtensible Interface

#### $\mathbf{BB}$

Black Block

#### BBK

Black Block Key

#### CA2

2's Complement

#### CLA

Carry-Lookahead Adder

#### CPU

Central Processing Unit

#### CSA

Carry-Save Adders

#### $\mathbf{CSR}$

Control and Status Register

#### $\mathbf{CU}$

Control Unit

#### DUT

Design Under Test

#### $\mathbf{F}\mathbf{A}$

Full-Adder

#### $\mathbf{FPU}$

Floating Point Unit

#### $\mathbf{FSM}$

Finite State Machine

#### $\mathbf{FVA}$

Functional Validation Architecture

#### ISA

Instruction Set Architecture

#### $\mathbf{LSB}$

Least Significant Bit

#### $\mathbf{M}\mathbf{M}\mathbf{U}$

Memory Management Unit

#### $\mathbf{MSB}$

Most Significant Bit

#### OCB

Ones Count Block

#### $\mathbf{PGB}$

Propagate Generate Block

#### $\mathbf{PMP}$

Physical Memory Protection

#### PPGB

Permuted Propagate Generate Block

#### RCA

Ripple-Carry Adder

#### SIMD

Single Instructions Multiple Data

#### UART

Universal Asynchronous Receiver-Transmitter

#### WB

White Block

#### WKB

White Key Block

# Chapter 1 Introduction

In recent years, the way we interact with our surroundings has changed dramatically, especially thanks to the rise of the Internet of Things.

These networked devices consist of sensors, which are managed by an increasing number of processors running programs and exchanging data. While this represents technological advancement, it also expands the attack surface. Among all applications, the automotive, aerospace, and defense industries, which require complete reliability and security, are the most sensitive in this regard.

The reason for this concern lies in the fact that modern processor architectures have been shown to be vulnerable to **fault injection attacks**, as noted in [1], [2], and [3]. Fault injection involves introducing errors that can cause timing malfunctions or logic errors in the circuit, enabling information exfiltration from the faulty behavior and computation on false data. This means corrupting the contents of circuit registers or control signals while the circuit is still operating, using multi beams laser attack, which is a kind of attack that raises problems difficult to manage among all the possibilities(electromagnetic injection, clock glitch, power glitches,...).

The objectives of these injections can vary, with the most critical being the maintenance of **data integrity** during program execution. Indeed, it is possible to bypass security controls, such as permissions and authenticity checks, to gain complete access to sensitive information from any running critical section.

The type of attack discussed here involves physical contact with the target system, which, for example, can cause voltage or current changes, such as those that occur in a bridging fault by introducing a short circuit.

Moreover, the rise of embedded systems in both the public and private sectors has significantly expanded the vulnerability landscape. With the growing use of open-source implementations like RISC-V, where attackers have full knowledge of the architecture, the level of sensitivity becomes even higher. The adoption of these implementations has proven necessary for many companies to reduce production costs, by benefiting from community support without internal big expenses in the specific areas of validation and verification.

Consequently, designing countermeasures against fault injection attacks has become essential to ensure data integrity. Existing countermeasures consist of both correction and **detection methods**, but we propose focusing on the latter. While correction techniques show good effectiveness, they come at a much higher cost and are not as widely adopted.

Fault detection, in particular, consists of hardware or software techniques capable of recognizing any unauthorized alterations, with the objective of maintaining system functionality, data integrity, and security.

At the hardware level, systems can adopt three mechanisms as proposed by [4]:

- Hardware redundancy involves duplicating the circuit section to be protected in order to compare differences with the result obtained. It is the most straightforward and simplest to implement, but it has the highest cost in terms of area, as it doubles the resource usage. It can also be applied using a multiple modular redundancy approach, with costs proportional to the number of redundancies.

- **Temporal redundancy** involves repeating operations either in reverse or through duplication, so that the result of the computation can be compared with the previous or duplicated value. Among the three methods, it has the highest cost in execution time, as the same operation is performed twice.

- Information redundancy involves adding state information, such as parity bits or checksum. Of the three methods, it is the most efficient in terms of resource overhead, as it only extends the parallelism of the data being transmitted.

**Figure 1.1:** Block diagram representation of redundancy techniques: a) hardware redundancy, b) temporal redundancy, c) information redundancy

The technique discussed in this study is the dual modular hardware redundancy, which duplicates the path of interest, but this alone is not sufficient. The ability to target multiple bits simultaneously has made simple hardware replication ineffective and more vulnerable to injections. Therefore, an additional transformation of the data is necessary to enhance the system and make it more difficult for the attacker to select bits in the detection branch.

This work proposes a fault detection methodology called **«permutation-based homomorphic tags**», which provides a redundant hardware implementation that performs arithmetic and logic operations, in a permuted domain associated with a specific key that is randomly changed. The main goal is to preserve data integrity by verifying the correctness of the results.

Given that we aim to maintain data integrity in a processor, the choice of permutation is not trivial: it is required a parallel domain to the original one that operates at high frequencies and within the same clock cycle. The primary focus is to identify the best transformation for logical and arithmetic operations, and only then choose the replication area. Thus, the design, implementation, and adaptation of arithmetic-logic components, capable of handling the generated tags, are developed.

In our case, these architectural considerations were implemented targeting the 64-bit RISC-V CVA6 application core.

Figure 1.2: Dual modular redundancy and error detection example. The Permutation blocks(P) are stages of transformation of the operands for the new alternative domain while the Depermutation block( $P^{-1}$ ) is a stage of reconstruction of the native result.

#### **1.0.1** Thesis objectives and structure

The objective of the internship is to develop a permuted Arithmetic Logic Unit(ALU) for a 64-bit core target, precisely the CVA6 application core of the openHW Group, that will be used by the team for Application Specific Integrated Circuit(ASIC) integration.

Here it is necessary to support all the extensions of the core according to the RISC-V Instruction Set Architecture(ISA), and then it is necessary to validate and verify all the modules developed in SystemVerilog.

After this introductory Chapter 1, the thesis is structured as follows:

- Chapter 2: presents a description of the countermeasure development environment. We discuss the language adopted in Section 2.1 and the CVA6 application processor, as the target core, along with its RISC-V ISA in Section 2.2.

- **Chapter 3**: introduces the permutation-based homomorphic tags countermeasure in Section 3.1, including the definition of the new representation domain and its properties.

- Chapter 4: presents the implementation of the arithmetic-logic components required for the realization of the redundant ALU. We start with two elementary operations, such as single-bit extraction and setting values, in Sections 4.1.1 and 4.1.2. We then address Boolean operations in Section 4.2, the addition operation and its adaptations in Section 4.3, the shift operation in Section 4.4, and count operations in Section 4.5.

- Chapter 5: presents the implementation of a permuted multiplier using an iterative approach in Section 5.1 and a 2-way Karatsuba approach in Section 5.2.

- **Chapter 6**: discusses the validation phase, providing a description of the validation architecture in Sections 6.1 and 6.2, followed by a discussion of the results obtained.

- Chapter 7: summarizes the conclusions of this thesis, including a brief overview of the decisions made regarding countermeasure integration.

# Chapter 2 Environment

The topic of this thesis project is based on a previous research conducted by G. Leplus, O. Savry, L. Bossuet and M. Panigati, at CEA-Leti (Grenoble, France), which developed the theory of elementary components of countermeasures as noted in [5], [6] and [7].

Moreover the work is characterized by a dual aim: first to extend the existing adder and shifter architectures from an initial 32-bit parallelism to 64-bit parallelism; second to implement from scratch the «permuted ALU» consistent the one of the CVA6, aiming to handle all its extensions, as well as to explore a potential architecture for the multiplier, envisioned as a standalone component.

In this chapter it is introduced the hardware description language used, as proposed by the [8], [9], [10] articles, and the target core for the integration of the countermeasure as noted in [11] and [12].

## 2.1 SystemVerilog

SystemVerilog is the hardware description language used for countermeasure development.

It is a language that was standardized by the IEEE around 2005 with the primary goal of extending Verilog and combining VHDL to design, simulate, test and implement electronic systems.

Additionally to simplify the description of the hardware behavior from a syntactic point of view, it incorporates features of the C++ programming language, which makes easier the simulation and verification phases through a more object-oriented approach.

Its main features include:

- 1. Syntax extensions and compatibility: maintains compatibility with the previous language, so a project written in Verilog is still valid in SystemVerilog, despite the fact that the latter introduces new extensions that make writing code clearer and more fluent. For example, it introduces new data types such as *logic* in place of *wire* and *reg* without creating ambiguity and destitution between signals.

- 2. Advanced data types and interconnections: introduces from the software world the use of data types such as *enum* and *struct* that makes easier the reading of the code

- 3. Classes and Assertions: when writing Testbench, it allows an objectoriented description that can greatly simplify the code; assertions allow us to visualise that certain conditions during the test phase are fulfilled.

According to these features and the compatibility of our target core language, SystemVerilog is a versatile and ideal language for the development of our countermeasure where before one design language and another for verification were needed.

## 2.2 CVA6

CVA6 is a configurable 32- or 64-bit single-issue RISC-V application core developed by the OpenHW group for ASIC or FPGA implementations. Specifically, it is the name of a GitHub repository in SystemVerilog, where the CV prefix identifies it as a member of the CORE-V family, following th RISC-V specification, and the A6 indicates that it is an application class processor with a six-stage execution pipeline.

In terms of on-board processor functionality, the CVA6 is characterized by many hardware components: Control and Status Register(CSR), Advanced eXtensible Interface(AXI), L1 write-through or write-back configurable cache, optional Floating Point Unit(FPU), optional Memory Management Unit(MMU), optional Physical Memory Protection(PMP) and others.

However, our focus for implementing a countermeasure is limited to the ALU. The countermeasure in fact wants to act where the integrity of the data could be endangered, and therefore in correspondence with computation processes.

It is possible to conclude thus that the area of our competence it is mostly the Execution Stage of the pipeline, where the data manipulation takes place, and a small percentage of the general core pipeline where the permutation domain is propagated. Figure 2.1 shows this area zoomed in.

#### 2.2.1 RISC-V

The CORE-V family is a member of a group of processors following the RISC-V specification.

It is a computer architecture started in 2021 by the Berkeley University, in order to propose an open and flexible ISA in respect Intel or Arm ISAs that, for example, are not open; «V» indicates the fifth generation of the project.

The ISA includes some faculties, through extensions, to provide more functionality: floating point(F), multiplication and division(M), atomic(A), compressed(C), or other manipulation. All this makes the ISA generic in nature, giving the possibility of customising its CPU according to the needs of the application.

In general following this approach can be observed three different features that makes this kind of implementation different:

- Open Source: RISC-V is an open-source architecture, which means that anyone can use, modify and implement the specification without paying royalties.

- Modularity: RISC-V is modularly designed, allowing developers to select specific functionalities

- Standardisation: RISC-V is supported by a foundation that promotes standardisation between implementations.

Figure 2.1: Placement countermeasure in CVA6 pipeline Source: image taken from the CVA6 GitHub [12]

## Chapter 3

# Homomorphic security tags and permutation

The alternative domain plays a fundamental role in the countermeasure, as the main challenge is developing networks capable of delivering authentic results, where here the concept of authenticity refers to maintaining a direct connection to the original data. Even more crucial is ensuring excellent performance at the processor level while leaving for a potential verification stage.

This approach forms the basis for the countermeasure developed, through the definition of homomorphism.

## 3.1 Definition of the countermeasure

A homomorphism is

"a map between two algebraic structures of the same type that preserves the operations of the structures"

Wikipedia, 2020, [13]

In other words given an operation and two operands u and v we assert that  $\phi$  is a homomorphism if the following equality holds:

$$\phi(u * v) = \phi(u) \cdot \phi(v) \tag{3.1}$$

This means that calculating the operation  $\langle * \rangle$  on u and v and applying the function  $\phi$  should generate the same result as applying  $\phi$  on the two operands and only after performing the operation  $\langle \cdot \rangle$ .

Now if the intent is to create an alternative domain, while maintaining a connection through a verification stage, can be observed well how the transformation sought is convenient to be homomorphic. In fact, the complexity would come in looking, for each logical or arithmetic operation, the respective permuted version that would enforce the equality of the Formula 3.1.

For us, equality means that performing the operation (\*\*) on u and v, and then converting to the new domain, must generate the same result as the operation (\*) on the authenticity tags. Consequently, considering that we are working with binary numbers, the choice of the function  $\phi$  fell on the transposition function, i.e.

"the modification of the position of certain elements within an ordered object"

Treccani, 2020, [14]

The function constituting the countermeasure, however, is not just about transposition. In fact, it is necessary a function over which it is possible to have decision power in reversing the ordering.

In this way can be constructed the «permutation» function, an association between a transposition and a key with the power to decide whether to make an inversion rather than an identity. Permute will consist of dividing an input data into blocks of bits and rotate them according to the associated control signal.

In searching for an elementary block capable of emulating the behavior just described, it is found a cell called «Fredkin gate», as in Figure 3.1, containing three inputs: two input data X1 and X2 and a selection signal *Sel*. According to its truth Table 3.1, swap is performed when the control signal is worth 1 and vice versa identity when the control signal is worth 0.

X1SelX2Y1Y20 0 0 0 0 0 1 1 0 0 0 0 1 1 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 1 1 1 0 0 1 1 1 1 1 1

Figure 3.1: Fredkin gate block

Table 3.1: Fredkin gate truth table

Using this cell, as an elementary module, on a multilevel structure we are able to define the permutation.

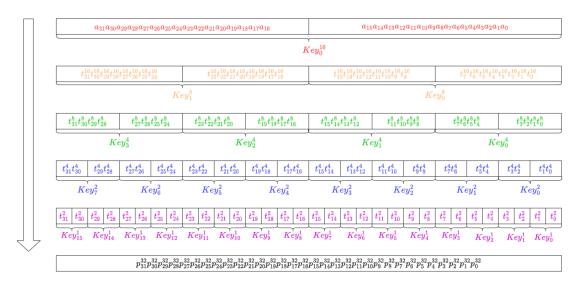

## 3.2 Permutation

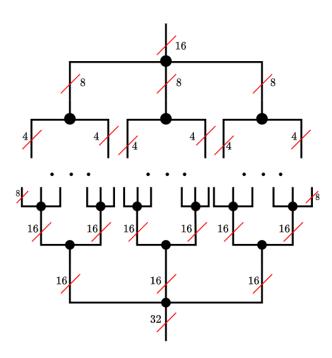

The permutation function is a dichotomous tree in which each node consists of a Fredkin gate. The idea of the tree structure is shown in Figure 3.2 in which can be observed the organization on multiple levels for a 32-bit data and how each block on each section is on the power of 2, consecutive and not overlapping.

The application of permutation begins dividing the input into two halves, with the Most Significant Bit(MSB) of the key serving as the control signal. Then, by progressing to the least significant bits, the same principle of division into two halves is applied to each sub-block, until the lowest level of the tree is reached, consisting of single-bit section.

It means that if it is taken a 64-bit data the first division would be in two 32-bit blocks, the second division would be in four 16-bit blocks and so on up to sixty-four 1-bit blocks. In the transition from one stage to the next, an output signal is generated at the initial level of parallelism, which becomes the input to the subsequent stage. This process occurs over a depth of  $\log_2(n)$ , where *n* represents the width of the input data.

Figure 3.2: Dichotomous tree for 32-bit permutation function Source: image taken from the [5] article

Constructing the permutation, it is used the notation  $Key_j^i$  to refer to a single bit of the key: *i* represents the size of the subsection on which to make the decision; *j* represents the position index of the key dedicated to that specific size. For example, the  $Key_{[7:0]}^2$  notation represent the eight bits related to swap control for 2-bit groups.

To generalize now for a generic width of the data is fundamental to understand how

can be determined the size of the permutation key. Starting from the last Figure 3.2 and applying the function from the MSB toward the Least Significant Bit(LSB), can be seen how for 16-bit groups only one bit is needed, for 8-bit groups two bits are needed until sixteen bits for 1-bit groups. It means that key is characterized by 31 bits of width in correspondence to a 32-bit data.

In this way, the iterative application and the use of power-of-2 blocks allow to conclude that the dimension must be n - 1 bits for data of width n. This property is illustrated in the example of Figure 3.3, which shows an 8-bit data and its corresponding 7-bit key with the notation  $k = k_0^4 k_1^2 k_0^2 k_3^1 k_2^1 k_1^1 k_0^1$ .

Figure 3.3: Permuted dichotomous tree example for 8-bit operand

Here according to the theory presented, an ascending key association and dichotomous tree with depth  $\log_2(n=8) = 3$  are observed, where the distinction into blue and red blocks facilitates the idea of division for each sub-section into two halves, on which to take a swap or identity decision.

### 3.3 Depermutation

Complementary to the permutation function it is needed the inverse operation to bring back the native domain, presumably in a symmetric way with respect to the previous one.

The new function in this case is called «depermutation» and creates the opposite association of the same key, from the LSB toward the MSB, generating an inverted alternation of swap and identity. The structure is still a dichotomous tree with depth  $\log_2(n = 8) = 3$  just flipped, as Figure 3.4 reports.

Figure 3.4: Depermuted dichotomous tree example for 8-bit operand

Here, making a comparison with the permutation Figure 3.3, can be easily observed the similarity with a symmetric application of the function where the distinction into blue and red blocks, once again, facilitates the idea of division for each sub-section into two halves, on which to take a swap or identity decision.

#### **3.4** Effectiveness countermeasure

The proposed theory explains a technique capable of changing the representation domain, by being able to easily recreate native data when needed, where the homomorphic choice is the main aspect, because allows the insertion of a comparison stage to detect a possible attack.

However, it still did not answer the most important question:

#### Why would the proposed countermeasure work?

The fault injection technique uses simultaneous laser beams that target single or multiple data bits to compromise their integrity and extract sensitive information. Our aim is to create redundant hardware that computes arithmetic and logic operations in a permuted domain associated with a specific key, where the permuted execution ensures that no faults have been injected, into the processed data, by preventing attackers from consistently targeting the same bits, as the permutation key is randomly changed.

The last aspect of randomness corresponds to the crucial point because it does not allow predictions about the placement of the new weights and thus not predict the operations. In fact, as the permutation example in Figure 3.3 shows, the new representation will be directly dependent on each individual bit of the key: a change of a single bit could result in large variations in the representation.

It is still necessary that each network, developed in accordance with the technique, makes no reference to the native representation neither uses a static arrangement of weights. This means to have an internal propagation of bits that differs with each new key generated; in this way, the circuit will also possess their own intrinsic and completely random computation and will guarantee not predictable execution. So far then, the new domain transformation technique has been presented; it must now concern with understanding how the different recurring operations can be handled.

If, for example, we were to refer to the sum operation, a random sorting of the new permuted data would not allow us to solve the calculation in the classical sense, but would require the search for dedicated hardware. Similarly, the same may apply to those simpler operations such as extraction and set that are normally done through indexing.

# Chapter 4 Permuted ALU

The ALU is a fundamental component within a Central Processing Unit(CPU), responsible for performing arithmetic and logical operations. It represents the heart of the computational process, as it handles basic mathematical operations such as addition and subtraction and logical operations such as shift, AND, OR, NOT. Each operation performed by the ALU is supervised by a Control Unit(CU), that decides which operation is to be performed according to the instructions, and which data to select from the many registers present.

The countermeasure discussed above is applied here, where the task is to adapt the elementary components to create a new redundant path, thereby forming a «permuted ALU». By recalling that CVA6 is the target core, can be observed that the ALU can be divided into four sections:

- Logic circuits: performs logic operations

- Addition: performs the sums and count operations

- Shift: performs shift operations

- Comparison: compare two operands

By adapting these four sections and their components, we are able to develop all 63 planned operations as listed in Table 4.1. To achieve this, two elementary operations of single-bit extraction and set are analysed first, and only after the Boolean operations, an adder, a shifter and finally some networks for count operations. The latter, despite containing the adder, are characterised by dedicated structures in order to handle permutation.

| Termited ALC              |           |                                  |  |  |

|---------------------------|-----------|----------------------------------|--|--|

|                           |           |                                  |  |  |

| Description               | Operation | Description                      |  |  |

| AND                       | СРОР      | Count set bits                   |  |  |

| AND with inverted operand | CPOPW     | Count set bits in word           |  |  |

| OR                        | CLZ       | Count leading zero bits          |  |  |

| OR with inverted operand  | CLZW      | Count leading zero bits in word  |  |  |

| Exclusive OR              | CTZ       | Count trailing zeros             |  |  |

| Exclusive NOR             | CTZW      | Count trailing zero bits in word |  |  |

| Add                       | МАХ       | Maximum                          |  |  |

| Add word                  | MAXU      | Unsigned maximum                 |  |  |

| Add unsigned word         | MIN       | Minimum                          |  |  |

| Subtract                  | MINU      | Unsigned minimum                 |  |  |

| Subtruct Word             | SLTS      | Set if Less Than, Signed         |  |  |

| Chift Loft Logical        | CUTU      | Cot if Loop Than Unsigned        |  |  |

Operation

ANDL ANDN ORL

ORN

XORL XNOR

| ADD      | Add                                   | MAX       | Maximum                                                                           |

|----------|---------------------------------------|-----------|-----------------------------------------------------------------------------------|

| ADDW     | Add word                              | MAXU      | Unsigned maximum                                                                  |

| ADDUW    | Add unsigned word                     | MIN       | Minimum                                                                           |

| SUB      | Subtract                              | MINU      | Unsigned minimum                                                                  |

| SUBW     | Subtruct Word                         | SLTS      | Set if Less Than, Signed                                                          |

| SLL      | Shift Left Logical                    | SLTU      | Set if Less Than, Unsigned                                                        |

| SRL      | Shift Right Logical                   | BCLR      | Single-Bit Clear                                                                  |

| SRA      | Shift Right Arithmetic                | BCLRI     | Single-Bit Clear (Immediate)                                                      |

| SLLW     | Shift Left Logical Word               | BEXT      | Single-Bit Extract                                                                |

| SRLW     | Shift Right Logical Word              | BEXTI     | Single-Bit Extract (Immediate)                                                    |

| SRAW     | Shift Right Arithmetic Word           | BINV      | Single-Bit Invert                                                                 |

| SHIADD   | Shift left by 1 and add               | BINVI     | Single-Bit Invert (Immediate)                                                     |

| SH2ADD   | Shift left by 2 and add               | BSET      | Single-Bit Set                                                                    |

| SH3ADD   | Shift left by 3 and add               | BSETI     | Single-Bit Set (Immediate)                                                        |

| SHIADDUW | Shift unsigned word left by 1 and add | SEXTB     | Sign extend byte, 16-bit encoding                                                 |

| SH2ADDUW | Shift unsigned word left by 2 and add | SEXTH     | Sign extend halfword, 16-bit encoding                                             |

| SH3ADDUW | Shift unsigned word left by 3 and add | ZEXTH     | Zero extend halfword, 16-bit encoding                                             |

| ROL      | Rotate Left (Register)                | REV8      | Byte-reverse register                                                             |

| ROR      | Rotate Right (Register)               | ORCB      | Bitwise OR-Combine, byte granule                                                  |

| RORI     | Rotate Right (Immediate)              | SLLIUW    | Shift-left unsigned word (Immediate)                                              |

| ROLW     | Rotate Left Word (Register)           | CZERO_EQZ | Moves zero to a register <i>rd</i> , if the condition <i>rs2</i> is equal to zero |

| RORW     | Rotate Right Word (Register)          | CZERO_NEZ | Moves zero to a register <i>rd,</i> if the condition <i>rs2</i> is nonzero        |

| RORIW    | Rotate Right Word by Immediate        | NE        | Branch if not equal                                                               |

| EQ       | Branch if equal                       | GES       | Branch if greater than or equal signed                                            |

| LTS      | Branch if less than signed            | GEU       | Branch if greater than or equal unsigned                                          |

| LTU      | Branch if less than unsigned          |           |                                                                                   |

|          |                                       |           |                                                                                   |

**Table 4.1:** ALU operations supported by the CVA6 coreSource: definitions from the [15] book and the [16] manual

### 4.1 Elementary operations

Elementary operations are understood to be extractions and sets of individual bits usually provided for specific operations. An extraction for example is fundamental in the case of arithmetic shift, for which it is essential to observe and replicate the sign bit; a set for example is fundamental for creating masks or activating status flags.

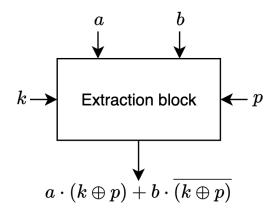

#### 4.1.1 Extraction single bit

The extraction of a bit is normally achieved by a selection of the specific bit and so, taking the example of the sign extension, by simple indexing to the left most position.

In the case of a permuted operand, remembering that we are dealing with data whose weights are out of phase with the native representation, this is no longer possible. In general, for any given position, it is required to find a dedicated structure that brings us back to the bit of the desired weight by comparing the requested position with the corresponding bit of the key. A shape to fulfil this behavior corresponds to the elementary block shown in Figure 4.1.

**Figure 4.1:** Extraction block Source: image taken from the [6] article

The cell receives as input two data bits (a and b), a key bit (k) and a position bit (p). If k and p are different it propagates the input a, if k and p are equal it propagates the input b.

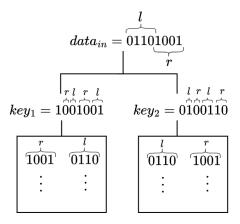

Obviously the block solves for only one decision bit; it is necessary to develop a generic network on n bits resulting from the connection of several levels as shown in Figure 4.2 for an 8-bit case and a key with the notation  $k = k_0^4 k_1^2 k_0^2 k_3^1 k_2^1 k_1^1 k_0^1$ . As can be seen, the architecture has a similar shape to the one of the depermutation

in Figure 3.4, i.e. a descending dichotomous tree. This occurs when it is attempted to apply the key during the reconstruction phase, assigning it from the least significant index to the most significant one.

Also in this case the depth of the tree it is equal to  $\log_2(n = 8)=3$  corresponding to the width of the position signal $(p_2p_1p_0)$ . Each level it is thus linked to each bit of this signal and it allows to make a comparison with the corresponding key section.

Figure 4.2: Extraction dichotomous tree example for 8-bit permuted operand Source: image taken from the [6] article

#### 4.1.2 Set single bit

A bit set is normally achieved by indexing the required specific bit and by the application of a logical function rather than a direct assignment. It means that the access is usually realised by indexing the desired weight followed by a specific operation.

In the case of a permuted operand, as with extraction, remembering that we are dealing with data whose weights are out of phase with the native representation, this is no longer possible. In general, for any given position, it is required to find a dedicated structure that brings us back to the bit of the desired weight, by comparing the requested position with the corresponding bit of the key.

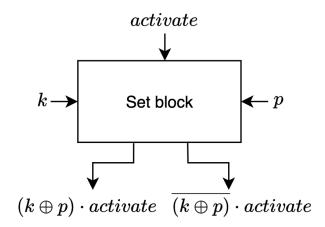

A shape to satisfy this behavior corresponds to the elementary block shown in Figure 4.3.

Figure 4.3: Set block Source: image taken from the [6] article

The cell receives as input an activation bit (*activate*), a key bit (k) and a position bit (p). If k and p are different it propagates the input *activate* to the left, if k and p are the same it propagates the input *activate* to the right.

We thus observe that the *activate* input controls the activation of the entire network because if it were equal to 0 the network would never encounter a stimulus that results in an all-zero output.

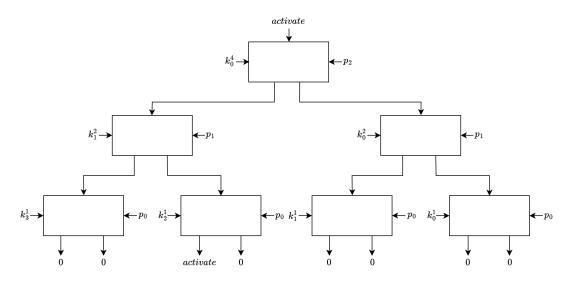

Obviously, the block solves for only one decision bit; it is necessary to develop a generic network on n bits resulting from the linking of several levels as shown in Figure 4.4 for an 8-bit case and a key with the notation  $k = k_0^4 k_1^2 k_0^2 k_3^1 k_2^1 k_1^1 k_0^1$ .

Figure 4.4: Set dichotomous tree example for 8-bit permuted operand Source: image taken from the [6] article

As can be seen, the architecture has a similar shape to that of the permutation in Figure 3.3, i.e. an ascending dichotomous tree in a complementary way in respect the previous one of extraction.

This happens because, if the extraction involves starting from a data vector and arriving at a 1-bit output, the set performs the reverse operation by propagating a 1-bit input to the desired position accordingly to the permutation. There is in a such way an assignment of the key from the most significant index to the least significant one.

The output of this architecture it is a signal with the same parallelism as the data, where the idea is to render it as a mask. Indeed the bit with the logical value 1 it is aligned to the corresponding weight, allowing to apply some function in the new permuted domain.

Also in this case the depth of the tree it is equal to  $\log_2(n=8)=3$  corresponding to the width of the position signal $(p_2p_1p_0)$ . Each level is thus linked to each bit of this signal and allows to make a comparison with the corresponding key section.

#### 4.2 Boolean operations

The first class of operations to observe are the logical functions: ANDL, ANDN, ORL, ORN, XORL, XNOR.

In this case, since these are bit-wise operations, the concept of permutation becomes essential, inducing the need to introduce a simple permutation stage. In fact, the two operands involved, apart from the permutation, possess a weight alignment that allows the direct application of the logic function.

Figure 4.5 shows the example of the logical AND function, where can be seen how a dedicated network is not necessary.

$$a_{7} a_{6} a_{5} a_{4} a_{3} a_{2} a_{1} a_{0} b_{7} b_{6} b_{5} b_{4} b_{3} b_{2} b_{1} b_{0}$$

$$key = 1011100 key = 1011100$$

$$a_{2} a_{3} a_{0} a_{1} a_{5} a_{4} a_{7} a_{6} b_{2} b_{3} b_{0} b_{1} b_{5} b_{4} b_{7} b_{6}$$

$$a_{2} a_{3} a_{0} a_{1} a_{5} a_{4} a_{7} a_{6} b_{2} b_{3} b_{0} b_{1} b_{5} b_{4} b_{7} b_{6}$$

$$a_{2} a_{3} a_{0} a_{1} a_{5} a_{4} a_{7} a_{6} operand_{a}$$

$$AND b_{2} b_{3} b_{0} b_{1} b_{5} b_{4} b_{7} b_{6} operand_{b}$$

$$c_{2} c_{3} c_{0} c_{1} c_{5} c_{4} c_{7} c_{6} result$$

Figure 4.5: Permuted AND logic function example for 8-bit operand

### 4.3 Addition operations

The second elementary computation is the addition. Through an adder in fact we are able to manage various arithmetic operations: ADD, ADDW, ADDUW, SH1ADD, SH2ADD, SH1ADDUW, SH2ADDUW, SH3ADDUW.

As for elementary and Boolean operations discussed in the previous sections, it is needed to evaluate whether to develop a basic architecture capable of support the new domain of the countermeasure. One initial idea could be the use of the classical adders: the Ripple-Carry Adder(RCA).

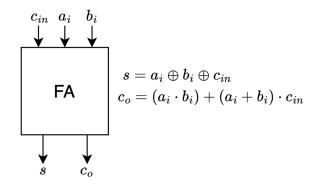

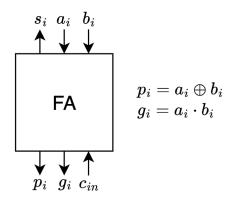

The architecture begins by analysing the binary addition generally described as a 2-input block that outputs the *sum* bit and the *carry* bit. However, generalizing over a multiple number of bits leads to connect the carry of the previous block as the input of the next one, resulting in a new 3-input cell called the *«Full-Adder»*(FA). About this latter, given two data inputs  $a_i$  and  $b_i$  and a third input  $c_{in}$  of carry, can be derived the respective 3-input truth table and the output logical functions as shown in Figure 4.6.

**Figure 4.6:** Full-Adder block with sum(s) and  $carry-out(c_o)$  generation

The architecture of an RCA consists of a chain of FAs and represents the simplest type that can be realized. However, the carry signal propagation between each block highlights the weakest point of this structure: the linear connection of the architecture, that first of all creates a significant critical path for high parallelism, complicates adaptation to the permuted domain.

The necessary propagation shown in Figure 4.7, due to the rearrangement introduced by the permutation function, is difficult to adapt from the first input carry as it is not known which block to attach it to.

Requiring too complex networks we are forced to shift our attention to different architectures. Trying to find a better solution among those in the mathematical literature, in the Carry-Lookahead Adder(CLA) configuration several affinities with the permutation are met.

Figure 4.7: Propagation problem for Ripple-Carry Adder connection typology

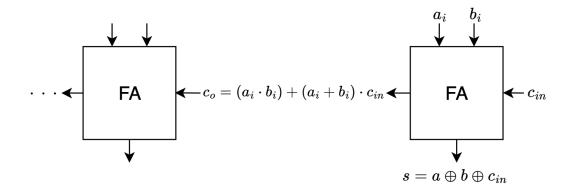

The starting point for this design is the generation of the signals propagate(p) and generate(g) through which the carry-out can be re-expressed as their function. These are internal signals from inputs generated that given two bits of the same operand weight, such as  $a_i$  and  $b_i$ , correspond to their XOR and AND respectively. Accordingly their definitions are generated through an initial layer of FAs, that have been redefined without a carry-out, as shown in Figure 4.8.

**Figure 4.8:** Full-Adder block with generate(g) and propagate(p) generation

To derive the architecture the crucial step lies in observing that the carry-out(index i) of the adder can be re-expressed as a function of the last *propagate* and *generate* at the index i-1:

$$g_i = a_i \cdot b_i$$

$$\implies \qquad c_i = a_{i-1} \cdot b_{i-1} + a_{i-1} \cdot c_{i-1} + b_{i-1} \cdot c_{i-1} = g_{i-1} + p_{i-1} \cdot c_{i-1}$$

$$p_i = a_i \oplus b_i$$

Continuing, now the carry recurrence at the index i-1 can be unrolled founding directly a function of the input carry and of p and g terms derived from input operands as developed in Figure 4.9.

For simplicity of the propagation concept, we will now refer, in the derived tree structure, to left and right signals as shown in the following circuit solutions.

$c_{i} = g_{i-1} + c_{i-1} p_{i-1}$ =  $g_{i-1} + (g_{i-2} + c_{i-2} p_{i-2}) p_{i-1}$ =  $g_{i-1} + g_{i-2} p_{i-1} + c_{i-2} p_{i-2} p_{i-1}$ =  $g_{i-1} + g_{i-2} p_{i-1} + g_{i-3} p_{i-2} p_{i-1} + c_{i-3} p_{i-3} p_{i-2} p_{i-1}$ =  $g_{i-1} + g_{i-2} p_{i-1} + g_{i-3} p_{i-2} p_{i-1} + g_{i-4} p_{i-3} p_{i-2} p_{i-1} + c_{i-4} p_{i-4} p_{i-3} p_{i-2} p_{i-1}$ =  $\dots$

> **Figure 4.9:** Unrolling carry recurrence Source: image taken from the [17] article

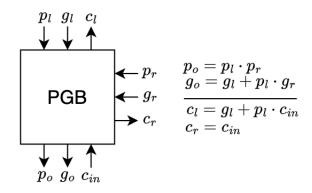

The latter steps are the most important because if the substitution appears to be very complex, the different g and p signals could be combined with what is called *«propagate/generate block»*(PGB), reported in Figure 4.10.

It is a combination structure that receives a carry for a specific position, along with two pairs generated and propagated from the left and right. It manages their propagation through output signals, which are a combination of them to be used as interconnections for further PGBs, along with two output carries.

The output *propagate term* is set to 1 if both those of the input pair are worth 1; the *generate term* is set to 1 if the g from the left is worth 1 or if the p from the left and the g from the right are both worth 1.

Figure 4.10: Propagate/generate block

Permuted ALU

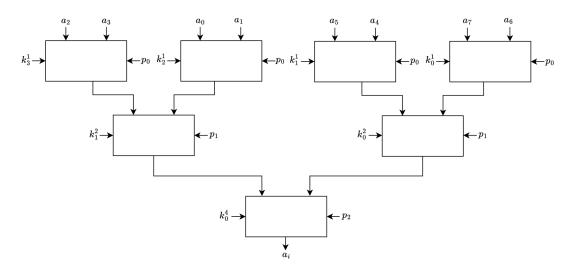

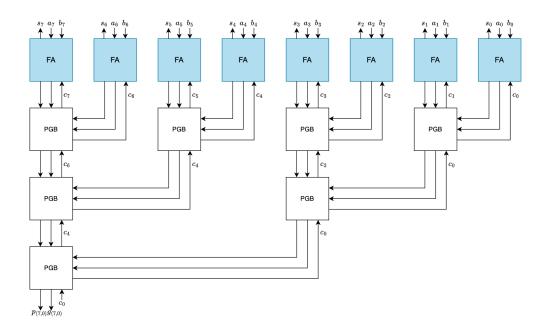

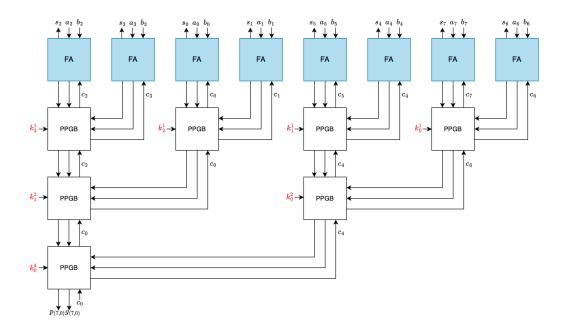

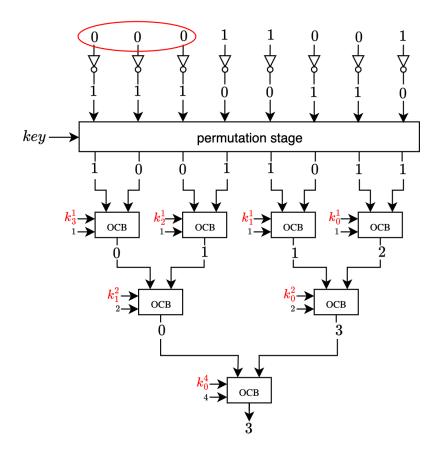

With these observations, these last two blocks of Figures 4.8 and 4.10 give the possibility of depicting the final structure of the CLA, as the Figure 4.11 with an 8-bit case, where the several affinities mentioned come to the eye when observing a permutation-like configuration.

It is in fact the same dichotomous tree, with a depth equal to  $\log_2(n = 8) = 3$ , starting from the bottom where the carry  $c_0$  corresponds to  $c_{in}$ .

Figure 4.11: Dichotomous tree example for 8-bit CLA Source: image derived from the [6] article

The adder works through the operands that enter at the top to calculate g and p signals, they flow to the bottom to calculate the intermediate carries from the input one and then data flow back up to calculate the sum.

This kind of propagation optimizes the design for the permutation by demonstrating that a carry does not need to be used simultaneously with its generation. In the final step of back-propagation using FAs, all carries arrive in the same moment, allowing the sum to be computed.

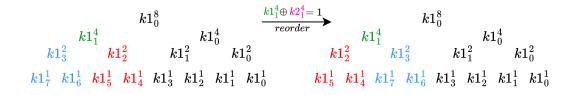

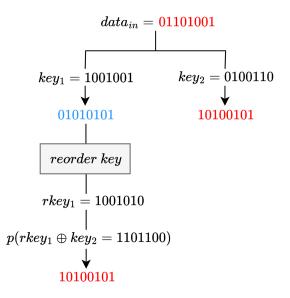

Starting from the input carry, the adaptation object becomes the propagation to the right weight of the internal carries by inserting the key as a decisional signal in the transmission directions.

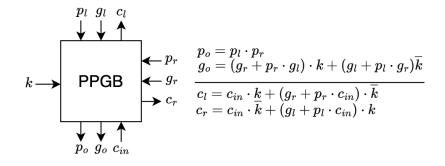

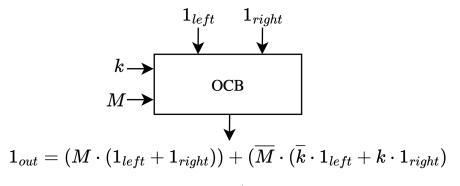

In this way from the PBG can be derived the *«permuted propagate/generate block»*(PPGB), as shown in Figure 4.12, where the outputs correspond to a mix between the left and right ones depending on the key that equal to 0 would return to the native domain.

Figure 4.12: Permuted propagate/generate block

This last block is the only point required to find the final permuted architecture, analogous to the previous Figure 4.11, where each PPGB, with an input key bit, allows to correctly handle an operand with a random weight arrangement. The final configuration of the adder is thus represented in Figure 4.13, once again for the 8-bit case and a key notation  $\mathbf{k} = k_0^4 k_1^2 k_0^2 k_3^1 k_2^1 k_1^1 k_0^1$ , with a visible correspondence of the weights of the input bits with that of each internal carry resulting from the back-propagation.

Figure 4.13: Dichotomous tree example for 8-bit permuted CLA Source: image derived from the [6] article

## 4.3.1 Subtracter

Algebraic operations do not end with addition but also include subtraction operations such as SUB and SUBW.

While in a digital circuit addition is relatively simple to implement, due to the first configuration of the RCA, subtraction is more complicated, mainly due to the calculation of credits between the various bits.

This is why it is generally exploited the property whereby subtracting a number is equivalent to adding its complement with the entry of the 2's complement(CA2), a binary numerical representation for negative numbers. It is obtained by inverting all the bits of the operand and then adding 1, but the crucial aspect lies in the observation that if a number is added to its CA2, the result it is 0.

This is a fundamental property because it means that subtracting a number b from a number a is equivalent to add the CA2 of b to a providing a method to transform a subtracter into an adder through the same logical units, which can potentially be shared as a single component.

The steps to follow become two:

- reverse the bits of b

- add 1 to the negated result

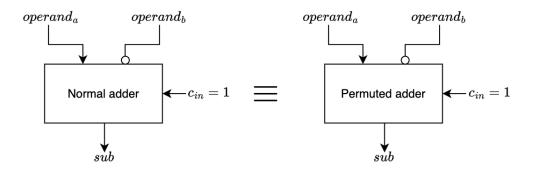

Thus, using any summing machine as a basis, it is possible to integrate these two steps through a logical NOT( $\circ$  its notation), before the connection of the operand b, and an input carry of 1.

The final extension required is the adaptation for permuted operands, as shown in Figure 4.14, where no further modifications are needed. In fact, the same changes applied in the native domain can be computed with the permuted adder, given that the logical operations do not require dedicated structures, and the +1 can be seamlessly integrated as input carry.

Figure 4.14: Subtracter adaptation for native and permuted domain Source: image derived from the [6] article

## 4.3.2 Comparator

The architecture of an ALU often has instructions for comparing operands in order to implement set and branch instructions. This means, for example, taking decisions after checking whether the first operand a is greater than, less than or equal to the second operand b.

A unit of this type in our case would allow to cover several operations: MAX, MAXU, MIN, MINU, LTS, LTU, SLTS, SLTU, GES, GEU, EQ, EN.

In this way the goal becomes to build the unit where, fortunately, the previously defined logic can be reused. In particular, it is only needed the subtracter configuration with three additional output signals on which to take a decision:

- zero bit

- less unsigned bit

- less signed bit

Sometimes in the case of the CVA6 the result may not be the primary interest. For operations such as EQ, LTS... it is directly the single bit of *zero* or *less* that concerns us, which is why the CVA6 ALU has a dual output: the «result» of 64-bit and the «branch» of 1-bit.

An equality comparator, and therefore the unit for controlling the *zero* bit signal, can be easily computed using a XNOR function between the two operands that, as a logical function, does not have problems of adaptation. In this way, computing another AND with all the bits of the result the *zero* bit it is set to 0, indicating different inputs, otherwise, the *zero* bit it is set to 1, meaning the operands are equal and the condition is satisfied.

A relational comparator, and therefore the unit for controlling the *less* bit signal, must necessary be a subtracter. From here, having already dealt with its adaptation in the permuted domain, can be taken the previous configuration of the adder and insert some considerations from the obtained result.

Starting with the unsigned case, four examples are shown in Figure 4.15, allowing us to observe certain properties, particularly highlighting the values of the zero and carry bits.

Figure 4.15: Comparison examples for  $>, <, \ge, =$

The first example in the case of A = 5 and B = 2 shows how the difference of the two operands A-B = 3 returns carry bits equal to 1 and zero bits equal to 0. The second example in the case of A = 1 and B = 3 shows how the difference of the two operands A-B = -2 returns carry bit equal to 0 and zero bit equal to 0. The third example similarly with A-B = 0 returns carry equal to 0 and zero bit equal to 0 and zero bit equal to 1 and the fourth example with A-B = 1 returns 0 and 1 respectively. Each of these examples illustrates that a decision can be made directly as a function of the carry and zero bits, accordingly with the request, and this is the main result because trying to generalise with any comparison request we are able to construct a unique logical decision function, to fix the *less* signal, deriving the Table 4.2.

| Case                      | Logical function           |  |  |  |  |

|---------------------------|----------------------------|--|--|--|--|

| A > B                     | carry $\cdot \overline{z}$ |  |  |  |  |

| $A \ge B$                 | carry                      |  |  |  |  |

| A < B                     | $\overline{carry}$         |  |  |  |  |

| $A \leq B$                | $\overline{carry} + z$     |  |  |  |  |

| $\mathbf{A} = \mathbf{B}$ | Z                          |  |  |  |  |

| $A \neq B$                | $\overline{z}$             |  |  |  |  |

**Table 4.2:** Comparison cases as function of zero bit(z) and carry-out bit(carry)

It was not the only case because in order to complete the unit of comparison there is the need to deal with the signed numbers that at the moment are uncovered. However luckily, in this case another additional dedicated structure is not necessary and a few expedients are sufficient. Precisely there are two possible scenarios:

- when the signs of the operands are the same, the previous Table 4.2 is still valid and the same subtracter configuration can be used.

- when the signs of the operands are different it is even easier to determine the comparison. In fact the subtracter is not longer necessary because can be compared directly the signs of the inputs. For example, if the operands have different signs, it could be possible to conclude that they are different or that the operand with sign equal to 0, i.e. a positive integer, is the greater.

To conclude for this last signed case, several shortcuts can be implemented using simple 2-bit logic gates, thereby conserving resources.

But as a final point, it is important to note that when interacting with permuted operands, if no further adjustments are needed for the unsigned case, as the permuted subtracter configuration is already complete, a final adaptation is required for the signed case: due to the random order of the bits, it is not possible to directly access the MSB and we are obliged to insert the dedicated network of extraction from Section 4.1.1.

## 4.4 Shift operations

The third fundamental computation is the shift. Through a shifter in fact we are able to manage various logic operations: SLL, SRL, SRA, SLLW, SRLW, SRAW, SH1ADD, SH2ADD, SH3ADD, SH1ADDUW, SH2ADDUW, SH3ADDUW, ROL, ROR, RORI, ROLW, RORW, RORIW, REV8, SLLIUW.

The manipulation refers to a bit-wise logical function that involves moving the bits of a number either to the right or to the left by a specific amount. The vacant positions created during this operation are filled with zeros, ones, or bits from the same operand, depending on the operation required.

Now to fulfil all these possible instructions and arrive at a permuted Barrel Shifter architecture, i.e. a shifter conformed to any amount and mode, it is necessary to go through four steps:

- 1. Shift left by 1

- **2.** Shift left by 2

- **3.** Shift left by a power of 2

- 4. Barrel Shifter

Of the various operations, we rely on the logical shift to the left as the most classic model and from which the others can be derived by means of some adaptation.

## 4.4.1 Shift left by 1

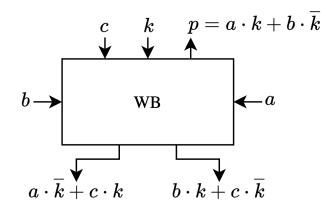

The shift left by 1 is the simplest case of all, being of one position only, that finds its starting point in a block called «*White block*»(WB) shown in Figure 4.16. The component has 3 data inputs a,b,c and a control input k, correspondent with the permutation key, that has the ability to recreate a rotation in its function.

Figure 4.16: White block

The final structure, that can be derived, is a multi-level tree that provides the mean of rotation in a propagation of the input signals towards an upper level or a lower level. First of all a decision is made between the inputs a and b, on which to propagate upwards, via the signal propagate(p) and the permutation key(k): if k = 0 the input a is brought out on the left side, together with c on the right side and b in the propagate position; if k = 1 the input b is brought out on the right side, together with c on the left side, together with c on the right side.

The previously mentioned rotation concept became visible trying to construct the tree architecture where can be observed the third input c coming from an upper level, as shown in Figure 4.17 for a 4-bit case and the permuted data  $a_0a_1a_3a_2$ .

Figure 4.17: Permuted shift left by 1 example with White Block(WB) Source: image derived from the [6] article

The final architecture is dichotomous as for permutation, with a key connection to each WB until the LSB, and a number of levels equal to  $\log_2\left(\frac{n}{block}\right)$  where *n* represents the width and *block* the shift amount.

It is worth noting in the example the ejection of the bit corresponding to position  $a_3$ , in correspondence of the last *propagate* signal in the top position, and how in the same top block, since there are no other upper levels, the third input c is equal to 0, i.e. the point at which the vacant positions are fulfilled.

To conclude if it is observed in detail at the output level of the tree, can be observed such a structure is capable of placing the new zero-weighted bit in its permuted position, generating a signal equal to  $a_2a_1a_00$  and thus the value we would expect with input  $a_3a_2a_1a_0$ .

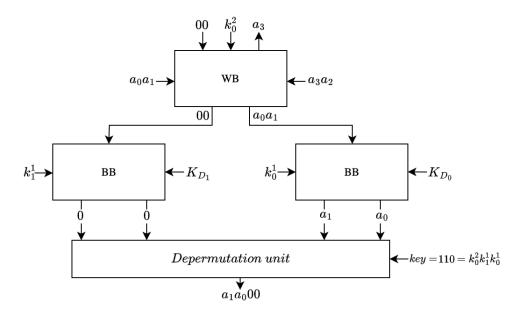

## 4.4.2 Shift left by 2

The shift left by 2 is the second easiest case to handle, being of two positions only. This step is fundamental because trying to apply the same WB structure, it reveals that this block is no longer sufficient. In fact, the 4-bit example in Figure 4.18 shows how, with a structure that would now be only one level remembering the formula  $\log_2(\frac{n}{block})$ , it would arrive at an output equal to  $a_0a_100$  when for an input of  $a_3a_2a_1a_0$  it would be expected to get  $a_1a_000$ .

Figure 4.18: Permuted shift left by 2 example with White Block(WB) Source: image derived from the [6]

Here the main problem arises from the fact that the structure has a depth of one such that the permutation key is partially associated. In this way is possible to conclude that for shifts with powers greater than one the WB is not able by itself to take into account the LSB of the key.

The example with the output  $a_0a_100$  clearly demonstrates this error, where the most significant pair appears in reverse order from what is expected that could be resolved applying the respective LSB of the key with value 1.

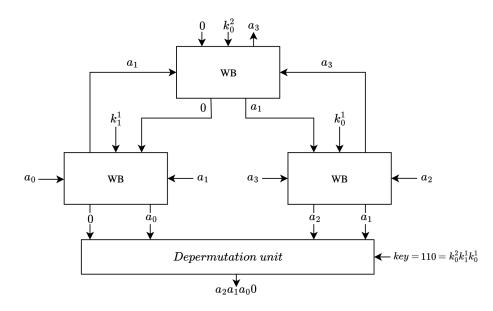

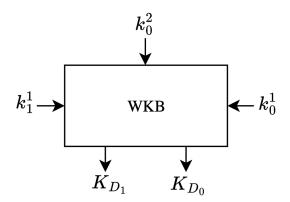

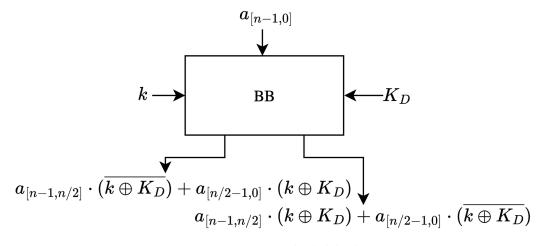

The problem in other words can be described by observing that by shifting to higher powers we create a division of the data into sections larger than 1-bit and, in the event of a shift of these sections, they would respect a different segment of the key from the original one before the operation. So, if our goal is to achieve generality for any given shift amount, we are forced to introduce something new. The two involved blocks are the «White Key Block»(WKB) and the «Black Block»(BB), as shown in Figures 4.19 and 4.20, respectively.

**Figure 4.19:** White key block Source: image derived from the [6] article

The first is a block useful for generating a new key denoted  $K_D$ . The example with n = 4 and block = 2 provides a 3-input cell, matching with the bits of the key, where the one of the top, corresponding with the MSB, takes the decision if invert or not the least significant positions.

The vector  $K_D$  in fact does not possess a dimension identical to the native key but a reduced size with only the bits that could not be applied due to the insufficient depth of the tree. Precisely if the MSB is 1 the outputs are the two LSBs but in reverse order, if the MSB is 0 the order remains the same.

Figure 4.20: Black block Source: image derived from the [6] article

The second block is capable of resolving inconsistencies by using the native key and the vector  $K_D$ , deciding whether to swap the halves of its input: if the signals k and  $K_D$  are equal the outputs are left and right sides in the same order, otherwise they are reversed.

Such as the shift by 1, in this way the mismatch between larger sections of a bit and respective segments of the permutation key is resolved and a new dichotomous tree structure can be derived. As shown in the 4-bit example in Figure 4.21 it is correctly obtained  $a_1a_000$  from the permuted data  $a_0a_1a_3a_2$ .

**Figure 4.21:** Permuted shift left by 2 example with White Block(WB), Black Block(BB) and White Key Block(WKB)

Source: image derived from the [6] article

Here the generation of the two components  $K_{D_0}$  and  $K_{D_1}$  is implicit: we would have to include the WKB to have a complete diagram.

## 4.4.3 Shift left by a power of 2

The shift left by a power of 2 is the third case which is already more complex than the previous ones.

In this case this step is fundamental because trying to apply the same structure previously mentioned there is a limitation: the vector  $K_D$  was generated with a simple block having to manage only a 3-bit key as the number of inputs of the block itself, not including generalities.

Therefore this step is crucial to extend the network in a new tree structure called

«White key tree». Here the purpose remains the same: it is requested to recognize any mismatches between the data sections and the key segments providing a new key  $K_D$  that bridges the inconsistencies.

The solution for a more generic shift amount is obtained by observing the previously developed approach for the data. Indeed the architecture is entirely analogous as it is sufficient to note that we are concerned with rotating the key's segments in the same direction as the data. The difference lies ensuring that no additional input bits are required and considering the possibility of inverting the LSBs at a later stage.

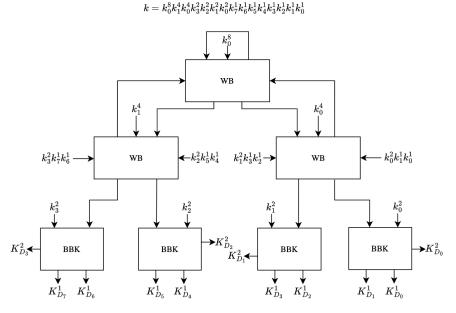

On this last aspect, the structure can be derived introducing a new block called «Black block key»(BBK) as shown in Figure 4.22.

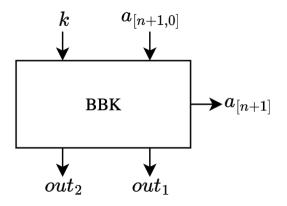

**Figure 4.22:** Black block key Source: image derived from the [6] article

The cell receives an input bit of the key along with an its segments where the MSB of this latter is immediately taken to the output as part of the new vector  $K_D$  but is also used in a XOR function with k to decide whether to invert the LSBs.

In this context, it should be noted that the inversion does not mean to change the order of some bits but follows the permutation, swapping precisely two branches of the dichotomous tree.

The final architecture is thus provided through the example in Figure 4.23 for a 16-bit data and a shift amount of four where the three main aspects, already mentioned, can be observed:

- The architecture is analogous to that of the data.

- The top block of the structure has a link between the shifted-out value and the shifted-in value.

• The key could be divided into MSBs for the first levels of rotation and LSBs to manipulate internal swaps.

**Figure 4.23:** Permuted shift left by a power of 2 adaptation for 16-bit  $K_D$  generation with White Block(WB) and Black Block Key(BBK).

Source: image derived from the [6] article

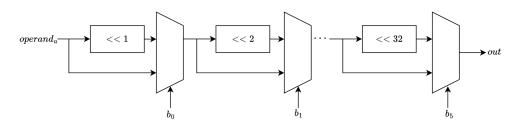

## 4.4.4 Barrel shifter

The final implementation concerns the most complex case for handling any shift amount.

Unlike the previous steps, this is the only case in which directly a reuse of the last proposed architecture is applied: it is sufficient to organize in a multiplexer selection some blocks of shifts by a power of 2 as shown in Figure 4.24.

Figure 4.24: Barrel shifter configuration with multiplexer selection Source: image derived from the [6] article

Knowing that a generic shift amount can be represented as the sum of the contributions from the powers of 2 of its bits, can be established a selection structure between a simple wire and the output of the shifter. Furthermore, working on 64 bits, this shift-amount, consisting of 6 bits of the second operand, corresponds to the mux selectors and tells whether or not to consider the shift of that weight.

As last remark the final implementation proposed until this moment knows how to manipulate permuted operands in the case of a logical shift to the left.

What to do for the other shift types? As initially stated starting with this last Barrel shifter configuration, small variations are sufficient:

- Logical shift to the right: can be obtained simply by observing that the negation of the key reverses the direction of rotation of the bits

- Arithmetical shift to the right: can be achieved by extracting the MSB and connecting it as an input to the upper block of the network

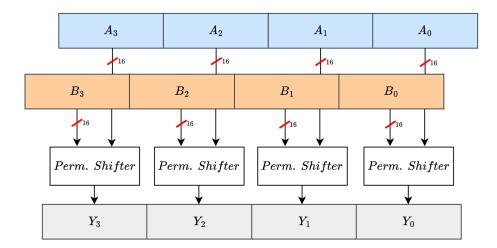

- Rotation to the left or to the right: reverse from the top block of the inputs without new insertion and without takes care about the permutation key