# POLITECNICO DI TORINO

# **Electronic Engineering**

# Master thesis

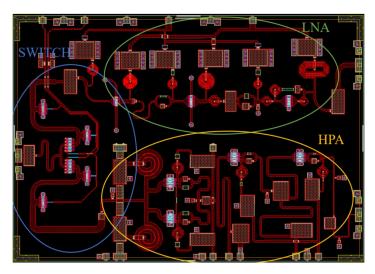

# Characterization and design of high frequency SPDT switch working in a 8-14 GHz band

Gabriele Abate

Graduand: Gabriele Abate Supervisors: Marco Pirola Jesus Grajal de la Fuente

## Acknoledgments

I dedicate this work to those who have significantly contributed to my academic and personal development: to my family, who have been by my side the whole time—my mother Letizia, my father Emanuele, and my sister Grace.

Secondly, I'd like to extend my heartfelt thanks to the friends I made during my academic journey. A special mention goes to my dear friend Taus, to Zoe, and to the friends I met during my year abroad in Spain, especially my dear friend Sofia. Their support and companionship made this experience unforgettable.

Lastly, I dedicate this work and give thanks to my supervisor, Jesús Grajal, for his invaluable help and dedication throughout this project. I also extend my gratitude to Marta Ferreras Mayo and all the members of SSR for giving me the opportunity to complete this project.

## Contents

| 1        | Higl | High frequency electronics switches                                                    |    |  |  |

|----------|------|----------------------------------------------------------------------------------------|----|--|--|

|          | 1.1  | Introduction                                                                           | 7  |  |  |

|          | 1.2  | Operation of high frequency electronics switches                                       | 7  |  |  |

|          | 1.3  | Parameters of interest                                                                 | 8  |  |  |

|          |      | 1.3.1 Linearity parameters                                                             | 8  |  |  |

|          |      | 1.3.2 Non-Linearity parameters                                                         | 9  |  |  |

|          | 1.4  | Technological features                                                                 | 10 |  |  |

|          | 1.5  | Optimization techniques                                                                | 11 |  |  |

|          |      | 1.5.1 Linear analysis                                                                  | 12 |  |  |

|          |      | 1.5.2 Non-Linear analysis                                                              | 14 |  |  |

|          | 1.6  | Consideration on the asymmetry of the switch                                           | 15 |  |  |

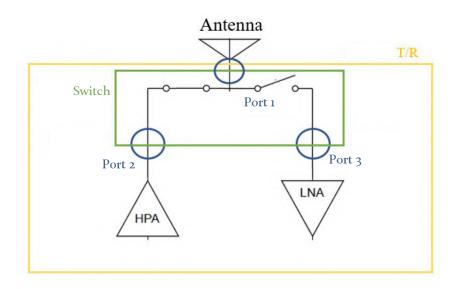

| <b>2</b> | Rad  | io frequency switch design                                                             | 17 |  |  |

|          | 2.1  | Introduction                                                                           | 17 |  |  |

|          | 2.2  | The design instruments                                                                 | 17 |  |  |

|          |      | 2.2.1 Harmonic Balance                                                                 | 17 |  |  |

|          |      | 2.2.2 Large signal S-Parameters                                                        | 18 |  |  |

|          |      | 2.2.3 Electromagnetic co-simulation                                                    | 18 |  |  |

|          |      | 2.2.4 Global and Local Optimization                                                    | 19 |  |  |

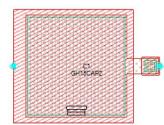

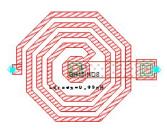

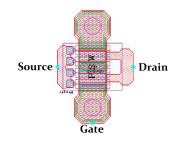

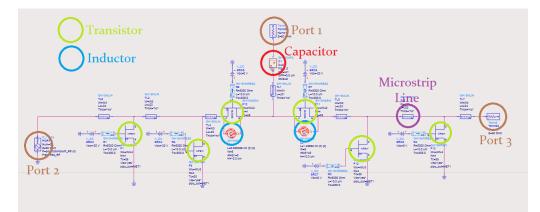

|          |      | 2.2.5 PDK Elements                                                                     | 20 |  |  |

|          | 2.3  | Initial steps                                                                          | 21 |  |  |

|          | 2.4  | Basic circuit design                                                                   | 22 |  |  |

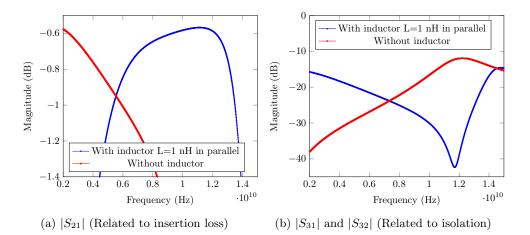

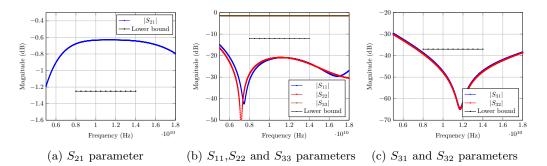

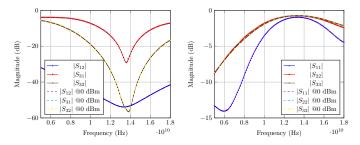

|          |      | 2.4.1 Small signal analysis                                                            | 23 |  |  |

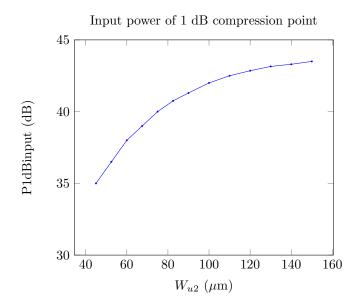

|          |      | 2.4.2 Large signal analysis                                                            | 23 |  |  |

|          | 2.5  | Basic circuit design with geometry                                                     | 24 |  |  |

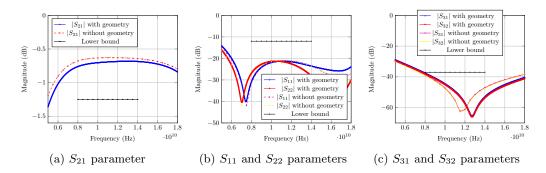

|          |      | 2.5.1 Small signal analysis                                                            | 25 |  |  |

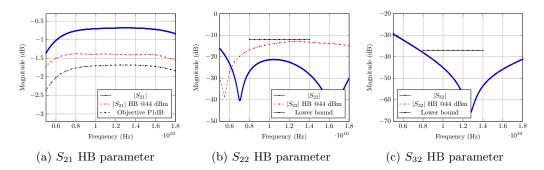

|          |      | 2.5.2 Large signal analysis                                                            | 26 |  |  |

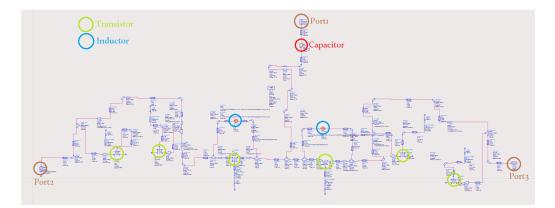

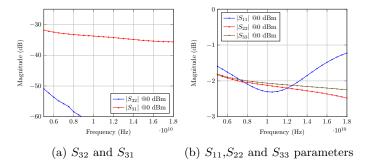

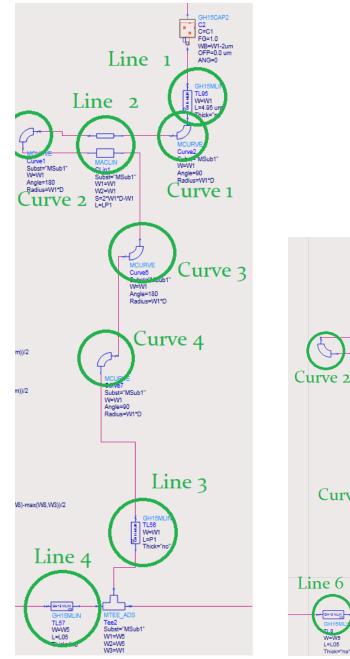

|          | 2.6  | Design with electromagnetic co-simulation.                                             | 27 |  |  |

|          |      | 2.6.1 Small signal analysis                                                            | 27 |  |  |

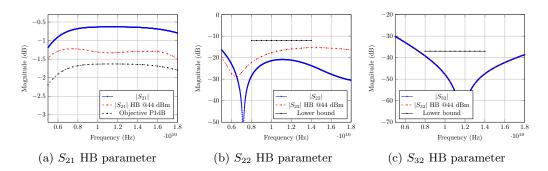

|          |      | 2.6.2 Large signal analysis                                                            | 28 |  |  |

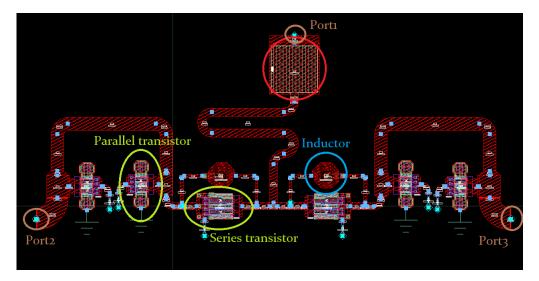

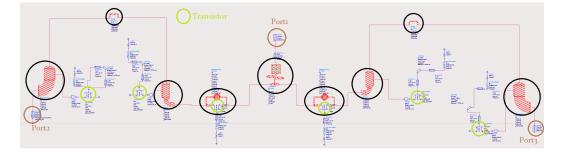

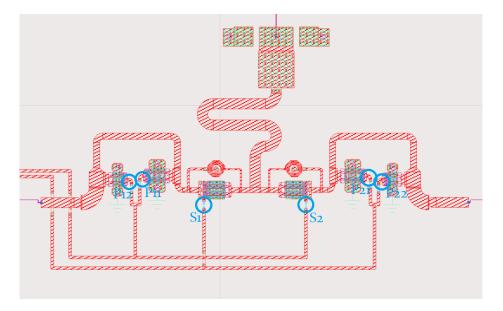

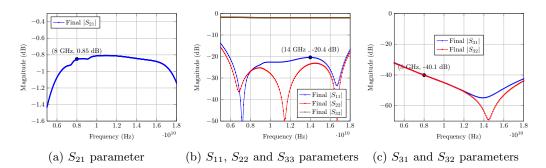

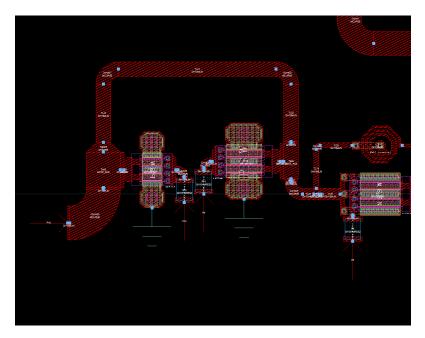

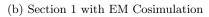

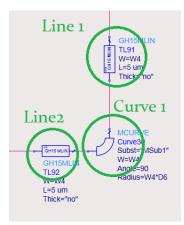

|          | 2.7  | Design with fully electromagnetically co-simulationed layout.                          | 29 |  |  |

|          |      | 2.7.1 Small signal analysis                                                            | 29 |  |  |

|          |      | 2.7.2 Large signal analysis                                                            | 30 |  |  |

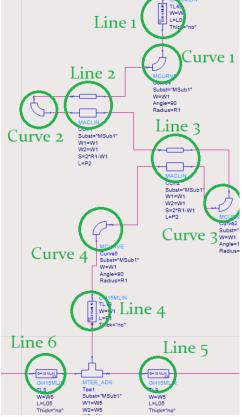

|          | 2.8  | Co-simulated design with full-layout and power supply lines $\ldots$ $\ldots$ $\ldots$ | 31 |  |  |

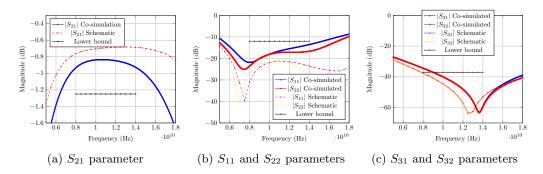

|          |      | 2.8.1 Small signal analysis                                                            | 31 |  |  |

|          |      | 2.8.2 Large signal analysis                                                            | 32 |  |  |

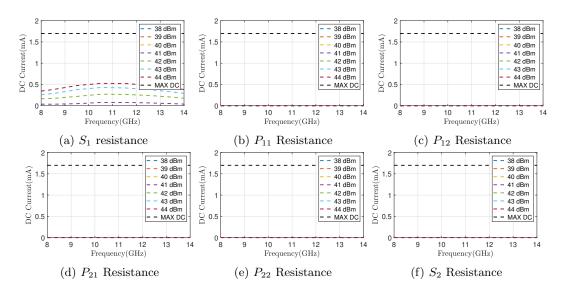

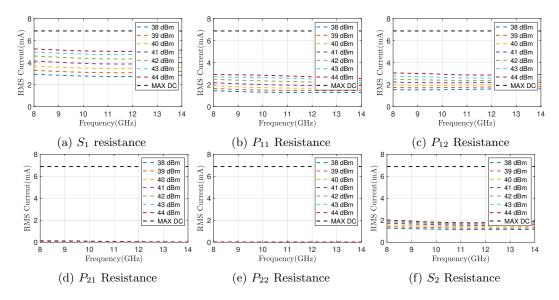

|          | 2.9  | DRC and maximum ratings analysis                                                       | 32 |  |  |

|          | 2.10 | Switch states analysis                                                                 | 35 |  |  |

|          |      | 2.10.1 TX Short, RX Open                                                               | 35 |  |  |

|          |      | 2.10.2 TX Open, RX Short                                                               | 35 |  |  |

|          |      | 2.10.3 TX Open, RX Open                                                                | 35 |  |  |

|          |      | 2.10.4 TX Short, RX Short                                                              | 36 |  |  |

|          | 2.11 | Conclusions                                                                            | 37 |  |  |

| 3 | Radio frequency switch design - Monte Carlo Analysis |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |  |  |

|---|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

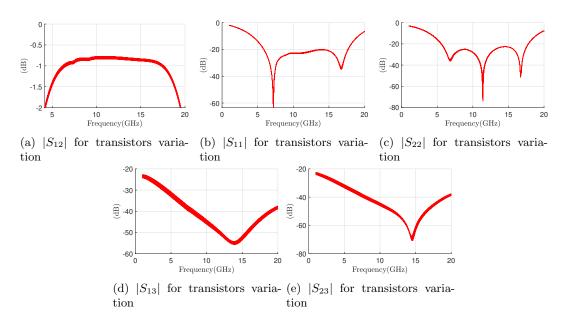

|   | 3.1                                                  | Monte Carlo Analysis - Transistor behaviour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38        |  |  |

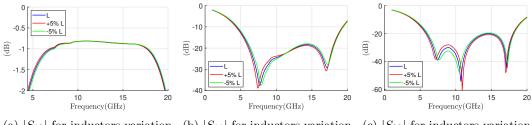

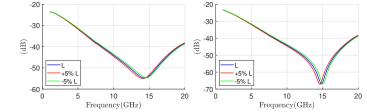

|   | 3.2                                                  | Monte Carlo Analysis - Inductor behaviour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39        |  |  |

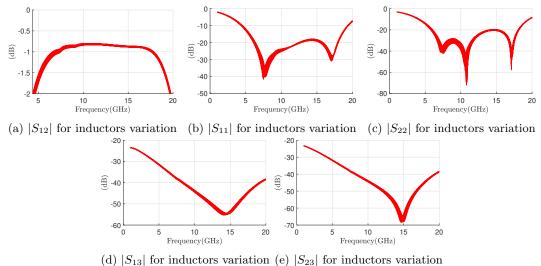

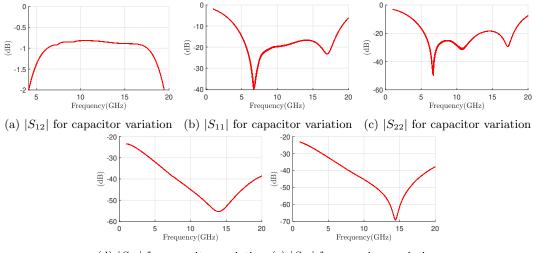

|   | 3.3                                                  | Monte Carlo Analysis - Capacitor behaviour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40        |  |  |

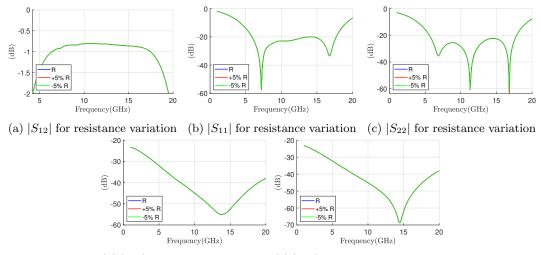

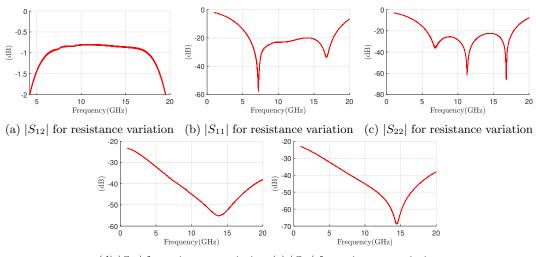

|   | 3.4                                                  | Monte Carlo Analysis - Resistor behaviour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42        |  |  |

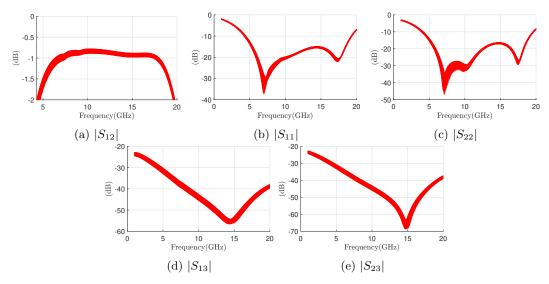

|   | 3.5                                                  | Monte Carlo Analysis - Final analysis and conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43        |  |  |

| 4 | Rad                                                  | lio frequency switch design - Transient analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>45</b> |  |  |

|   | 4.1                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45        |  |  |

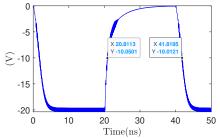

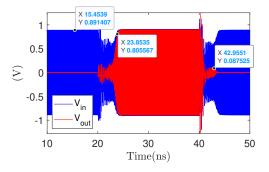

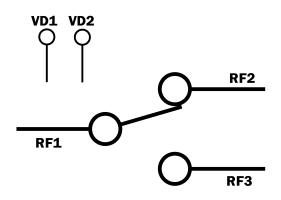

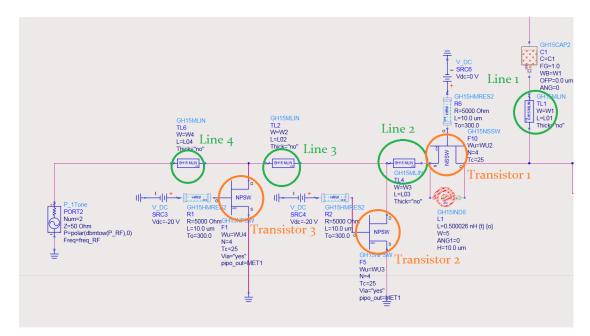

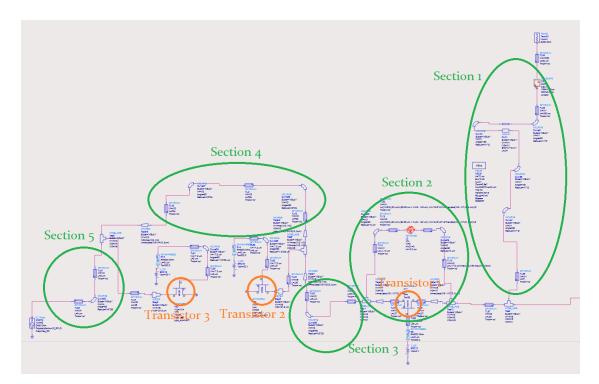

|   | 4.2                                                  | Transient time analysis - Scheme and description $\hdots \ldots \hdots \hdot$ | 46        |  |  |

|   | 4.3                                                  | Transient time analysis - Simulation results $\hdots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47        |  |  |

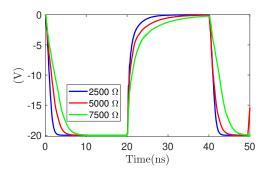

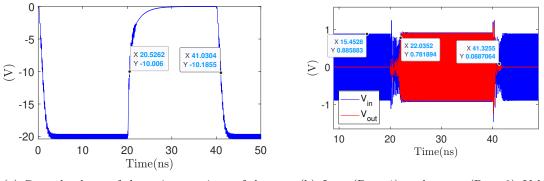

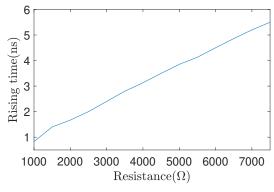

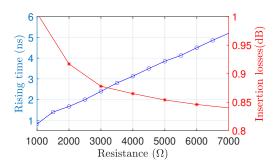

|   | 4.4                                                  | Transient time analysis - Optimization $\hdots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48        |  |  |

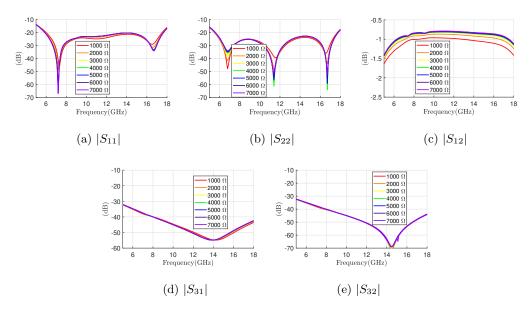

|   | 4.5                                                  | Transient time analysis - Optimization effects on the other parameters $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50        |  |  |

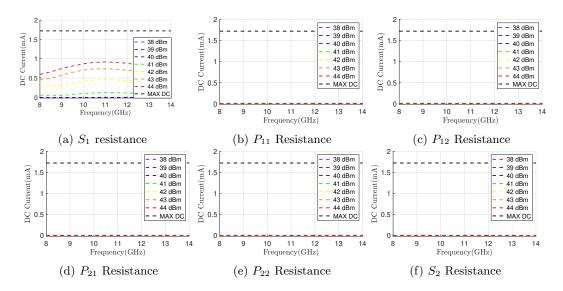

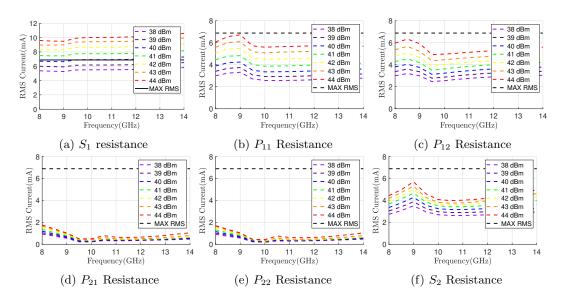

|   | 4.6                                                  | Transient time analysis - The supply lines current issue $\hfill \ldots \ldots \ldots \ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51        |  |  |

|   | 4.7                                                  | Transient time analysis - Possible solutions to the problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52        |  |  |

|   | 4.8                                                  | Transient time analysis - Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53        |  |  |

| 5 | Ref                                                  | Reflexive switch - Measurement 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |  |  |

|   | 5.1                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54        |  |  |

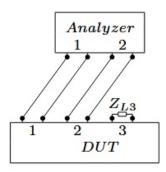

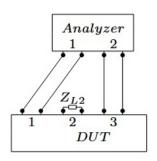

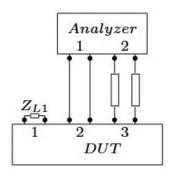

|   | 5.2                                                  | Measurement procedure configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54        |  |  |

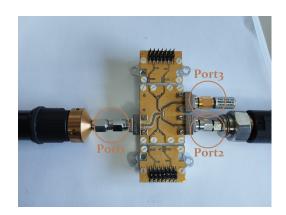

|   | 5.3                                                  | Measurement 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55        |  |  |

|   | 5.4                                                  | Measurement 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56        |  |  |

|   | 5.5                                                  | Measurement 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58        |  |  |

|   | 5.6                                                  | Criticalities of the process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59        |  |  |

|   | 5.7                                                  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60        |  |  |

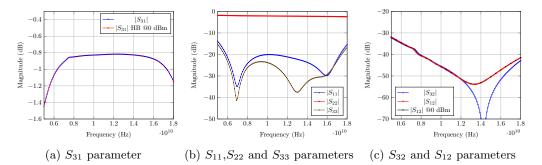

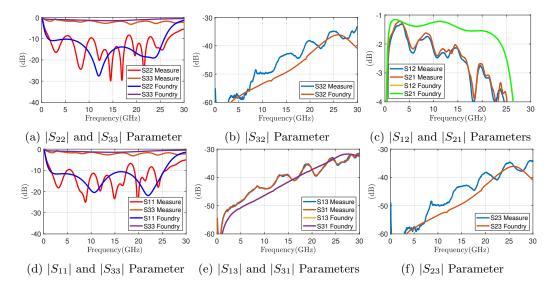

|   | 5.8                                                  | Results - S-Parameters of the $(1 \rightarrow 2)$ ON configuration comparison $\ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60        |  |  |

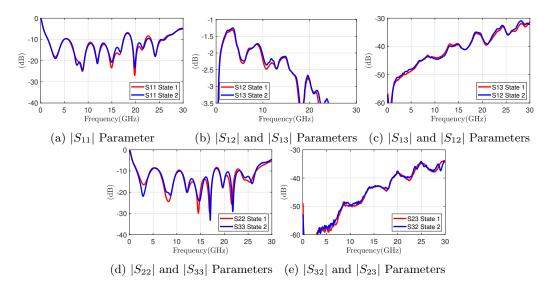

|   | 5.9                                                  | Results - State 1 - State 2 configurations comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61        |  |  |

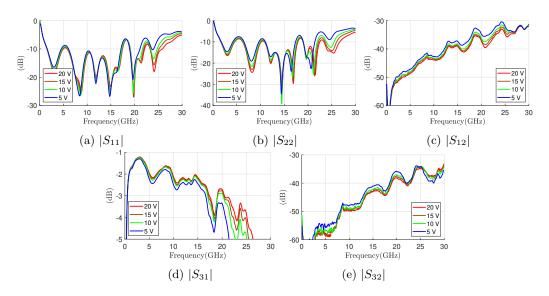

|   | 5.10                                                 | Results - Polarization variations comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61        |  |  |

|   | 5.11                                                 | Temperature analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62        |  |  |

|   | 5.12                                                 | Temperature measurement procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63        |  |  |

|   | 5.13                                                 | Temperature measurement results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64        |  |  |

| 6 | App                                                  | pendix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66        |  |  |

|   | 6.1                                                  | Appendix A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66        |  |  |

|   |                                                      | 6.1.1 Dimensions for the circuit with no geometry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70        |  |  |

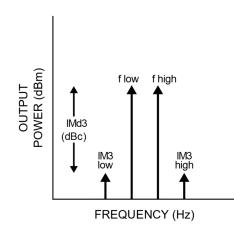

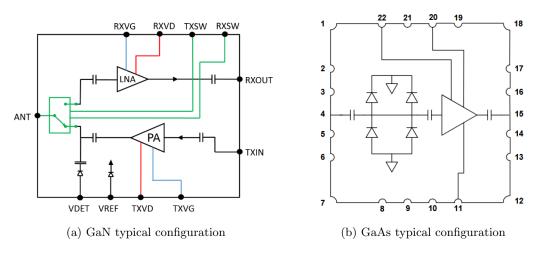

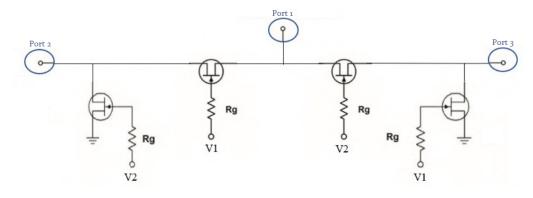

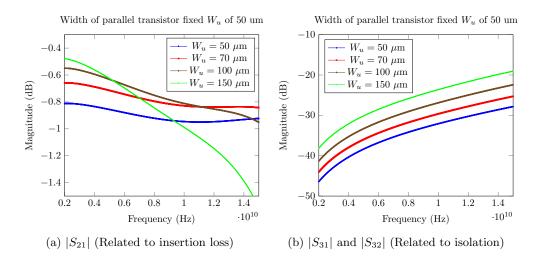

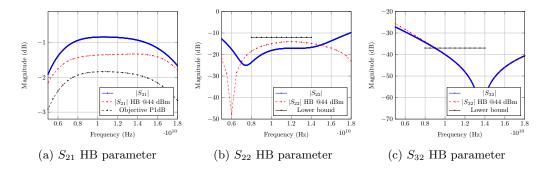

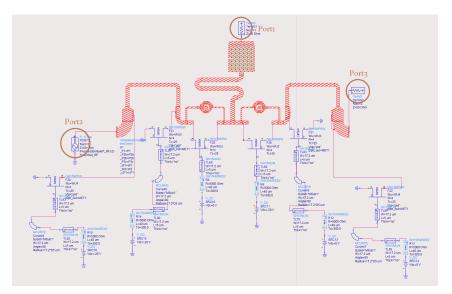

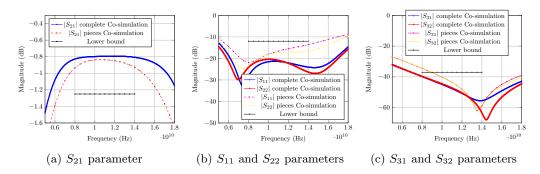

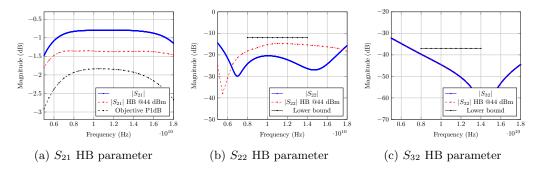

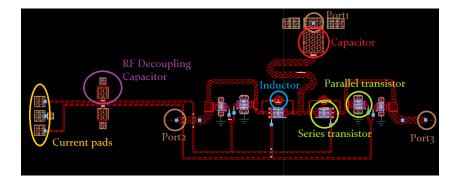

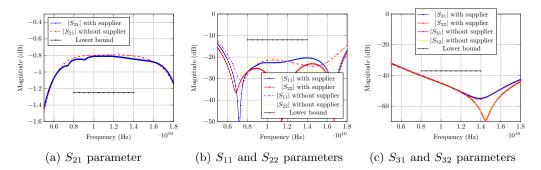

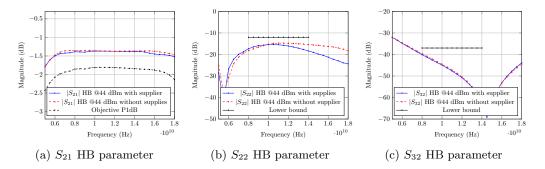

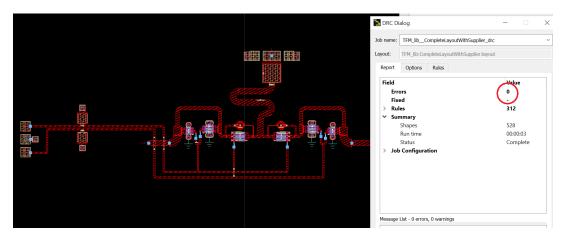

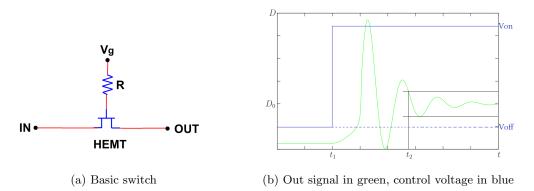

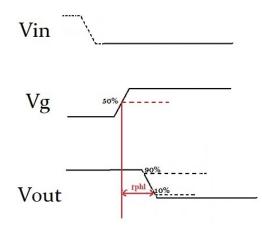

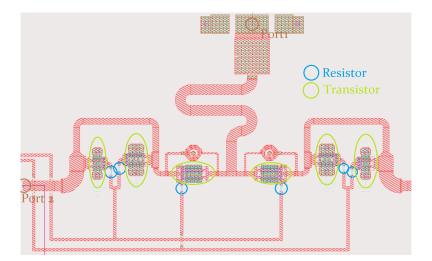

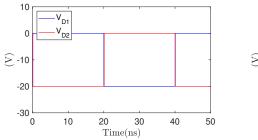

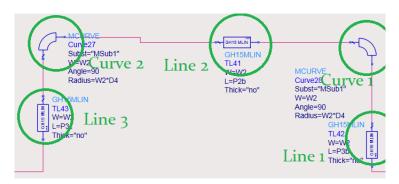

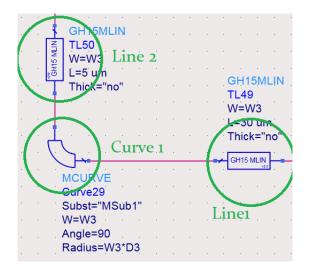

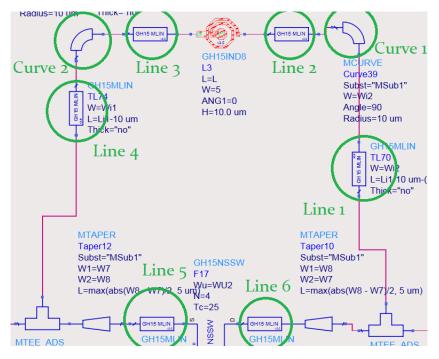

|   |                                                      | 6.1.2 Dimensions for the circuit with geometry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71        |  |  |