Master's Degree Thesis in Electronic Engineering

# UVM environment for I3C Target Device

Supervisors Prof. Maurizio MARTINA Prof. Guido MASERA Ing. Sandro SARTONI Candidate

Federica BONGO

July 2023

#### Abstract

I3C Basic is a scaled-down and less complex version of the powerful, flexible and efficient I3C interface, suitable for a wide range of device connectivity applications, including sensor and memory interfaces. The I3C interface was developed by the MIPI Alliance and is designed to overcome the limitations of the I2C interface, while maintaining backward compatibility.

Similar to I2C, devices on the I3C bus communicate in a controller/target environment, where both the controller and target device can initiate communication.

In this project, the I3C target device used is the I3CS IP, which supports functions based on the MIPI I3C v.1.1.1. Due to the size and complexity of the project, functional verification becomes a challenge throughout the design flow. For this reason, a suitable verification environment must be developed to accelerate the verification phase. Starting from the architecture study of the target, the objective of this work, performed in collaboration with TDK InvenSense, is to develop a verification environment that can be used to test the correct functioning of the main operations of the I3CS IP target.

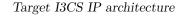

The testbench environment consists of the VIP block, which simulates the controller, the DUT, i.e. the design under test (IP I3CS), the Register File, which serves as the reference model; and a Scoreboard, which compares the actual values sent by the VIP with the values expected by the Register File. An interface must be defined between the VIP and DUT blocks so that the Controller (VIP) can communicate with the I3CS IP Target (DUT) via two buses, Serial Data (SDA) and Serial Clock (SCL). In this way, the controller can generate stimuli for the DUT to verify its correct behaviour.

The verification environment is based on the Universal Verification Methodology (UVM), with the UVM class library adding many automation functions such as sequences and data automation to the System Verilog language. In the UVM environment there are several components that together are responsible for driving the input tests to the Design Under Test (DUT), collecting the output transactions and finally comparing the actual results with the expected ones. To improve the verification of the I3CS IP target, it is necessary to test its functionality outside normal operating conditions by performing appropriate tests, including illegal frames.

# **Table of Contents**

| Li       | st of | Tables                  |                                            | IV   |

|----------|-------|-------------------------|--------------------------------------------|------|

| Li       | st of | Figures                 |                                            | V    |

| Ac       | crony | ms                      |                                            | VIII |

| 1        | Intr  | oduction                |                                            | 1    |

|          | 1.1   | Goal of the thesis and  | structure                                  | 1    |

| <b>2</b> | Ove   | rview of I3C Protoc     | ol and UVM Environment                     | 3    |

|          | 2.1   | Introduction to I3C P   | rotocol                                    | 3    |

|          |       | 2.1.1 I3C Controller    | Device                                     | 4    |

|          |       | 2.1.2 I3C Target Dev    | vice                                       | 6    |

|          | 2.2   | Introduction to Verific | $\operatorname{ration}$                    | 6    |

|          |       | 2.2.1 Verification Pla  | an                                         | 7    |

|          | 2.3   | The Universal Verifica  | tion Methodology                           | 8    |

|          |       | 2.3.1 The UVM Con       | nponents                                   | 12   |

| 3        | Targ  | et I3CS IP architec     | ture                                       | 15   |

|          | 3.1   | Bus Configuration       |                                            | 15   |

|          | 3.2   |                         | rt Conditions                              |      |

|          |       | 3.2.1 I3C Address H     | eader                                      | 17   |

|          |       | 3.2.2 I3C Address A     | rbitration                                 | 18   |

|          | 3.3   | I3C SDR Data Words      |                                            | 19   |

|          |       | 3.3.1 Transition from   | n Address ACK to SDR Controller Write Data | 22   |

|          | 3.4   | Legacy I2C Transactio   | on on I3C Bus                              | 22   |

|          |       | 0 0                     | ad and Private Write                       |      |

|          | 3.5   | Dynamic Address Assi    | ignment Mode                               | 23   |

|          |       | •                       | ess Assignment Procedure                   |      |

|          |       | ÷                       | 8-bit Provision ID                         |      |

|          |       | 0                       | n Command Code)                            |      |

|              | $\begin{array}{c} 3.6\\ 3.7\end{array}$ | Hot-Join MechanismHotHDR ModeHot                                                                                                                           |          |

|--------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4            | UV                                      | M Environment                                                                                                                                              | 29       |

|              | 4.1                                     | Test-Bench scheme                                                                                                                                          | 29       |

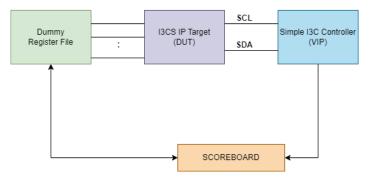

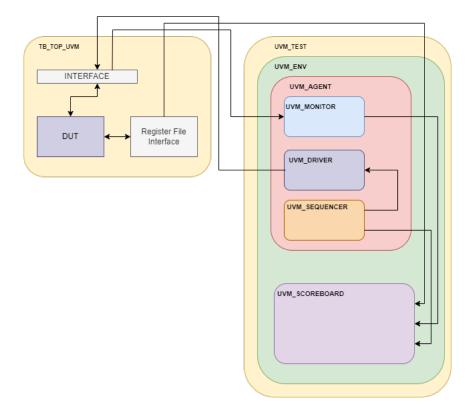

|              | 4.2                                     | UVM Structure                                                                                                                                              |          |

|              |                                         | 4.2.1 Top                                                                                                                                                  | 32       |

|              |                                         | 4.2.2 Sequences                                                                                                                                            | 34       |

|              |                                         | 4.2.3 Sequencer Operations                                                                                                                                 | 39       |

|              |                                         | 4.2.4 Packet sequence                                                                                                                                      | 40       |

|              | 4.3                                     | Environment                                                                                                                                                | 40       |

|              | 1.0                                     | 4.3.1 Agent                                                                                                                                                | 41       |

|              | 4.4                                     | Driver                                                                                                                                                     | 41       |

|              | 1.1                                     | 4.4.1 Tasks of Driver                                                                                                                                      | 42       |

|              | 4.5                                     | Scoreboard                                                                                                                                                 | 44       |

|              | 4.0                                     | 4.5.1 uvm_event                                                                                                                                            | 44       |

|              | 4.6                                     | Register File                                                                                                                                              | 40<br>46 |

|              | 4.0<br>4.7                              | Timing Specification                                                                                                                                       | 40<br>47 |

|              | 4.7                                     |                                                                                                                                                            | 41       |

| <b>5</b>     | Test                                    | t and Results                                                                                                                                              | 50       |

|              | 5.1                                     | Tests                                                                                                                                                      | 50       |

|              |                                         | 5.1.1 UVM Base Test                                                                                                                                        | 51       |

|              |                                         | 5.1.2 I2C Private Write with Static Target Address Test                                                                                                    | 52       |

|              |                                         | 5.1.3 I2C Private Read with Static Target Address                                                                                                          |          |

|              |                                         | 5.1.4 I2C Private Write with Broadcast Address                                                                                                             | 53       |

|              |                                         | 5.1.5 I2C Private Read with Broadcast Address                                                                                                              | 54       |

|              |                                         | 5.1.6 I3C Private Write                                                                                                                                    | 55       |

|              |                                         | 5.1.7 I3C Private Read                                                                                                                                     | 55       |

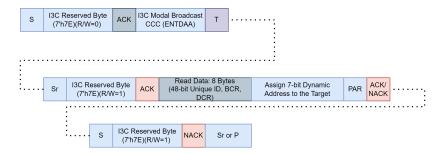

|              |                                         | 5.1.8 Dynamic Address assignment: I3C ENTDAA Procedure                                                                                                     | 56       |

|              | 5.2                                     | Results and analysis                                                                                                                                       | 57       |

|              | 0.2                                     | 5.2.1 Simulation Results                                                                                                                                   | 58       |

|              |                                         |                                                                                                                                                            |          |

| 6            | Cor                                     | nclusion and Future works                                                                                                                                  | 80       |

| $\mathbf{A}$ | Wo                                      | rking Test Codes                                                                                                                                           | 82       |

|              |                                         | tdk_i3c_uni_base_test.sv                                                                                                                                   | 82       |

|              |                                         | tdk_i3c_uni_I2C_write_test.sv                                                                                                                              | 83       |

|              |                                         | $tdk\_i3c\_uni\_I2C\_write\_bd\_test.sv \dots \dots$ | 85       |

| Bi           | bliog                                   | graphy                                                                                                                                                     | 89       |

# List of Tables

| 3.1 | CCCs Table                                                         | 26 |

|-----|--------------------------------------------------------------------|----|

| 4.1 | I3C Timing Requirements When Communicating With I2C Legacy Devices | 40 |

|     |                                                                    | 49 |

# List of Figures

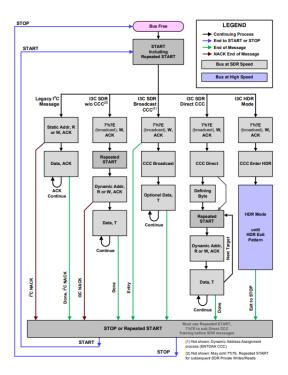

| 2.1  | I3C Communication Flow                                                                        | 4  |

|------|-----------------------------------------------------------------------------------------------|----|

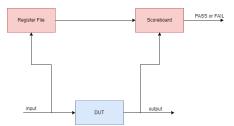

| 2.2  | Scoreboard approach                                                                           | 8  |

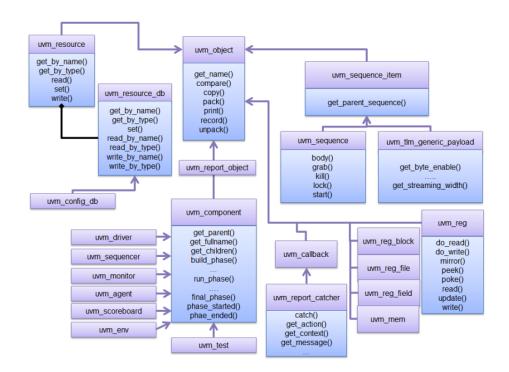

| 2.3  | UVM Class Diagram                                                                             | 10 |

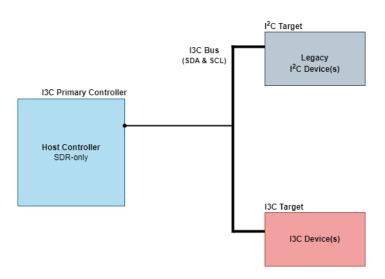

| 3.1  | Typical I3C Bus Configuration                                                                 | 16 |

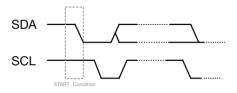

| 3.2  | START Condition                                                                               | 17 |

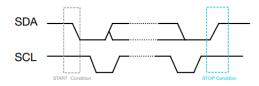

| 3.3  | STOP Condition                                                                                | 17 |

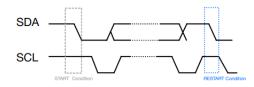

| 3.4  | RESTART Condition                                                                             | 18 |

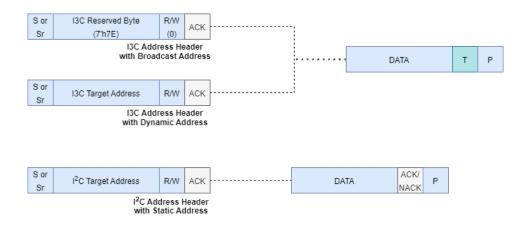

| 3.5  | Address Header Comparison                                                                     | 20 |

| 3.6  | Legacy I2C and I3C SDR protocol                                                               | 23 |

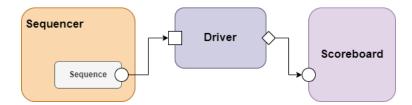

| 4.1  | Test-Bench Scheme                                                                             | 29 |

| 4.2  | Typical UVM Framework Structure                                                               | 31 |

| 4.3  | UVM Framework Structure                                                                       | 32 |

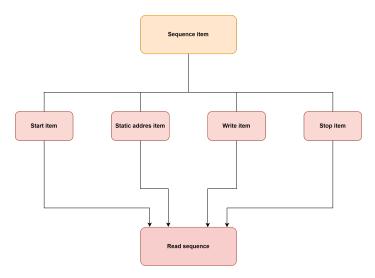

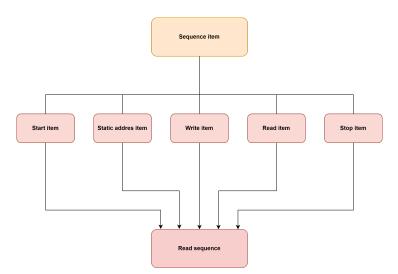

| 4.4  | Reference diagram of the sequence hierarchy levels for write operation<br>with Static Address | 35 |

| 4.5  | Reference diagram of the sequence hierarchy levels for read operation<br>with Static Address  | 36 |

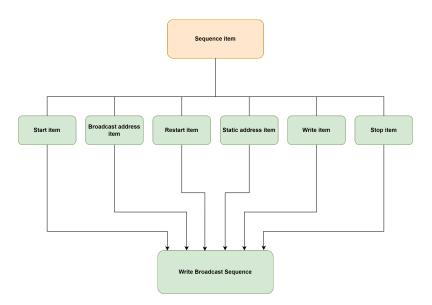

| 4.6  | Reference diagram of the sequence hierarchy levels for write operation                        | 50 |

| 4.0  | with Broadcast Address                                                                        | 36 |

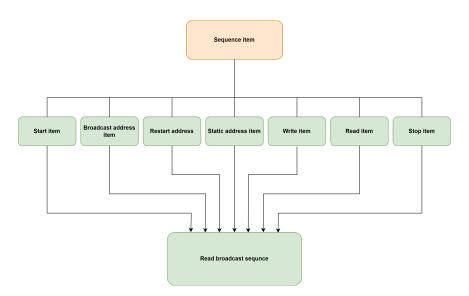

| 4.7  | Reference diagram of the sequence hierarchy levels for read operation                         |    |

|      | with Broadcast Address                                                                        | 37 |

| 4.8  | Types of Driver connection with Scoreboard and Sequence                                       | 41 |

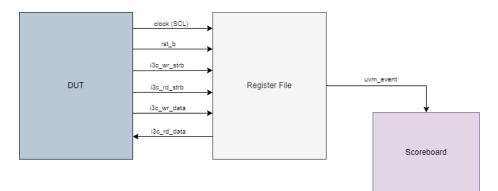

| 4.9  | Register File connections with the DUT and Scoreboard                                         | 46 |

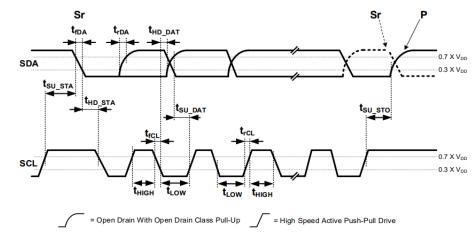

| 4.10 | I3C Legacy Mode Timing                                                                        | 48 |

| 5.1  | Frame images Legend                                                                           | 50 |

| 5.2  | File Code used to run the tests                                                               | 51 |

| 5.3  | Reference timing of I2C Write Operation with Static Target Address                            | 61 |

| 5.4  | Reference frame of I2C Write Operation with Static Target Address                             | 62 |

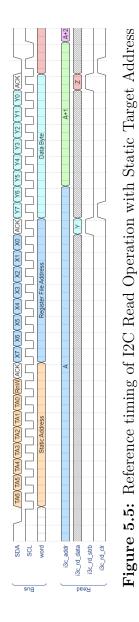

| 5.5  | Reference timing of I2C Read Operation with Static Target Address                             | 63 |

|      |                                                                                               |    |

| 5.6  | Reference frame of I2C Read Operation with Static Target Address    | 64 |

|------|---------------------------------------------------------------------|----|

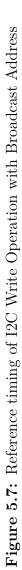

| 5.7  | Reference timing of I2C Write Operation with Broadcast Address .    | 65 |

| 5.8  | Reference frame of I2C Write Operation with Broadcast Address .     | 66 |

| 5.9  | Reference timing of I2C Read Operation with Broadcast Address .     | 67 |

| 5.10 | Reference frame of I2C Read Operation with Broadcast Address        | 68 |

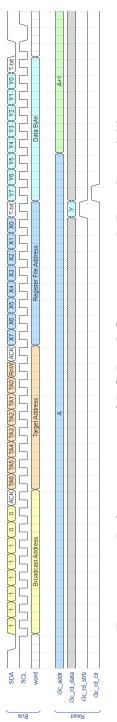

| 5.11 | Reference timing of SDR Write Operation with Broadcast Address      | 69 |

| 5.12 | Reference frame of SDR Write Operation with Broadcast Address .     | 70 |

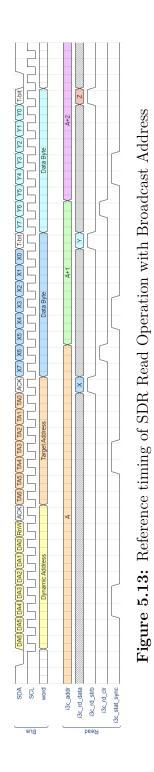

| 5.13 | Reference timing of SDR Read Operation with Broadcast Address       | 71 |

| 5.14 | Reference frame of SDR Read Operation with Broadcast Address .      | 72 |

| 5.15 | Reference timing of ENTDAA procedure                                | 73 |

| 5.16 | Reference frame of ENTDAA Procedure                                 | 74 |

| 5.17 | Simulation of an I2C Write Operation using Static Address           | 75 |

| 5.18 | Result of the comparison provided by the Scoreboard                 | 76 |

| 5.19 | Simulation of an I2C Write Operation using Broadcast Address        | 77 |

| 5.20 | Result of the comparison provided by the Scoreboard                 | 78 |

| 5.21 | Detail of the simulation regarding the sequence Broadcast Address   |    |

|      | 7'h7E, Repeated Start and Static Address 7'h68                      | 78 |

| 5.22 | Detail of the simulation regarding the Transition Bit at the end of |    |

|      | each Data Byte                                                      | 79 |

# Acronyms

### VIP

Verification IP

### $\mathbf{DUT}$

Design Under Test

### UVC

Universal Verification Component

### UVM

Universal Verification Methodology

### OVM

Open Verification Methodology

### SCL

Serial Clock

### SDA

Serial Data

### I2C

Inter Integrated Circuit

### I3C

Improved Inter Integrated Circuit

### BCR

Bus Characteristics Register

### CCC

Common Command Code

### DCR

Device Characteristics Register

### SDR

Single Data Rate

#### HDR

High Data Rate

### ENTDAA

Enter Dynamic Address Assignment

### $\mathbf{RTL}$

Register Transfer Level

### $\mathbf{SV}$

System Verilog

### OOP

**Object Oriented Programming**

### $\mathbf{TLM}$

Transaction-Level Modeling

### ACK

Acknowledgment

### NACK

Negative Acknowledgment

# Chapter 1

# Introduction

### 1.1 Goal of the thesis and structure

The aim of the thesis activity is to verify the correct operation of the I3CS IP Target device using the UVM (Universal Verification Methodology). This activity is carried out by the Verification team at TDK Invensense, a company based in Milan.

The primary goal is to perform top-level verification of the I3C Target device architecture, identify and rectify any potential design errors. As digital systems become increasingly complex, ensuring comprehensive coverage of all scenarios and working conditions becomes more challenging. The UVM methodology is employed to address this challenge by providing tools for creating a verification environment capable of covering all cases.

The UVM methodology offers advantages such as reduced verification time through randomization and parallel simulation, and automatic generation of test scenarios.

By leveraging the UVM methodology, the thesis work aims to achieve thorough verification of the I3C Target device and ensure its compliance with the specifications outlined by the I3C protocol.

The topics covered in the various chapters of the thesis are outlined below.

In chapter 2 the I3C protocol and UVM methodology are introduced in general. The parts that make up the I3C protocol, Controller and Target, are described at a high level, and particular attention is paid to the interfacing between these two blocks. Next, the UVM standard used for verification is described at a high level, focusing on the description of the fundamental aspects that make it efficient compared to other standards, namely the use of uvm\_components and uvm\_phases. The verification flow pursued in the thesis work will be detailed in the following chapters, providing a step-by-step description of the methodology used to verify

the I3CS IP Target device.

chapter 3 focuses on the analysis of the architecture of the Target I3CS IP device provided by the company. The features of the Target device are described and a particular emphasis is made on the modes it supports. These modes include SDR mode, Legacy I2C mode, and HDR mode. The chapter provides an overview of each mode and explains their significance in the context of the I3C protocol.

Additionally, the chapter introduces and explores various features of the I3C protocol that are supported by the Target device. This includes an overview of CCC (Common Command Code), which are standardized commands used by the Controller to communicate with the Target. The hot-join mechanism is also discussed, which allows the Target to join the I3C bus after it has been configured.

The communication frame between the Controller and Target is analyzed in detail. The frame consists of various components, such as the START condition, Header, Data, and STOP condition. Each component is explained, highlighting its role in the communication process between the Controller and Target.

In chapter 4, the focus is on the detailed structure of the UVM verification environment developed for the verification of the Target I3CS IP device. The discussion starts by delineating the reference test-bench that served as the foundation for developing the entire environment. The main blocks of the test-bench are identified, and their development is described.

The chapter provides insights into the thought process and decision-making involved in developing the sequences and tasks within the driver. It highlights the importance of considering various scenarios and working conditions to ensure thorough verification coverage of the Target device.

In chapter 5, the focus is on the analysis of the tests implemented during the thesis activity. The chapter begins by providing a list of the different test cases that are designed and executed. These test cases cover various scenarios and aspects of the Target I3CS IP device, including the main read and write operations.

Furthermore, the results generated by the executed tests are represented. The chapter includes information on the success or failure of each test case, any errors or issues encountered during the verification process, and any deviations from the expected behavior. The results provide valuable insights into the correctness and functionality of the Target device, as well as the effectiveness of the UVM test environment in capturing and detecting errors.

chapter 6 deals with conclusions highlighting the aims achieved in terms of completeness of the functional verification and effectiveness of the tests, moreover the skills acquired and the portability of the tests devised are emphasised.

# Chapter 2

# Overview of I3C Protocol and UVM Environment

### 2.1 Introduction to I3C Protocol

I3C is a two-wire bidirectional serial Bus, optimized for multiple sensor target devices and controlled by only one I3C controller device at a time. I3C is backward compatible with many Legacy I2C Devices, but I3C Devices support higher speeds up to a maximum of 12.5 MHz, new communication Modes, and new Device roles.

In the I3C protocol, communication between the Controller and the Target is facilitated through a two-wire interface consisting of the SDA (Serial Data) line and the SCL (Serial Clock) line.

The **SDA** line is responsible for carrying the actual data during the transfer. It is bidirectional, allowing both the Controller and the Target to transmit and receive data. The Controller initiates the communication by driving the SDA line to transmit data, while the Target responds by either driving the line to transmit data back or releasing it to allow the Controller to transmit.

The **SCL** line serves as a clock signal that synchronizes the communication between the Controller and the Target. It provides timing information to ensure that data is transferred at the correct rate. The SCL line is typically driven by the Controller, and both the Controller and the Target read and write data on the SDA line in synchronization with the clock pulses on the SCL line.

By using this two-wire interface, the I3C protocol enables communication between the Controller and the Target, allowing them to exchange data and synchronize their actions during the transfer. This approach ensures efficient and reliable data transfer in a simplified manner, as compared to protocols with additional communication lines.

fig:Communication Flow illustrates how I3C communication is initiated.

Figure 2.1: I3C Communication Flow

- **SDA** is a bidirectional data pin

- SCL

An I3C Bus supports the mixing of various Message types:

- 1. I2C-like SDR Messages, with SCL clock speeds up to 12.5 MHz

- 2. Broadcast and Direct CCC Messages that allow the Controller to communicate to all or one of the Targets on the I3C Bus, respectively

- 3. I2C messages to Legacy I2C Targets

### 2.1.1 I3C Controller Device

In the I3C protocol, the Active Controller refers to the I3C device that currently has control over the bus and is actively initiating and controlling the communication. The Active Controller can be considered as the "master" device in the I3C bus system.

Typically, the Active Controller is the device that sends the majority of the I3C Commands (CCC) on the bus. These commands can be either Broadcast CCCs, which are intended for all targets on the bus, or Directed CCCs, which

are specific to individual targets. The Active Controller uses these commands to initiate various operations and control the behavior of the targets on the bus.

Moreover, the Active Controller is the only device on the I3C bus allowed to send I2C Messages. This means that it can communicate with I2C devices that are present on the bus, providing backward compatibility with the legacy I2C protocol.

By being the Active Controller, a device assumes the role of actively controlling the communication on the I3C bus, sending commands and interacting with the targets. This distinction helps in managing the bus and coordinating the communication between different devices effectively.

In addition to send I3C Commands and I2C Messages, an I3C Controller Device also performs several other important functions in the I3C bus system. Some of these functions include:

- Dynamic Address Assignment: The I3C Controller Device is responsible for assigning unique Dynamic Addresses to the Target devices connected to the bus. It initiates the Dynamic Address Assignment procedure by broadcasting the ENTDAA (Enter Dynamic Address Assignment) command.

- Arbitration: The I3C Controller Device participates in address arbitration when multiple devices on the bus attempt to drive an address simultaneously. It follows the Open Drain approach and competes with other devices, including other Controllers and Targets, to determine the device that successfully drives the address onto the bus.

- Clock Generation: The I3C Controller Device generates and controls the clock signal (SCL) on the bus. It ensures that the clock signal is synchronized with the data signal (SDA) for reliable and accurate communication between the devices.

- **Bus Management**: The I3C Controller Device manages the overall operation and behavior of the I3C bus. It controls bus transactions, timing, and protocols to ensure proper data transfer and synchronization between the devices.

- **Power Management**: The I3C Controller Device may also have the capability to manage power-related functions on the bus. It can control power modes, perform power management operations, and coordinate power-related activities with the connected devices.

- Error Handling: The I3C Controller Device monitors and handles errors that may occur during communication on the bus. It detects and manages bus errors, data integrity issues, and other error conditions to ensure reliable and robust communication.

Overall, the I3C Controller Device plays a crucial role in managing and controlling the I3C bus system. It is responsible for initiating communication, assigning addresses, coordinating transactions, generating clocks, and ensuring smooth and efficient operation of the bus.

### 2.1.2 I3C Target Device

An I3C Target Device primarily listens to the I3C Bus for relevant I3C Commands sent by the Active Controller and responds accordingly. It acts as a "slave" device in the communication process. Additionally, an I3C Target Device always supports I3C SDR Mode, which is the basic mode of operation for I3C.

Unlike the I3C Controller Device, an I3C Target Device does not generate the bus clock (SCL). It relies on the clock generated by the Active Controller for synchronization during data transfer. The Target Device follows the timing and synchronization provided by the Active Controller.

For addressing, the I3C Target Device supports the Dynamic Address Assignment method, known as ENTDAA. This method allows the Target Device to participate in the Dynamic Address Assignment procedure initiated by the Active Controller. Through this procedure, the Target Device can obtain a unique Dynamic Address assigned by the Controller, which it uses for subsequent communication on the I3C Bus.

In summary, an I3C Target Device listens to commands, supports SDR Mode, follows the bus clock generated by the Active Controller, and participates in Dynamic Address Assignment for proper addressing on the bus. In addition the I3C Target Device can optionally:

- Generate Hot-Join events

- Request to become Active Controller, if the I3C Target Device also has I3C Controller Device capability.

- [1] [2]

## 2.2 Introduction to Verification

The development of a verification environment for the I3C Target Device is a crucial aspect of the thesis, and traditional testbenches may not be sufficient for verifying the functionality of a large-scale design like the I3CS IP Target. The UVM (Universal Verification Methodology) methodology is chosen to address these challenges.

UVM is a SystemVerilog-based verification methodology that provides a standardized framework for developing modular, reusable, and robust verification environments. It is built upon the OVM (Open Verification Methodology) version 2.1.1, which was created by Accellera. The UVM Class Library offers pre-defined building blocks and guidelines that aid in the development of well-structured and reusable verification components and test environments.

The primary goal of the verification process is to compare the RTL (Register Transfer Level) implementation of the design with its intended functionality. This involves defining the expected behavior of the DUT and comparing it against the observed behavior during simulation. The discrepancies or logic errors observed between the expected and observed behavior highlight potential functional logic errors in the design.

These logic errors can occur due to different factors and the verification process helps to uncover these errors and ensure that the design functions as intended according to the specifications.

By using the UVM methodology and developing a comprehensive verification environment, the thesis aims to enhance the verification process, improve test coverage, and detect any functional logic errors in the I3C Target Device design.

### 2.2.1 Verification Plan

The three key aspects of a verification plan in hardware design are:

- Coverage Measurements;

- Stimulus Generation;

- Response Checking.

**Coverage Measurement** This section is the one in which the verification scopes are described. This section determines if all bugs have been found .

**Stimulus generation** This section is responsible to generate the input test vector required to test the whole behaviour of a design. This part is crucial, since it generates not only valid test vectors but also invalid test vectors to drive the device outside of normal operating parameter in order to check the error detection logic of DUT. The goal is to generate test-vectors that allow reaching an high coverage level.

**Response Checking** The response checking section is responsible to verify the DUT responses conform to the specifications regarding the Reference model. One of the approaches used for this section is based on a Register File and Scoreboard in a structure like the one shown in Figure 2.2. For example, written and read values from Register File should match. When a written operation is performed to

the design, the Scoreboard receives the packet with output value from VIP and it should be the actual value. After that, the same Register File is read back from the design and the data is the expected value which is always sent to UVM Scoreboard. At this point the Scoreboard can compare the expected and the actual values to check if they match.

Figure 2.2: Scoreboard approach

## 2.3 The Universal Verification Methodology

The Universal Verification Methodology is an IEEE standard and the power of this methodology consists mainly in three aspects.

- The drastic reduction in the cost of verification: the verification engineer is assisted by the tools available within the UVM class library, thanks to which there is an increase in productivity.

- Reusability: it is possible to make use of previously created VIPs and configure them for new DUT with the same interfaces.

- Interoperability: the UVM standard makes it possible to standardise the construction of verification environments, allowing easy communication between different verification teams.

UVM is based on SV (System Verilog), a hardware description and verification language. It is open-source and compatible with all the major commercial simulator like Cadence, Mentor Graphics, Aldec and Synopsys. The base classes in the UVM hierarchy largely fall into three distinct categories:

• UVM Components: These classes represent the fundamental building blocks of a verification environment. They encapsulate reusable functionality and provide a modular structure for organizing the verification environment. Examples of UVM components include the *uvm\_component* class, which serves as the base class for all UVM components, and the *uvm\_test* class, which is used to define the top-level test sequences and scenarios.

- UVM Phases: Phases are used to orchestrate the execution of different tasks within the verification environment. They provide a structured flow for initializing, configuring, running, and shutting down the verification components. The UVM phases allow for better control and synchronization of the verification process. Some of the key UVM phases include the *build\_phase*, *connect\_phase*, *run\_phase*, and *shutdown\_phase*.

- UVM Transactions: Transactions represent the communication between the testbench and the DUT. They encapsulate the data and control information exchanged between the verification components and the DUT. UVM transactions provide a standardized format for stimulus generation, response checking, and functional coverage collection. The *uvm\_transaction* class is a base class for creating custom transaction classes tailored to specific communication protocols or interfaces.

These base classes, along with other supporting classes and utilities, form the foundation of the UVM methodology. They promote **reusability**, **scalability**, and **maintainability** in the verification process by providing a standardized framework for developing verification environments. By leveraging these classes, verification engineers can focus on developing the specific test scenarios and sequences needed to thoroughly verify the functionality of the design.

In UVM, the following phases are commonly used to synchronize and coordinate the activities of different components within the test-bench:

### **Build Phase**

- **uvm\_build\_phase**: This phase is responsible for constructing and initializing the components of the testbench. It is typically used to create and configure the necessary objects, set up connections, and allocate resources required for the testbench.

- **uvm\_connect\_phase**: In this phase, the connections between the different components of the testbench are established. It ensures that the signals and interfaces are correctly connected and ready for communication.

- **uvm\_end\_of\_elaboration\_phase**: This phase occurs after the elaboration of the design and testbench is complete. It is often used for performing any final configuration or initialization tasks before the simulation starts.

- **uvm\_start\_of\_simulation\_phase**: This phase marks the beginning of the simulation and is typically used to set up initial stimulus or prepare the testbench for simulation.

Figure 2.3: UVM Class Diagram

### Run phase

• **uvm\_run\_phase**: The run phase is the main phase where the testbench executes the test scenarios and sequences. It includes generating stimulus, driving the signals, and verifying the expected behavior of the design.

#### Clean up phase

- **uvm\_extract\_phase**: This phase is used for collecting and analyzing coverage data, functional coverage, and other metrics related to the verification progress.

- **uvm\_check\_phase**: It checks for any unexpected conditions in the verification environment.

- uvm\_report\_phase: It reports results of the test.

- uvm\_final\_phase: It ends the simulation.

These phases provide a structured and synchronized flow for the testbench components, ensuring that they execute their tasks in the appropriate order. By using these phases, the testbench components can collaborate effectively and exchange information at the right stages of the verification process.

### 2.3.1 The UVM Components

UVM is based on OOP, this allows to increase the redeployment. UVM Library provides a set of useful class from which deriving object and components, each class contains methods to deal with common operations.

The UVCs present in the verification environment are developed to communicate with the Target I3CS IP, and they behave as a Controller because:

- They send I3C commands: the UVCs generate and send I3C commands to the Target I3CS IP. These commands can be broadcast commands that target all devices on the bus or directed commands that address specific devices. By sending these commands, the UVCs emulate the behavior of an I3C Controller.

- They control the bus clock: the UVCs are responsible for generating and controlling the bus clock (SCL) signal during communication with the Target I3CS IP. They synchronize the data transfer and ensure that the communication occurs at the correct timing and frequency.

- They handle the communication protocol: the UVCs implement the I3C communication protocol, including the formatting of messages, addressing, and data transfer. They follow the rules and specifications defined by the I3C protocol to ensure proper communication with the Target I3CS IP.

By behaving as a Controller, the UVCs simulate the actions and behavior of an I3C Controller device, allowing for the verification of the Target I3CS IP's response and behavior in various scenarios and test cases.

Moreover, UVM uses TLM (Transaction-Level Modeling) APIs to facilitate communication between UVM components. TLM provides an abstraction layer that allows components to exchange transactions, which are packets of data representing specific actions or events in the DUT.

Sequences are used to define a sequence of transactions or actions to be performed by a UVM component. These sequences can be customized and extended to represent various scenarios and test cases. The sequences generate transactions that carry the necessary information and commands for the DUT.

Methods such as **put** and **get** are used to send or receive transactions between components. The **put** method is used to send a transaction from one component to another, while the **get** method is used to receive a transaction. These methods provide a standardized interface for communication and ensure that transactions are correctly passed between components.

By using TLM APIs and combining sequences and methods, UVM components can effectively exchange transactions and communicate with each other, enabling the coordinated and synchronized execution of test scenarios and the verification of the DUT's behavior. **Design Under Test** It is basically the RTL description in the designing language. It describes the features and functions of the design.

**Sequencer** It is the entity on which the sequences will run. In order to test DUT behavior, sequence of transaction needs to be applied. Sequencer runs stimulus generation code and sends sequence items down to driver whenever driver demands by it.

Driver It acts as an active component in the verification environment.

It receives sequence items from the sequencer, which encapsulate the necessary data and information about the desired transactions. The driver then translates these sequence items into appropriate signal values on the interface of the DUT. It uses the appropriate protocol or interface-specific mechanisms to send the transactions to the DUT.

**Monitor** It plays a crucial role in capturing and analyzing the behavior of the DUT, enabling the verification environment to collect coverage information, perform checks, and ensure the correctness of the design under verification.

**Agent** It serves as a bridge between the testbench and the DUT. It manages the communication and data flow between the testbench and the DUT through its driver and monitor. The sequencer within the agent controls the generation and sequencing of transactions or stimulus that are sent to the DUT.

The agent can operate in two modes: passive and active.

**Scoreboard** It is responsible for verifying the correctness of the DUT's behavior by comparing its output signals, registers, or other relevant data with the expected values. It ensures that the DUT is producing the expected results according to the specified functionality or requirements.

**Environment** It is a higher-level structure that assembles and manages various components of the verification environment. It provides a modular and organized approach to building the testbench for verifying the design under test.

**Test** It is the top-level component in the verification environment hierarchy. It is represented by a class that is derived from the uvm\_test base class provided by the UVM library.

The test class serves as a container for configuring the testbench and coordinating the overall verification process. It allows you to control the dynamic behavior of the testbench components, such as the DUT (Design Under Test), VIP (Verification IP), and other UVM components, by utilizing sequences.

**Sequence items** They are the necessary data objects that are passed at an abstract level between the verification components. Sequence items can contain fields or properties that represent different aspects of the transaction, such as addresses, data values, control signals, or any other relevant information. These fields are typically defined as class variables within the sequence item class.

**Sequences** They are responsible for generating a set of transactions or stimuli to be applied to the design under test (DUT). Sequences gather sequence items, which encapsulate the necessary data for each transaction, and combine them to create a coherent set of inputs.

Sequences can be either randomized or pre-determined, depending on the specific testing requirements.

[3]

# Chapter 3 Target I3CS IP architecture

Prior to delving into the implementation of the UVM framework, it is important to provide an introduction to the device under verification and its features.

The DUT, in this case, is the I3CS Target IP, which is designed to adhere to the specifications outlined in the MIPI I3C Standard v1.1.1.

The I3CS supports the following features:

- I2C Private Read and Private Write,

- I3C SDR Private Read and Private Write,

- I3C CCC Broadcast and Direct commands,

- I3C Hot Join request,

- I3C ENTDAA procedure.

## 3.1 Bus Configuration

An I3C bus can have the following compatible devices connected to it:

- I3C Primary Controller,

- I3C Secondary Controller,

- I3C Target,

- I2C Target.

In the context of I3C, a pure bus refers to a scenario where there are no I2C devices present on the bus, and all devices connected to the bus are I3C devices.

On the other hand, a mixed bus refers to a scenario where both I3C devices and I2C devices are present on the bus.

When an I3C bus is initially configured, it is done so in SDR mode by the I3C Primary Controller. The Primary Controller is responsible for controlling and managing the bus operations. If there is an I3C Secondary Controller present on the bus, it operates as a Target to the Primary Controller. The Secondary Controller follows the instructions and commands issued by the Primary Controller and participates in the bus transactions accordingly.

It's worth nothing that I3C is designed to be backward compatible with I2C, allowing I2C devices to coexist on the same bus. However, in a pure I3C bus configuration, there won't be any I2C devices present, and all devices on the bus will adhere to the I3C protocol.

A typical bus typology is reported in Figure 3.1.

Figure 3.1: Typical I3C Bus Configuration

[1]

### **3.2** Start, Stop and Restart Conditions

I3C uses a Frame encapsulation method. Each I3C Frame consists of the START, Header, Data, and STOP, which are always present.

Every transaction on the I3C bus begins with a START condition. This condition occurs when the SDA line transitions from high to low while the SCL line remains consistently high. The Target detects the Start condition on the bus, while the Controller initiates it. Conversely, all transactions on the I3C bus conclude with a STOP condition asserted by the Controller. A STOP condition is triggered by a low-to-high transition on the SDA line while the SCL line remains consistently high. The Target detects the STOP condition on the bus, while the Controller asserts it.

Instead of relying solely on the STOP condition, the I3C protocol also introduces a RESTART condition. This allows for the transmission of multiple messages within the same frame without requiring a stop and start signal between each message.

It is worth noting that the Start, Restart, and Stop conditions in the I3C Protocol are identical to those found in the I2C protocol. The behaviour of the SDA and SCL signals during the START, STOP and RESTART condition are shown in Figure 3.2, Figure 3.3 and Figure 3.4 respectively

Figure 3.2: START Condition

Figure 3.3: STOP Condition

### 3.2.1 I3C Address Header

After initiating a START, the Header in I3C serves the purpose of Bus Arbitration. The Controller utilizes the Header to address the Target Device.

An I3C Bus consists of one Controller and one or more Targets. A device that possesses both I3C Controller and I3C Target capabilities cannot simultaneously function as both a Controller and a Target. Instead, it must be configured to operate either as an I3C Target Device or as an I3C Controller Device.

Figure 3.4: RESTART Condition

Within the I3C protocol, various Controller and Target Device Roles are defined to represent the functional capabilities of each respective I3C device. Each I3C Device must support at least one Device Role, although it can be designed to support multiple Device Roles. The supported Device Roles of an I3C Device are exposed through its BCR (Bus Characteristics Register).

During a data transfer, the bus Controller initiates the process. It begins by issuing a START signal to all connected devices. Subsequently, the Controller sends the ADDRESS of the specific Target device it intends to communicate with. The Read or Write operation signal bit is also transmitted alongside the ADDRESS bits. All devices connected to the bus compare the received address bits with their own address. If there is no match, they simply wait until the bus is released. Conversely, if the address matches, the chip generates an ACK (Acknowledgment) signal in response.

Upon receiving an acknowledgement, the Controller proceeds with the transmission of DATA. Each data byte comprises 8 bits, and an acknowledgement or transition bit follows each transferred byte. Once the transmission is complete, the Controller issues the STOP signal.

### 3.2.2 I3C Address Arbitration

An Address Header that follows a START condition, excluding a Repeated START, is susceptible to Arbitration. This means that both the Controller and one or more Targets may contend for control of the Bus and attempt to drive their respective Addresses onto the Bus using the SDA line. The Arbitration model employed in this scenario adheres to the standard Open Drain approach.

In this model, both the Controller and the Target(s) that are transmitting an Address must adhere to the same rule:

1. If the current bit to transmit is a 0, then the Device shall drive SDA Low after the falling edge of SCL and hold Low until the next falling edge of SCL.

2. If the current bit to transmit is a 1, then the Device shall not drive SDA, but rather shall High-Z SDA on the falling edge of SCL.

### 3.3 I3C SDR Data Words

An I3C Message is considered an SDR Message if it adheres to the specifications and requirements of the SDR mode in the I3C protocol. Here are the conditions that define an SDR Message in I3C:

- The Address in the Address Header could be 7'h7E, that is the I3C Broadcast Address. All I3C Targets shall match Address value 7'h7E. While, no I2C Target will match the Broadcast Address because this value is reserved and unused in I2C.

- The Address in the Address Header matches the Target's Dynamic Address. All I3C Targets shall match their own Dynamic Address.

In summary, an I3C Message is classified as an SDR Message when it follows the specifications and requirements of the SDR mode in terms of mode of operation, data rate, frame format, signal levels, and device support.

The I3C SDR mode is backward compatible with I2C protocol and conditions, which allows for legacy I2C Target Devices to coexist with I3C devices on the same I3C bus. The MIPI I3C Specification strongly suggests that legacy I2C devices incorporate 50 ns spike filters on the SDA and SCL pads to make it possible for them to ignore the I3C traffic higher speeds. With spike filters implemented for all I2C targets on the bus, the I3C bus can operate at the maximum rated clock frequency. The I3C Target module on this device can be used in I2C Target mode until it is assigned a Dynamic Address.

In Figure 3.5 is reported the frame about I3C SDR mode and about the I2C Legacy mode.

In I3C SDR, the Data Words match I2C only in the sense that they are both 9 bits long. I3C SDR Data Words differ from I2C in two ways.

• Ninth Bit of SDR Controller Written Data as Parity : In I2C, the ninth Data bit written by the Controller serves as an ACK from the Target. However, in I3C, the ninth Data bit written by the Controller represents the Parity of the preceding eight Data bits. As a result, in I3C, the Target is not required to drive the SDA line for Data written by the Controller in SDR mode.

In the context of SDR, the ninth bit of Write data in I3C is commonly referred to as the Transition Bit (T-bit).

Figure 3.5: Address Header Comparison

• Ninth Bit of SDR Target Read Data as End-of-Data: In I2C, the ninth Data bit transmitted from the Target to the Controller serves as an ACK by the Controller. However, in I3C, this ninth Data bit has a different purpose. It allows the Target to terminate a Read operation, and it enables the Controller to abort a Read operation. In the context of SDR mode in I3C, the ninth bit of Read data is referred to as the T-Bit. It has specific significance in determining the end of a Read operation. To facilitate this, a Target should incorporate an SDA Read detector. This detector monitors whether the SCL clock has remained unchanged for a duration of 100 microseconds (us) or more. If such a condition is detected, the Target can abort the ongoing Read operation by switching SDA to a High-Z state (high impedance) and waiting for a Repeated START or STOP condition.

Ninth Bit of SDR Controller Written Data as Parity bit In I3C, the ninth data bit of each SDR Data Word written by the Controller is a Parity Bit, which is calculated using odd parity. The value of this Parity bit is determined by performing an XOR operation on the 8 Data bits along with a binary 1, as follows: XOR(Data[7:0], 1).

During the SCL High period, Parity bit writes should be maintained valid. This means that the Parity bit should remain stable and not change during this period. When the T-Bit represents the last data byte being transmitted, the write of the Parity bit is kept valid through the SCL High period. Once the SCL transitions to Low, the Controller can then proceed to either change the SDA line or leave it unchanged in preparation for the Repeated START or STOP condition that follows.

Ninth Bit of SDR Target Read Data as End of Data In I2C, the Read operation from the Target is controlled by the Controller only, which means that the Target has no control over the amount of data it returns. However, in I3C SDR, the Target has the ability to control the number of data words it returns, providing more flexibility. Additionally, the I3C Controller also has the ability to abort the Read operation prematurely if necessary.

The mechanism that controls the Read operation in I3C SDR is based on the ninth (T) data bit of each data word returned by the Target. The Target can return the ninth bit in one of three ways:

- No Change: the Target keeps the ninth bit the same as the previous data word, indicating that there is more data to be read.

- Change to 1: the Target changes the ninth bit to 1, indicating that it has finished returning data and there is no more data to be read.

- Change to 0: the Target changes the ninth bit to 0, indicating an abort condition. This allows the Controller to prematurely abort the Read operation if necessary.

By manipulating the ninth bit in this manner, the Target and Controller can effectively control the amount of data transferred during a Read operation in I3C SDR.

- The I3C Target returns the ninth bit as 0 (SDA Low) to end the Message:

- The Target shall set SDA Low on the falling edge of SCL.

- On the following rising edge of SCL, the Target shall set SDA to High-Z.

- The I3C Controller shall drive SDA Low on the rising edge of SCL.

- The I3C Controller then shall issue either a STOP, or a Repeated START.

- The I3C Target returns the ninth bit as 1 (SDA High) to continue the Message:

- The Target shall set SDA High on the falling edge of SCL.

- On the following rising edge of SCL, the Target shall set SDA to High-Z.

- The Target shall monitor the SDA on the falling edge of SCL:

- If SDA is High, then the Target shall continue with the next value.

- If SDA is Low and if there has been a Repeated START, then the Message has been aborted, and the Target shall not drive SDA after that.

### 3.3.1 Transition from Address ACK to SDR Controller Write Data

The end of any Address Header is an ACK or NACK by the one or more addressed Targets, using Open Drain on SDA:

- If 7'h7E, then it is the ACK of all I3C Targets on the Bus.

- If a single Target Address, then it is the ACK (or NACK) of the addressed Target, or a NACK if no such Target is on the Bus.

When the Address Header results in an ACK, I3C SDR specifies how the handoff is to occur.

## 3.4 Legacy I2C Transaction on I3C Bus

Until the Dynamic Address is assigned, the I3C Target operates in I2C Target Mode and uses the Static Address to represent itself on the bus. When in this mode, the Controller can use an **I2C Write** Transfer to write data to the Target directly and an **I2C Read** Transfer to read data from the Target directly. It is possible for an I2C Transaction to take place even when the bus is configured to operate in I3C SDR Mode or when an I3C SDR Transaction is in progress. For instance, the Controller can choose to transmit I3C Broadcast Address 7'h7E/W followed by a Restart and I2C Static Address to begin an I2C Transaction while in I3C SDR Mode.

### 3.4.1 I2C Private Read and Private Write

I3C Targets are capable of acting as standard I2C Targets as long as they have an I2C Static Address. The I3CS IP supports two types of I2C transfers:

- 1. Legacy I2C transfer starting with the Static Target address

- 2. Legacy I2C transfer starting with the 7'h7E broadcast address

Both types of transfer support Read and Write access types.

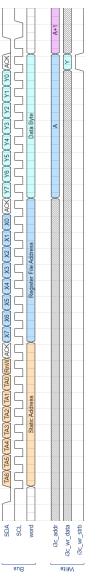

In legacy I2C and I3C SDR the Controller must use the following protocol to transmit the register offset then the data to the I3CS IP.

The ADR field is the Target Static or Dynamic address, OFFSET is the register offset. DATA is an unbounded series of bytes, The first phase is always a Write transaction to set the OFFSET, the second phase can be a Read or Write transaction.

| Fi      | rst phase (S | DR)    |    | :   | Second phase ( | SDR)    |

|---------|--------------|--------|----|-----|----------------|---------|

| S<br>Sr | ADR          | OFFSET | Sr | ADR | DATA           | P<br>Sr |

Figure 3.6: Legacy I2C and I3C SDR protocol

In **Read mode**, the first DATA byte will come from a register read access at address OFFSET. Then each subsequent byte will come from a read access at the previous address incremented by one if ena\_autoinc is set to one.

In Write mode, the first DATA byte will be sent to register write access at address OFFSET. Then each subsequent byte will be sent to a write access at previous address incremented by one through ena\_autoinc signal.

- The I3C START and STOP are identical to the I2C START and STOP in their signaling, but they vary in their timing. In I3C SDR, a STOP or Repeated START is tolerated any time that SCL is high while the Controller checks SDA or SDA is Open-Drain. This is unlike I2C, which wants STOP or Repeated START only after a NACK of an address, or after ACK/NACK of data.

- The I3C Address Header is identical to the I2C Address Header in bit form and in signaling, but it may vary from I2C in its timing.

- The Data 9-bit Words use the same bit count as I2C, but differ in the ninth bit where the acknowledge is substituted with the Transition Bit.

## 3.5 Dynamic Address Assignment Mode

The Active Controller assumes the responsibility of conducting the Dynamic Address Assignment procedure, which aims to assign a unique Dynamic Address to every I3C Device connected to the Bus. Once a Target device receives a Dynamic Address, it will use this address for all subsequent transactions on the I3C Bus, unless the Controller decides to change it, if applicable.

The Dynamic Address Assignment procedure involves an Address Arbitration process that shares similarities with I2C. However, it diverges from I2C by incorporating the concatenated values of the 48-bit Provisioned ID, BCR (Bus Characteristics Register), and DCR (Device Characteristics Register). In each Arbitration round, the Device on the I3C Bus with the lowest concatenated value emerges as the winner, and the Controller assigns a unique Dynamic Address to each victorious Device.

### 3.5.1 Dynamic Address Assignment Procedure

The Dynamic Address Assignment procedure in I3C is initiated by the Active Controller through broadcasting the ENTDAA CCC. If a Target device does not have a Dynamic Address already assigned, it automatically participates in this procedure.

During the Dynamic Address Assignment, the Target device sends its own 48-bit Provisional ID, BCR, and DCR in Open Drain mode to engage in Arbitration. The Target device will win the Arbitration if it has the lowest concatenated value of the Provisional ID, BCR, and DCR.

Once the Target device wins the Arbitration, the Active Controller transfers a 7-bit Dynamic Address to the Target device, followed by the Parity T-bit. If the parity is valid, the Target device acknowledges (ACK)s the Active Controller, stores the Dynamic Address, switches to I3C SDR mode, and updates its Dynamic Address accordingly.

However, if the parity is invalid, indicating an error in the data transmission, the Target device passively NACKs (negative acknowledgement) the Active Controller and waits for the next Arbitration round to retry the Dynamic Address Assignment procedure. Figure 5.16 shows the frame format for a typical Dynamic Address Assignment procedure.

### 3.5.2 Target Device48-bit Provision ID

A Device that supports the Broadcast Command Code Enter Dynamic Address Assignment shall have a 48-bit Provisioned ID. The Controller shall use this 48-bit Provisioned ID, unless the Device has a Static Address and the Controller uses the Static Address.

The 48-bit Provisioned ID is composed of three parts:

- 1. Bits[47:33]:MIPI Manufacturer ID (15 bits) only the 15 Least Significant Bits are used.

- 2. Bit[32]:Provisioned ID Type Selector(One Bit, 1'b1:Random Value, 1'b0:Vendor Fixed Value)

- 3. **Bits**[**31:0**]:32 bits containing either a Vendor Fixed Value or a Random Value, depending on the value of Bit[32]. If the value of **Bit**[**32**] is **1'b0** : Vendor Fixed Value

### 3.5.3 CCC (Common Command Code)

Common Command Codes are standardized commands that are universally supported and can be transmitted by the Controller in the I3C bus. These commands

can either be directed to a specific target or broadcasted to all targets simultaneously. The CCC protocol is formatted using I3C SDR mode and always commences with the I3C Broadcast Address (7'h7E/W). This specific address is recognized by all I3C targets present on the bus. However, any I2C target on the bus will NACK the request as 7'h7E is a reserved address in the I2C protocol.

Each CCC is assigned a unique 8-bit command code. The command code space is divided into two categories: Broadcast CCCs and Direct CCCs.

Broadcast CCCs encompass command codes ranging from 0x00 to 0x7F. These codes are used for commands that are broadcasted to all targets on the bus simultaneously.

On the other hand, Direct CCCs include command codes from 0x80 to 0xFE. These codes are utilized for commands directed specifically to a particular target.

To differentiate between the two types of CCCs, targets can examine the Most Significant bit (bit 7) of the command code. If bit 7 is set to 0, it indicates a Broadcast CCC, whereas if it is set to 1, it signifies a Direct CCC.

For a comprehensive list of the command codes associated with all supported CCCs in this Target module, please refer to table 3.1.

All the Broadcast CCCs share the same general frame format and has the following sequence:

- Start or Restart, followed by the Broadcast Address,

- Broadcast CCC value, followed by any required defining byte or data,

- End of command.

All the Direct CCCs share the same general frame format and has the following sequence:

- Start or Restart, followed by the Broadcast Address,

- Direct CCC value, followed by any required defining byte or data,

- Restart, followed by the address of the targeted Target, followed by any required defining byte or data,

- Repeat step 3 if the Controller wants to address multiple targets in the same CCC transaction,

- End of command.

In this thesis activity, the tested CCC is the ENTDAA command. However, it's important to note that the Target module also supports other commands listed

in table 3.1. The Controller employs the Broadcast ENTDAA CCC to signal all I3C devices on the bus to initiate the Dynamic Address Assignment procedure, as outlined in the Dynamic Address Assignment section. The Target module will participate in this procedure unless it already has a Dynamic Address assigned. In such cases, the Target will NACK the ENTDAA command and wait for the next Start condition.

It's important to note that the ENTDAA CCC always concludes with a Stop condition (not a Restart).

| Common Command<br>Code (CCC) | Туре                                          |                                | Value        | Brief Description                               |

|------------------------------|-----------------------------------------------|--------------------------------|--------------|-------------------------------------------------|

| ENEC                         | Enable Events Command                         | Broadcast Write                | 0x00         | Enable Target events                            |

| LIVEO                        | Enable Events Command                         | Direct Write                   | 0x80         | such as Hot-Join                                |

| DISEC                        | Disable Events Command                        | Broadcast Write                | 0x01         | Disable Target event                            |

|                              |                                               | Direct Write                   | 0x81         | such as Hot-join                                |

|                              | Enter Dynamic Address<br>Assignment           | Broadcast Write                | 0x07         | Enter Controller initiation                     |

| ENTDAA                       |                                               |                                |              | of Dynamic                                      |

| LIGDAA                       |                                               |                                |              | Address Assignment                              |

|                              |                                               |                                |              | Procedure                                       |

| RSTDAA                       | Reset Dynamic Address                         | Broadcast Write                | 0x06         | Discard Current                                 |

| 10510111                     | Assignment                                    | Direct Write                   | 0x86         | Dynamic Address                                 |

|                              | Set New Dynamic<br>Address                    | Direct Write                   | 0x88         | Controller assigns                              |

| SETNEWDA                     |                                               |                                |              | new Dynamic Address                             |

|                              |                                               |                                |              | to a Target                                     |

| GETPID                       | Get provisional ID                            | Direct Read                    | 0x8D         | Controller queries                              |

|                              | P                                             | Direct Read                    | ONOD         | Target's Provisional ID                         |

|                              |                                               | Direct Read                    | 0x8F         | Controller queries                              |

| GETDCR                       | Get Device<br>Characteristics Register        |                                |              | Target's                                        |

| dliben                       |                                               |                                |              | Device Characteristics                          |

|                              |                                               |                                |              | Register                                        |

| GETBCR                       | Get Bus Characteristics<br>Device             | Direct Read                    | 0x8E         | Controller queries                              |

|                              |                                               |                                |              | Target's Bus Characteristics Register           |

| RSTACT                       | Target Reset Action                           | Broadcast Write                | 0x2A         | Controller configures                           |

| nomer                        |                                               | Direct Write and               | 0x9A         | and/or queries                                  |

|                              |                                               | Read                           | 0.01         | Target Reset action and timing                  |

| SETMRL                       | Set Maximum Read                              | Broadcast Write                | 0x0A         | Controller sets                                 |

|                              | Length                                        | Direct Write                   | 0x8A         | maximum read length and IBI payload size        |

| SETMWL                       | Set Maximum Write                             | Broadcast Write                | 0x09         | Controller sets                                 |

|                              | Length                                        | Direct Write                   | 0x89         | maximum write length<br>Controller queries      |

|                              | Get Mximum Read<br>Length                     | Direct Read                    | 0x8C         |                                                 |

| GETMRL                       |                                               |                                |              | Target's maximum<br>possible read length        |

| GEIMINL                      |                                               |                                |              | and IBI                                         |

|                              |                                               |                                |              | and IBI<br>payload size                         |

|                              |                                               |                                |              | Controller queries                              |

| CETMWI                       | Get Maximum Write<br>Length                   | Direct Read                    | 0x88         | 1                                               |

| GETMWL                       |                                               |                                |              | Target's maximum<br>possible write length       |

|                              |                                               |                                |              |                                                 |

| GETMXDS<br>SETBUSCON         | Gets Maximum Data<br>Speed<br>Set Bus Context | Direct Read<br>Broadcast Write |              | Controller queries<br>Target's maximum          |

|                              |                                               |                                | 0x94<br>0x0C | read and write                                  |

|                              |                                               |                                |              | data speeds                                     |

|                              |                                               |                                |              | and maximum read                                |

|                              |                                               |                                |              | turnaround time                                 |

|                              |                                               |                                |              | Controller specifies a                          |

|                              |                                               |                                |              | Controller specifies a<br>higher-level protocol |

|                              |                                               |                                |              | and/or                                          |

|                              |                                               |                                |              | and/or<br>I3C specification version             |

|                              |                                               |                                |              | Controller queries                              |

| GETSTATUS                    | Get Device Status                             | Direct Read                    | 0x90         |                                                 |

|                              |                                               | L                              |              | Target's operating status                       |

Table 3.1: CCCs Table

# 3.6 Hot-Join Mechanism

The Hot-Join mechanism in I3C allows a Target to join the I3C bus even after the bus has been configured according to the I3C Bus Configuration. Hot-Join is typically used in scenarios where the Target remains depowered until needed or when the Target is physically inserted into the I3C bus without disrupting the SDA and SCL lines.

To initiate a Hot-Join request, the Target must meet the following conditions:

- The Target is Hot-Join capable.

- The Target does not have a Dynamic Address already assigned.

- Hot-Join is enabled on the bus by the Controller.

The Target can initiate a Hot-Join request and once the request has been made, the Target will wait for the Bus Idle condition before proceeding. In the standard Hot-Join process, the Target will issue a Start on the bus by pulling the SDA line low. The Active Controller acknowledges the Start condition by sending clocks on the SCL line, marking the beginning of the Arbitrable Address Header. During this phase, the Target transmits the 7'h02/W Hot-Join Address on the bus.

However, it is not always necessary for the Target to wait for the Bus Idle condition to occur. If another device on the bus issues a Start signal before the Bus Idle condition, the Target can still participate in the Address Arbitration process. In this case, the Target will passively engage in the arbitration by transmitting the 7'h02/W Hot-Join address on the bus. After the Target successfully wins the address arbitration and the Controller acknowledges the Hot-Join request, the Controller proceeds with sending the Broadcast ENTDAA CCC on the bus. This initiates the Dynamic Address Assignment procedure for the Target, following the guidelines outlined in the Dynamic Address Assignment section.

In the event that the Hot-Join request is unsuccessful, either due to the Controller NACKing the request or the Target losing arbitration, the Target will continue to attempt the Hot-Join request in subsequent opportunities. In the case of standard Hot-Join, the Target will retry at the next Bus Idle condition. In the case of passive Hot-Join, the Target will retry at the next Start condition on the bus. The Target will make further attempts until the Hot-Join request is successfully acknowledged. The frame format of a successful Hot-Join transaction is shown in

## 3.7 HDR Mode

The I3C HDR (High Data Rate) modes are specifically designed to enable the transfer of larger amounts of data while maintaining the same bus frequency.

However, it's important to note that the Target module on this particular device does not support the HDR modes specified in the MIPI I3C Specification.

Despite not supporting the HDR modes, the Target module is still capable of detecting HDR Enter and Exit Patterns. This allows the module to appropriately respond to bus traffic involving HDR operations, ensuring compatibility and seamless communication within the I3C bus.