# POLITECNICO DI TORINO

Department of Control and Computer Engineering (DAUIN)

Master's Degree Thesis

Leveraging Deep Learning Techniques for Cross-Family Side-Channel Attacks on 8-bit Microcontrollers

Advisor Paolo Ernesto Prinetto Co-Advisor Samuele Yves Cerini Candidate Antonio De Luca

Academic Year 2022/2023

# Acknowledgements

I wish to sincerely thank Professor Prinetto for the opportunity to work on this thesis, having me face problems that I never thought I could solve by myself, and for the availability towards me. Special thanks go to his team, that made me feel welcome since the very first day and who I owe many coffees to, more than I can remember.

I would like to express my deepest gratitude to Samuele "Sem" Cerini, who helped me throughout the work and shared passion for the topics (and problems) of this thesis.

I am extremely grateful to my three families: all my family in Lucera to whom I dedicate my whole academic path, my Portuguese family who has adopted me since three years and my friends, that I consider as a further family. You are too many to thank individually, but you know how much you all mean to me.

Finally, to my girlfriend, the one person that made all of this possible, cheering me up in bad times. The only person I feel unutterably close to, even across different countries.

# Abstract

The decreasing price of consumer electronics and the rise of the Internet of Things ("IoT") paradigm are contributing to the massive spread of embedded systems and microcontrollers. These low cost devices, often characterised by limited performance, internet connectivity and low power consumption are now permeating our lives with applications in home appliances, wearable devices and industrial controllers.

Despite being so widely spread, the protection of the data they handle is rarely tackled. Cryptographic algorithms were developed to provide effective protection mechanisms against cyber attackers, although their implementation on physical devices plays an important role in their attack resistance, exposing new vulnerabilities.

The elevated number of embedded devices combined with the importance of sensitive data led to new attack methodologies, known as *Side-Channel Analysis* ("SCA"). SCA consists of a series of techniques that exploit energy leakages (e.g., power, thermal, electromagnetic) to extract secret information about data handled by a device, and decrease the time needed to lead a successful attack by orders of magnitude with respect to brute-force.

In recent years, Deep Learning techniques have been leveraged to achieve improvements in this research field, leading to the rise of *Deep Learning Side-Channel Analysis* ("DLSCA").

Deep Learning promises to solve some of the problems encountered by classic Side-Channel Analysis techniques, such as the need for human intervention (e.g., features extraction and leakage model selection), and aims at improving the accuracy and the efficiency of the attacks.

The relevance of DLSCA is increasing, as demonstrated by the large quantity of studies carried out since the past mid-decade. Similarly, new challenges for researchers in the field are arising, such as the need to use the knowledge acquired during attacks to build effective defensive mechanisms, the portability of attacks across different devices or "ablation" as a solution to design lighter Deep Learning models.

Among these challenges, the problem of the portability of attacks is tackled only marginally, needing considerable expertise in both Security for Embedded Systems and Deep Learning Techniques.

This work aims at studying the behaviour of Deep Learning models in cross-devices scenarios, exploring their capabilities and limits in new portability contexts, taking advantage of the novelties introduced by DLSCA.

The knowledge gained from devices in a specific group of microcontrollers (known as *profiling devices*, considering *Microchip*'s PIC18XXXK42 family) is exploited to launch an attack on devices from a different group of microcontrollers (referred to as *attack devices*, from *Microchip*'s PIC18XXXK20 family), despite the differences between the two groups.

In the case of Power Side-Channel Analysis, the acquisition of traces from the 8-bit microcontrollers is performed thanks to an open-source toolkit called "ChipWhisperer",

by *NewAE*. The work relies on the open-source framework "AISY", developed by the *Delft University of Technology*, and partly on the framework for DLSCA by *eShard*.

The results obtained demonstrate that it is possible to perform cross-family attacks with all the trained models shown in the thesis, although the best performance can only be achieved leveraging an ad-hoc model tuned for the profiling dataset, correctly configured for the attack.

# List of Figures

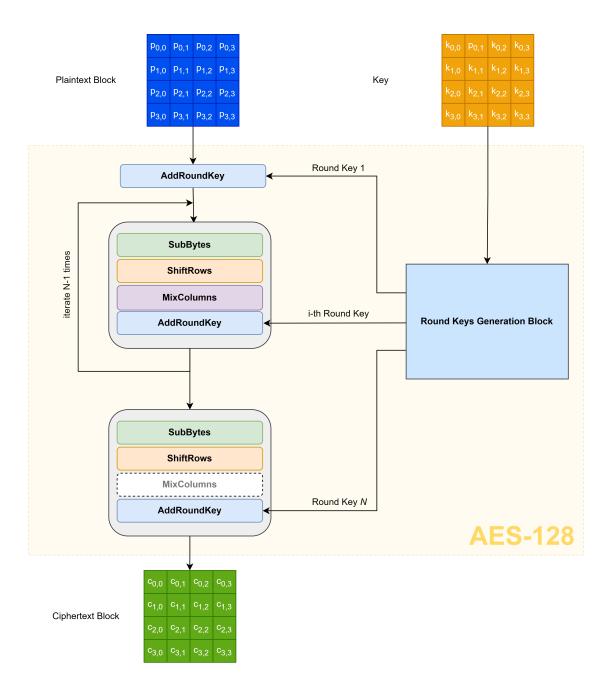

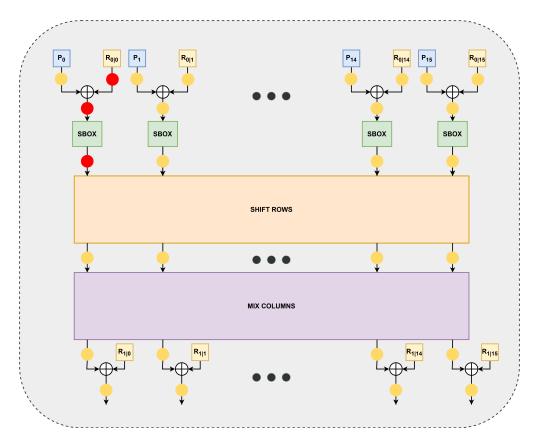

| 2.1  | Diagram of operations performed during encryption in AES-128                  | 14 |

|------|-------------------------------------------------------------------------------|----|

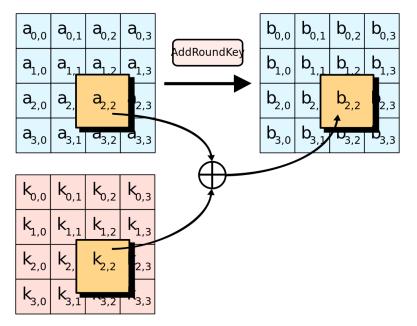

| 2.2  | The AddRoundKey operation [1].                                                | 15 |

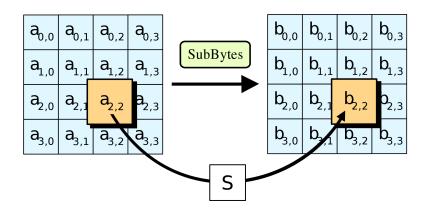

| 2.3  | The SubBytes operation [2].                                                   | 15 |

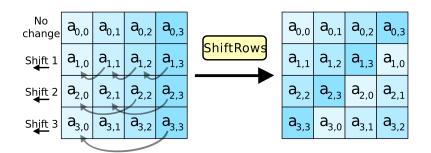

| 2.4  | The ShiftRows operation [3]                                                   | 16 |

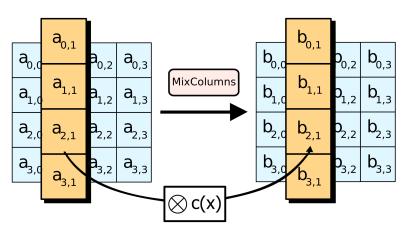

| 2.5  | The MixColumns operation [4]                                                  | 16 |

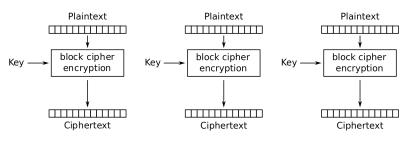

| 2.6  | Encryption in ECB mode [5].                                                   | 19 |

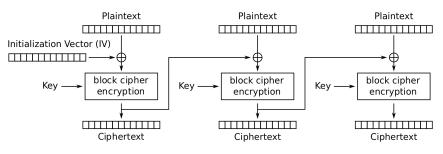

| 2.7  | Encryption in CBC mode [6].                                                   | 19 |

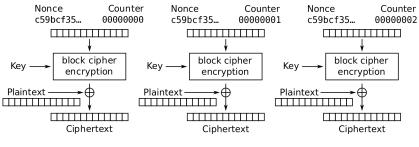

| 2.8  | Encryption in CTR mode [7]. $\ldots$                                          | 19 |

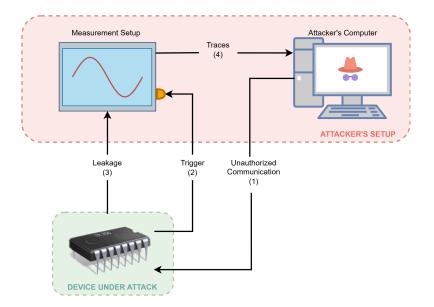

| 3.1  | Generic Setup for SCA [8]                                                     | 22 |

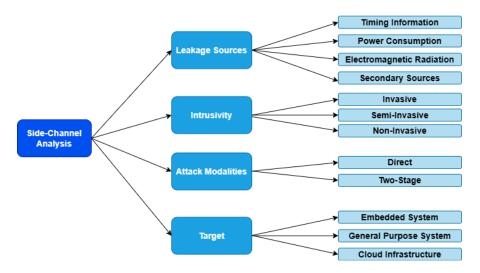

| 3.2  | Taxonomy of Side-Channel Analysis.                                            | 23 |

| 3.3  | String comparison that leaks timing information.                              | 23 |

| 3.4  | Effect of input switch in CMOS inverter                                       | 24 |

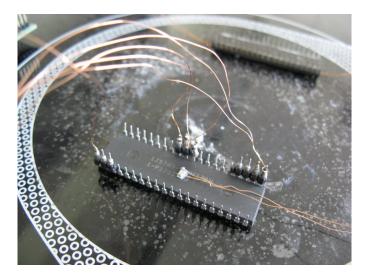

| 3.5  | Probe for electromagnetic measurements used in [9]                            | 25 |

| 3.6  | Heating plate with two temperature sensors for an ATmega162 [10]              | 25 |

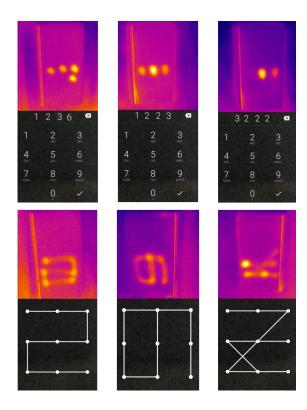

| 3.7  | Thermal trace that allows to recover secret pin and sign on mobiles [11].     | 26 |

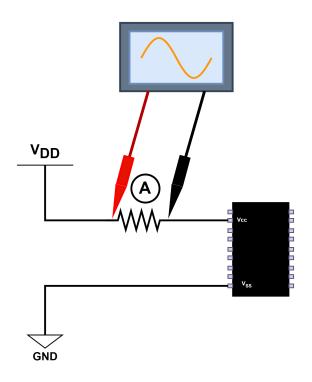

| 3.8  | Shunt resistor located upstream of the target device                          | 29 |

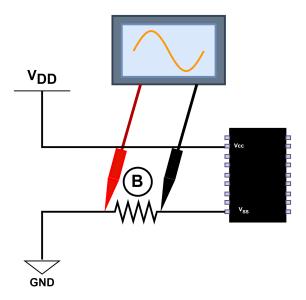

| 3.9  | Shunt resistor located downstream of the target device                        | 29 |

| 3.10 | Implementation of the exponentiation algorithm in RSA [12]. $\ldots$ $\ldots$ | 30 |

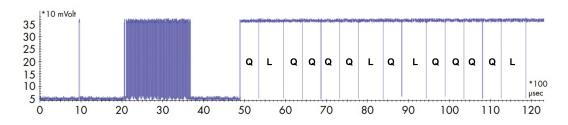

|      | Power consumption trace of the exponentiation algorithm [12]                  | 31 |

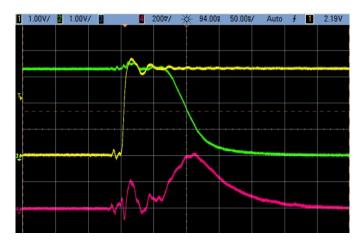

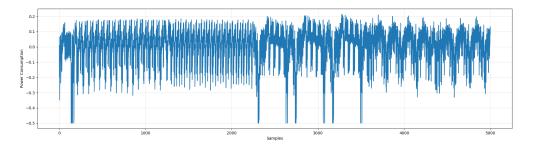

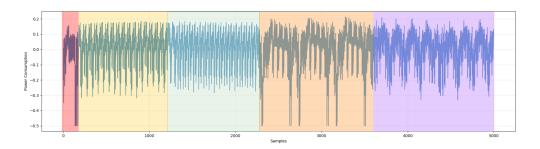

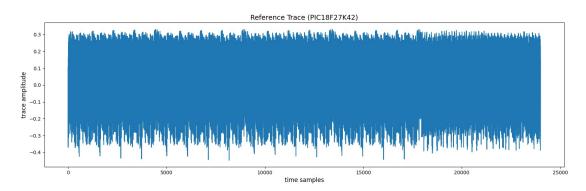

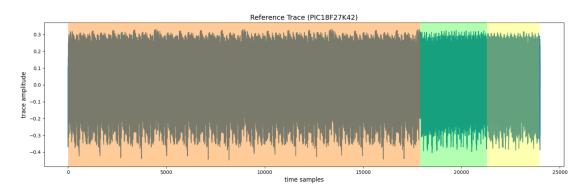

|      | Power trace collected during AES encryption on XMEGA target                   | 31 |

| 3.13 | Simple Power Analysis, annotations on power trace.                            | 32 |

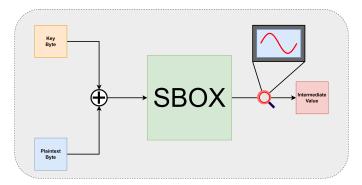

| 3.14 | Particular of the $\tt AES$ algorithm: the AddRoundKey and SubBytes steps     | 32 |

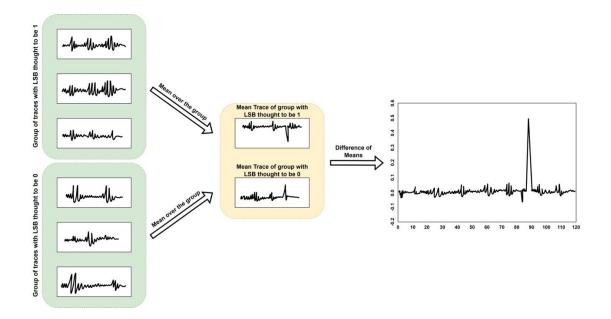

| 3.15 | Python script of DPA attack on a single bit of the key                        | 33 |

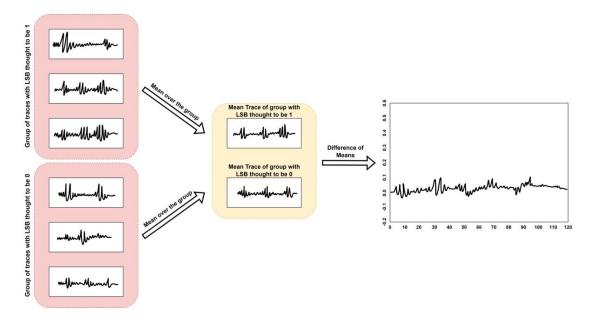

| 3.16 | Wrong grouping of traces. The mean does not reveal the contribution of        |    |

|      | the LSB                                                                       | 34 |

| 3.17 | Correct grouping of traces. The mean reveals the contribution of the LSB.     | 35 |

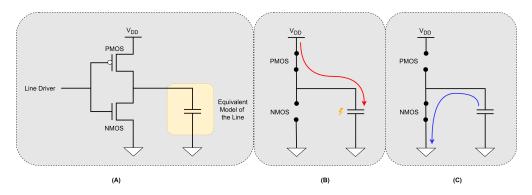

| 3.18 | Working principles of a single data bus line                                  | 36 |

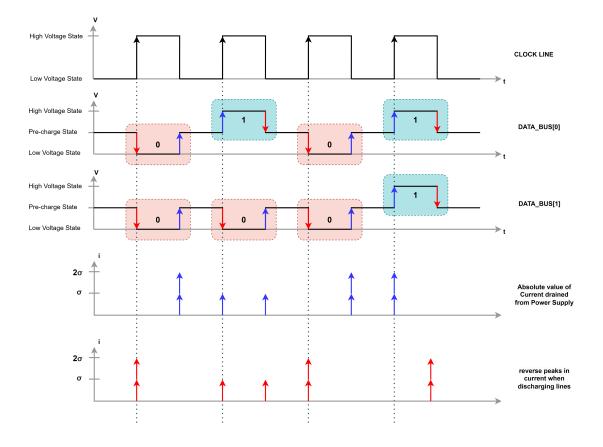

| 3.19 | Current peaks due to bit transfers on bus lines                               | 37 |

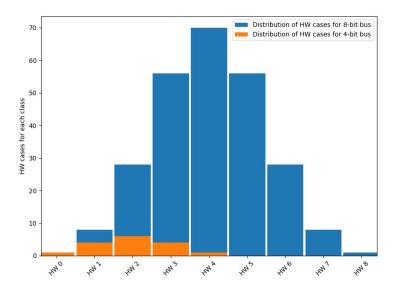

| 3.20 | Values distribution of Hamming Weight for 4-bit and 8-bit data buses          | 38 |

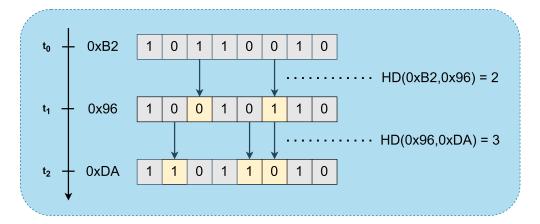

|      | Hamming Distance of a register at successive time instants                    | 38 |

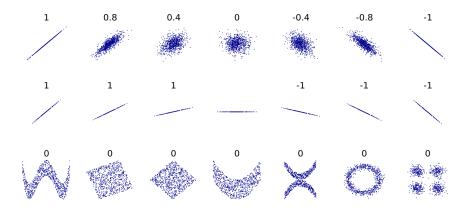

| 3.22 | Visual representation of correlation between two random variables             | 39 |

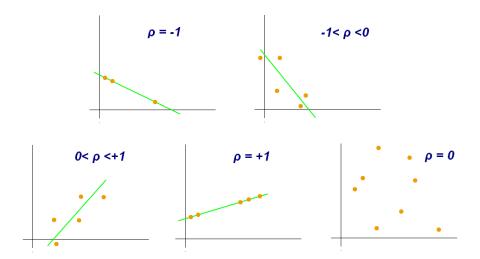

| 3.23 | Scatter diagram of Pearson's Correlation Coefficient [13]                     | 40 |

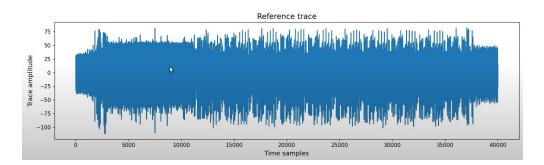

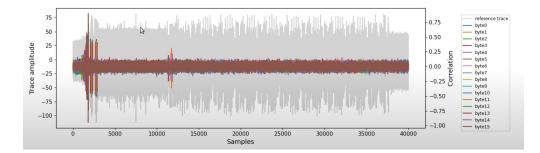

| 3.24 | Example of trace collected during attack on AES-128 [14]                      | 42 |

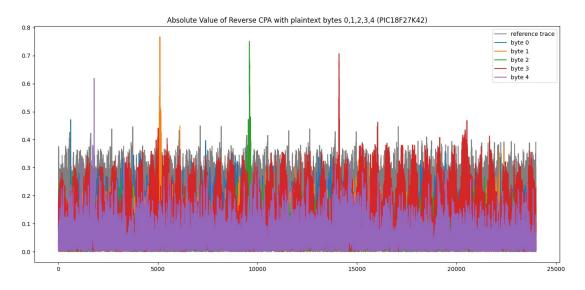

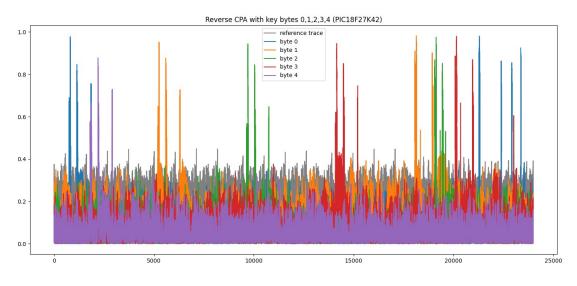

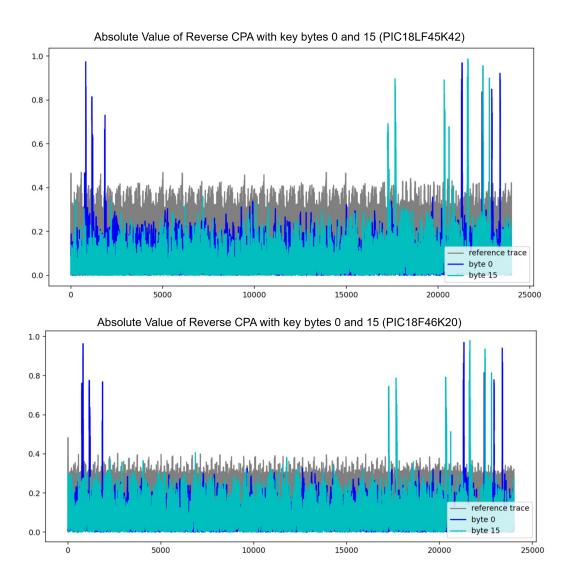

|      | Reverse CPA with respect to plaintext on collected AES-128 trace [14]         | 42 |

| 3.26 | Attack Points in AES [15]. $\ldots$                                           | 43 |

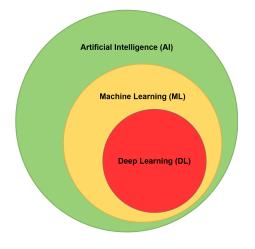

| 4.1  | AI, ML and DL.                                                                | 47 |

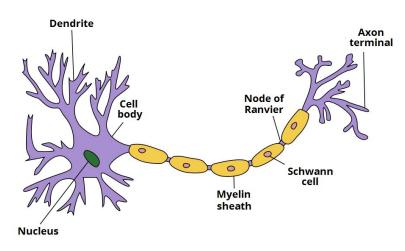

| 4.2  | Neuron in the human brain [16].                                               | 48 |

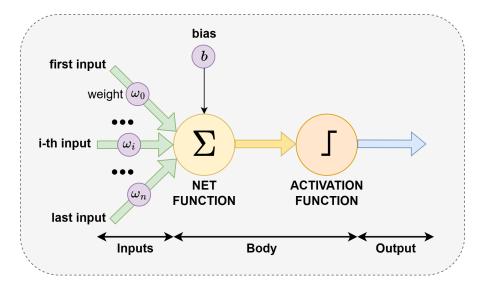

| 4.3  | Artificial neuron.                                                            | 49 |

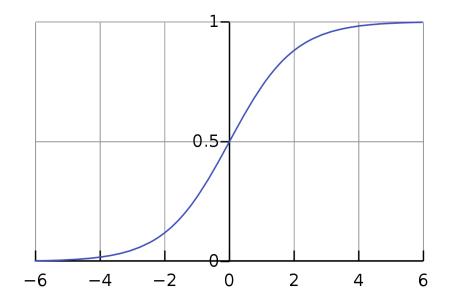

| 4.4  | The sigmoid activation function [17].                                         | 50 |

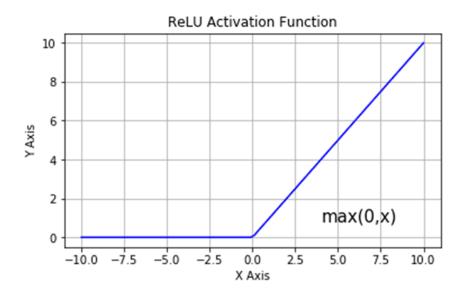

| 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | The ReLU activation function [18]                                                                                                                                                                                             | 50                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

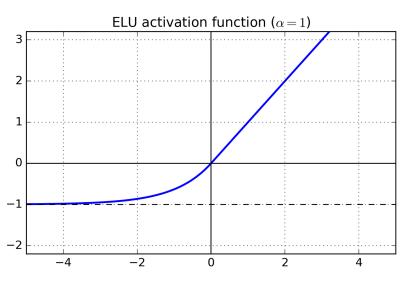

| 4.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | The ELU activation function [18]                                                                                                                                                                                              | 51                                                                                                                                    |

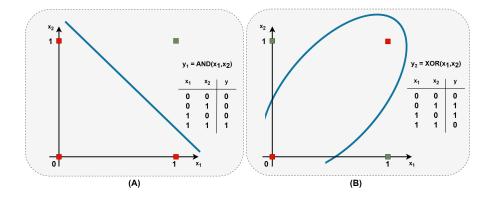

| 4.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AND (A) and XOR (B) truth tables [19].                                                                                                                                                                                        | 52                                                                                                                                    |

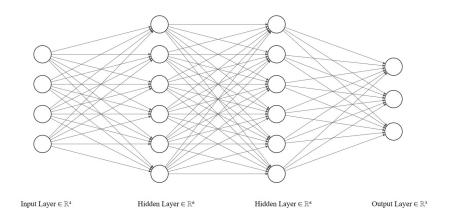

| 4.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Example of the MLP architecture.                                                                                                                                                                                              | 52                                                                                                                                    |

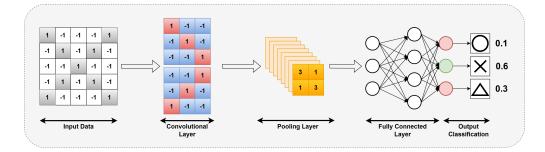

| 4.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Example of CNN architecture.                                                                                                                                                                                                  | 53                                                                                                                                    |

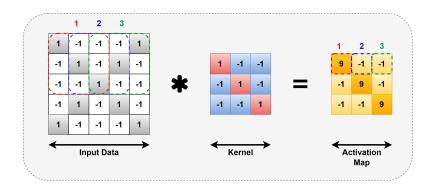

| 4.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Convolution operation in CNNs.                                                                                                                                                                                                | 54                                                                                                                                    |

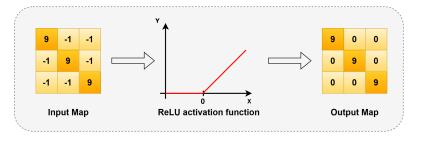

| 4.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Rectification in CNNs                                                                                                                                                                                                         | 54                                                                                                                                    |

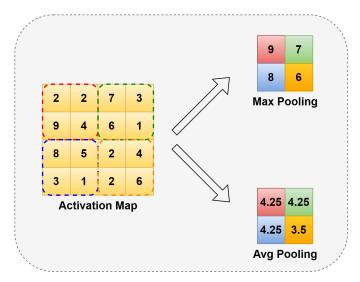

| 4.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Max and Avg pooling in CNNs                                                                                                                                                                                                   | 54                                                                                                                                    |

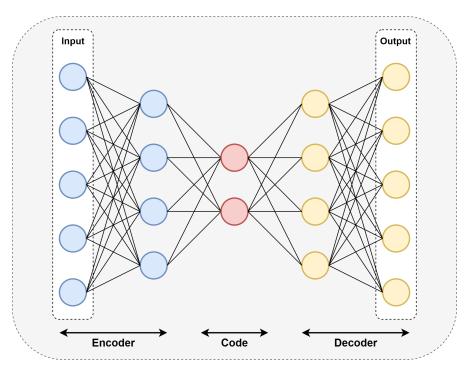

| 4.13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Example of Autoencoder network.                                                                                                                                                                                               | 55                                                                                                                                    |

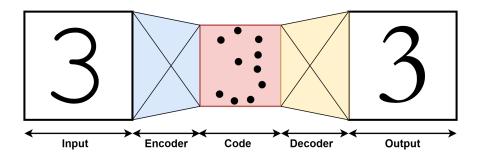

| 4.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Effect of Autoencoder on handwritten digit.                                                                                                                                                                                   | 56                                                                                                                                    |

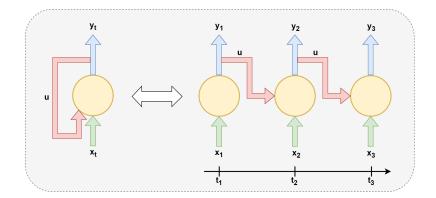

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Effect of feedback in RNNs.                                                                                                                                                                                                   | 57                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Scores in classification problem [20].                                                                                                                                                                                        | 58                                                                                                                                    |

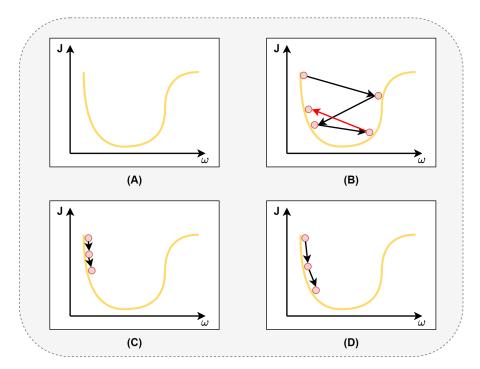

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The Gradient Descent.                                                                                                                                                                                                         | 59                                                                                                                                    |

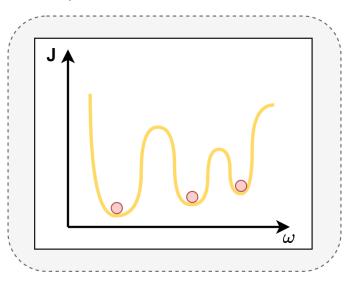

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Non-convex cost function.                                                                                                                                                                                                     | 60                                                                                                                                    |

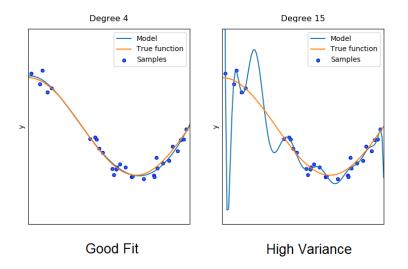

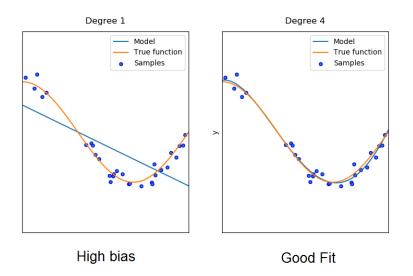

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Overfit [21]                                                                                                                                                                                                                  | 62                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Underfit [21]                                                                                                                                                                                                                 | 63                                                                                                                                    |

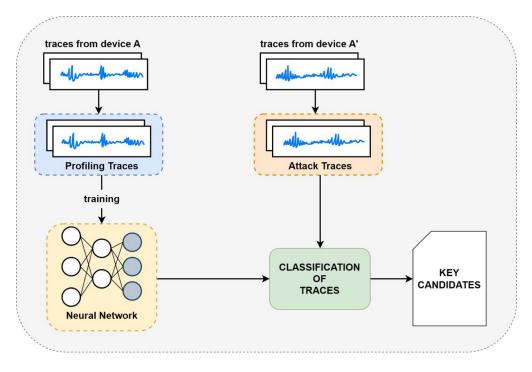

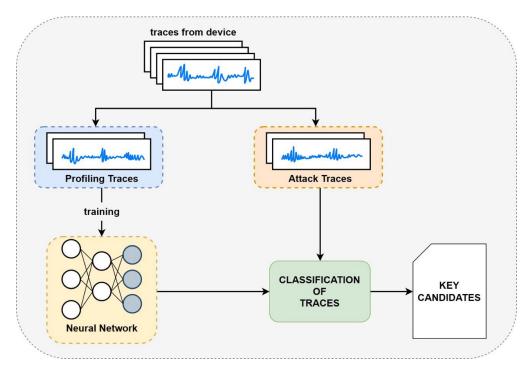

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Supervised Learning for DLSCA [22]                                                                                                                                                                                            | 65                                                                                                                                    |

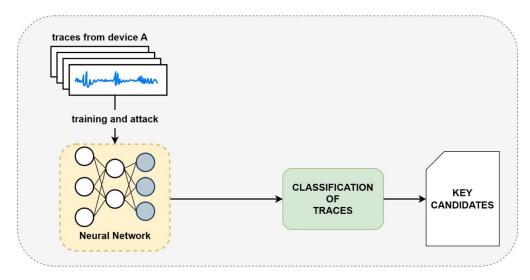

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Unsupervised Learning for DLSCA [22].                                                                                                                                                                                         | 65                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Confusion Matrix for multi-class classification problem.                                                                                                                                                                      | 67                                                                                                                                    |

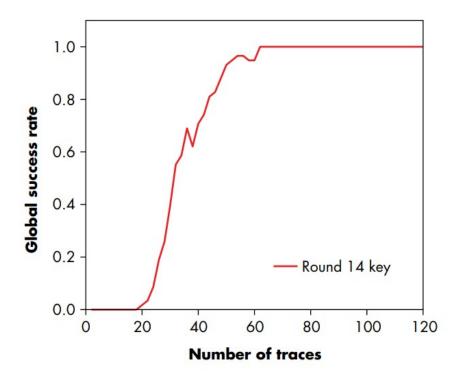

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Success Rate [12]                                                                                                                                                                                                             | 68                                                                                                                                    |

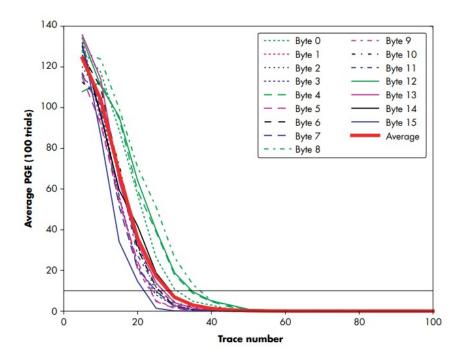

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Partial Guessing Entropy [12]                                                                                                                                                                                                 | 69                                                                                                                                    |

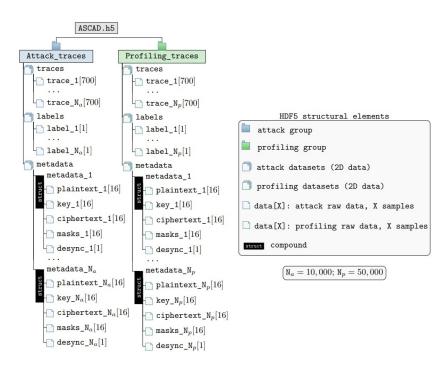

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ASCAD structure [23].                                                                                                                                                                                                         | 70                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Example script using the AISY framework [24].                                                                                                                                                                                 | 72                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Example script using the SCAred framework [25]                                                                                                                                                                                | 72                                                                                                                                    |

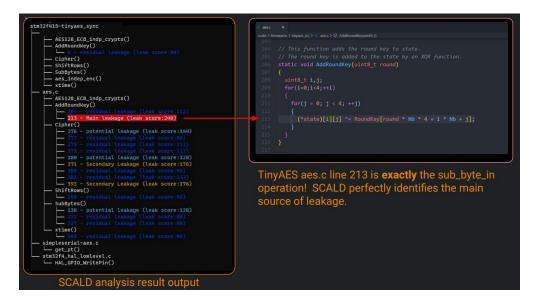

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Leakage detection on TinyAES with SCALD [26].                                                                                                                                                                                 | 73                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                               |                                                                                                                                       |

| 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Shortcut Setting for Supervised Learning [22].                                                                                                                                                                                | 74                                                                                                                                    |

| $5.1 \\ 5.2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Shortcut Setting for Supervised Learning [22]                                                                                                                                                                                 | 74<br>76                                                                                                                              |

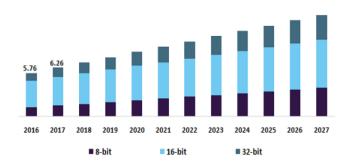

| 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Relevance of 8-bit microcontrollers in the North American market [27]                                                                                                                                                         | 76                                                                                                                                    |

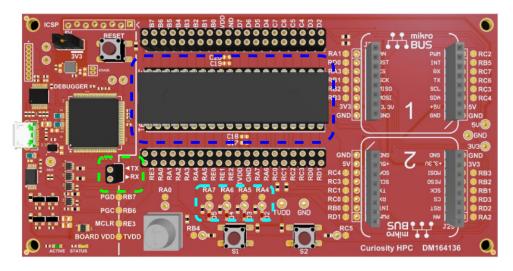

| $5.2 \\ 5.3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Relevance of 8-bit microcontrollers in the North American market [27]<br>Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                       | 76<br>76                                                                                                                              |

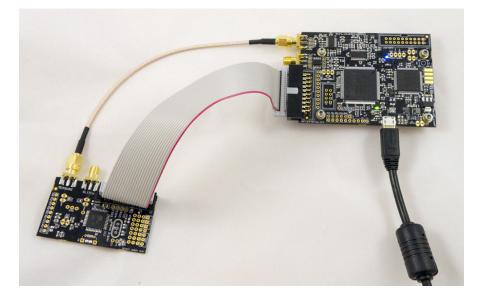

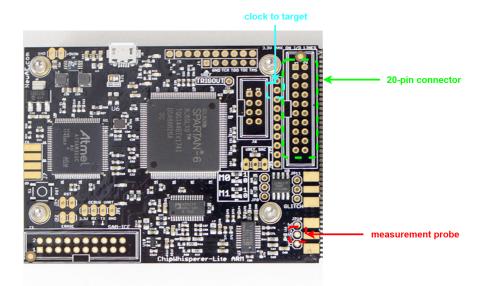

| $5.2 \\ 5.3 \\ 5.4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Relevance of 8-bit microcontrollers in the North American market [27]<br>Top view of the HPC Development Board by <i>Microchip</i> [28]<br>ChipWhisperer-Lite by <i>NewAE</i>                                                 | 76<br>76<br>77                                                                                                                        |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Relevance of 8-bit microcontrollers in the North American market [27]<br>Top view of the HPC Development Board by <i>Microchip</i> [28]<br>ChipWhisperer-Lite by <i>NewAE</i>                                                 | 76<br>76<br>77<br>78                                                                                                                  |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Relevance of 8-bit microcontrollers in the North American market [27].Top view of the HPC Development Board by Microchip [28].ChipWhisperer-Lite by NewAE.The Capture Board.Example of code including SimpleSerial functions. | 76<br>76<br>77<br>78<br>79                                                                                                            |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Relevance of 8-bit microcontrollers in the North American market [27]<br>Top view of the HPC Development Board by $Microchip$ [28]<br>ChipWhisperer-Lite by $NewAE$                                                           | 76<br>76<br>77<br>78<br>79<br>81                                                                                                      |

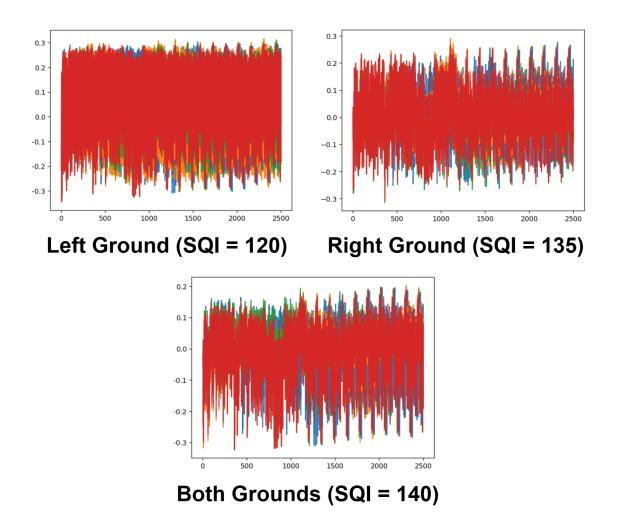

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>78<br>79<br>81<br>82                                                                                                |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>78<br>79<br>81<br>82<br>83                                                                                          |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Relevance of 8-bit microcontrollers in the North American market [27]<br>Top view of the HPC Development Board by <i>Microchip</i> [28]<br>ChipWhisperer-Lite by <i>NewAE</i>                                                 | 76<br>76<br>77<br>78<br>79<br>81<br>82<br>83<br>84                                                                                    |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>77<br>78<br>79<br>81<br>82<br>83<br>84<br>85                                                                                    |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11 \\ 5.12$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>78<br>79<br>81<br>82<br>83<br>84<br>85<br>85                                                                        |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11 \\ 5.12 \\ 5.13 $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>78<br>79<br>81<br>82<br>83<br>84<br>85<br>85<br>85                                                                  |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11 \\ 5.12 \\ 5.13 \\ 5.14 $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>78<br>79<br>81<br>82<br>83<br>84<br>85<br>85<br>85<br>86<br>87                                                      |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11 \\ 5.12 \\ 5.13 \\ 5.14 \\ 5.15 \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>78<br>79<br>81<br>82<br>83<br>84<br>85<br>85<br>85<br>85<br>86<br>87<br>88                                          |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11 \\ 5.12 \\ 5.13 \\ 5.14 \\ 5.15 \\ 5.16 \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>78<br>79<br>81<br>82<br>83<br>84<br>85<br>85<br>85<br>86<br>87<br>88<br>88                                          |

| $\begin{array}{c} 5.2\\ 5.3\\ 5.4\\ 5.5\\ 5.6\\ 5.7\\ 5.8\\ 5.9\\ 5.10\\ 5.11\\ 5.12\\ 5.13\\ 5.14\\ 5.15\\ 5.16\\ 5.17\end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>81<br>82<br>83<br>84<br>85<br>85<br>85<br>86<br>87<br>88<br>88<br>88<br>88<br>89                                    |

| $\begin{array}{c} 5.2\\ 5.3\\ 5.4\\ 5.5\\ 5.6\\ 5.7\\ 5.8\\ 5.9\\ 5.10\\ 5.11\\ 5.12\\ 5.13\\ 5.14\\ 5.15\\ 5.16\\ 5.17\\ 5.18\end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>81<br>82<br>83<br>84<br>85<br>85<br>85<br>85<br>86<br>87<br>88<br>88<br>88<br>89<br>89                              |

| $\begin{array}{c} 5.2\\ 5.3\\ 5.4\\ 5.5\\ 5.6\\ 5.7\\ 5.8\\ 5.9\\ 5.10\\ 5.11\\ 5.12\\ 5.13\\ 5.14\\ 5.15\\ 5.16\\ 5.17\\ 5.18\\ 5.19\end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28]                                                                                          | 76<br>76<br>77<br>88<br>83<br>84<br>85<br>85<br>86<br>87<br>88<br>88<br>88<br>89<br>90                                                |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.12<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.16<br>5.17<br>5.18<br>5.17<br>5.18<br>5.17<br>5.18<br>5.17<br>5.12<br>5.13<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.12<br>5.12<br>5.13<br>5.12<br>5.12<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.20 | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28] ChipWhisperer-Lite by <i>NewAE</i>                                                       | 76<br>76<br>77<br>88<br>81<br>82<br>83<br>84<br>85<br>85<br>86<br>87<br>88<br>88<br>88<br>89<br>90<br>91                              |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.12<br>5.12<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.16<br>5.17<br>5.18<br>5.16<br>5.17<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.12<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12                                                                                                                 | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28] ChipWhisperer-Lite by <i>NewAE</i>                                                       | $\begin{array}{c} 76\\ 76\\ 77\\ 78\\ 79\\ 81\\ 82\\ 83\\ 84\\ 85\\ 85\\ 85\\ 86\\ 87\\ 88\\ 88\\ 89\\ 89\\ 90\\ 91\\ 93 \end{array}$ |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.16<br>5.17<br>5.18<br>5.16<br>5.17<br>5.18<br>5.12<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.12<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.12<br>5.12<br>5.12<br>5.14<br>5.15<br>5.16<br>5.17<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.20<br>5.22                                                                                                                                                                                                                                         | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28] ChipWhisperer-Lite by <i>NewAE</i>                                                       | 76<br>76<br>77<br>81<br>82<br>83<br>84<br>85<br>85<br>86<br>87<br>88<br>88<br>88<br>89<br>90<br>91<br>93<br>93                        |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.16<br>5.17<br>5.18<br>5.17<br>5.18<br>5.19<br>5.12<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.12<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.12<br>5.22<br>5.23                                                                                                                                                                                                                                                                 | Relevance of 8-bit microcontrollers in the North American market [27] Top view of the HPC Development Board by <i>Microchip</i> [28] ChipWhisperer-Lite by <i>NewAE</i>                                                       | $\begin{array}{c} 76\\ 76\\ 77\\ 78\\ 79\\ 81\\ 82\\ 83\\ 84\\ 85\\ 85\\ 85\\ 86\\ 87\\ 88\\ 88\\ 89\\ 89\\ 90\\ 91\\ 93 \end{array}$ |

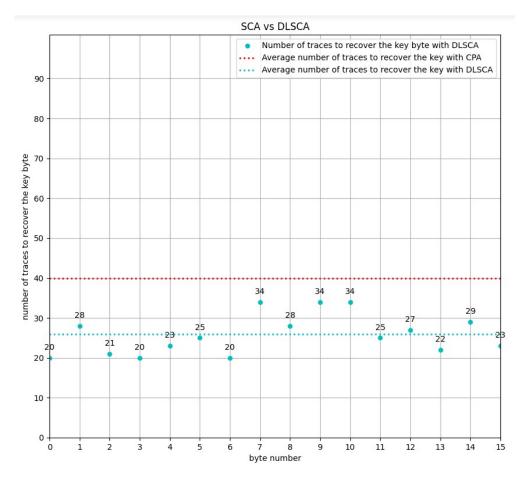

| 6.1 | SCA and DLSCA on PIC18F27K42                                            | 96  |

|-----|-------------------------------------------------------------------------|-----|

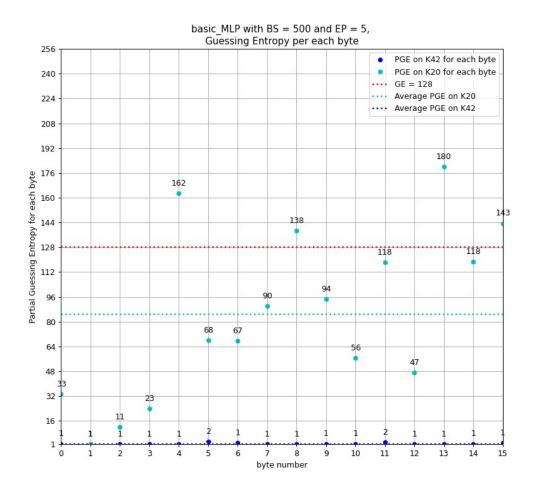

| 6.2 | <code>basic_MLP</code> with BS=500 and EP=5 on K42_K42 and K42_K20      | 98  |

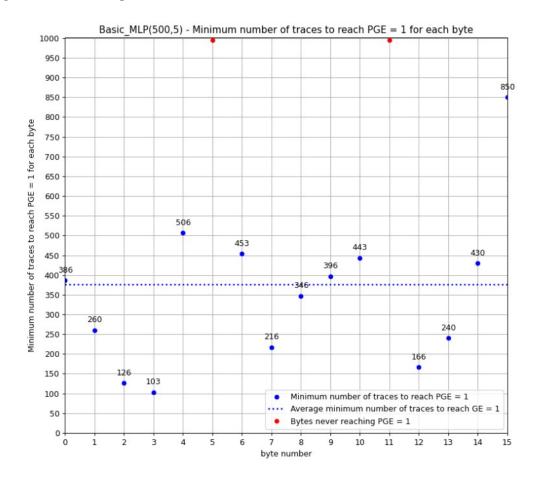

| 6.3 | Minimum number of traces to reach $PGE = 1$ with basic_MLP(500,5) on    |     |

|     | K42_K42                                                                 | 99  |

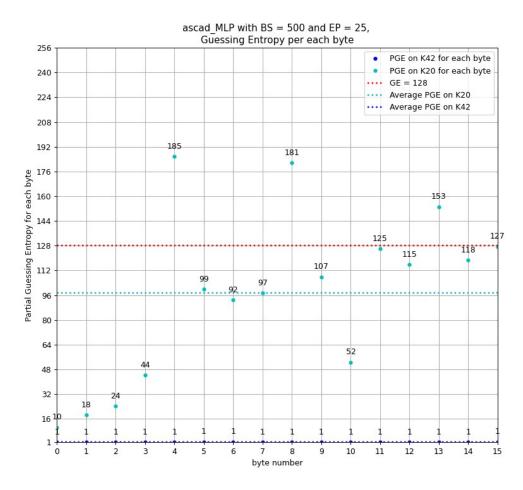

| 6.4 | ascad_MLP with BS=500 and EP=25 on K42_K42 and K42_K20 1                | 100 |

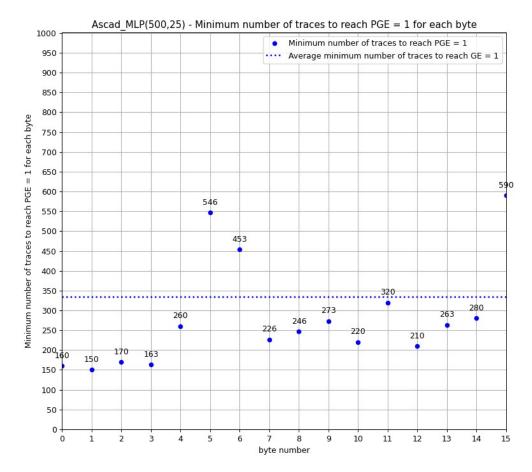

| 6.5 | Minimum number of traces to reach $PGE = 1$ with ascad_MLP(500,25)      |     |

|     | on K42_K421                                                             | 101 |

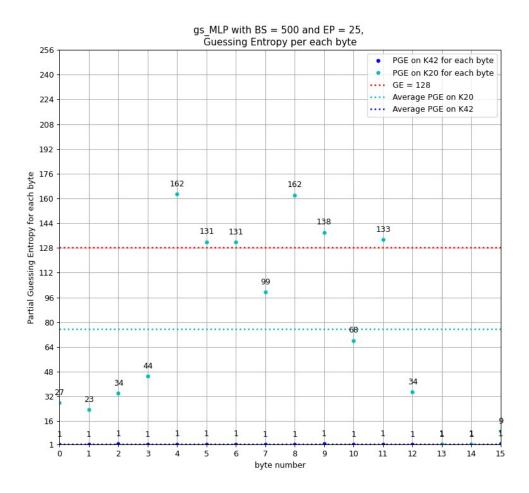

| 6.6 | gridsearch_MLP with BS=500 and EP=25 on K42_K42 and K42_K20 1           | 102 |

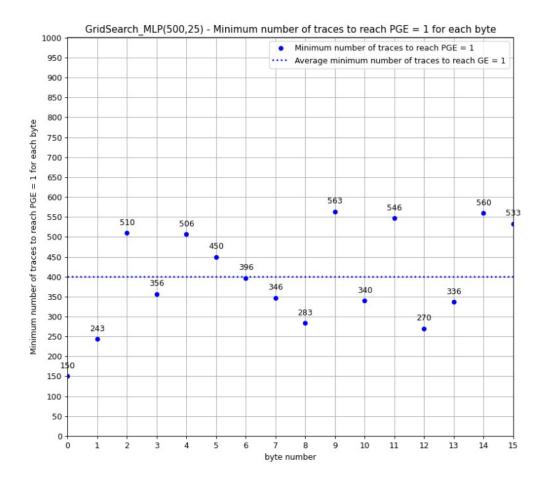

| 6.7 | Minimum number of traces to reach $PGE = 1$ with gridsearch_MLP(500,25) |     |

|     | on K42_K42                                                              | 103 |

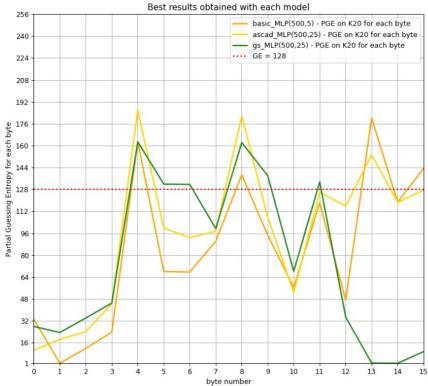

| 7.1 | PGE achieved by all the best configurations of MLPs                     | 104 |

# List of Tables

| 4.1 | Key used in ASCAD-F.                                                      | 70  |

|-----|---------------------------------------------------------------------------|-----|

| 5.1 | Key bytes recovered with CPA on $\tt PIC18F27K42$ in dependence to number |     |

|     | of traces                                                                 | 92  |

| 5.2 | Key used in both datasets                                                 | 92  |

| 5.3 | Intervals used for the Grid Search.                                       | 95  |

| 6.1 | Number of Epochs and Batch Size investigated in the work                  | 97  |

| 6.2 | Average PGE on 16 bytes for basic_MLP on K42_K20                          | 98  |

| 6.3 | Average PGE on 16 bytes for ascad_MLP on K42_K20                          | 100 |

| 6.4 | Average PGE on 16 bytes for gridsearch_MLP on K42_K20                     | 102 |

| 7.1 | Average PGE on 16 bytes for basic_MLP, ascad_MLP and gs_MLP on K42_K20.   | 105 |

# Contents

| 1        | Intr | oducti  | on                                                    | 10        |

|----------|------|---------|-------------------------------------------------------|-----------|

| <b>2</b> | Adv  | vanced  | Encryption Standard (AES)                             | 12        |

|          | 2.1  | Introd  | uction to AES                                         | 12        |

|          | 2.2  | The A   | lgorithm                                              | 13        |

|          |      | 2.2.1   | Encryption Process                                    | 13        |

|          |      | 2.2.2   | Decryption Process                                    | 16        |

|          |      | 2.2.3   | Key Schedule Algorithm                                | 16        |

|          | 2.3  | Crypta  | analysis of the AES Algorithm                         | 17        |

|          | 2.4  |         | nd Hardware Vulnerabilities                           |           |

|          |      | 2.4.1   | Hardware and Software Implementations                 | 18        |

| 3        | Side | e-Chan  | mel Analysis (SCA)                                    | <b>21</b> |

|          | 3.1  |         | uction to SCA                                         | 21        |

|          | 3.2  |         | omy of Side-Channel Analysis Attacks                  |           |

|          |      | 3.2.1   | Leakage Sources                                       |           |

|          |      | 3.2.2   | Access Level                                          |           |

|          |      | 3.2.3   | Attack Modalities                                     |           |

|          |      | 3.2.4   | Common Targets                                        |           |

|          | 3.3  | Power   | Analysis and related Techniques                       | 28        |

|          |      | 3.3.1   | Simple Power Analysis (SPA)                           |           |

|          |      | 3.3.2   | Differential Power Analysis (DPA)                     |           |

|          |      | 3.3.3   | Correlation Power Analysis (CPA)                      |           |

|          |      | 3.3.4   | Attack Points in AES                                  |           |

|          | 3.4  | Count   | ermeasures                                            |           |

| 4        | Dee  | en Lear | rning Side-Channel Analysis (DLSCA): State of the Art | 46        |

| -        | 4.1  | -       | uction to Deep Learning Side-Channel Analysis         |           |

|          | 4.2  |         | Principles of Deep Learning                           |           |

|          |      | 4.2.1   | Artificial Neurons                                    |           |

|          |      | 4.2.2   | Artificial Neural Networks                            |           |

|          |      | 4.2.3   | The Learning Process                                  |           |

|          |      | 4.2.4   | Adjusting the Networks: Hyperparameters Tuning        |           |

|          | 4.3  |         | Learning applied to Side-Channel Analysis             |           |

|          | 1.0  | 4.3.1   | Power Models                                          |           |

|          |      | 4.3.2   | Metrics                                               |           |

|          |      | 4.3.3   | Datasets                                              |           |

|          |      | 4.3.4   | Frameworks                                            |           |

| <b>5</b> | Development          |                                                                                                               |    |  |

|----------|----------------------|---------------------------------------------------------------------------------------------------------------|----|--|

|          | 5.1                  | Motivation and Objectives                                                                                     |    |  |

|          | 5.2                  | Experimental Equipment                                                                                        |    |  |

|          |                      | 5.2.1 8-bit MCUs by $Microchip$                                                                               | 76 |  |

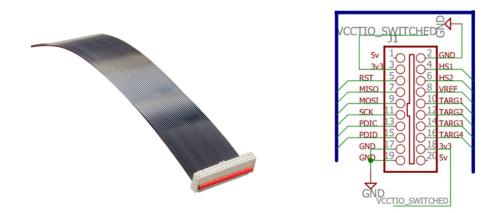

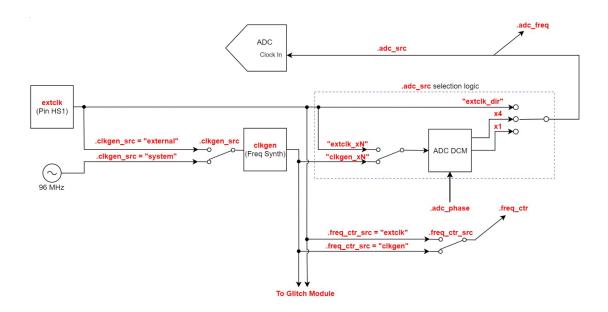

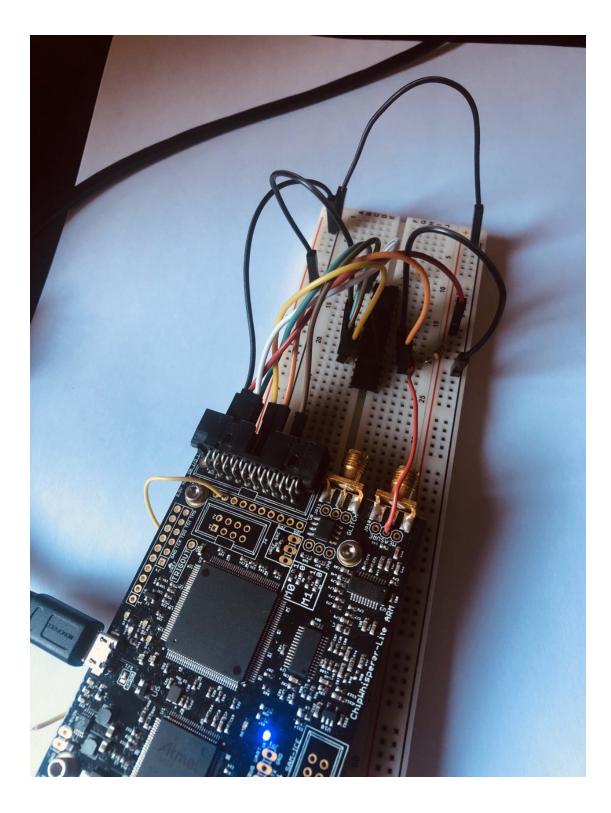

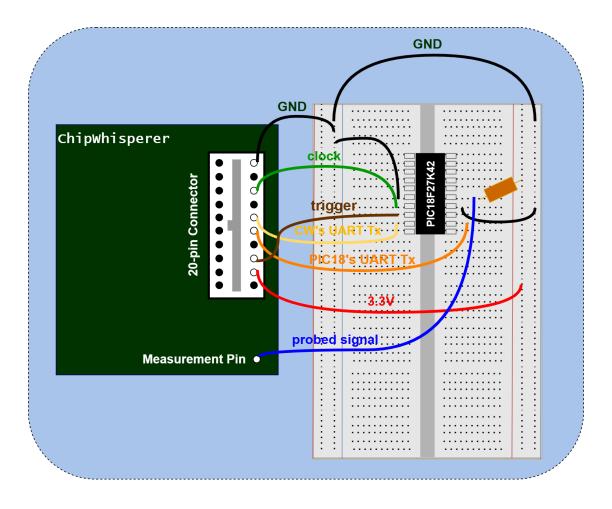

|          |                      | 5.2.2 The $ChipWhisperer^{TM}$ Toolchain                                                                      | 77 |  |

|          | 5.3                  | Configuration of the Hardware Setup                                                                           |    |  |

|          |                      | 5.3.1 Setting up the Target Board                                                                             | 80 |  |

|          |                      | 5.3.2 Setting up the Capture Board                                                                            | 81 |  |