## POLITECNICO DI TORINO

## Corso di Laurea Magistrale in Computer Engineering

Tesi di Laurea Magistrale

## Development and evaluation of Synthesis and Optimization strategies for digital integrated circuits

Realizzata in collaborazione di: STMICROELECTRONICS srl

#### Relatori

#### Candidato

Dario Licastro

Dr. Prof. Enrico Macii *Firma* .....

Dr. Prof. Andrea Calimera *Firma* .....

### Supervisore Aziendale

Dr. Michelangelo Grosso *Firma* .....

November 2022

## Abstract

Synthesis and optimization strategies for digital integrated circuits are topics of great importance. Interest in this area has increased in recent years because of its utility in the various fields characterized by the current technological revolution. Computer-aided design (CAD) techniques have provided the methodology for efficient and successful design of large-scale high-performance circuits for a wide range of applications, from automotive to biomedical signal processing, and so on. The exponential increase in design complexity has necessitated the development of automated techniques to achieve adequate results in a shorter time. For this reason, smarter strategies need to be developed to reduce human interaction in the design process. Human interaction is time-consuming and error-prone. Strategies must overcome several challenges, from area timing, energy consumption, and testability. Testability is important to reduce testing time, which is the most expensive part of the design process. This thesis focuses on the development and evaluation of several synthesis and optimization strategies for digital integrated circuits, comparing the effects of different choices in the flow on the main design metrics, i.e., power, area and timing. The goal is to develop a flow capable of minimizing metrics with the least complexity and time. In addition, the developed strategies were verified and evaluated, showing how the key parameters affect the outcome and how the flow can be adjusted for better results. The strategies were applied in a mixed-signal ASIC design to evaluate the result. The project started with a basic synthesis flow that is stable and scalable, and starting from this flow, an exploration of possible further strategies is presented. The main areas in which these flow variants are developed are clock gating, the introduction of different cell libraries and the different sequences of optimizations in the flow. Clock gating was explored with the introduction of cloning techniques, or the variation of relevant parameters such as maximum fanout, minimum bandwidth and maximum number of stages. Various types of cell libraries, low leakage and low scale were used to investigate designs with less prohibitive power supply models or designs with fewer timing issues. Strategies have been developed for managing the

synthesis flow, varying parameters during synthesis and thus giving the EDA tool different starting points during synthesis. The main metrics taken into account are area, power consumption and timing. Each strategy developed is consequential to the information gained from the previous strategies. The aim is to create stable alternative strategies by analysing the results obtained and the various metrics.

# Contents

| 1 | Intro | oduction                                  | 10 |

|---|-------|-------------------------------------------|----|

|   | 1.1   | Motivation                                | 10 |

|   | 1.2   | Purpose and Objectives                    | 11 |

|   | 1.3   | Thesis Structure                          | 11 |

| 2 | Bac   | kground                                   | 13 |

|   | 2.1   | Microelectronic Digital Design Flow       | 13 |

|   | 2.2   | Metrics                                   | 19 |

|   |       | 2.2.1 Pareto curve                        | 19 |

|   | 2.3   | Abstract models                           | 20 |

|   | 2.4   | Architectural Level Synthesis             | 22 |

|   |       |                                           | 22 |

|   |       |                                           | 24 |

|   | 2.5   | Logic Level Synthesis                     | 25 |

|   | 2.6   | Verification Techniques                   | 26 |

|   |       |                                           | 26 |

|   |       | 2.6.2 Formal verification                 | 28 |

|   | 2.7   | Power Modeling                            | 28 |

|   |       |                                           | 31 |

|   |       | 2.7.2 Clock Gating                        | 31 |

|   | 2.8   | Timing Analysis                           | 34 |

|   |       | 2.8.1 Critical Paths                      | 35 |

|   | 2.9   | Practical example of a RTL synthesis flow | 36 |

|   |       | 2.9.1 Loading Design and Technology Data  | 37 |

|   |       | 2.9.2 Constraints application             | 39 |

|   |       |                                           | 41 |

|   |       |                                           | 42 |

|   |       |                                           | 43 |

| 3 | App   | roach                                     | 44 |

|   | 3.1   |                                           | 44 |

|   |       |                                           | 45 |

|   | 3.2   | v i                                       | 50 |

|   | 3.3 | Simulation of Digital Systems                                          | 53 |

|---|-----|------------------------------------------------------------------------|----|

|   |     | 3.3.1 VCD/FSDB file                                                    | 53 |

|   | 3.4 | Validation and Evaluation of the Synthesis and Optimization strategies | 54 |

|   |     | 3.4.1 Evaluation metrics                                               | 54 |

|   |     | 3.4.2 Formal verification                                              | 55 |

|   |     |                                                                        |    |

| 4 | -   |                                                                        | 57 |

|   | 4.1 |                                                                        | 57 |

|   |     |                                                                        | 57 |

|   |     | 5 1                                                                    | 58 |

|   |     |                                                                        | 58 |

|   | 4.0 |                                                                        | 59 |

|   | 4.2 |                                                                        | 60 |

|   |     | 0 2                                                                    | 60 |

|   |     | 0 2                                                                    | 60 |

|   | 4.3 | Proposed Synthesis and Optimization strategies                         | 61 |

| 5 | Res | ults                                                                   | 72 |

|   | 5.1 | Clock Gating                                                           | 73 |

|   |     | ÷                                                                      | 73 |

|   |     |                                                                        | 75 |

|   |     |                                                                        | 76 |

|   |     |                                                                        | 78 |

|   |     |                                                                        | 79 |

|   |     |                                                                        | 82 |

|   |     | -                                                                      | 84 |

|   | 5.2 | ° °                                                                    | 86 |

|   |     |                                                                        | 86 |

|   |     | Č                                                                      | 88 |

|   | 5.3 | 0 0 0                                                                  | 90 |

|   |     | *                                                                      | 91 |

|   |     |                                                                        | 92 |

| - | _   |                                                                        |    |

| 6 |     |                                                                        | 95 |

|   | 6.1 | 8 8                                                                    | 95 |

|   | 6.2 |                                                                        | 96 |

|   | 6.3 | $\overline{\mathcal{G}}$                                               | 97 |

|   | 6.4 | Future works                                                           | 97 |

# **List of Figures**

| 2.1  | MOSFET from STMicroelectronics.                                         | 14 |  |  |

|------|-------------------------------------------------------------------------|----|--|--|

| 2.2  | Microelectronic digital design Flow.                                    | 15 |  |  |

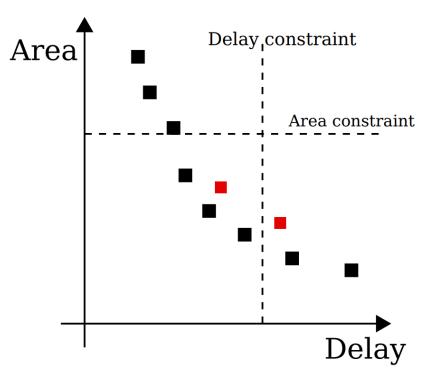

| 2.3  | In black, Pareto point for a Delay-Area trade-off. In red, not optimal  |    |  |  |

|      | point                                                                   | 20 |  |  |

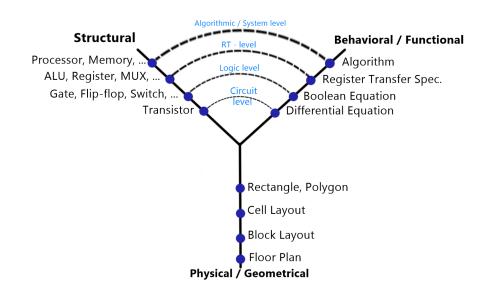

| 2.4  | Gajski–Kuhn chart showing the many perspectives on VLSI hardware        |    |  |  |

|      | design                                                                  | 21 |  |  |

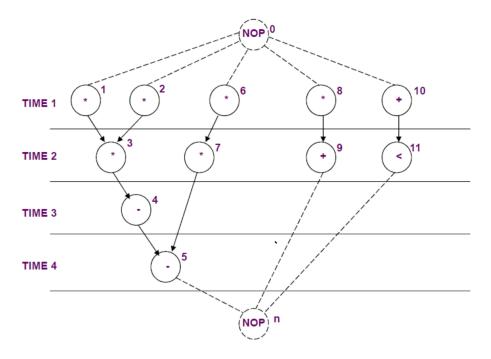

| 2.5  | ASAP scheduling $[16]$                                                  | 23 |  |  |

| 2.6  | ALAP scheduling                                                         | 24 |  |  |

| 2.7  | A Testbench entity                                                      | 27 |  |  |

| 2.8  | Switching Activity, representation of 4 switch on 8 clocks              | 29 |  |  |

| 2.9  | I flow on transition                                                    | 30 |  |  |

| 2.10 | Peak current during output transition.                                  | 30 |  |  |

| 2.11 | Clock Gating example with ENABLE signal                                 | 31 |  |  |

| 2.12 | Clock Gating example with Control Unit that produce the ENABLE          |    |  |  |

|      | signal [1]. The Control Unit is composed by a counter, an input "inc"   |    |  |  |

|      | and a logic memory containing the desired value                         | 32 |  |  |

|      | AND gate-based clock gating[1]                                          | 32 |  |  |

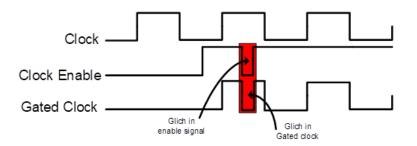

| 2.14 | Glitch AND gate-based clock gating[1]                                   | 32 |  |  |

|      | Integrated Gated Clock (ICG) cells[1]                                   | 33 |  |  |

|      | Multi-level propagation of Enable clock gating signal[1]                | 33 |  |  |

| 2.17 | Figure a : Clock Gating without cloning, Figure b : Clock Gating        |    |  |  |

|      | with cloning and fanout distribution[3]                                 | 34 |  |  |

|      | Critical path composed by nodes A,D,G,O is a false path                 | 35 |  |  |

|      | Synthesis from a concept to an object.                                  | 36 |  |  |

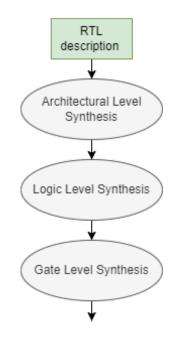

|      | RTL synthesis flow.                                                     | 37 |  |  |

|      | Example of timing path                                                  | 39 |  |  |

|      | Timing constraints on input and output port                             | 40 |  |  |

|      | Default synthesis step                                                  | 41 |  |  |

| 2.24 | Two-pass synthesis flow.                                                | 43 |  |  |

| 3.1  | Example of an ASIC RTL schematic with datapath and control unit[6].     | 45 |  |  |

| 3.2  | Phases of basic design flow and application location of new strategies. | 47 |  |  |

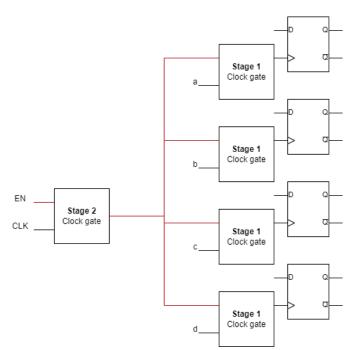

| 3.3  | Multistage Clock Gating.                                                | 49 |  |  |

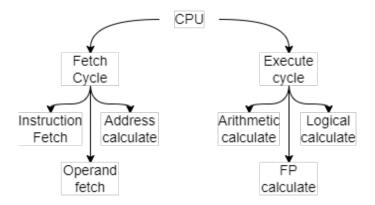

| 3.4  | Example of Behavioral Hierarchy of a CPU.                               | 51 |  |  |

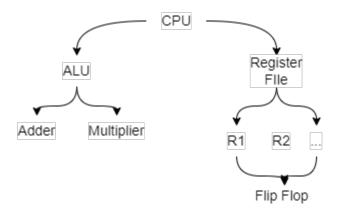

| 3.5 | Example of Structural Hierarchy of a CPU                 | 52 |

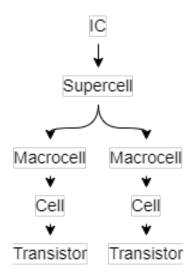

|-----|----------------------------------------------------------|----|

| 3.6 | Example of Physical Hierarchy of an Integrated Circuit   | 52 |

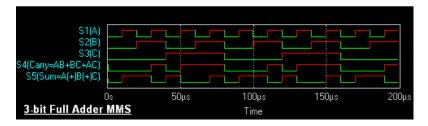

| 3.7 | xcelium ouput waveform for a 3 bits RCA                  | 53 |

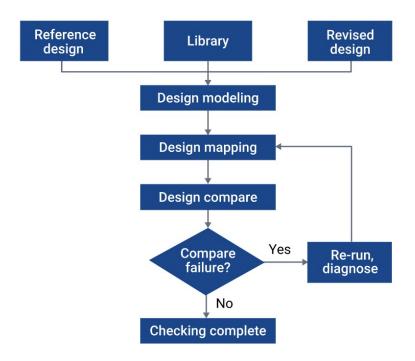

| 3.8 | Logic equivalence check (LEC) process [15]               | 56 |

|     |                                                          |    |

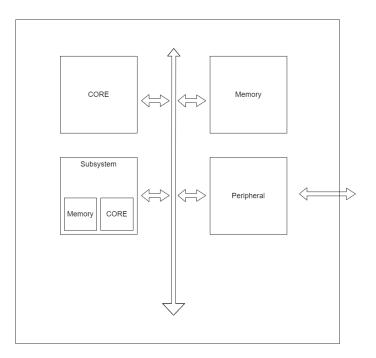

| 4.1 | A sketch about the top digital module of the design      | 62 |

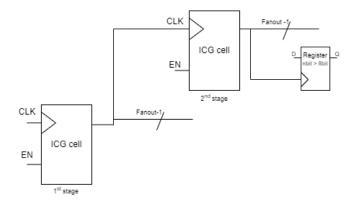

| 4.2 | The clock gating structure is applied to the basic flow. | 63 |

# List of Tables

| 1.1  | Integration density of Integrated Circuits (ICs)               |

|------|----------------------------------------------------------------|

| 5.1  | Setup violation for no clock-gating flow                       |

| 5.2  | Hold violation for no clock-gating flow                        |

| 5.3  | Clock gating report for no clock-gating flow                   |

| 5.4  | Power analysis for no clock-gating flow                        |

| 5.5  | Area for no clock-gating flow                                  |

| 5.6  | Setup violation for no clock-gating cloning flow               |

| 5.7  | Hold violation for no clock-gating cloning flow                |

| 5.8  | Clock gating report for no clock-gating cloning flow           |

| 5.9  | Power analysis for no clock-gating cloning flow                |

| 5.10 | Area for no clock-gating cloning flow                          |

| 5.11 | Setup violation for high Fan-out strategies                    |

| 5.12 | Hold violation for high Fan-out strategies                     |

| 5.13 | Clock gating report for high Fan-out strategies                |

| 5.14 | Power analysis for high Fan-out strategies                     |

| 5.15 | Area for high Fan-out strategies                               |

| 5.16 | Setup violation for low Fan-out strategies                     |

| 5.17 | Hold violation for low Fan-out strategies                      |

| 5.18 | Clock gating report for low Fan-out strategies                 |

|      | Power analysis for low Fan-out strategies                      |

| 5.20 | Area for low Fan-out strategies                                |

|      | Setup violation for more stages strategies                     |

| 5.22 | Hold violation for more stages strategies                      |

| 5.23 | Clock gating report for more stages strategies                 |

| 5.24 | Power analysis for more stages strategies                      |

| 5.25 | Area for more stages strategies                                |

| 5.26 | Setup violation for different Bitwidth exploration             |

| 5.27 | Hold violation for different Bitwidth exploration              |

| 5.28 | Clock gating report for different Bitwidth exploration         |

| 5.29 | Power analysis for different Bitwidth exploration              |

| 5.30 | Area for different Bitwidth exploration                        |

| 5.31 | Setup violation for clock gating without sharing strategies 85 |

| 5.32 | Hold violation for clock gating without sharing strategies     |

| 5.33 | Clock gating report for clock gating without sharing strategies           | 85 |

|------|---------------------------------------------------------------------------|----|

| 5.34 | Area for clock gating without sharing strategies                          | 85 |

| 5.35 | Setup violation for synthesis with LVT cells                              | 87 |

| 5.36 | Hold violation for synthesis with LVT cells                               | 87 |

| 5.37 | Clock gating report for synthesis with LVT cells                          | 87 |

| 5.38 | Power analysis for synthesis with LVT cells.                              | 87 |

| 5.39 | Number of cell for each cell library for synthesis with LVT cells         | 88 |

| 5.40 | Area for synthesis with LVT cells                                         | 88 |

| 5.41 | Setup violation for synthesis with LVT cells and low fonout clock         |    |

|      | gating structure.                                                         | 88 |

| 5.42 | Hold violation for synthesis with LVT cells and low fonout clock gat-     |    |

|      | ing structure.                                                            | 89 |

| 5.43 | Clock gating report for synthesis with LVT cells and low fonout clock     |    |

|      | gating structure.                                                         | 89 |

| 5.44 | Power analysis for synthesis with LVT cells and low fonout clock          |    |

|      | gating structure.                                                         | 89 |

| 5.45 | Number of cell for each cell library for synthesis with LVT cells         | 90 |

|      | Area for synthesis with LVT cells and low fonout clock gating structure.  | 90 |

| 5.47 | Setup violation for synthesis with different clock gating structure after |    |

|      | first compile.                                                            | 91 |

| 5.48 | Hold violation for synthesis with different clock gating structure after  |    |

|      | first compile.                                                            | 91 |

| 5.49 | Clock gating report for synthesis with different clock gating structure   |    |

|      | after first compile.                                                      | 91 |

| 5.50 | Power analysis for synthesis with different clock gating structure after  |    |

|      | first compile.                                                            | 92 |

| 5.51 | Area for synthesis with different clock gating structure after first com- |    |

|      | pile                                                                      | 92 |

| 5.52 | Setup violation for synthesis with introduction of LVD cells after first  |    |

|      | compile                                                                   | 92 |

| 5.53 | Hold violation for synthesis with introduction of LVD cells after first   |    |

|      | compile                                                                   | 93 |

| 5.54 | Clock gating report for synthesis with introduction of LVD cells after    |    |

|      | first compile.                                                            | 93 |

| 5.55 | Power analysis for synthesis with introduction of LVD cells after first   |    |

|      | compile                                                                   | 93 |

| 5.56 | Area for synthesis with introduction of LVD cells after first compile     | 94 |

|      |                                                                           |    |

## **1** Introduction

In recent years, digital microelectronics has been the driving force behind the development of embedded systems. The ever-increasing level of integration of electronic devices has led to an increase in the complexity of systems[4]. The first generation of chips was called Small-Scale Integration (SSI) (Table 1.1) and enabled the development of logic gates on a single chip through the use of diodes, transistors, resistors, and capacitors. This was followed a few years later by the development of Very Large-Scale Integration (VLSI) (Table 1.1) chips that could contain millions of logic gates in a single chip. The increasing complexity of systems has led to an exponential increase in development time. This resulted in the importance of electronic design automation (EDA) tools, which made it possible to automate and simplify development processes. Synthesis and optimization are two processes in the development of embedded systems. Synthesis deals with compiling an abstract model into a logical model that contains information about the circuit, such as area, time, and power consumption. Optimization is the process of refining the logical model into a more efficient one.

| Density of integration               | Gates per IC         |

|--------------------------------------|----------------------|

| Small-Scale Integration (SSI)        | < 10                 |

| Medium-Scale Integration (MSI)       | 10 to 100            |

| Large-Scale Integration (LSI)        | 100 to 10,000        |

| Very Large-Scale Integration (VLSI)  | 10,000 to 100,000    |

| Ultra Large-Scale Integration (ULSI) | 100,000 to 1,000,000 |

| Giga-Scale Integration (GSI)         | > 1,000,000          |

Table 1.1: Integration density of Integrated Circuits (ICs).

### 1.1 Motivation

The introduction of new technologies in the semiconductor market and the increasing complexity of chips lead to the need to research and analyse the best development strategies. The process of synthesis and optimization of integrated systems is a complex and highly customisable process.

Different synthesis strategies and the use of innovative techniques lead to variations in the quality of the final result. The strategy used must be able to minimise metrics such as area and power consumption while respecting the limits of metrics such as timing. The theoretical approach suggests several synthesis strategies that can be applied in EDA. These techniques need to be integrated into strategies that are most suitable for specific technologies and different design structures.

An analysis of the different strategies will allow the exploration and development of specific strategies for the synthesis of specific integrated circuits.

## 1.2 Purpose and Objectives

The first objective of this work is to develop a synthesis and optimization flow with good quality results, analyzing how the different strategies affect the metrics. Therefore, the first part of the project was spent analyzing the EDA tools used in RTL synthesis and studying the different possible customizations. Sequentially, a given basic synthesis flow is evaluated and used as a starting point. The evaluation and verification phases introduce some complexity that needs to be addressed. A key part is the development of a correct evaluation and verification methodology. The second objective of this work is to classify how different strategies affect the synthesis of the digital portion of a mixed-signal integrated circuit. To this end, a number of synthesis flows have been developed and evaluated. The two objectives are interrelated and should be developed in parallel. The classification of strategies helps the designer to achieve good quality of results.

#### **Problem formulation**

- What are the available synthesis and optimisation strategies?

- How do the metrics vary as the synthesis strategies change?

- What is the correct methodology for evaluating metrics?

- What are the methods for verifying the resulting netlist?

- Which combination of strategies produces the overall best results considering the design metrics?

## **1.3 Thesis Structure**

The thesis will be structured in 6 chapters as follows:

• Chapter 2 presents an introduction to the concepts of Microelectronic design flow, the general use case of this study, and an overview of the state-of-the-art of synthesis and optimization strategies. It introduces basic knowledge about how to simulate an RTL netlist.

- Chapter 3 will focus on the technical description of RTL to logic synthesis flow, with an overview of the methodologies to handle with hierarchical design. Chapter 3 describes the approach proposed to evaluate and verify the netlist.

- Chapter 4 will describe the used software tools for the different parts of the implementation and the used libraries for the synthesis. Chapter 4 describe the proposed synthesis and optimization strategies implemented functionalities.

- Chapter 5 will describe the mixed-signal design under development and report the different results of the various Synthesis and Optimization strategies on the selected case study.

- Chapter 6 present an evaluation of the different strategies considering the main metrics and the execution time and draws some conclusions.

## 2 Background

This chapter introduces the necessary theoretical information to fully understand the main solution proposed in this work. The description of the microelectronic design flow is intended to situate this work within the overall development process. The different synhtesis strategies used in this thesis were evaluated using different metrics. This is to compare the different results and focus on adaptation. The measurement and classification methods are described in the metrics section. The synthesis thread starts with the definition of the abstract models and the synthesis connection process to reach each model. The state of art of power modeling and timing analysis is briefly discussed with the main concept of verification. Simulation and formal verification are both important to correctly analyzing the design structure. The reader may fully comprehend the objectives and decisions made to achieve the thesis goals using these principles.

## 2.1 Microelectronic Digital Design Flow

Over the last decades, the electronics industry has grown at a frenetic pace, owing to fast advancements in integration technologies and large-scale system design. The number of transistors per chip has increased enormously and, with it, the integration scale. The first MOSFET was invented in 1959 (an example by STMicroelectronics is shown in figure 2.1). Very large-scale integration (VLSI) was introduced in 1978 and is the paradigm changer in the Microelectronic ecosystem.

Microelectronic design flow (figure 2.2) is now a well-established procedure in silicon chip design. To ensure a successful design, is important to follow proven methodologies.

Figure 2.1: MOSFET from STMicroelectronics.

Microelectronic digital design incorporates two primary stages:

- Front-End Design includes the specification of digital design using a hardware description language, as Verilog, System Verilog, and VHDL. Additionally, this step includes design verification through simulation and other types of verification. It also includes architectural level synthesis. (2.4).

- Back-End Design concerns floorplanning, place and route, and verification of the physical design.

Figure 2.2: Microelectronic digital design Flow.

#### **Design specification**

Requirement definition is the starting point of each design flow. This step is not formal. Consequently, a step to formalize the design is needed. The formal language used in microelectronics is called Hardware Description Language (HDL). HDLs, such as VHDL and Verilog, are powerful computer languages for describing electronic circuit topology and function.

#### **RTL** design

In the logic design stage (HDL design in figure 2.2), a model is drawn using HDL. The function of the model is to be verified using a test bench to ensure the correctness of the design with respect to requirements.

The following lines provide an example of the RTL description of a generic multiplexer in VHDL:

library IEEE;

```

use IEEE.std_logic_1164.all;

entity MUX21_GENERIC is

Generic (NBIT: integer:= numBit;

DELAY_MUX: Time:= tp_mux);

std_logic_vector(NBIT-1 downto 0);

Port (

A :

In

In

std_logic_vector(NBIT-1 downto 0);

B:

SEL:

In

std_logic;

Out

std_logic_vector(NBIT-1 downto 0));

Y :

end MUX21_GENERIC;

architecture BEHAVIORAL of MUX21_GENERIC is --normal multiplexer

begin

Y <= A when SEL='1'

else B;

end BEHAVIORAL;

```

#### Synthesis

In the synthesis stage, the model is converted into a gate level netlist. A synthesis tool performs this process, which takes as input:

- Hierarchy;

- Input and output ports of entities;

- Architectural structures: Generic maps and Port maps, Boolean functions, Process and Sensitivity lists.

It generates a generic gate-level architecture using Boolean laws and complex algorithms. At this stage, dependency on the real library and constraints are not taken into account.

#### Design for testability

Design for Testability is a strategy for incorporating testability characteristics into the design of a hardware product. The new capabilities simplify the development and application of manufacturing tests to the designed hardware.

Tests are performed at many stages of the hardware production process and may also be utilised for hardware maintenance in the customer's environment. Test programmes are often used to drive the tests, which are then executed on automated test equipment (ATE) or, in the case of system maintenance, within the constructed system itself. Tests may be able to log diagnostic information regarding the type of test failures in addition to detecting and alerting the presence of faults. The diagnostic data can be utilised to pinpoint the source of the failure.

#### Mapping

The mapping's goal is to provide a netlist with the desired behaviour using only cells from the standard cell library. A standard cell library is a clustering of low-level electronic logic functions like AND, OR, INVERT, flip-flops, latches, and buffers. The key feature of these library cells is that they have a fixed height, allowing them to be planned in rows and thus simplifying the process of the automated digital layout. Cells are typically optimized full-custom layouts that reduce delays and area. A standard-cell library contains a library database and a timing abstract. The views that make up a library database include a variety of logical and simulation aspects, as well as views like layout, schematic, symbol, and abstract. The timing abstract gives each cell information on timing, power, and noise along with functional definitions (liberty file). The following extra elements could also be included in a standard-cell library:

- Transistor models of the cells (Spice).

- DRC rule decks.

The synthesis tool explores the power, speed, and size space to provide different implementations that meet the provided constraints. Each implementation can differ significantly from the others, each of which minimizes a metric or a combination of metrics. During mapping, static timing analysis and power analysis are performed for the purpose of analyzing and optimizing the critical path and the requested power. Both time analysis and power modeling theoretical elements are introduced in section 2.7 and 2.8. A verification step is used to to verify that the synthesis result is logically equivalent to the original RTL description.

Example of AREA report:

| Number of ports:                |                         | 16         |     |            |                      |       |

|---------------------------------|-------------------------|------------|-----|------------|----------------------|-------|

| Number of nets:                 |                         | 94         |     |            |                      |       |

| Number of cells:                |                         | 82         |     |            |                      |       |

| Number of combinational ce      | lls:                    | 82         |     |            |                      |       |

| Number of sequential cells      | :                       | 0          |     |            |                      |       |

| Number of macros:               |                         | 0          |     |            |                      |       |

| Number of buf/inv:              |                         | 12         |     |            |                      |       |

| Number of references:           |                         | 11         |     |            |                      |       |

| Combinational area:             | 109.325999              |            |     |            |                      |       |

| Noncombinational area:          | 0.000000                |            |     |            |                      |       |

| Net Interconnect area:          | undefined               | (Wire load | has | $\rm zero$ | $\operatorname{net}$ | area) |

| Total cell area:<br>Total area: | 109.325999<br>undefined |            |     |            |                      |       |

Example of TIMING report with constraints (slack positive):

| Startpoint: B[0] (input <b>port</b> )<br>Endpoint: Co (output <b>port</b> )<br>Path Type: max |      |      |  |  |

|-----------------------------------------------------------------------------------------------|------|------|--|--|

| Des/Clust/Port Wire Load Model Library                                                        |      |      |  |  |

| RCA                                                                                           |      |      |  |  |

| Point                                                                                         | Incr | Path |  |  |

| input external delay                                                                          | 0.00 | 0.00 |  |  |

| B[0] (in)                                                                                     | 0.00 | 0.00 |  |  |

| add_1_root_add_58_2/B[0] (RCA_DW01_add_0)                                                     | 0.00 | 0.00 |  |  |

| add_1_root_add_58_2/U14/ZN (OAI21_X1)                                                         | 0.05 | 0.05 |  |  |

| add_1_root_add_58_2/U1/ZN (INV_X1)                                                            | 0.02 | 0.07 |  |  |

| add_1_root_add_58_2/U13/ZN (AOI21_X1)                                                         | 0.06 | 0.13 |  |  |

| add_1_root_add_58_2/U3/ZN (INV_X1)                                                            | 0.02 | 0.16 |  |  |

| add_1_root_add_58_2/U12/ZN (OAI21_X1)                                                         | 0.04 | 0.20 |  |  |

| add_1_root_add_58_2/U11/ZN (OAI21_X1)                                                         | 0.04 | 0.24 |  |  |

| add_1_root_add_58_2/U10/ZN (OAI21_X1)                                                         | 0.05 | 0.29 |  |  |

| add_1_root_add_58_2/U2/ZN (INV_X1)                                                            | 0.02 | 0.31 |  |  |

| add_1_root_add_58_2/U9/ZN (AOI21_X1)                                                          | 0.06 | 0.37 |  |  |

| add_1_root_add_58_2/U5/ZN (INV_X1)                                                            | 0.02 | 0.40 |  |  |

| add_1_root_add_58_2/U8/ZN (OAI21_X1)                                                          | 0.04 | 0.44 |  |  |

| add_1_root_add_58_2/U7/ZN (OAI21_X1)                                                          | 0.03 | 0.47 |  |  |

| add_1_root_add_58_2/SUM[4] (RCA_DW01_add_0)                                                   | 0.00 | 0.47 |  |  |

| Co (out)                                                                                      | 0.00 | 0.47 |  |  |

| data required time                                                                            |      | 0.50 |  |  |

| data arrival time                                                                             |      | 0.47 |  |  |

| slack (MET)                                                                                   |      | 0.03 |  |  |

#### Floorplanning

A floorplan of an integrated circuit is a schematic depiction of the location of its principal functional blocks and pins in electrical design automation.

Floorplans are developed in the current electrical design process during the floorplanning design stage, which is an early stage in the hierarchical approach to integrated circuit design.

#### Placement

The tool places the various blocks and I/O pads across the chip area, following the design constraints. Physical components are placed and analog blocks or external IP cores are integrated. Placement tools have many inputs, such as a post-synthesis netlist, a layout view (LEF) for geometry and pin position, a timing description (.lib), and a power dissipation description. They place cells in a row of equal height, connecting them to power and ground lines.

#### Routing

Routing is the process of connecting each element of the design together, starting with the clock tree synthesis (CTS) and then designing logical interconnections. Place and route step produces a GDSII (GDS2) file. GDSII is a binary file format that hierarchically represents planar geometric forms, text labels, and other layout-related data. It is the file that the foundry uses to create silicon.

#### Verification

A detailed view is available after the physical design. Signoff checks are three-step physical design verifications. They are used to check if the layout works as it is designed to do.

The practice of comparing the geometry/layout to the schematic/netlist is known as layout versus schematic (LVS). Design rule checks (DRC) is the process of ensuring that the geometry in the GDS file complies with the guidelines provided by the foundry. Logical equivalence checks (LEC) is the process of checking the equivalence between RTL and post-synthesis and post-layout design.

Other custom verification could be applied at this step, such as a temperature check. A temperature check is used to better evaluate the distribution of heat the heat on the chip.

## 2.2 Metrics

Synthesis and optimization techniques have the main objective of creating a lower abstraction level representation of the design that is logically equivalent to the starting RTL design and with high Quality Of Result (QOR).

The main metrics are based on the composition of the circuit and are used to measure the synthesis results. Delay, area, and power consumption are the central metrics for evaluating a circuit. Delay is the time it takes for an impulse to travel from an entire path. The area is the dimension of a chip. Power consumption is divided into two types: dynamic and static; It measures the amount of power necessary for the system. New metrics, such as routability, have become central with the advancement of technology and increased density. Testability is the propensity of a system to be adequately tested. It became central with the increase in the number of transistors in a chips.

#### 2.2.1 Pareto curve

Optimisation of one parameter most often leads to the deterioration of another parameter. This is because optimisation aims to decrease that parameter as much as possible at the expense of the others. As an example, in the project case, the optimization of the design with respect to timing violations can introduce a power consumption downgrade. Optimization techniques aim to find the respective minimum for parameter tuples respecting all constraints, that is called optimum.

A point is a Pareto Optimal point if there is no other point with at least one better parameter and all others are inferior or equal. A Pareto point definition is used to define a minimal point with respect to two or more metrics. In this work, the definition is used to identify great area/power/timing trade-offs. Vilfredo Pareto introduced the idea of the Pareto Curve in 1964[12]. The curve formed by the set of Pareto Optimal points is called the Pareto curve (figure 2.3).

Figure 2.3: In black, Pareto point for a Delay-Area trade-off. In red, not optimal point.

## 2.3 Abstract models

The objective of synthesis is to take an abstract model of a higher level and produce an abstract model of a lower level. The lower level abstract model contains more information and more levels of optimization. For RTL synthesis, the tool takes a register-transfer level model and produces a logic level model.

Based on the integration capabilities gained from 1958 to 1965, Gordon Moore (Fairchild Semiconductor and later co-founder of Intel Corporation) observed that integration complexity was increasing and would have grown at an exponential rate[11].

The driving force of this evolution is "abstraction." The first microprocessors were developed directly from the layout level with knowledge of the entire module, from the instruction set down to the transistor layout. The design flow is now based on models, each with some characteristics and parameters. A model is a representation of a circuit showing some information relative to the use-case of the model. It enables correct communication about the design between humans and EDA tools.

Abstraction layers and views are used to categorize models. Views are the main language to describe the design; they could be behavioural, structural, or physical. Abstraction layers are formal, they are based on graphs and discrete mathematics to avoid ambiguity; Abstract models describe problems, and create an appropriate algorithm with the properties to formalize the problem.

Abstract models could be classified as:

- Architectural-level models, which describe the model as Data-flow and sequencing graphs. It is used to abstract behavioral models.

- Logic-level models, which are used for efficiently representing logic networks and state diagrams. Logic networks are described using Binary Decision Diagram (BDD). BDD is an acyclic graph that can model a Boolean function.

- Circuit-level models, used to work with the circuit based information of the design.

The abstract models and views are well organised in a specific graph called "Y-chart". The "Y-chart" (figure 2.4) was constituted by Gajski-Kuhn in 1983. It is used to determine the different stages of synthesis and optimization.

Figure 2.4: Gajski–Kuhn chart showing the many perspectives on VLSI hardware design.

## 2.4 Architectural Level Synthesis

Architectural Level Synthesis (ALS) is a series of techniques for transforming an abstract model of circuit behaviour to the datapath. A datapath is a collection of functional units that work together to process data. The hardware behavioural model is described using Hardware Description Language (HDL) and is used as an entry point for this technique. ALS techniques are evaluated based on some metrics, such as Area, Delay or Throughput. The main steps of a ALS are:

- Definition of the sequencing graph based on the formal information contained in the HDL;

- Optimization of the desired metrics;

- Constraint driven synthesis and optimization.

In each technique there are 3 fixed-steps:

- In Scheduling the resources are fixed in a given start time. Scheduling determines latency;

- In Binding the required resources are associated with the possible one;

- Sharing is the possibility of a resourced to be used in more than one operation. Sharing and Binding determines Area.

Performance, timing or area constraint are also considered in this technique.

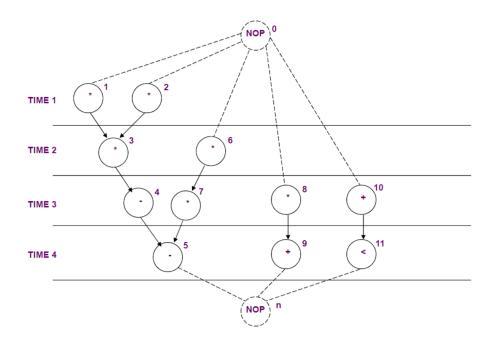

In scheduling, the starting times of each operation are determined, considering the constraints. A Dataflow Graph (DFG) describing all the dependencies is the starting point of the Architectural Level Synthesis. A DFG is a direct graph which is described by a list of nodes and edges and it represents a data dependency between operations.

#### 2.4.1 Scheduling and Binding

Binding is the process of assigning a given component to a given operation. In the case of several available components, this is referred to as an optimisation problem. The solution to the problem must aim to minimise metrics and takes place in parallel with sharing and sheduling.

Scheduling algorithms are classified in:

- Unconstrained scheduling;

- Scheduling with timing constraints;

- Scheduling with resource constraints;

- Minimum resources scheduling under latency constraints.

Unconstrained scheduling is used to calculate the minimum latency. The As soon as possible (ASAP) algorithm calculates the lowest starting time for a task. ASAP schedules the node with no data dependencies at the first possible time (figure 2.5). It starts from the node father down to the leaves (figure 2.5).

Figure 2.5: ASAP scheduling[16].

Scheduling with timing constraints introduces the concept of an external constraint. An external constraint is a limit imposed by an external necessity, such as throughput, area, or delay. A timing constraint is the maximum acceptable latency. The As late as possible (ALAP) algorithm assigns to each operation the maximum starting time possible(figure 2.6). It starts from the sink up to the node(figure 2.6).

Figure 2.6: ALAP scheduling.

Scheduling with resource constraints is a type of algorithm with an exponential increase in complexity. Complexity increases due to the number of operations to be scheduled. The problem of scheduling with resource constraints can be split into two parts: scheduling with a minimum latency and area constraint and scheduling with a minimum area and latency constraint.Complexity can be decreased by using approximate methods that are faster but not exact.

Integer Linear Programming (ILP) is an exact algorithm that is used to minimize a cost function. The cost function could be related to area or delay and is an equation. The number of iterations required to solve this algorithm under a latency constraint is equal to *lambda* (latency) multiplied by the number of nodes.

List scheduling is an example of an approximate algorithm. It schedules first the node with no data dependencies and with the most resources available and the lowest slack. Slack is defined by the difference between the minimum possible starting time and the maximum.

#### 2.4.2 Sharing

Resource sharing describes the problem of assigning a hardware resource to different tasks. Two tasks can be executed by the same resource if they need the same hardware and they are not concurrent.

The left-edge algorithm was proposed by Hashimoto and Stevens in 1971[7] and can be used for the sharing problem. The algorithm works with an ordered list of intervals and places the earlier operation first. It produces a representation of the interval and possible concurrent operations.

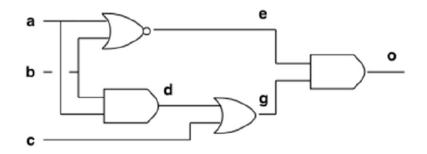

## 2.5 Logic Level Synthesis

Logic level synthesis is the process of converting an abstract specification described at Register Transfer Level (RTL) into a design implementation in terms of logic gates.

Two-level logic synthesis concerns the sum of the product expression of a Boolean function. The main purpose of two-level logic synthesis is to minimize the cover of a Boolean function. A cover of a Boolean function is a set of implicants that covers all its minterms. A product of one or some inputs is an implicant for a Boolean function if it implies a true value for the Boolean function. A minterm is a product of inputs in which each input appears once.

Multi-level logic synthesis concerns all types of basic logic gates. It is the state of the art of the current commercial synthesis tool. In two-level synthesis, behavioral and structural models have the same topology. In multi-level synthesis, we start from a Boolean function (model of behaviour) and arrive to a logic network (model of structure). Multi level's purpose is to find an equivalent representation of a given logic function that minimizes the key metrics (area, delay, power, etc.). There are no exact methods, on the other hand there are some heuristic algorithms.

Algorithms are based on five operators:

- Elimination;

- Decomposition;

- Substitution;

- Extraction;

- Simplification.

Elimination is the operation of removing a node from the network. Consequently, we have to update all the data dependencies with the node value. The main reason for the elimination is to reduce the number of levels.

Decomposition is the operation of splitting a node into two or more nodes. It increases the number of levels but decreases the cardinality of the literal set of the node.

Substitution is used to simplify a node using a local function. The division of the node for the local function returns the new node if the division has no remainder. This operation reduces the number of literals and avoids the recomputing of the same node.

Extraction finds a common sub-expression between two or more expressions. Extract it as a new function and introduce a new block. decomposition of a node and substitution in other nodes.

Simplification is used to simplify the local function of a node using a minimizer.

## 2.6 Verification Techniques

Modern chips are highly complex and can contain millions of transistors. Checking the correctness of the design flow output is a key point for a high Quality Of Result (QOR) design. The growing size and complexity of new chips produces the necessity for faster and more exact verification techniques. Verification can consume up to 70% of a design's time. Verification is used to check that a design meets requirements and specifications.

"Verification. The evaluation of whether or not a product, service, or system complies with a regulation, requirement, specification, or imposed condition. It is often an internal process. Contrast with validation."[9]

"Validation. The assurance that a product, service, or system meets the needs of the customer and other identified stakeholders. It often involves acceptance and suitability with external customers. Contrast with verification."[9]

#### 2.6.1 Simulation

Simulation is a dynamic verification technique that verifies a model's behaviour in time. Simulation concerns the evaluation of the design output for some input stimuli. A simulator is a tool that can calculate signal values over time. It generates waveforms to check the behaviour of the systems. A waveform is a curve that represents the wave's shape at a specific time. Simulation is also used to evaluate the behaviour of signals over time and derive certain parameters such as switching activity. Switching activity is the measuring of changes in signal levels.

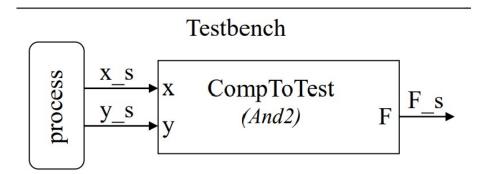

Figure 2.7: A Testbench entity

Simulation is performed by simulating a special entity called Testbench (figure 2.7). The testbench is an entity written in an HDL language. It implements the components under test and checks the components with some input stimuli. The number of input stimuli needed to check all possible input combinations grows exponentially with the number of input  $2^{input}$ . In large designs such as VLSI, the needed test time exceeds the possibility. The concept of coverage is introduced as the number of input stimuli on the number of possible inputs.

RTL description of a Testbench for a "numbit" MUX:

```

entity TBMUX21_GENERIC is

end TBMUX21_GENERIC;

architecture TEST of TBMUX21_GENERIC is

constant NBIT: integer := 16;

signal

A1:

std_logic_vector(NBIT-1 downto 0);

signal

B1:

std_logic_vector(NBIT-1 downto 0);

signal

std_logic;

S1:

signal

std_logic_vector(NBIT-1 downto 0);

output1:

signal

output2:

std_logic_vector(NBIT-1 downto 0);

component MUX21_GENERIC

Generic (NBIT: integer:= numBit;

DELAY_MUX: Time:= tp_mux);

Port (

A :

In

std_logic_vector(NBIT-1 downto 0) ;

std_logic_vector(NBIT-1 downto 0);

B:

In

SEL:

In

std_logic;

std_logic_vector(NBIT-1 downto 0));

Y:

Out

end component;

```

#### begin

```

U1 : MUX21_GENERIC

Generic Map (NBIT, 3 ns)

Port Map ( A1, B1, S1, output1);

U2 : MUX21_GENERIC

Generic Map (NBIT)

Port Map ( A1, B1, S1, output2);

A1 <= "0000000100000001";</pre>

```

```

B1 <= "100000000000001";

S1 <= '0', '1' after 5 ns;

```

#### end TEST;

#### 2.6.2 Formal verification

Formal verification is the process of applying formal mathematical techniques to demonstrate or refute the correctness of the intended algorithms supporting a system concerning a certain formal specification or property. The design is a set of interacting systems, each with a set of possible configurations, or states. A Finite State Machine (FSM) is a composition of states and interactions among them. An FSM can be represented by a state transition graph. Model-checking consists of exploring a state transition graph and checking the mathematical relations between each node. Equivalence checking is used to determine if another implementation of a design behaves the same as the verified one. It is used to check that a design function doesn't change after synthesis and optimization. In a microelectronic flow, formal verification is used to check equivalence between each stage.

## 2.7 Power Modeling

Digital integrated circuit design has become more complex. Timing analysis and power modeling are becoming part of the design flow. Power modeling has been talked about for years by the ASIC industry. PM should have become a game changer in the developing flow, but it encountered various problems due to the error-prone development of the integrated cicruits. There are no standard models and this leads to the possibility of estimation errors. The structure of a low-power synthesis has developed over the years, leading to an improvement in the standard for power modeling at the gate level.

Power consumption has two basic contributors:

$$P = P_{gates} + P_{interconnects}$$

The dissipation relative to the gate can be described as:

$$P_{gates} = P_{dynamic} + P_{short-circuit} + P_{leak}$$

$P_{dynamic}$  is due to the charging and discharging of the capacitance.

$$P_{dynamic} = \alpha * C_{load} * V_{dd}^2 * f$$

$C_{load}$  is the total capacitance seen from the output gate,  $V_{dd}$  is the supply voltage. f = 1/T is the working frequency, where T is the period.

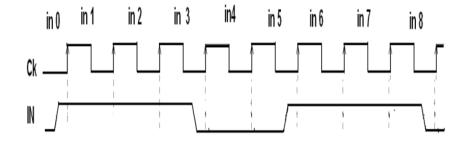

In each period, the capacitance is charged and discharged.  $\alpha$  is the switching activity (figure : 2.8); each gate is not switched in each clock cycle, consequently the capacitance is not discharged. Switching activity is the probability that a gate has to be switched.

Figure 2.8: Switching Activity, representation of 4 switch on 8 clocks.

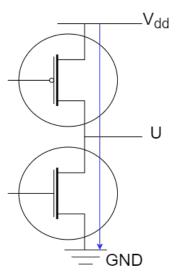

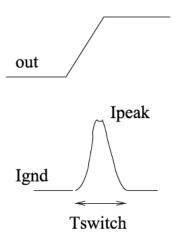

Low-to-high and high-to-low transitions are not instantaneous. Consequently, for an amount of time, both P and N networks are ON (figure 2.9) and a short-circuit current is present,  $P_{short-circuit}$ .

$$P_{short-circuit} = V_{dd} * (I_{PEAK} * t_{switch})/2 * \alpha * f$$

Figure 2.9: I flow on transition.

$I_{peak}$  and  $t_{switch}$  depend on the transistor size, the total load, the input  $t_{rise}$  and  $t_{fall}$ , and the voltage threshold.

Figure 2.10: Peak current during output transition.

$P_{leakage}$  depends on the leakage current. Leakage current is due to the minority charge carriers flowing in the transistor. It depends on transistor size and temperature.

$$P_{interconnects} = V_{dd}^2 * \alpha * f * C_{int}$$

$C_{int}$  is the total interconnection capacitance. Interconnections are also resistive; consequently, a part of power is dissipated in heat due to the Joule effect.

### 2.7.1 Switching Activity

Switching activity is a key measure for evaluating power consumption. It is affected by probability and switching density.

A probability of switching activity is the possibility that a signal has the value "1". Thus, if the signal is always "0", the probability is 0. The number of switches in a clock cycle is calculated as toggling density.

A digital simulation is important to measure the switching activity. Therefore, it is influenced by the behavior of the testbench. The simulation information is written to a file in VCD or FSDB format.

In power analysis, the power dissipation of a circuit is calculated. The required information, such as leakage power, capacitance and wire load model, is embedded in the cell library. This documentation is used along with switching activity data to calculate the design's power model and circuit physical information that take into account the parasitic effects of interconnecting signals. Switching activity is also an important consideration in optimization. It can be reduced by preventing flip-flop switching and memory gating. Clock gating, memory gating and power gating are techniques to reduce switching activity.

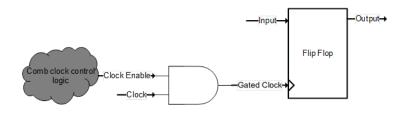

### 2.7.2 Clock Gating

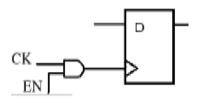

Clock gating is a technique that disables the clock on a portion of the design when the input to the register does not change. This is done using an enable signal (Figure : 2.11). Switching activity is reduced by disabling the clock.

Figure 2.11: Clock Gating example with ENABLE signal.

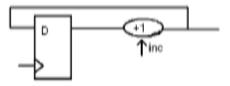

The enable signal is controlled by a control unit that knows when the input changes (Figure: 2.12).

Figure 2.12: Clock Gating example with Control Unit that produce the ENABLE signal [1]. The Control Unit is composed by a counter, an input "inc" and a logic memory containing the desired value.

There are two approaches to using clock gating. The first is done by the RTL designer, and it is introduced as functionality in the RTL. The second is applied by a synthesis and optimization tool by identifying the flip-flops that share the control logic. The simplest way to implement a clock gate is to use a ENABLE signal with a AND gate (Figure: 2.13). The clock is activated when the signal ENABLE is high.

Figure 2.13: AND gate-based clock gating[1].

This solution is prone to glitches due to the asynchronous signal, the delay caused by the gate AND, and the combinatorial logic behind the signal ENABLE (Figure: 2.14).

Figure 2.14: Glitch AND gate-based clock gating[1].

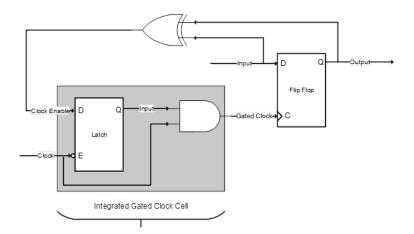

Synthesis tools use custom cells for clock gating called Integrated Gated Clock (ICG) (Figure: 2.15). IGC cells consist of a AND gate, an XOR gate to check the

equivalence between the D value and the Q value, and a sensitive low-level latch to synchronize the enable signal.

Figure 2.15: Integrated Gated Clock (ICG) cells[1].

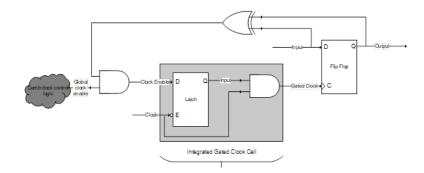

Multi-level clock gating can be achieved by transferring the enable signal from a higher hierarchical level to a lower level (Figure: 2.16).

Figure 2.16: Multi-level propagation of Enable clock gating signal[1].

There are 3 options that typically characterize the clock gating techniques to be used in the synthesis tools:

- Fanout is the maximum number of FFs that can be gated;

- Bitwidth is the minimum number of bits of a register that can be gated by an ENABLE signal;

- Stage is the number of levels of multi-level clock gating.

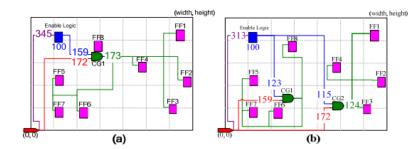

#### **Clock gate cloning**

Clock gate cloning duplicates an ICG cell while maintaining the same enabling logic. It is applied in two cases:

- The fanout of the IGC cell is greater than the maximum;

- The output of the ICG cell is spread over a large area.

The second case is important because a large area entails longer interconnections (Figure: 2.17), which is a key timing constraint problem. A clustering algorithm is used to divide the FFs among the different ICG cells. The clustering algorithm considers the fanout and wire lengths. The number of ICG cells is referred to as sets.

Figure 2.17: Figure a : Clock Gating without cloning, Figure b : Clock Gating with cloning and fanout distribution[3]

## 2.8 Timing Analysis

Static timing analysis (STA) is used to evaluate the timing performance of a design and to identify any possible violations. Dynamic simulation could be used to evaluate the timing performance, but, due to its complexity, it cannot be exhaustive. Therefore, STA is faster and more comprehensive. STA is faster because it does not require simulation time, and it is comprehensive because it examines the route rather than the pure logical circumstance from the testbench.

Some metrics are defined for each node in a network:

- The time taken by the node during the propagation process;

- Data arrival time: the time when an input signal is ready for processing;

- Data required time, i.e. the time constraint for data arrival time;

- Slack is the amount of time lag between data requests and data arrival.

A STA tool calculates the timing perspective of the design after dividing the design into a series of paths. The information about the timing behaviour of the cell is contained in the cell library or can be calculated from an SDF file that contains back-annotated delay information. The analysis is done with respect to different corners, each corner is defined as a different situation (worst, best, leakage, scan). Hold and setup time are calculated for each timing analysis. Setup violations are solved in previous stage, hold violations are solved in physical stages.

Timing constraints for synthesis are created by the designer and are a collection of constraints applied to a given set of paths or nets that determine the intended performance of a design. Period, frequency, net skew, maximum delay between end points, or maximum net delay are all possible constraints.

STA checks the design constraints after reading the cell information and the design data. The constraints result from the behaviour of the clock tree and the registers.

# 2.8.1 Critical Paths

The critical path is the longest sequence of components in the circuit, and it is the upper bound of the clock speed.

In STA, the critical path is the one that has slack of 0, i.e., the one that has the maximum latency for the given constraints.

Constraint could contain execptions, as false path. A false path is a path where the input signal could not be propagated to the output(Figure: 2.18). Synthesis tools reduce the number of false paths by logical optimization. STA has to take into consideration the presence of false paths for timing analysis.

Figure 2.18: Critical path composed by nodes A,D,G,O is a false path.

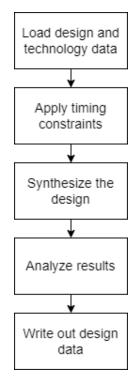

# 2.9 Practical example of a RTL synthesis flow

Synthesis is the transformation of a concept into something useful and capable of satisfying the concept.

Figure 2.19: Synthesis from a concept to an object.

RTL synthesis is a process that generates a gate-level netlist from a block-level RTL design with acceptable post-placement timing and congestion.

The RTL synthesis flow includes the following steps:

- Reading hierarchical block-level RTL designs;

- Loading libraries, technology data and floorplan constraints;

- Applying and checking timing constraints;

- Synthesizing RTL to gate using a top-down or a bottom-up approach;

- Generating timing reports

- Analyzing and improving layout congestion

- Generating output file for physical design tools

Synthesis concerns three parts: Translation, Logic Optimization, and Gate Mapping. Translation from an RTL source to a Generic Boolean Gate (unmapped ddc format). Logic optimization works with a boolean equation using the logic level optimization technique. The last part concerned the mapping of the gate. Transform an unmapped ddc format to a mapped one. Constraints are important before optimization to prevent useless implementation. Synthesis ends with the saving of the results.

Figure 2.20: RTL synthesis flow.

# 2.9.1 Loading Design and Technology Data

The first step of RTL synthesis is to load the necessary information. The information loaded in this step is:

- Design description in an HDL language.

- Logical libraries (db file).

- Physical or layout libraries.

- Routing layer definition file (tf file).

- Floorplan data (TCL physical constraint or DEF file).

The last four files are specially used in topographical synthesis. Topographical synthesis performs placement-driven design mapping and optimization to achieve high QOR and facilitate the back-end flow.

# **Loading Logical Libraries**

The name, cell area, timing behavior, functionality, design rule constraint, and electrical characteristics for each pin are all embedded in a .lib file. Example of a OR description in .lib format:

```

cell ( or2_4x ) {

area : 3.00 ;

pin ( Y ) {

direction : 2 ;

timing ( ) {

related_pin : "A" ;

timing_sense : positive ;

rise_propagation ( ) {

value ("0.22, 0.28, ...")

}

}

function : "(A | B)";

max_capacitance : 2.90 ;

min_capacitance : 0.02 ;

}

pin ( A ) {

direction : 1;

capacitance : 0.12;

. . .

}

}

```

Logical libraries are used during compilation to create a netlist with technology specifications.

### Loading RTL Designs

Hierarchical design is read starting from the bottom entity HDL file and going up to the top entity HDL file. The reading phase could be split into "analyze" and "elaborate" phases. In Analyze, the HDL description syntax is checked. Elaborate is used to connect specific designs and to establish the top entity.

# Loading Physical Data

Some physical data is needed for topographical synthesis. Reference libraries of standard cells, IP or macro cells, and I/O pad cells contain information about size and pin locations.

Technology files contain definitions of routing layers, vias, and layout rules. It also contains information about parasitic net models. The technology files have the typical ".tf" extension. Each file is unique to each technology and describes metal layer technology parameters such as:

- Name, number, physical and electrical characteristic for each layer;

- Dielectric constant for technology;

- Units and precision for the value.

Floorplan information contains constraints on the placement of the cell that are needed in topographical synthesis.

The ASIC Vendor provides reference libraries and technology files. Floorplan information is from previous analysis of the netlist and specification.

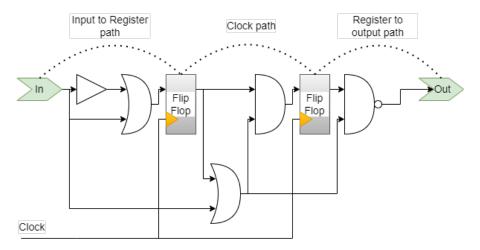

# 2.9.2 Constraints application

Physical constraints are used in topographic synthesis. This constraint regards the floorplan and could be about the core area, ports, macros, and placement. The floorplanning constructs and constraints are contained in Design Exchange Format (DEF). Some options could not be embedded in an DEF file, so an optional tcl file is used.

From timing perspective, timing constraints are utilized to ensure that a design is functional and that it will perform as intended once it is manufactured.

Figure 2.21: Example of timing path.

In figure 2.21, three path are underlined:

• Input to register path;

- The clock path, is called clock path because the timing length is equal to one clock cycle;

- Register to output path;

- InOut path, sum of the previous one.

There are three types of timing constraints that can be identified: Clocking Requirements, Boundary Settings, and Timing Exceptions.

### **Clocking Requirements**

Clocks should be defined with the following parameters:

- Clock period, period contain the delay value of the clock path (figure 2.21);

- Clock source: port, net, pin or virtual;

- Duty Cycle, Skew and Uncertainty;

- Clock tree propagation latency;

- Rise and fall time.

#### **Boundaries Settings and Timing Exceptions**

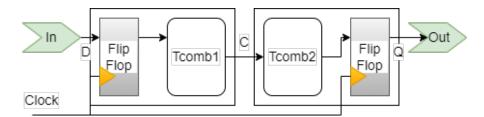

Input and output delays are constraints applied to the I/O ports. They are the arrival and required times that should be considered by a block.

Figure 2.22: Timing constraints on input and output port.

In figure 2.22, an input delay example in C could be the clock timing to Q plus the Tcomb1 delay. The output delay on port D should consider the set-up time of the Flip Flop plus the Tcomb2 delay.

Tcomb2 with Tcomb1 is a combinational path. A minimum or maximum delay could be constrained.

# 2.9.3 Synthesize the Design

Synthesis is the central part of the flow, a brief introduction is presented in section 2.1. Good synthesis can only occur through two excellent previous steps. For example, an HDL code that leaves no optimisation possible at the architectural level results in a worse synthesis. Missing constraints could result in incorrect synthesis or worse QOR.

The synthesis approach must cover the entirety of the design in order to give the EDA tools the possibility of possible optimisation. In this flow, a topographical synthesis is considered, which performs an initial placement to improve the synthesis possibilities and to have greater reliability in the results.

Figure 2.23: Default synthesis step.

In figure 2.23 the synthesis step is explained. The EDA tool uses three-level optimization to produce better QOR.

Each of these three-step synthesises produces some changes in the design. The produced design could not be accomplished with the timing constraint. For this reason, logic level and gate-level optimization techniques could be reused. For example, the duplication technique increases area but could solve the longest path timing problem.

Resource sharing is a technique of architectural level synthesis. This technique could be used only in well-coded RTL. An example of a component in which resource sharing is prevented:

```

Add1 <= A + B;

Add2 <= C + D;

if (sel == 1'b1)

sum <= Add1;

else

sum <= Add2;

end if;

```

Other technique of architectural level synthesis is:

- Boundary Optimization, it consist in optimization in the first/last gate of the module;

- Register Replication, it is used to deal with critical path timing;

- Adaptive retiming, involves moving the register across the combinational circuit to reduce the timing violations. Adaptive retiming could move, duplicate and merging register, but the "End-to-End" behaviour of the circuit is unchanged.

# 2.9.4 Write out results and Design Data

Congestion analysis using the heat map allows for identifying floorplan-based congestion and netlist topologies-based congestion. Netlist topologies-based congestion could be reduced with Physical optimization. Floorplan-based congestion could be optimised by modifying the floorplan.

Report Quality Of Result (QOR), Area, Timing and Power are used to analyze the synthesis results.

A timing report is used to determine all the constraint violations in the design. That could be related to low-quality RTL, wrong constraints, or errors in synthesis. Consequently, designers have to analyze the violating timing path.

Data output needed for Physical Design:

- Gate-level netlist;

- SDC constraints file;

- Floorplan DEF and Tcl files;

- Scan chain definitions;

- Propagate backward SAIF, power profile;

- Unified Power Format (UPF) command script with power intent.

SCAN-DEF file contains the scan chain information.

# 2.9.5 Two-pass synthesis flow

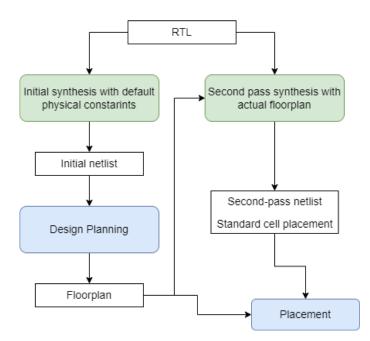

To perform a topographical synthesis, a floorplan is needed; to get a floorplan, a netlist is needed; and to get a netlist, a floorplan is needed. This problem is a Catch-22 problem. A catch-22 is a paradoxical circumstance from which a person is unable to escape due to competing rules or restrictions[8].

A solution to this problem is called "Two-pass synthesis." The synthesis tool would then work with a standard floorplan. The first synthesis loop produces a floorplan to be used in a second complete synthesis.

Figure 2.24: Two-pass synthesis flow.

In figure 2.24, on the left the first pass synthesis, on the right the second pass synthesis. The first pass starts with a constrained synthesis using a default floorplan. Also, a user-defined custom floorplan could be used. The initial netlist is the output and it is sent to a design planning tool that generates the floorplan. The second pass starts using the produced floorplan. The netlist produced with the floorplan is used for placement. This technique should be used with challenging QOR requirements. Re-synthesizing with a more accurate starting point produces the best result. But if QOR is not critical, the second pass could be skipped in order to reduce the synthesis duration.

# **3** Approach

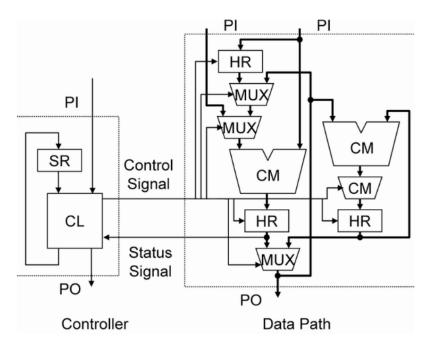

# 3.1 Synthesis Purpose

The objective of the thesis is the formation of a stable synthesis and optimization flow that leads to consistent and valuable results.

The consistency comes from the ability of the flow's ability to be replicated in different designs with minimal changes. Value is determined by the best results of the flow that minimize metrics and adhere to constraints. The results must be certain and verified.

The design to be analyzed is a complex mixed-signal component with memory and a core unit. The modules that make up the design are important to identify better options in the flow. A large memory could have an important improvement by using an important clock gating structure. This optimization is due to the mapping-structure of the memories that increases the probability of more registers switching at the same time. A core logic needs cells with low delay, and a peripheral controller needs cells with high strength. Most of the time, pads and memories are external modules, therefore they are not part of the design. In the specific case of the analyzed design, memories are both internal and external, as pads.

Figure 3.1: Example of an ASIC RTL schematic with datapath and control unit[6].

The main metrics to be met and optimised are area, delay and power consumption. These metrics are influenced by each other and other metrics such as congestion, fanout and strength of the gate, temperature, placement, etc.

The synthesis tool is heuristic and not exact. The synthesis time is also a metric, as usually better results can be obtained with a longer synthesis time. The synthesis time is constrained by the time to market of the product and the development time. Time to market is the time needed before the product can be sold. It is important to meet industry requirements. Development time is a non-recurrent cost, it is a one-time cost.

The objective of this work is to understand the effect of different synthesis settings and parameters (such as use of specific library subsets, clock gating, etc.) in the final results and to propose and compare different flows. The final netlist should be evaluated and verified.

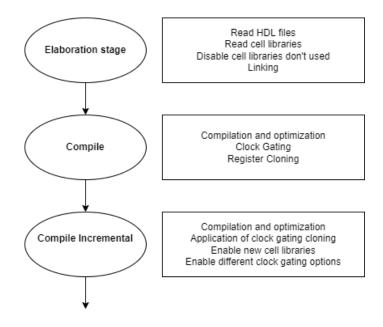

# 3.1.1 Custom synthesis parameters

The approach to synthesis flow is both theoretical and experimental. The tool's algorithm for synthesis and optimization is heuristic rather than exact. Experimentation is the key to developing strategies with higher QoR. The basic flow was presented using only theoretical applications (Section 2.9). The basic flow serves as a starting point for feature development and investigation. It consists of three macros: Elaboration, First Compilation, and Second Compilation.

The elaboration phase is the setup part of the flow. It provides the EDA tool with the main information about the design. HDL files and cell libraries were read and analyzed. Both are linked together and the resulting design is checked. The cell libraries are used in this step, so all decisions about the use of the cell libraries should be made in this step. In the strategies presented below, the cell libraries are limited to a portion of the design or can be disbaled in an early stage of the flow to be used in the next phases.

Clock-gating techniques are introduced in the initial compilation phases. The first compilation phase is characterized by the elaboration of the timing constraint and the application of parameters such as clock gating, register cloning or pin buffering. After the first compilation, area optimization must be performed. Clock gating techniques are our main goal in this phase. This work focuses on adapting clock gating techniques to the given design and analyzing the results of different clock gating applications.

The second compilation introduces new concepts that will be used in the development of this work: the idea of incremental compilation, the clock-gating cloning technique, and the possibility of enabling cell libraries in future compilation phases. After compilation, an area optimization phase is introduced. This is a standard sequential command of each compilation phase. One of the strategies explored in this work is the use of additional cell libraries in subsequent phases. This is possible thanks to incremental compilation. An already synthesized netlist is used as a starting point for the introduction of new cell libraries. This application can also be applied to some modules to fix errors in their timing path.

The steps presented previously are those that characterize the basic flow. More steps have been analyzed in the different strategies presented in this work. The introduction of new stages opens the door for new analyses on new strategies related to different areas: cell libraries applied in the next stage, and different clock gating approaches in different compilation stages.

The concept underlying this evaluation is that each netlist can be used as a starting point for new compilation steps. Consequently, one synthesis strategy could be mixed with another at different stages to manually solve the resulting problems.

The strategies applied to the basic synthesis flow fall into two categories: Flow Structure and Parameter Variation. Parameter variation strategies can be divided into three categories: Clock control parameters, cell libraries, and placement parameters.

Figure 3.2: Phases of basic design flow and application location of new strategies.

# **Clock Gating approach**

Clock gating is used to reduce the dynamic power consumption of the system. It introduces logic into the clock tree, as well as delays that could be reported as timing violations. The logic cell used for clock gating is called integrated clock gating (ICG). In this project, many aspects of clock gating are analyzed. The basic procedure is characterized by clock gating with cloning. Cloning is a technique to duplicate a clock cell to minimize the wire length. The wire length leads to capacitance and hence delays.