## POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

Master's Degree Thesis

## Implementation of the comparison in Residue Numeral System

Supervisor

Candidate

Prof. Guido MASERA

Maria Francesca CASCONE

July 2022

# Summary

Residue Number Systems, RNSs, have been considered a potential tool to parallelize the arithmetic elements breaking the long carry-propagation chain by bounding the RNS inside smaller modulo channels that work in parallel with each other. This parallelism is quite profitable for addition and multiplication and has made possible the usage of RNS in a range of application from embedded and digital signal processing systems to cryptography [1].

However, some operations are difficult to perform using RNS: its non-positional representation makes hard to implement the comparison operation, indeed the existing comparison methods compare the RNS numbers by converting them in positional numeral system.

The *Positional Attribute Non-positional Code*, PANC, method is a mathematical algorithm that allows the comparison in RNS without converting the numbers under consideration. It associates the RNS number to an index that identifies the interval in which the number falls and then performs the comparison between the two indexes associated to both inputs [2].

After a brief introduction to the RNS considering its advantages, disadvantages and applications in Chapter 1, it is fully described in Chapter 2. The different comparison methods along with the PANC one are reported in Chapter 3. Chapter 4 aims to portray the implemented architectures in detail, but their results in terms of simulation in **ModelSim** and synthesis with **Synopsys Design Compiler**, using a 65 nm technology, are both reported in the first part of Chapter 5, while in the second one those new architectures are compared with the state of the art. Finally, the future implementations together with the conclusion are in Chapter 6.

For openers, it must be pointed out that RNS is a mathematical non-positional method based on the Chinese Remainder Theorem, CRT. This last one takes credit to the reduction of the carry-propagation chain speeding up the arithmetic comparison- and division- free operations. This reduction is achieved since the RNS operands are tuples of residues associated to a proper modulus in the moduli set, and therefore, given that the operations are performed on the tuples' components and not on the whole tuple itself, those are going to have a reduced bit-width. The addition, multiplication and subtraction operations are carried out only on residues associated with the same modulus, generating results that could be negative or higher than the modulus itself. As a consequence, since the residues are part of the tuple and that they are associated with each modulus, these two conditions can't occur, but if this should happen, the resultant residues will be reconverted. This has led to seek better solutions in the implementation of those combinatorial elements.

Moreover, it is necessary to convert and reconvert numbers from a positional numeral system to RNS, for this reason several methods of comparison have been studied in order to obtain the most convenient in terms of performance.

Even if the reconversion methods have been used also for the comparison operation in RNS, there are no implemented algorithms that performs the comparison in the RNS' domain. The PANC method is one of those algorithms.

However, nowadays this mathematical method has not been implemented yet, indeed this work aims to create a digital design to transpose this method and analyse its performances. The considered moduli set is  $[2^n - 1, 2^n, 2^n + 1]$  since it is the most used set in RNS' datapaths [3], while the *n* values considered are n = 5 and n = 8, together with n = 3 even if it is not usually adopted for RNS datapaths. Several solutions have been evaluated in order to implement the digital design, nevertheless only the most interesting ones have been selected. In particular, these implemented structures are:

- The Golden model is the architecture that parallelize all the operations, thus it is very attractive because it is the fastest one. In fact, the latency of the operation doesn't depend on the value n or on the moduli set and yet, those last values affect the area occupied by the structure that exponentially increases with n.

- The *Resource sharing* design is the opposite of the previously described golden model as the resources used are fixed and do not change either as *n* or the moduli set vary, but the latency depends on those values giving us a very slow architecture.

- Finally, the Unfolded resource sharing wants to combine the positive sides of both previous architectures applying the technique of the unfolding to the resource sharing design. In this way, the resources are increased by  $2^k$ according to the unfolding level, hence slightly complicating the structure but proportionally reducing the delay.

Those three designs have been analysed in terms of delay, area occupied and power consumption considering a  $65 \ nm$  technology.

Comparing the performances of these three implementations with the state of the art of the actual comparators in RNS, it is clear that our comparators are slower and wider than the existent implementations, although the total power dissipation is lower than the those last ones by at least one order of magnitude.

This is due not only to the lower operating frequency of our implementations but also to the management of the different combinatorial elements that are totally switched-off when not in use. Indeed, even if the increased area affects the power increase, the strong reduction of the switching activity allows to obtain good results, offsetting both area and delay drawback.

Finally, this thesis shows how it is possible, starting by this algorithm, to implement a comparison system not leaving the residue numbering system. As well as the low-power advantages that allows to apply this comparator in energysaving systems so as IoT, the lack of a reconvertion system allows to use the same comparator in datapath RNS taking advantage of the same components again.

# Acknowledgements

Se insisti e resisti, raggiungi e conquisti

# **Table of Contents**

| Li            | st of                     | Tables                                                                                                     |   | IX                                     |

|---------------|---------------------------|------------------------------------------------------------------------------------------------------------|---|----------------------------------------|

| $\mathbf{Li}$ | st of                     | Figures                                                                                                    |   | Х                                      |

| A             | crony                     | vms                                                                                                        | Х | KIV                                    |

| 1             | <b>Intr</b><br>1.1<br>1.2 | <b>roduction</b> Motivation                                                                                |   | 1<br>1<br>2                            |

| 2             | <b>Res</b><br>2.1<br>2.2  | idue Number System methodConversion and ReconversionOperations in RNSConversion in RNS                     |   | $egin{array}{c} 3 \ 6 \ 7 \end{array}$ |

| 3             | Con<br>3.1<br>3.2         | <b>nparison with Residue Number System</b> Current comparison methodsPANC methodCurrent comparison methods |   | 10<br>10<br>11                         |

| 4             | <b>Des</b><br>4.1         | ign to implement the PANC method comparisonGolden Model4.1.1Datapath4.1.2Control Unit                      |   | 16<br>20<br>20<br>26                   |

|               | 4.2                       | Resource sharing                                                                                           |   | 29<br>29<br>36                         |

|               | 4.3                       | Unfolding of the resource sharing                                                                          |   | 38<br>39<br>43                         |

| 5             | <b>Res</b><br>5.1         | ults<br>Results                                                                                            |   | 44<br>44<br>44                         |

|    |       | 5.1.2   | Resource sharing $n=3$                     | 45 |

|----|-------|---------|--------------------------------------------|----|

|    |       | 5.1.3   | Unfolded resource sharing $n=3$ with $k=2$ | 46 |

|    |       | 5.1.4   | Golden model n=5                           | 47 |

|    |       | 5.1.5   | Resource sharing $n=5$                     | 48 |

|    |       | 5.1.6   | Unfolded resource sharing $n=5$ with $k=2$ | 48 |

|    |       | 5.1.7   | Unfolded resource sharing $n=5$ with $k=3$ | 49 |

|    |       | 5.1.8   | Unfolded resource sharing $n=5$ with $k=4$ | 50 |

|    |       | 5.1.9   | Resource sharing $n=8$                     | 51 |

|    |       | 5.1.10  | Unfolded resource sharing $n=8$ with $k=2$ | 52 |

|    |       | 5.1.11  | Unfolded resource sharing $n=8$ with $k=3$ | 53 |

|    |       | 5.1.12  | Unfolded resource sharing $n=8$ with $k=4$ | 54 |

|    | 5.2   | Compa   | arison with existing methods               | 55 |

| 6  | Con   | clusior | and future implementations                 | 61 |

| Bi | bliog | raphy   |                                            | 63 |

# List of Tables

| 4.1            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     |   |     |   |   | 17       |

|----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|---|-----|-----|---|-----|---|---|----------|

| 4.2            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     | • |     |   |   | 21       |

| 4.3            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     |   |     |   |   | 25       |

| 4.4            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     |   |     |   |   | 26       |

| 4.5            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     |   |     |   |   | 28       |

| 4.6            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     |   |     |   |   | 29       |

| 4.7            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     |   |     |   |   | 36       |

| 4.8            |   |   |   |   |   |   |   |   |   |   |   |   | • |   |   | • | • |   |   |   |   | • | • |   |   | • |   |   |   | • |     |   | •   |     |   | • • |   |   | 37       |

| 4.9            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   | •   |     | • |     |   |   | 38       |

| 4.10           |   |   |   |   |   |   |   |   |   |   | • |   | • |   |   | • | • |   |   |   |   | • | • |   |   | • |   |   |   | • |     |   |     |     |   |     |   |   | 39       |

| 4.11           |   |   |   |   |   |   |   |   |   |   | • |   | • |   |   | • | • |   |   |   |   | • | • |   |   | • |   |   |   | • |     |   |     |     |   |     |   |   | 40       |

| 4.12           |   |   |   |   |   |   |   |   |   |   | • |   | • |   |   | • | • |   |   |   |   | • | • |   |   | • |   |   |   | • |     |   |     |     |   |     |   |   | 40       |

| 4.13           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     | • |     | • |   | 43       |

| ۳ 1            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     |   |     |   |   | 15       |

| 5.1            | · | · | · | · | · | · | · | • | • | · | · | • | • | • | • | • | • | • | · | • | · | • | • | • | • | • | • | • | • | • | • • |   |     |     |   |     |   | • | 45       |

| 5.2            | · | • | · | · | · | · | · | · | • | · | · | · | • | · | • | • | - | - | - | - | - | - |   | - | - |   | - | - | - | - | • • |   |     |     |   |     | • | • | 46       |

| 5.3            | · | · | · | · | · | · | · | • | • | · | · | · | • | · | · | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • • |   |     |     |   |     |   | • | 47       |

| 5.4            | · | · | · | · | · | · | · | • | • | · | · | · | • | · | · | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • • |   |     |     |   |     |   | • | 47       |

| 5.5            | · | • | · | · | · | · | · | · | • | · | · | · | • | · | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |     |   |     |     |   | • • |   | • | 48       |

| 5.6            | · | • | • | · | • | · | · | • | • | · | • | · | • | · | • | • | • | · | - | · | - | - | • | - | • |   | - | • | - | - | • • |   |     |     |   |     | • | • | 49       |

| 5.7            | · | · | · | · | · | · | · | • | • | · | · | · | • | · | · | • | · | - | - | - | - | - |   | - | - |   | - |   | - | • |     | • |     |     |   |     | • | • | 50       |

| 5.8            | · | • | • | • | · | · | · | • | • | · | • | · | • | · | • | • | • | • | - | - | • | - | • | - | - | - | - | • | • | • | • • | • | • • |     |   |     | • | • | 51       |

| 5.9            | · | • | • | • | · | · | · | • | • | · | • | · | • | · | • | • | • |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     |   | • • | • | • | 52       |

| 5.10           | · | • | · | · | · | · | · | · | • | · | · | · | • | · | • | • | · | • | • | • | • | • | • | • | • | • | • | • | • | • | • • |   |     | • • |   | • • |   | • | 53       |

| 5.11           | · | • | · | · | · | · | · | · | • | · | · | · | • | · | • | • | • | · | - |   | - | - | • | - | - |   | - | • | - |   | • • |   |     |     |   | • • |   | • | 54       |

| $5.12 \\ 5.13$ | · | • | • | • | · | · | · | · | • | · | · | · | • | · | • | • | • | • | • | • | · | • | • | • | • | • | • | • | • | • |     |   |     | • • |   | • • |   | • | 54       |

| 5.13<br>5.14   | · | • | · | · | • | · | · | • | • | · | • | · | • | · | • | • | • | - | - | - | - | - | • | - | - | - | - | • | • | • | • • |   |     |     |   | • • | • | • | 56       |

| -              | · | • | • | • | · | · | · | · | • | · | · | · | • | • | · | - | - |   | - |   | - | - |   | - | - |   | - |   | - |   |     |   |     |     |   |     | - | - | 58       |

| 5.15<br>5.16   | • | • | · | · | · | · | · | · | • | • | · | · | • | · | · | • | • | • | • | • | · | • | • | • | • | • | • | • | • | • |     |   |     | • • |   |     |   | • | 59<br>50 |

| $5.16 \\ 5.17$ | • | • | · | · | · | · | · | · | - | - | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |     |     |   |     |   | • | 59<br>60 |

| 0.17           | • | · | · | · | · | · | · | • | • | · | · | · | · | · | • | · | · | · | · | · | · | · | • | · | · | · | · | · | • | • | • • | • |     |     | • | • • |   | • | 60       |

# List of Figures

| 2.1 | Representation of the signed RNS numbers in range $M. \ldots \ldots$                                                                           | 4  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Overview of an RNS based application.                                                                                                          | 5  |

| 2.3 | Operations of addition subtraction and multiplication considering                                                                              |    |

|     | the moduli set [3,4,5] and the input values $X = 8$ and $Y = 7$                                                                                | 9  |

| 3.1 | Whole range $M$ divided in $N_{m_i}$ intervals of $m_n$ magnitude                                                                              | 12 |

| 4.1 | Graphical representation of the decreasing clock cycles for increasing                                                                         | 10 |

|     | unfolding level computed as $2^k$                                                                                                              | 18 |

| 4.2 | Graphical representation of the decreasing clock cycles for increasing<br>unfolding level computed as $2^k$ considering $n = 3$                | 19 |

| 4.3 | Graphical representation of the decreasing clock cycles for increasing                                                                         | 10 |

| 1.0 | unfolding level computed as $2^k$ considering $n = 5$                                                                                          | 19 |

| 4.4 | Graphical representation of the decreasing clock cycles for increasing                                                                         |    |

|     | unfolding level computed as $2^k$ considering $n = 8$                                                                                          | 20 |

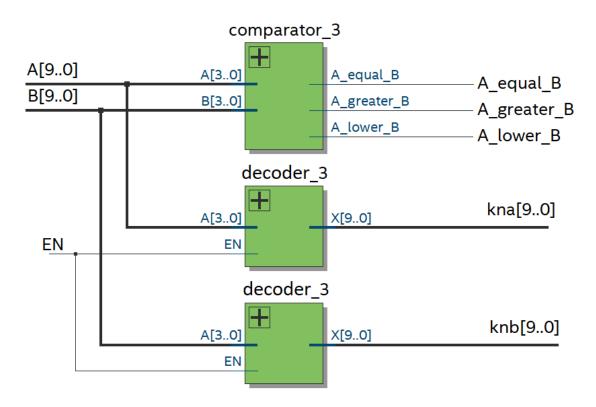

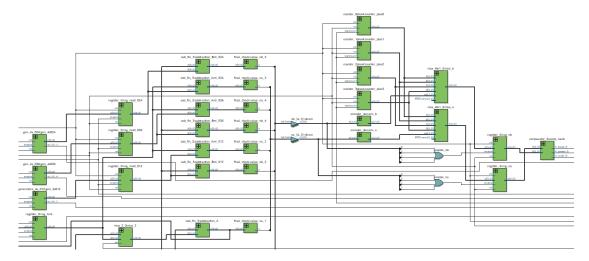

| 4.5 | The first part's RTL structure for $n = 3$ in which the inputs A<br>and B's $n + 1$ bits are used to both generate the proper zeroing          |    |

|     | constant with the decoders and the result of the comparison between                                                                            |    |

|     | its $m_n$ -th residue                                                                                                                          | 22 |

| 4.6 | Modular subtractor in case $n = 3$ : each component is considered                                                                              |    |

|     | with respect of the associated modulus $([7, 8, 9])$                                                                                           | 23 |

| 4.7 | Multiplier used in the designs for $n = 3$ : the first $n + 1$ bits are                                                                        |    |

|     | forced to 0, the following $n$ bits are given as output while the least                                                                        |    |

|     | $n$ bits are modified by the circular shift. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                      | 24 |

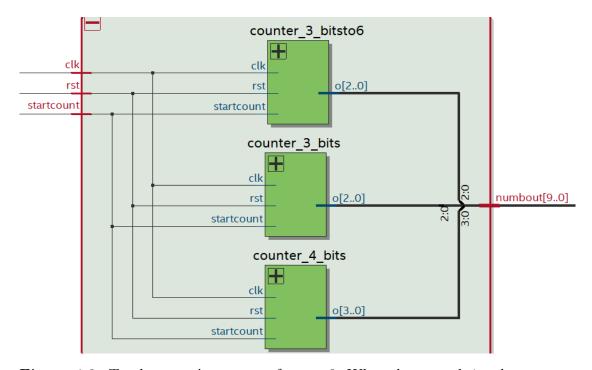

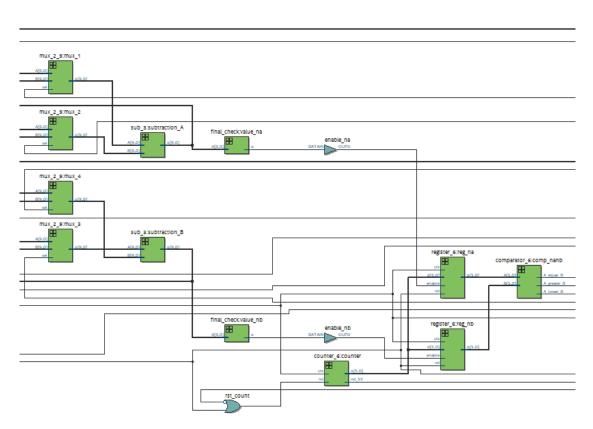

| 4.8 | Golden Model's Finite State Machine                                                                                                            | 27 |

| 4.9 | Total counter's structure for $n = 3$ . When the control signal <i>start-count</i> is asserted, the counters start computing all the following |    |

|     | values adding always $+1$ . The counters <i>counter_3_bitsto6</i> and                                                                          |    |

|     | counter_4_bits have an internal reset when they reach the maxi-                                                                                |    |

|     | mum value respectively of 6 and 8                                                                                                              | 30 |

|     |                                                                                                                                                |    |

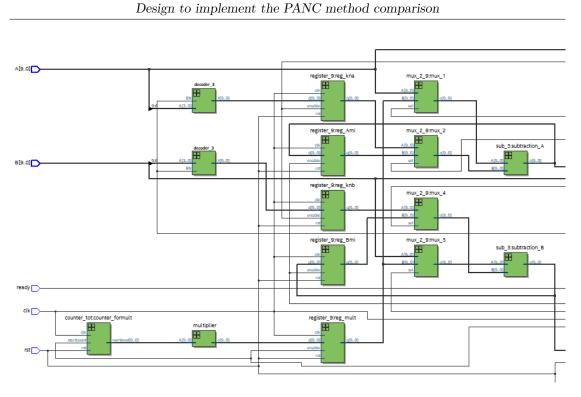

| 4.10 | Resource sharing's first and second part with the two decoders<br>used to generate the zeroing constants, the registers allocated for                                                                                                                                                                                                                                                                                                      |          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | the zeroing constants and the multiples, the four multiplexers to<br>select the subtractors inputs and the counters together with the                                                                                                                                                                                                                                                                                                      |          |

|      | fake-multiplier and the multiplication's output register                                                                                                                                                                                                                                                                                                                                                                                   | 31       |

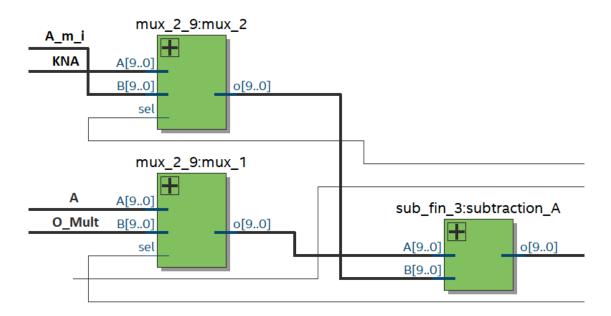

| 4.11 | The multiplexers and their inputs together with the subtractor used<br>in the Resource sharing's design                                                                                                                                                                                                                                                                                                                                    | 32       |

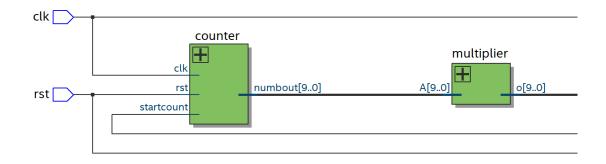

| 4.12 | The connection between the counter and the fake-multiplier in the Resource sharing's design.                                                                                                                                                                                                                                                                                                                                               | 32       |

| 4.13 | The indexes $n_A$ and $n_B$ generation in the third part: the subtraction<br>results are checked thanks to an equality comparator and enables<br>the indexes register if their outcome is asserted. To generate the<br>indexes, it is used a binary counter. After the indexes memorization,                                                                                                                                               | 0.4      |

| 4.14 | those values are compared in a comparator                                                                                                                                                                                                                                                                                                                                                                                                  | 34       |

|      | $nanb\_ready = nA\_greater\_nB \ OR \ nA\_lower\_nB \ OR \ nA\_equal\_$<br>and the $done = A\_greater\_B \ OR \ A\_lower\_B \ OR \ A\_equal\_B$<br>signal, finally the multiplexer that select the final output which is<br>stored in the registers                                                                                                                                                                                        | nB<br>35 |

| 4.15 | Resource sharing's Finite State Machine                                                                                                                                                                                                                                                                                                                                                                                                    | 37       |

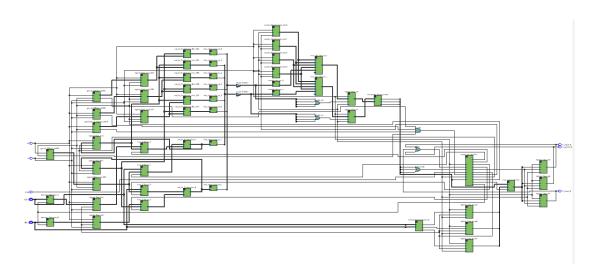

| 4.16 | Unfolded Resource sharing design for $n = 3$                                                                                                                                                                                                                                                                                                                                                                                               | 42       |

| 4.17 | Unfolded Resource sharing design for $n = 3$ : the counter generates<br>all the multiplied results that are stored in their proper registers,<br>then they are subtracted from the multiplies values and this latter<br>output is detected from the equality comparator. All the outcomes of<br>the 4 equality comparator are stored used from the encoder to select<br>the 4 binary counters' output to be stored in the index' register. |          |

|      | Finally those indexes values are compared                                                                                                                                                                                                                                                                                                                                                                                                  | 42       |

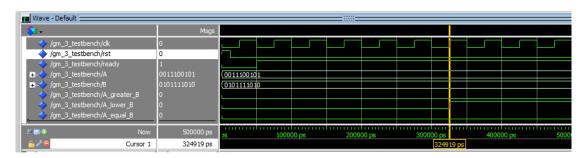

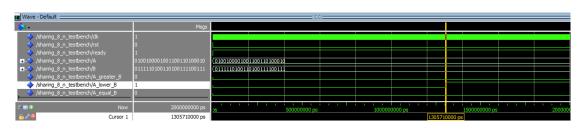

| 5.1  | Golden model design simulation for $n = 3$ with inputs $A = 12$ and $B = 23$ : the result is $A < B$                                                                                                                                                                                                                                                                                                                                       | 45       |

| 5.2  | Resource sharing design simulation for $n = 3$ with inputs $A = 503$<br>and $B = 502$ : the result is $A > B$ .                                                                                                                                                                                                                                                                                                                            | 45       |

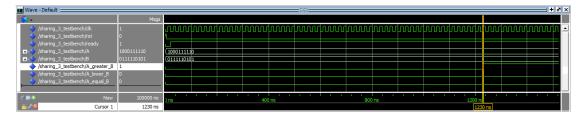

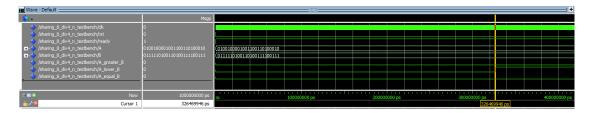

| 5.3  | Unfolded resource sharing $n = 3$ with $k = 2$ design simulation with inputs $A = 2$ and $B = 3$ : the result is $A < B$ .                                                                                                                                                                                                                                                                                                                 | 46       |

| 5.4  | Golden model design for $n = 5$ with inputs $A = 2569$ and $B = 35$ :<br>the result is $A > B$                                                                                                                                                                                                                                                                                                                                             | 47       |

| 5.5  | Resource sharing's Finite State Machine.                                                                                                                                                                                                                                                                                                                                                                                                   | 48       |

|      | -                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

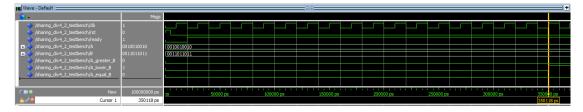

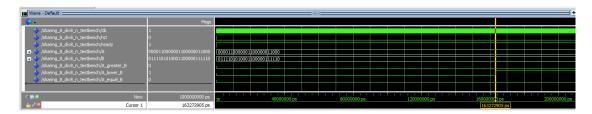

| 5.6  | Unfolded resource sharing $n = 5$ with $k = 2$ design simulation with |    |

|------|-----------------------------------------------------------------------|----|

|      | inputs $A = 378$ and $B = 4779$ : the result is $A < B$               | 49 |

| 5.7  | Unfolded resource sharing $n = 5$ with $k = 3$ design simulation with |    |

|      | inputs $A = 378$ and $B = 4779$ : the result is $A < B$               | 50 |

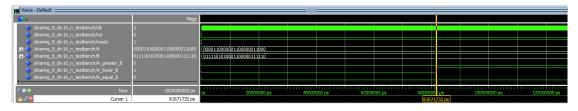

| 5.8  | Unfolded resource sharing $n = 5$ with $k = 4$ design simulation with |    |

|      | inputs $A = 2549$ and $B = 567$ : the result is $A > B$               | 51 |

| 5.9  | Resource sharing design for $n = 8$ and inputs $A = 2457$ and $B =$   |    |

|      | 489321: the result is $A < B$                                         | 52 |

| 5.10 | Unfolded resource sharing $n = 8$ with $k = 2$ design simulation with |    |

|      | inputs $A = 2457$ and $B = 489321$ : the result is $A < B$            | 52 |

| 5.11 | Unfolded resource sharing $n = 8$ with $k = 3$ design simulation with |    |

|      | inputs $A = 24$ and $B = 75032$ : the result is $A < B$               | 53 |

| 5.12 | Unfolded resource sharing $n = 8$ with $k = 4$ design simulation with |    |

|      | inputs $A = 24$ and $B = 75032$ : the result is $A < B$               | 54 |

|      |                                                                       |    |

## Acronyms

#### $\mathbf{RNS}$

Residue Number System

#### CRT

Chinese Reminder Theorem

#### MRC

Mixed Radix Conversion

#### VLSI

Very Large Scale Integration

#### FPGA

Field-Programmable Gate Array

#### ASIC

Application-Specific Integrated Circuit

#### TPP

Totally Parallel Prefix

#### $\mathbf{RPP}$

Regular Parallel Prefix

## Chapter 1

## Introduction

#### 1.1 Motivation

The Residue Number System is a mathematical method invented in 1959 based on the Chinese Remainder Theorem, CRT. The CRT has detected some interesting number theoretic properties and features that can speed up some operations by reducing the the carry-propagation chain which is the main bottleneck of fast arithmetic operations [4]. The RNS operands have reduced bit-width with respect of the binary ones since the operations are performed on the residues associated to the division of each modulus in a specific moduli set. In this way the actual bit-width depends on the modulus value which cannot be exceeded so that all the operations conducted in each modulus channel are independent and carry-free. From 1961, the RNS features have been used in design digital systems division and comparison free, finding out a great speed advantage and motivating researchers to use RNS to improve the speed for digital systems that performs difficult operations.

Since the RNSs lead to increasing performances and reducing hardware cost [5], those systems are widely applied in digital signal processing, medical imaging [6] and artificial neural networks [7]. The RNS' modularity offers advantages for all the division and comparison free algorithms because of the progresses in the architectures of addition [8], subtraction and multiplication [9].

However, the operations of division and comparison are still sore points in the RNSs' structures. About the comparisons methods, those operations are supported with converting structures in order to convert the non-positional RNS' numbers in positional ones, but nowadays it has not been implemented a digital system that performs the comparison in RNS without converting the values. Nonetheless there are algorithms that allows to perform the RNS comparison without converting the values. One of those algorithm has been exposed in [2], but never implemented with digital systems.

This work aims to create a possible digital design to compare two RNSs numbers using the proposed mathematical algorithm and evaluate its performances in terms of delay, power consumption and occupied area.

#### 1.2 Work flow

To implement the algorithm proposed in [2], it is first important to understand the RNS operations and generations also referring to open-source tools as seen in Chapter 2. In this way it becomes easier to figure out the mathematical algorithm and the necessary elements to perform the comparison with this new method as reported in 3.2. After the stabilization of the algorithm using **Python** and the selection of the moduli set, all the possible structures have been designed on paper in order to choose the best designs to implement.

Three structures have been selected and described in VHDL: the first and the second ones are respectively the fastest but widest and the slightest but slowest, so the third architecture is a trade-off between those two designs applying the *unfolding method* to the second design. All the structures have been analysed in Chapter 4, while in Chapter 5 are reported the related results in ModelSim together with the synthesized ones with Synopsys Design Compiler and the comparison between those new implementations with respect of the existing ones, exploited in 3.1.

The other possible choices and the ideas for future implementations are reported in Chapter 6, together with the final conclusions.

## Chapter 2

# Residue Number System method

An RNS is characterized by a set of N relatively coprime numbers known as moduli  $m_i$  with i = 1, 2, ..., N to represent all the numbers in the dynamic range M equal to the multiplication between all the used moduli  $m_i$ , as reported in Equation (2.1) [4].

$$M = \prod_{i=1}^{N} m_i \tag{2.1}$$

Considering a number X, the non-negative reminders  $x_i$  associated to the division  $\frac{X}{m_i}$  represent the RNS value as  $X_{RNS} = [x_1, x_2, \dots, x_N]$  with the moduli set  $[m_1, m_2, \dots, m_N]$ .

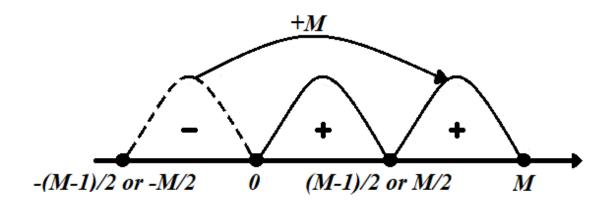

If X is an unsigned number, then it is represented in the range [0, M), while if it is a signed number it falls in the range  $[0, \frac{M}{2})$  if X is positive, or in  $[\frac{M}{2}, M)$  if it is negative [1]. To better understand their representation, we may refer to Figure 2.1.

Figure 2.1: Representation of the signed RNS numbers in range M.

It is evident that all the residues are non-negative and cannot exceed the associated modulus value, but rather if those two conditions do not occur those values must be reconverted, as exploited in detail in 2.2.

The RNS is a non positional numeral system in which there is not a weight associated with any digit, however its tuple representations as  $X_{RNS} = [x_1, x_2, \dots, x_N]$ allows to perform each operations in parallel across smaller modulus channels.

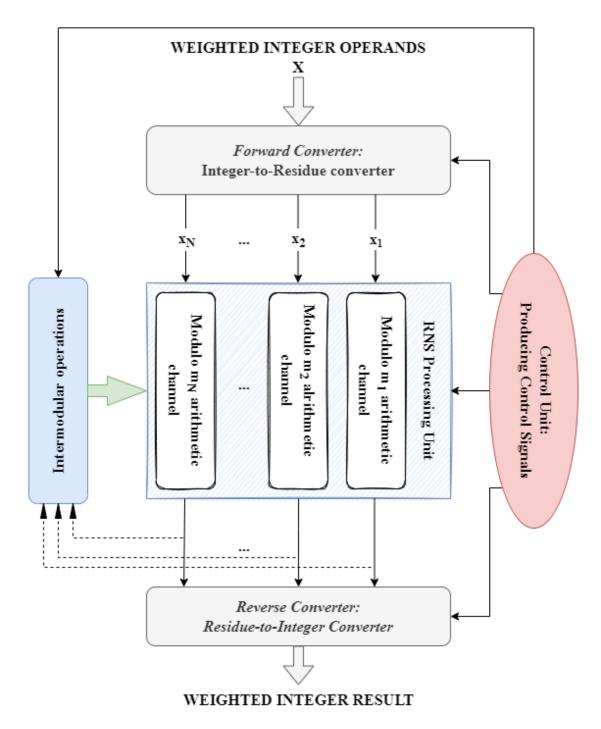

Indeed, in Figure 2.2 is reported an overview of an RNS based application: at first the positional values are converted in RNS with a *Forward Converter*, then in a *RNS Processing Unit* the residues associated to each modulus are menaged and finally are reconverted thanks to the *Reverse Conversion* [4].

Figure 2.2: Overview of an RNS based application.

In this work the traditional 3-moduli set  $[2^n - 1, 2^n, 2^n + 1]$  is used since it is the most common one in RNS datapaths [3], even if it is not the best one in terms of dynamic range: this is the reason together with its reduced parallelism that has led to investigate on larger and different moduli set [1].

#### 2.1 Conversion and Reconversion

The *Residue Numeral System* is based on the *Chinese Reminder Theorem*, CRT, a method whose theory ensures us the RNS application. Thanks to the CRT it is possible to say that if the moduli set has been chosen appropriately, then each number in the considered dynamic range will have a unique representation in RNS so that it can be converted and reconverted [10]. The CRT reconversion is also used as a method to implement the comparison by compare the numbers in a positional numeral system after the proper reconversion.

Indeed, the CRT methods states that considering a moduli set  $[m_1, m_2, \ldots, m_N]$  of positive pairwise relatively prime integers, any number X in the M range can be written in RNS as reported in Equation (2.2):

$$X_{RNS} = [|X|_{m_1}, |X|_{m_2}, \dots, |X|_{m_N}] = [x_1, x_2, \dots, x_N]$$

(2.2)

where  $|X|_{m_i}$  is the mathematical representation of the reminder of  $\frac{X}{m_i}$ .

Any RNS number can be reconverted thanks to the CRT as in Equation (2.3):

$$X = \left| \sum_{i=1}^{N} M_i \times \left| k_i \times x_i \right|_{m_i} \right|_M$$

(2.3)

where  $M_i = \frac{M}{m_i}$  and  $k_i = |M_i^{-1}|_{m_i}$  which represents the multiplicative inverse of  $|M_i|_{m_i}$  so that  $|M_i \times M_i^{-1}|_{m_i} = 1$  [4].

As it is possible to see, the CRT method requires a binary inner product operation and a large modulo M operation that makes the VLSI realization slow and complex. Therefore, other reconversion's methods may be used to improve VLSI reconversion's realization such as the *Mixed Radix Conversion*, MRC, algorithm.

The MRC method is sequential and cannot be parallelized, so that it is not suitable for high-speed design [11]. The reconversion takes place through Equation (2.4).

$$X = \sum_{i=1}^{n} v_i a_i \tag{2.4}$$

where n > 1,  $v_i = \prod_{j=1}^{i-1} m_j$  for  $2 \le i \le n$  considering  $v_1 = 1$  while  $a_i = |Y_i|_{m_i}$ , by imposing  $Y_1 = X$  and  $Y_i = (Y_{i-1} - a_{i-1})|m_{i-1}^{-1}|_{m_i}$  [11]. The combination of CRT and MRC methods generates another reconversion technique [11] reported in Equation (2.5).

$$X = \sum_{j=1}^{n-2} \left[ \alpha_{j+1} \prod_{i=1}^{j+1} m_i \right] + \alpha_1 m_1 + \alpha_0$$

(2.5)

where  $\gamma_i = M |M_i^{-1}|_{m_i} / m_1 m_i$ ,  $\alpha_{j+1} = \left| \left| \sum_{i=1}^{j+2} \gamma_i x_i / \prod_{i=2}^{j+1} m_i \right| \right|_{m_j+2}$ .

The modified CRT algorithm reduces the modulo base of  $m_i$  leading to an efficient and independent of the moduli sets' size converter design for small-sized moduli set [11]. It uses the Equation (2.6).

$$X = x_1 + m_1 \left| \sum_{i=1}^n w_i x_i' \right|_{m_n \dots m_2}$$

(2.6)

where n > 1,  $w_1 = \frac{(M_1|M_1^{-1}|_{m_1}-1)}{m_1}$ ,  $w_i = \frac{M_i}{m_1}$ ,  $x'_1 = x_1$  and  $x'_i = |M_i^{-1}|_{m_i} x_i$  considering  $i \in [2, n]$ .

In order to get a faster reconversion, other techniques and algorithms are investigated. One of the faster is reported in [12] which is based on the CRT scheme, while partial methods such as the *partial CRT* or *partial MRC* are preferred for the better performances [3].

#### 2.2 Operations in RNS

The operations carried successfully with RNS are addition, subtraction and multiplication. Those operations are performed on each residue in a modular way. To better understand their formulation, considering two numbers X and Y and the moduli set  $[m_1, m_2, \ldots, m_N]$  of positive pairwise relatively prime integers, the operations of addition, subtraction and multiplication on the two RNS values  $X_{RNS} = [x_1, x_2, \ldots, x_N]$  and  $Y_{RNS} = [y_1, y_2, \ldots, y_N]$  are reported respectively in Equations (2.7), (2.8) and (2.9).

$$X_{RNS} + Y_{RNS} = [|x_1 + y_1|_{m_1}, |x_2 + y_2|_{m_2}, ..., |x_N + y_N|_{m_N}]$$

(2.7)

$$X_{RNS} - Y_{RNS} = [|x_1 - y_1|_{m_1}, |x_2 - y_2|_{m_2}, ..., |x_N - y_N|_{m_N}]$$

(2.8)

$$X_{RNS} \times Y_{RNS} = [|x_1 \times y_1|_{m_1}, |x_2 \times y_2|_{m_2}, ..., |x_N \times y_N|_{m_N}]$$

(2.9)

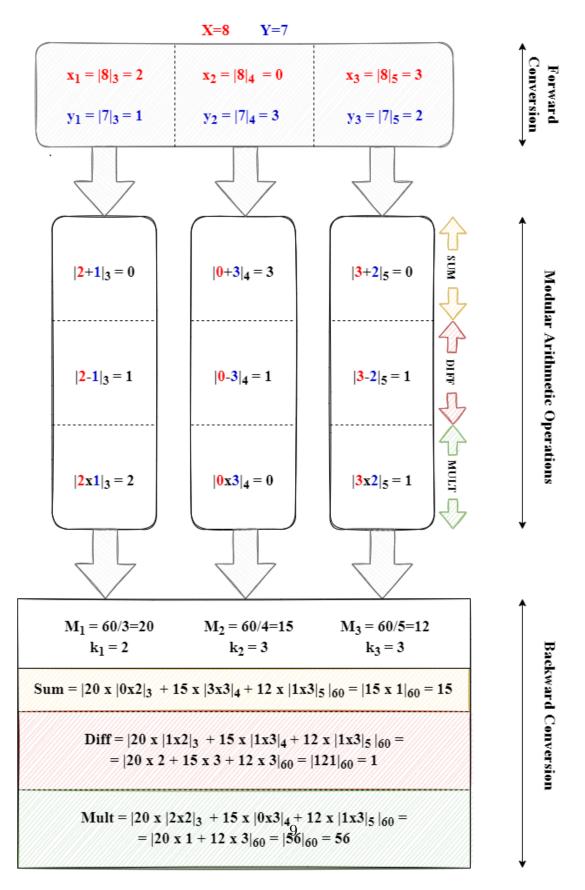

An example is reported in Figure 2.3 in which two values of X and Y are converted with the moduli set [3,4,5] as in Equation (2.2), then the three operations

of addition, subtraction and multiplication are applied and finally those two values are reconverted as in Equation (2.3).

As it is possible to see, the RNS operations' results are always positive reminders that do not exceed the associated modulus value.

Those consideration help us to understand the algorithms used in open source software solutions: if the result of a modular addition or multiplication is higher than the modulus, then the reminder associated to the modulus is recomputed; instead, if the result of a modular subtraction is negative, then the reminder associated to the modulus is recomputed by adding the modulus value itself.

The algorithms of addition, subtraction and multiplication are reported respectively in Algorithm 1, 2 and 3  $\,$

| Algorithm 1 Addition in RNS           |

|---------------------------------------|

| for $i=1:1:length(moduli\_vector)$ do |

| add(i)=a(i)+b(i);                     |

| $if add(i) > moduli_vector(i) then$   |

| $add(i)\% = moduli\_vector(i);$       |

| end if                                |

| end for                               |

| return add                            |

|                                       |

#### Algorithm 2 Subtraction in RNS

```

for i=1:1:length(moduli_vector) do

sub(i)=a(i)-b(i);

if sub(i)<0 then

sub(i)+=moduli_vector(i);

end if

end for

return sub</pre>

```

| Algorithm | 3 | Multiplication in RNS |  |

|-----------|---|-----------------------|--|

|-----------|---|-----------------------|--|

```

for i=1:1:length(moduli_vector) do

mult(i)=a(i)*b(i);

if mult(i)>moduli_vector(i) then

mult(i)%=moduli_vector(i);

end if

end for

return mult

```

Figure 2.3: Operations of addition subtraction and multiplication considering the moduli set [3,4,5] and the input values X = 8 and Y = 7.

## Chapter 3

# Comparison with Residue Number System

#### **3.1** Current comparison methods

Nowadays to implement the comparison in *Residue Number System* different solutions are proposed. The most used and exploited methods are the following [3].

- 1. Conversion-Based Schemes: This first method is the easiest one that solves the problem at the source comparing the two values in a positional system after their reconversion. However, the drawback is choosing the best reconversion system to get the best performances.

- 2. Subtraction-Based Methods: This method is about checking the sign of the difference between the two operands to understand their relation. The sign check operation is not easy to implement in RNS, so the RNS subtraction result can be both reconverted in binary or its sign is recognized using the proper techniques.

- 3. Parity Checking Schemes: Studying the comparison results, it is possible to see that if all the modulus are odd the comparison is a result of the operands' parity and their difference. This method avoids the conversion but needs some specifications in the moduli set that are not so used since the modulus  $m_i = 2^n$  is one of the most efficient arithmetic channel.

- 4. Diagonal Mapping: Since the numbers in the dynamic range of a k moduli RNS can be arranged in a k-dimension space, it is possible to group all the RNS numbers in diagonal lines if k = 2, diagonal surfaces if k = 3 and so on. The diagonals are associated to integers so that it is possible to compare the

numbers associated to each diagonal to evaluate the comparison result, if the inputs are on the same diagonal the comparison is performed between the two residues.

The method exploited in this work is similar to the Diagonal mapping one: as in this latter method, every number is associated to indexes that are compared. The diagonal evaluation uses the Equation (3.1) [13].

$$D(x) = \left| \sum_{i=1}^{n} k_i x_i \right|_{SQ} \tag{3.1}$$

where  $SQ = \sum_{i=1}^{n} M_i$ ,  $k_i = \left| -\frac{1}{m_i} \right|_{SQ}$  and  $x_i$  represents the residue associated to the modulus  $m_i$  [13].

The diagonal mapping has been investigated to speed up the most difficult and costly operation which is the modulo-SQ addition. In addition, there are also different methods that modifies the diagonal function evaluation that represents the RNS numbers [14].

The parity checking method examines the parities of both the operands and their difference and then effectuates the final decision using a simple algorithm. However, the parity detection method is quite complex to implement and requires that all the moduli are odd.

The conversion-based scheme is widespread and encourages to research improved conversion methods: in [15] the comparison is achieved after converting the RNS values in MRC digits, [16] and [3] split the range in subranges via partitioning functions achieved thanks to a *partial CRT* reconversion, [11] uses Equation (2.5) to reconvert the inputs and then compare them in binary.

The conversion method is also needed for the subtraction-based schemes since after the RNS-subtraction the result can be fully [17] or partially [18] reconverted to check its sign ([19], [20]).

#### 3.2 PANC method

The method exploited in this work is the *Positional Attribute of Non-positional Code*, also known as PANC. The numbers represented in RNS cannot be directly compared due to the non-positional representation, however the PANC method aims to carry out the comparison without converting the numbers and therefore using the Residue Number System representation.

The PANC method is not based on the comparison between the two RNS values in question, but it associates them to a specific range in order to compare those two latter numbers. Even if this method does not resort to any conversion of the numbers, it features some disadvantages such as the computational complexity of forming PANC and the difficulty of directly use the method during the implementation of data comparing operations.

The aim of this work is to create architectures that can perform the mathematical method which uses the PANC, as done in [2], for quickly and accurately comparing two numbers in RNS.

The procedure to perform the comparison with the mathematical method which uses the PANC is reported in this section to better understand the architectural choices.

Before the description it is necessary to define some operands:

- 1.  $m_n$  is the highest modulus considered in the moduli set.

- 2.  $N_{m_i}$  is the product between all the moduli except the highest one.

- 3.  $KN_{m_n}^{A_{RNS}}$  and  $KN_{m_n}^{B_{RNS}}$  represent the zeroing constants of the two operands  $A_{RNS}$  and  $B_{RNS}$ .

- 4. The vectors  $K_{N_{m_n}}^{(n_A)}$  and  $K_{N_{m_n}}^{(n_A)}$  contain all the difference values respectively of  $Z_i^{A_{RNS}}$  and  $Z_i^{B_{RNS}}$ .

- 5.  $a_n$  and  $b_n$  are the residues associated to the last modulus  $m_i$ .

- 6.  $n_A$  and  $n_B$  represent the range associated respectively  $A_{RNS}$  and  $B_{RNS}$  and they are the positional attribute of the non-positional code.

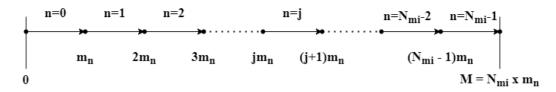

The inputs  $A_{RNS}$  and  $B_{RNS}$  should be in the range (0, M] with  $M = \prod_{i=1}^{n} m_i$ , the aim of the exposed mathematical method is identify and compare the two values  $n_A$  and  $n_B$  by dividing the whole range M in  $N_{m_i}$  intervals of  $m_n$  magnitude as represented in Figure (3.1).

Figure 3.1: Whole range M divided in  $N_{m_i}$  intervals of  $m_n$  magnitude.

The accuracy by which the comparison is evaluated depends on the size of the  $N_{m_i}$  intervals as  $W_{m_i} = \frac{1}{m_i}$ . Since  $m_i$  is the largest modulus, the accuracy  $W_{m_i}$  is the lowest possible. However the number of intervals  $N_{m_i}$  is also the lowest and

this is a huge benefit given that, as will be described in the algorithm, on this value depends the number of operations used to obtain the vectors  $K_{N_{m_i}}^{(n_A)}$  and  $K_{N_{m_i}}^{(n_A)}$  whose magnitude is, as a matter of fact,  $N_{m_i}$ .

In order to obtain an higher accuracy, it is checked the relationship between the residues associated to the highest modulus:  $a_n$  and  $b_n$ . If the two numbers under observation  $A_{RNS}$  and  $B_{RNS}$  fall in the same interval  $j = n_A = n_B$ , indeed, then the values  $a_n$  and  $b_n$  are going to establish exactly the magnitude of each operands leading to the result of the comparison.

The algorithm can be described in six steps, taking into account that both the numbers under observation A and B are already in their RNS form, respectively  $A_{RNS}$  and  $B_{RNS}$ :

- 1. The evaluation of  $N_{m_i}$ ;

- 2. The formation of zeroing constants  $KN_{m_n}^{A_{RNS}}$  and  $KN_{m_n}^{B_{RNS}}$ ;

- 3. The evaluation of  $A_{m_n}$  and  $B_{m_n}$ , computed as in Equation (3.3). Those latter values are multiples of modulo  $m_n$  of RNS;

- 4. The definition of each single component  $Z_i^{A_{RNS}}$  and  $Z_i^{B_{RNS}}$  in order to create the vectors  $K_{Nm_n}^{(n_A)}$  and  $K_{Nm_n}^{(n_A)}$ , computed as in (3.4);

- 5. The formation of the quantitative values  $n_A$  and  $n_B$  for which  $Z_{n_A}^{(A)} = 0$  and  $Z_{n_B}^{(B)} = 0$ ;

- 6. The comparison's implementation for  $A_{RNS}$  and  $B_{RNS}$  as reported in (3.5).

As already said, the  $N_{m_i}$  is the product of all the moduli except the last one. Since this value is not generally used when operating in RNS, we must evaluate this as in Equation (3.2):

$$N_{m_i} = \prod_{i=1}^{n-1} m_i \tag{3.2}$$

where n is the maximum modulus' index.

Each zeroing constant represents the RNS value of the number in the range  $[0, m_n)$  that has the same input's  $m_n$ -th residue [21]. To better understand its significance, knowing that any value X in RNS can be written as

$$X_{RNS} = (x_1 || x_2 || \dots || x_{i-1} || x_i || x_{i+1} || \dots || x_n)$$

its related zeroing constant  $KN_{m_n}^{(X_{RNS})}$ , which is associated to the  $m_n$  modulus, is going to have all different residues with respect of the ones of the input  $X_{RNS}$  except the *n*-th one:

$$KN_{m_n}^{(X_{RNS})} = (x_1'||x_2'||...||x_{i-1}'||x_i'||x_{i+1}'||...||x_n)$$

If a number is multiple of a modulus, then its associated residue is going to be 0. This latter consideration let us understand that  $A_{m_n}$  and  $B_{m_n}$ , defined as *multiples* of the modulus  $m_n$ , can be extrapolated as the difference between the inputs and their proper zeroing constant as reported in Equation (3.3).

$$A_{m_{i}} = A_{RNS} - KN_{m_{n}}^{(A)} =$$

$$= (a_{1}||a_{2}||...||a_{i-1}||a_{i}||a_{i+1}||...||a_{n}) - (a'_{1}||a'_{2}||...||a'_{i-1}||a'_{i}||a'_{i+1}||...||a_{n}) =$$

$$= (a_{1}^{(1)}||a_{2}^{(1)}||...||a_{i-1}^{(1)}||a_{i}^{(1)}||a_{i+1}^{(1)}||...||0)$$

$$B_{m_{i}} = B_{RNS} - KN_{m_{n}}^{(B)} =$$

$$= (b_{1}||b_{2}||...||b_{i-1}||b_{i}||b_{i+1}||...||b_{n}) - (b'_{1}||b'_{2}||...||b'_{i-1}||b'_{i}||b'_{i+1}||...||b_{n}) =$$

$$= (b_{1}^{(1)}||b_{2}^{(1)}||...||b^{(1)}_{i-1}||b^{(1)}_{i}||b^{(1)}_{i+1}||...||0)$$

(3.3)

During this third step, both the inputs  $A_{RNS}$  and  $B_{RNS}$  have been reported in one of the  $N_{m_i}$  intervals, even if to get their exact position it is necessary to execute the next operation: the computation of each single  $Z_i^{A_{RNS}}$  and  $Z_i^{B_{RNS}}$  to form the vectors  $K_{N_{m_n}}^{(n_A)}$  and  $K_{N_{m_n}}^{(n_A)}$ . Both  $Z_i^{A_{RNS}}$  and  $Z_i^{B_{RNS}}$  are evaluated by subtracting respectively from  $A_{m_i}$

Both  $Z_i^{A_{RNS}}$  and  $Z_i^{B_{RNS}}$  are evaluated by subtracting respectively from  $A_{m_i}$ and  $B_{m_i}$  all the multiples of  $m_n$  in the whole range [0, M), evaluated as the multiplication between  $m_n$  and all the numbers in the interval  $[0, N_{m_i})$ . Their computation is reported in Equation (3.4).

$$\begin{cases}

A_{m_{i}} - 0 \cdot m_{n} = Z_{0}^{(A_{RNS})}, \\

A_{m_{i}} - 1 \cdot m_{n} = Z_{1}^{(A_{RNS})}, \\

A_{m_{i}} - 2 \cdot m_{n} = Z_{2}^{(A_{RNS})}, \\

\vdots \\

A_{m_{i}} - (N-2) \cdot m_{n} = Z_{N-2}^{(A_{RNS})}, \\

A_{m_{i}} - (N-1) \cdot m_{n} = Z_{N-1}^{(A_{RNS})}, \\

B_{m_{i}} - 1 \cdot m_{n} = Z_{1}^{(B_{RNS})}, \\

B_{m_{i}} - 2 \cdot m_{n} = Z_{2}^{(B_{RNS})}, \\

\vdots \\

B_{m_{i}} - (N-2) \cdot m_{n} = Z_{N-2}^{(B_{RNS})}, \\

B_{m_{i}} - (N-2) \cdot m_{n} = Z_{N-2}^{(B_{RNS})}, \\

B_{m_{i}} - (N-1) \cdot m_{n} = Z_{N-1}^{(B_{RNS})};

\end{cases}$$

(3.4)

The result of the Equation (3.4) is a binary sequence of ones and only one zero. This only one zero is representing the exact interval position of the considered input:

$$A_{m_i} - n_A \cdot m_n = 0 \to A_{m_i} = n_A \cdot m_n$$

$$B_{m_i} - n_B \cdot m_n = 0 \to B_{m_i} = n_B \cdot m_n$$

Now that the exact interval positions of both the intervals are known, the algorithm can be finally implemented as in Equation (3.5):

$$A_{RNS} = B_{RNS}, if [(n_A = n_B) and (a_n = b_n)] A_{RNS} > B_{RNS}, if (n_A > n_B) or [(n_A = n_B) and (a_n > b_n)] A_{RNS} < B_{RNS}, if (n_A < n_B) or [(n_A = n_B) and (a_n < b_n)]$$

(3.5)

In Equation (3.5), according to the accuracy's considerations, also the residues associated to the last modulus  $a_n$  and  $b_n$  are taken into account.

### Chapter 4

# Design to implement the PANC method comparison

In this chapter are reported all the architectural choices made in order to create a valuable PANC comparator. Once the proper moduli set has been chosen, the best architectural designs in terms of delay, area and power consumption have been selected. The next three models are described in the paragraphs 4.1, 4.2 and 4.3, while the results associated to each design are discussed in the next chapter, section 5.1.

The chosen moduli set is  $[2^n - 1, 2^n, 2^n + 1]$ , since it is the most popular one in Residue Number System's datapaths [22]. The *n* values most commonly used are n = 5 and n = 8: all the considered designs operate with both the two moduli set [31, 32, 33] and [255, 256, 257]. Another moduli set for which tests are done is the one with n = 3, [7, 8, 9], since its simplicity makes it easier to build and useful to find out the system's problems.

With the moduli set proposed, the comparator has to work with values represented on 3n + 1 bits ((n) + (n) + (n + 1)) and for each modulus  $m_i$  considered the maximum number represented is  $m_i - 1$  [17]. Therefore, for n = 5 the numbers are represented with 16 bits and the maximum RNS number representable is [30, 31, 32] equal to 32735 in decimal, while with n = 8, 25 bits are needed to operate on all the numbers within 0 and 16776959, whose value in RNS is [254, 255, 256].

To be aligned with the others architectures found, the number's representation for each design is composed by the first n + 1 most significant bits associated to the modulus  $2^n + 1$ , then the last 2n bits are related respectively to the moduli  $2^n$ and  $2^n - 1$ .

The first proposed solution in the paragraph 4.1 is the *Golden Model* in which we assume that all the operations are performed in parallel with the highest resources

possible. This architectural design is expecting to be the faster but also the wider.

The second architectural design in paragraph 4.2 is the opposite of the Golden Model because the resources used are reduced to the minimum and shared: indeed, it is the *Resource sharing* one. Since this latter design is the reverse of the first one, we anticipate the smaller but slower performances because all the operations are done sequentially. Furthermore, as it is possible to see from the algorithm's description in 3.2, all the steps are sequential except the comparison between the residues associated to the larger modulus  $m_n$ . Besides, it is possible to divide all the sequential steps depending on the values of  $m_n$  and  $N_{m_i}$ : the zeroing constants evaluation rely on  $m_n$ , while all the next operations, the generation of the vectors  $K_{N_{m_n}}^{(n_A)}$  and  $K_{N_{m_n}}^{(n_A)}$  and the indexes identification  $n_A$  and  $n_B$ , depend on  $N_{m_i}$ . Only the determination of  $KN_{m_n}^{A_{RNS}}$  and  $KN_{m_n}^{B_{RNS}}$  is not depending on any of those values. To clearly illustrate the values of  $m_n$  and  $N_{m_i}$  for the different n considered, it is possible to refer to Table 4.1.

| n | $N_{m_i}$ | $m_n$ |

|---|-----------|-------|

| 3 | 56        | 9     |

| 5 | 992       | 33    |

| 8 | 65280     | 257   |

Table 4.1

From those consideration, the Golden Model is expected to take the same clock cycles to perform the algorithm regardless of the n considered, however to get the performance's parallelization, the number of architectural elements is depending on both the values  $m_n$  and  $N_{m_n}$ , and, therefore, on n.

Conversely, the resource sharing model is expected to be formed by the same number of logical elements independently on n and to take about  $N_{m_i}$  clock cycles, since the zeroing constant evaluation is performed thanks to a *decoder*.

Both those two solutions are not ideal: the first one will occupy a lot of area, the second one will be too slow. To reach a trade off between those two solutions it has been applied the *unfolding* technique to the resource sharing design as reported in the section 4.3. Considering the  $N_{m_i}$ 's magnitude, only the algorithmic steps related to  $N_{m_i}$  have been unfolded.

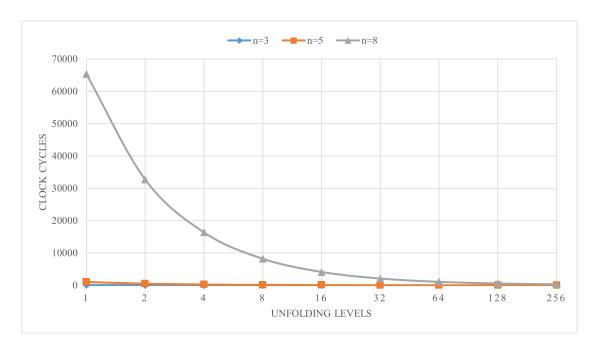

In order to evaluate the best unfolding level, in Figure 4.1 is shown a graph in which are reported the clock cycles taken for each unfolding level  $2^k$  with increasing k. The clock cycles are computed as  $2 + \frac{N_{m_i}}{2^k}$  since we surely need 2 clock cycles to generate the zeroing constants  $KN_{m_n}^{A_{RNS}}$  and  $KN_{m_n}^{B_{RNS}}$  and the multiples  $A_{m_n}$  and  $B_{m_n}$ , but we are replicating each unit that accomplishes the algorithm' steps depending on  $N_{m_n}$  as  $2^k$ .

Design to implement the PANC method comparison

Figure 4.1: Graphical representation of the decreasing clock cycles for increasing unfolding level computed as  $2^k$ .

The most interesting cases are the ones with k = 2,3,4: considering k = 2 the clock cycles are reduced by almost 4 times, but in the n = 8 case the computation should still need more than  $10^4$  cycles (16322 more specifically), also the results for n = 5 are not optimal, while for n = 3 the reduction is significant; this is why we moved to the next unfolding level k = 3 for both n = 5 and n = 8, we have not considered the case for n = 3 since we calculated that clock cycles' gain would have been lower with respect of the structure's complexity. Those considerations also apply for k = 16 in the n = 5 case, which is where we stopped also in case n = 8 to be in line with the results.

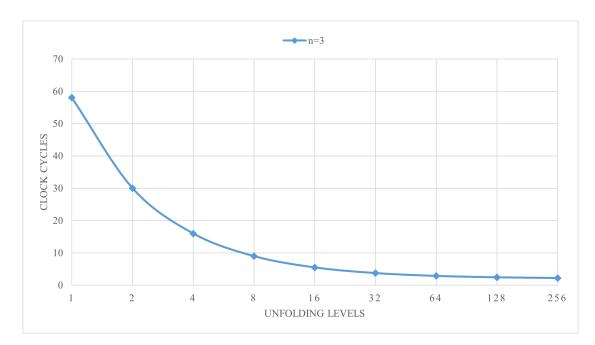

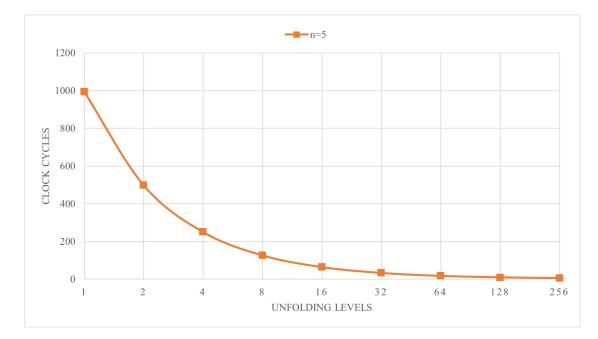

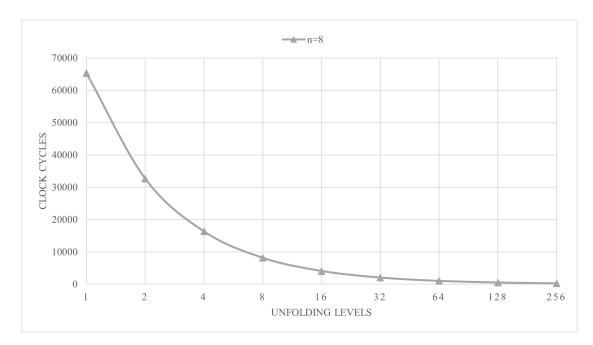

In Figure 4.2, 4.3 and 4.4 are reported in detail the decreasing clock cycles for increasing unfolding level  $2^k$  respectively for n = 3, n = 5 and n = 8 in order to better understand their behavior.

Design to implement the PANC method comparison

**Figure 4.2:** Graphical representation of the decreasing clock cycles for increasing unfolding level computed as  $2^k$  considering n = 3.

**Figure 4.3:** Graphical representation of the decreasing clock cycles for increasing unfolding level computed as  $2^k$  considering n = 5.

Design to implement the PANC method comparison

Figure 4.4: Graphical representation of the decreasing clock cycles for increasing unfolding level computed as  $2^k$  considering n = 8.

In section 4.3 those designs are reported, analyzed and commented and those consideration are better exploited.

#### 4.1 Golden Model

The first structure analyzed is the *Golden Model*. As already anticipated, this architecture is the fastest and largest, but it is also the simplest that can be imagined and the starting point for the definition of other designs.

At first it is described in details the *Datapath* associated to this design, then it is explained how its *Control Unit* works.

#### 4.1.1 Datapath

The Golden Model's design is a direct implementation of the algorithm, this is why in its description it is divided in three different parts that will be described in detail in this section.

The first part includes the definition of the zeroing constants and evaluates the result of the comparison between  $a_n$  and  $b_n$ . Both those two instructions can be performed by simply using the inputs' n + 1 most significant bits since the latter instruction can be easily performed by a simpler n + 1 bits comparator, while

the zeroing constants  $KN_{m_n}^{A_{RNS}}$  and  $KN_{m_n}^{B_{RNS}}$  are evaluated using **two decoders** with n + 1 input bits and 3n + 1 output bits. Each decoder associates the  $m_n$ 's residue to its number in RNS as reported in the truth table in Table 4.2 referred to the simplest case of n = 3 where each output has been lined with its associated modulus.

| INPUT | $m_9$ | $m_8$ | $m_7$ |

|-------|-------|-------|-------|

| 0000  | 0000  | 000   | 000   |

| 0001  | 0001  | 001   | 001   |

| 0010  | 0010  | 010   | 010   |

| 0011  | 0011  | 011   | 011   |

| 0100  | 0100  | 100   | 100   |

| 0101  | 0101  | 101   | 101   |

| 0110  | 0110  | 110   | 110   |

| 0111  | 0111  | 111   | 000   |

| 1000  | 1000  | 000   | 001   |

Table 4.2

To clarify the functioning of the first part in Figure 4.5 is reported its RTL scheme for n = 3. The decoder's EN input signal is generated by the control unit and used to make the decoder working only when necessary, so during this first clock cycle.

Figure 4.5: The first part's RTL structure for n = 3 in which the inputs A and B's n + 1 bits are used to both generate the proper zeroing constant with the decoders and the result of the comparison between its  $m_n$ -th residue.

This first part's outputs are  $KN_{m_n}^{A_{RNS}}$  and  $KN_{m_n}^{B_{RNS}}$ , the two zeroing constants on 3n + 1 bits, and the outcome of the comparison represented as 3 single bit signals representing the possible outcome of the operation:  $a_n > b_n$ ,  $a_n < b_n$  and  $a_n = b_n$ . All the results are written in their proper registers, ready to be used in the following steps.

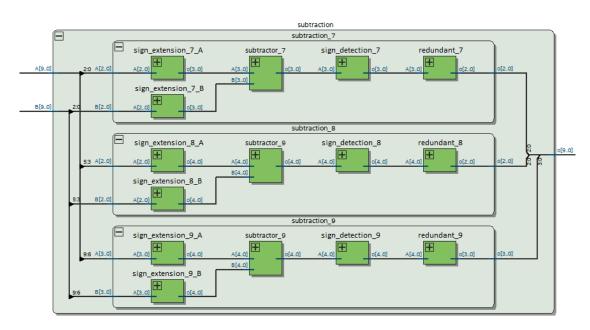

The second part gives as results the inputs'  $m_n$  multiples  $A_{m_n}$  and  $B_{m_n}$  and each single component  $Z_i^{A_{RNS}}$  and  $Z_i^{B_{RNS}}$ , both computed as in Equation (3.3) and (3.4) respectively. Those two RNS operations are both modular and are respectively a **subtraction** and a **multiplication for a constant value**. It is, indeed, performed the subtraction between the inputs and their proper zeroing constants, computed in the previous part and stored in their proper registers, and the multiplication of all the numbers in the range  $[0, N_{m_i})$  by the constant  $m_n$  value in RNS equal to [2, 1, 0].

The subtraction cannot give any negative residue result since the negative numbers in RNS are identified considering the dynamic range [5]. In order to avoid the negative numbers, the subtractor has been built following the Algorithm 2 as reported in all the open-source software solutions.

Each modular subtractor is formed by 4 elements:

- 1. **Sign extension** by which is added '0' at the start of the residue knowing that all the values are for sure positive;

- 2. Subtractor to perform the subtraction between signed numbers;

- 3. Sign detection to detect the most significant bit and add the modulus value in case the MSB is equal to '1', so the number is negative, otherwise the number is given to the last element without any change;

- 4. To keep the number on its proper bitwidth, the last component eliminates the most significant bit, that is for sure '0', and it is named as **redundant**.

With the chosen moduli set it is necessary to add only one bit to the residues associated to both the highest and lowest moduli. The  $2^n$  modulus is written on n + 1 bits, so its signed subtraction must be performed on n + 2 bits and this is the reason why the *sign extention* component adds two zeroes "00" and the last component truncates the two most significant bits.

In Figure 4.6 is reported the modular subtractor structure for n = 3 where each component is marked with respect of the associated modulus ([7, 8, 9]).

Figure 4.6: Modular subtractor in case n = 3: each component is considered with respect of the associated modulus ([7, 8, 9]).

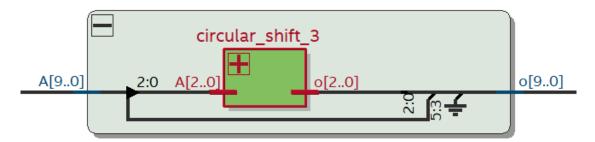

As it is possible to see from the algorithm, each number in the interval  $[0, N_{m_i})$  must be multiplied by the constant  $m_n$  value in RNS form. Also, all those inputs must be available all at the same moment, that is why they are all stored in their proper 3n + 1 bits registers. Considering our moduli set, this RNS constant is equal to [2, 1, 0]. It is not worth to use a proper RNS multiplier, but, looking at the numbers, it is possible to set all the 3n + 1 bits as follows:

- The most significant n + 1 bits are forced to 0;

- The following *n* bits are equal to the input ones;

- The least *n* bits are multiplied by 2. Observing the software' solutions Open-Source, if after the multiplication the resultant residue is higher than the modulus' value, the result's residue must be ri-evaluated, as reported in the Algorithm 3. Although, it is possible to see that each multiplication result is its *circular shifted* value, making possible to only use a **circular shift** to perform the multiplication.

This is the reason why the multiplier has been named as Fake-multiplier. Its structure considering the design with n = 3 is reported in Figure 4.7.

Figure 4.7: Multiplier used in the designs for n = 3: the first n + 1 bits are forced to 0, the following n bits are given as output while the least n bits are modified by the circular shift.

To accomplish this second algorithmic part are necessary 2 subtractors,  $N_{m_i}$  circular shifts and  $N_{m_i} + 2$  registers of 3n + 1-bits to memorize the results and parallelize the operation. Also it is necessary to remember the needs of  $N_{m_i}$  registers to get the multiplication inputs.

The third part completes the comparison. The operations managed in this part are the evaluation of the vectors  $K_{N_{m_n}}^{(n_A)}$  and  $K_{N_{m_n}}^{(n_A)}$ , computed as in (3.4), the formation of the quantitative values  $n_A$  and  $n_B$  for which  $Z_{n_A}^{(A)} = 0$  and  $Z_{n_B}^{(B)} = 0$  and finally the comparison between  $A_{RNS}$  and  $B_{RNS}$  as reported in (3.5). The

algorithmic formation of the vectors  $K_{Nm_n}^{(n_A)}$  and  $K_{Nm_n}^{(n_A)}$  is implemented by subtracting from the  $m_n$ 's multiples,  $A_{m_n}$  and  $B_{m_n}$ , the results of the previous multiplication and by inserting a '1' whenever the subtraction gives a result different from 0, otherwise is put a '0'. Those two vectors can be created by using only subtractors and an **equality comparator**, but there has been made a slightly modification by inserting a '1' if the subtraction result gives a 0 and '0' otherwise. In this way has been exploited an **encoder** to achieve the indexes  $n_A$  and  $n_B$ 's detection. In Table 4.3, is reported the encoder's truth table considering n = 3 (even if is not reported in its enterety).

| INPUT                                   | OUT    | Decimal |

|-----------------------------------------|--------|---------|

|                                         | 001    | value   |

| 000000000000000000000000000000000000000 | 000000 | 0       |

| 000000000000000000000000000000000000000 | 000001 | 1       |

| 000000000000000000000000000000000000000 | 000010 | 2       |

| 000000000000000000000000000000000000000 | 000011 | 3       |

| 000000000000000000000000000000000000000 | 000100 | 4       |

| 000000000000000000000000000000000000000 | 000101 | 5       |

| 000000000000000000000000000000000000000 | 000110 | 6       |

| 000000000000000000000000000000000000000 | 000111 | 7       |

|                                         |        |         |

| 000000000000000000000000000000000000000 | 100011 | 35      |

| 000000000000000000000000000000000000000 | 100100 | 36      |

| 000000000000000000000000000000000000000 | 100101 | 37      |

|                                         |        |         |

| 001000000000000000000000000000000000000 | 110101 | 53      |

| 010000000000000000000000000000000000000 | 110110 | 54      |

| 100000000000000000000000000000000000000 | 110111 | 55      |

#### Table 4.3

Now that both the indexes are ready to be compared, a **comparator** on  $log_2(N_{m_i})$  bits decides which is the relationship between the indexes  $n_A$  and  $n_B$ .

This third part uses  $2 \cdot N_{m_i}$  subtractors and equality comparator, 2 encoders  $N_{m_i} - to - \log_2(N_{m_i})$  and one comparator on  $\log_2(N_{m_i})$  bits. At the end of this path the results, the 3 bits that identifies respectively  $n_A > n_B$ ,  $n_A < n_B$  and  $n_A = n_B$ , are stored in 3 final registers of 1 bit.

Since the last step is the selection of the result, it is used a multiplexer 2 - to - 1 which takes as inputs the 3 bits associated to the last residue and indexes comparison, but the selection signal is due to the control unit and depends on the  $n_A = n_B$  result. This operation needs to delay the output of one clock cycle thanks to 3 register of 1 bit in which the 3 output signals that decides if A > B, A < B or A = B are stored.

| Algorithm<br>part | Number of<br>elements | Element                  | Number of<br>Bits                |

|-------------------|-----------------------|--------------------------|----------------------------------|

| First             | 2                     | Decoder                  | n+1 - to - 3n + 1                |

| part              | 1                     | Comparator               | n+1                              |

| Second            | 2                     | Subtractor               | 3n + 1                           |

| part              | $N_{m_i}$             | Fake-multiplier          | 3n + 1                           |

|                   | $2 \cdot N_{m_i}$     | Subtractor               | 3n + 1                           |

| Third             | $2 \cdot N_{m_i}$     | Zero check               | 3n + 1                           |

| part              | 2                     | Encoder                  | $N_{m_i} - to - \log_2(N_{m_i})$ |

| part              | 1                     | Comparator               | $log_2(N_{m_i})$                 |

|                   | 1                     | Multiplexer $2 - to - 1$ | 3                                |

| Total             | $4 + 2 \cdot N_{m_i}$ | Register                 | 3n + 1                           |

| registers         | 9                     | Register                 | 1                                |

In Table 4.4 are reported all the units used in this datapath, considering the modular operators.

#### Table 4.4

Since the components are too wide, it was not possible to generate the Golden model with n = 8.

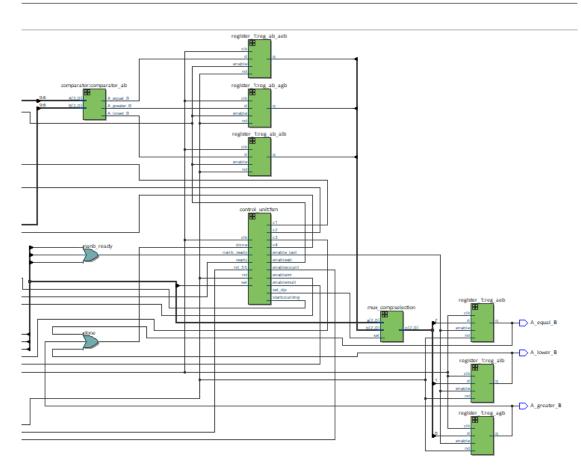

#### 4.1.2 Control Unit

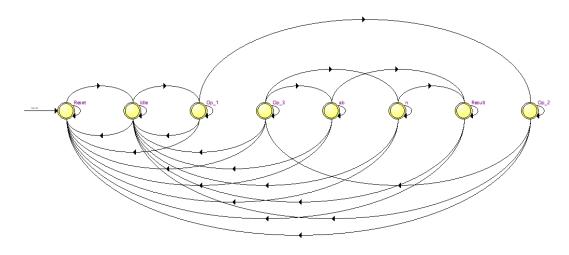

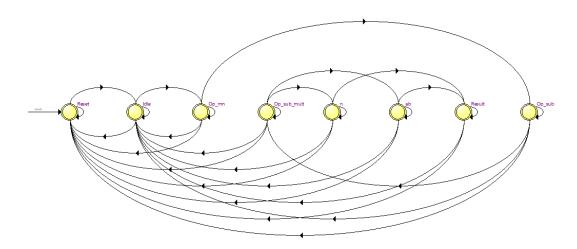

The *control unit* is formed by 8 states:

- 1. **RESET** if the general *reset* is asserted;

- 2. **IDLE** when the inputs are awaited;

- 3. **OP\_1** to enable the registers and the operations related to the *first part* (enabling the two decoders and the  $KN_{m_n}^{A_{RNS}}$  and  $KN_{m_n}^{B_{RNS}}$  registers and the output of the comparison between  $a_n$  and  $b_n$  ones). The system gets in this state if all the inputs are ready to be processed;

- 4. **OP\_2** to enable the registers related to the *second part* (the  $A_{m_n}$  and  $B_{m_n}$  ones and the multiplication results). The system gets in this state if nothing in the previous step has changed;

- 5. **OP\_3** to enable the registers related to the *third part* (the registers of the comparison between the indexes  $n_A$  and  $n_B$ ). The system gets in this state if nothing in the previous step has changed;

- 6. **ab** to correctly select the outputs related to the first comparison. The system gets in this state if the last comparison is over and if the signal related to  $n_A = n_B$  is asserted;

- 7. **n** to correctly select the outputs related to the last comparison. The system gets in this state if the last comparison is over and if the signal related to  $n_A = n_B$  is negated;

- 8. **Result** the output is available and are enabled the 3 registers related to the result (the ones associated to the relationship between the inputs). The system gets to this state when one of the last output signals is asserted and thanks to a proper signal announces the end of operation.

The control unit scheme is reported in Figure 4.8.

Figure 4.8: Golden Model's Finite State Machine.

In Table 4.5 are reported both the signals in input and output and is described their function and their computation.

| Signal      | Input/Output | Significance                     |

|-------------|--------------|----------------------------------|

|             |              | The general <b>Reset</b>         |

| rst         | Input        | is asserted: the system is       |

|             |              | resetted                         |

| noodu       | Input        | The inputs signal are            |

| ready       | Input        | ready to be analyzed.            |

|             |              | When the both indexes            |

|             |              | have been analyzed and           |

| nanb_ready  | Input        | their relation has               |

|             |              | been evaluated,                  |

|             |              | this signal is asserted          |

| 1           | T            | The operation is ended:          |

| done        | Input        | the result has been computed     |

|             |              | This signal is asserted          |

|             |              | only if the two indexes          |

|             | Input        | $n_A$ and $n_B$ are equal        |

| sel         |              | and allows to step in            |

|             |              | one of the states                |

|             |              | <b>ab</b> or <b>n</b> .          |

| onchla 1    | Output       | The registers related to         |

| enable_1    | Output       | the first part are enabled.      |

| anabla 0    | Output       | The registers related to         |

| enable_2    | Output       | the second part are enabled.     |

| anable 2    | Output       | The registers related to         |

| enable_3    | Output       | the third part are enabled.      |

|             |              | It is the multiplexer' selection |

|             |              | signal deciding if the           |

| sel_dp      | Output       | output depends on the            |

|             | 1            | indexes' comparison or the       |

|             |              | last residue.                    |

|             |              | It enables the last registers    |

| anabla last | Output       | associated to the result         |

| enable_last | Output       | and it is asserted only          |

|             |              | in the <b>Result</b> ' state.    |

Table 4.5

## 4.2 Resource sharing

The *Resource sharing* design is expected to be the smallest and slowest. In this chapter its architecture is described and analyzed. This paragraph is divided as the Golden model one, but the main components are not described since they are the same used in the previous design and so they have been already explained.

#### 4.2.1 Datapath

The first part is related to the generation of the zeroing constants and the comparison between the two residues associated to the greatest modulus.

Since the usage of decoders is helping us in the zeroing constants' evaluation, this first part is unchanged with respect of the Golden Model design. Its RTL structure is the same reported in Figure 4.5 and to achieve those first results are needed only **two decoders** of n+1 – to – 3n+1 bits and a n+1 bits **comparator** to evaluate the relation between the inputs'  $m_n$ -th residues. Also, two registers on 3n + 1 bits and three single bit registers are needed.

The second part is designated to compute the multiples  $A_{m_n}$  and  $B_{m_n}$  and the first result of the multiplication by the RNS constant [0, 1, 2]. Reusing the resources implies that one multiplication at time is performed, so only the very first one is performed in this cycle obtaining that only **two subtractors** and **one circular shift** are used together with another component that generates all the values included in the interval  $[0, N_{m_i})$ . This latter component is a modular **counter** because it is formed by 3 counters that works on n + 1, n and n bits respectively simultaneously to generate the 3n + 1 output. Observing the sequence of the RNS numbers, indeed, it is possible to write each number by always adding 1 and ensuring that each counter reaches its associated maximum value which is  $m_i - 1$ . This feature is obtained by generating an internal reset to ensure that when the counter gets to  $m_i - 1$  it is restarted. In Table 4.6 are reported the maximum values reached by each modulus for all the n considered in order to make clear that the internal reset is applied only to the  $2^n - 1$  and  $2^n + 1$  moduli, since the  $2^n$  one has its internal reset generated by its overflow.

|       |     | $2^n - 1$ |     | $2^n$    |     | $2^n + 1$ |

|-------|-----|-----------|-----|----------|-----|-----------|

| n = 3 | 6   | 110       | 7   | 111      | 8   | 1000      |