## POLITECNICO DI TORINO

Master's Degree in ELECTRONICS ENGINEERING

Master's Degree Thesis

## FIRMWARE DESIGN OF 3-PHASE GRID-TIED CONVERTER

Supervisors Prof. Gianmario PELLEGRINO Dott. Fausto STELLA Candidate Muhammad Umar SHARIF

**APRIL 2022**

## Summary

The grid-connected systems are being developed very fast and are now in operation worldwide. As an important source of distributed generation the systems need to comply with standard requirements in order to ensure the safety and the seamless transfer of the electrical energy to the grid. But the converters has highlighted the some problems specifically of harmonic interaction between converters and the grid. Because, electrical grids are complex and dynamic systems affected by multiple factors such as continuous connection of loads and an abruptly disconnection of loads, disturbances and resonances resulting from the harmonic currents flowing through the lines, lightning strikes. This thesis aims to implement the three phase Grid-tied converter and test at different loads. In the meanwhile, by monitoring continuously the grid parameters in order to make sure that grid is suitable for normal power converter operation. The test bench behaves like a Boost-Converter which is connected with grid at normal grid dedicated voltage and performs accordingly at variable loads. The designed system can also be use for lab activities by students of Electrical Engineering.

## Acknowledgements

I would like to thanks first and foremost the God Almighty for His endless grace. A debt of gratitude is also owed to my advisor Fausto Stella and supervisor Gianmario Pellegrino for their continuous support and help whenever I stuck in a problem or had any question about my project. They always helped me in this endeavour. Without their active guidance, help, cooperation and encouragement, I would not have made headway in this project.

I also acknowledge with a deep sense of reverence, my gratitude towards my parents and especially to my late father whom I lost in 2019. I wish that he could see me today. I extend my gratitude to my family and my friends for providing me endless support and encouragement throughout my study period. This milestone would never be accomplished without their support.

Thank you all!

Muhammad Umar SHARIF

# **Table of Contents**

| st of                | Tables                                                                                                                        | VII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| List of Figures VIII |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Intr                 | oduction                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 1.1                  | Future Scope of Grid Connected Converters                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 1.2                  | Dynamic Problems in Grid monitoring and Grid Synchronization .                                                                | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 1.3                  | Standards Requirements for Grid-Tied Converters                                                                               | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 1.4                  | Literature Review on Converter                                                                                                | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                      | 1.4.1 Converter General Description and Schematic                                                                             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                      | 1.4.2 Micro controller STM32                                                                                                  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                      | 1.4.3 CPLD                                                                                                                    | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 1.4.4 Gate Drivers                                                                                                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 1.4.5 MOSFET's                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Pre                  | liminary Tests on Converter                                                                                                   | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2.1                  | PWM Control of Converter                                                                                                      | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2.2                  | Execution of Finite State Machine on Micro-controller                                                                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2.3                  | LCL Filter Design Analysis                                                                                                    | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 2.3.1 Software Modelling                                                                                                      | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2.4                  | Converter Configuration with Grid                                                                                             | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 2.4.1 Calculation of Grid Impedance                                                                                           | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 2.4.2 Test-Case for Short-Circuit Test                                                                                        | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Con                  | verter Model and Control Scheme                                                                                               | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 3.1                  | General Converter Structure                                                                                                   | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 3.1.1 Active Front End                                                                                                        | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 3.2                  | Topology under Test                                                                                                           | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 3.2.1 Converter's Main Specifications                                                                                         | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | 3.2.2 Converter's Configuration with Grid                                                                                     | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 3.3                  | Converter Control Scheme                                                                                                      | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | <b>St of</b><br><b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4<br><b>Pre</b><br>2.1<br>2.2<br>2.3<br>2.4<br><b>Con</b><br>3.1<br>3.2 | Introduction         1.1       Future Scope of Grid Connected Converters         1.2       Dynamic Problems in Grid monitoring and Grid Synchronization         1.3       Standards Requirements for Grid-Tied Converters         1.4       Literature Review on Converter         1.4.1       Converter General Description and Schematic         1.4.2       Micro controller STM32         1.4.3       CPLD         1.4.4       Gate Drivers         1.4.5       MOSFET's         1.4.5       MOSFET's         1.4.5       MOSFET's         2.1       PWM Control of Converter         2.2       Execution of Finite State Machine on Micro-controller         2.3       LCL Filter Design Analysis         2.3.1       Software Modelling         2.4.1       Calculation of Grid Impedance         2.4.2       Test-Case for Short-Circuit Test         2.4.2       Test-Case for Short-Circuit Test         3.1.1       Active Front End         3.2.1       Converter's Main Specifications         3.2.2       Converter's Configuration with Grid |  |

|    | 3.4    | 4 Grid Synchronization in Three-Phase Power Converters 40                  |    |

|----|--------|----------------------------------------------------------------------------|----|

|    |        | 3.4.1 Modeling under abc Reference Frame                                   | 41 |

|    |        | 3.4.2 Coordinates Transformation from abc to $\alpha\beta$ Reference Frame | 42 |

|    |        | 3.4.3 Modeling under dq Reference Frame                                    | 43 |

|    | 3.5    | Techniques for Grid Synchronization                                        | 44 |

|    |        | 3.5.1 Phase-Locked Loop                                                    | 44 |

|    | 3.6    | Control Design of $3-\phi$ AFE (PI Controller)                             | 46 |

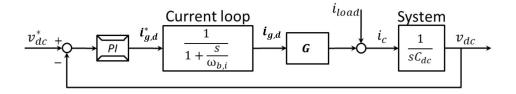

|    |        | 3.6.1 Design of Controller for AFE - Inner Current Loop                    | 47 |

|    |        | 3.6.2 Control of AFE - Outer Voltage Loop (Vdc)                            | 51 |

|    | 3.7    | Hardware Setup                                                             | 52 |

| 4  | Con    | clusions                                                                   | 54 |

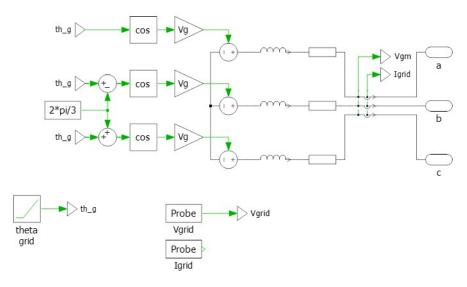

|    | 4.1    | Simulation Validation using PLECS                                          | 54 |

|    | 4.2    | Experimental Results                                                       | 57 |

|    | 4.3    | Conclusion                                                                 | 74 |

|    | 4.4    | Future Works                                                               | 74 |

| Bi | ibliog | graphy                                                                     | 75 |

## List of Tables

| 2.1 | MATLAB based LCL Filter Specifications                                                                                                                                           |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2 | Under-Test Transformer's Parameters                                                                                                                                              |

| 2.3 | Short-Circuit Test Results                                                                                                                                                       |

| 3.1 | Converter's Specifications                                                                                                                                                       |

| 3.2 | Calibration for Current Control                                                                                                                                                  |

| 3.3 | Calibration for Voltage Control                                                                                                                                                  |

| 4.1 | Gains for Current Control Loop                                                                                                                                                   |

| 4.2 | Gains for Current Control Loop for $f_{sw,i} = 10 \text{ kHz} \dots \dots \dots 64$                                                                                              |

| 4.3 | Gains for Current Control Loop for $f_{sw,i} = 15 \text{ kHz} \dots \dots$ |

| 4.4 | Gains for Current Control Loop for $f_{sw,i} = 20 \text{ kHz} \dots \dots \dots 69$                                                                                              |

|     |                                                                                                                                                                                  |

# List of Figures

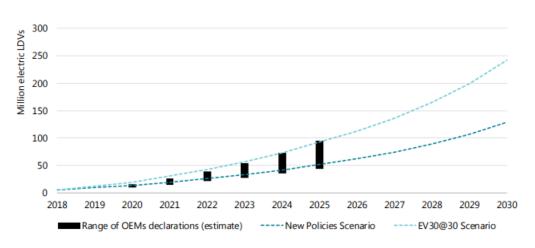

| 1.1        | Global Electrical Car Stock                                                        | 2  |

|------------|------------------------------------------------------------------------------------|----|

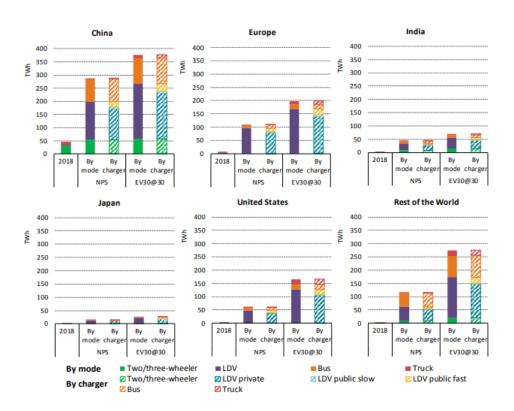

| 1.2        | Demand of EV's Electricity by Region, Mode and charger                             | 3  |

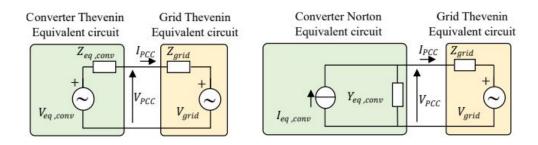

| 1.3        | Norton and Thevenin Equivalent Circuit of Grid                                     | 5  |

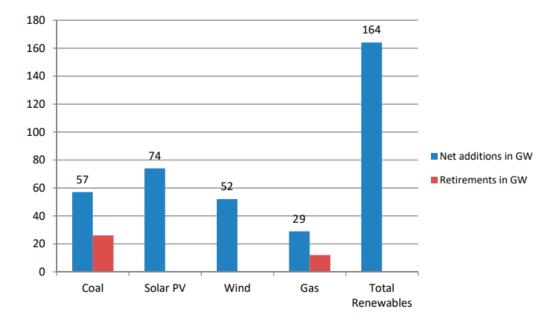

| 1.4        | Total Energy capacity in 2016                                                      | 6  |

| 1.5        | PCB Circuit                                                                        | 8  |

| 1.6        | MCU STM32 on Converter                                                             | 9  |

| 1.7        | Flash Memory Interface Connection inside System Architecture                       | 12 |

| 1.8        | CPLD on PCB                                                                        | 13 |

| 1.9        | Gate Driver on Converter                                                           | 14 |

| 1.10       | Gate Driver Control Architecture                                                   | 14 |

| 1.11       | MOSFET's placement on Converter                                                    | 16 |

| 0.1        |                                                                                    | 10 |

| 2.1        | Finite State Machine Implementation Loop                                           | 18 |

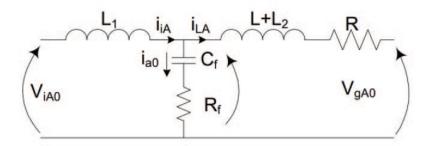

| 2.2        | LCL Filter Configuration with Grid and Converter                                   | 20 |

| 2.3        | Per-Phase Configuration of LCL Filter                                              | 20 |

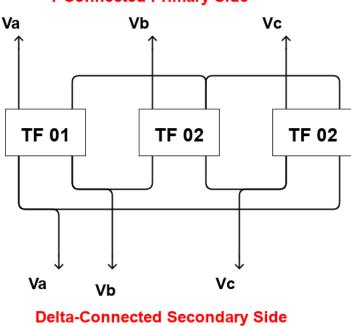

| 2.4        | Transformer's Y- $\triangle$ Configuration as a Grid $\ldots \ldots \ldots \ldots$ | 23 |

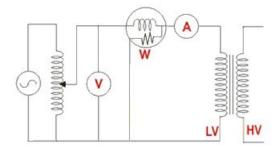

| 2.5        | Open-Circuit Test Configuration                                                    | 24 |

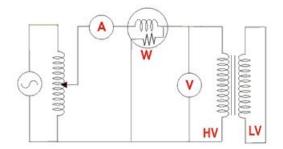

| 2.6        | Short-Circuit Test Configuration                                                   | 25 |

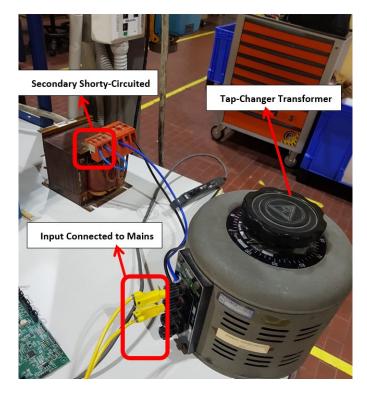

| 2.7        | Short-Circuit Test Configuration with Tap-Changing Transformer .                   | 26 |

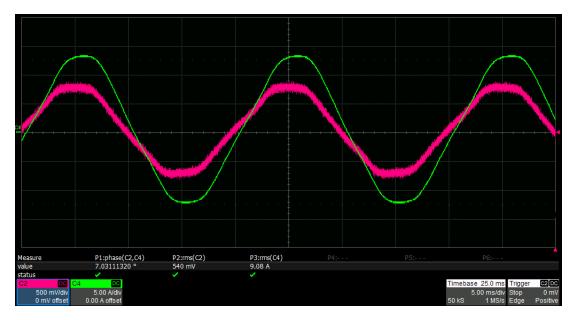

| 2.8        | Test 01 Result on Oscilloscope                                                     | 27 |

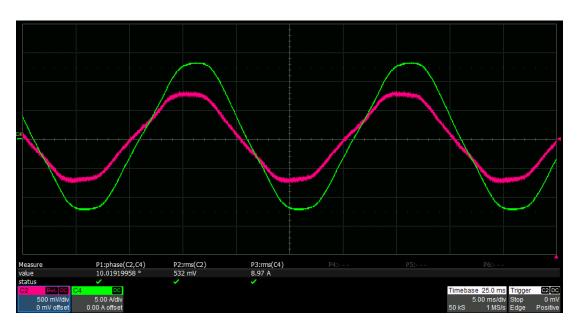

| 2.9        | Test 02 Result on Oscilloscope                                                     | 28 |

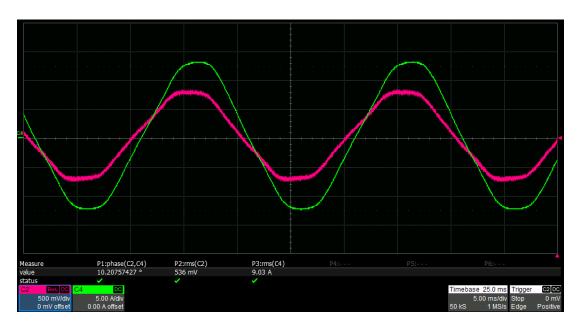

| 2.10       | Test 03 Result on Oscilloscope                                                     | 29 |

| 2.11       | Test 04 Result on Oscilloscope                                                     | 30 |

| <b>9</b> 1 | Companyal Companyation Strengthered                                                | าก |

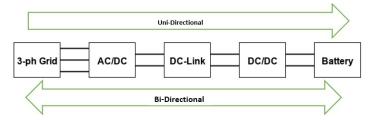

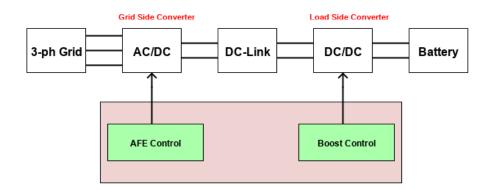

| 3.1        | General Converter Structure                                                        | 32 |

| 3.2        | Converter Block Scheme with AFE                                                    | 33 |

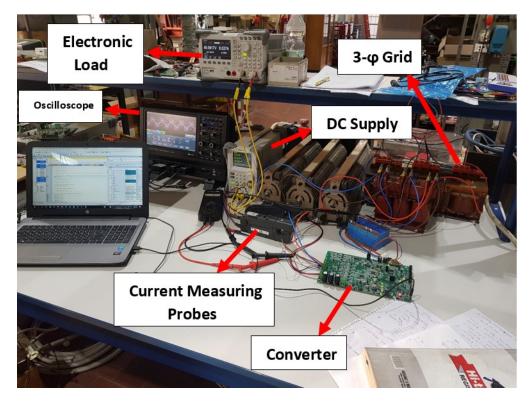

| 3.3        | Complete Hardware Setup                                                            | 34 |

| 3.4        | Block Diagram of Complete System                                                   | 35 |

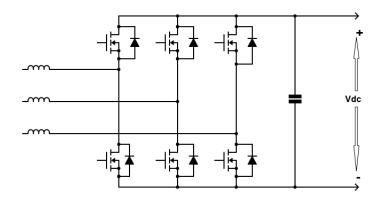

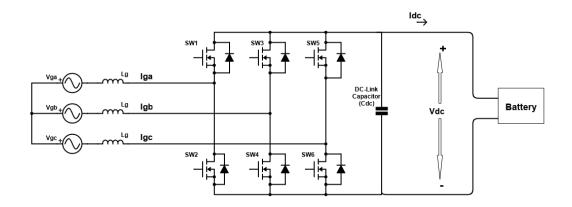

| 3.5        | 2 Levels Three-Phase Converter Topology                                            | 35 |

| 3.6        | Structure of 3-phase Grid-Connected Converter                                      | 37 |

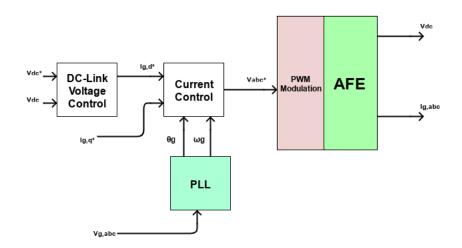

| 3.7        | Converter Control Overview                                                         | 38 |

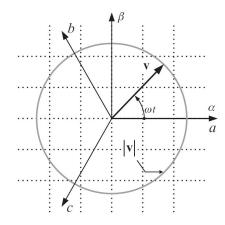

| 3.8          | 3-Phase Voltage Vector under Ideal conditions                                                          | 39              |

|--------------|--------------------------------------------------------------------------------------------------------|-----------------|

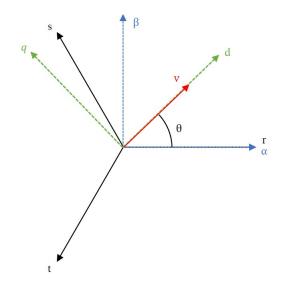

| 3.9          | Positioning of the dq-axis on Rotating Reference Frames                                                | 39              |

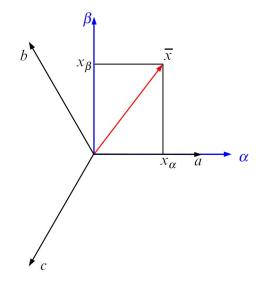

| 3.10         | Coordinate Transformation from 3- $\phi$ static abc to 2- $\phi$ static $\alpha\beta$ reference frame. | 43              |

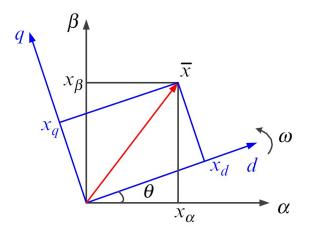

| 3.11         | Coordinate Transformation from 3- $\phi$ stationary $\alpha\beta$ to rotating dq reference frame.      | 44              |

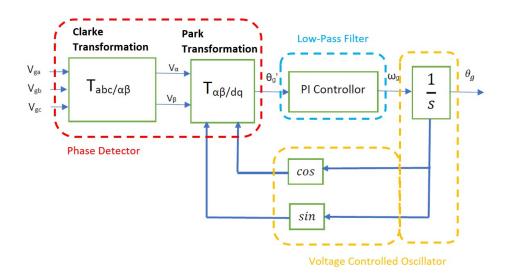

| 3.12         | Block Diagram for Grid Synchronization of SRF-PLL                                                      | 45              |

| 3.13         |                                                                                                        | 46              |

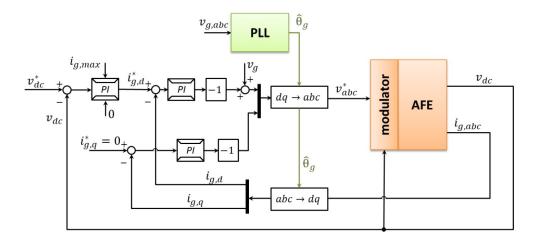

|              | Complete Block Schematic for Converter Control                                                         | 47              |

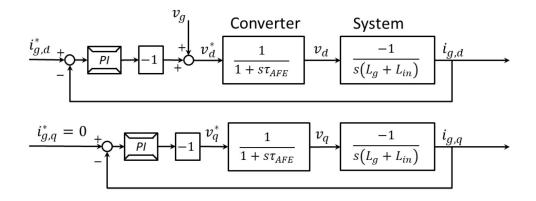

|              | Complete Block Architecture of Inner Current Loops                                                     | 48              |

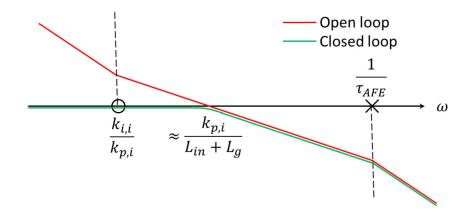

|              | Bode Plot for Open-Loop and Closed-Loop Transfer Functions                                             | 50              |

|              | Voltage Control Loop                                                                                   | 51              |

|              | Complete Hardware Setup                                                                                | 53              |

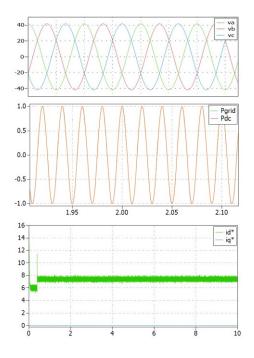

| 4.1          | PLECS Schematic of Grid Design                                                                         | 55              |

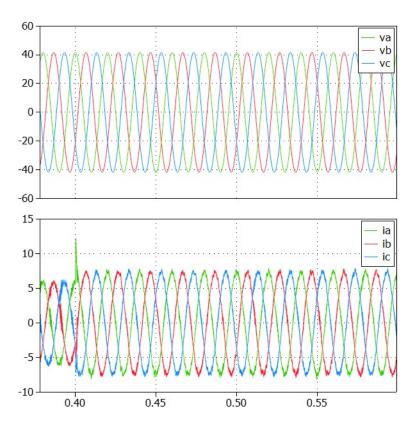

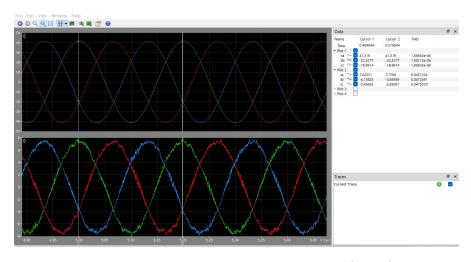

| 4.2          | Transient behaviour of Current during Voltage Step in 3- $\Phi$ Frame $% \Phi$ .                       | 55              |

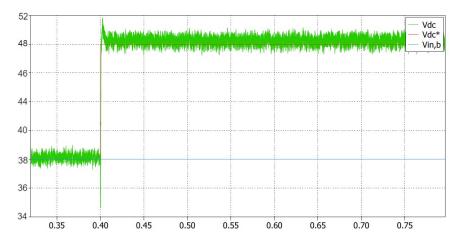

| 4.3          | Validation of Transient behaviour of DC-Link Voltage using PLECS                                       | 56              |

| 4.4          | Validation of Total Harmonic Distortion (THD) at 10 kHz using PLECS                                    | 56              |

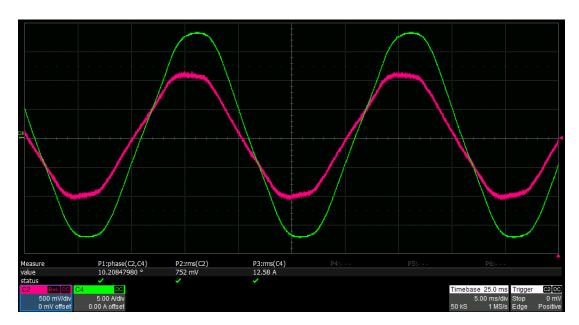

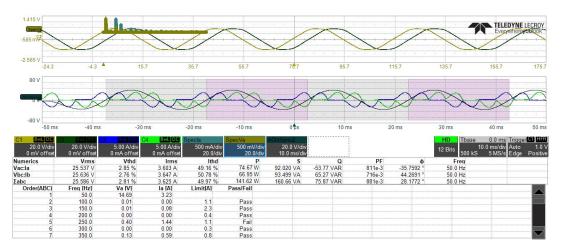

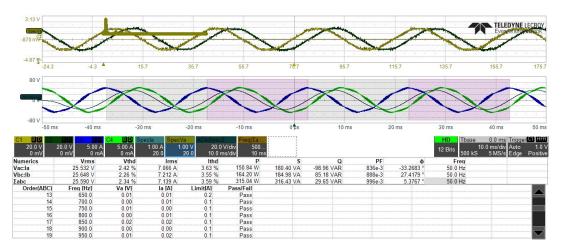

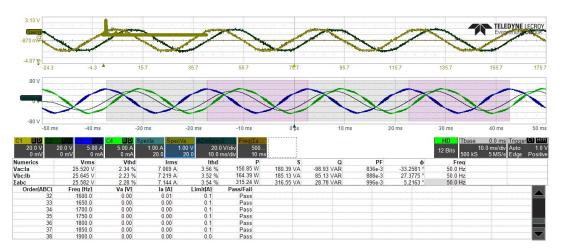

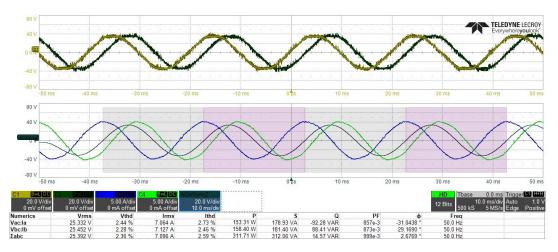

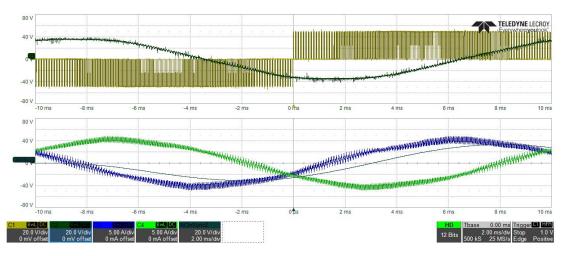

| 4.5          | Converter results under 8kHz Switching Frequency                                                       | $50 \\ 57$      |

| 4.5<br>4.6   | Converter results under 8kHz Switching Frequency before enabling                                       | 57              |

| 4.0          | the Harmonics                                                                                          | 58              |

| 4.7          | Converter results under 8kHz Switching Frequency after enabling                                        | 58              |

| 1.0          | the Harmonics                                                                                          | $\frac{58}{59}$ |

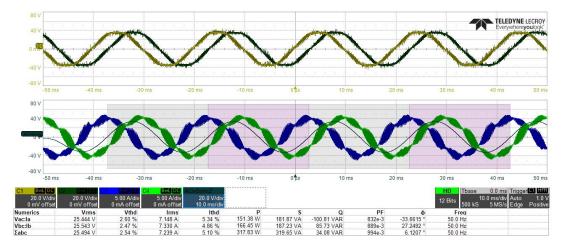

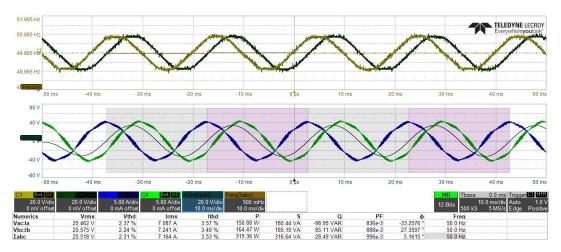

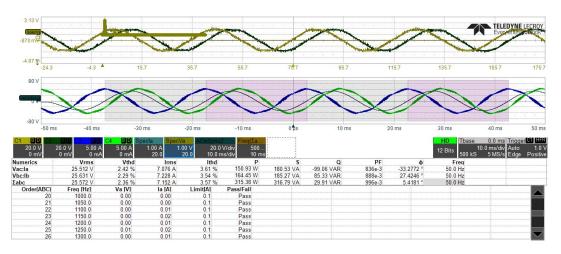

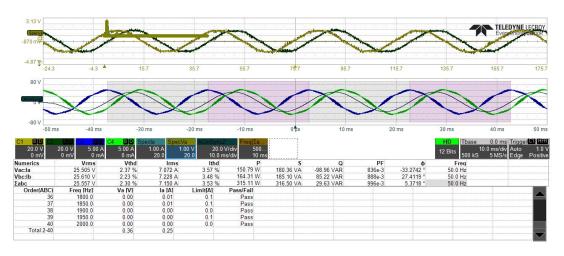

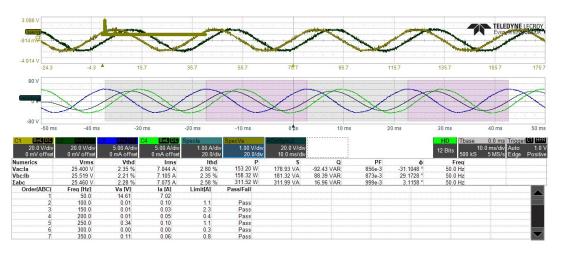

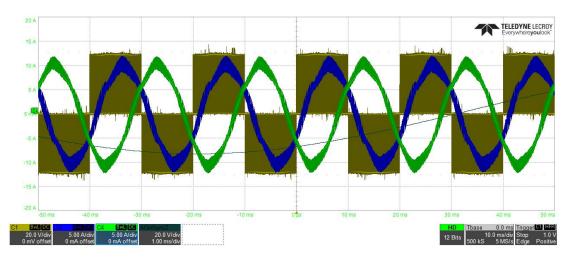

| $4.8 \\ 4.9$ | Current Control Gains for 8kHz Switching Frequency Converter results under 10kHz Switching Frequency   | 59<br>60        |

| 4.9<br>4.10  | Ŭ - Ŭ                                                                                                  | 00              |

| 4.10         | the Harmonics                                                                                          | 60              |

| 4.11         | Converter results under 10kHz Switching Frequency after enabling                                       |                 |

|              | the Harmonics                                                                                          | 61              |

| 4.12         | Converter results under 10kHz Switching Frequency after enabling the Harmonics                         | 61              |

| 4 13         | Converter results under 10kHz Switching Frequency after enabling                                       | 01              |

| 1.10         | the Harmonics                                                                                          | 62              |

| 4.14         | Converter results under 10kHz Switching Frequency after enabling                                       | 0-              |

|              | the Harmonics                                                                                          | 62              |

| 4.15         | Converter results under 10kHz Switching Frequency after enabling                                       |                 |

|              | the Harmonics                                                                                          | 63              |

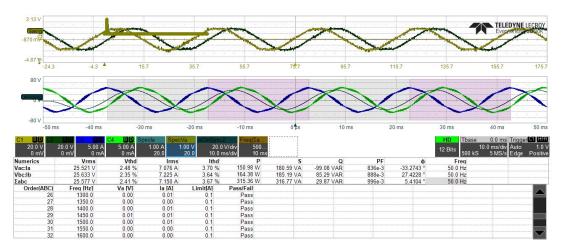

| 4.16         | Converter results under 10kHz Switching Frequency after enabling                                       |                 |

|              | the Harmonics                                                                                          | 63              |

|              |                                                                                                        |                 |

| 4.17 | Converter results under 10kHz Switching Frequency after enabling   |    |

|------|--------------------------------------------------------------------|----|

|      | the Harmonics                                                      | 64 |

| 4.18 | Current Control Gains for 10kHz Switching Frequency                | 65 |

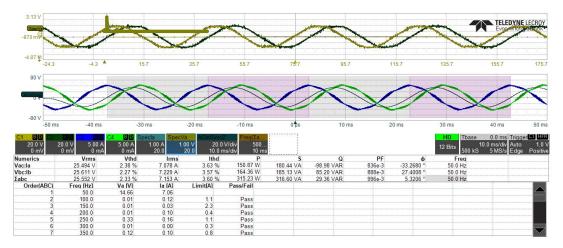

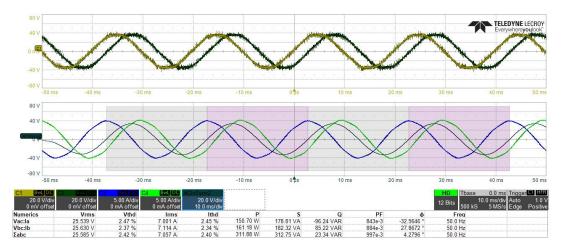

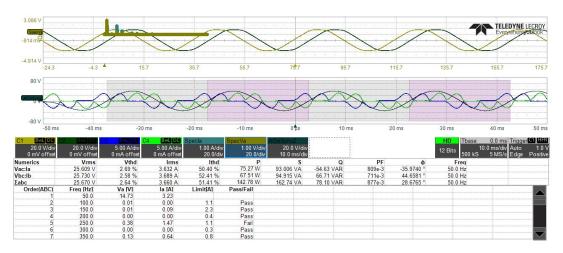

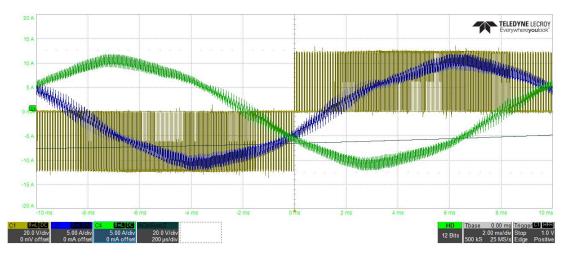

| 4.19 | Converter results under 15kHz Switching Frequency                  | 65 |

| 4.20 | Converter results under 15kHz Switching Frequency after enabling   |    |

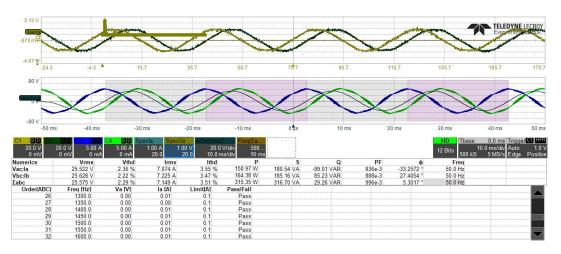

|      | the Harmonics                                                      | 66 |

| 4.21 | Current Control Gains for 15kHz Switching Frequency                | 67 |

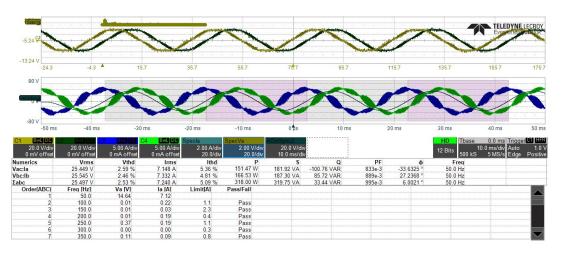

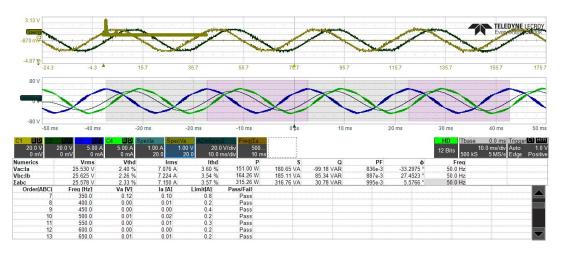

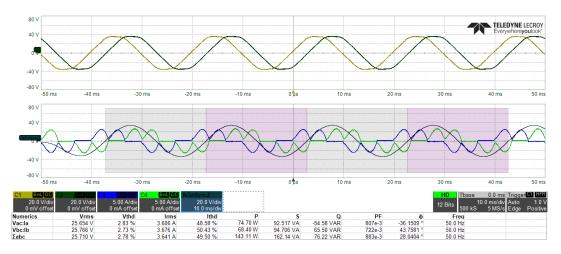

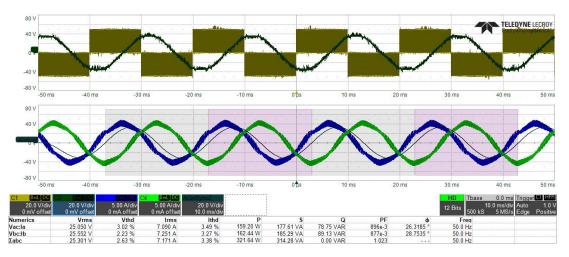

| 4.22 | Converter results under 20kHz Switching Frequency                  | 67 |

| 4.23 | Converter results under 20kHz Switching Frequency before enabling  |    |

|      | the Harmonics                                                      | 68 |

| 4.24 | Converter results under 20kHz Switching Frequency after enabling   |    |

|      | the Harmonics                                                      | 68 |

| 4.25 | Current Control Gains for 20kHz Switching Frequency                | 69 |

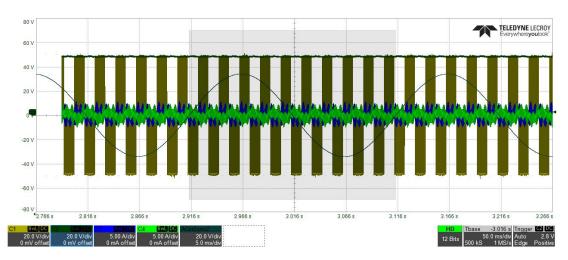

| 4.26 | Converter Output Waveforms at 10 kHz Switching Frequency           | 70 |

| 4.27 | Converter PWM Output Waveform at 10 kHz Switching Frequency        | 70 |

| 4.28 | Converter Current Waveform w.r.t to PWM Output at 10 kHz           |    |

|      | Switching Frequency                                                | 71 |

| 4.29 | Converter Current Waveform w.r.t to PWM Output at 10 kHz           |    |

|      | Switching Frequency                                                | 71 |

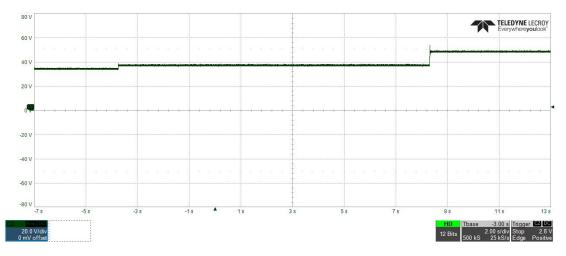

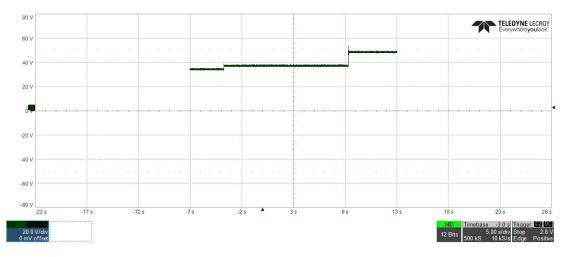

| 4.30 | Transient Response of Vdc triggering at 48V                        | 72 |

| 4.31 | Transient Response of Vdc triggering at 48V                        | 72 |

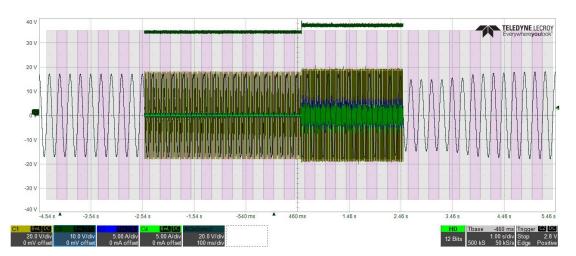

|      | Transient Response of Vdc triggering at 48V w.r.t to PWM at Output | 73 |

| 4.33 | Transient Response of Vdc triggering at 48V w.r.t PWM at Output    | 73 |

# Chapter 1

## Introduction

#### **1.1** Future Scope of Grid Connected Converters

It has been seen that in past few decades, the use and dependency on renewable energies has been significantly increased and all future predictions are giving a strong sign of more dependency on renewable energies in near future.

There is an increase in the trend of power converters due to an increase in the reliability of renewable energy resources. These power converters help these resources to easily connect with the grid lines.

As the field of power electronics is expanding its horizon, there is a great development in the power converters on the side of EV's battery charges. In the coming future the electric mobility is continue to increases exponentially. In 2018, the selling of electric car increases 5.1 million and increases day by day. China is become the largest buyer of these electric car's. US and Europe are on the second and third tier.

Electric cars basically save more energy as compare to the oil driven electric cars. Increasing demand in the electric car's basically have a great impact on demand of the oil use products. In the recent stock exchange, the EV's stock is estimated to escape 127 million tonnes of oil equivalent according to the New Policies Scenario.

The electrification in car market result in a rapid growth of automotive battery manufacturing capacity. The reason behind is the maximum number of electrical car sold as compare to the other modes of car. This electrification result in reducing the cost of automotive battery pack. EV's play a pivotal role to facilitate the availability of energy storage at a low cost. EV's also play an instrumental role in the future for the cleaner energy system.

In the case of power systems, the EVs are now becoming the integral part as compare to the past due to its advancement. The incremental need for the peak power generation and transmission capacity can be achieved when we run EVs drive

Figure 1.1: Global Electrical Car Stock

at uncontrolled charging mode. These EVs drives can greatly impact our power system total annual electricity demand, daily charging pattern on load profiles and location of power levels utilized under charging.

The recent development in Electric batteries greatly influence the road transport which are running on oil. The total global EVs stock is approximated nearly 127 million of oil equivalent in 2030. The product EV30@30 will move toward 215 MToe of oil product in 2030.

The electricity demand for the global EV fleet will surpass 640 TWH in 2030 in the figure below according the New Policies Scenario. In 2018, it was approximately 58 TWH but it is exponentially increase altogether. Its equal to final consumption of France and Spain in 2016. In the EV30@30 Scenario, the larger volume of the global EV fleet leads to 1 110 TWH of electricity demand in 2030, nearly double the amount of the New Policies Scenario. [1]

The light-duty vehicles (LDV's) are growing its user as compare to the other modes of wheeler's in 2020. The expert predicts that in 2030 LDV's will get 60% of total vehicles as compare to buses 26%, two wheeler's 12% and trucks 3%. So, LDV's in the coming future will be use by everyone throughout the world.

EV's can play its part in the flexibility of Power System when it is used in a controllable mode. When it is operated in this mode it has a very good results on the variable renewable energy, power generation mix and grid stability issues. Here are following features of EV's are as follow:

- In a power system, the load profile can be reduced by using the EV's which can control the charging patterns to occur with low demand periods.

- In a power system, when utilize EV's it can give us the feature of ultra-short

Figure 1.2: Demand of EV's Electricity by Region, Mode and charger

term demand response and provide use very fast and precise response to control signals.

• The energy store in EV's can use for multi-purpose other than providing energy to the locomotive.

#### 1.2 Dynamic Problems in Grid monitoring and Grid Synchronization

As the renewable energy, distribution generation resources and EV charging stations are evolving with the time, the importance of power converters is also simultaneously increases. But there is a downside to use the converter due to harmonic interactions between multiple converters. The drawback of these harmonics is that they bring instability in the system and produces resonances which affect the quality of power in the grid. When these sort of oscillations and harmonics produced in such a grid which is connected of multiple converters so it will damage the grid due to the unbalance voltage and current in result of those oscillations. So we have to rectify this problem on bus system level.

In a year 1995, due to these high frequency switching oscillations it damages the new generation trains lines started in Zurich. Similarly, its happen in Swiss Railway when they interchange the old locomotive design with the new high switching frequency design, the trains automatically stop due to increase strength of the oscillation produced on those locomotive. So on the side the old design was far better than this modern design because the old design produces less oscillation in the system.

Due to this evolving issue, the Italian Transmission Service Operator(TSO) Terna is deploying the dynamic model of machines which should be used in the plants. Every wind or solar plant owner must interact with Terna to show the simulation of working of their plant under following conditions:[2]

- Steady-state condition.

- Transient state condition.

- Both electrically and magnetically steady-state condition.

- Steady-state condition connected with grid under the influence of harmonics.

We must have to do the literature review of dynamic interaction of power converter with the transmission lines to have complete insight of the connection. The analysis can be performing through different methods so we have to select that one which is best suited for our model. Power electronic systems are non-linear due to these high frequency switching harmonics and oscillation produced in the practical grid systems. There are some technical points that we have to check when we are doing the literature review which are follow as:

- We have to study the linear state space model in the control system in which analysis is done through eigenvalue. In the eigenvalue analysis the system is divide into two blocks one is the hardware and other is a software block which are connected with each other through Component Connection Method (CCM). This method helps us to change the parameter of a single block without changing the parameter of the whole single block. We can also see the result of each block and change the setting of each block according to our desire result. The participation factors are used to identify zero and pole to address the dynamic interaction between the power converters. It provides us the analytical modelling but require much more information of both the block hardware and software which are not quite available in commercials systems.

- We utilize Nyquist criterion to study the frequency domain analysis on the admittance model of the converters. In this model we can represent each block

of converter with the Thevenin or a Norton equivalent model which is show in the figure below. There are following advantages of the method:

- i The integration of power converter with grid will be simple because all the converter changes into generator-admittance circuits.

- ii We can analyze the negative resistance behavior in our controllers by the help of bode diagram.

- iii Equivalent admittance can be achieved using measurement so black box method is suited for commercial use of the converters.

Figure 1.3: Norton and Thevenin Equivalent Circuit of Grid

[3]

#### 1.3 Standards Requirements for Grid-Tied Converters

Power generating system are rapidly growing with the time and we have to connect these sources to our grid. For instance, the energy generated by the solar PV cell must be processed and filter through an inverter before we connect the energy to our grid system. So, a converter is placed between the power generating system and the grid system which is responsible for the proper connection of energy. As there is an advancement in the field of power electronics, it become necessary for us to utilize the renewable resources energies to connect with our small and medium grid level system. Especially the solar and wind energy sources are very cheap and it's playing to be competitive sources of energy in comparison with fossil fuels so converter plays an important role for the connection of these sort of energy resources with transmission line.

Figure 1.4: Total Energy capacity in 2016

From the above graph you can see that the Solar PV cell is producing more energy that the remaining renewable resources. We can analyze from the growing trend of producing energy from renewable resource, it become very vital for us to produces the converter circuit which would add this energy to our current grid system. There are following Standard requirement that we have to follow in order to connect it with the grid which are as follows:[2]

- Less cost at the power converter level.

- Converter should be reliable.

- Output harmonics should be minimum.

- Reduced switch to be deploy in integration with the grid.

- Continuity in the input supply should be required.

- Maximum Power Point Tracking (MPPT) must be used to find the maximum operating power point in case of solar system.

The power converters are very sensitive to harmonics and oscillation produced in the transmission line under abnormal condition which can trip the protection system and damage our power converter or utilities other services. At the coupling stage, power converter connects the renewable energy with the grid system and it generally reduced the voltage abnormality and other undesired effects. These voltage oscillations and harmonics should be detected by both the synchronization system and power converts so to have smooth connection between the two source of energies.

Three phase voltage converter grid synchronization also used advance detection schemes which basically reject the higher order harmonics in the voltage and current and identify the sequence of voltage vector in a very quick and accurate way. Flexible Alternating Current Transmission System (FACTS) basically used STATCOM (Static Synchronous Compensator) and SSSC (Static Series Synchronous Compensator) is also used to detect the harmonics and remove it from the transmission line and can help to inject or reject the active and reactive power in the transmission line according to our desire requirements.

#### 1.4 Literature Review on Converter

#### 1.4.1 Converter General Description and Schematic

This converter is designed by the department of Electrical Engineering of Politecnico Di Torino. This converter has the ability to work for motor drive applications or also as the Grid-Tied converter and or as an On-Board Battery charger. The main goal of design of this thesis was to be a operate this multi-purpose converter which can mold itself according to different applications as a Grid-connected converter. One of the main feature of this converter that it would sustain with least amount of THD (Total Harmonic Distortion) when we utilize in above mentioned applications. It increases the efficiency of performance when we integrate this circuit with those applications. There are a number of components which are being used on this converter and we can discuss those component below:.

The following Fig. 1.5 shows the complete PCB structure of the converter which is under test.

Figure 1.5: PCB Circuit

There are number of components which are being used on this converter and some of those components explained below and there are follow as:

#### 1.4.2 Micro controller STM32

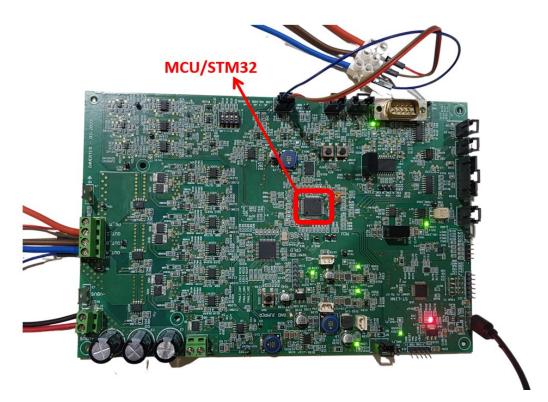

The central unit of any circuit is known as the "Micro-controller". This is an integrated circuit which is operated at 3.3 V, and can be programmed using various software. It is showing in the following Fig. 1.6 as where it is present on the printed Circuit Board (PCB).

Figure 1.6: MCU STM32 on Converter

The chosen micro-controller is part of a family of 32-bit micro controllers, i.e. STM32. The STM32 micro-controllers are characterized by their excellent performance, as well as operation at minimal voltage, and availability of flexible management. The micro-controller used here is called STM32F703RE, which has been developed on the ARM Cortex M processors. Such micro-controllers have certain vital components. The essential parts of this type of micro-controller are following:

- First is the processor of the microcontroller, also called its CPU.

- A volatile memory, known as RAM is required for implementation of operations as well as calculations.

- Flash: non-volatile memory, contains program instructions. Several peripherals including:

- Timers: all digital operations are managed by one or more timers, which they synchronize the inputs (sampling and communication), the execution of the algorithm (calculations) and the execution of commands and monitoring signals (outputs). Furthermore, the timers they can also have the functionality of PWM modulators, generating the commands of the switch, starting from the desired duty cycles, according to the usual method of comparison with a triangular carrier. They can also be used as signals for encoders or as pulse counters

- 4. Analog to Digital Converters (ADC) are used, which have a general conversion time of 20 us. The resolution can be varied between 0 and 12 bit.

- CAN.

The micro-controller is programmed using a method called 'Host-Target programming', in which these are programmed using a PC. In such a case, the PC would correspond to the host, while the micro-controller would correspond to the board. Typically, C++ language can be used for programming purposes. Another code editor that could be used is the KEIL uVision. This consists of a compiler as well as a linker, which enables it to produce a code that could be generated on the micro-controller.

- Program memory (CODE), where the program instructions reside.

- Data memory (SRAM), volatile memory used for program execution.

- Device configuration registers and I/O port contents, described thereafter.

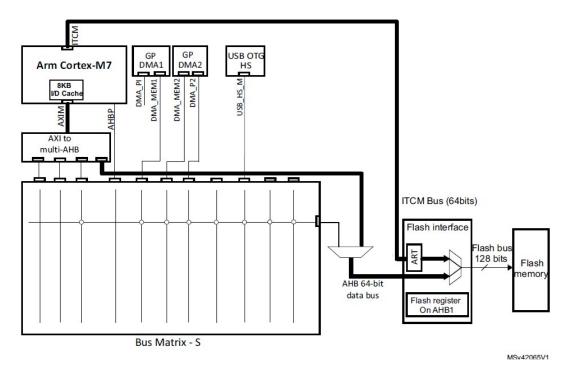

The micro-controller memory consists of 32-bit registers, which include the Program Memory (CODE). This is where the instructions of the program are stored. They also have the Data Memory (SRAM). This is the volatile memory which is utilized during execution of the program. Finally, the Device configuration registers are also present. The code of the machine's control and mapping routine is executed electric, is performed with a frequency of 10 kHz.

As mentioned above, the main peripherals of the micro-controller include the ADC converter, and timers. Now, there are 14 timers with the micro-controller. Out of these, two timers (TIM1 and TIM8) are known as advanced-control timers. TIM1 timers creates the PWM signals. These are sent over to the gate drivers. They then provide drive power for the mosfets. All timers have input as well as output channels, which are utilized in input appears, and hence judge the duration

of impulses of both input and output appears. This helps generate command output. The advantage of the advanced control timers is that they allow generation of complementary PWM commands with dead time insertion. Some of the main features of timers include:

- A 16-bit up down counter.

- A 16-bit pre-scalar. This programmable unit allows slowing the clock by up to 65536 times.

- Input and Output channels.

- PWM generation with saw-tooth (edge) or triangular (Center-aligned)

- Connection of multiple timers and synchronization of external signals.

- Generation of complementary three-phase PWM commands with dead-time, only for timers

- Presence of a repetition counter.

- Interrupt generation, if an underflow or overflow occurs during update event, or in case of a trigger event of a software. Interrupt can also be triggered in the event of input capture, or output appears.

- A compatibility with incremental encoders. Now, while each timer has registers, there are four major ones. These include the counter register, the auto-reload register, the repetition count register, and the pre-scalar register.

The execution of the program therefore consists in the sequential execution of instructions. However, the program execution sequence can be interrupted by a jump of address due to calling a subroutine. In real-time systems like this one case, this happens following an interrupt and the routine to be executed is indicated with Interrupt Service Routine (ISR).

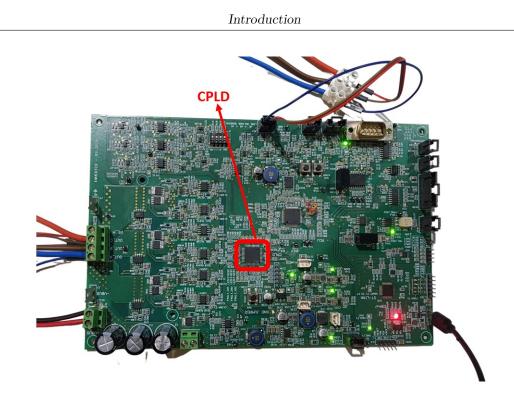

#### 1.4.3 CPLD

A Complex Programmable Logic Device, also known as CPLD, is a logic device which consists of macro-cells as well as totally programmable AND OR arrays. The CPLD is situated on PCB. Much like the micro-controller, the hardware of the CPLD can be configured using appropriate firmware. The CPLD comes into use for monitoring the system if any issue arises during the execution of the code by the microcontroller. The CPLD is used mostly in an educational context, and allows students the required protection in case a faulty programming code is used. In such

Figure 1.7: Flash Memory Interface Connection inside System Architecture

a case, the CPLD comes into play, and through activation of a special protection pin. This allows prevention of damage of the hardware due to implementation of incorrect programming.

Figure 1.8: CPLD on PCB

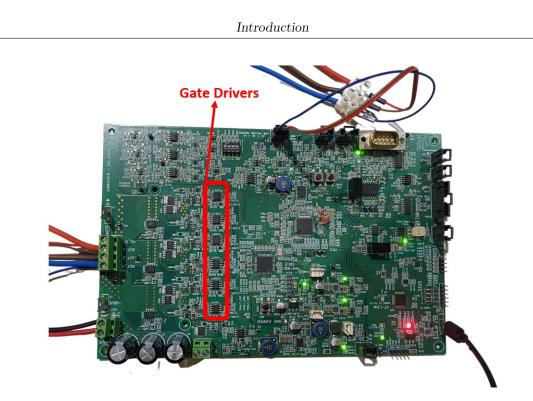

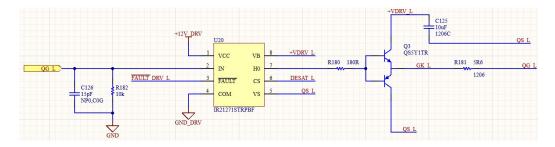

#### 1.4.4 Gate Drivers

Gate drivers are devices that amplify power, by receiving low power input from IC controller, and outputting the relevant high current gate drive which is required for a power drive. They are basically integrated circuits, which are used, in this scenario, to provide drive to the MOSFET's used with the PCB. The PCB contains a total of 7 drivers, which are provided by 12 V power. One of them would control the brake-leg MOSFET, while remaining 6 would control the 6 respective 3-phase inverter MOSFET's. The purpose of the brake leg in the system to prevent any occurring bus surges. In practical application, the power flow is reversed during slowing down of the motor. This results in an increased voltage difference at the DC link. This could cause damage to it if the voltage is too high. Therefore, if and when the voltage increases past the allowed limit, it is closed by the driver and the MOSFET's of the brake leg. Also, to prevent damaging components, some portion of the braking energy is used on external resistance. It may be noted that the command for closing may be initiated from either the micro-controller or the CPLD, both are valid.

The following Fig. 1.10 shows the placement of Gate Driver's on Converter.

Figure 1.9: Gate Driver on Converter

The break leg closing command can come from both the micro-controller and by the CPLD. Each of these drivers has 8 pins, each of which is assigned to a specification function. Below is a schematic image of a driver, highlighting the functionality of each pin. The unsaturated pin is fundamental and has dual functionality. The first is that of making the MOSFET work on that area, on the voltage-current level, where it has a resistive behavior, far from the saturation zone, otherwise for currents high, too high voltages would occur and the component would burn, which would be lost too.

Figure 1.10: Gate Driver Control Architecture

In that area, you can end up there either because there is too much current and therefore the MOSFET is characterized by a characteristic on the volt-ampere plane in which at the point of work loses too much, or because the MOSFET is badly driven, for example because the bootstrap capability has discharged and I would go to apply a drive voltage lower, which would mean that with the same current, the voltage across the device is shifts more towards the saturation zone, compared to that for correct piloting. Of Consequently, the protection of the unsaturated pin must be incurred.

On the data-sheet of the MOSFET there is an estimate of its resistance value in a determined temperature range, the unsaturated pins detect the voltage across the MOSFET, for which an estimate of the current flowing through the device can be traced back, if too high, the driver commands the OFF state and the passage of current is prevented in the device.

An important aspect of the unsaturated pin is that of the analog circuit that characterizes it: the voltage on the MOSFET depends on its state, ie. conduction. Taking the high side MOSFET as a reference, when it is open, the de-saturation pin would have all the bus voltage,  $V_b us$ , in our case 48V, whereby we condition the signal using a diode, in order to prevent the voltage of the bus arrives on the driver pin, which is a signal pin. The two top diodes, take care instead of preventing the voltages from going beyond the 0-12 V range. The analog circuit just explained is the following.

Another fundamental utility of the unsaturated pin is the protection guarantee, when the current sensors, due to band problems, do not intervene. The sensors of in fact, they have a limited bandwidth. In the event that faults occur, and the currents rise suddenly (short of leg or phase-to-phase short) the current sensors would not be able to detect them, for which the unsaturated protection would intervene again, which it generally protects from current peaks, not due to a thermal fault pin which comes from the micro-controller. When the 3.3 V comes from the micro-controller at that pin, the input rises to 12 V and is communicated at the output with the following circuit analog, between pin  $V_B$  and pin  $V_S$ .

If the driver goes into fault it is necessary to communicate it out to the CPLD and then to the micro controller, closing with an open drain. The fault is denied, when in fault they are 0 V present, when no 3.3 V is present.

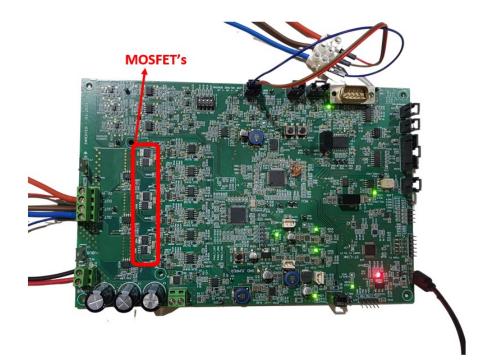

#### 1.4.5 MOSFET's

The switches that have been used for modulation and consequent regulation of the average value of the motor power supply voltage are the MOSFET's, two for each leg, and an additional one placed on the brake leg, to avoid damage of the DC link, in case of braking by the motor. They are controlled by the drivers, which through the DC capacitors apply a voltage of 12 V between gate and source, commanding its conduction, or a zero voltage, resulting in its interdiction. [IEEEexample:article\_typical] Introduction

Figure 1.11: MOSFET's placement on Converter

### Chapter 2

# Preliminary Tests on Converter

#### 2.1 PWM Control of Converter

Now in order to generate PWM, our converter is become the source and our transformer act as an inductive load. We give 5V to the micro-controller which is on the converter which provide us the 12V PWM at the output of the converter. In the normal case our converter behave as the rectifier, but we want to generate PWM from the converter board.

Our load is Y-connected 3 phase inductor transformer. The current loop make sure that the output voltage remain constant which is done by the micro-controller. We are using constant voltage topology, in which we have a value of the voltage but the value of current is zero. In our preliminary test on the converter the output current was zero but have a constant voltage there.

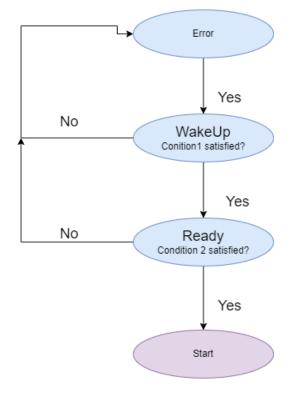

#### 2.2 Execution of Finite State Machine on Microcontroller

We can design logical connection by utilizing the Finite State Machine (FSM) which basically execute the mathematical expressions. Electronic design mostly used this type of machines to implement their model. It consists of finite number of state and transition between each state is run in such a way when desire condition is met. FSM start with the start state and then went to other states depending upon the inputs and finally reach its ending state. The following model is followed by FSM shown in the Fig. 2.1 below.

The micro-controller STM32 is being used for the implementation of FSM

irrespective of using CPLD for the following reason:

- Micro-controller performance increases exponentially.

- Cost of such micro-controllers are very less.

Figure 2.1: Finite State Machine Implementation Loop

These micro-controllers are very easy to use with FSM and are low power devices with many input peripheral's. There are many advantages of using software based Finite State machines which are follow as:

- Flexibility: When we implement Finite State on a micro-controller, it will give us the leverage of changing the design at any time during the project cycle. If we implement FSM on hardware side, the behavior of FSM can be change when the circuit is produced. If we have to change anything, we would have to redesign the circuit again. So this facility to executed the FSM on micro-controller help us to change the design according to our requirement at any time.

- Error Detection: Micro-controller software development environment helps us to debug the error in our FSM easily. For instance, you can use break point

in the software to check every step of code in the micro-controller which help you to debug your error very easily.

• Capability of software control FSM: One of the major advantage of using software FSM is that we can manage the complicate sequential problem very easily because it helps us to debug every error line by line using the breakpoints. We can also use the multiple peripherals for the micro-controller design so that our FSM design can handle multiple I/O operation as well.

In recent times, the use of finite machines with the micro-controller is usual industrial approach in coding, although there use is beyond the scope of coding. These are now used in-order to rectify bugs, to prevent indefinite loops and especially for the ease of debugging. The first state in which the control enters by default at startup is that of error. In this state the inverter outputs are disabled and all the control variables are initialized.

The error state is entered when the micro-controller is turned on or reset, or when something abnormal occurs during the check routine, which can produces the larges amount of current which damages the hardware circuits and devices.

In this Finite state machine I have used 4 major states which are Error, Wake-up, Ready and Start states. Using these four states I can get my desire outcome. Next, the state START, where the machine control code is executed.

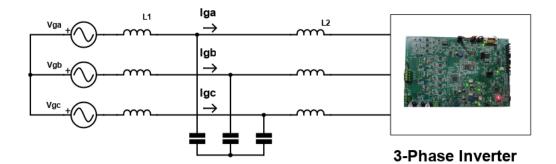

#### 2.3 LCL Filter Design Analysis

In the last decade, the demand of energy is escalating day by day and its result in more depletion of overall fossil fuels. As the world is supporting the cause of using renewable energy due to environmental concern as well. The use of power converter is increasing day by day due to growth in renewable energy resources especially wind and solar. We want extract maximum energy from these two sources and also interfacing these sources with our power grid lines. In the connection of a power converter with power grid lines the LCL plays a very vital role in it.[4]

Grid code play an important role in the making of small, medium, and large wind turbines designs. These grid codes vary from one country to another counter which make it difficult for the vendor to select an optimum grid codes for the wind turbine. Due to variations of these grid codes, when we try to integrate wind energy with power grids LCL plays an important role to control and mitigate the harmonics and oscillations in the voltage and current.