### POLITECNICO DI TORINO

Master degree course in Electronic Engineering

Master Degree Thesis

### HLS techniques for high performance parallel codes in Logic-in-Memory systems

Supervisors Prof.ssa Mariagrazia GRAZIANO Prof. Maurizio ZAMBONI Prof.ssa Giovanna TURVANI Candidate Alessio NACLERIO ID: 270065

ACADEMIC YEAR 2021 - 2022

### Summary

Recently, several researches have been conducted at the VLSI Laboratory of Politecnico di Torino on the Logic-in-Memory (LiM) model. It is an innovative architectural paradigm that aims at tackling the set of limitations showed by the von-Neumann model, usually referred to as memory wall or von-Neumann bottleneck. The key idea behind the concept of LiM is the implementation of memory devices in which standard cells are equipped with simple computational units. As a result, memory accesses are largely reduced, as well as power consumption and data-fetching latency. Moreover, high timing performance can be achieved, as the regular structure of LiM systems offers the possibility to perform parallel processing.

Two tools have been developed at the VLSI Laboratory with the purpose of creating a framework that allows a designer to easily devise and characterize LiM architectures. Firstly, *DEXiMA* was born as a simulator for LiM systems, providing the user with information about *timing performance, space occupation* and *static and dynamic power consumption*. Then, *Octantis* has been proposed, presenting itself as a *High-Level Synthesizer* that handles a C program and generates a LiM architecture for its execution. In order to accomplish this translation process, it considers the *LLVM Compiler Framework*, whose front-end (*Clang*) and *Optimization Passes* have been exploited. The Octantis back-end receives the *LLVM IR* code generated by the previous steps and produces the description of the LiM architecture by means of configuration files for DEXiMA. For this purpose, the typical four-stage structure of HLS tools have been implemented, encompassing allocation, scheduling, binding and code emission.

Although being able to synthesize parts of several LiM architectures already proposed at the VLSI Laboratory, Octantis only provided solutions for the handling of simple code constructs. The main objective of this thesis has been the enlargement of the set of data structures and C constructs available for the description of the input program while considering the benefits that they could derive from the parallelization opportunities offered by a LiM implementation. Hence, the work mainly focused on the identification of strategies for the management of for-loop nests and the synthesis of operations involving linear and two-dimensional arrays, whose elements can be visited by means of well-defined Array Access Patterns. The handling of these complex structures along with the implementation of loop unrolling allows Octantis to synthesize highly parallel structures capable of executing algorithms that require non-trivial access the elements of arrays.

A new Pass called **InfoCollector** has been developed in order to deal with the increased complexity of information characterizing the input algorithm. It performs an accurate analysis of the LLVM IR code with two main purposes: speeding up the scheduling phase and, most importantly, gather information regarding nested loops and array accesses inside the LLVM IR code. As regards the former, InfoCollector implements techniques that allow the overall execution time of the mentioned stage not to be affected by the larger amount of instructions to be taken into account. As a matter of fact, more elaborated algorithms can result in a huge number of LLVM IR operations to be considered by the scheduler. The latter task is crucial for the correct mapping and parallelization of operations involving vectors or matrices onto the final LiM architecture. Several concepts belonging to the mathematical framework referred to as *Polyhedral Model* have been employed to let Info-Collector provide the binder with data structures that allow the generation of an optimal LiM system, in which its intrinsic parallel capabilities are fully exploited.

As a consequence, the scheduling and binding phases have undergone some modifications in order to benefit from the introduction of the new pass. Specifically for the binding phase, an important target-dependent optimization strategy has been developed aimed at limiting the amount of needed hardware resources and the overall area as much as possible, while ensuring high timing performance. The implementation of parallel processing indeed offers the advantage of drastically reducing the total execution time but, at the same time, it causes an increase of space occupation.

Moreover, the code emission stage has also been expanded with the insertion of two new modules. The former aims at the production of configuration files for the new **DEXiMA-CAD**, which is a tool for DEXiMA that enables the visual representation of the LiM architecture. The latter deals with the generation of a *VHDL* description of the system devised by Octantis synthesis process, as well as an associated VHDL *testbench* in order to check its correct behaviour by carrying out simulations with commercial EDA tools, such as *Modelsim*.

Finally, several *Image Processing* algorithms have been chosen for the synthesis on LiM devices. Since they are usually data-intensive, they are accelerated through parallel computing systems, such as GPUs. Hence, the LiM model may represent an alternative way to address their efficient implementation. Results have shown that Octantis is now able to synthesize *more complex structures with the possibility of parallelizing the execution of elaborated operations*, which can also require sophisticated access patterns to be considered for the visit of both C vectors and matrices. Furthermore, the introduced optimization strategy has been proved to enable a great saving of area and hardware resources.

In conclusion, the handling of loop nests and array accesses represents the starting point for the *synthesis of acknowledged HLS benchmarks* on LiM architectures, thus enabling the performance comparison with other already available implementations. Moreover, it is important to envision a more complex system where a LiM device and a conventional processing unit can coexist, in order to allow the implementation of even more complex operations. As a consequence, Octantis would have to devise several strategies to allocate the implementation of each instruction to one of the two units.

# Contents

| Li           | st of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Li           | st of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                  |

| Introduction |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

| Ι            | Octantis, a tool for Logic-in-Memory exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                 |

| 1 2          | Motivation and background         1.1       An introduction to the Logic-in-Memory model         1.2       DExIMA: a simulation tool for LiM systems         1.2       DExIMA: a simulation tool for LiM systems         The Octantis project         2.1       Introduction         2.2       The LLVM Project         2.2.1       The LLVM Intermediate Representation         2.3       The structure of Octantis         2.3.1       From the input C algorithm to the optimized LLVM III         2.3.2       The Back-End | . 17<br>19<br>. 19<br>. 20<br>. 21<br>. 24<br>? 24 |

| II           | The expansion of Octantis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31                                                 |

| In           | troduction and Motivations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                 |

| 3            | Polyhedral Model: a powerful mathematical framework3.1Introduction to the Polyhedral Model3.1.1Definitions and concepts3.1.2The Loop Array Dependence graph                                                                                                                                                                                                                                                                                                                                                                    | . 38                                               |

| 4            | InfoCollector: a preliminary analysis pass                    | 45  |

|--------------|---------------------------------------------------------------|-----|

|              | 4.1 Introduction                                              | 45  |

|              | 4.2 The collection of information                             | 46  |

|              | 4.2.1 The importance of alias analysis                        | 46  |

|              | 4.2.2 The handling of loops                                   | 50  |

|              | 4.2.3 The handling of pointers                                | 56  |

|              | 4.3 The construction of Access Pattern Matrices               | 63  |

|              | 4.4 The identification of <i>valid</i> Basic Blocks           | 65  |

| 5            | The evolution of Octantis structure                           | 67  |

|              | 5.1 Introduction                                              | 67  |

|              | 5.2 The scheduling phase: leveraging InfoCollector            | 68  |

|              | 5.3 The binding phase: facing higher complexities             | 70  |

|              | 5.3.1 Handling array access patterns                          | 72  |

|              | 5.3.2 A new target-dependent optimization                     | 83  |

| 6            | The expansion of the code emission phase                      | 89  |

|              | 6.1 The generation of VHDL files                              | 90  |

|              | 6.2 The generation of DExIMA-CAD configuration files          | 92  |

| 7            | Tests                                                         | 95  |

|              | 7.1 Image Processing algorithms                               | 95  |

|              | 7.1.1 Synthesis of the Integral Image algorithm               | 96  |

|              | 7.1.2 Synthesis of a multi-image encryption algorithm         | 99  |

|              | 7.1.3 Synthesis of an approximated Arithmetic Mean Filter . 1 | .03 |

| 8            | Conclusions and future works 1                                | 07  |

| Bibliography |                                                               |     |

# List of Tables

| 7.1 | Results regarding the types of rows present in the LiM system  |       |

|-----|----------------------------------------------------------------|-------|

|     | that implements the generation of the Integral Image. Data     |       |

|     | are provided for each optimization level.                      | . 98  |

| 7.2 | Results obtained from the synthesis of the algorithm for the   |       |

|     | generation of the Integral Image. Along with the optimization  |       |

|     | level, different data are provided.                            | . 99  |

| 7.3 | Aggregated results of the synthesis by Octantis of the algo-   |       |

|     | rithm for the generation of both the XOR-Image and the XOR-    |       |

|     | Keys                                                           | . 102 |

| 7.4 | Results concerning the types of rows inside the LiM system     |       |

|     | that implements the application of the approximated Arith-     |       |

|     | metic Mean Filter. Different values are provided along with    |       |

|     | the optimization level.                                        | . 105 |

| 7.5 | Overall results obtained from the synthesis of the algorithm   |       |

|     | implements the application of the approximated Arithmetic      |       |

|     | Mean Filter. Along with the optimization level, different data |       |

|     | are provided.                                                  | . 105 |

|     | Mean Filter. Along with the optimization level, different data | . 1   |

# List of Figures

| 2.1 | The retargetability principle is highlighted in figure. It allows         |    |

|-----|---------------------------------------------------------------------------|----|

|     | a compiler to handle multiple source programming languages                |    |

|     | and target machines.                                                      | 21 |

| 2.2 | Analysis and Transform Passes in the LLVM Compiler structure.             | 23 |

| 2.3 | Block diagram of the Octantis structure.                                  | 24 |

| 3.1 | A SCoP with the possible representations of the related Iter-             |    |

|     | ation Domain. Iteration Domain $a$ is the set of all iteration            |    |

|     | vectors, while $b$ shows the linear inequalities that, in turn,           |    |

|     | form the 2-dimensional polyhedron.                                        | 39 |

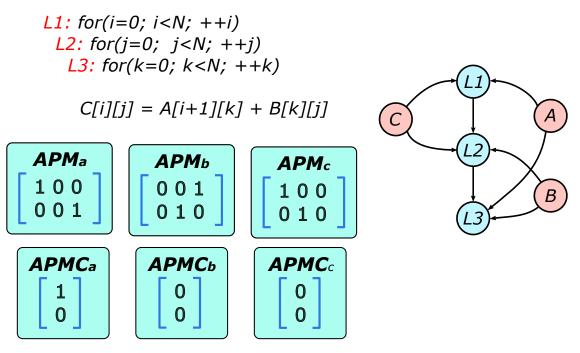

| 3.2 | A simple C code with 3 nested loops is provided along with                |    |

|     | the associated LAD graph and the APMs and APMCs of each                   |    |

|     | array                                                                     | 42 |

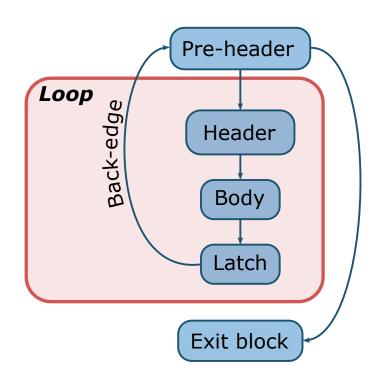

| 4.1 | Structure of an LLVM natural loop                                         | 52 |

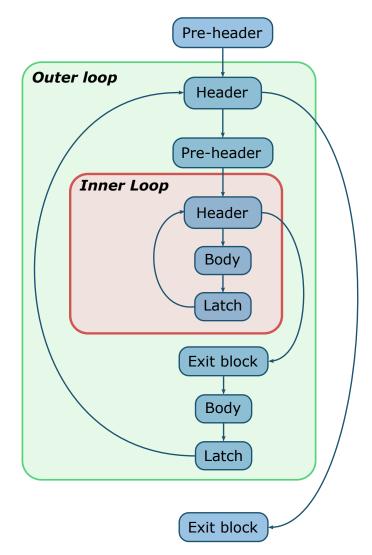

| 4.2 | Structure of a loop nest composed of two loops after the loop-            |    |

|     | simplify Pass has been issued                                             | 53 |

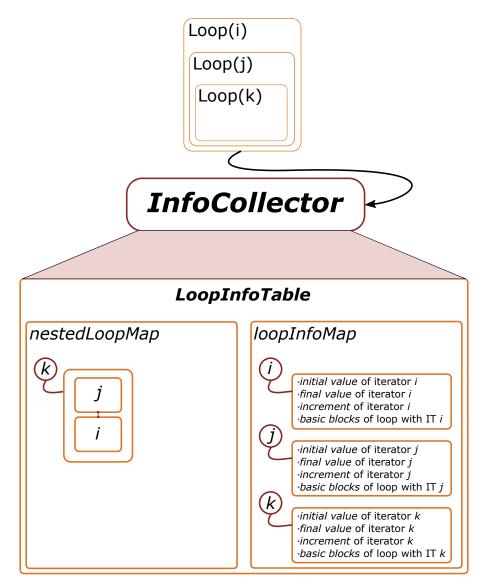

| 4.3 | A simplified example program composed of 3 nested loops                   |    |

|     | is considered. <i>LoopInfoTable</i> and the related organization of       |    |

|     | data inside <i>loopInfoMap</i> and <i>nestedLoopMap</i> are detailed      | 56 |

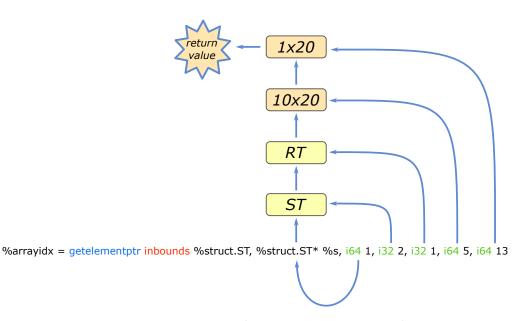

| 4.4 | Visual representation of how the parameters of a <i>getelementptr</i>     |    |

|     | instruction are used to obtain the final pointer in the first             |    |

|     | example provided                                                          | 59 |

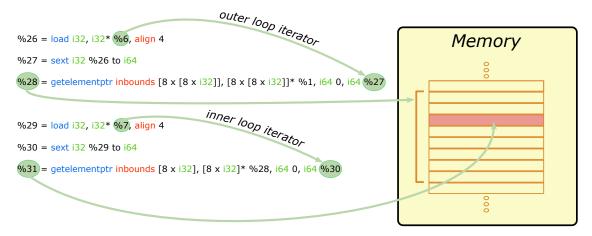

| 4.5 | Code snippet related to the second example examined. The                  |    |

|     | use of loop iterator in <i>getelementptr</i> instructions is highlighted. | 60 |

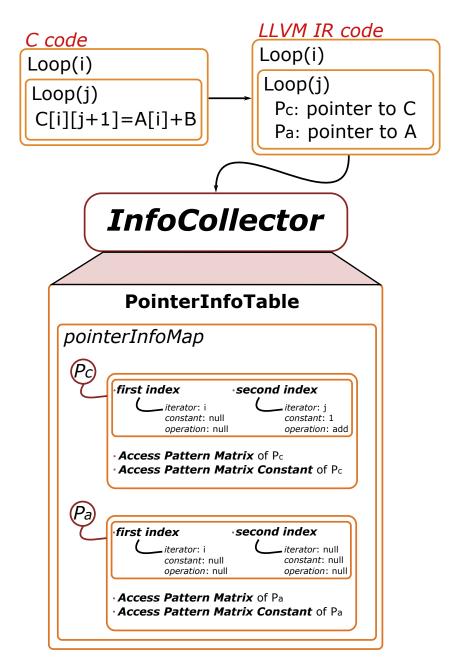

| 4.6 | Internal structure of <i>PointerInfoTable</i> for a simplified code       | 62 |

| 4.7 | A simplified code with 4 nested loops where the access to ar-             |    |

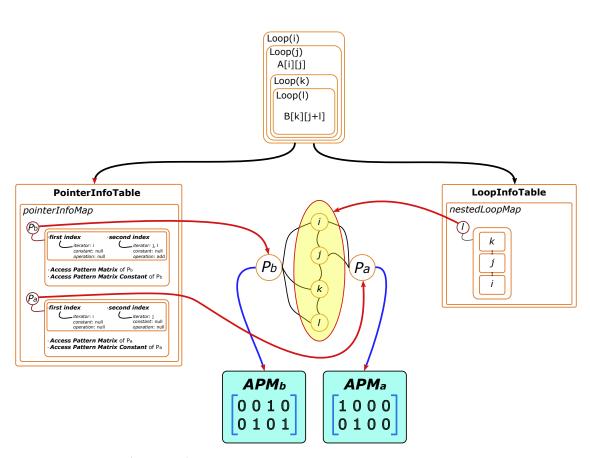

|     | rays $A$ and $B$ is provided at the top. The organization of              |    |

|     | information by means of <i>PointerInfoTable</i> and <i>LoopInfoTable</i>  |    |

|     | allows the creation of a <i>LAD graph</i> , from which the APMs of        |    |

|     | the two arrays are extracted                                              | 64 |

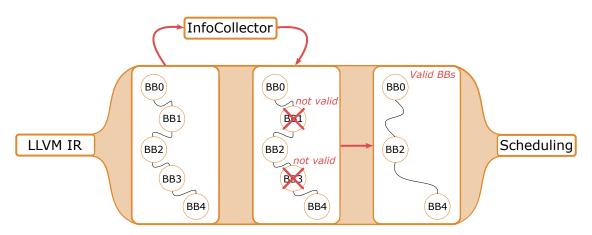

| 4.8 | Scheme showing the filter-like behaviour of InfoCollector                 | 65 |

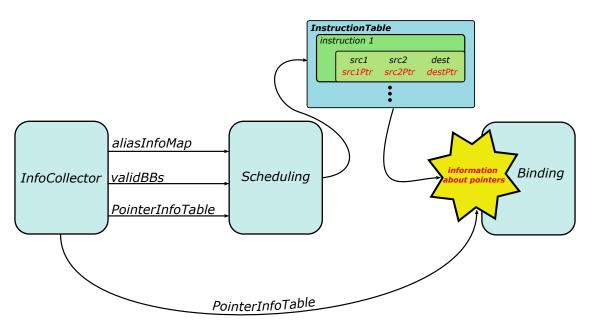

| 5.1 | Movement of information and data structures among InfoCol-     |    |

|-----|----------------------------------------------------------------|----|

|     | lector, the scheduler and the binder, with the introduction of |    |

|     | parameters regarding pointers in Instruction Table.            | 69 |

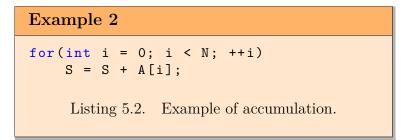

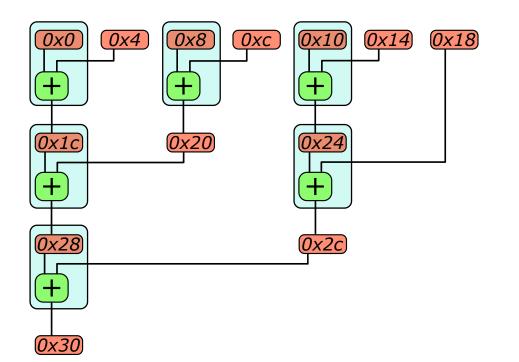

| 5.2 | Mapping of the accumulation operation on an set of LiM rows    |    |

|     | implemented following a <i>reduction-tree</i> strategy         | 71 |

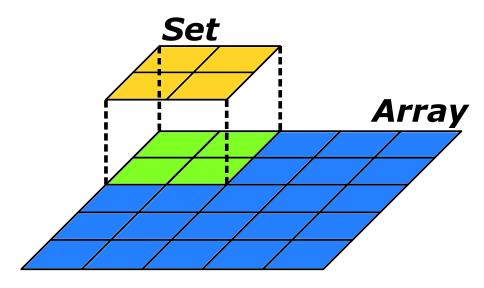

| 5.3 | Identification of a set inside an array                        | 76 |

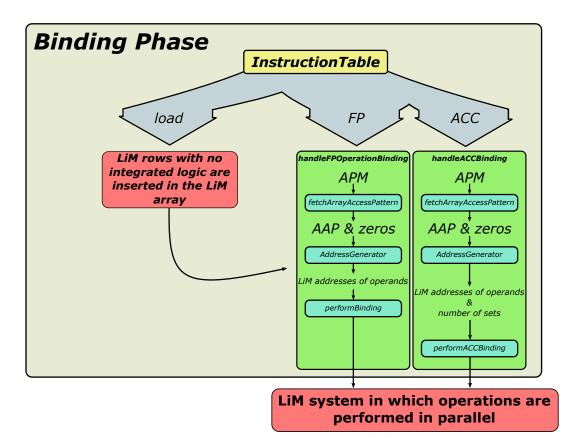

| 5.4 | New internal structure of Octantis binder.                     | 81 |

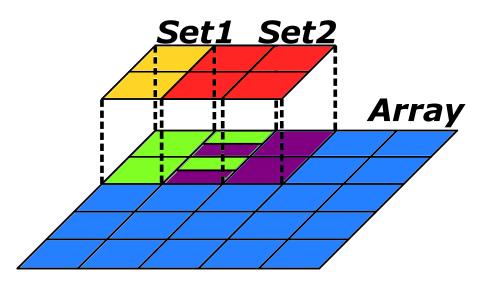

| 5.5 | Two overlapping accumulation sets inside an array.             | 86 |

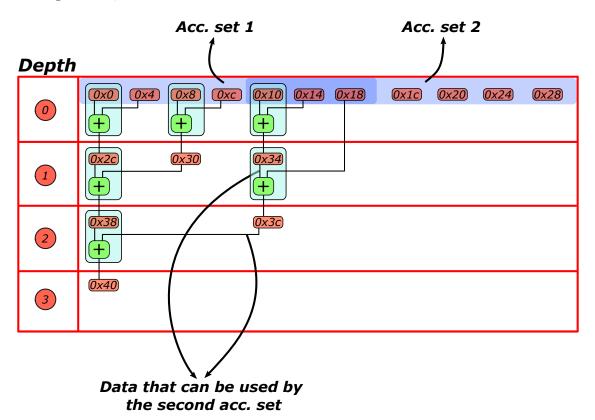

| 5.6 | Two overlapping accumulation sets.                             | 87 |

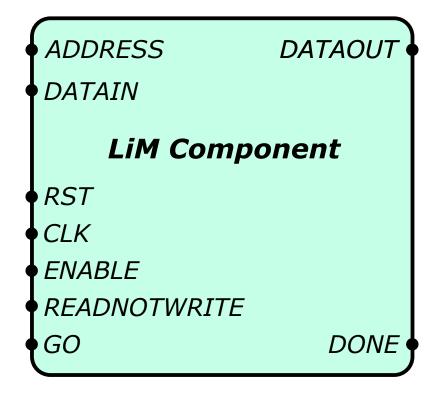

| 6.1 | Interface of the entity generated by means of PrintVHDLFiles.  | 90 |

### Introduction

The work carried out within this thesis aimed at the *expansion of the Octantis* project, a High-Level Synthesis tool for the exploration of Logic-in-Memory systems developed at the *VLSI Laboratory* of Politecnico di Torino. Given the intrinsic parallel capabilities of LiM systems, the Octantis synthesis process has been designed to be well-suited for applications that could benefit from a parallelized implementation. Hence, in this thesis, the set of data structures and constructs available for the development of the input algorithm has been enlarged, with particular interest shown towards the ones that are mostly employed for the description of parallel codes. Therefore, as deeply discussed in the second part of this document, the major focus has been put into the handling of *nested loops* and *one/two-dimensional arrays*. The combination of the loop unrolling technique and the study of array access patterns, namely the order in which their elements are visited, allowed the effective parallelization of more complex algorithms, suitable for the mapping on a LiM architecture.

In the first part of the document, the motivations behind the development of Octantis are presented, and the description of the internal structure of the tool is discussed. An overview of the research works carried out at the *VLSI Laboratory* of Politecnico di Torino on LiM architecture is provided, along with a brief introduction to DEXiMA. After that, the various stages that contribute to the Octantis synthesis process are analyzed.

In the second part, the introduction of *InfoCollector Pass* is deepened along with the consequent modification of the other Octantis HLS phases. The dissertation starts with the presentation of the *Polyhedral Model*, a mathematical framework whose main concepts have been exploited for the organization of information and the analyses implemented by InfoCollector. After that, the main tasks carried out by this new Pass are addressed, highlighting the complex code structures that it allows handling and the strategies implemented towards their synthesis. Successively, the *evolution of both the scheduling and the binding phases* is discussed. As regards the former, the benefits derived from several techniques performed by InfoCollector are presented. As for the latter, the discussion is focused on how the structure of the binder has been modified to drive the synthesis process according to the data structures produced by the new Pass. Moreover, the insertion of an additional *target-dependent optimization technique* within the binding phase is addressed too, showing the advantages that it can bring in terms of saving of area occupation and hardware resources.

While InfoCollector enables the enhancement of Octantis input capabilities, the expansion of the code emission stage allows for a wider set of output description formats of the final LiM system to be available. Two new modules respectively aimed at the generation of *VHDL* and *DEXiMA-CAD* files are presented.

Finally, tests have been carried out addressing data-intensive algorithms belonging to the *Image Processing* field. Their C implementation has been given to Octantis for the synthesis on LiM systems. The results gathered about area occupation, hardware resources and timing performance are reported and discussed. Hence, the correctness of the novelties introduced and the improvements with respect to the previous version of the tool have been checked, along with the considerations on possible future expansions.

### Part I

# Octantis, a tool for Logic-in-Memory exploration

### Chapter 1

# Motivation and background

### 1.1 An introduction to the Logic-in-Memory model

During recent years, several researches have been carried out at VLSI Laboratory of Politecnico di Torino concerning the Logic-in-Memory paradigm. It represents a promising architectural solution that aims at overcoming the drawbacks of the von-Neumann model which are being experienced in the last decades.

As a matter of fact, the architecture of digital processing systems has been conceived according to this model, which requires the separation between the device responsible for the storage of data, the *memory*, and the one that performs computations, the *CPU*. Within this scheme, the CPU has to access the memory in order to retrieve data useful for subsequent elaboration. However, while the former has become more and more powerful over time due to CMOS technology scaling, the latter has not undergone the same improvement. This has resulted in a substantial difference between the computational speed that characterizes modern CPUs and the time required to perform memory accesses. As a consequence, a larger amount of time and energy is wasted while fetching data rather than elaborating them. Moreover, especially for data-intensive applications, the huge need for memory access highly affects the total power consumption. The set of issues that stem from the separation between memory and CPU as well as their performance gap is generally referred to as memory wall or von-Neumann bottleneck.

The presented drawbacks gave energy to the exploration of the Logic-in-Memory model, whose main objective is to integrate computational units directly inside the memory. This choice can result in a drastic reduction of data-fetching latency and the related power consumption, also enabling faster elaboration of data with lower energy waste. From a structural point of view, LiM architectures have been conceived as arrays of *memory cells that can be equipped with relatively simple operational units*. In this way, all data elaborations are enclosed inside the LiM array, without the need of transferring information outside of it. Moreover, the high degree of regularity that characterizes this kind of structure enables the possibility to perform parallel computing, which represents a key feature that many implementations could take benefit from.

The research works carried out at VLSI Laboratory led to the definition of CLiMA [1], a Configurable Logic-in-Memory Architecture. The key feature of CLiMA is the availability of arrays whose basic block is represented by the so-called CLiM cells. The choice of this name derives directly from their internal structure, which consists of a normal memory cell equipped with logic that is configurable in order to allow different operations to be carried out. CLiMA has been exploited for the implementation of a Quantized Convolutional Neural Network[1] and the Bitmap Indexing Algorithm[2], providing promising performance results. Furthermore, studies regarding the possible benefits that LiM architectural solutions may derive from beyond-CMOS technologies have been carried out. For instance, always in [1] the Perpendicular Nano Magnetic Logic (pNML) technology has been considered for the implementation of CLiMA.

In conclusion, many researches have addressed the adoption of the LiM model for specific architectures. However, the main objective would be the creation of a framework that allows the exploration and characterization of LiM implementations, thus having a more comprehensive view that takes into account multiple abstraction levels. This is the main reason behind the development of both DEXiMA, which is briefly presented in the next section, and Octantis, whose description is deepened in Chapter 2.

### 1.2 DExIMA: a simulation tool for LiM systems

DEXiMA is a C++ based tool developed at VLSI Laboratory of Politecnico di Torino that performs the characterization of a system composed of a LiM component and an out-of-memory CMOS circuit, which are connected through a bus. By means of the implementation of both static and dynamic analysis, it can provide important information regarding *timing performance*, *area occupation* and *static* and *dynamic power consumption*.

A purely structural description of the entire system must be devised and fed to DEXiMA through proper configuration files. The *front-end* of the tool is responsible for producing the correct data structures required for the actual simulation starting from these files. As regards the LiM unit, a rectangular array of LiM cells must be defined. Its description has to contain information about the types of LiM cells employed, the modules that carry out intra-row or intra-column operations and how they are connected. Different kinds of cells can be exploited, each one characterized by different integrated logic. The out-of-memory system has to be defined in a similar way, firstly specifying the hardware modules, chosen from a pre-defined set of available components, that are required for the implementation and, after that, their interconnections.

The DEXiMA back-end is the one in charge of performing the simulation of the circuit. In order to do that, suitable models have been considered for the characterization of both the traditional logic and the memory cells. As regards the first, the information provided by TAMTAMS[3] has been taken into account. It is a web-based framework developed at *Politecnico di Torino* that can be employed for the analysis of CMOS circuits starting from their characteristic parameters. On the other hand, the memory performances are estimated by CACTI[4], an open-source simulator of memories developed by *Hewlett-Packard Laboratories*. However, solutions dealing with beyond-CMOS technologies are being considered, as the mentioned model turned out to be not suitable for the proper description of LiM cells.

As already mentioned, the simulation implemented by DEXiMA addresses both static and dynamic analysis. The former allows obtaining important static parameters like space occupation, maximum delay and static power consumption. However, the latter enables the definition of dynamic power consumption, which is much more relevant with respect to the static one. For this purpose, the description of the algorithm that the system performs is needed, and it has to be provided in input to DEXiMA following a specific syntax.

In conclusion, DEXiMA represents a promising tool for the characterization of LiM systems, in constant evolution along with the research around this new innovative model. After the development of this tool, the introduction of the Octantis project has been taken into account in order to broaden the scope of the entire framework that was being designed. As a matter of fact, it has been decided to express the LiM array devised by the Octantis synthesis process by means of DEXiMA configuration files, thus enabling its simulation and connecting the two software.

### Chapter 2

### The Octantis project

### 2.1 Introduction

During the previous chapter, the main elements that have characterized the research on LiM systems carried out at VLSI Laboratory of Politecnico di Torino have been discussed. Octantis emerged within this lively environment, with the purpose of further exploring the potential of the LiM paradigm. It was born in 2020 thanks to the thesis work carried out by A. Marchesin[5], and the promising results that have been obtained led to the development of a scientific paper[6].

Octantis is a *High-Level Synthesizer*, developed in C++, whose main objective is the generation of an optimal LiM architecture, starting from an input algorithm described using standard C language. As it will be better clarified throughout the following sections, Octantis highly exploits the *LLVM Compiler Framework* in order to accomplish the mentioned "translation". LLVM not only offers a fully-developed open-source compiler infrastructure but also a set of related projects as well as libraries allowing developers to perform code analysis, transformation and optimization.

Octantis presents itself as an *agile tool for the exploration of LiM architectures*, enabling designers easy access to this innovative model, without being concerned by the implementation details. As a matter of fact, Octantis guides users through the examination of LiM solutions while letting them focus on the development of the input algorithm. Furthermore, a *modular approach* has been adopted for the internal structure of the tool in order to help future developers in the expansion of the code.

### 2.2 The LLVM Project

LLVM was born as a research project at the University of Illinois in 2000, under the responsibility of V. Adve and C. Lattner, addressing the implementation of modern strategies for supporting static and dynamic compilation of multiple programming languages. Since then, LLVM has evolved into a collection of modular and reusable compiler technologies, involving several subprojects, some of which are also used in production by several open source and commercial tools, as well as being largely exploited in academic research.

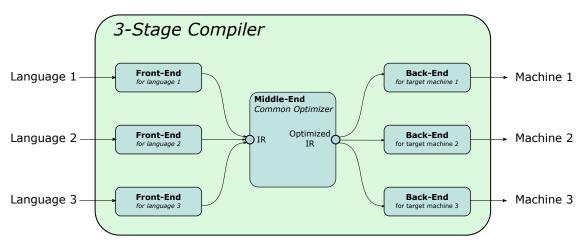

As highlighted by the same C. Lattner in its chapter of *The Architecture* of *Open Source Applications*[7], the LLVM compiler follows the traditional three-stage compiler structure that consists of:

- a Front-End: it parses the input code and checks for its overall correctness by conducting lexical, syntax and semantic analysis. As regards the LLVM compiler, these operations are carried out by *Clang*[8], a frontend specifically designed for C/C++. The last step of this stage is responsible for the generation of the *Intermediate Representation (IR)* of the source code. It consists in a semantically-equivalent description of the input algorithm expressed by means of a low-level, machine-like language. LLVM has its own intermediate representation, which will be examined in the following section.

- a **Middle-End**: during this stage, the IR undergoes a set of *target-independent optimizations*, which are achieved through the analysis of the code and the subsequent transformation.

- a **Back-end**: the main objective of this final step is the translation of the IR into the desired output description format, with the possibility of employing machine-dependent code optimizations, too.

The discussed architecture presents a crucial advantage that can be referred to as **retargetability**. The main aim of *retargetable compilers* consists in the exploitation of the common IR, which can be considered as a midpoint where different back-ends share the same comprehension of the source program. By means of this representation, also visualized in Figure 2.1, it is possible to *share the set of target-independent optimizations among multiple back-ends*. Moreover, this design allows the easy handling of a new source or target language, as it is unnecessary to redevelop the entire compiler structure. For instance, porting the compiler to manage a new source language only requires the implementation of a new dedicated front-end, while the IR optimizer and the back-end can remain the same.

Figure 2.1. The retargetability principle is highlighted in figure. It allows a compiler to handle multiple source programming languages and target machines.

Another main advantage of this design, which also follows directly from retargetability, is that the compiler can serve a *larger set of programmers* than it would if it only provided solutions for the handling of one source and target language. For an open-source project, this results in the presence of a larger community of potential contributors to draw from, which naturally leads to more and faster improvements to the compiler.

Finally, one of the key aspects that favoured the choice of LLVM for the development of Octantis relies on its free licence, which allows deriving also commercial products from the original LLVM project.

#### 2.2.1 The LLVM Intermediate Representation

As already highlighted in the previous section, the IR represents the *backbone* of the compiler structure, being the connection point between the front-end and the back-end. The LLVM project has its own intermediate representation, the *LLVM IR*, which consists of a *low-level language*, with a *RISC-like instruction set*. It has three equivalent forms:

- An in-memory representation.

- An on-disk representation encoded by means of the bitcode files.

• An on-disk representation provided in a human-readable form (the LLVM assembly files).

The internal structure of LLVM IR can be compared to the one that characterizes *Chinese Boxes*, a collection of several boxes one contained inside another. Similarly, the top-level entities of LLVM IR are represented by *modules*, which are composed of different *functions*. The latter, in turn, are formed by a sequence of *basic blocks*, whose fundamental units are single *instructions*. A module also contains *peripheral* entities, such as global variables, the target data layout, external function prototypes and data structure declarations.

The *control flow* of the program is determined by basic blocks, which are characterized by the presence of a single *entry point* and a single *exit point*. When a basic block is entered, all of its internal instructions are executed. Then, the terminator instruction is the one responsible for jumping to another block or returning from the function. Moreover, the first basic block of a function is a special one, as it must not be the target of any branch instruction.

Furthermore, the LLVM IR presents the following fundamental properties:

- It employs the Static Single Assignment (SSA) form. Each value only has a single instruction that defines it, and all of its successive uses can be immediately retraced to that specific instruction. This design choice allows the creation of *use-def chains* that highly simplifies the implementation of optimizations, avoiding the need of a separate data flow analysis to compute these chains.

- The structure of instructions follows the **three-address code** form. The operations that elaborate data act on two source operands and place the result in a distinct destination one.

- It has an **infinite number of registers**. LLVM local identifiers can assume any name that starts with the % symbol, including numbers that start from zero, such as %0 and %1, with no limitations on the maximum number.

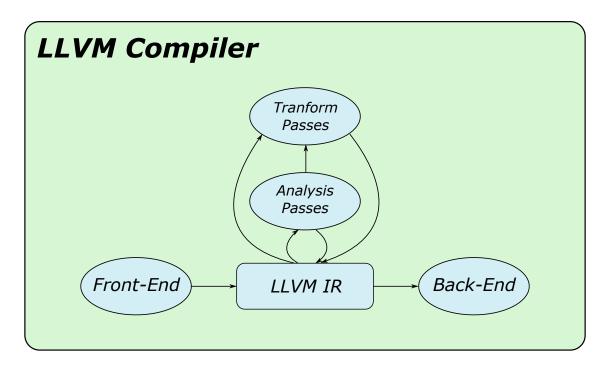

As shown in Figure 2.2, the IR is the point where *target-independent* optimizations take place. As regards LLVM IR, they are implemented as

*Passes*[9], which parse portions of the program in order to either collect useful information or transform the code. Three main types of Passes are available in LLVM, each with different purposes:

- 1. Analysis Passes gather the information that other passes can effectively exploit to properly carry out their tasks. They efficiently recognize useful code proprieties and optimization opportunities.

- 2. *Transform Passes* remodel the code aiming at its optimization, eventually using the data structure generated by previously issued analysis passes.

- 3. *Utility Passes* provide useful utilities that do not otherwise fit categorization. For example, passes that write a module to bitcode are neither analysis nor transform passes.

Figure 2.2. Analysis and Transform Passes in the LLVM Compiler structure.

In conclusion, further details about the LLVM structure and its IR can be found in [10].

#### 2.3 The structure of Octantis

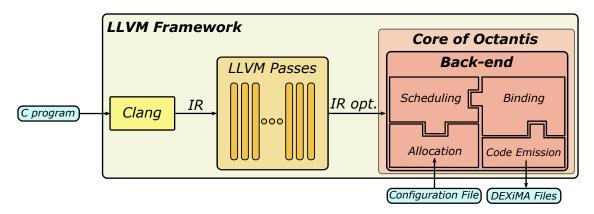

The Octantis project highly exploits the *LLVM Framework* to achieve the translation from C code to DExIMA configuration files, which are used for the description of the final LiM architecture.

First of all, in order to properly handle an input C algorithm, it takes advantage of the native LLVM front-end, *Clang.* Then, some already available *LLVM Passes* have been employed, as well as the one specifically designed for the implementation of loop unrolling, in order to perform the desired optimizations on the LLVM Intermediate Representation. From this step forward, the back-end of Octantis takes place, whose internal organization follows the typical four-stage structure common to all modern High-Level Synthesis tools, which consists of *allocation*, *scheduling*, *binding* and *code emission*. These phases are implemented by means of several C++ classes that are coordinated by a unique new Pass named *OctantisPass*. In Figure 2.3, a schematic overview of the blocks that contribute to the structure of Octantis is shown.

Figure 2.3. Block diagram of the Octantis structure.

#### 2.3.1 From the input C algorithm to the optimized LLVM IR

As already mentioned, the first step of Octantis compilation requires the input C program to be handed over to Clang, which is in charge of translating it into LLVM Intermediate Representation. However, several *constraints*

must be considered while developing the algorithm. As a matter of fact, even though the C language offers the possibility to exploit high-level programming constructs, the users shall keep in mind that the design of a hardware component is being performed. Hence, the following things should be strictly avoided:

- **Dynamic allocation of memory**: a LiM system is basically a memory, hence this feature is in direct contrast with the very concept of LiM.

- **Recursive function calls**: they represent a highly complex C structure difficult to handle for whatever hardware implementation.

- Multiplication and division: they are known to consume a large number of hardware resources. As for the LiM system, the complexity is required to be rather limited in order to enable fast parallel computations with low power consumption. However, shift operations represent an alternative option, although only approximated results can be obtained.

Hence, all of these operations would be either meaningless or inconvenient to integrate into a LiM architecture. Furthermore, it is compulsory to *declare variables as integers*, due to the fact that the LiM system only handles arithmetic operations on this type of data. Finally, the users can also exploit *bit-wise logic operators*, even the negative ones (i.e. nand, xnor, nor), which are not included in standard C.

In addition to the input C program, Octantis also requires a *configuration* file. Its structure has been designed to gather all the possible constraints that can be exploited in order to explore the design space throughout the synthesis process. As regards Octantis first release, only the handling of the information that determines the dimension of a LiM row has been effectively implemented. However, the organization of the configuration file is such to manage other types of parameters during future expansions of the program.

Once Clang has generated the LLVM IR, several optimizations are run, mainly performed by already available *LLVM Passes*, such as *mem2reg* and *simplifycfg*. The former promotes memory references with register ones, strengthening the SSA form of the code. The latter performs dead code elimination and merging of basic blocks when possible, in order to produce a more efficient code. Along with these two, passes that address loop analysis and transformation have been taken into account. The introduced LLVM Passes dealing with loops are:

- **licm Pass**: it tries to reduce the size of the body of the loop by removing as many instructions as possible. This operation can help the next phases reduce the number of resources used.

- **loop-deletion Pass**: it prunes the input IR code in order to delete all the loops that do not participate in the computation of the final results.

- **loop-reduce Pass**: it reduces the number of array references inside the loops and, in particular, the ones regarding the management of the variable used as the index.

- **loop-simplify Pass**: it is responsible to transform loops in simpler forms whenever possible.

While all these passes mostly deal with the generation of a more compact and efficient code, a **loop unrolling** pass has been developed as it represents a relevant optimization technique to be exploited in relation to LiM architectures. As a matter of fact, the intrinsic parallel capabilities of this kind of system are well-suited for the concurrent execution of multiple loop iterations. This results in an increasing amount of hardware resources as well as area occupation, but it has the great advantage of largely reducing the overall execution time.

#### 2.3.2 The Back-End

The back-end is the core of the Octantis project, as it is responsible for the effective generation of the final optimized LiM architecture starting from the IR code coming from the previous steps. As already mentioned, its internal organization follows the structure of all modern High-Level Synthesis tools, which is composed of allocation, scheduling, binding and code emission phases. During the next paragraphs, an overview of the tasks carried out by each of the four stages is presented, motivating the design choices that have been made.

#### Allocation

The allocation phase is the one responsible for the identification of the constraints specified by the designer inside the configuration file. The collection of this information is crucial in order to properly drive the whole synthesis process. As regards Octantis, the allocator actually handle only the parameter that defines the memory word size. As already discussed, the structure of the configuration file has been devised with the purpose of being easily expandable, thus allowing the introduction of new constraints that could be useful in future versions of the tool.

#### Scheduling

The main aim of the scheduling phase is to assign each instruction that must be mapped on hardware with an execution time, thus creating a sort of *finite state machine* of the program. The scheduler of Octantis implements an *As Soon As Possible* (ASAP) algorithm, whose objective is to determine the lowest possible time instant in which a specific operation can be issued. In order to properly carry out this task, the presence of data dependencies must be checked, as they have to be respected for the correct execution of the algorithm devised by the designer.

As regards Octantis, the structure of the LLVM IR code must be carefully considered in order to keep track of the evolution of the input program. As a matter of fact, a well-defined and fixed approach is implemented in the LLVM IR, from the definition of variables to their elaboration. Once this "pattern" is known, it can be followed to identify all the operations performed in the algorithm. First of all, each variable has to be *allocated* in the stack region of the memory. When an arithmetic or logic operation between two operands has to be performed, a *load* must be executed to store them inside local registers. Then, the actual operation is issued, followed by a *store*, which is useful to save the obtained result again into the stack.

Since the main goal of Octantis is the generation of a memory, load and store instructions that take into account a stack region are meaningless for the mapping on such a device. However, they are highly exploited by the scheduler respectively in order to know which variable must be allocated inside the LiM array, and when a result is available. Hence, they are essential for the detection of *data dependencies*. Regarding the effective operations that can be carried out for the elaboration of two source operands, Octantis supports *sum* and *bit-wise logic operators*, such as and, xor, or, along with their negated form (nand, xnor, nor). Their detection is performed by the scheduler, too.

At the end of the described process, the instructions are stored in a dedicated data structure, called *Instruction Table*, which can only contain:

- **load** operations, specifying the operand to be allocated inside the LiM array.

- arithmetic and logic operations that are performed between two source operands, which have been previously allocated.

#### Binding

The binding phase is responsible for the correct mapping of instructions onto the desired output hardware structure, which, in the case of Octantis, is represented by a LiM architecture. The C++ class responsible for the mentioned task is called *LiMCompiler*, and it is invoked right after the scheduler by OctantisPass. It generates a LiM unit that is capable of performing the operations required by the input algorithm, and a related *finite state machine* based on the control information gathered during the scheduling phase.

Before starting the discussion about how the binder carries out its task, it is useful to have an overview of the LiM architecture taken as a reference by Octantis. The main characteristic of the memory array is its *regularity*. Each row has the same size and the cells belonging to a single row are uniform and equipped with the same internal logic. As regards interfaces, rows can handle *two input connections*, one in input to the memory cell and the other to the internal logic, and *one output connection*. In order to carry out an operation, two source operands are needed. They are stored inside two separate memory rows, one of which must include the needed computational unit useful for the required elaboration. Finally, an additional row is exploited to store the result. Moreover, also configurable cells can be defined, referring to the structure of the CLiM-Architectures briefly described before.

When LiMCompiler is launched, the parsing of the Instruction Table begins. As already pointed out in the previous section, two possible types of instructions can be found inside this data structure, load and arithmetic/logic operations. When considering the former, the binder inserts a new memory row with the same size specified in the configuration file inside the array, without the need of equipping its cells with any logic. On the other hand, the latter requires more complex handling, described as follows. Once the two source operands memory rows are identified, three cases can occur:

• both or one of the source rows are not equipped with any logic: one of the two is chosen to be enhanced with the needed operators, connecting

their other input to the second operand.

- one of the source rows has the same logic required for the current operation: if the number of input connections previously present in the mentioned row was 1, an additional connection is added coming from the other source row. This choice has been made in order to reduce complexity.

- both source rows have different logic operators from the one required by the current operation: this obviously represents the worst case, having to duplicate one of the two source rows in a new one with the right LiM cells. The other row is set as the other input for the logic.

Special cases are the ones represented by operations inside loops and accumulations. As regards the former, the scheduler collects the needed information for the binder in order to properly map the unrolled loop onto the LiM array. Hence, the number of inserted source or result LiM rows is given by the number of loop iterations. On the other hand, the latter represents a peculiar case effectively detected by the scheduler, in which one of the two source operands is also the destination one. In this situation, the binder identifies the set of LiM rows that contain the data to be accumulated, and it inserts rows with intermediate results following a *reduction tree* strategy, in order to compute the final result.

Along with the LiM array described above, LiMCompiler is also responsible for the generation of a data structure handling the control flow of the mentioned architecture. Its main aim is to keep track of the active time of each LiM row. This type of information is fundamental in order to properly simulate the behaviour of the overall structure, but also to estimate its dynamic power consumption thanks to DExIMA.

#### **Code Emission**

The code emission phase, which is handled by *PrintDexFile* class, is in charge of generating the output configuration file for DExIMA, starting from the data structures that describe the final LiM system produced by the Octantis synthesis process. This file is crucial to provide DEXiMA with both the synthesized LiM architecture and the control flow of instructions that are meant to be executed, which is useful for the dynamic simulation. The description of the array takes place as a traditional RTL circuit. First of all, the memory dimension has to be specified. Then, LiM cells composing the structure have to be declared specifying their internal logic. In parallel, the definition of *interconnections* has to be provided, which can be either *inter* or *intra cells*. The former refers to the connection between two different LiM rows, thus having a "vertical" flow of information. The latter indicates connections inside a single row. This case occurs when an addition operation is mapped, having to propagate the carry among the cells of the same row. This type of connection is not made explicit by Octantis, however, PrintDex-File recognizes it and properly defines it in the configuration file.

During Octantis first release, it has been decided not to print the section regarding control signals due to the fact that DExIMA simulation details were under study. However, Octantis could provide in output the full list of memory rows with their respective active time, in order to perform a quick debug on the generated structure.

# Part II The expansion of Octantis

## Introduction and Motivations

During the previous dissertation, an overview of the Octantis project has been provided. As already highlighted, the expressiveness of the input C algorithm is highly limited, mainly due to the fact that certain C structures are not easy or even feasible to map on an hardware component. Furthermore, being Octantis in its early stages, it has been decided to focus on providing the internal structure of the program with a *modular* organization rather than handling complex code constructs, which has been left to future expansions of the tool. Hence, the main aim of this thesis work is to **broaden the set of C structures to be considered by the Octantis synthesis process**. The choice of the algorithmic constructs to be taken into account has been made examining the possible benefits that they could derive from parallel processing on LiM systems.

Switch and for loops represent the main basic C statements that the first version of Octantis could manage. While the former does not take much advantage from a LiM implementation, the latter is certainly more likely to profit from the intrinsic *parallel capabilities* of the Logic-in-Memory paradigm. As a matter of fact, a *loop unrolling* pass has been specifically designed in order to fully exploit the mentioned characteristic. However, Octantis synthesis could only handle:

- Simple for loops with *no nesting structures*.

- *Trivial access* only to *one-dimensional arrays* inside loops, namely the common row major order.

The innovations introduced in the scope of this work mainly aim at overcoming these limitations, giving Octantis the possibility to manage **loop**  **nests** and the synthesis of instructions involving **one/two-dimensional arrays**, whose elements can be visited following well-defined **Array Access Patterns**. At the same time, the extent of use of loop unrolling has been enlarged in order to cope with the new structures. As a matter of fact, if data dependencies are avoided, the LiM system can hugely benefit from the application of the mentioned technique, especially in terms of execution time. Moreover, this expansion of the tool represents a step forward in the analysis of LiM capabilities in relation to *data-intensive applications*, which are highly affected by the drawbacks of the *Von Neumann bottleneck*, as already pointed out in the introduction of the thesis.

As will be better clarified during the next chapters, a new Pass called **Info-Collector** has been introduced at the beginning of Octantis synthesis process, with the purpose of handling the *increased amount of information* coming from the input C algorithm. It organizes it exploiting dedicated data structures that are also useful for the subsequent phases. The introduction of this preliminary pass has indeed led to the **expansion of the previous structure of Octantis**. Furthermore, **target-dependent optimizations** have been explored in order to minimize the amount of needed hardware resources used for the final LiM architecture, whose area occupation may become huge when considering more complex data-intensive algorithms.

Finally, the code emission phase has been enlarged with the addition of two modules. The former addresses the generation of a **VHDL description** of the LiM structure, including both the declaration of the datapath and the control unit useful to properly drive the execution of the algorithm. A *VHDL testbench* is also provided in order to test the correct behaviour of the system. The latter is responsible for the production of the needed configuration files for the new **DExIMA-CAD** tool, which allows a visual representation of the LiM architecture.

The innovations carried out towards the expansion of Octantis are presented and discussed during the next chapters. First of all, an introduction to the *Polyhedral Model* is provided in Chapter 3, since InfoCollector Pass and the rest of the synthesis process exploit several data structures that are originated from the main concepts and definitions of this model. After that, the actual innovations are highlighted. The introduction of *InfoCollector* is presented in Chapter 4. The aims and strategies adopted by the pass regarding the handling of information are addressed, as well as the employed data structures. In Chapter 5 the expansion of Octantis structure is addressed, highlighting the modifications to the HLS stages and the benefits they have derived from the introduction of the new pass are described. Successively, the expansion of the code emission phase is discussed in Chapter 6. Finally, Chapter 7 is dedicated to the *test cases* that have been devised in order to verify the behaviour of the implemented innovations and gather meaningful results.

### Chapter 3

## Polyhedral Model: a powerful mathematical framework

#### 3.1 Introduction to the Polyhedral Model

InfoCollector takes advantage of some of the mathematical definitions that belong to the *polyhedral model* in order to effectively organize and successively use the information regarding *nested loops* and *array accesses*.

The polyhedral model is a mathematical framework whose theoretical foundations can be traced back to the work carried out by Karp, Miller, and Winograd in 1968 within their seminal contribution called The Organization of Computations for Uniform Recurrence Equations[11]. After that, several studies[12] were conducted addressing the possibility of representing programs by means of a set of linear equations, with the purpose of restructuring them for parallel execution. Moreover, a great contribution was given by the researches on loop transformations[13] and systolic arrays design[14] that were carried out between the 70s and the 80s. During the 90s, all the mentioned theoretical bases led to the actual development of the first tools that enabled the use of polyhedral optimizations, such as PIP[15] and PolyLib[16].

In the last decades, the polyhedral model has been considered in the field of **compilation tools** as it is capable of providing an innovative way of representing programs that can be exploited for **optimized code generation**. Nowadays, the large adoption of parallel hardware accelerators, such as Graphic Processing Units (GPUs), requires compilers to implement proper code analyses and transformations to let the algorithms benefit from the mapping on such kinds of devices. The polyhedral model ensures a *finegrained representation* of the program, which is achieved by means of the construction of mathematical relationships among several variables of interest present in the program itself. This is particularly useful in applications characterized by a large number of operations, such as algorithms with loop nests. This model allows addressing the entire set of loop iterations at once, thus devising restructuring opportunities that enable advanced optimization techniques aimed at the parallelization of the program.

The progress made in the exploration of the capabilities of the polyhedral model led to the birth of the so-called **polyhedral compilation**[17], which includes the set of compilation analysis and optimization techniques that rely on the representation provided by the model. It has been already employed in many compiler tools, such as Polly[18] for what concerns the LLVM framework. Its application has been also proposed to be employed in other contexts, including *memory usage optimizations*[19], code generation for high-level synthesis[20]. Moreover, the polyhedral community has a strong academic background and it is a lively research community, always exploring possible further applications of the model.

#### **3.1.1** Definitions and concepts

The mathematical objects around which the theory of the polyhedral framework revolves are referred to as **Polyhedra**. They consist of sets of points in a  $\mathbb{Z}$  vector space whose borders are originated by a set of **linear inequal***ities*. The main aim of this model is to represent a program by means of polyhedra, which can be manipulated using mathematical transformations in order to optimize the code that originated them. The exploitation of this representation is well-suited for algorithms characterized by the presence of *loops*.

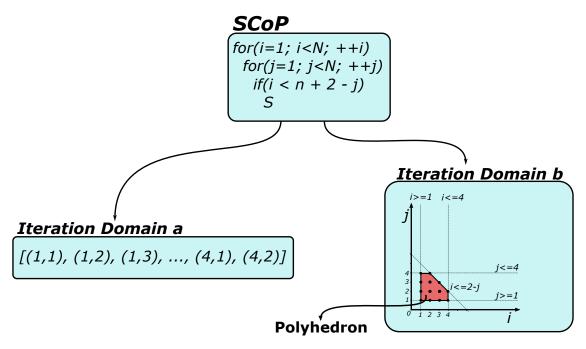

Each loop in a program is characterized by *boundaries* and, eventually, *conditionals*, which are identified by *if statements* that can be present in the loop itself. The operands that are involved in the definition of both loop boundaries and conditionals must only depend on *loop iterators* and *constants* in order to produce the mentioned inequalities that generate a polyhedron. The set of consecutive statements in the code where loop bounds and conditionals satisfy these requirements is defined as **Static Control Part** (SCoP).

The discussed features can be also expressed by means of a proper mathematical formalism. To begin with, in programming languages like C, an *n*-deep loop nest can be represented through an *n*-entry vector called **Iteration Vector**:

$$\vec{x} = (i_1, i_2, \dots, i_{n-1}, i_n) \tag{3.1}$$

Each element  $i_k$  indicates the iterator of the  $k^{th}$  loop, where k indicates the depth of the loop itself, n being the innermost one. Since iterators can assume multiple values depending on the characteristics of the related loop, many iteration vectors are originated, and they identify the **Iteration Domain**. It can also be represented by the set of linear inequalities that stem from loop bounds and conditionals mentioned above.

Figure 3.1. A SCoP with the possible representations of the related Iteration Domain. Iteration Domain a is the set of all iteration vectors, while b shows the linear inequalities that, in turn, form the 2-dimensional polyhedron.

Figure 3.1 shows an example SCoP and the related visualizations of the

iteration domain. As it can be noticed in the referenced Figure, a *twodimensional polyhedron* has been generated by representing the iteration domain on the *ij*-plane. The number of dimensions that characterize this mathematical object is equal to the maximum depth of the loop nest.

At this point in code analysis, the generation of optimized code relies on the proper *scanning of polyhedra* that have been produced. However, this thesis work addresses the handling of nested loops towards the efficient parallelization and mapping of operations involving arrays onto a LiM architecture. Hence, other concepts that belong to the same model and deal with the management of array accesses have been considered, thus leaving the optimization of the algorithm to eventual improved future versions of Octantis.

In the polyhedral model, each array access is assigned with an **Array Access Function**. In order to allow its comprehension, the concept of **Access Vector** must be introduced. Given a *m*-dimensional array  $A[a_1][a_2]...[a_{M-1}][a_M]$ , it is defined as:

$$R_A = (a_1, a_2, \dots, a_{M-1}, a_M) \tag{3.2}$$

Each of the possible values that  $R_A$  can assume enables access to a specific element of the array A, and the set of all these values forms the **Array Domain**. The array access function is defined as:

$$F: D_I \longrightarrow D_A, \tag{3.3}$$

where  $D_I$  is the iteration domain and  $D_A$  is the array domain, and its main purpose is to provide information about the element of the array A that is visited during a specific iteration of the loop nest. The function can be expressed by means of the following matrix equation:

$$F\begin{pmatrix}i_{1}\\i_{2}\\\cdot\\\cdot\\\cdot\\i_{n-1}\\i_{n}\end{pmatrix} = APM_{A}\begin{pmatrix}i_{1}\\i_{2}\\\cdot\\\cdot\\\cdot\\\cdot\\\cdot\\i_{n-1}\\i_{n}\end{pmatrix} + APMC_{A}$$

(3.4)

where APM is an  $M \ge N$  matrix that will be hereinafter referred to as Access Pattern Matrix (APM) that multiplies the  $N \ge 1$  iteration vector, and the result is added to the so-called Access Pattern Matrix Constant (APMC), which is  $M \ge 1$ . APM and APMC can identify a well-defined Array Access Pattern for the array A that indicates the order in which the elements of the array are visited in the loop nest.

#### 3.1.2 The Loop Array Dependence graph

As already mentioned, one of the main tasks that the InfoCollector module must accomplish consists in the collection of information about nested loops and array accesses. This would allow obtaining the access pattern for each array instance in the algorithm, and consequently performing the mapping of the related operations onto a LiM system. Hence, InfoCollector needs to implement a proper solution to enable the *efficient organization of data regarding loops nests and arrays in order to create all the needed APMs and APMCs*, which will be exploited for the *correct mapping of operations during the binding phase*.

The concept of Loop Array Dependence Graph (LAD) has been developed in [21] the context of design space exploration for HLS tools. It is capable of representing the relationships among loops belonging to the same nest but also between the loops and arrays accesses. The formal definition of the LAD graph is the following:

• Given:

1. a loop nest L composed of N loops:  $L = L_1, L_2, ..., L_{N-1}, L_N$

2. a set A of M arrays accessed inside the nest:  $A = A_1, A_2, ..., A_{M-1}, A_M$

- The LAD is the the directed graph G(V, E) where:

- 1.  $V = L \cup A$

- 2. E is made up of the following edges:

- $-(L_i, L_{i-1})$ , if elements of L appear in order from the outermost to the innermost, as  $L = L_1, L_2, ..., L_{N-1}, L_N$ .

- $-(L_i, A_j)$ , if array  $A_j$  is accessed using the iterator that belongs to loop  $L_i$ .

Figure 3.2. A simple C code with 3 nested loops is provided along with the associated LAD graph and the APMs and APMCs of each array.

A visual representation of the LAD graph is provided along with the C code that generates it in Figure 3.2. APMs can be easily retrieved by combining the information regarding the depth of each loop inside its nest and the iterators that contribute to the formation of the array indexes. As a matter of fact, the ordered organization of loops allows obtaining the iteration vector. The edges between an array and a loop node can be exploited in order to properly fill the related APM as follows:

- Given that array A is  $M \ge N$  and L loops are present:

- If the edge  $(L_i, A_j)$  is present and the iterator of  $L_i$  contributes to index k of A, the element at position (k, i) of the APM will be the integer n that multiplies the iterator in its occurrence within the array index.

- If the edge  $(L_i, A_j)$  is present but the iterator of  $L_i$  does not contribute to index k of A, the element at position (k, i) of the APM will be zero.

- If the edge  $(L_i, A_j)$  is not present, the element at position (i) in each row of the APM will be zero.

On the other hand, the elements of APMCs can easily be retrieved by checking for the presence of constants in the index of the array instance under consideration.

Figure 3.2 shows an example C code with the related LAD graph and the APMs and APMCs belonging to each of the three arrays instances inside the loop nest. As will be better explained in the following chapters, InfoCollector implements a strategy that takes great inspiration from how the LAD graph organizes these types of information. The main aim is to generate the APMs and APMCs, which are further analyzed to retrieve the access pattern of each array in order to perform the correct parallelization of operations while mapping them onto the final LiM system.

## Chapter 4

# InfoCollector: a preliminary analysis pass

#### 4.1 Introduction

Due to the necessity to handle more complex C constructs and data structures that can be employed for the description of the input algorithm, a new pass called **InfoCollector** has been developed. It has been introduced as it performs an appropriate *analysis of the LLVM IR code* to allow the upcoming stages, binding and scheduling, to efficiently *manage the access to* 1/2-dimensional arrays inside nested loops.

Several concepts presented in Chapter 3 have been exploited. As a matter of fact, gathering useful information for the creation of *Access Pattern Matrices* is one of the key tasks addressed by InfoCollector, as they represent the central objects around which the mapping and parallelization of operations on the LiM system revolve.

The set of data structures and the techniques implemented by InfoCollector are discussed in detail during the dissertation of the following sections, as they constitute a fundamental *preliminary step* that lays the foundation for the evolution of the scheduling and binding phases.

#### 4.2 The collection of information

As it can be easily noticed by its name, InfoCollector mainly focuses on the *collection of information from the LLVM IR code*. As a consequence, the structure, the organization of the control flow and the meaning of each instruction of LLVM IR must be clear to carry out this task in an efficient way. For this reason, during the dissertation about the various analysis performed by InfoCollector, several aspects of LLVM IR will be deepened, thus allowing a better understanding of the strategies adopted. Three main operations that address the gathering of information are implemented by the new pass:

- 1. Alias Analysis aims at the identification of multiple local registers that are used as aliases of a variable that has been allocated at the beginning of the IR program. A proper data structure is exploited to keep track of the relationship between aliases. It is extremely useful not only for other analysis operations carried out by InfoCollector itself but also to let the scheduling phase properly accomplish its task by quickly detecting data dependencies between instructions.

- 2. Loop Analysis is aimed at recognizing loop iterators, operands that identify loop bounds and, most importantly, the order of loops inside a nest. It highly exploits the fixed form that characterizes LLVM *natural loops*, presented in 4.2.2, in order to detect the mentioned parameters. The information gathered is fundamental for the creation of a structure inspired by the LAD graph.

- 3. **Pointer Analysis** explores the body of a loop searching for pointers, which are used in the LLVM IR code to perform accesses to arrays. They are easily recognizable as they are the result of the *getelementptr* instruction. Once identified, they are analyzed in order to contribute to the completion of the LAD graph.

In the next sections, the techniques adopted to carry out these three kinds of analysis are detailed.

#### 4.2.1 The importance of alias analysis

Here, the strategy that has been devised to execute *alias analysis* is considered. Before that, further details regarding the LLVM IR code structure are presented, as they are important for the proper comprehension of the technique implemented.

According to the LLVM IR conventions, any variable belonging to the input program has to be reserved its relative space inside the stack region of the memory using the *alloca* instruction. It returns a pointer to the mentioned location, which is stored in a local register. When an operation is performed, the required variable is fetched from the memory by means of a *load*, and it is put inside an internal register. As regards arrays, the required section in the stack frame has to be allocated as well at the beginning of the program. When an operation requires access to an array, the *getelementptr* instruction is used, as it returns a pointer that can be stored in a register. Then, it is used by a load operation as an address in order to retrieve the correct element of the array from the memory.

The objective of the alias analysis performed by InfoCollector is to keep track of the relationship between the values returned by alloca instructions and:

- For every **single variable**, the list of all *local registers where the same variable has been stored*.

- For each **array**, the list of *pointers used to access it*.

The data structure that has been exploited to specify the mentioned relations is a C++ map, named **aliasInfoMap**. It consists of an associative array composed of elements called *pairs*, each one having a unique key identifier and a related value field. This arrangement perfectly suits the modelling of information required by this task, as the creation of a univocal connection between the two parts mentioned above can be implemented. The strategy adopted to populate the data structure is reported in the following:

- When an **alloca** is detected, a new pair is created using its destination register as the key field, and it is inserted in aliasInfoMap. The associated value is left empty, waiting to be filled.

- When a **load** is found, if the operand of the instruction corresponds to a key inside aliasInfoMap, its destination register is added to the list of aliases in the related value field. In Listings 4.1 and 4.2, an example C code is provided along with the related LLVM IR, in which local identifiers %4 and %5 are the aliases respectively of %1 and %2.

```

Example of alias analysis for load instructions

define dso_local void @foo() #0 {

void foo(){

int A, B, C;

%1 = alloca i32, align 4

C = A + B;

%2 = alloca i 32, align 4

}

%3 = alloca i32, align 4

%4 = load i32, i32* %1, align 4

%5 = load i32, i32* %2, align 4

Listing 4.1. C code

\%6 = add nsw i32 %4, %5

store i32 %6, i32* %3, align 4

ret void

}

Listing 4.2. LLVM IR code.

```

• When a **getelementptr** is identified, its operand is searched among the various keys already present in aliasInfoMap, as it must refer to a previously allocated array. If it is found, the destination register of the getelementptr instruction is inserted in the list of aliases contained in the related value field. The example C code and the related LLVM IR are provided below in Listings 4.3 and 4.4. Registers %11 and %17 contain the pointer used for the access of arrays A and C, respectively identified in the LLVM IR with %1 and %3.

```

alias analysis for GEP instructions

void foo(){

int A[10], B, C[10];

for(int i = 0; i < 10; ++i){

C[i] = A[i] + B;

}

}

Listing 4.3. C code</pre>

```

```

alias analysis for GEP instructions

define dso local void @foo() #0 {

%1 = alloca [10 x i32], align 16

%2 = alloca i32, align 4

%3 = alloca [10 \times i32], align 16

%4 = alloca i32, align 4

store i32 0, i32* %4, align 4

br label %5

5:

; Loop Header

;Loop Body

8:

%9 = load i32, i32* %4, align 4

%10 = sext i32 %9 to i64

%11 = getelementptr inbounds [10 x i32], [10

x i32]* %1, i64 0, i64 %10

%12 = load i32, i32* %11, align 4

%13 = load i32, i32* %2, align 4

%14 = add nsw i32 %12, %13

%15 = load i32, i32* %4, align 4

%16 = sext i32 %15 to i64

%17 = getelementptr inbounds [10 x i32], [10

x i32]* %3, i64 0, i64 %16

store i32 %14, i32* %17, align 4

br label %18

18:

; Loop Latch

21:

ret void

}

Listing 4.4. LLVM IR code

```

• A sext instruction may be present right after a load in order to perform a sign extension of the value fetched from the memory. This is done only if the operation that successively elaborates the operand requires it. In these cases, the destination register of the sext instruction is considered as an alias of the variable retrieved by means of the previous load. The data structure created by means of the described process is a *support object* to the other operations performed by InfoCollector, as well as to the scheduling phase. As a matter of fact, each time an operation has to be carried out, alias registers are created either due to load or getelementptr instructions. Hence, the discussed analysis is fundamental to quickly identify which variable or array is addressed.

InfoCollector highly exploits aliasInfoMap during its exploration of loops and pointers, mainly in order to efficiently recognize the loop iterators that contribute to the formation of pointers and the arrays visited by means of the latter. On the other hand, the scheduler needs this type of information to properly construct the list of instructions to be mapped on the final LiM system.

#### 4.2.2 The handling of loops

As already pointed out, Octantis highly focuses on *for-loops*, as their proper management can allow for the implementation of parallel execution of operations on a LiM architecture. As a matter of fact, the tool performs loop unrolling whenever such structure is identified in the code, supposing *no correlations are present among different iterations due to data dependencies*. They indeed constitute the main threat to concurrent execution, and they must be avoided as much as possible in the development of the algorithm.

However, if loop unrolling is effectively carried out, *multiple operations sharing the same time frame can be mapped on a LiM system*, thus fully exploiting its intrinsic parallel capabilities. While the overall area occupation of the final circuit may become quite large, growing with the complexity of the input program, timing performance benefits significantly, remaining rather low even with more elaborated algorithms.