#### POLITECNICO DI TORINO

Dipartimento Energia Tesi di Laurea Magistrale in Ingegneria Elettrica

## Testing e caratterizzazione di un raddrizzatore attivo 3-livelli T-Type per caricabatterie di veicoli elettrici

Autore: Eugenio Bossotto Relatore: Prof. Radu Bojoi

Correlatore: Matteo Gregorio

### Ringraziamenti

Prima di iniziare la trattazione ritengo doveroso procedere con i ringraziamenti.

Innanzitutto, ringrazio il Professor Radu Bojoi per aver reso possibile lo svolgimento del mio lavoro di tesi su un progetto reale e concreto che mi ha permesso di imparare moltissimo. Un ringraziamento va a Matteo Gregorio, per la pazienza e la disponibilità che mi ha sempre mostrato durante tutto il periodo della tesi oltre ai preziosi consigli forniti.

Uno ringraziamento speciale lo dedico ai miei genitori, Lorenzo e Cristina, ed alle mie sorelle, Elisa e Rebecca, per tutto il sostegno e la fiducia che mi hanno dato, permettendomi di svolgere il mio percorso nel migliore dei modi. Grazie a mia nonna Marisa che mi è sempre stata vicina e consigliato nel modo più giusto. Un immenso grazie alla mia compagna Camilla per avermi supportato con tutte le forze possibili. Infine, non meno importante degli altri, un grazie va a tutti gli amici e le persone che mi sono state vicino in questi anni rendendo tutto più semplice.

# Indice

| 1 | Obi                   | ettivi del Progetto di Tesi                                      | 6         |

|---|-----------------------|------------------------------------------------------------------|-----------|

| 2 | Intr                  | roduzione                                                        | 8         |

| 3 | Act                   | ive Front-End 3 livelli T-Type                                   | 9         |

|   | 3.1                   | Struttura 3 Livelli T-Type Interleaved                           | 10        |

|   | 3.2                   | Tecnica di Modulazione ZMPC                                      | 14        |

| 4 | Deb                   | oug e Testing: Precarica/Scarica dc-link e Anelli di Con-        |           |

|   | $\operatorname{trol}$ | lo                                                               | 15        |

|   | 4.1                   | Schema Elettromeccanico e Set-up                                 | 15        |

|   | 4.2                   | Analisi e Testing della Precarica e Scarica del Dc-link          | 20        |

|   |                       | 4.2.1 Precarica del dc-link                                      | 21        |

|   |                       | 4.2.2 Scarica del dc-link                                        | 26        |

|   | 4.3                   | Debug e Testing Anelli di Controllo delle Correnti               | 29        |

|   | 4.4                   | Debug e Testing Anelli di controllo delle Tensioni               | 36        |

|   |                       | 4.4.1 Anello di Controllo della Tensione Totale di Dc-link       | 37        |

|   |                       | 4.4.2 Anello di Controllo della Tensione di Mid-Point            | 43        |

| 5 | Alg                   | oritmo di Controllo per l'Estrapolazione Automatizzata           |           |

|   | $\operatorname{dell}$ | e Mappe                                                          | <b>47</b> |

|   | 5.1                   | Introduzione all'Estrapolazione delle Mappe, Strumenti e Tool    |           |

|   |                       | Utilizzati                                                       | 47        |

|   | 5.2                   | Algoritmi di Controllo per la Caratterizzazione del Convertitore | 54        |

|   |                       | 5.2.1 Strategia di Controllo Constant Current                    | 57        |

|   |                       | 5.2.2 Strategia di Controllo <i>Constant Voltage</i>             | 60        |

|   | 5.3                   | Squilibrio del Carico Tramite DutyCycle di Modo Comune e         |           |

|   |                       | Relativa Saturazione                                             | 62        |

| 6 | Ris                   | ultati Sperimentali                                              | 69        |

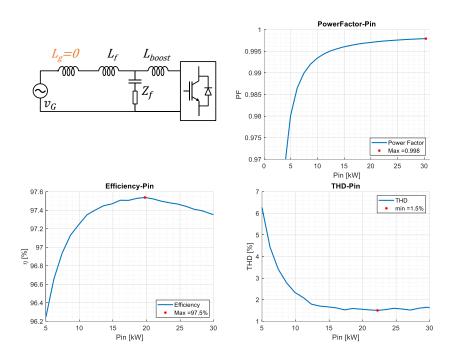

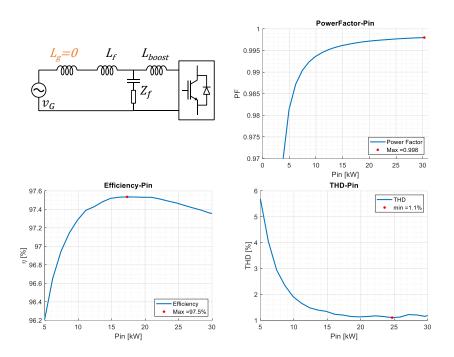

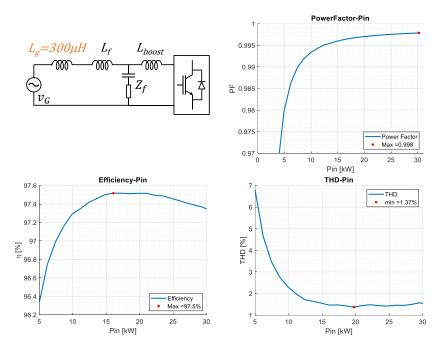

|   | 6.1                   | Test Filtro LCL in Ingresso ed Induttanza di Rete                | 71        |

|   | 6.2  | Mappe di Efficienza, THD, Fattore di Potenza e Perdite con   |       |   |

|---|------|--------------------------------------------------------------|-------|---|

|   |      | Filtro LCL e Carico Equilibrato                              | 7     | 7 |

|   | 6.3  | Mappe in Condizioni di Carico Squilibrato con e senza Satu-  |       |   |

|   |      | razione del DutyCycle di Modo Comune                         | . 86  | 3 |

|   | 6.4  | Ottenimento Sperimentale dei Limiti per la Saturazione del-  |       |   |

|   |      | l'Anello di Tensione di Mid-Point tramite LUT;               | 95    | 5 |

|   | 6.5  | Prestazioni del Convertitore in Condizioni di Fattore di Po- |       |   |

|   |      | tenza non Unitario                                           | . 98  | 3 |

| 7 | Con  | aclusioni                                                    | 101   | L |

|   | 7.1  | Conclusioni                                                  | 101   | Ĺ |

| A | Cod  | lice C Stati Macchina                                        | 103   | 3 |

|   | A.1  | Stato Soft Star                                              | 103   | 3 |

|   | A.2  | Stato Discharge dc-link                                      | . 104 | 1 |

| В | Scri | pt Matlab per Algoritmo di Controllo                         | 105   | ó |

|   | B.1  | Funzione "VoltageLoopDelta"                                  | . 110 | ) |

|   | B.2  | Funzione "ModuleCurrentLoop"                                 | . 11. | L |

|   | B.3  | Funzione "PhaseCurrentLoop"                                  | 113   | 3 |

|   | B.4  | Funzione "VoltageLoopAFE"                                    | . 114 | 1 |

|   | B.5  | Funzione "CurrentLoopDelta"                                  | . 115 | 5 |

|   | B.6  | Algoritmo per Caratterizzazione tramite Aggiunta di DutyCy-  |       |   |

|   |      | cle di Modo Comune                                           | . 116 | 3 |

ii INDICE

### Elenco delle tabelle

| 3.1 | Specifiche principali AFE                                                                                         | 10 |

|-----|-------------------------------------------------------------------------------------------------------------------|----|

|     | Condizioni utilizzate nel debug degli anelli di corrente Condizioni utilizzate nel debug degli anelli di tensione |    |

| 6.1 | Condizioni per l'esecuzione dei test sul filtro LCL ed induttanza di rete.                                        | 71 |

| 6.2 | Tabella riassuntiva delle condizioni di test sul filtro LCL, in-                                                  |    |

|     | duttanza rete e frequenza del controllo                                                                           | 73 |

| 6.3 | Condizioni per l'esecuzione delle prove a carico squilibrato                                                      | 86 |

# Elenco delle figure

| 3.1  | Schema generale caricabatterie Ultra-Fast Isolato.[4]              | 9  |

|------|--------------------------------------------------------------------|----|

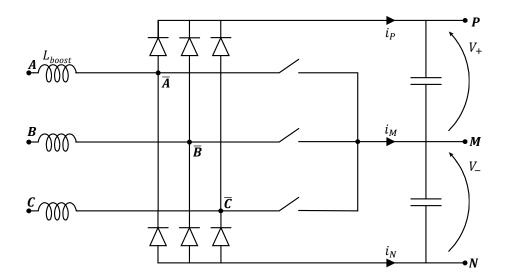

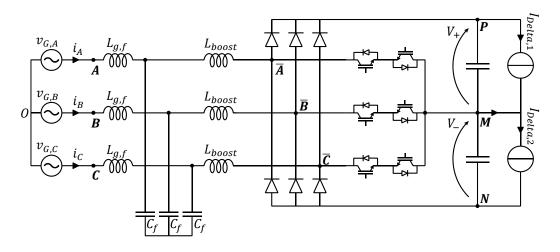

| 3.2  | Struttura a tre livelli t-type dell'AFE                            | 11 |

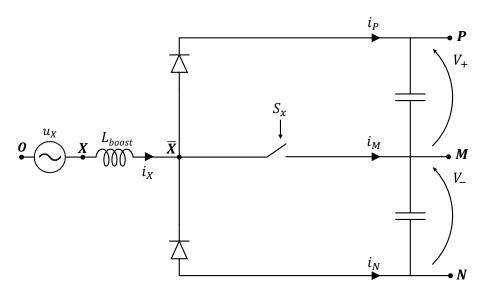

| 3.3  | Singola fase del raddrizzatore attivo                              | 11 |

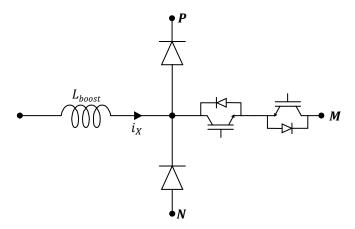

| 3.4  | Topologia T-type ad IGBT per convertitore 3-livelli                | 13 |

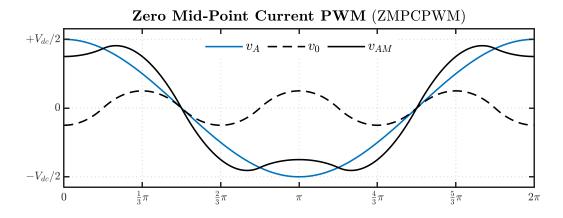

| 3.5  | Forme d'onda Zero Mid Point Current.[1]                            | 14 |

| 4.1  | Regatron TopCon TC.ACS (sx), Delta SM 500-CP-90 (dx)               | 16 |

| 4.2  | Schema elettromeccanico AFE                                        | 16 |

| 4.3  | Set-up sperimentale AFE                                            | 17 |

| 4.4  | Circuiti stampati per misure AC (sx) e DC (dx)                     | 18 |

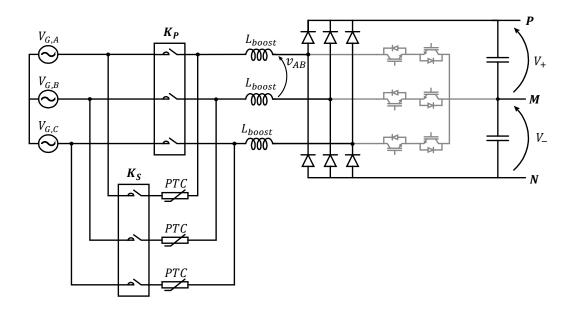

| 4.5  | Schema circuitale del convertitore completo con configurazione     |    |

|      | interleaved                                                        | 18 |

| 4.6  | Configurazione fisica del convertitore completo                    | 19 |

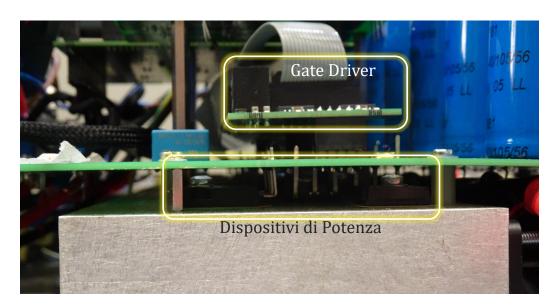

| 4.7  | Dispositivi di Potenza e Gate Driver                               | 20 |

| 4.8  | Circuito completo di precarica                                     | 22 |

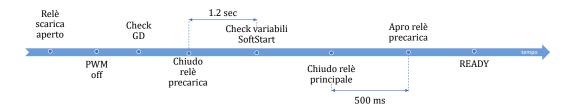

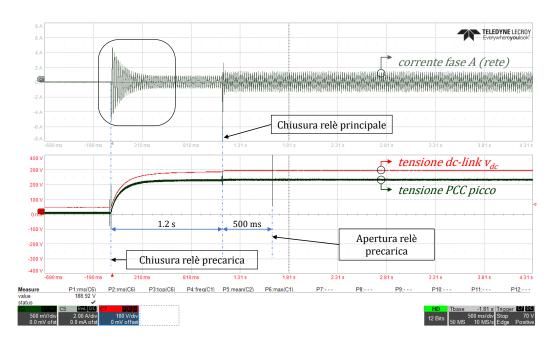

| 4.9  | Diagramma temporale precarica                                      | 22 |

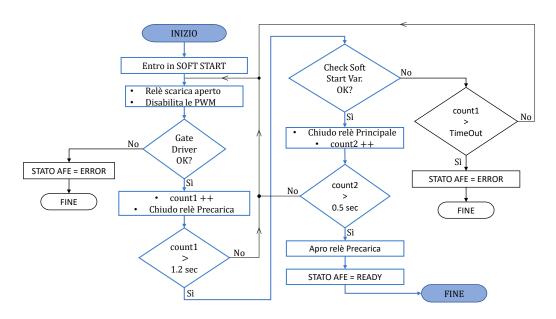

| 4.10 | Diagramma di flusso Soft Start                                     | 24 |

| 4.11 | Forme d'onda precarica, base tempi 500ms/div                       | 24 |

| 4.12 | Forme d'onda precarica, base tempi 200ms/div                       | 25 |

| 4.13 | Forme d'onda precarica a regime ed apertura relè principale        | 26 |

| 4.14 | Circuito equivalente scarica dc-link                               | 27 |

| 4.15 | Flow chart scarica dc-link                                         | 27 |

| 4.16 | Forme d'onda scarica de-link                                       | 28 |

| 4.17 | Forme d'onda scarica de-link                                       | 28 |

| 4.18 | Schema circuitale AFE                                              | 29 |

| 4.19 | Schema a blocchi anello di controllo delle correnti                | 31 |

| 4.20 | Duty cycle (in alto), correnti di fase (in basso) senza commu-     |    |

|      | tazione.                                                           | 32 |

| 4.21 | Duty cycle (in alto), correnti di fase (in basso) con $i_d^* = 0$  | 32 |

|      | Duty cycle (in alto), correnti di fase (in basso) con $i_d^* = 10$ | 33 |

|      | Duty cycle (in alto), correnti di fase (in basso) con $i_d^* = 25$ | 33 |

|      |                                                                    |    |

| 4.24 | Risposta ad un gradino di corrente da 0 a 25A                            | 34  |

|------|--------------------------------------------------------------------------|-----|

| 4.25 | Ritardi introdotti in seguito ad una variazione del riferimento          |     |

|      | di corrente                                                              | 35  |

| 4.26 | Tensioni e correnti di fase con $i_d^* = 25A$                            | 36  |

| 4.27 | Schema circuitale per il debug anelli di tensione                        | 37  |

| 4.28 | Circuito equivalente anello di controllo di tensione de-link             | 38  |

| 4.29 | Schema a blocchi anello di controllo $V_{dc}$                            | 39  |

| 4.30 | Plant anello di controllo tensione $V_{dc}$                              | 39  |

|      | Gradino di tensione $V_{dc}$ da 650V ad 800V                             | 40  |

|      | Gradino di tensione $V_{dc}$ da 650V ad 800V con forme d'onda            |     |

|      | scalate [4]                                                              | 41  |

| 4.33 | Setup per la prova sull'anello di tensione di dc-link                    | 41  |

| 4.34 | Gradino di carico da 10kW, istante iniziale                              | 42  |

| 4.35 | Gradino di carico da 10kW, istante del distacco                          | 42  |

| 4.36 | circuito equivalente anello di controllo tensione mid-point              | 43  |

| 4.37 | Schema a blocchi anello di tensione mid-point                            | 44  |

| 4.38 | Plant anello di controllo tensione di mid-point                          | 44  |

| 4.39 | Setup per la prova sull'anello di tensione di mid-point                  | 44  |

| 4.40 | Risultato della prova di sbilanciamento mid-point                        | 46  |

| 5.1  | Cohama circuitale con relativi punti di reigura                          | 48  |

| 5.2  | Schema circuitale con relativi punti di misura                           | 48  |

| 5.3  | HBM GEN4tB (sx), Power card GN310B (dx)                                  | 49  |

| 5.4  | Trasduttore di corrente LEM IT 200-S ULTRASTAB (in alto),                | 49  |

| 0.4  | condizionatore di segnale Signaltec MTCS (in basso)                      | 49  |

| 5.5  | Interfaccia grafica Perception                                           | 50  |

| 5.6  | Strumentazione: HBM, Signaltec e alimentatori DC Delta                   | 53  |

| 5.7  | Setup e collegamenti per misure di tensione e corrente                   | 53  |

| 5.8  | Schema generale comunicazione                                            | 54  |

| 5.9  | Schema temporale per trigger ed acquisizione misure                      | 55  |

|      | Diagramma di flusso della prima parte dell'algoritmo per la              | 90  |

| 5.10 | definizione delle condizioni della prova                                 | 56  |

| 5 11 | Schema equivalente del setup per la modalità constant current.           | 57  |

|      | Diagramma di flusso per strategia di controllo Constant Current.         | 59  |

|      | Schema equivalente del setup per la modalità constant voltage.           | 60  |

|      | Diagramma di flusso per strategia di controllo <i>Constant Voltage</i> . | 62  |

|      | Correzione del duty cycle di modo comune per il bilanciamento            | 02  |

| 0.10 | delle tensioni in uscita                                                 | 63  |

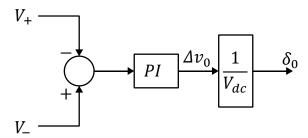

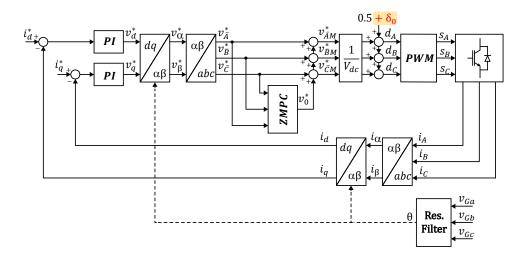

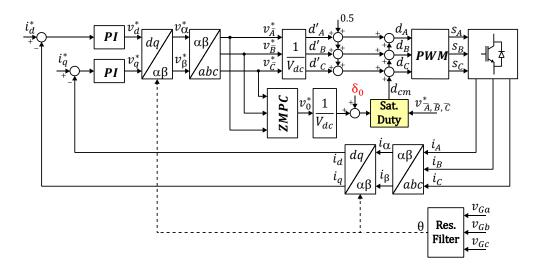

| 5.16 | Schema a blocchi con aggiunta della quota costante di duty               | 55  |

| J.10 | cycle di modo comune                                                     | 63  |

|      |                                                                          | 5 5 |

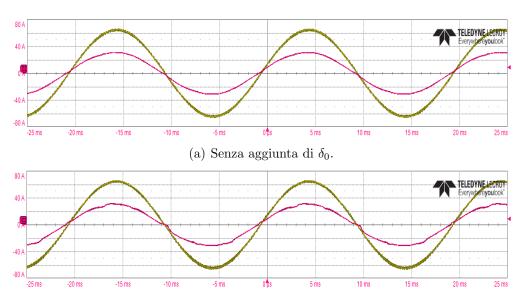

| 5.17 | Confronto tra corrente (rosa) e tensione (ocra) di fase con                                                                |     |

|------|----------------------------------------------------------------------------------------------------------------------------|-----|

|      | e senza aggiunta di duty cycle di modo comune costante $\delta_0$ ;                                                        |     |

|      | $V_G = 230V_{rms}, i_d^* = 30A \text{ e } V_{dc} = 800V. \dots \dots \dots \dots \dots$                                    | 64  |

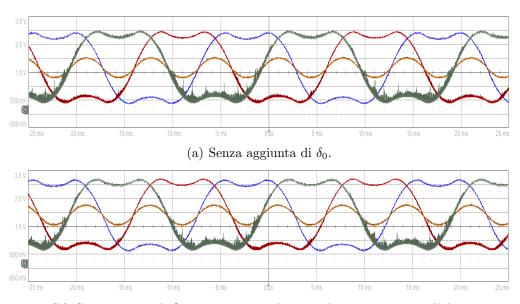

| 5.18 | Confronto dei duty cycle con e senza aggiunta di $\delta_0$                                                                | 64  |

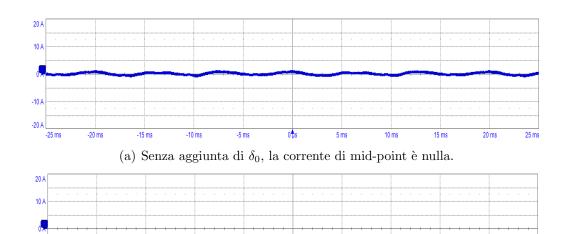

| 5.19 | Confronto della corrente di mid-point con e senza aggiunta di                                                              |     |

|      | $\delta_0$                                                                                                                 | 65  |

| 5.20 | Schema a blocchi con implementazione della saturazione dei                                                                 |     |

|      | duty cycle                                                                                                                 | 65  |

| 5.21 | Confronto tra corrente (rosa) e tensione (ocra) di fase con e senza saturazione del duty cycle di modo comune, a parità di | 0.0 |

|      | $\delta_0$ ; $V_G = 230V_{rms}$ , $i_d^* = 30A \text{ e } V_{dc} = 800V$                                                   | 66  |

| 5.22 | Confronto tra duty cycle con e senza saturazione del duty cycle                                                            | 0.0 |

|      | di modo comune, a parità di $\delta_0$                                                                                     | 66  |

| 5.23 | Confronto tra corrente di mid-point con e senza saturazione                                                                |     |

|      | del duty cycle di modo comune, a parità di $\delta_0$                                                                      | 67  |

| 5.24 | Diagramma di flusso per la caratterizzazione del convertitore                                                              | 0.0 |

|      | tramite aggiunta di duty cycle di modo comune $\delta_0$                                                                   | 68  |

| 6.1  | Tabella schematica riassuntiva delle prove svolte                                                                          | 70  |

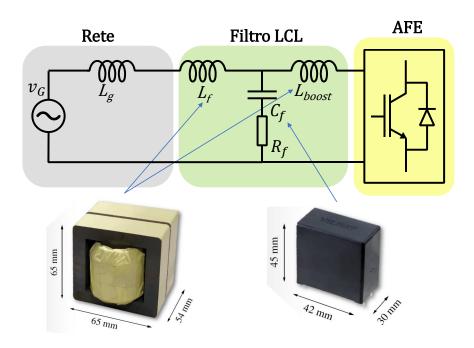

| 6.2  | Schema monofase equivalente per l'esecuzione dei test sul filtro                                                           |     |

|      | LCL ed induttanza di rete                                                                                                  | 72  |

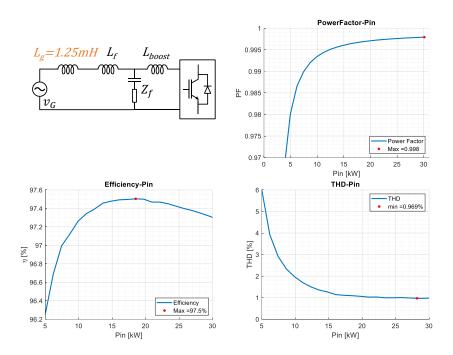

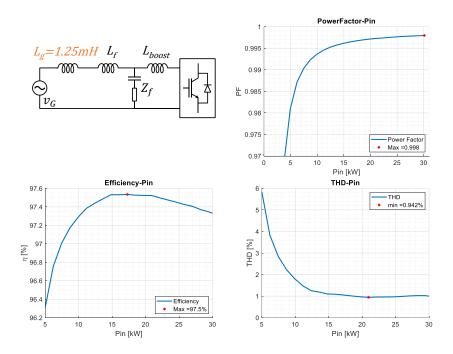

| 6.3  | Risultati test A su LCL e induttanza rete                                                                                  | 73  |

| 6.4  | Risultati test B su LCL e induttanza rete                                                                                  | 74  |

| 6.5  | Risultati test C su LCL e induttanza rete                                                                                  | 74  |

| 6.6  | Risultati test D su LCL e induttanza rete                                                                                  | 75  |

| 6.7  | Risultati test E su LCL e induttanza rete                                                                                  | 75  |

| 6.8  | Confronto delle prestazioni tra i vari setup con filtro LCL                                                                | 76  |

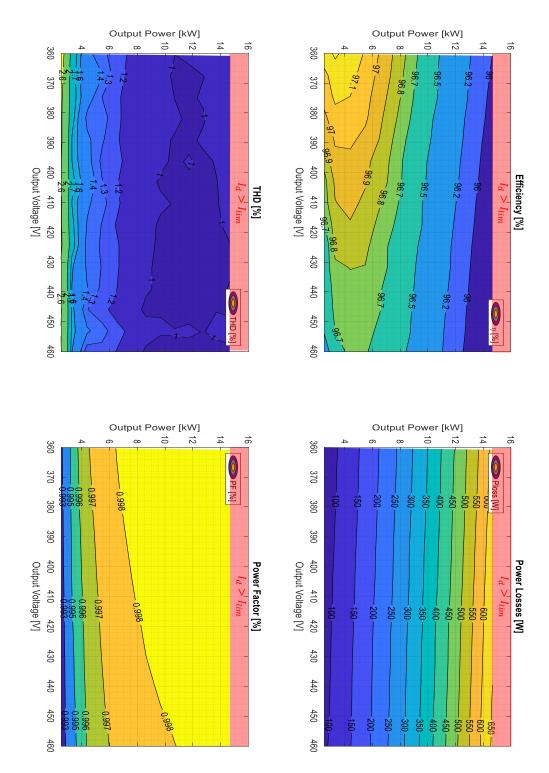

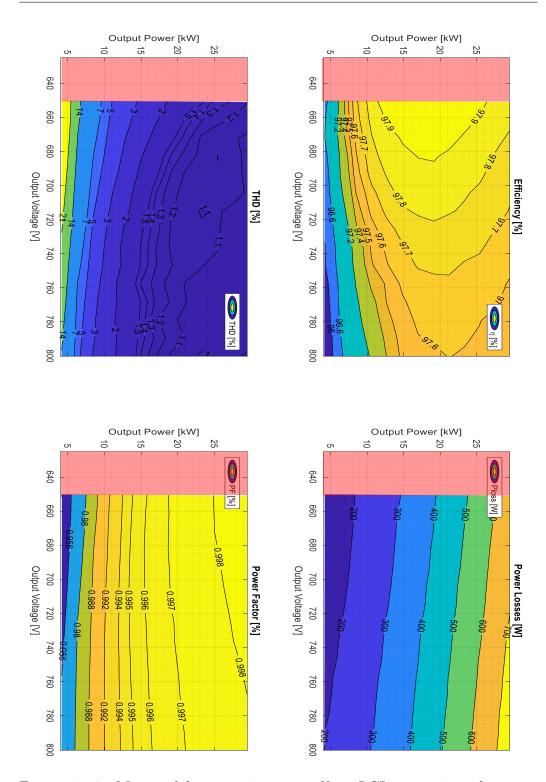

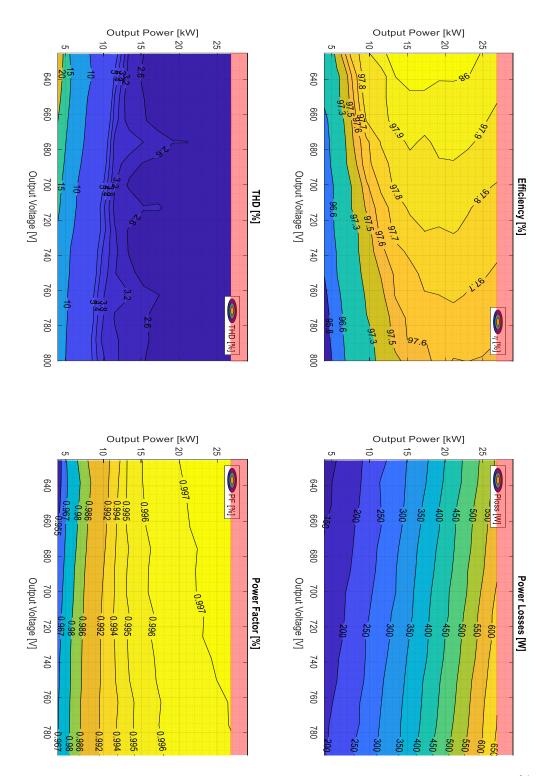

| 6.9  | Mappe del convertitore con filtro LCL e tensione di rete a                                                                 |     |

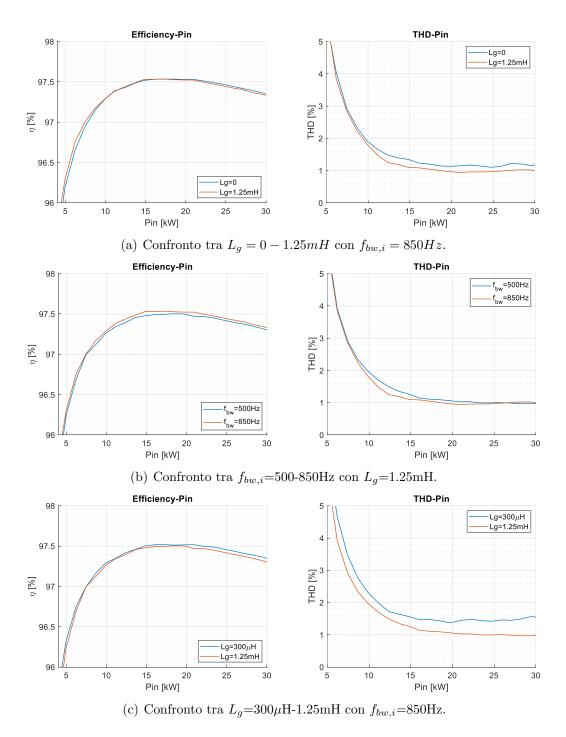

|      | $120-10\% \ V_{rms}$                                                                                                       | 78  |

| 6.10 | Mappe del convertitore con filtro LCL e tensione di rete a                                                                 |     |

|      | $120V_{rms}$                                                                                                               | 79  |

| 6.11 | Mappe del convertitore con filtro LCL e tensione di rete a                                                                 |     |

|      | $120+10\% V_{rms}$                                                                                                         | 80  |

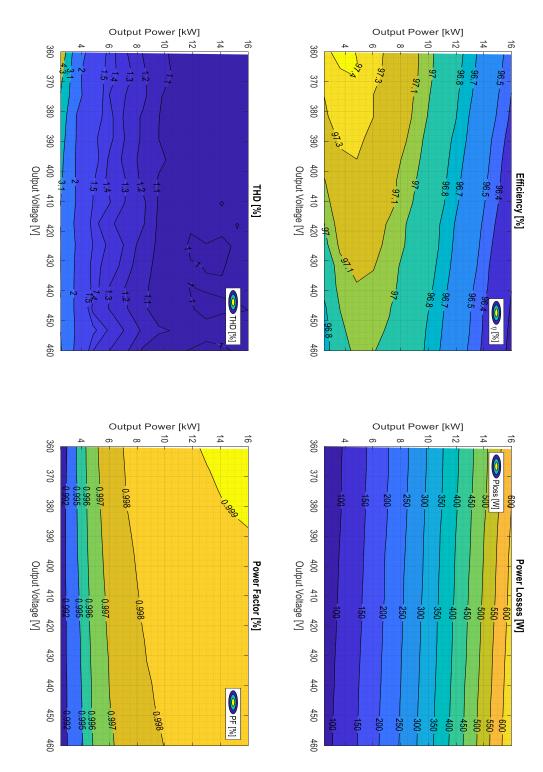

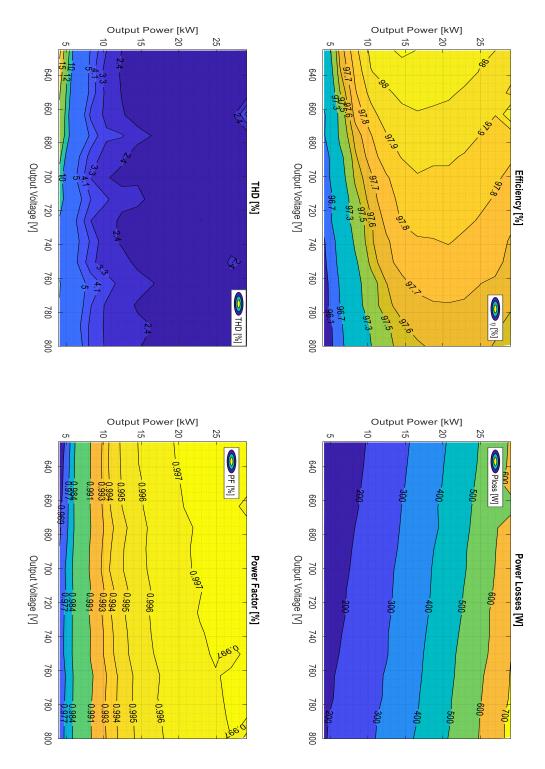

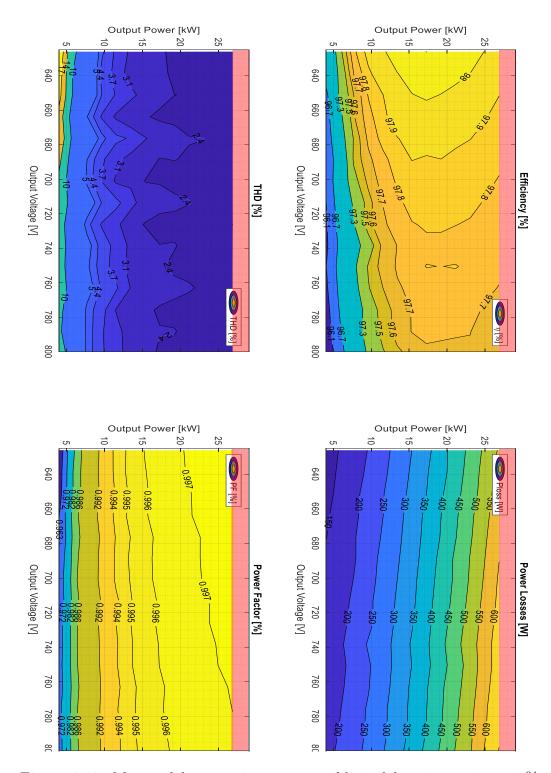

| 6.12 | Mappe del convertitore con filtro LCL e tensione di rete a                                                                 |     |

|      | $230\text{-}10\% \ V_{rms}$                                                                                                | 81  |

| 6.13 | Mappe del convertitore con filtro LCL e tensione di rete a                                                                 |     |

|      | $230V_{rms}$                                                                                                               | 82  |

| 6.14 | Mappe del convertitore con filtro LCL e tensione di rete a                                                                 |     |

|      | $230+10\%V_{rms}$                                                                                                          | 83  |

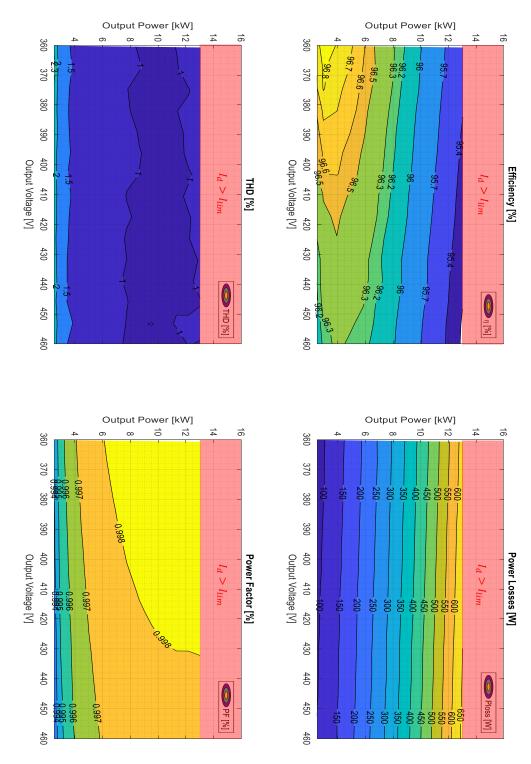

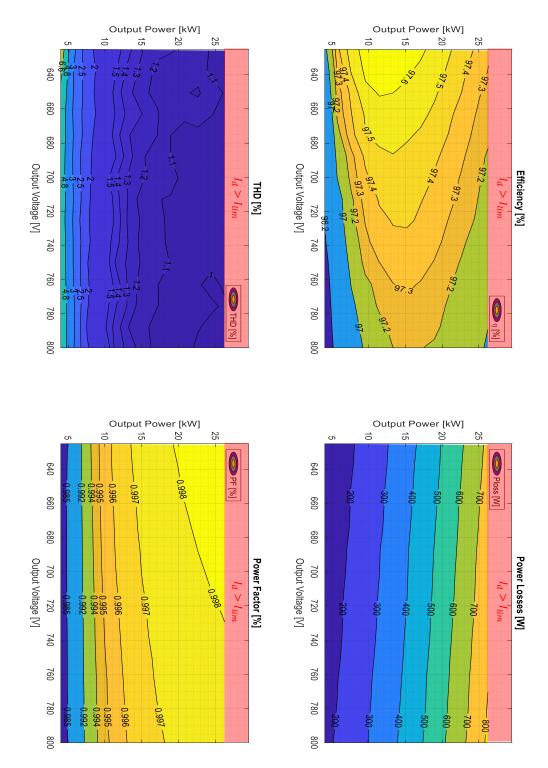

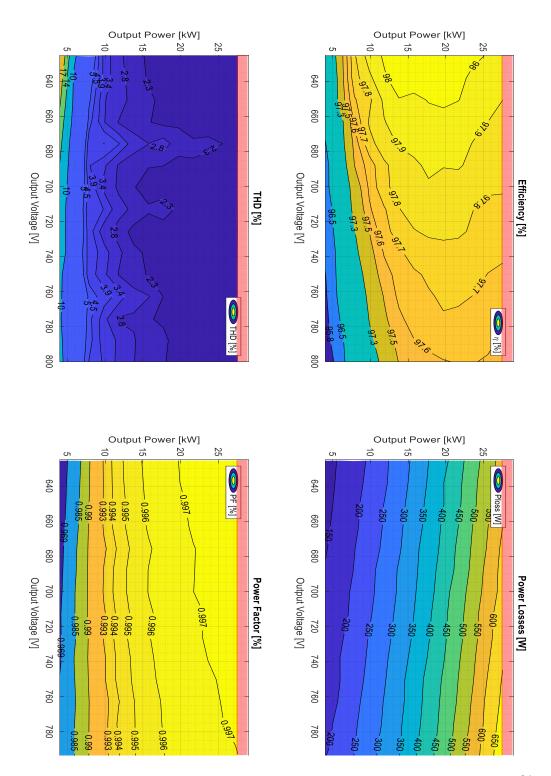

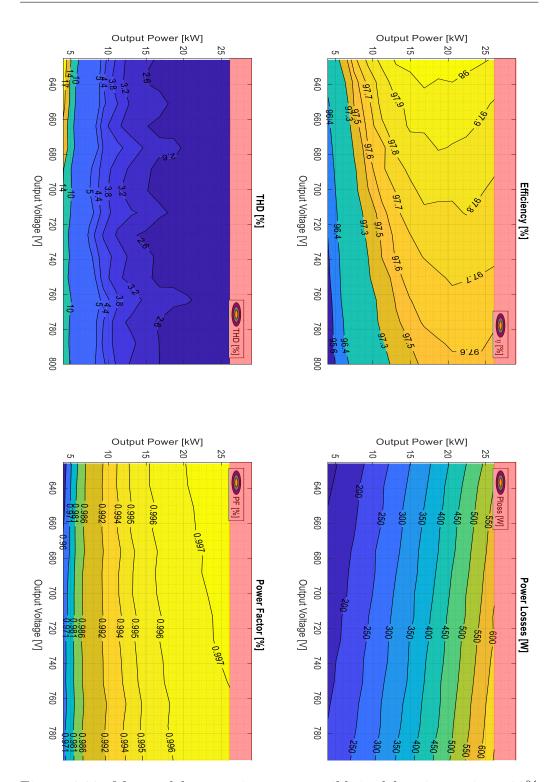

| 6.15 | Mappe del convertitore con carico equilibrato                                                                              | 87  |

| 6.16 | Mappe del convertitore con squilibrio del carico pari a $+10\%$ ,      |     |

|------|------------------------------------------------------------------------|-----|

|      | saturazione del duty cycle di modo comune disattivata                  | 88  |

| 6.17 | Mappe del convertitore con squilibrio del carico pari a -10%,          |     |

|      | saturazione del duty cycle di modo comune disattivata                  | 89  |

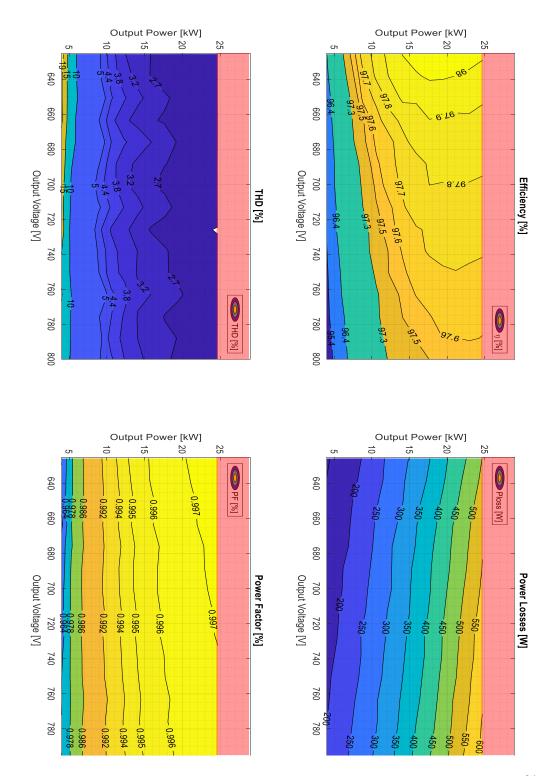

| 6.18 | Mappe del convertitore con squilibrio del carico pari a $+15\%$ ,      |     |

|      | saturazione del duty cycle di modo comune disattivata                  | 90  |

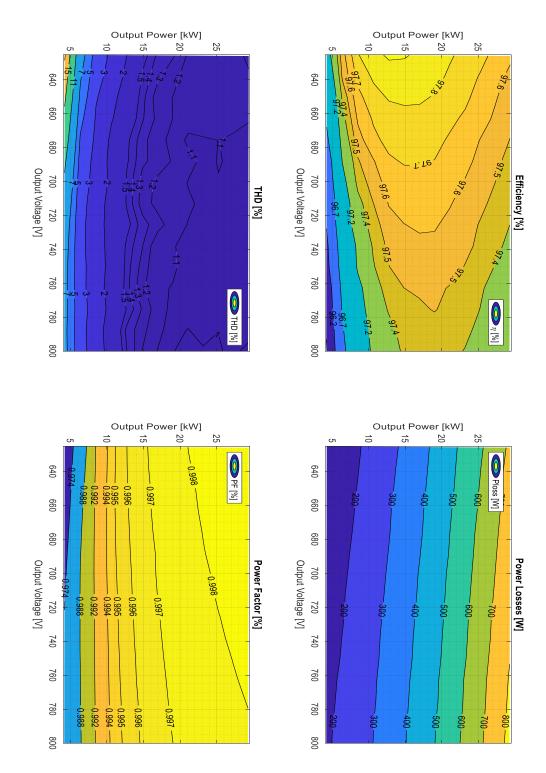

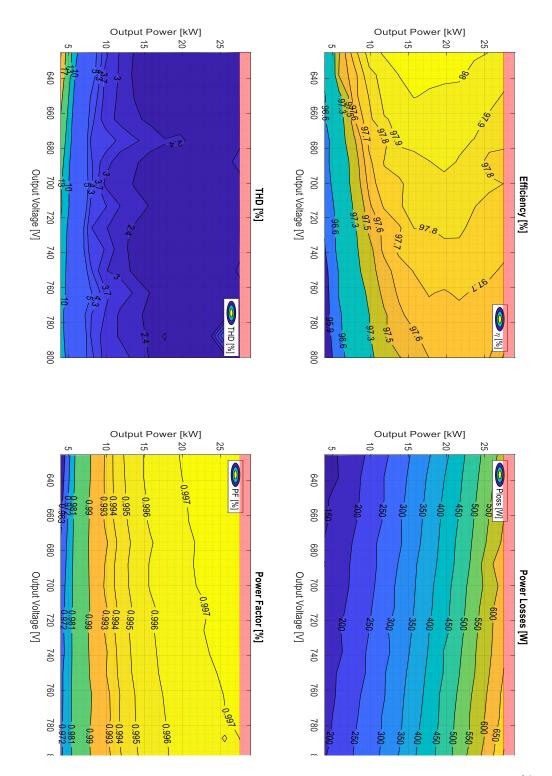

| 6.19 | Mappe del convertitore con squilibrio del carico pari a $+15\%$        |     |

|      | con saturazione del duty cycle di modo comune attiva                   | 91  |

| 6.20 | Mappe del convertitore con squilibrio del carico pari a $+20\%$        |     |

|      | con saturazione del duty cycle di modo comune attiva                   | 92  |

| 6.21 | Mappe del convertitore con squilibrio del carico pari a $+30\%$        |     |

|      | con saturazione del duty cycle di modo comune attiva                   | 93  |

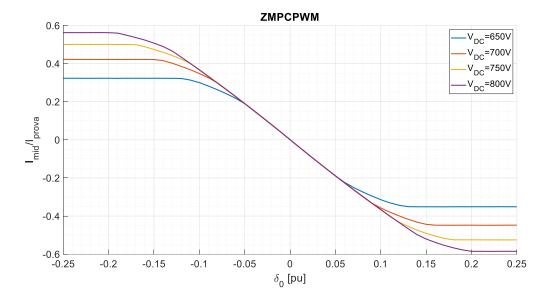

| 6.22 | Corrente di mid-point in funzione dell'addizione del duty cycle        |     |

|      | di modo comune $\delta_0$ con tecnica di modulazione ZMPCPWM           | 95  |

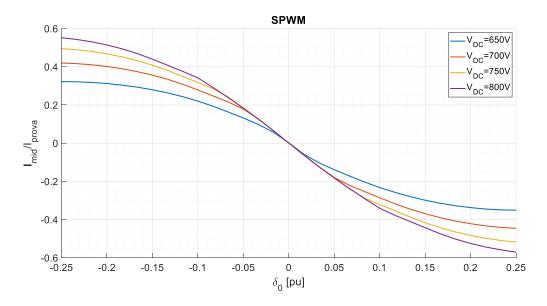

| 6.23 | Corrente di mid-point in funzione dell'addizione del duty cycle        |     |

|      | di modo comune $\delta_0$ con tecnica di modulazione SPWM              | 96  |

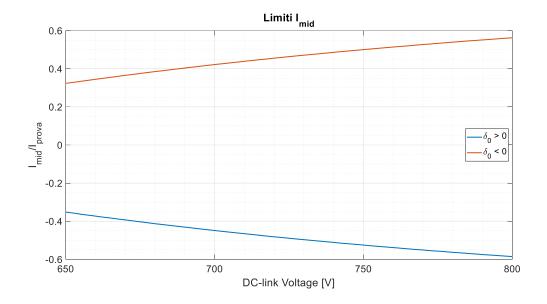

| 6.24 | Limiti per la saturazione dell'anello di tensione di mid-point         |     |

|      | con tecnica di modulazione ZMPCPWM                                     | 97  |

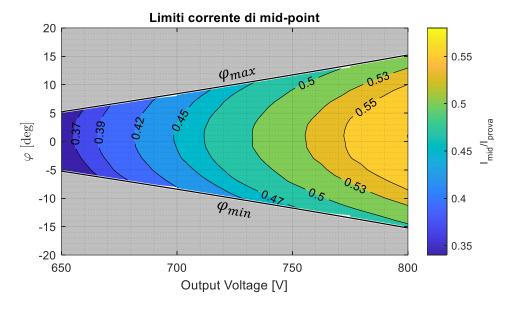

| 6.25 | Limiti della corrente di mid-point in funzione dell'angolo $\varphi$ e |     |

|      | tensione di dc-link                                                    | 98  |

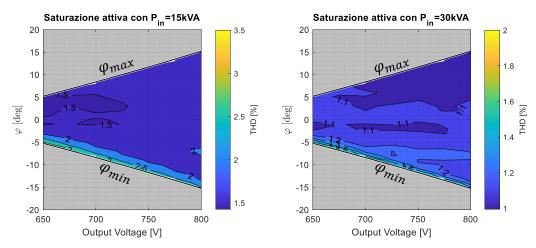

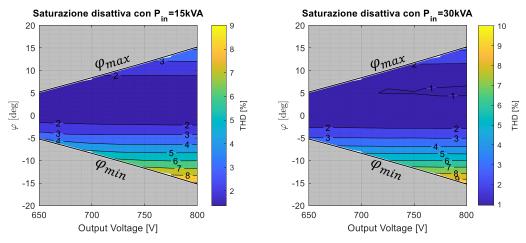

| 6.26 | Prestazioni in termini di THD per funzionamento a fattore di           |     |

|      | potenza non unitario con e senza saturazione di modo comune.           | 99  |

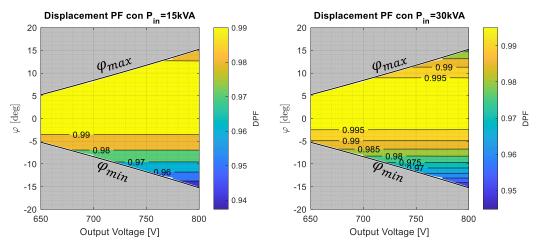

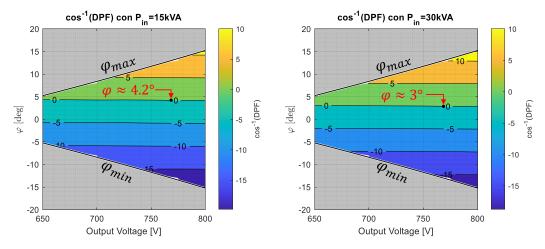

| 6.27 | Prestazioni in termini di Displacement Power Factor (DPF)              |     |

|      | e relativo angolo per funzionamento a fattore di potenza non           |     |

|      | unitario                                                               | 100 |

### Obiettivi del Progetto di Tesi

Il lavoro di tesi in questione è stato sviluppato nell'ambito del centro interdipartimentale PEIC Power Electronics Innovation Center del Politecnico di Torino lavorando su un progetto che ha come obiettivo la realizzazione di un caricabatterie ultra-fast che permetta la ricarica di autoveicoli elettrici in tempi molto ridotti. Il caricabatterie ha una struttura modulare in cui ogni singolo modulo ha un potenza nominale di 60kW ed è costituito da due stadi di conversione, un stadio ac/dc ed uno dc/dc isolato. Il mio progetto di tesi è stato svolto sullo stadio ac/dc, il quale è un Active Front End a tre livelli T-Type che si interfaccia con la rete elettrica.

Lo scopo principale del progetto di tesi è quello di testare la precarica/scarica del dc-link, gli anelli di controllo di corrente e tensione del convertitore ed infine sviluppare l'algoritmo di controllo atto ad ottenere l'estrapolazione delle mappe di efficienza, THD, fattore di potenza e perdite del raddrizzatore attivo tramite una procedura automatizzata di acquisizione delle misure e dei dati. Durante la prima parte del lavoro di tesi ho effettuato l'allestimento del prototipo e il relativo set-up per la connessione delle sorgenti di carico/alimentazione e degli strumenti di misura e di acquisizione dati. Successivamente, ho lavorato sulla procedura e relativa implementazione di precarica e scarica del dc-link ed al debug degli anelli di controllo delle correnti e delle tensioni in modo tale da assicurarsi che il convertitore esegua le varie regolazioni in maniera corretta, così da poter procedere, infine, alla stesura dello script Matlab per l'implementazione dell'algoritmo di controllo per gestire la parte di comunicazione con tutti gli strumenti che partecipano al funzionamento del raddrizzatore attivo e all'aquisizione dei dati per la successiva caratterizzazione del convertitore.

Il progetto di tesi presentato è suddiviso nei seguenti capitoli:

#### 1. Obiettivi del Progetto di Tesi

- 2. Introduzione

- 3. Active Front-End 3 livelli T-Type

- 4. Debug e Testing: Precarica/Scarica dc-link e Anelli di Controllo

- 5. Algoritmo di Controllo per l'Estrapolazione delle Mappe

- 6. Risultati Sperimentali

- 7. Conclusioni

### Introduzione

Al giorno d'oggi è ormai un dato di fatto che ci sia un costante aumento dei veicoli elettrici (EV) ed ibridi (PHEV) in circolazione. Per fare fronte alle esigenze degli utenti di EV, esiste la necessità di orientarsi verso tecnologie di ricarica ad alta potenza che permettano di ridurre le problematiche annesse all'utilizzo di vetture elettriche ed in grado di effettuare la ricarica delle loro batterie in tempi molto contenuti, in modo tale da poter essere paragonabili e competitivi nei confronti dei tempi di rifornimento delle automobili tradizionali. Il caricabatterie in oggetto ha una struttura modulare in cui ogni singolo modulo ha un potenza nominale di 60kW ed è costituito da due stadi di conversione, un stadio ac/dc ed uno dc/dc isolato. Il mio progetto di tesi è stato svolto sullo stadio ac/dc formato da un Active Front End tre-livelli T-Type, che si interfaccia direttamente con la rete elettrica. La scelta di utilizzare una struttura a tre livelli implica un aumento della complessità del sistema ed inoltre rende necessario l'utilizzo di quattro anelli di controllo, due per le correnti che viene eseguito sugli assi di riferimento dq e due per le tensioni di dc-link che vanno rispettivamente a regolare la tensione totale di dc-link e quella di mid-point, poiché essendo presente uno split dc-link bisogna mantenere le tensioni equilibrate su entrambe le parti; nonostante ciò, la struttura adottata risulta comunque essere un ottimo candidato per affrontare le esigenze sia della rete con cui si interfaccia che quelle degli utenti di veicoli elettrici, garantendo tensione constante di dc-link ed ottime prestazioni in termini di efficienza, distorsione armonica della corrente assorbita e fattore di potenza pressoché unitario, oltre al fatto di permettere l'utilizzo di semiconduttori con tensione nominale inferiore rispetto alle soluzioni più comuni a due livelli, riducendo inoltre lo stress sugli elementi reattivi lato ac.

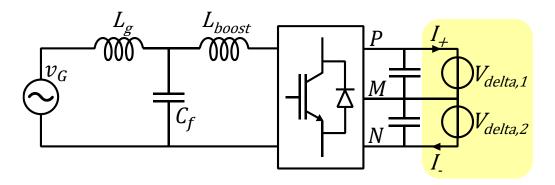

## Active Front-End 3 livelli T-Type

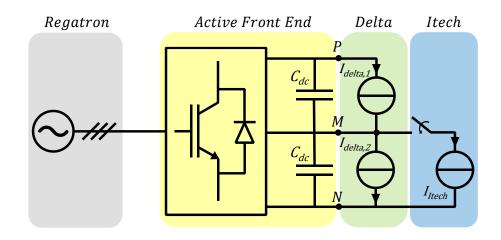

Il presente lavoro di tesi tratta il convertitore lato rete, da qui ne deriva la dicitura "Front-End", che è situato all'interno di un caricabatterie ultra-fast isolato per la ricarica rapida degli autoveicoli elettrici, il quale prevede l'utilizzo di due stadi di conversione inseriti tra la rete e l'autoveicolo come mostrato in Fig. 3.1. Essendo il convertitore che si interfaccia direttamente con la rete elettrica si tratta di un convertitore AC/DC con le seguenti proprietà:

- Power Factor Corrector (*PFC*);

- Struttura Tre Livelli;

- Topologia T-type;

- Interleaved;

- Unidirezionale.

Figura 3.1: Schema generale caricabatterie Ultra-Fast Isolato.[4]

Le specifiche principali richieste dal convertitore sono mostrate nella tabella seguente:

| Potenza Nominale          | 60        | kW        |

|---------------------------|-----------|-----------|

| Tensione Nominale AC      | 120/230   | $V_{rms}$ |

| Tensione Nominale dc-link | 650 - 800 | $V_{dc}$  |

| Corrente di Picco         | 125       | A         |

| Fattore di Potenza        | $\sim 1$  | /         |

| Frequenza di Commutazione | 20        | kHz       |

| Frequenza Rete            | 50/60     | Hz        |

Tabella 3.1: Specifiche principali AFE.

Lo scopo principale del convertitore è quindi quello di convertire il flusso di potenza alternata della rete trifase in continua, utilizzabile per la ricarica di batterie, garantendo un fattore di potenza pressoché unitario e distorsione armonica molto contenuta (THD ridotto).

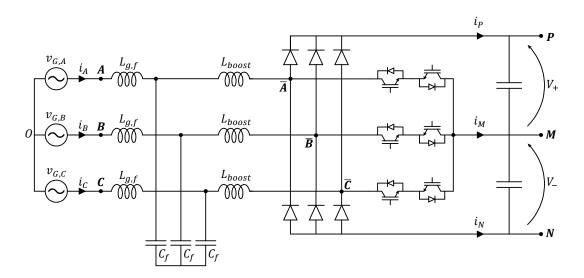

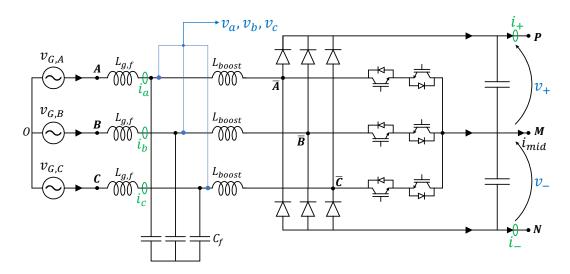

### 3.1 Struttura 3 Livelli T-Type Interleaved

La struttura completa a tre livelli utilizzata per l'Active Front-End (AFE) in questione è costituita principalmente da un ponte trifase a diodi che ha la funzione di raddrizzare la tensione alternata in ingresso ed è anche il motivo per cui il convertitore risulta unidirezionale, più 3 devices bipolari e bidirezionali comandabili in modo da formare tre gambe d'inverter come mostrato in Fig. 3.2.

La scelta di utilizzare un convertitore tre livelli, rispetto al due livelli, comporta un aumento della complessità del circuito, necessita l'utilizzo di un maggior numero di switches e si ha un grado di libertà in più da gestire, apportando però anche diversi benefici tra cui:

- Riduzione dell'induttanza di input;

- Perdite di commutazione ridotte;

- Riduzione dei filtri EMI.

Figura 3.2: Struttura a tre livelli t-type dell'AFE.

Come si può vedere in Fig. 3.2 in ingresso al convertitore è presente una induttanza, la quale ha anche una funzione filtrante oltre a quella di boost. Inoltre, si può notare che nel convertitore è presente un punto medio M, quindi, rispetto ai due stati possibili (-1, 1) presenti nei convertitori 2-livelli, si avrà a disposizione uno stato ulteriore ottenendo così i tre stati (P,M,N) del 3-livelli.

Riferendosi al circuito di una generica fase X, mostrato in Fig. 3.3, si possono ricavare le equazioni 3.1 e 3.2.

Figura 3.3: Singola fase del raddrizzatore attivo.

$$v_{\bar{X}M} = (1 - S_X) \cdot sign(i_X) \cdot \frac{V_{dc}}{2}$$

(3.1)

$$V_{dc} = V_{+} + V_{-} \quad con \quad V_{+} = V_{-} = \frac{V_{dc}}{2}$$

(3.2)

Dall'equazione 3.1 si possono quindi ricavare le tensioni generate nei 3 stati:

$$\begin{cases} Stato \ P: & v_{\bar{X}M} = +\frac{V_{dc}}{2} \\ Stato \ M: & v_{\bar{X}M} = 0 \\ Stato \ N: & v_{\bar{X}M} = -\frac{V_{dc}}{2} \end{cases}$$

La presenza del termine  $sign(i_X)$  è data dall'unidirezionalità del convertitore. Inoltre, le tensioni e correnti di fase del convertitore risultano essere:

$$v_{\bar{X}} = v_{\bar{X}M} - v_0 \tag{3.3}$$

$$i_{\bar{X}} = \frac{u_X - v_{\bar{X}}}{j \cdot \omega \cdot L_{boost}} \tag{3.4}$$

Nelle (3.3) e (3.4) si fa riferimento alla frequenza fondamentale ed i termini  $v_0$  e  $u_X$  indicano rispettivamente la tensione di modo comune, definita nella (3.5) e la tensione di rete.

$$v_0 = \frac{v_{\bar{A}M} + v_{\bar{B}M} + v_{\bar{C}M}}{3} \tag{3.5}$$

Come detto precedentemente, per formare le tre gambe d'inverter è necessario utilizzare devices comandabili, bipolari e bidirenzionali che però nella pratica non esistono, portando quindi a dover combinare più di un semiconduttore per ottenere le proprietà desiderate. Nel convertitore trattato è stata utilizzata la topologia T-type ottenendo la bidirezionalità combinando due IGBT in antiserie come mostrato in Fig. 3.4.

Figura 3.4: Topologia T-type ad IGBT per convertitore 3-livelli.

Nella configurazione mostrata, bisogna utilizzare diodi fast e dimensionati per tensione pari a quella del dc-link per il ponte raddrizzatore trifase mentre, per quanto riguarda gli interruttori comandabili, è sufficiente dimensionarli per una tensione pari a  $\frac{V_{dc}}{2}$  ed i relativi diodi possono non essere veloci. Questa topologia apporta anche i seguenti benefici al sistema:

- Perdite per conduzione molto basse;

- Numero di semiconduttori contenuto rispetto ad altre topologie;

- Richiede un solo gate-driver per gamba.

In aggiunta, sempre dal circuito mostrato in figura 3.4 e dalla (3.1) si può notare che lo stato (P, M, N) in cui ci si trova è determinato dal segno della corrente  $i_X$  ottenendo le seguenti condizioni:

$$\begin{cases} Stato \ P: & se \ i_X > 0, \ interruttori \ OFF \\ Stato \ M: & se \ i_X > 0, \ interruttori \ ON \\ Stato \ N: & se \ i_X < 0, \ interruttori \ OFF \\ Stato \ M: & se \ i_X < 0, \ interruttori \ ON \end{cases}$$

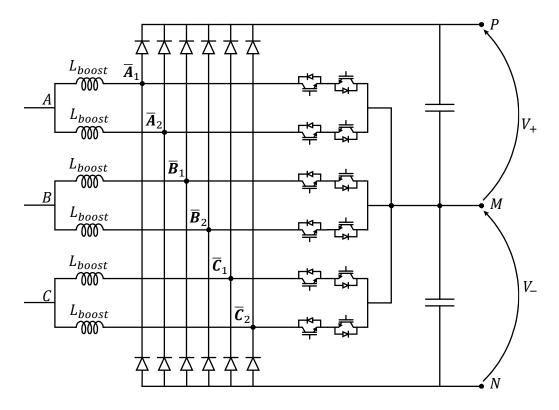

Vista l'elevata potenza e sopratutto il valore della corrente di picco richiesta, è stato deciso di utilizzare la configurazione *interleaved*, riducendo così lo stress termico sui semiconduttori. La configurazione in oggetto consiste nel porre in parallelo due convertitori identici come quelli in Fig. 3.2, facendoli

operare alla stessa frequenza di commutazione  $f_{comm}$  ma con la possibilità di inserire uno sfasamento  $\alpha_{PWM}$  tra le due portanti dei convertitori con limite:

$$0 \le \alpha_{PWM} \le \pi \quad [rad] \tag{3.6}$$

In base alla scelta del valore di  $\alpha_{PWM}$  si potranno avere benefici differenti. Utilizzare questa configurazione comporta però la possibilità di avere una corrente di circolazione ad alta frequenza di modo comune, in parte già limitata dalla presenza di  $L_{boost}$  ma comunque da controllare.

#### 3.2 Tecnica di Modulazione ZMPC

Un ultimo e rapido cenno, poiché non è argomento di questa tesi, riguarda la tecnica di modulazione utilizzata: la Zero Mid Point Current PWM. In questa tecnica di modulazione il modo comune iniettato è molto simile ad una sinusoide di terza armonica come è possibile vedere in Fig. 3.5, il quale scopo è quello di minimizzare il valore medio della corrente di mid-point (punto medio M).

Figura 3.5: Forme d'onda Zero Mid Point Current.[1]

### Debug e Testing: Precarica/Scarica dc-link e Anelli di Controllo

Nel seguente capito viene descritto il lavoro preliminare che ho svolto, il quale consiste in 3 parti principali:

- 1. Cablaggio e schema elettromeccanico

- 2. Precarica e scarica del convertitore

- 3. Debug Anelli di controllo di corrente e tensione

### 4.1 Schema Elettromeccanico e Set-up

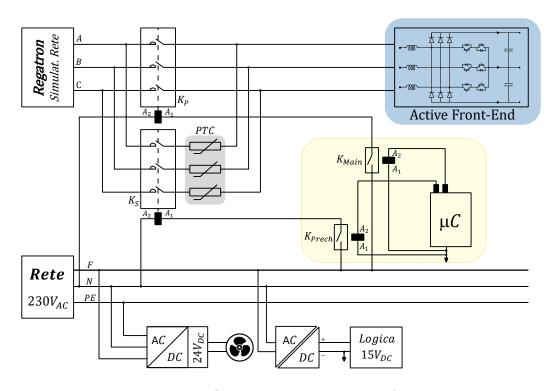

Il primo passo, oltre al cablaggio del convertitore, è stato quello di creare lo schema elettromeccanico mostrato in Fig. 4.2 nel quale è posto l'Active Fronte End, poiché c'è la necessità di collegare in ingresso al convertitore un alimentatore AC trifase programmabile che avrà il compito di emulare la rete elettrica ed in uscita il carico DC, in modo tale da avere il set-up ottimale per eseguire successivamente tutte le prove necessarie alla caratterizzazione completa del convertitore.

Come alimentatore programmabile AC ho usato un emulatore di rete a quattro quadranti Regatron TopCon TC.ACS, mentre per il lato DC due alimentatori bidirezionali Delta SM 500-CP-90 collegati in serie così da poter svolgere le prove alla tensione massima che può raggiungere il dc-link nel normale funzionamento, in quanto il singolo strumento ha una tensione massima di lavoro pari a 500V. Entrambi gli alimentatori sono mostrati in Fig. 4.1.

Figura 4.1: Regatron TopCon TC.ACS (sx), Delta SM 500-CP-90 (dx).

Figura 4.2: Schema elettromeccanico AFE.

Nello schema elettromeccanico si possono evidenziare cinque macro blocchi:

- Alimentazioni in AC: Regatron e rete monofase  $230V_{AC}$ ;

- $\bullet\,$ Relè di potenza  $K_P$ e  $K_S$  con le relative PTC di precarica;

## 16 CAPITOLO 4. DEBUG E TESTING: PRECARICA/SCARICA DC-LINK E ANELLI DI CONTROLLO

- Relè di controllo  $K_{Prech}$  e  $K_{Main}$  per azionare quelli di potenza;

- Alimentatore AC/DC  $24V_{dc}$  per alimentare le ventole di raffreddamento;

- Alimentatore AC/DC isolato  $15V_{dc}$  per l'alimentazione della logica di controllo.

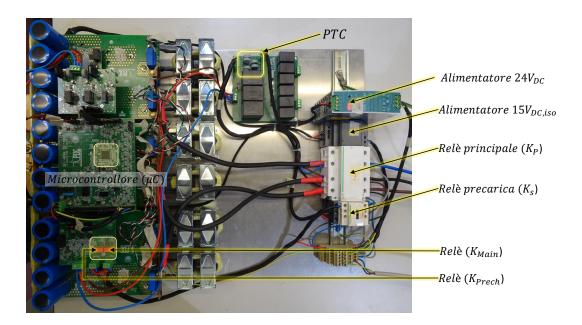

Tutti i componenti dello schema elettromeccanico sono mostrati nella seguente immagine che descrive il set-up reale utilizzato nelle prove sperimentali.

Figura 4.3: Set-up sperimentale AFE.

Come si può notare in Fig. 4.3, ai lati del PCB su cui è installato il micro-controllore ne sono presenti altri due. Il primo PCB, su cui sono installati i due relè di controllo arancioni  $K_{Prech}$  e  $K_{Main}$ , integra anche gli amplificatori isolati che vengono impiegati per le misure in AC della terna delle tensioni di rete, mentre nel PCB sul lato opposto sono presenti i convertitori DC/DC utilizzati per le misure in continua delle tensioni di dc-link e le due PTC con i relativi MOSFET di comando per eseguire la scarica del dc-link. Tutti i componenti sono mostrati in Fig. 4.4.

Figura 4.4: Circuiti stampati per misure AC (sx) e DC (dx).

Figura 4.5: Schema circuitale del convertitore completo con configurazione interleaved.

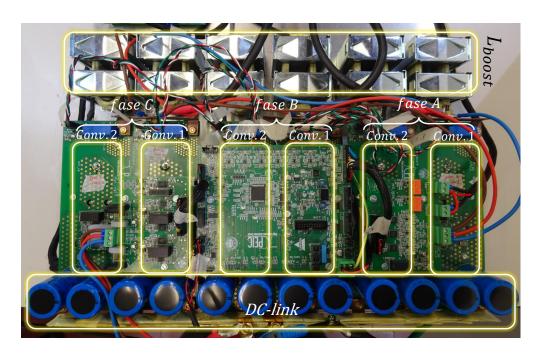

Infine, come già detto nel capitolo precedente, il convertitore completo è in configurazione interleaved ottenuta dalla messa in parallelo di due convertitori 3-livelli t-type come quelli in Fig. 3.2. Si ha quindi che il convertitore è composto da sei gambe e 3 fasi come appena mostrato in Fig. 4.5. Per quanto riguarda la configurazione reale del convertitore, la parte dei dispositivi di potenza non è facilmente visibile essendo che i devices sono montati tra il circuito stampato di potenza e il dissipatore di calore. Per capire la reale disposizione delle sei gambe si può fare riferimento alla Fig. 4.6 dove si può vedere la posizione delle sei gambe del convertitore con le relative induttanze di boost (una per gamba) e alla figura 4.7 dove viene mostrato il convertitore lateralmente.

Figura 4.6: Configurazione fisica del convertitore completo.

Figura 4.7: Dispositivi di Potenza e Gate Driver.

# 4.2 Analisi e Testing della Precarica e Scarica del Dc-link

In seguito alla descrizione hardware dell'AFE, ora si passa al lato software. Si tratta di un controllo digitale, in linguaggio C, implementato su microcontrollore STM32G474 basato su architettura 32-bit ARM®Cortex®in cui gli stati di funzionamento del convertitore sono regolati attraverso una macchina a stati. Quindi, prima di entrare nello specifico riguardo alla precarica e scarica del convertitore è utile definire in modo generale gli stati di macchina, in modo da contestualizzare meglio la parte a venire. Gli stati di macchina sono i seguenti sei:

- 1. Calibration: è lo stato eseguito inizialmente all'avvio del convertitore dove avviene l'azzeramento degli offset sulle misure di corrente;

- 2. *Error*: stato successivo all'intervento di una qualsiasi protezione dove vengono disabilitate le PWM, aperti tutti i relè e si controlla che la tensione del dc-link rispetti le soglie di sicurezza;

- 3. Soft Start: ha come obiettivo la carica del dc-link. Vengono eseguiti i comandi, discussi in questo capitolo, per effettuare la precarica del dc-link;

### 20 CAPITOLO 4. DEBUG E TESTING: PRECARICA/SCARICA DC-LINK E ANELLI DI CONTROLLO

- 4. Discharge dc-link: ha come obiettivo la scarica del dc-link per mantenere la tensione di uscita ad un valore di sicurezza, come lo stato precedente verrà discusso in questo capitolo;

- 5. Ready: il convertitore ha verificato che non ci siano errori ed è quindi pronto ad entrare in funzionamento, mantenendo ancora disabilitate le PWM vengono settate le correnti di riferimento a zero aspettando il comando di start;

- 6. Go: vengono abilitate le PWM ed si esegue la routine di controllo.

Nei paragrafi seguenti si analizzeranno nel dettaglio gli stati di *Soft Start* e *Discharge dc-link*. Per un corretto funzionamento del convertitore è necessario effettuare una soft-charge del dc-link prima di connettersi direttamente con la rete nel caso in cui esso si trovi ad una tensione inferiore ad un valore minimo stabilito, in modo tale da evitare elevate correnti di inserzione e immissione di disturbi.

Altrettanto importante è la possibilità di effettuare la scarica del dc-link nel caso in cui il convertitore vada in fault, abbia un guasto oppure venga semplicemente spento o scollegato dalla rete trifase, così da portare la tensione dc-link ad un valore inferiore a 50V, garantendo le condizioni di sicurezza. Tutte le prove effettuate in questo capitolo sono state svolte senza l'inserimento di un induttanza di rete.

#### 4.2.1 Precarica del dc-link

Visto l'elevato valore di capacità presente  $(4080\mu\text{F}$  sia per il dc-link inferiore che superiore), al completamento della precarica sul dc-link si otterrà una tensione di poco inferiore al valore di picco della tensione di alimentazione, che nel caso di un sistema trifase coincide con il valore di picco della concatenata, come espresso nella seguente relazione.

$$V_{dc,prec} = V_+ + V_- = \sqrt{2} \cdot \sqrt{3} \cdot V_G \tag{4.1}$$

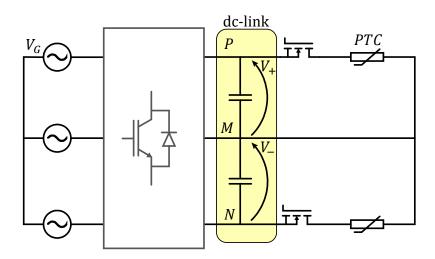

Il sistema in esame è quello mostrato in Figura 4.8.

Figura 4.8: Circuito completo di precarica.

Durante il processo di precarica le PWM di tutte le gambe sono disabilitate ed il controllo impone a tutti i duty cycle valore unitario che, considerando un convertitore a tre livelli, consiste nel mantenere tutti i semiconduttori comandati in stato di interdizione per il 100% del tempo di lavoro, il convertitore si comporta quindi come un ponte trifase a diodi.

Le fasi principali che compongono la precarica sono mostrate nel diagramma temporale in Fig. 4.9.

Figura 4.9: Diagramma temporale precarica.

Il primo passo è quello di aprire il relè di scarica e tramite un azione ridondante, poiché le PWM dovrebbero essere già state disabilitate nello stato di "Error", eseguire nuovamente il comando per disabilitarle in modo da avere una maggior sicurezza che non ci sia commutazione. Successivamente, in seguito ad un controllo sui gate driver (GD) in modo da assicurarsi che siano stati resettati e pronti per l'eventuale richiesta di utilizzo, si esegue la chiusura del relè di precarica  $K_S$  tramite la sua bobina di eccitazione, la quale

viene alimentata dalla rete monofase in seguito alla chiusura del relè  $K_{prech}$  comandato dal microcontrollore. In seguito alla chiusura di  $K_S$  inizia la carica dei condensatori del de-link e da codice viene attivato un contatore che introduce una pausa di 1.2 secondi in modo da garantire che il transitorio di precarica sia terminato e tutte le grandezze siano a regime. Durante la carica dei condensatori la corrente fluisce attraverso le resistenze PTC (Positive Temperature Coefficient) che, variando la loro resistenza significativamente con l'aumentare della temperatura, limitano le correnti assorbite. In seguito, viene eseguito un controllo sulle grandezze di precarica come espresso nelle 4.2 e 4.3.

$$iabc1.x + iabc2.x < i_{th,prec} \quad con \quad x = a, b, c$$

(4.2)

$$V_{dc} > V_{min,prec} \tag{4.3}$$

Dove iabc1.x sono le correnti misurate relative al convertitore 1 ed iabc2.xquelle del convertitore 2, in modo da distinguere le due unità poste in parallelo, mentre con  $i_{th,prec}$  e  $V_{min,prec}$  si fa riferimento alla corrente e tensione di soglia volute per assicurarsi che la carica dei condensatori sia completamente terminata. Il controllo sulle grandezze di precarica viene eseguito per un lasso di tempo limitato e nel caso di timeout lo stato di macchina passa da "Soft Start" ad "Error". A dc-link carico, con la stessa procedura descritta per la chiusura del relè di precarica, con la differenza che quelli coinvolti ora sono  $K_P$  e  $K_{main}$ , si effettua la chiusura del relè principale  $(K_P)$  collegando il convertitore alla rete trifase e dopo una pausa di 0.5 secondi, introdotta da un secondo contatore per assicurarsi che il relè principale sia attivo e che la corrente rimanente che passa nel relè di precarica fluisca nel circuito di potenza, si apre il relè di precarica con il conseguente passaggio dello stato di macchina a "Ready". In figura 4.10 è mostrato il diagramma di flusso che ho utilizzato per lo stato di macchina "Soft Start" e successiva scrittura del codice in linguaggio C presente in appendice A.1.

Figura 4.10: Diagramma di flusso Soft Start.

Nelle prove effettuate per testare il funzionamento della precarica è stata impostata una tensione di alimentazione lato rete  $V_G=120V_{rms}$  ad una frequenza  $f_G=50Hz$  andando così a caricare il dc-link ad una tensione  $V_{dc}\simeq 292V$ , come mostrato in Fig. 4.11.

Figura 4.11: Forme d'onda precarica, base tempi 500ms/div.

### 24 CAPITOLO 4. DEBUG E TESTING: PRECARICA/SCARICA DC-LINK E ANELLI DI CONTROLLO

Dall'immagine precedente si può notare che l'andamento esponenziale che seguono gli inviluppi della corrente è dato dal fatto che le PTC aumentano il loro valore di resistenza molto velocemente, combinato al fatto che il dc-link si sta caricando facendo diminuire ulteriormente l'intensità della corrente di fase. Il valore iniziale della tensione  $V_{dc}$  non è nullo in quanto nell'istante d'inizio della precarica il dc-link non è completamente scarico ma a circa 50V poiché si arrivava da una precedente scarica del dc-link. Le grandezze sopra descritte sono misurate con l'utilizzo di sonde poste sul circuito di potenza a differenza della misura di tensione PCC picco la quale è la stima della tensione AC di fase di picco che è generata da DAC e viene quindi calcolata all'interno del microcontrollore e successivamente restituita una tensione tra 0V e 3.3V con fondo scala pari a 500.

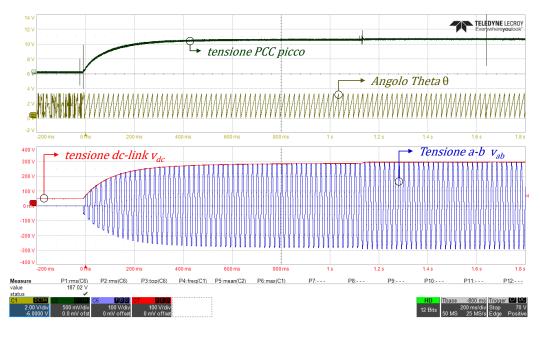

Nelle immagini successive, si possono vedere le grandezze coinvolte nella precarica con base tempi ridotta rispetto alla Fig. 4.11, con l'aggiunta della tensione  $v_{ab}$  misurata a valle delle induttanze di boost e  $\theta$  che definisce l'angolo della terna delle tensioni di rete utilizzato all'interno del controllo del convertitore.

Figura 4.12: Forme d'onda precarica, base tempi 200ms/div.

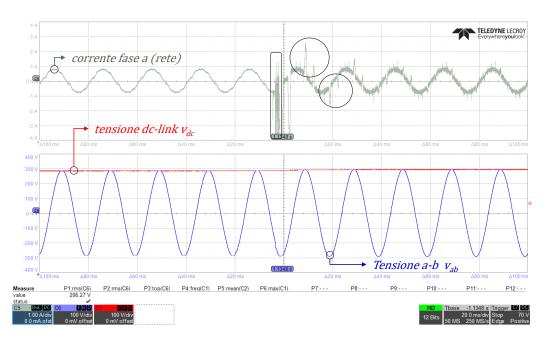

Figura 4.13: Forme d'onda precarica a regime ed apertura relè principale.

Dalla figura 4.12 si evince che l'angolo  $\theta$  prima della chiusura del relè di precarica non può essere rilevato poiché viene preso dal filtro risonante a 50Hz che utilizza misure di tensione presenti a valle del relè, si può notare anche che non va immediatamente a regime ma ritarda di circa due periodi di fondamentale (40ms). Sulla tensione concatenata  $v_{ab}$  si vede invece l'effetto esponenziale dato dalla caduta di tensione sulle PTC poiché la misura viene fatta a valle di esse.

Mentre, in Fig. 4.13 è possibile vedere le grandezze di precarica ormai a regime ed in particolare il disturbo creato dalla chiusura del relè principale sulla corrente di fase con i successivi picchi per mantenere la tensione del dc-link al valore di regime. Invece, per quanto riguarda le tensioni, una volta che  $v_{dc}$  ha raggiunto il valore di picco della tensione concatenata  $v_{ab}$  è praticamente una sinusoide.

#### 4.2.2 Scarica del dc-link

Come detto nell'introduzione del capitolo, è importante avere la possibilità di effettuare la scarica del dc-link in seguito ad un generico problema o spegnimento del convertitore, riportando il dc-link ad una tensione di sicurezza. Il procedimento di scarica utilizza resistenze PTC per dissipare l'energia accumulata nei condensatori come mostrato nel circuito equivalente in Fig. 4.14.

Figura 4.14: Circuito equivalente scarica dc-link.

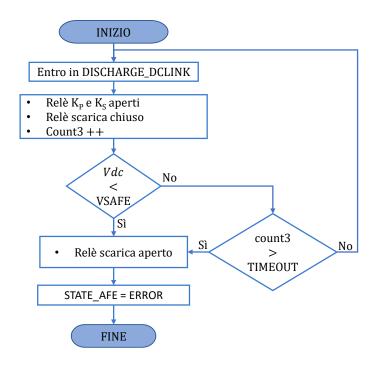

La scarica del dc-link viene effettuata tutte le volte che viene chiesto lo stato Error se  $v_{dc} > v_{SAFE}$ , dove la tensione di sicurezza è settata a 50V. Per la stesura del codice C, presente in appendice A.2, ho utilizzato il flow chart in Fig. 4.15.

Figura 4.15: Flow chart scarica de-link.

Nelle seguenti figure sono mostrate le grandezze rilevanti nel processo di scarica del dc-link.

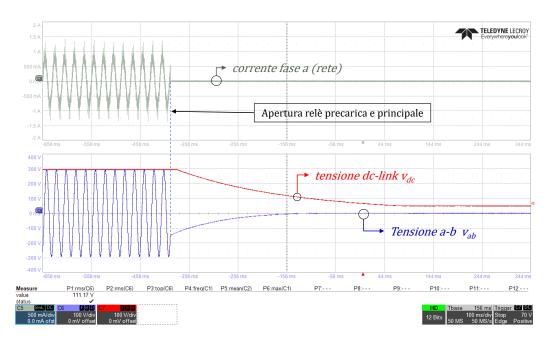

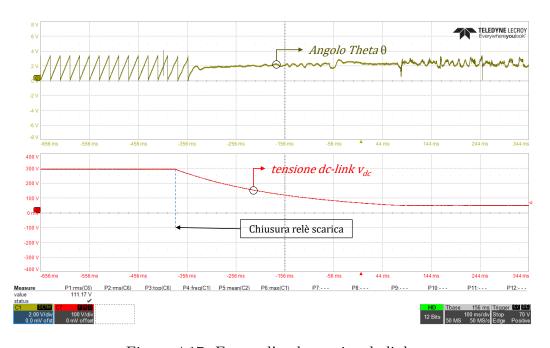

Figura 4.16: Forme d'onda scarica de-link.

Figura 4.17: Forme d'onda scarica de-link.

Dalle Fig. 4.16 e 4.17 si può osservare che all'apertura dei relè di precarica e principale la corrente crolla a zero, la tensione  $v_{ab}$  decresce esponenzialmente a causa delle PTC e l'angolo  $\theta$  dopo circa due periodi di fondamentale viene perso totalmente.

Inoltre, per essere sicuri che entrambi i relè di precarica e principale siano realmente aperti si inserisce un piccolo ritardo (omesso nel flow chart) tra la loro apertura e la chiusura di quello per la scarica, dopo di che la tensione  $v_{dc}$  decresce esponenzialmente seguendo un comportamento RC con valore di resistenza variabile.

### 4.3 Debug e Testing Anelli di Controllo delle Correnti

Il debug degli anelli di corrente viene fatto per assicurarsi che il convertitore funzioni in maniera corretta e che ci sia una regolazione ottimale, agendo in modo graduale così da evitare danni al convertitore.

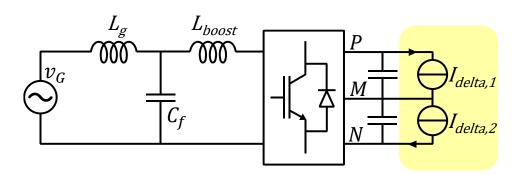

Lo schema circuitale presente al momento del debug degli anelli di corrente è mostrato in figura 4.18. Inoltre, non avendo attivi gli anelli di controllo delle tensioni, l'alimentatore di carico DC (Delta) viene impostato in modo tale da mantenere la tensione del dc-link costante ed equilibrata  $(V_+ = V_-)$  ad un valore superiore al picco della tensione concatenata di alimentazione in modo da avere margine di regolazione.

Figura 4.18: Schema circuitale AFE.

Rispetto al circuito illustrato nel Cap.3 si può vedere la presenza dei condensatori  $C_f$  del filtro di ingresso e le induttanze  $L_f$  ed  $L_g$  che sono rispettivamente l'induttanza di filtro nel caso si voglia utilizzare un LCL in ingresso e l'induttanza di rete. Come si può vedere in Tab. 4.3, per le prove di debug degli anelli di controllo delle correnti, in ingresso viene utilizzato solamente un filtro LC e induttanza di rete nulla.

| Tensione di Rete AC    | 120     | $V_{rms}$ |

|------------------------|---------|-----------|

| Tensione dc-link       | 350     | $V_{rms}$ |

| Frequenza Rete         | 50      | Hz        |

| Tecnica di Modulazione | ZMPC    | /         |

| Induttanza Boost       | 150-200 | $\mu H$   |

| Induttanza Rete        | 0       | $\mu H$   |

| Induttanza Filtro      | 0       | $\mu H$   |

| Capacità Filtro        | 15      | $\mu F$   |

Tabella 4.1: Condizioni utilizzate nel debug degli anelli di corrente.

Le correnti assorbite dal convertitore si possono ricavare applicando la (3.4) alle tre fasi, ottenendo le relazioni espresse nella (4.4).

$$i_A = \frac{v_{G,A} - v_{\bar{A}}}{j \cdot \omega \cdot L_{eq}}; \qquad i_B = \frac{v_{G,B} - v_{\bar{B}}}{j \cdot \omega \cdot L_{eq}}; \qquad i_C = \frac{v_{G,C} - v_{\bar{C}}}{j \cdot \omega \cdot L_{eq}}$$

(4.4)

Dove l'induttanza  $L_{eq}$  è quella equivalente vista da una fase del convertitore. Inoltre, le prove che ho svolto per il debug dell'AFE sono sulla singola unità non andando ad utilizzare la configurazione interleaved; si avrà quindi lo schema a blocchi dell'anello di controllo delle correnti su assi dq mostrato in figura 4.19, che risulta perciò privo dell'anello di modo comune non essendoci la possibilità di circolazione di corrente tra le due unità.

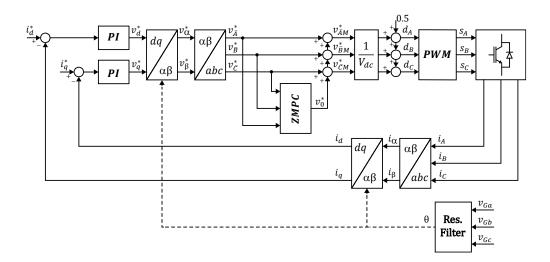

Figura 4.19: Schema a blocchi anello di controllo delle correnti.

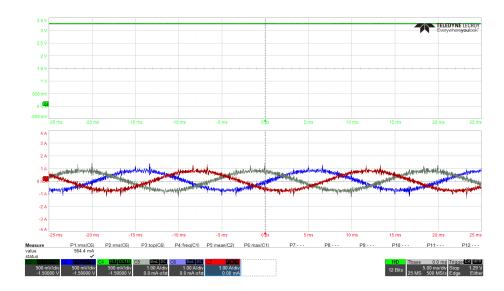

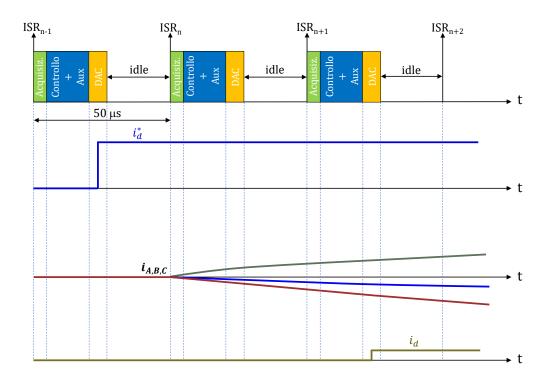

La banda passante del controllo delle correnti è imposta ad 1/20 della frequenza di commutazione. In seguito ad un controllo dei gate driver e tutti gli altri componenti coinvolti nella commutazione ho proceduto, come prima prova, imponendo manualmente dal programma di debug dei valori di riferimento della corrente in asse d $(i_d^*)$  partendo da zero fino a 25A di picco, mantenendo la corrente di riferimento in asse q  $(i_q^*)$  pari a zero in tutte le prove poiché non si ha intenzione di assorbire potenza reattiva. Per quanto riguarda la tensione di dc-link, avendo una tensione di rete pari a 120V efficaci, a fine precarica, si avrà una tensione  $v_{dc}$  pari a circa 290V, successivamente ho utilizzato gli alimentatori DC Delta, regolati in tensione, per portare la  $v_{dc}$  a 350V in modo da avere margine per la regolazione delle correnti. Di seguito sono mostrate alcune delle acquisizioni fatte durante le prove dove vengono mostrate le correnti di fase assorbite con i relativi duty cycle. Le correnti sono state misurate tramite pinza amperometrica posta sui conduttori di potenza tra la rete e l'ingresso del convertitore, mentre i duty cycle sono generati da DAC giustificando la presenza di maggiore rumore sulle forme d'onda e sono compresi nell'intervallo [0; 3.3V]. In Fig. 4.20 si nota che le correnti di fase non sono nulle, nonostante il convertitore non stia commutando poiché non è attiva la modulazione ed i duty cycle del convertitore sono fissi ad 1 (3.3V da DAC). Questo fenomeno è giustificato dalla presenza del filtro in ingresso con le capacità  $C_f$  che danno origine ad una componente di corrente capacitiva. Mentre, in figura 4.21 il convertitore sta commutando con riferimento nullo delle correnti e rispetto al caso precedente si può vedere la corrente capacitiva del filtro più il ripple di modulazione, confermando che il convertitore è in grado di regolare le correnti fino a zero.

Figura 4.20: Duty cycle (in alto), correnti di fase (in basso) senza commutazione.

Figura 4.21: Duty cycle (in alto), correnti di fase (in basso) con  $i_d^* = 0$ .

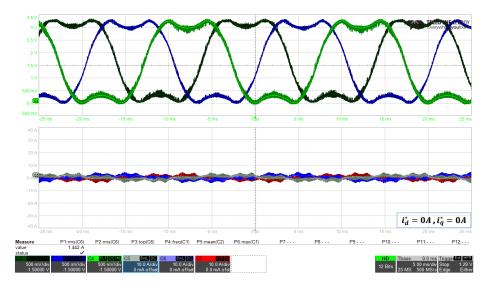

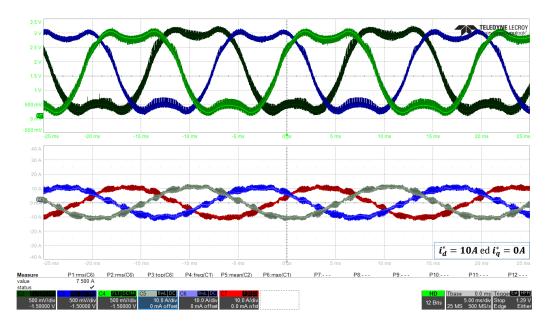

Dalle Fig. 4.22 e 4.23, si può vedere invece come aumenti in modo significativo la qualità delle correnti assorbite al crescere del loro valore di riferimento. Questo fenomeno è dato dal fatto che facendo le prove a tensioni e correnti ridotte, soprattutto per quanto riguarda la tensione di dc-link, si sta facendo lavorare il convertitore in un intervallo di potenza molto inferiore rispetto a quello per cui è stato progettato e nel quale dovrà trovarsi

a funzionare. Si consideri che per una corrente di riferimento pari a  $10\mathrm{A}$  e tensione di dc-link pari a  $350\mathrm{V}$  si ha una potenza di circa un decimo di quella nominale.

Figura 4.22: Duty cycle (in alto), correnti di fase (in basso) con  $i_d^*=10.$

Figura 4.23: Duty cycle (in alto), correnti di fase (in basso) con  $i_d^*=25$ .

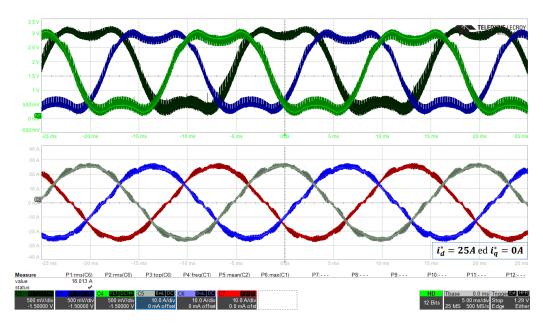

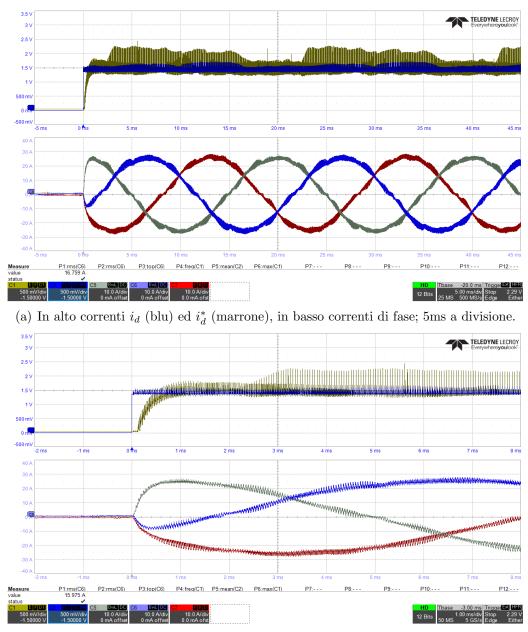

La seconda prova per testare gli anelli di corrente consiste nel vedere la risposta ad un riferimento a gradino della corrente  $i_d^*$ . Nella prova mostrata in 4.21 ho dato un riferimento a gradino in asse d pari a 25A.

(b) In alto correnti  $i_d$  (blu) ed  $i_d^*$  (marrone), in basso correnti di fase; 1ms a divisione.

Figura 4.24: Risposta ad un gradino di corrente da 0 a 25A.

Ovviamente le grandezze  $i_d$  ed  $i_d^*$ , non essendo quantità direttamente mi-

## 34 CAPITOLO 4. DEBUG E TESTING: PRECARICA/SCARICA DC-LINK E ANELLI DI CONTROLLO

surabili ma interne al controllo, sono generate da DAC con le solite proprietà già descritte precedentemente. In Fig. 4.24 si può vedere che sono presenti due ritardi:

- 1. Tra il riferimento a gradino  $i_d^*$  e la variazione delle tre correnti di fase  $i_{A,B,C}$ ;

- 2. Tra l'inizio della variazione delle correnti  $i_{A,B,C}$  e la variazione della corrente  $i_d$ .

Il ritardo complessivo è di due Interrupt Service Routine (ISR) complete che, commutando a 20kHz, consiste in un ritardo di  $100\mu\text{s}$ . Per rendere più chiaro il motivo dei ritardi che si vengono a creare si può fare riferimento alla Fig. 4.25, tenendo in considerazione che i duty cycle vengono aggiornati quanto il timer raggiunge il valore di Auto-Reload Register (ARR).

Figura 4.25: Ritardi introdotti in seguito ad una variazione del riferimento di corrente.

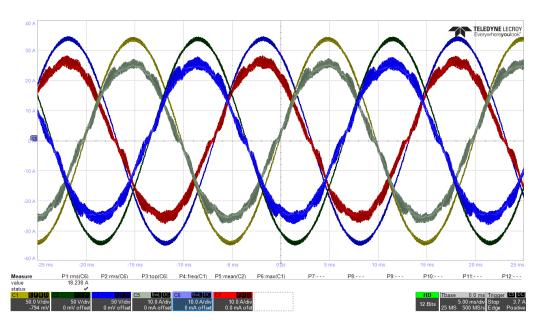

Infine, in Fig. 4.26 sono presenti le tre tensioni e correnti di fase dove si può notare un leggero sfasamento tra di esse a causa della corrente capacitiva

del filtro in ingresso a cui è anche attribuita la piccola perdita in termini di fattore di potenza.

Figura 4.26: Tensioni e correnti di fase con  $i_d^* = 25A$ .

### 4.4 Debug e Testing Anelli di controllo delle Tensioni

Come per il debug degli anelli di corrente, anche quello relativo agli anelli di tensione viene fatto con l'obiettivo di assicurarsi che ci sia una regolazione delle tensioni sul dc-link. Le grandezze di interesse saranno quindi la tensione totale di dc-link  $V_{dc}$  e quella di mid-point  $V_M$  definita nelle (4.6) e (4.5).

$$V_{dc} = V_{+} + V_{-} \tag{4.5}$$

$$V_M = \frac{V_- - V_+}{2} \tag{4.6}$$

Le condizioni delle prove sugli anelli di tensione sono presenti in Tab. 4.2, per quanto riguarda il convertitore non ho fatto nessuna modifica hardware rispetto alle prove appena descritte per gli anelli di corrente ma, per l'esecuzione di queste prove, ho collegato i due Delta in parallelo alle due parti del de-link con impostazioni tali che vadano a lavorare in saturazione di corrente sul limite impostatogli assorbendo una corrente costante ed avendo quindi un comportamento da generatore ideale come mostrato in Fig. 4.27.

| Tensione di Rete AC    | 230       | $V_{rms}$ |

|------------------------|-----------|-----------|

| Tensione dc-link       | 650-800   | $V_{rms}$ |

| Frequenza Rete         | 50        | Hz        |

| Tecnica di Modulazione | ZMPC      | /         |

| Induttanza Boost       | 150 - 200 | $\mu H$   |

| Induttanza Rete        | 100       | $\mu H$   |

| Filtro LCL Ingresso    | NO        | $\mu H$   |

Tabella 4.2: Condizioni utilizzate nel debug degli anelli di tensione.

Figura 4.27: Schema circuitale per il debug anelli di tensione.

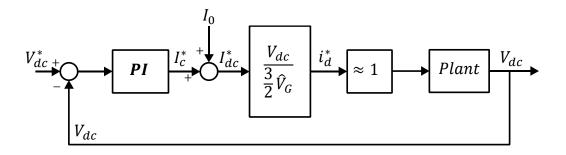

### 4.4.1 Anello di Controllo della Tensione Totale di Dclink

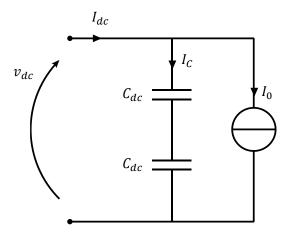

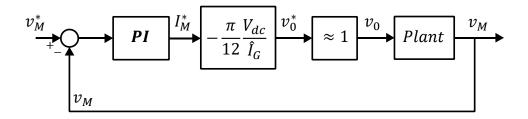

L'anello di controllo esaminato ha l'obiettivo di regolare la tensione totale del dc-link con banda passante impostata ad un decimo della banda degli anelli di corrente. Il sistema fisico equivalente per l'anello considerato è mostrato in Fig. 4.28.

Figura 4.28: Circuito equivalente anello di controllo di tensione dc-link.

La variabile di stato  $v_{dc}$  è espressa nella 4.7 come:

$$v_{dc} = \frac{2 \cdot (I_{dc} - I_0)}{s \cdot C_{dc}} \tag{4.7}$$

Per mettere in relazione la corrente di dc-link  $I_{dc}$  con quella di fase in ingresso si applica un bilanciamento delle potenze, mostrato nella 4.8, considerando un fattore di potenza unitario.

$$P = \frac{3}{2} \cdot \hat{V}_G \cdot \hat{I}_G \cdot \cos\varphi = \frac{3}{2} \cdot \hat{V}_G \cdot i_d = v_{dc} \cdot I_{dc}$$

(4.8)

ottenendo così la relazione mostrata nella (4.9).

$$I_{dc} = \frac{3}{2} \cdot \frac{\hat{V}_G}{v_{dc}} \cdot i_d \tag{4.9}$$

Lo schema a blocchi del controllo è mostrato in Fig. 4.29, applicando inoltre la linearizzazione nei confronti della tensione di dc-link con condizione  $v_{dc} = V_{dc}$ .

## 38 CAPITOLO 4. DEBUG E TESTING: PRECARICA/SCARICA DC-LINK E ANELLI DI CONTROLLO

Figura 4.29: Schema a blocchi anello di controllo  $V_{dc}$ .

Mentre lo schema a blocchi del plant è mostrato in figura 4.30.

Figura 4.30: Plant anello di controllo tensione  $V_{dc}$ .

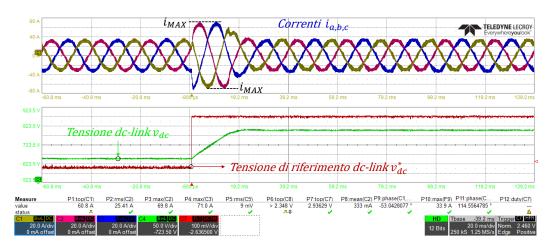

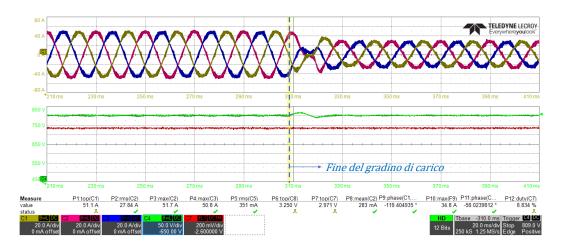

Per quanto riguarda l'anello di controllo in questione sono state svolte due prove differenti. La prima prova consiste nell'imposizione di un gradino sulla tensione di riferimento del dc-link per passare dalla tensione minima in uscita  $(V_{dc,min}=650V)$  a quella massima  $(V_{dc,max}=800V)$ , il risultato è mostrato nell'aquisizione da oscilloscopio presente in Fig. 4.31. Il setup è sempre composto dall'alimentatore programmabile AC in ingresso (Regatron) e dai due carichi DC in uscita (Delta) che, rispetto alla prove svolte sull'anello di corrente, sono impostati per mantenere una potenza in uscita costante pari a 15kW.

Figura 4.31: Gradino di tensione  $V_{dc}$  da 650V ad 800V.

Nell'immagine sopra riportata sono presenti, in alto, le tre correnti di fase mentre in basso sono mostrate la tensione totale di dc-link misurata tramite sonda e la tensione di riferimento  $v_{dc}^*$  generata invece da DAC. Si può vedere che la tensione, a seguito del gradino, ci mette circa 20ms per arrivare a regime; le due grandezze di tensione non vanno a coincidere poichè sono rappresentate su fondo scala differente. Inoltre, l'anello di tensione, saturato in modo da limitare la massima corrente del convertitore, durante il periodo transitorio, impone un riferimento di corrente pari a quella massima dell'AFE il quale si comporta da generatore costante di corrente poichè si è in risposta saturata di entrambi gli anelli, facendo sì che la tensione del dc-link salga a rampa in quanto anche il carico, assorbendo un valore di corrente fisso, fa si che ci sia corrente costante anche nei condensatori di dc-link. Una volta che la  $v_{dc}$  ha raggiunto la situazione di regime le correnti tornano al valore precedente al gradino tale da sostenere il carico presente. Per una comprensione migliore della risposta, in Fig. 4.32, è mostrato lo stesso gradino di tensione di Fig. 4.31 con forme d'onda scalate.

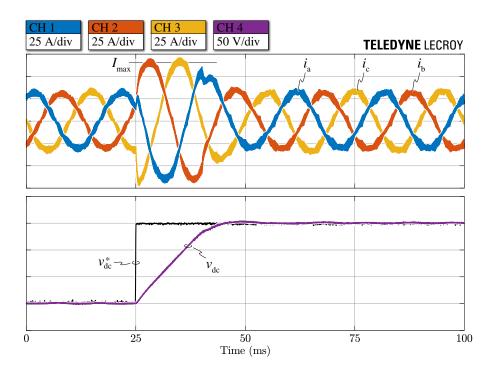

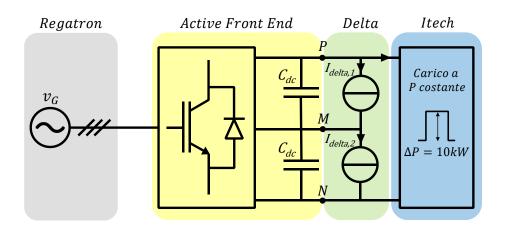

La seconda prova consiste invece nell'imporre un gradino di carico di ampiezza pari a 10kW, passando da una potenza in uscita di 12.5kW a 22.5kW rimanendo sempre in condizioni di equilibrio in quanto le correnti assorbite dai Delta sono uguali  $I_{delta,1} = I_{delta,2}$ , andando così a valutare l'impatto della variazione di carico sulla tensione  $v_{dc}$  la quale ha il riferimento fisso a  $V_{dc,max}$ . Per questa prova, rispetto a quella precedente, è stato collegato in parallelo al dc-link ed ai due carichi DC un ulteriore alimentatore DC programmabile bidirezionale (Itech) in grado di lavorare a potenza costante, il setup della prova è schematizzato in Fig. 4.33.

Figura 4.32: Gradino di tensione  $V_{dc}$  da 650V ad 800V con forme d'onda scalate [4].

Figura 4.33: Setup per la prova sull'anello di tensione di dc-link.

Mentre, il risultato della prova è mostrato nelle Fig. 4.34 e 4.35 le quali mostrano rispettivamente l'istante in cui viene imposto il gradino di carico e l'stante in cui viene staccato. Dalle immagini si può vedere l'ottima reazione dell'anello di tensione che, in seguito alla variazione della potenza in uscita, riesce a mantenere la tensione sul dc-link perfettamente costante a quella di

riferimento. Anche per quanto riguarda il distacco del carico l'anello si comporta molto bene, presentando solamente una piccola sovratensione dovuta al fatto che per un istante successivo al distacco viene erogata la corrente che era necessaria a sostenere il gradino di carico, andando a caricare il dclink ad una tensione leggermente superiore ad 800V prima che tutti gli anelli si adeguino alla nuova condizione, considerando inoltre che il convertitore è unidirezionale e non può quindi imporre una corrente negativa per forzare la scarica del dc-link, ma può agire imponendo corrente di riferimento nulla oppure, nel caso di piccoli sbilanciamenti, ridurre il riferimento di corrente e lasciare che sia il dc-link stesso a scaricarsi e a raggiungere la tensione voluta.

Figura 4.34: Gradino di carico da 10kW, istante iniziale.

Figura 4.35: Gradino di carico da 10kW, istante del distacco.

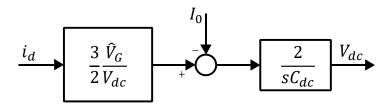

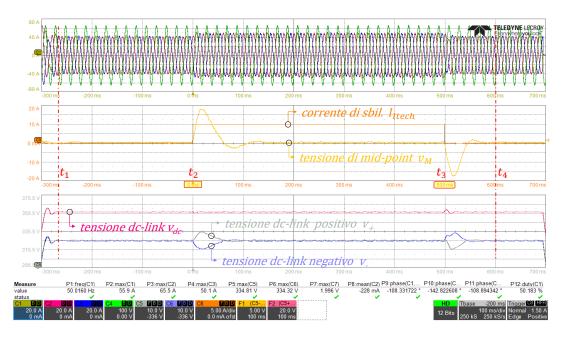

#### 4.4.2 Anello di Controllo della Tensione di Mid-Point

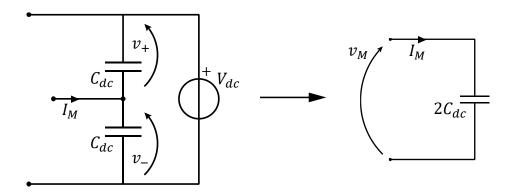

L'anello di controllo della tensione di mid-point ha lo scopo di regolare le tensioni DC in uscita in modo da tenere bilanciate la parte di dc-link alta e quella bassa, ottenendo quindi una tensione di mid-point nulla e  $V_+ = V_-$ . Il circuito equivalente per l'anello di mid-point è riportato in Fig. 4.36.

Figura 4.36: circuito equivalente anello di controllo tensione mid-point.

Le due capacità equivalenti di dc-link si comportano come se fossero in parallelo, mentre la tensione totale  $V_{dc}$  è considerata costante in quanto regolata dall'anello visto precedentemente. Da queste considerazioni si ottiene quindi la relazione per la variabile di stato mostrata nella (4.10).

$$v_M = \frac{I_M}{s \cdot 2C_{dc}} \tag{4.10}$$

Inoltre, tramite calcoli presenti in [2], si ottiene anche la relazione tra la corrente di mid-point e la variabile di controllo mostrata nella (4.11), dove la tensione  $v_0$  è quella di modo comune.

$$I_M = -\frac{12}{\pi} \cdot \frac{v_0}{V_{dc}} \cdot \hat{I}_G \tag{4.11}$$

Infine, lo schema a blocchi risultante del controllo e quello del plant sono mostrati rispettivamente in Fig. 4.37 e 4.38.

Figura 4.37: Schema a blocchi anello di tensione mid-point.

Figura 4.38: Plant anello di controllo tensione di mid-point.

Le prove svolte per questo anello di controllo consistono nell'imporre uno squilibrio, in termini di corrente erogata, sulle due parti di dc-link. Per effettuare queste prove uno degli alimentatori DC Delta è collegato tra il punto positivo P del dc-link ed il punto M di mid-point ed il secondo tra il punto M e il punto negativo N come già mostrato in Fig. 4.33 con la differenza che il carico aggiuntivo Itech viene collegato sul dc-link basso e fatto lavorare a corrente costante ottenendo il setup mostrato in Fig. 4.39.

Figura 4.39: Setup per la prova sull'anello di tensione di mid-point.

## 44 CAPITOLO 4. DEBUG E TESTING: PRECARICA/SCARICA DC-LINK E ANELLI DI CONTROLLO

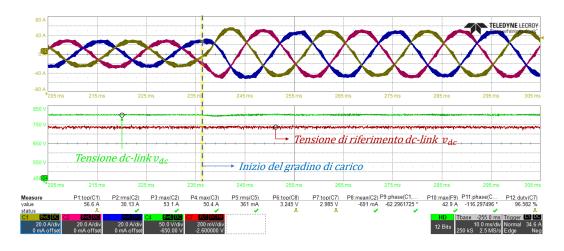

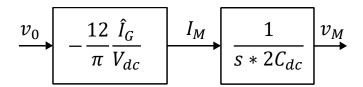

I risultati della prova sono mostrati in Fig. 4.40 e si può suddividere in diversi intervalli temporali relativi alle azioni eseguite:

- $t < t_1$ : periodo transitorio di carica del dc-link fino al valore di riferimento voluto che in questo caso coincide con  $V_{dc,min}$ . Le correnti di fase sono saturate al valore massimo accettabile fino a carica conclusa;

- $t_1 \le t < t_2$ : a seguito della carica del dc-link tutte le grandezze sono a regime, il valore di corrente totale in uscita è settato a  $30A_{dc}$  con  $I_{delta,1} = I_{delta,2} = 15A_{dc}$ ;

- $t = t_2$ : il carico Itech viene attivato e si crea uno sbilanciamento di  $10A_{dc}$  sul dc-link basso creando istantaneamente un abbassamento della tensione ai suoi capi ed un innalzamento di quella presente sul dc-link alto;

- $t_2 < t < t_3$ : successivamente allo sbilanciamento l'anello di tensione di mid-point reagisce riportando una situazione di equilibrio tra le tensioni  $v_+$  e  $v_-$  agendo tramite l'iniezione di una componente di modo comune per ottenere sempre  $v_M = 0$ , raggiungendo in seguito la situazione di regime con carico sbilanciato;

- $t=t_3$ : l'alimentatore Itech viene disattivato ritornando così ad una richiesta di corrente al dc-link equilibrata tra le due parti creando però una situazione transitoria di squilibrio rispetto al regime precedentemente raggiunto.

- $t_3 < t < t_4$ : in seguito alla variazione di carico l'anello di controllo interviene nuovamente per ristabilire l'equilibrio sulle due tensioni;

- $t > t_4$ : la situazione di regime è nuovamente raggiunta.

Figura 4.40: Risultato della prova di sbilanciamento mid-point.

## Capitolo 5

# Algoritmo di Controllo per l'Estrapolazione Automatizzata delle Mappe

L'obiettivo principale di questo capitolo è quello di chiarire l'algoritmo creato, la metodologia, gli strumenti hardware/software ed i setup utilizzati per l'acquisizione delle misure e l'estrapolazione delle mappe di efficienza, THD, fattore di potenza e perdite del raddrizzatore attivo al fine di ottenere tutte le informazioni e le misure in modo automatizzato.

### 5.1 Introduzione all'Estrapolazione delle Mappe, Strumenti e Tool Utilizzati

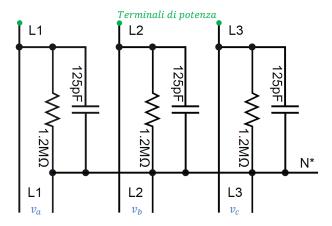

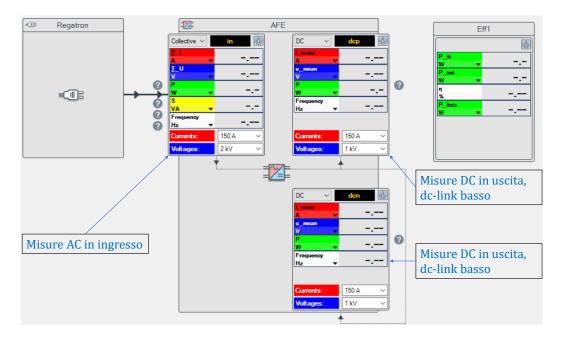

Il primo passo è quello di definire tutti i punti in cui si vogliono eseguire le misure, in modo tale da poter ottenere i valori di potenza necessari alla caratterizzazione del convertitore. Il posizionamento degli strumenti di misura sono mostrati in Fig. 5.1 e consistono in cinque misure di tensione (in blu) ed altrettante di corrente (in verde) utili ad acquisire le seguenti grandezze:

- tre tensioni di fase  $v_a, v_b, v_c$ , misurate in ingresso al convertitore attraverso l'utilizzo di un centro stella artificiale mostrato in Fig 5.2;

- due tensioni di dc-link, superiore  $v_{+}$  ed inferiore  $v_{-}$ ;

- tre correnti di fase  $i_a, i_b, i_c$  misurate all'ingresso del convertitore;

- due correnti di dc-link  $i_+$  ed  $i_-$ , relative alla parte alta e bassa, in modo da poter avere i valori di potenza distinti sulle due parti per riuscire ad analizzare al meglio anche prove con carico squilibrato.

Figura 5.1: Schema circuitale con relativi punti di misura.

Figura 5.2: Centro stella artificiale HBM per la misura delle tensioni di fase.

Per l'acquisizione delle misure e dei dati ho utilizzato un HBM GEN4tB Transient Recorder and Data Acquisition System equipaggiato con power card GN310B, entrambi mostrati in Fig. 5.3, i quali permettono di effettuare le misure con cadenza di 2 MS/s e con un accuratezza di misura dello 0.015% del valore indicato e 0.02% del campo di misura ottenendo così alta precisione ed affidabilità. Le misure di tensione possono essere collegate direttamente al mainframe HBM poiché può effettuare misure dirette per tensioni fino a  $\pm 1500V_{picco}$  mentre, per quanto riguarda le misure di corrente ho utilizzato dei trasduttori LEM IT 200-S ULTRASTAB con relativo condizionatore di segnale Signaltec MTCS mostrati in Fig. 5.4 interposti tra il punto di misura ed il mainframe HBM.

Figura 5.3: HBM GEN4tB (sx), Power card GN310B (dx).

Figura 5.4: Trasduttore di corrente LEM IT 200-S ULTRASTAB (in alto), condizionatore di segnale Signaltec MTCS (in basso).

Come tool software per gestire la parte di acquisizione dati e svolgimento dei calcoli real-time con le misure effettuate ho utilizzato il software dedicato per HBM, *Perception*, nel quale viene "ricreato" il sistema fisico per la definizione delle grandezze misurate, come mostrato in Fig. 5.5, per la successiva definizione del modo in cui utilizzarle.

Figura 5.5: Interfaccia grafica Perception.

Prima di esprime le relazioni utilizzate su Perception per effettuare i calcoli real-time con le misure acquisite è utile definire alcune funzioni utilizzate dal programma:

- CycleDetect: individua un periodo di fondamentale per segnali periodici, chiamato successivamente CycleMaster, su cui si basano i calcoli dei valori medi ed efficaci. La grandezza di riferimento per il rilevamento del ciclo è la tensione  $v_a$ ;

- CycleRMS: calcola il valore efficace delle grandezze scelte sul riferimento CycleMaster;

- CycleMean: calcola il valore medio del segnale voluto sempre rispetto al riferimento CycleMaster;

- CycleTHD: calcola la distorsione totale del segnale in ingresso tramite la seguente relazione:

$$CycleTHD = 100 \cdot \sqrt{\left(\frac{RMS_{ingresso}}{RMS_{fondamentale}}\right)^2 - 1}$$

(5.1)

Come primo passo su Perception vengono calcolati i valori efficaci effettivi delle tensioni e delle correnti AC in ingresso come:

$$V_k = CycleRMS(v_k, CycleMaster)$$

(5.2)

$$I_k = CycleRMS(i_k, CycleMaster)$$

(5.3)

dove k=a,b,c sta ad indicare la fase considerata del convertitore. Successivamente vengono calcolate le potenze attive sulle singole fasi tramite il calcolo del valor medio del prodotto delle grandezze istantanee di tensione e corrente e la potenza apparente tramite il prodotto dei valori efficaci effettivi delle tensioni e delle correnti:

$$P_k = CycleMean(p_k, CycleMaster) \quad con \ p_k = v_k \cdot i_k$$

(5.4)

$$P_{in} = P_a + P_b + P_c \tag{5.5}$$

$$S_k = V_k \cdot I_k \tag{5.6}$$

$$S_{in} = S_a + S_b + S_c \tag{5.7}$$

La potenza reattiva viene invece calcolata utilizzando quella attiva ed apparente appena calcolate:

$$Q_{in} = \sum_{k=a,b,c}^{k=a,b,c} \sqrt{S_k^2 - P_k^2}$$

(5.8)

Una volta ottenute tutte le potenze viene calcolato il fattore di potenza sia per la singola fase che quello complessivo:

$$PF_k = \frac{P_k}{S_k} \tag{5.9}$$

$$PF = \frac{P_{in}}{S_{in}} \tag{5.10}$$

51

Per quanto riguarda le misure DC in uscita il procedimento è lo stesso mostrato per le grandezze AC:

$$V_{dc,i} = CycleRMS(v_i, CycleMaster)$$

(5.11)

$$I_{dc,j} = CycleRMS(i_j, CycleMaster)$$

(5.12)

dove il pedice j=+,- sta ad indicare se si considera il dc-link alto o basso.

CAPITOLO 5. ALGORITMO DI CONTROLLO PER L'ESTRAPOLAZIONE AUTOMATIZZATA DELLE MAPPE

$$\bar{V}_{dc,j} = CycleMean(v_j, CycleMaster)$$

(5.13)

$$\bar{I}_{dc,i} = CycleMean(i_i, CycleMaster)$$

(5.14)

$$P_{out,j} = CycleMean(v_j \cdot i_j, CycleMaster)$$

(5.15)

$$P_{out} = P_{out,+} + P_{out,-} (5.16)$$

La funzione *CycleMean* viene eseguita anche sulle grandezze in continua per avere il riferimento temporale delle misure coincidente a quello delle grandezze in alternata. Ora che tutte le potenze sia in ingresso che in uscita sono note si posso calcolare, sempre real-time, l'efficienza e le perdite del convertitore come:

$$\eta = \frac{P_{out}}{P_{in}} \tag{5.17}$$

$$P_{loss} = P_{in} - P_{out} \tag{5.18}$$

Infine anche i valori di THD delle singole correnti lato rete e quello complessivo vengono calcolati tramite la funzione *CycleTHD* che utilizza la (5.1) tramite le relazioni seguenti:

$$THD_k = CycleTHD(i_k, CycleMaster, f_{fond})$$

(5.19)

$$THD = \frac{\sum_{k=a,b,c} THD_k}{3} \tag{5.20}$$

In seguito vengono definite altre grandezze che verranno utilizzate nelle mappe ma che non vengono misurate direttamente ed è quindi necessario ottenerle tramite la combinazione di quelle dirette.

$$\bar{V}_M = \bar{V}_{dc,+} - \bar{V}_{dc,-} \tag{5.21}$$

$$\bar{V}_{dc} = \bar{V}_{dc,+} + \bar{V}_{dc,-} \tag{5.22}$$

$$\bar{I}_{mid} = -\left(\bar{I}_{dc,-} + \bar{I}_{dc,+}\right)$$

(5.23)

Nelle (5.21), (5.22) e (5.23) sono rispettivamente espresse la tensione di mid-point, quella totale di dc-link e la corrente di mid-point, in accordo con

52

le convenzioni di segni mostrate in Fig. 5.1. Finita un'intera acquisizione, da Perception si ottiene un file con la registrazione completa di tutte le forme d'onda con i valori istantanei delle grandezze per ogni sweep ed un secondo file .XML che contiene le grandezze medie (es. tensioni, correnti, efficienza, THD ecc.) per ogni sweep acquisito, riferito quindi ad un singolo punto di lavoro. Essendo che tutte le formule appena descritte vengono eseguite in tempo reale da HBM, per ottenere il singolo valore delle grandezze per ogni punto di lavoro considerato, sarà necessario eseguire la media sui più cicli contenuti all'interno degli sweep. Infine sono mostrate le foto del setup di misura:

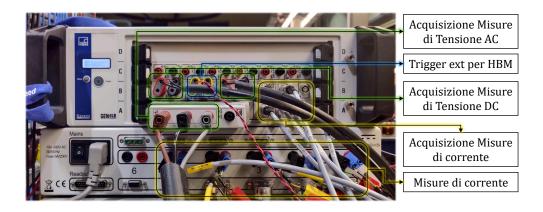

Figura 5.6: Strumentazione: HBM, Signaltec e alimentatori DC Delta.

Figura 5.7: Setup e collegamenti per misure di tensione e corrente.

### 5.2 Algoritmi di Controllo per la Caratterizzazione del Convertitore

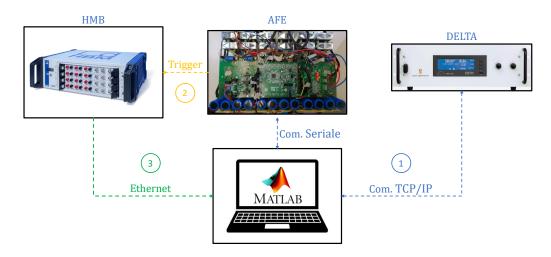

Per raggiungere l'obiettivo prefissato dell'acquisizione automatizzata di tutti i dati necessari ad ottenere le mappe per la caratterizzazione del convertitore ho sviluppato degli script Matlab che permettono la comunicazione tra computer, microcontrollore dell'Active Front End, sorgenti di carico Delta ed il sistema di acquisizione dei dati HBM.

Figura 5.8: Schema generale comunicazione.

Lo schema generale della comunicazione è mostrato in Fig. 5.8, da cui si può notare che sono presenti tre vie di comunicazione principali:

- 1. Tramite lo script Matlab si esegue la comunicazione diretta con il microcontrollore (via seriale) del convertitore e con gli alimentatori Delta (protocollo TCP/IP) tramite cui verranno scambiate tutte le informazioni ed i riferimenti necessari ad ottenere i punti di lavoro voluti.

- 2. In seguito alle comunicazioni effettuate precedentemente il convertitore viene fatto passare nei vari stati di macchina, sempre tramite comandi software, fino allo stato di GO con le condizioni volute e viene inviato un segnale differenziale di trigger a ±3.3V tramite le periferiche general-purpose input/output (GPIO) ad HBM in modo da determinare l'istante in cui deve effettuare l'acquisizione dei dati per ogni singolo punto di lavoro.

3. Alla fine dell'acquisizioni di tutti i singoli punti di lavoro (sweep di Perception) i dati vengono inviati dall'HMB al computer tramite cavo di rete.

A livello del microcontrollore, appena si entra nello stato di GO si attiva un contatore usato per determinare il tempo di attesa prima dell'invio del trigger ad HBM in modo che si esegua l'acquisizione delle misure in stato di regime del punto di lavoro considerato e successivamente all'invio del trigger viene attivato un secondo contatore che tiene conto del tempo di lavoro del convertitore in quelle condizioni prima di tornare nello stato di READY per potere cambiare i riferimenti e svolgere poi le misure del punto di lavoro successivo. Per il tempo di attesa e di lavoro ho scelto rispettivamente 100ms e 400ms; il tempo di lavoro è stato definito in modo tale da non far variare notevolmente la temperatura dei semiconduttori e per effettuare le misure in tempi sufficientemente lontano dal cambio di stato di macchina. Inoltre, una volta che il trigger è stato inviato ed HBM ha iniziato ad acquisire tutte le misure, Perception calcola la media delle varie grandezze definite nelle espressioni mostrate nel paragrafo precedente su una finestra con ampiezza temporale di cinque periodi di fondamentale centrata sui 400ms di sweep, lo schema temporale è mostato in Fig. 5.9.

Figura 5.9: Schema temporale per trigger ed acquisizione misure.

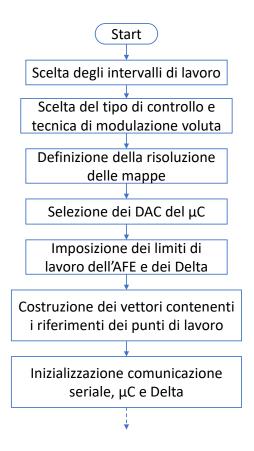

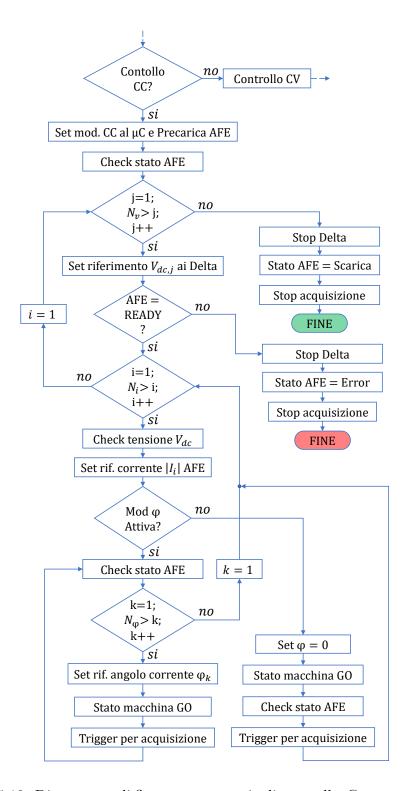

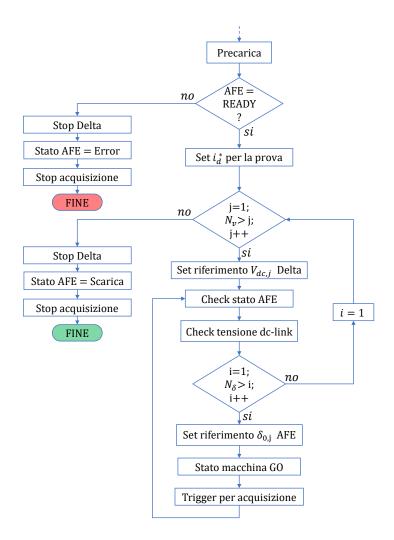

Nella prima parte, comune a tutte le modalità dell'algoritmo che verranno presentate, vengono scelte ed impostate tutte le condizioni della prova che si vuole eseguire come mostrato nel diagramma di flusso in Fig. 5.10:

- Scelta degli intervalli di lavoro: vengono impostati i valori massimi e minimi delle variabili controllabili  $V_{dc}$ , |I|,  $\varphi$  che sono rispettivamente la tensione di dc-link ed il modulo e l'angolo della corrente di riferimento in ingresso negli assi dq, in caso di prove a carico sbilanciato verrà impostato anche il livello percentuale di squilibrio;

- Scelta della modalità di controllo AFE: si decide se lavorare in modalità CC "Constant Current" oppure CV "Constant Voltage" (successivamente definite) e si effettua la scelta del tipo di tecnica di modulazione che si vuole utilizzare;

- Definizione della risoluzione delle mappe e scelta dei DAC: vengono scelti i numeri di step da eseguire delle tre variabili controllabili e viene comunicato al microcontrollore quali grandezze visualizzare tramite DAC nel caso si voglia monitorare qualche grandezza da oscilloscopio non misurabile dall'esterno;

- Limiti e controllo dei valori inseriti: viene eseguito un check e successiva saturazione rispetto ai valori massimi di  $V_{dc}$ , |I|,  $\varphi$  e dei limiti dei Delta nel caso ci sia stato un errore nell'inserimento di essi;

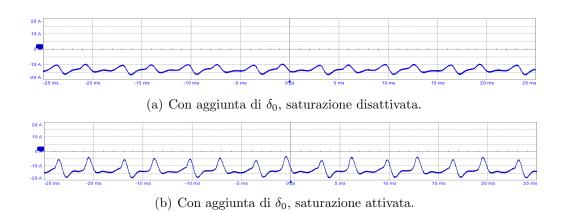

- Costruzione dei vettori: vengono creati vettori con componenti equi spaziate contenenti i valori delle variabili controllabili che andranno quindi a definire tutti i punti di lavoro in cui il convertitore andrà a lavorare durante la prova.

Figura 5.10: Diagramma di flusso della prima parte dell'algoritmo per la definizione delle condizioni della prova.

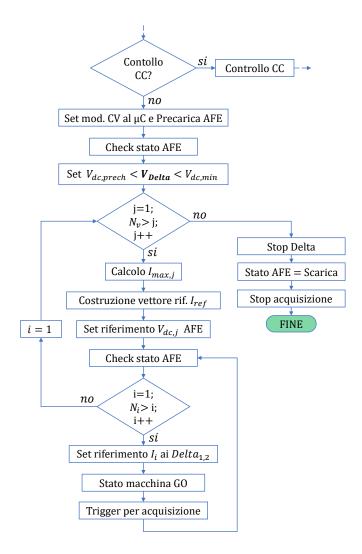

#### 5.2.1 Strategia di Controllo Constant Current