# RISC-V : an FPGA implementation for general purpose prototyping hardware

Author: Federico Pozzana

Supervisor : Guido Masera Co-supervisor : Elia Delledonne Co-supervisor : Fabrizio Fraternali

# A thesis presented for the Master degree in Electronic engineering

Department of Electronics and Telecommunication Politecnico di Torino 18 December 2020

### Abstract

The RISCV project began in 2010 at UC Berkely. It set out to provide a flexible, open source instruction set architecture to offer an alternative to proprietary ISAs which require non disclosures agreements and royalties to be used. Currently the RISCV foundation own, maintain and publish intellectual property related to RISCV's definition [1]. Although it started out in academia the RISCV instruction set architecture has been adopted by numerous companies, such as

- SiFive

- Codasip

- $\bullet$  lowRISC

and many more [2]. With such strong industrial adoption, RISCV poses itself as a rival to the ARM's hegemony in the microcontroller world.

This study, made in collaboration with Maxim Integrated [3], aims to integrate general purpose peripherals (such as I2C, SPI, UART, etc...) with an available RISCV IP provided by an internal group. This work is intended to be a feasibility study for the aformentioned core; possible applications for the microcontroller could be

- motor control applications

- replace big control finite state machines

- industrial communication applications

The methodology followed these steps

- RISCV IP RTL study

- publicly available toolchain/IDE selection

- compiler performance evaluation

- peripheral dedicated firmware development

- peripherals integration

- develop regression environment for RTL validation

- CORDIC peripheral development

- LINTing of newly developed RTL

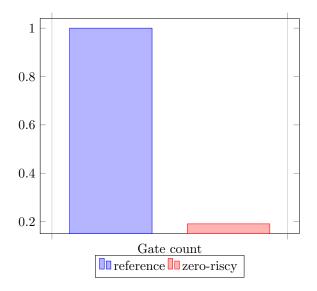

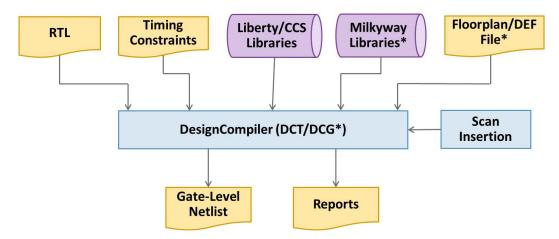

- synthesis step with Design Compiler

The conclusions can be observed in the "Conclusion" chapter.

## Acknowledgements

I would like to thank my supervisor, Professor Guido Masera. His knowledge and guidance helped me during the technical challenges that this thesis presented.

I would like to thank my co-supervisors, Elia Delledonne and Fabrizio Fraternali, for their guidance during this master thesis project. They were always present to steer me in the right direction from start to finish.

I would also like to thank the people that have been close to me for all these years. I am particularly grateful to Laura, whom had the arduous task of putting up with me for the past decade.

Last, but not least, I would like to thank my family. Their constant support throughout my university studies have been invaluable.

# Contents

| 1 | Introducti   | on 10                             |

|---|--------------|-----------------------------------|

|   | 1.0.1        | Tools                             |

|   | 1.0.2        | PULP                              |

|   | 1.0.3        | RISCV IP                          |

| 2 | Memories     | description 16                    |

| _ | 2.0.1        | Portmap and timing diagram        |

|   | 2.0.2        | Vivado's synthesis                |

|   |              |                                   |

| 3 | IDE setup    | 18                                |

|   | 3.0.1        | IDE                               |

|   | 3.0.2        | HEX file                          |

| 1 | Initial test | cs 20                             |

| 4 | 4.0.1        | Testbench                         |

|   | 4.0.2        | Initial tests                     |

|   | 4.0.2        | Illitiai tests                    |

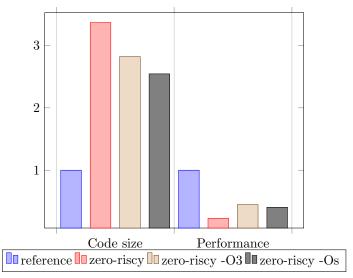

| 5 | Embench      | tests 24                          |

|   | 5.0.1        | Tests setup                       |

|   | 5.0.2        | Results analysis                  |

|   | 5.0.3        | Simulation                        |

| 6 | FPGA no      | rting process 28                  |

| U | 6.0.1        | Board choice                      |

|   | 6.0.2        | Porting process                   |

|   | 6.0.3        | FPGA resource utilization         |

| _ |              |                                   |

| 7 |              | s integration 31                  |

|   | 7.0.1        | UART                              |

|   | 7.0.2        | SPI                               |

|   | 7.0.3        | I2C                               |

| 8 | Peripheral   | ls stress test 44                 |

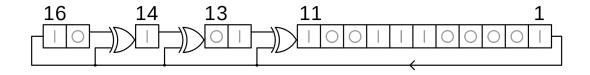

|   | 8.0.1        | LFSR 45                           |

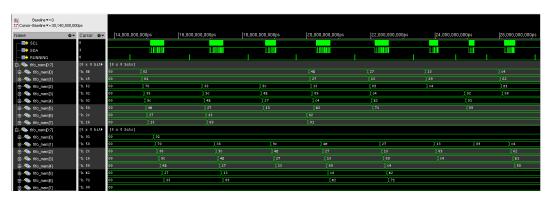

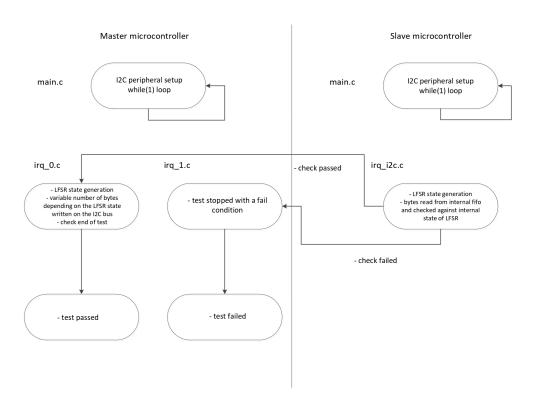

|   | 8.0.2        | I2C master write                  |

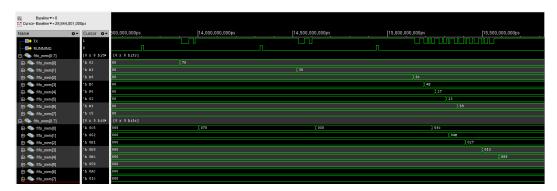

|   | 8.0.3        | I2C master read                   |

|   | 8.0.4        | UART communication                |

|   | 8.0.5        | SPI communication                 |

| 9 | Cordic       | 53                                |

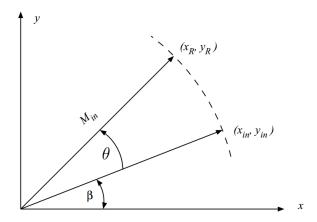

|   | 9.0.1        | Cordic algorithm                  |

|   | 9.0.2        | Numerical example                 |

|   | 9.0.3        | CORDIC generalized equations      |

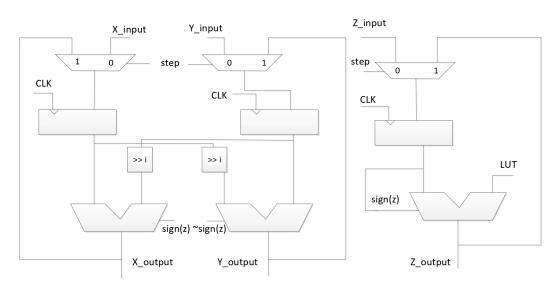

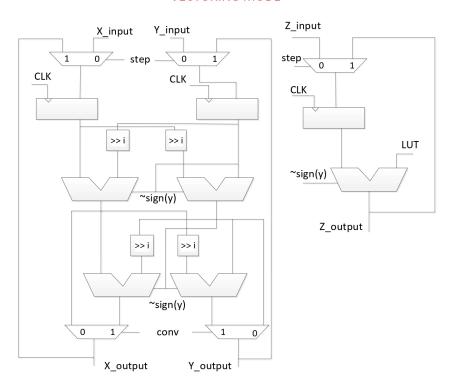

|   | 9.0.4        | Hardware implementations          |

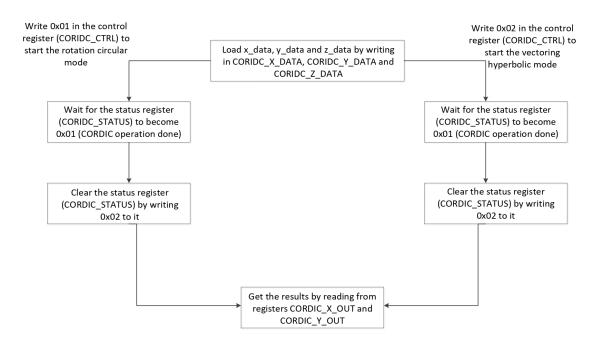

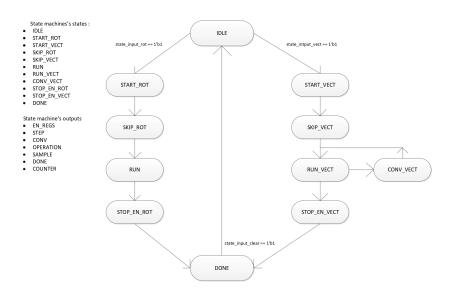

|   | 9.0.5        | Complete CORDIC peripheral design |

|   | 9.0.6        | Data representation               |

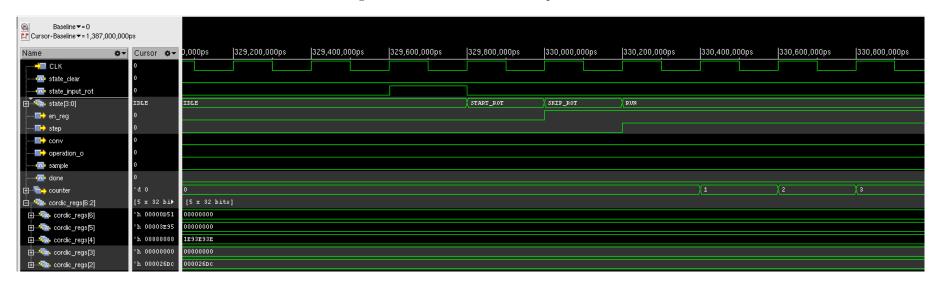

|   | 9.0.7        | Testing phase                     |

|   | 0.08         | 0 <b>.</b>                        |

CONTENTS

| 10           | From | nt-end                   |                                | 80  |

|--------------|------|--------------------------|--------------------------------|-----|

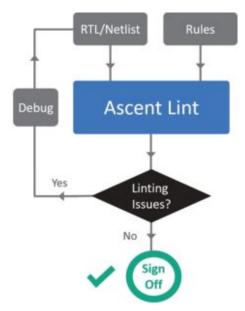

|              |      | 10.0.1                   | Linting                        | 80  |

|              |      |                          | Synthesis                      | 81  |

| 11           | Con  | clusio                   | n                              | 84  |

| $\mathbf{A}$ | Pro  | ject so                  | ources                         | 85  |

|              | A.1  | Memor                    | ries RTL model                 | 85  |

|              |      | A.1.1                    | ROM RTL model                  | 85  |

|              |      | A.1.2                    | RAM RTL model                  | 86  |

|              | A.2  | State 1                  | machine RTL model              | 87  |

|              | A.3  | $C \operatorname{cod} e$ |                                | 93  |

|              |      | A.3.1                    | March C                        | 93  |

|              |      | A.3.2                    | APB random test                | 95  |

|              |      | A.3.3                    | CORDIC precision test          | 96  |

|              |      | A.3.4                    | I2C master write - master code | 98  |

|              |      | A.3.5                    | I2C master write - slave code  | 99  |

|              |      | A.3.6                    | I2C master read - master code  | 101 |

|              |      | A.3.7                    | I2C master read - slave code   | 104 |

|              |      | A.3.8                    | UART - master code             | 106 |

|              |      | A.3.9                    |                                | 109 |

|              |      | A.3.10                   |                                | 111 |

|              |      |                          |                                | 114 |

# List of Figures

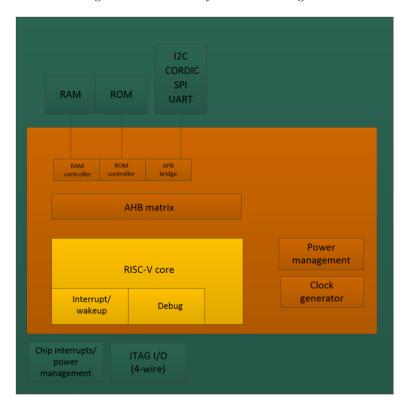

| 1.1  | reference microcontroller architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1.2  | RAM read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12        |

| 1.3  | RAM write operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12        |

| 1.4  | ROM read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12        |

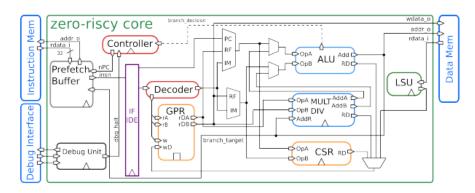

| 1.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13        |

| 1.6  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13        |

| 1.7  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14        |

| 1.8  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14        |

| 1.9  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15        |

| 1.0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LO        |

| 2.1  | RAM read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17        |

| 2.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17        |

| 2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - ·<br>17 |

| 2.0  | 10012 10000 operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ٠.        |

| 3.1  | Eclipse IDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

| 4.1  | testbench architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21        |

| 4.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21        |

| 4.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22        |

| 4.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22        |

| 4.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22        |

| 4.6  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22        |

| 4.7  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23        |

| 4.1  | AT D test - It. write 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20        |

| 5.1  | Eclipse optimization flag setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25        |

| 0.1  | Zonpoe opomination may recome the contract of |           |

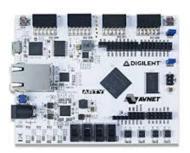

| 6.1  | Arty A7 100T board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28        |

|      | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

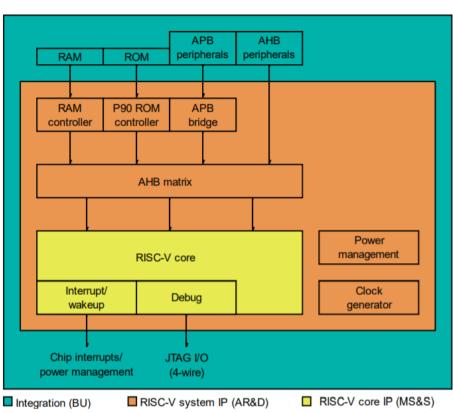

| 7.1  | RISC-V system block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32        |

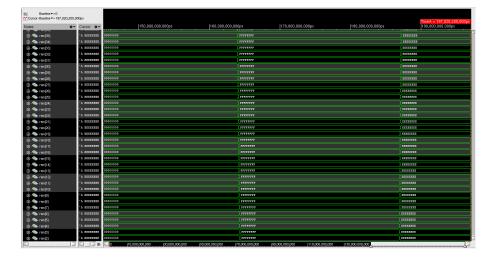

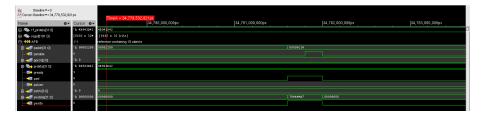

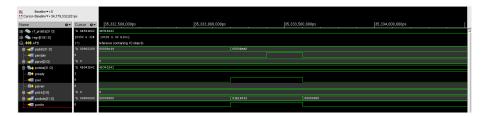

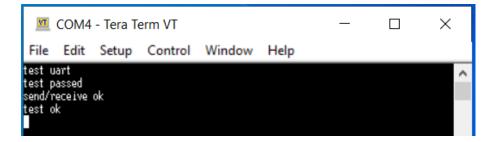

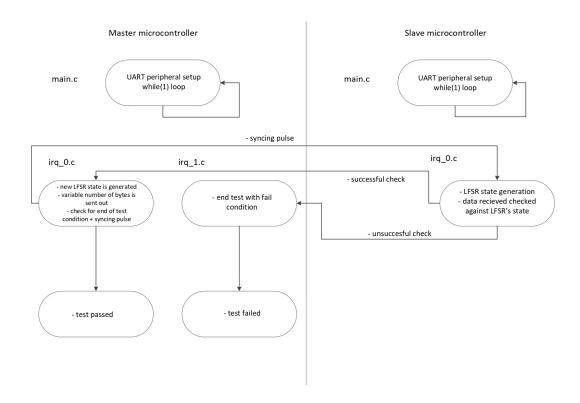

| 7.2  | UART testing phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35        |

| 7.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35        |

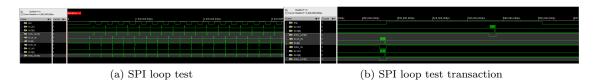

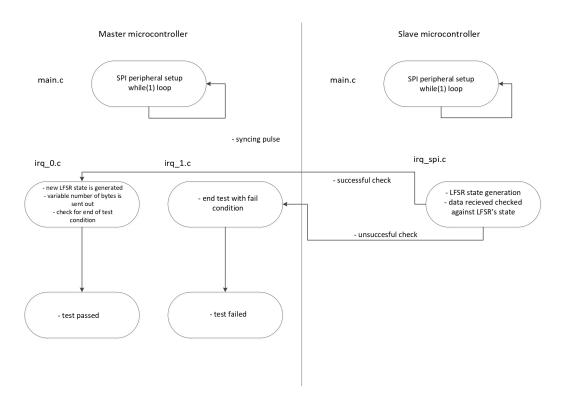

| 7.4  | ~ -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38        |

| 7.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38        |

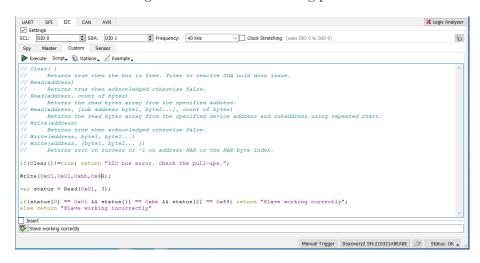

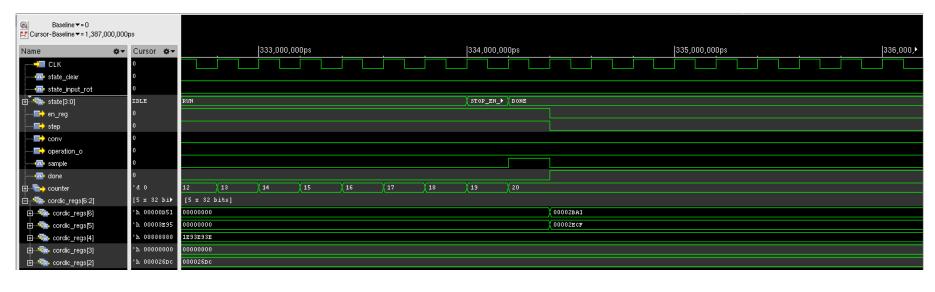

| 7.6  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39        |