### POLITECNICO DI TORINO

Master Degree Course in Electronic Engineering

Master Thesis

### High-Level Synthesis for Ultralow Power FPGAs

Supervisor: Prof. Mihai LAZARESCU Candidate: Davide SALUSSO (257688)

Academic year 2019-2020

### Acknowledgements

The path I followed was not easy, but it taught me what it means to have constancy and perseverance in doing things. I thank my friends who helped me even just by asking about what I was working on or how the exams were going. I thank my family who allowed me to undertake this path and helped in times of difficulty. I thank my girlfriend, Sara, the real engine of my strength, a reference point that gave me the motivation to improve myself more and more.

Thank you all.

## Contents

| Li            | st of | Tables                                                 | V   |

|---------------|-------|--------------------------------------------------------|-----|

| $\mathbf{Li}$ | st of | Figures                                                | VII |

| 1             | Intr  | oduction                                               | 1   |

|               | 1.1   | Detection techniques for people indoors                | 1   |

|               | 1.2   | Capacitive sensing compared to other techniques        | 2   |

|               | 1.3   | Data processing with neural networks on the sensor     | 3   |

|               | 1.4   | High level neural networks synthesis                   | 3   |

| <b>2</b>      | Cap   | acitive Sensors                                        | 5   |

|               | 2.1   | Operating principles                                   | 5   |

|               | 2.2   | Localization and identification applications           | 7   |

|               | 2.3   | Types of reading front end                             | 8   |

|               | 2.4   | Data processing on the sensor                          | 14  |

| 3             | Neu   | ral networks for sensor data processing                | 15  |

|               | 3.1   | What is a neural network                               | 15  |

|               |       | 3.1.1 Learning method                                  | 16  |

|               |       | 3.1.2 Advantages and disadvantages of a neural network | 18  |

|               | 3.2   | Types of neural networks                               | 18  |

|               | 3.3   | Multi-Layer Perceptron neural networks                 | 19  |

|               | 3.4   | Description of the neural network used                 | 20  |

| 4             | Ver   | y low power FPGA                                       | 25  |

|               | 4.1   | FPGAs types and performances compared                  | 25  |

|               |       | 4.1.1 Lattice FPGA features                            | 26  |

|               |       | 4.1.2 Microsemi FPGAs features                         | 26  |

|               |       | 4.1.3 Other low power FPGAs                            | 26  |

|               |       | 4.1.4 Microcontrollers                                 | 27  |

|               | 4.2   | FPGA programming mode                                  | 29  |

|               |       | 4.2.1 Manual programming                               | 29  |

|              |       | 4.2.2   | High level synthesis                                                                              | • |   |   |   |   | 30 |

|--------------|-------|---------|---------------------------------------------------------------------------------------------------|---|---|---|---|---|----|

|              |       | 4.2.3   | Optimizations                                                                                     | • | • | • | • | • | 30 |

| <b>5</b>     | Hig   | n level | synthesis for FPGA                                                                                |   |   |   |   |   | 33 |

|              | 5.1   | High le | evel synthesis flow                                                                               |   |   |   |   |   | 33 |

|              | 5.2   | Limits  | of Vivado HLS                                                                                     |   |   |   |   |   | 35 |

|              | 5.3   | Code u  | used for neural network and optimizations                                                         |   |   |   |   |   | 36 |

|              |       | 5.3.1   | Synthesis diretives                                                                               | • |   |   |   |   | 38 |

|              |       | 5.3.2   | Design space exploration                                                                          | • | • | • | • | • | 40 |

| 6            | Exp   | erimen  | ntal results                                                                                      |   |   |   |   |   | 43 |

|              | 6.1   |         | devices                                                                                           |   |   |   |   |   | 43 |

|              | 6.2   |         |                                                                                                   |   |   |   |   |   | 43 |

|              |       | 6.2.1   | Radiant Software 2.0                                                                              |   |   |   |   |   | 44 |

|              |       | 6.2.2   | Libero SoC v11.9                                                                                  |   |   |   |   |   | 46 |

|              | 6.3   | Workfl  | ow                                                                                                |   |   |   |   |   | 47 |

|              | 6.4   | FPGA    | manual programming results                                                                        | • |   |   |   |   | 52 |

|              |       | 6.4.1   | Manual implementation on Lattice ICE40UP5K $\therefore$                                           | • |   |   |   |   | 52 |

|              |       | 6.4.2   | Manual implementation on Microsemi AGLN250 . $% \left( {{{\rm{AGLN250}}} \right)$ .               | • |   |   |   |   | 52 |

|              |       | 6.4.3   | Manual implementation on Microsemi<br>$\rm M1AGL600$ .                                            | • |   |   |   |   | 53 |

|              |       | 6.4.4   | Manual implementation on Microsemi M1AGL1000                                                      |   |   |   |   |   | 53 |

|              |       | 6.4.5   | Achieved manual results                                                                           | • |   |   |   |   | 54 |

|              | 6.5   | Results | s and discussion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | • |   |   |   |   | 55 |

|              |       | 6.5.1   | DSP mapping on Lattice FPGA                                                                       |   |   |   |   |   | 58 |

|              |       | 6.5.2   | Lattice ICE40UP5K FPGA                                                                            | • |   |   |   | • | 61 |

|              |       | 6.5.3   | Microsemi AGLN250 FPGA                                                                            |   |   |   |   |   | 67 |

|              |       | 6.5.4   | Microsemi M1AGL600 FPGA                                                                           |   |   |   |   |   | 72 |

|              |       | 6.5.5   | Microsemi M1AGL1000 FPGA                                                                          |   |   |   |   |   | 77 |

|              |       | 6.5.6   | Comparison with objectives and manual flow                                                        | • |   |   | • | • | 81 |

| 7            | Con   | clusion | 1                                                                                                 |   |   |   |   |   | 89 |

| $\mathbf{A}$ | App   | endix   |                                                                                                   |   |   |   |   |   | 91 |

|              |       |         | of the MLP neural network $(.c++)$                                                                |   |   |   |   |   | 91 |

|              | A.2   |         | of the MLP neural network (.h) $ \cdot $                                                          |   |   |   |   |   | 94 |

|              | A.3   |         | of DSP (.c++) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                        |   |   |   |   |   | 94 |

|              |       |         | of DSP $(h)$ $(.h)$ $()$                                                                          |   |   |   |   |   | 95 |

| Bi           | bliog | raphy   |                                                                                                   |   |   |   |   |   | 97 |

## List of Tables

| 2.1  | Variation of dielectric properties in different body tissues at different |    |

|------|---------------------------------------------------------------------------|----|

|      | frequencies.                                                              | 6  |

| 4.1  | Features of ultralow-power FPGAs used in the reference programming.       | 27 |

| 4.2  | Features of low power FPGAs used in the reference programming             | 27 |

| 4.3  | Results of manual programming on MCUs                                     | 28 |

| 5.1  | Summary of the advantages and disadvantages of the directives used.       | 40 |

| 6.1  | Performance and resource on FPGAs in the manual programming               |    |

|      | experiment                                                                | 55 |

| 6.2  | Resource occupation of the test of DSPs on Lattice FPGAs                  | 61 |

| 6.3  | Directives used in the solutions for the Lattice FPGA.                    | 63 |

| 6.4  | Performance of the solution 12 of the Lattice FPGA ICE40UP5K. $\ .$       | 63 |

| 6.5  | Performance of the solution 13 of the Lattice FPGA ICE40UP5K. $\ .$       | 64 |

| 6.6  | Performance of the solution 14 of the Lattice FPGA ICE40UP5K. $\ .$       | 65 |

| 6.7  | Report data for the solution of Lattice FPGA                              | 66 |

| 6.8  | Comparison of resources occupation between Vivado and Radiant             | 67 |

| 6.9  | Directives used in the solutions for the Microsemi AGLN250 FPGA.          | 69 |

| 6.10 | Performance of the solution 6 of the Microsemi FPGA AGLN250. $\ .$        | 69 |

| 6.11 | Performance of the solution 7 of the Microsemi FPGA AGLN250. $\ .$        | 70 |

| 6.12 | Power and energy comparison for solution 6 and 7 of Microsemi             |    |

|      | FPGA AGLN250 between VCD and vectorless analysis                          | 71 |

| 6.13 | Report data for the solutions of Microsemi AGLN250 FPGA                   | 71 |

| 6.14 | Directives used in the solutions for the Microsemi M1AGL600 FPGA.         | 72 |

| 6.15 | Performance of the solution 11 of the Microsemi FPGA M1AGL600.            | 74 |

| 6.16 | Performance of the solution 12 of the Microsemi FPGA M1AGL600.            | 74 |

|      | Performance of the solution 13 of the Microsemi FPGA M1AGL600.            | 75 |

| 6.18 | Power and energy comparison for solution 11, 12 and 13 of Microsemi       |    |

|      | M1AGL600 between VCD and vectorless analysis                              | 76 |

|      | Report data for the solution of Microsemi M1AGL600 FPGA                   | 76 |

| 6.20 | Directives used in the solutions for the M1AGL1000 of Microsemi           |    |

|      | FPGA                                                                      | 77 |

|      | Performance of the solution 16 of the Microsemi FPGA M1AGL1000.           | 79 |

| 6.22 | Performance of the solution 17 of the Microsemi FPGA M1AGL1000.           | 80 |

| 80 |

|----|

| 81 |

| 82 |

| 82 |

|    |

## List of Figures

| 2.1  | Principal four capacitance of a load mode capacitive sensor            | 5        |

|------|------------------------------------------------------------------------|----------|

| 2.2  | Capacitive sensor based on 555 integrated circuit.                     | 7        |

| 2.3  | A circuit used to determine the capacitance                            | 9        |

| 2.4  | Resistor network for low-pass filter and experimental setup            | 10       |

| 2.5  | Front end interface used to measure the difference in amplitude be-    |          |

|      | tween the output of two RC low-pass filters and experimental setup.    | 11       |

| 2.6  | Front end interface used to reduce the environmental noise and ex-     |          |

|      | perimental setup                                                       | 13       |

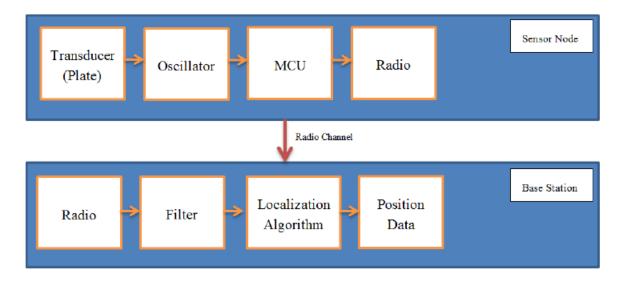

| 2.7  | Main blocks of sensor node and base station                            | 14       |

| 3.1  | Typical Architecture of neural network                                 | 16       |

| 3.2  | Structure of a neuron.                                                 | 17       |

| 3.3  | Behavior of ReLU function.                                             | 20       |

| 3.4  | Flow of data augmentation.                                             | 21       |

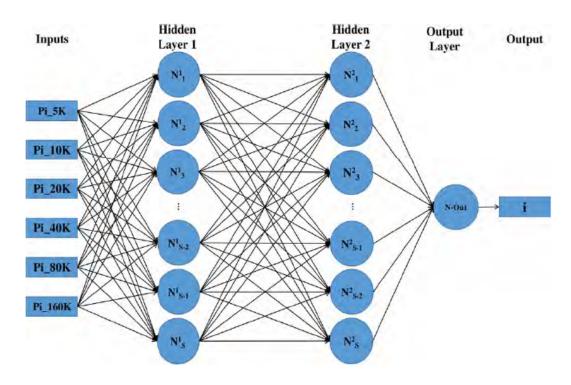

| 3.5  | Structure of multi-layer perceptron neural network                     | 22       |

| 5.1  | Vivado HLS flow design to test the operation.                          | 34       |

| 5.2  | Flow of directives used to find the best performance                   | 42       |

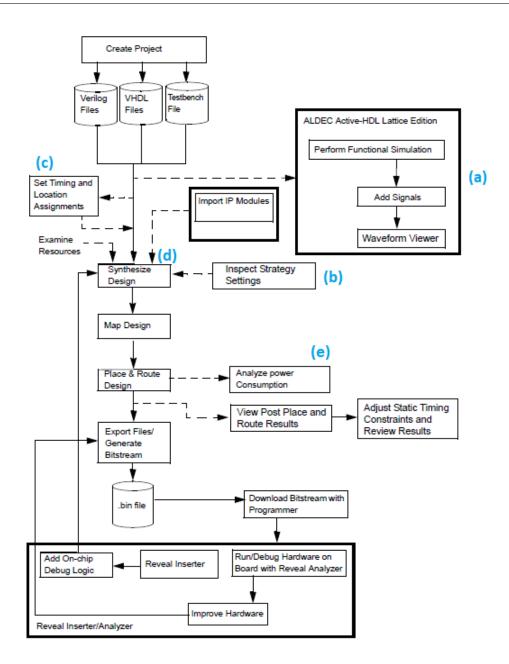

| 6.1  | Workflow of Radiant Software                                           | 45       |

| 6.2  | Workflow of Microsemi Software                                         | 46       |

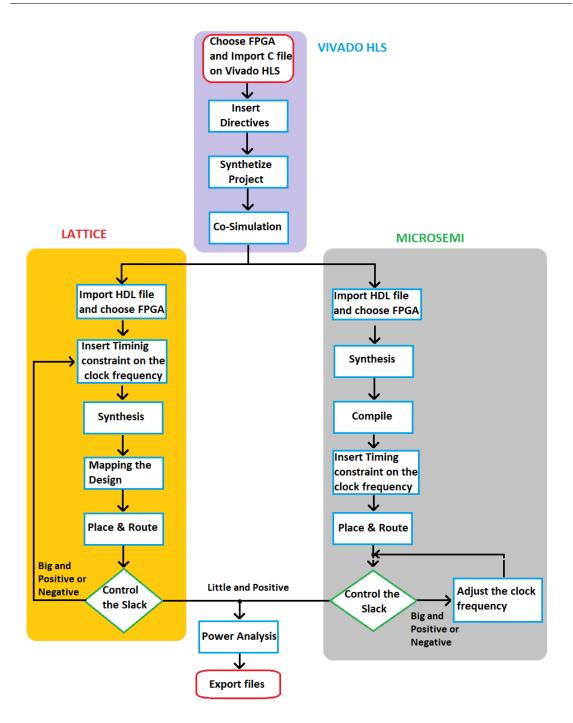

| 6.3  | Workflow followed to obtain .bin file for programming                  | 48       |

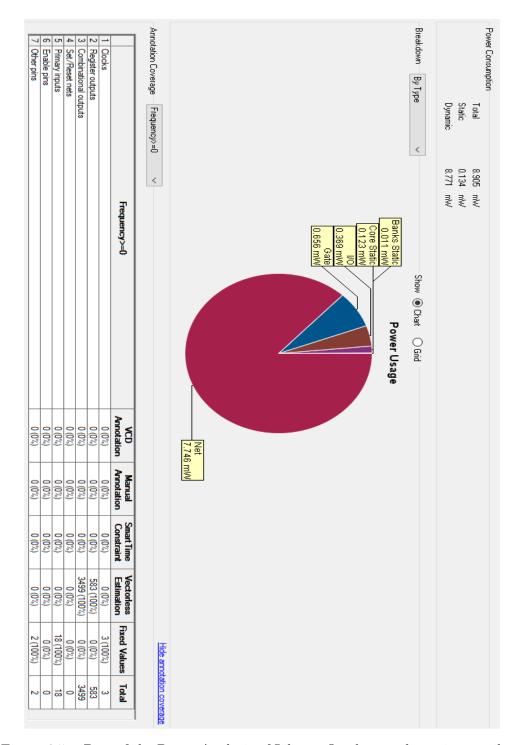

| 6.4  | Part of the Power Analysis to see the power of the inputs              | 50       |

| 6.5  | Part of the Power Analysis of Libero                                   | 51       |

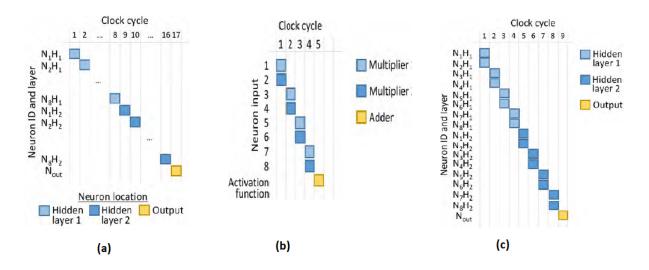

| 6.6  | Ideal scheduling of the operation of the neural network for the man-   |          |

|      | ual programming                                                        | 53       |

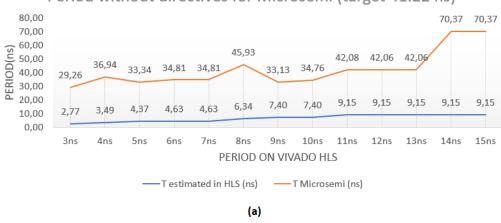

| 6.7  | Trend of the clock period based on the modification at the HLS level   |          |

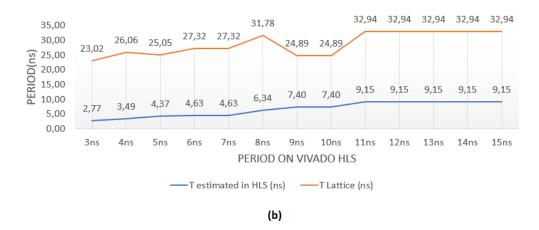

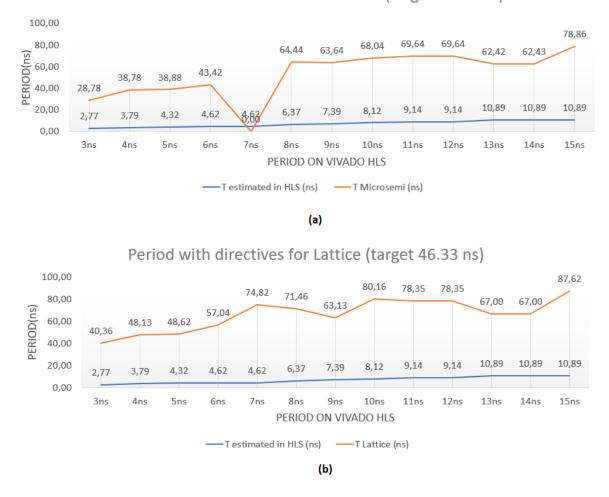

|      | with no directives.                                                    | 57       |

| 6.8  | Trend of the clock period based on the modification at the HLS level   | 58       |

| 6.0  | With directives.                                                       | 99       |

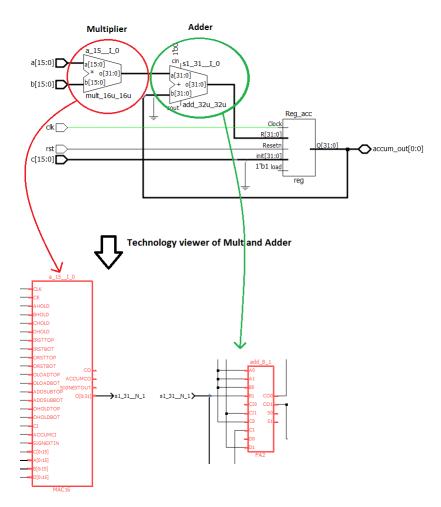

| 6.9  | Netlist Analyzer and Technology View of DSP used as MAC write manually | 60       |

| 6 10 | Report of Radiant on area used of DSP write manually.                  | 60       |

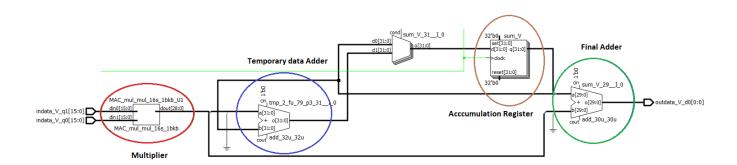

|      | Datapath of circuit with one DSP written in HLS.                       | 60<br>61 |

| 0.11 | Datapath of circuit with one DSF written in fills                      | 01       |

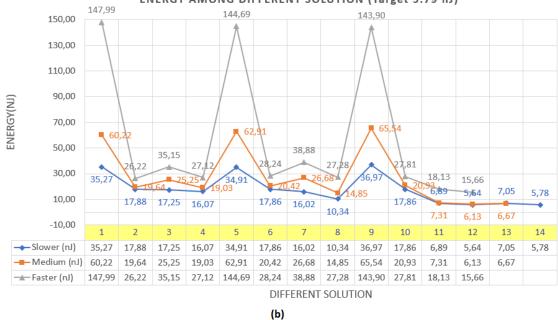

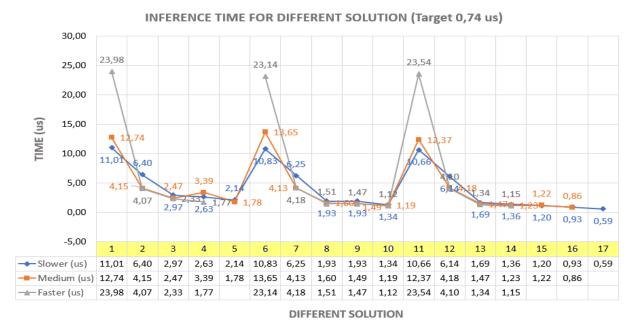

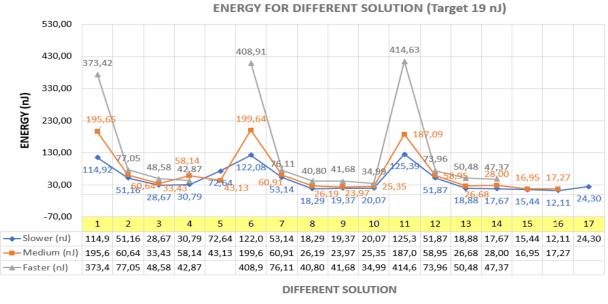

| 6.12 | Inference time and Energy for different 14 Solution for Lattice FPGA |    |

|------|----------------------------------------------------------------------|----|

|      | ICE40UP5K                                                            | 62 |

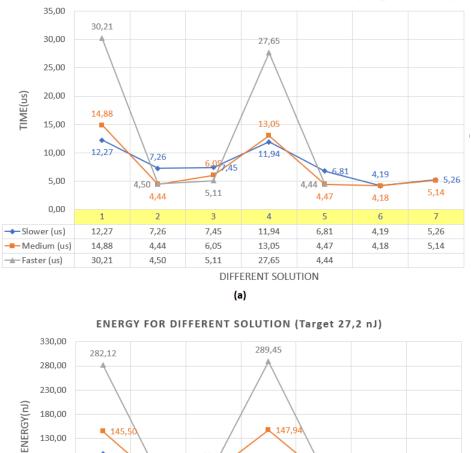

| 6.13 | Inference time and Energy for different 7 Solution for Microsemi     |    |

|      | FPGA AGLN250                                                         | 68 |

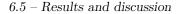

| 6.14 | Inference time and Energy for different 13 Solution for Microsemi    |    |

|      | FPGA M1AGL600                                                        | 73 |

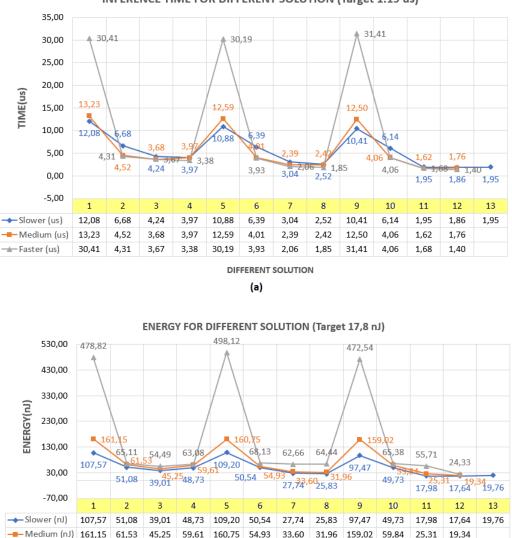

| 6.15 | Inference time and Energy for different 17 Solution for Microsemi    |    |

|      | FPGA M1AGL1000                                                       | 78 |

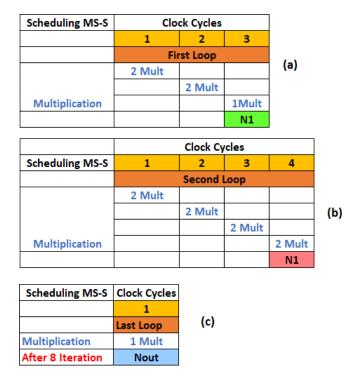

| 6.16 | Scheduling find on Vivado HLS in the Analysis view for the solution  |    |

|      | of Lattice FPGA                                                      | 83 |

| 6.17 | Scheduling of the multiplications to obtain one output of the neuron |    |

|      | of the neural network for the solution for Microsemi FPGA AGLN250.   | 85 |

| 6.18 | Scheduling find on Vivado HLS in the Analysis view for the solution  |    |

|      | of Microsemi FPGA M1AGL600.                                          | 86 |

| 6.19 | Scheduling find on Vivado HLS in the Analysis view for the solution  |    |

|      | of Microsemi FPGA M1AGL1000                                          | 88 |

#### Abstract

The subject of this thesis is the capacitive sensors used in locating people indoors, a field that is becoming very important especially for the health care of the elderly. This sensors have numerous advantages: cost, power, privacy and ease of installation while their main disadvantage is the steep loss of sensitivity by increasing the distance between the sensor and the person. To reduce the cost and installation complexity, the sensors are used in load mode, i.e. only one plate of the capacity is needed because the other plate is the person's body along with the surrounding environment.

In this thesis instead of processing the data on board the sensor with a microcontroller we used an ultralow-power FPGA like a hardware accelerator, and to process the data we use a neural network of the Multi-layer perceptron type synthesized with the high-level-synthesis (HLS) method. We will then compare the results obtained in terms of inference time, energy, power, clock frequency, clock cycles and area compared to the data obtained in a manual implementation [1]. The neural network (NN) used is of the multi-layer perceptron type, in which there are two hidden layers formed by eight neurons each and an output layer formed by a neuron. The NN takes six 16-bit inputs and generates one output of four-bit. The C code of this NN will be synthesized using Vivado HLS, which also allows to insert directives to optimize the generated code. Subsequently the created VHDL code will be compiled using the FPGA tools, which are: Radiant tool for ICE40UP5K of the Lattice family and Libero tool for AGLN250, M1AGL600 and M1AGL1000 of the Microsemi family. These FPGAs, that have all different resources, have been chosen as they are ultra low-power. So, the code created by HLS, is implemented on these FPGAs. The FPGA-specific synthesis tool may not be the completely compatible with the Xilinx Vivado HLS generated code.

The method followed to collect the data to be compared with those found by manual programming has been: start from HLS where the C code is synthesized by also adding directives to optimize it, and they have been added in such a way as to being able to explore multiple solutions, starting from a low level of parallelism and then increasing it from solution to solution and seeing how the various performance and resource metrics changed. After that, through Co-simulation, again on Vivado-HLS, it was verified that the synthesized code still worked as expected. From here, the two tools of the two families of FPGAs were used to implement the code on them and collect the various data. Many solutions have been created for the different FPGAs, and there are different implementations of the same solution as we tried to change the speed (clock period) imposed on HLS and see what effect it would have on the final implementation. The trade-off is between performance and resource occupation, controlled using synthesis directives, and the ensuing Vivado HLS overhead. In addition to the area occupied by the optimizations, there is also the area occupied by the state machine that Vivado HLS creates for the control of the project. The maximum parallelism may not be achieved always, due to resource limitations. This is also due to the imperfect compatibility of the HDL code created by HLS with the two synthesis tools of the families of target FPGAs.

The results of the manual programming of the NN achieved by the reference manual implementation were not achieved for all the FPGAs, in particular for the smallest ones, AGLN250, and the M1AGL600, even if in any case the values of the data found are not far from the target ones. Excellent results were obtained for the Lattice FPGA, with, the lowest power and energy of both HLS and manual programming 5.23 mW and 5.78 nJ are obtained, against 6.24 mW and 5.79 nJ find in the manual implementation. This is because on this FGPA there are blocks that perform dedicated operations, DSP, and in particular, multiplications, which are the operations that require more area, have been assigned to these blocks thus not consuming any other area and thus allowing to add directives to obtain maximum parallelism. Also the inference time find is good, 1.10  $\mu$ s, which is very close to that find in manual programming, 0.93  $\mu$ s. With the Microsemi M1AGL1000 FPGA, the largest, it was possible to achieve excellent results, in particular the lowest inference time, 0.86  $\mu$ s among all FPGAs with HLS, while in reference programming  $0.74 \ \mu s$ . Also a good energy was obtained, 17.27 nJ against 19 nJ of the manual programming.

# Chapter 1 Introduction

Identifying people indoors is extremely useful in a lot of fields, especially in the health care of the elderly. Over the years many techniques have been adopted but they always had a counterpart that made their use counterproductive, for example techniques based on image, video and gait recognition have very good performance, but are very expensive and violate privacy of the user, or techniques in which the person have to brought a device to be located, but this can be uncomfortable and can be forgotten. It turned out that capacitive sensors could be used, which had great benefits in terms of cost and consumption. Their big problem was that they lost reliability with increasing distance of the person to be located. To improve the data processing on board the sensor, it was decided to use a neural network installed on a microcontroller or on a FPGA (Field-Programmable Gate Array), which can be implemented through manual programming, therefore the programmer describes the network by creating the HDL (Hardware Description Language) file himself, or through high level (C or C++), the tool created the HDL file by itself.

#### **1.1** Detection techniques for people indoors

The techniques for detecting people in buildings or rooms have become extremely important for a wide range of applications such as home or building automation, security, video games with virtual reality and in trying to make life of elderly people more confident and assisted.

Over the years, the scientific community has proposed many solutions for this research, where the main objectives were to create a device easy-to-install, inexpensive, low-power, small and, above all, respecting the privacy of those who use it. Another fundamental requirement is that they are not harmful to the human body, ultrasound transceivers [2] have been created for the localization of people or objects, but exposure for a long time to ultrasound can be harmful in fact to prevent these emissions many countries have imposed a limit on the body's exposure to ultrasound, so as to prevent health problems [3]. The results provided by these detections have to be reliable, D.Yang et al. proposed a technique based on pyroelectric infrared (PIR) sensors and an accessibility map of the indoor environment [4], but the results provided by these sensors were not optimal as they are prone to errors given by the environment and sources of heat, and to obtain good results the system need more sensor, so the cost increases. Other techniques based on Wi-Fi [5] or Bluetooth [6], on the other hand, require people to carry a device with them, which can be both unreliable and uncomfortable, as well as the fact that they can often forget to wear it. Techniques that use devices that instead violate people's privacy terms are those proposed by Y.Zheng et al. [7] and G. Lu et al. [8], who respectively proposed a technology based on an indoor vision-based navigation system and a system based on thermal images for localization, and these techniques, in addition to not respecting privacy, are expensive.

The alternative to these techniques are capacitive sensors, which can meet most of the indicated requirements.

#### 1.2 Capacitive sensing compared to other techniques

Capacitive sensors are used in many short-range applications such as the smartphone touchscreen, in tunnel-effect scanning microscopes, in editing systems and also in musical instruments. Thanks to their properties, it has been thought of being able to use them also in the recognition of people, in their identification and localization. The type of capacitive sensors used for this purpose operates in loadmode using a single plate while other plate is made by the environment and human body. This sensor measures the capacity of the human body at different frequencies, and this measurement will be influenced by the composition of it (height, gender, weight, muscles, etc.) and environment which must be compensated. Given these differences, the electrical and dielectric properties of the users will change, and from them people can be identified. So being that they can be built using simply with a plate, they are very easy to install (can be install near the light switches [9] or in the bed [10] to monitor the sleep disorders), they are not expensive (like system based on thermal imaging for indoor localization [11]), they do not invade the user's privacy like [11] and do not require any additional devices that must be worn like technique based on Wi-Fi or Bluetooth. Thanks to their ease of installation there are other uses of capacitive sensors, at lower ranges than localization in a room, for example they can be installed in a computer so that they can interact during a game [12], they can be used in beds to determine sleep patterns [10] or on a chair to prevent the patient from falling [13]. They can also be used to detect different types of walks [14].

The downside of these sensors is the loss of sensitivity with increasing distance. They become very sensitive to environmental factors such as electrostatic and magnetic noise, humidity or temperature. From [15] it turns out that at a distance greater than 10 times the size of the sensor, the variation of the capacity measurement is below 0.01%, therefore hardly distinguishable from noise, this latter in fact affect the measurements of the voltage across the capacitance for example, but not affect the capacitance itself, that depends on the electric and dielectric properties, and geometry of the sensor and environment.

## **1.3** Data processing with neural networks on the sensor

The accuracy of the capacitive sensor is an essential quality to obtain good results, to improve it can can be used Machine Learning algorithms, especially Neural Networks (NNs), such as 1-D Convonutional NNs (CNNs) or Long-Short Term Memory NNs (LSTM). In [16] a study is carried out on the recognition of people using 1D CNNs, a Recursive Neural Network (RNN) and a hybrid architecture with various sensors, in [17] LSTM networks are used together with 1D CNN to find and to classify rare acoustic sounds, in [18] the authors use LSTM networks for localization in closed environments using light and magnetic sensors.

Neural networks can be implemented in software (SW) using microcontrollers (MCUs) or in hardware (HW) using FPGA, and the goal of both implementations is to accelerate the neural network by trying to consume as little energy as possible. In the article by Braga et al. [19] the performance, accuracy, use of resources and power consumption of an NN implemented both in SW (using Xilinx Microblaze microprocessor) and in HW (using FPGA of the Xilinx family) are analyzed. The authors of [20] propose a method to optimize accuracy by minimizing the area for a Multi-Layer Perceptron (MLP) neural network implemented on FPGA. To try to improve the critical path (CP), and consequently improve operating frequency, of an MLP neural network, Bahoura et al. [21] propose a low latency real-time system for gas classification using an accurate MLP neural network implemented on Xilinx FPGA with fixed point arithmetic. In the study of Marwen et al. [1] the performance of an MLP neural network is tested on two low power MCUs and subsequently on four different ultralow-power FPGAs.

#### 1.4 High level neural networks synthesis

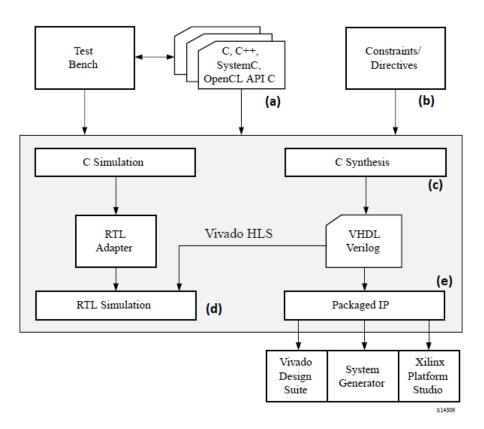

The HLS is the link between hardware and software domain. The tools used for HLS, starting from the high level code (written in C, C++ or SystemC) and generates the code written at low level, register transfer level (RTL), in Verilog or VHDL,

which can then be implemented on FPGA. HLS provides benefits both from the HW point of view, in fact it improves productivity because it allows the HW programmer to work at a higher level of abstraction and at the same time to create HW with optimization, but also from the point of view of the software programmer, allowing to speed up the calculation of the algorithms on the future FPGA used. For these reasons, various tools [23] have been created over the years for this purpose, like Vivado HLS which synthesizes high-level code and then implements it on the FPGA of the Xilinx family.

The experiment performed is based on the use of this tool to synthesize an neural network of the MLP type, used in the field of capacitive sensors to increase its accuracy, and try to compare the performances obtained in terms of power, energy, inference time, operating frequency and latency, with the performance obtained in [1] in which HLS is not used for the creation of the NN, but only low level language (RTL). Both experiments were performed on 4 different ultralow-power FPGAs that do not belong to the Xilinx family (one of them is from the Lattice iCE40 family while the other three are from the Microsemi IGLOO family), then the RTL code generated by Vivado HLS, which should be implemented on FPGAs of the family mentioned above, will not perfectly adapt to the design of the ultralow-power FPGAs used for the experiment, which have been selected from those of Xilinx for their low static power [1].

# Chapter 2 Capacitive Sensors

For locating people indoors, many techniques have been used, including the capacitive sensors. They have several advantages, first of all the low power consumption. There are various front-end configurations used each with a different purpose.

#### 2.1 Operating principles

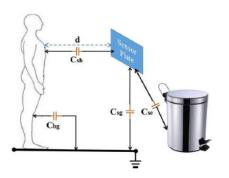

The capacitive sensors can be used to localize and monitor persons or objects. They are used in load-mode, where the human body is used as second plate of capacitance, and this mode needs only a single transducer plate that form with the human body and the environment several capacitances, in particular four:  $C_{sg}$ , capacitance between sensor and ground,  $C_{bg}$ , capacitance between the human body and ground,  $C_{se}$ , capacitance between sensor and environment and  $C_{sb}$ , capacitance between sensor and human body, like Figure 2.1 (taken from [24]) shows.

Figure 2.1. Principal four capacitance of a load mode capacitive sensor, taken from [24]:  $C_{sg}$ , between sensor and ground,  $C_{bg}$ , between the human body and ground,  $C_{se}$ , between sensor and environment and  $C_{sb}$ , between sensor and human body.

To identify the person is taken the value of  $C_{sb}$  at different frequencies, in particular, the person dielectric and electric properties change with different composition of the human body, in fact the values of permittivity ( $\epsilon$ ) and conductivity ( $\sigma$ ) of the human body change with the frequencies of the electric fields, so, thanks to this difference, is possible to recognize the members of a small group of people like a family. In this regard, Gabriel [25] made a study on how the dielectric properties change according to the parts of the body, they are summarized in Table 2.1, at the frequencies used by our sensors.

Table 2.1. Variation of dielectric properties ( $\epsilon$  and  $\sigma$ ) in different body tissues (muscle, fat, bones and breast fat) at different frequencies, taken from [25].

| Frequency | Mu                  | ıscle                | Fat                 |                      | Bo                   | nes                  | Breast fat           |                       |  |

|-----------|---------------------|----------------------|---------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|--|

| (kHz)     | $\varepsilon_r$     | $\sigma$ (S/m)       | $\varepsilon_r$     | $\sigma$ (S/m)       | $\varepsilon_r$      | $\sigma$ (S/m)       | $\varepsilon_r$      | $\sigma$ (S/m)        |  |

| 5         | $6.0 \times 10^{4}$ | $4.0 \times 10^{-1}$ | $1.2 \times 10^{3}$ | $1.8 \times 10^{-2}$ | $1.4 \times 10^{3}$  | $3.0 \times 10^{-3}$ | $1.0 \times 10^{3}$  | $11.0 \times 10^{-3}$ |  |

| 10        | $3.0 \times 10^4$   | $5.0 \times 10^{-1}$ | $1.0 \times 10^{3}$ | $1.8 \times 10^{-2}$ | $1.2 \times 10^{3}$  | $3.0 \times 10^{-3}$ | $1.3 \times 10^2$    | $11.0 \times 10^{-3}$ |  |

| 20        | $1.0 \times 10^{4}$ | $6.0 \times 10^{-1}$ | $1.4 \times 10^{2}$ | $1.8 \times 10^{-2}$ |                      | $3.0 \times 10^{-3}$ | $1.1 \times 10^{2}$  | $11.0 \times 10^{-3}$ |  |

| 40        | $1.4 \times 10^{3}$ | $6.0 \times 10^{-1}$ | $1.1 \times 10^{2}$ | $1.9 \times 10^{-2}$ | $1.05 \times 10^{3}$ | $3.0 \times 10^{-3}$ | $1.0 \times 10^{2}$  | $11.0 \times 10^{-3}$ |  |

| 80        | $1.1 \times 10^{3}$ | $6.0 \times 10^{-1}$ | $1.0 \times 10^{2}$ | $1.9 \times 10^{-2}$ | $1.0 \times 10^3$    | $4.0 \times 10^{-3}$ | $1.4 \times 10^1$    | $11.0 \times 10^{-3}$ |  |

| 160       | $2.9 \times 10^2$   | $7.0 \times 10^{-1}$ | $1.5 \times 10^{1}$ | $1.9 \times 10^{-2}$ | $1.9 \times 10^{2}$  | $4.0 \times 10^{-3}$ | $1.3 \times 10^{-1}$ | $11.0 \times 10^{-3}$ |  |

The capacitance measured (in Farad) between two parallel infinitely large plates with a small distance between them is given by the formula (2.1):

$$C = \frac{\varepsilon_0 kA}{d} \tag{2.1}$$

where:

- k: is the relative dielectric permittivity of the material between plates, that in the case of free space is 1.

- $\epsilon_0$ : is the absolute dielectric permittivity of free space (equal to  $8.854 \times 10^{-12}$  F/m).

- d: is the distance between the capacitors plates.

- A: is the area of capacitors plates.

Capacitance plate strongly depends both on the area of the capacitive sensor and on the distance at which the measurement is carried out since the sensor works in load-mode.

So  $C_{sb}$  depends from the distance of the human body and the sensor, and if this distance grows up, the measurement it is no longer accurate because will be affected by environmental factors like noise, temperature and humidity. In particular, the noise can limit the sensor range to 10-15 times the diagonal of their plate [26].

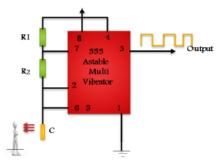

A possible type of circuit, used to measure the capacitance between the transducer and the human body while changing the distance, is the one shown in Figure 2.2, taken from [27], which is formed by an oscillator based on a 555 integrated circuit (IC) configured as an astable multivibrator, for which the oscillation frequency is given by the formula (2.2):

Frequency =

$$\frac{1}{0.7 (R_1 + 2R_2) C}$$

(2.2)

Figure 2.2. Structure of a capacitive sensor, taken from [27], based on 555 integrated circuit configured as an astable multivibrator.

#### 2.2 Localization and identification applications

In addition to capacitive sensors, other techniques are used for locating people indoors. For example, J. Rivera-Rubio et al. did a study on a video-based localization method in which the person brought the camera with him and the localization carried out through solutions based on simultaneous localization and mapping (SLAM) algorithms [28].

Other techniques that require that the person to be located wear a device are those based on radio frequency such as GPS, Bluetooth, RFID and Smart phone [29], [30], [31], [32]. These could be problematic as not always people, especially the elderly, remember to wear it, in addition to fact that maybe the device is not comfortable to wear. Instead, techniques based on image, video and gait recognition are often used. Ding et al. presents a pose-invariant facial recognition technique [33], or in [34] a technique has been proposed for facial recognition through the use of deep learning. While for gait recognition a system based on arbitrary view transformation model [35] can be used. There are many techniques based on these principles and the results that they give are very good, their problem is that they are expensive and hardly susceptible for long-term battery-powered operations. Furthermore, being based on images or videos, they violate the user privacy. Other techniques for the identification of the person are: wireless techniques, such as [36], ultra-wideband sensors [37] and techniques that use footstep induced structural vibrations [38].

Capacitive sensors, on the other hand, thanks to their low cost, their easy installation method and their low power consumption, have been designed for identification and tracking of the person in indoor environment. A.R. Akhmareh et al. studied a system based on capacitive sensors for indoor tagless identification in a room [27]. Using the capacitance of the sensors he built an RC oscillator whose frequency is dependent on the distance of the human body, the author also had to apply many noise reduction techniques as at a long distance the sensor loses sensitivity and therefore the movements are no longer captured correctly, in particular at distances greater than the dimensions of the transducter [39] it becomes sensitive to environmental factors. The performance of this localization method depends strictly on the sensor performance. A [15] study was also done to improve the sensitivity of the sensor at distances greater than 10 times its diameter. As explained in the Section 2.1, a capacitance,  $C_{sb}$ , is formed between the human body and the sensor, which depends on the dielectric properties of the body, and based on this, Iqbal et al. [40] presents an identification method based on capacitive sensors, in which the capacitance of the human body at different frequencies is measured and it will be linked to the different structure of the body. Several improvements have been made to this method in [41] that have improved the resolution. In [27] another method has been proposed for the identification of a single person inside a room, also improving the sensitivity on measurement at long distances. The method is based on the indirect measurement of the transducer capacitance by measuring the frequency through an oscillator, after which a baseband digital filter is used to attenuate the measurement noise, finally through localization algorithms the position of the person is found using all the data of the various sensors inserted in the room. Based on this work, in [42], the performance of the localization system is studied using different Machine Learning (ML) algorithms, which are very important if the improvement of the performance of the system is the goal.

#### 2.3 Types of reading front end

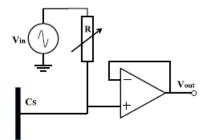

In the studies done over the years, several front-end interfaces for capacitive sensors have been developed in this research group, all based on the principle of measuring the capacitance that forms between the human body and the sensor at different frequencies. In [41], an attempt was made to measure the capacity through its reactive effects at different stimulating frequencies. The circuit used is the one in Figure 2.3, in which the capacitive sensor  $C_s$  is connected in a first order RC low pass filter configuration, and a sine wave is applied as input,  $V_{in}$ , and knowing the amplitude and the frequency is read out of the filter using a high impedance unitary gain buffer thus obtaining the output signal  $V_{out}$ .

Figure 2.3. Circuit used to determine the capacitance made of a first order RC low pass filter, a sine wave applied as input and a high impedance unitary gain buffer, taken form [41].

In this specific experiment the author decided to use a frequency  $f_m = 5 \text{ kHz}$ , so if a signal is put at the input:

$$V_{\rm in}(t) = A\sin(2\pi f t + \theta) \tag{2.3}$$

where  $f = f_m$ . Then tries to calibrate the value of the LPF resistor R, in the event that there are no people in the sensor range, to obtain:

$$V_{\text{out}}(t) = \frac{A}{\sqrt{2}} \sin\left(2\pi f t + \theta - \frac{\pi}{4}\right)$$

(2.4)

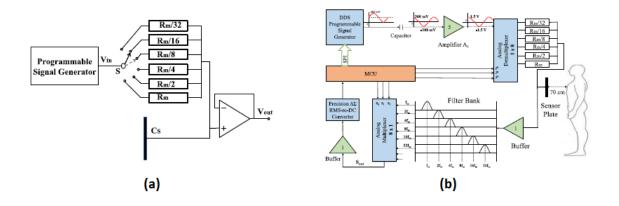

This output is typical low-pass RC filer in which the cutoff frequency is equal to  $f_m$ . After finding the value of resistor R, it is called  $R_m$ , and on the basis of this the resistor array is built as shown in Figure 2.4 (a). Note that both the value of  $f_m$  and of the resistor do not have to be precise, because the method used to find the capacitance is a method based on relative measurements and therefore systematic errors usually cancel themselves out. While it is important that the value of the resistors remain stable and also the excitation frequency of the signal  $V_{in}(t)$  which is tuned as:

$$f = 2^n f_m \tag{2.5}$$

Furthermore, for each frequency generated, the correct resistance is selected by means of an analog switch, S, which is therefore also tuned with the excitation frequency:

$$R = \frac{R_m}{2^n} \tag{2.6}$$

It is important to note that to eliminate excessive attenuation at high frequencies, thus improving the SNR, the cut-off frequency of the RC low pass filter must be kept tuned to the excitation frequency.

Figure 2.4. Resistor network used to create the first-order LPFs tuned for every excitation frequency (from 5 kHz to 160 kHz) and experimental setup of the circuit, taken from [41].

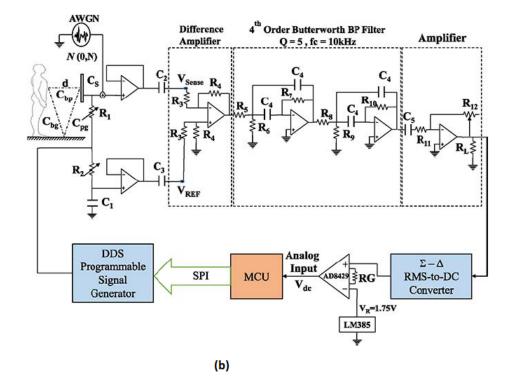

The circuit just described is then part of a final circuit used in the experiments, and is the one shown in Figure 2.4 (b), in which using a direct digital synthesys (DDS) programmable signal generator the excitation frequency is created, it is then programmed from a microcontroller using a serial peripheral interface (SPI). The sine wave generated by the DDS has 600 mVpp and an offset of 300 mV DC then eliminated by a capacitance in series. After that there is an amplifier  $A_1$  which brings the signal entering the switch, S, to an amplitude of 3 Vpp. The switch is controlled by both the MCU and the DDS in order to tune the cutoff frequency of the RC filter. The output of the filter is then buffered and brought into input to a filter bank formed by narrow-band bandpass filters, each of which is centered at the frequency given by (2.5). The filter used will be selected via a multiplexer from the MCU, once the output from the filter bank is obtained, it is converted to DC using a  $\Delta\Sigma$  RMS-to-DC converter and then measured by the MCU.

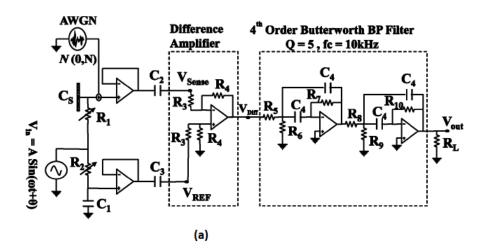

Another front-end capacitive sensor interface is shown in Figure 2.5 (a), taken from [24]. It is used to measure the difference in amplitude between two RC lowpass filters on the same sinusoidal input signal  $V_{in}$ . The first RC filter is made up of  $R_1C_s$ , which varies with  $C_s$ , while the second is  $R_2C_1$  which is therefore fixed with  $C_s$ . Two equal high impedances are used to read the filter output voltage repeaters. Then, before entering the difference amplifier, the capacities  $C_2$  and  $C_3$  eliminate the DC offset. As said before, both  $R_2$  and  $C_1$  are fixed so  $V_{ref}$  has constant amplitude and phase, while  $V_{sense}$ , being  $C_s$  variable, will have non-constant amplitude and phase. The task of the difference amplifier is to subtract  $V_{sense}$  from  $V_{ref}$ , and then amplify the difference by a factor  $G = R_4/R_3$ , at the output there will be  $V_{diff}$ which will be modulated as  $C_s$  varies . Finally, two narrow band high Q-factor

Figure 2.5. Capacitive sensor front end interface used to measure the difference in amplitude between the output of two RC low-pass filters receiving the same sinusoidal input signal and experimental setup used, taken from [24].

band-pass filter are used to eliminate the noise narrow band high Q-factor bandpass filters. This circuit, as shown in Figure 2.5 (b), is then inserted in the final diagram, as was also done with the previous circuit described.

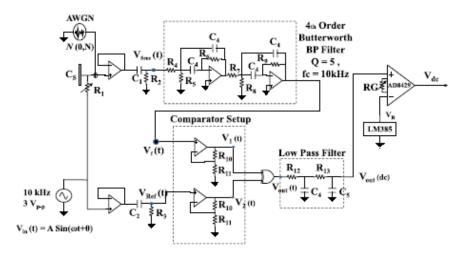

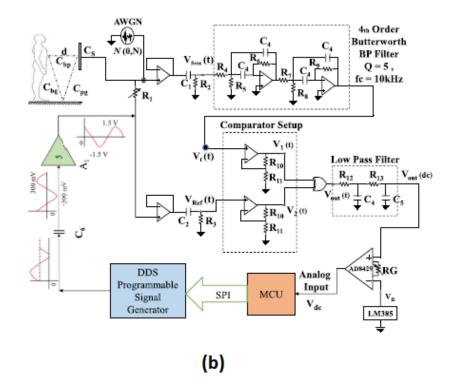

Another front-end interface is the one described in the [15] article, shown in Figure 2.6 (a). The interface measures the phase shift variation of a low pass filter, in which there is also the transducer capacitance. Thanks to this way of measuring it is possible to greatly reduce the environment noise while still having high sensitivity to variations in capacitance. It consists of two analog parts excited by the same signal  $V_{in}(t)$ . In the upper part the signal enters a low-pass filter formed by  $R_1C_s$ , and the characteristics of the filter depend precisely on  $C_s$  which in turn depends on the distance from the person's body. After that the filter output enters a high impedence voltage repeater. In the lower part it is sent to a reading circuit similar to the previous one.

The circuit then, as in the two previous cases, is inserted in the same way in the final circuit used for the experiment, 2.6 (b).

Figure 2.6. Capacitive sensor front end interface used to reduce the environmental noise: circuit and experimental setup, taken from [15].

#### 2.4 Data processing on the sensor

To detect and localize a person in a room, in [27] use a lot of sensors installed in the room, for example in walls or chairs, sofas, etc. The detection system is therefore formed by these sensors and a base station that processes the data collected by them, to estimate the position using various methods such as: Naïve Bayes, k-Nearest-Neighbors, Support Vector Machine.

Figure 2.7 shows the architecture of the detection system. The movement of the person changes the transducer capacity with the distance to the human body. Using the oscillator, like the one in Figure 2.2, this change is converted into a variation in frequency, in fact when the person is close to the sensor plate, the capacitance  $C_{sb}$  becomes larger and the oscillation frequency, according to (2.2), becomes smaller. Then the sensor MCU measures the oscillator frequency with a certain rate, and then via a Zigbee radio module sends it to the base station. In the base station there is a Zigbee radio receiver which receives a continuous stream of raw frequency measurements from all sensors installed in the room. Finally, the data streams received are contained from the base station to a personal computer via a USB connection, so as to perform further processing.

Figure 2.7. Architecture of localization system based on a Zigbee radio transmitter and receiver, taken from [27].

# Chapter 3 Neural networks for sensor data processing

Machine Learning (ML), builds through data analysis analytical models, and is used in many sectors, especially in the field of artificial intelligence. Artificial neural networks (ANN), a part of ML, are mathematical models composed of neurons, whose structure resembles that of a human brain. There are many neural network types since they are used in many fields: Feedforward Neural Network (FNN), like Multilayer Perceptron (MLP), Recurrent Neural Network (RNN), etc. In this thesis, an MLP neural network was used for locating people indoors through capacitive sensors, and it is well suited for classification tasks.

#### 3.1 What is a neural network

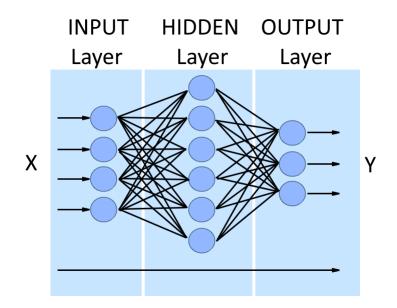

A neural network is a mathematical model whose layered structure remember the structure of the human brain. It is used to solve Artificial Intelligence engineering problems related to different technological fields, for example it can learn from data, so it can be trained to recognize speech patterns or images, like the human brain does, an image of typical NNs is in Figure 3.1 taken from [43].

It is composed of artificial neurons arranged and connected to each other in different layers, usually there is at least one layer for the inputs (input layer) and one for the output (output layer), but the more complex the problems to solve, the more layers there will be (layer between input and output are call hidden layers). Each neuron has a set of inputs and its own weight, to indicate the different importance of each of them, which is regulated, according to a specific rule, automatically neuron by neuron during training until the neural network correctly performs the desired activity (in the beginning they are set randomly). The various neurons of each layer operate in parallel, the first layer receives external inputs, and every neurons with their weights calculate their outputs and then through an activation function

Figure 3.1. Typical Architecture of neural network in which there is an input layer, a hidden layer, and an output layer, taken from [43].

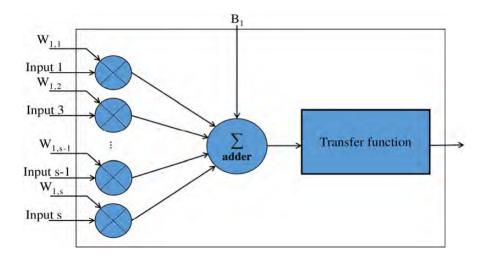

and a threshold value the output value of the neuron is weighted, and then it will enter as input into all neurons of the next layer, and this procedure is follow until the end. An image of a neuron is Figure 3.2, taken from the article of Marwen [1], where all inputs are multiplied with their weights, then all the results are added together with also a bias which is used to adjust the output along with the weighted sum of the inputs to the neuron, thus, bias is a constant which helps the model in a way that it can fit best for the given data. Then the output is calculated through the transfer (activation) function, that is used to determine the output of NN like "yes" or "no", so it map the output in range that can go from 0 to 1, -1 to 1 etc.

#### 3.1.1 Learning method

To understand how to behave and solve the specific problem for which it will be used, the neural network will need to be trained, then modify their structure by changing the value of the weights according to the learning method used. Three main algorithms are used for this:

• Supervised Learning: with this method the NN is supplied with both an input set (call training set) and the corresponding desired outputs that should be obtained with that specific input set. Through them, the network is able to understand the link between input and output, so that, having understood this connection, the network is able to reuse this rule with other similar problems. The operator will have the task of adjusting the various weights in order to

Figure 3.2. Structure of a neuron, taken from [1]: all inputs are multiplied with their weights, then the results are added together with also the bias and finally pass through the activation function.

have better and better outputs, therefore there is an Error-back Propagation mechanism in this method. If the training is successful, the network learns the relationship between input and output and therefore from now on will be able to predict the exit even when it is unknown. Neural networks of the MLP type use this method.

- Unsupervised Learning: with this method, only a set of inputs is provided to the NN, and according to them the neural network learns the scheme and the logical structure of the inputs. The weight value will be modified during the learning of the same nodes of the network. A neural network that uses this method is the Hopfield network.

- Reinforcement learning: in this method the NN does not try to find an input-output association as in the previous methods, but it learns by interacting only with the environment trying to get to the desired result through a mechanism of "rewards" (actions that allow to get closer to the result) and "punishment" (errors to be eliminated but from which one tries to learn). Then through a feedback mechanism, the algorithm is guided to the right learning process.

#### 3.1.2 Advantages and disadvantages of a neural network

The fundamental advantages of neural networks, which have led to their use in vast fields, are:

- They can work in parallel thus treating a large amount of data.

- Fault tolerance, this is a consequence of the first advantage, in fact the possibility of an error occurs but it is unlikely that it will block the whole system, perhaps it will only reduce performance.

- Noise tolerance, often even if the inputs provided are not precise, it still manages to operate correctly.

- It is able to self-regulate in case of environmental changes.

However they also have limits:

- They are "Black box", that is the internal calculations cannot be fully analyzed, even if the final output is correct or otherwise acceptable.

- The training phase to fix the weights of individual neurons can take a long time if the number of available variables is very large.

- The output often are not the perfect output, but this in many cases is not necessary.

- The creator of the network has a fundamental role, because there are no algorithms that define an optimal network, everything lies in the skill of the operator.

#### 3.2 Types of neural networks

There are several neural network architectures, which differ from each other in the learning method used and the specific problem for which they are used. The most important are:

• Feedforward Neural Network: they are the simplest neural networks. The data only propagate in input-output direction. They consist of an input layer and an output layer, and between them they can have, or not have, one or more hidden layers. Every layer have a set of neurons, and their output are the input of the neuron of the next layer. This network can be used for the recognition of shapes or calculation of simple functions.

- Multilayer Perceptron (MLP): it is a type of network that has the input layer, the output layer and one or more hidden layer. Each layer will have a series of neurons, the outputs of which will be connected, as inputs, to all the neurons of the next layer. It can calculate any function and is also widely used in the field of facial recognition.

- Convolutional Neural Network (CNN): this network is a subset of the MLP networks. It is made up of various layers, at least 5, and the outputs of each layer are used as inputs in the next layer, to which the convolutional operations are applied which make the network deeper but with fewer parameters. The fields of application of this network are vast: image or video recognition, natural language processing but they are also applicable in the field of Signal Processing and image classification.

- Recurrent Neural Network(RNN) like Long Short Term Memory: in these networks the output of the upper layers are used as inputs of the lower layers, this to allow the system to create a memory supply so as to better predict the output. In this way, if the output was wrong, the system warns itself of the error so that in back-propagation it corrects it. Used for example in text-to-speech conversion.

- Modular Neural Network: works with different networks each independent of the other therefore they do not interact with each other during the calculation, but each one works alone to arrive at the final output. So being that they work independently the calculation process will be complex but faster being that they don't have to interact with each other.

These are only the main neural networks used in the various fields of applications but they are not all, we can still mention:

- Radial basis function Neural Network, based on the radial basis function.

- Modular Neural Network, in which there are a lot of small NN that cooperate or compete from each other to compute the output.

- Physical Neural Network, in which there are physical electric resistance to simulate artificial synapses.

#### 3.3 Multi-Layer Perceptron neural networks

The NN used in [1] by Marwen is a MLP neural network, that is of the type Feed Forward, made up of at least 3 layers, an input layer that receives external inputs, one or more hidden layers, and an output layer that calculates the final result. Its training is supervised learning so as to find weights and biases in order to minimize the error. In every layers there is a set of neurons, each of them do the multiplications between every inputs and their weights, and then sum all these results with the bias of the corresponding neuron, finally this output go through Activation Function. The two typical activation functions used for this type of network can be sigmoids:

$$y(x_i) = \tanh(x_i) \tag{3.1}$$

and

$$y(x_i) = \left(1 + e^{-x_i}\right)^{-1}$$

(3.2)

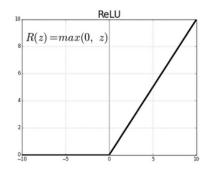

The range of the first is between -1 and 1, while the range of the second is between 0 and 1, but these functions often create numerical problems (Vanishing Gradient Problem [44]) so are replaced by the Rectifier Linear Unit (ReLU) activation function, also call ramp function, and his range, like Figure 3.3, taken from [45], shows, go from 0 to infinity, in particular the output is zero when it is less then zero while is equal to own value when it is equal or greater than zero.

Figure 3.3. ReLU function, taken from [45]. The output will be zero, if the input is less than zero, otherwise it will be equal to the input value if equal or greater than zero.

#### **3.4** Description of the neural network used

In the experiment of Marwen [1], an MLP network is used, which is suitable for this purpose. He uses the experimental data taken from [42], in which the data are taken from four different people at six different frequencies: 5 kHz, 10 kHz, 20 kHz, 40 kHz, 80 kHz, and 160kHz. To optimize and train this NN he used an augmented experimental data because the data available are too few for a good NN training. The flow used for the augmented data, using Matlab R2017a, is that shown in Figure 3.4, taken from [1].

First of all, Gaussian noise has been added, through noise generators, to significantly increase the number of data and avoid overfitting of the specific data sets used for training, but trying to keep the main characteristics of the original set, they are 10000 labeled six-tuples were then generated for each of the four people (40,000 tuples in total). The data are then normalized between 0 and 1 to improve the convergence of NN training. Finally, the data is split into 3 groups: 70% of the tuples (so 28000) are used for the training set (so they are used to fit the model), 15% (so 6000) for the validation (to give a partial evaluation of the model adapted to the training set during the optimization for the model parameters) and optimization and 15% (so 6000) for the test of NN performance.

Figure 3.4. Flow of data augmentation for the training, validation and optimization of a neural network, taken from [1].

After that the author decided how many hidden layers, how many neurons per layer and which activation function to use. For the latter, the sigmoid functions (LogSig) were used at the beginning, but given the excessive use of resources of these activation functions [42], they have been replaced by ReLU, for all the layers apart from the output layer in which it is used a linear identity activation. For the optimal number of hidden layers a search was made by narrowing the field down to neural networks with the same number of neurons per layer. The architecture with 2 hidden layers each of eight neurons was chosen, because the accuracy would have changed little if multiple hidden layers had been used (Table 3 of [42]). An image of the NN used is Figure 3.5, taken from [1]. Note that the first hidden layer will have only 6 multiplication for each neuron because the inputs are six, while in the second there will be eight multiplications per neuron.

Figure 3.5. Multi-layer perceptron neural network with two hidden layer made of eight neurons and one output layer with one neuron, taken from [1].

Below, Algorithm 1 is a pseudocode of the MLP NN, taken from [1]. The first two for the loops constitute the first hidden layer: the first loop goes from 0 to the number of neurons of the first hidden layer, in this case eight, the second loop instead goes from 0 to the number of inputs, in this case six. Inside this last loop the various results of the neuron multiply and accumulate, once the loop is released the bias of that neuron is added to the final result and then the activation function is applied to it. After that each time the final output of the neuron is calculated, the accumulation variable is reset. The second hidden layer is implemented with the same structure but the second for now goes from 0 to all the outputs of the first hidden layer, so in this case eight. The last layer, Output layer, is implemented only with a for loop, which goes from 0 to all the outputs of the second hidden layer, then all the multiplications are performed and the results are accumulated, and finally the bias is added to it and we obtain the person's ID.

#### Algorithm 1 Neural network MLP pseudocode, taken from [1]

```

1: First hidden layer

2: for i = All neurons on first hidden layer do

for j = All inputs do

3:

Product \leftarrow input\_data[j] \times weights\_0[i][j]

4:

Sum \leftarrow Sum + Product

5:

end for

6:

Hidden\_L0[i]Sum \leftarrow b0[i]

7:

if Hidden_L0 [i] < 0 then

8:

Hidden\_L0[i] \leftarrow 0

9:

10:

end if

Sum \leftarrow 0

11:

12: end for

13: Second hidden layer

14: for i = All neurons on second hidden layer do

15:

for j = All outputs of first hidden layer do

Product \leftarrow Hidden\_L0[j] \times weights\_1[i][j]

16:

Sum \leftarrow Sum + Product

17:

end for

18:

Hidden\_L1[i]Sum \leftarrow b1[i]

19:

if Hidden\_L1 \ [i] < 0 then

20:

21:

Hidden\_L1[i] \leftarrow 0

end if

22:

23:

Sum \leftarrow 0

24: end for

25: Output layer

26: for i = All neurons on second hidden layer do

Product \leftarrow Hidden\_L1[j] \times weights\_2[i]

27:

Sum \leftarrow Sum + Product

28:

29: end for

30: Person ID \leftarrow sum + b2

```

# Chapter 4 Very low power FPGA

In this experiment neural networks are implemented on MCUs or on ultralow-power FPGAs. The performances achieved by the latter are better than those of the MCUs. The ways in which they can be programmed are either manually (therefore writing the VHDL or Verilog code by hand) or through high level synthesis using a special tool which, starting from the code written in C or C++, creates the HDL code.

#### 4.1 FPGAs types and performances compared

The use of neural networks, in recent years, has intensified a lot, this because they are applicable to a large number of fields, also obtaining excellent results. Their problem, however, is that more accuracy is desired, more complicated will be the NN and therefore they are really difficult to integrate into an embedded system such as a smart-phone or a robots, this is because their consumption of resources is very heavy. So, to overcome this problem, the neural network used for locating people indoors through the use of capacitive sensors, can be implemented via software, using powerful CPU or GPUs, or via hardware, using FPGAs as HW accelerators, which bring benefits both from the point of view of validity, of power [46] but also from the point of view of accuracy and resources used [47].

The families of FPGAs used by Marwen in the experiment [1], are of the ultralowpower type, therefore that from the point of view of power (both static and dynamic) they consume very little. In particular, two families of FPGAs were chosen, Lattice iCE40 family and Microsemi IGLOO family, of which respectively were chosen:

- ICE40UP5K for Lattice.

- IGLOO AGLN250, IGLOO M1AGL600 and IGLOO M1AGL1000 for Microsemi.

#### 4.1.1 Lattice FPGA features

The Lattice ICE40 UltraPlus FPGA is used in smart-homes, factories and cities. It allows to have a low power of computing resources by also implementing complicated systems such as neural networks, in fact it is manufactured using a CMOS low power process. It has:

- 5280 Look-Up Table (LUTs), or structures data/tables used to replace a complex calculation with a consultation of this table, thus speeding up the operation.

- DSP blocks, in particular it has 8 blocks, and they are blocks capable of doing specific operations such as accumulation, multiplication, multiplication or accumulation (MAC) without going to use LUTs. It could be used as a 16x16 multiplier and as a 32 bit accumulator, therefore as a MAC block.

- 1024 Kbits Single Port Random Access Memory (SPRAM).

- Standby current is typically less than 100 uA.

#### 4.1.2 Microsemi FPGAs features

From the Microsemi family, 3 ultralow-power FPGA IGLOOs were chosen, created by a 130-nm flash process. IGLOO devices use a Flash\*Freeze technology that allows to enter and exit the ultralow-power mode which consumes less than 5 uW keeping system memory data and data registers. The three FPGAs used are:

- AGLN250: it is the smallest FPGA on which the experiment was made, in fact it has only 6144 VersaTiles (which are the equivalent of the LUTs for Lattice). It has no dedicated DSP blocks, it has 36 blocks of RAM 1024 Kbits. It has the lowest static power of all FPGA used in this experiment, 0.08 mW.

- M1AGL600: it has 13824 VersaTiles, has no dedicated DSPs and static power is 0.13 mW, also has 108 blocks RAM 1024 Kbits.

- M1AGL1000: it is the largest Microsemi FPGA has 24576 VersaTiles, has no dedicated DSPs and static power is 0.21 mW, also has 144 blocks RAM 1024 Kbits.

The Table 4.1 summarizes the characteristics just mentioned. Note that the static power information is taken from [1].

#### 4.1.3 Other low power FPGAs

The choice to use the ultralow-power FPGAs of the Lattice and Microsemi family falls on the fact that they have a much lower static power than other FPGAs.

| Table 4.1.  | Description of features (LUTs, DSPs, Pstatic and Ram) of the FPGAs |

|-------------|--------------------------------------------------------------------|

| used in the | e reference programming, taken from $[1]$ .                        |

| FPGA's Family         | Device    | LUTs  | $\mathbf{DSPs}$ | Pstatic  | Ram       |

|-----------------------|-----------|-------|-----------------|----------|-----------|

| LATTICE ICE ULTRAPLUS | ICE40UP5K | 5280  | 8               | 0.28  mW | 4 Kbits   |

| Microsemi IGLOO       | AGLN250   | 6144  | N/A             | 0.08  mW | 36 Kbits  |

| Microsemi IGLOO       | M1AGL600  | 13824 | N/A             | 0.13  mW | 108 Kbits |

| Microsemi IGLOO       | M1AGL1000 | 24579 | N/A             | 0.21  mW | 144 Kbits |

In fact, FPGAs from the Xilinx or Altera family could also have been used, in particular the first would have been excellent since the code generated by Vivado HLS is suitable for the FPGAs of this family. The problem is that comparing the power consumption of the latter devices, it is not comparable to that of the Lattice and Microsemi FPGAs, being they only low-power and not ultra-low-power. In particular, the FPGAs of the Xilinx and Altera family that could be used are those shown in the Table 4.2, in fact, it can be noticed that even if there are many LUTs and also DSPs are many and therefore they could be used for specific operations, the static power at least an order of magnitude greater than the ultralow-power FPGA.

Table 4.2. Description of the features (LUTs, DSPs and Pstatic) of other low power FPGAs not ultralow-power, taken from [1].

| FPGA's Family     | Device   | LUTs   | DSPs | Pstatic |

|-------------------|----------|--------|------|---------|

| XILINX SPARTAN 3  | XC3S200  | 4320   | 12   | 41 mW   |

| Xilinx Spartan 3  | XC3S200A | 4032   | 16   | 43  mW  |

| XILINX ARTIX 7    | XC7A100T | 162240 | 240  | 41  mW  |

| Altera Cyclone II | EP2C8    | 8256   | 18   | 40  mW  |

## 4.1.4 Microcontrollers

In addition to FPGAs, to implement the neural network, is possible use the software approach, i.e. implementation on a CPU or GPU. Unlike FPGAs, CPUs are suitable for running code sequentially and not with parallel implementation. The hardware architecture of a CPU is defined by the programmer, therefore it is not modifiable. In addition, the neural network or the system to be implemented will be in C/C++ while in the FPGA in Verilog or VHDL.

The neural network, show in Figure 3.5 was done on two ARM Cortex M3 MCUs [1] :

- STM32L152RE: that is optimize for ultralow-power, the field of the applications is various: medical, gaming, PC pheripheral, GPS and sport equipment etc, alarm systems, wired and wireless sensor.

- STM32F103RB: that is optimize to reach good performance, typical applications are motor drives and application control, medical, industrial application, printers and scanners, alarm systems, video intercom.

These MCUs include HW multipliers, and thanks to the way in which they were created there is the possibility to measure the current consumption during the execution of the program. The results find in [1], are show in Table 4.3

| MCU Parameter             | MCU device              |           |           |  |  |  |

|---------------------------|-------------------------|-----------|-----------|--|--|--|

| WICO Farameter            | STM32L152RE/STM32F103RB |           |           |  |  |  |

| Clock frequency           | 8/8                     | 16/16     | 32/64     |  |  |  |

| (MHz)                     | 0/0                     | 10/10     | 52/04     |  |  |  |

| FLASH latency             | 0/0                     | 0/0       | 1/2       |  |  |  |

| (wait states)             | 0/0                     | 0/0       |           |  |  |  |

| Clock cycles for          | 1474/1474               | 1474/1474 | 1740/1831 |  |  |  |

| NN inference              |                         | 14/4/14/4 | 1740/1031 |  |  |  |

| NN inference              | 184/184                 | 92.1/92.1 | 54.4/28.6 |  |  |  |

| time ( $\mu$ s)           | 104/104                 | 92.1/92.1 | 54.4/20.0 |  |  |  |

| Current(mA)               | 1.85/4.00               | 3.60/6.80 | 8.60/23.9 |  |  |  |

| Voltage (V)               | 3.0/3.3                 | 3.0/3.3   | 3.3/3.3   |  |  |  |

| Power (mW)                | 5.55/13.2               | 10.8/22.4 | 28.4/78.9 |  |  |  |

| Energy $(\mu \mathbf{J})$ | 1.02/2.43               | 0.99/2.06 | 1.54/2.26 |  |  |  |

Table 4.3. Comparison between the results obtained by manual programming implementing the neural network on the two MCUs under different operating conditions, taken from [1].

For STM32L152RE the best results from the point of view of energy are at 16 MHz, for the power instead it is at 8 MHz (5.55 mW), with a low energy however. Instead from the point of view of time, the best result is found with a clock of 32 MHZ, and the result found is about half the time that it is at 16 MHz, this is because the frequency in the second case is higher and therefore the time taken is less but the energy and power increase. The clock cycles for 8 MHz and 16 MHz are the same, while for 32 MHz they increase (from 1474 to 1740) due to the latency of the FLASH which is higher.

For STM32F103RB the best results from the point of view of energy are found at 64 MHz, however there is an increase in power due to the high operating frequency, while for 8 MHz there is still a low energy (only 0.17 uJ more than the previous case), but the power, being the lowest frequency, is much lower (13.2 mW).

## 4.2 FPGA programming mode

In order to implement a circuit on an FPGA, it must be programmed. There are two main programming modes:

- By schematic: that is, the user manually inserts every single block that forms the project.

- Through hardware description language (HDL): that is, the programmer describes the behavior of the project in Verilog or VHDL.

The first method prefers the speed and simplicity of development as well as facilitating the visualization of the design of the project, on the other hand, however, it can only be used for simple schemes. Describing the hardware to be implemented with the second method leads to flexibility and maintainability of the project, also large and complex designs can also be managed. The most used HDL languages are VHDL and Verilog.

Regarding the latter programming method, the VHDL or Verilog files, which describe the project, can be created starting from the high level description in C or C++ language, after which, using a tool, Vivado HLS, the high level code is synthesized to create the HDL file to be implemented on FPGA, in doing so the designer describes the design at a higher level of abstraction, leaving the synthesis tool to create the HDL files.

## 4.2.1 Manual programming

With manual programming, the programmer must describe the project hardware by using the block diagram, or by writing the VHDL or Verilog code. In both cases, the programmer has absolute freedom on the HW choices that can be made, and has complete control over the components that will then be used in the project. As for programming through the use of blocks, it can be done on relatively simple projects, because if the project becomes too complex, the various connections between the blocks would not be simple, so the creation of the project would become slow. If, on the other hand, HDL languages are used to describe the project, the programmer can better describe the HW, without wasting too much time in creating and connecting the various blocks because the synthesizer will take care of these operations. The disadvantage of the latter method is that it is not a programming language but a HW description language, so if there is a program to synthesize in which there are IF, FOR, WHILE, etc. constructs it can be done but the programming is more complicated, so it would take time to create the project.

In both cases, however, any design can be described to be implemented on FPGA, the time it takes to write the program depends on the complexity, and the optimization of the code, must be done always by hand. However, the programmer have full control over the creation of the project, so if there is a need to look

for an error during the simulation phase, it would be easily traceable because the programmer in theory knows all the signals, which is not the case using the HLS technique, in which the components of the synthesized HDL code will have different names and there is no control over the hardware it will insert.

## 4.2.2 High level synthesis

High level synthesis interprets the high level description of a given algorithm, and transforms it into the equivalent algorithm but described in a hardware description language. This is an automated process, and the goal of the HLS is to allow the hardware designer to create a project efficiently, making available optimizations to improve it, give the possibility to verify the actual operation and accelerate the generation of the HDL.

The advantages of adopting this type of programming are:

- Increase in performance.

- Reduction of power consumption.

- Improve the level of abstraction of the algorithm by being written in C/C++.

- Reduces the time, compared to HDL, to write complex algorithms (such as digital signal processing (DSP)).

But there are also disadvantages:

- The generated HDL code is poorly readable.

- Loose control of the described hardware architecture.

Then, starting from the C/C++ code written by the programmer, HLS extracts a Finite State Machine (FSM), after which it identifies the operations and they will be mapped in each state, then the operations are scheduled by mapping them in the various clock cycles and finally assign operations to available functional units.

## 4.2.3 Optimizations

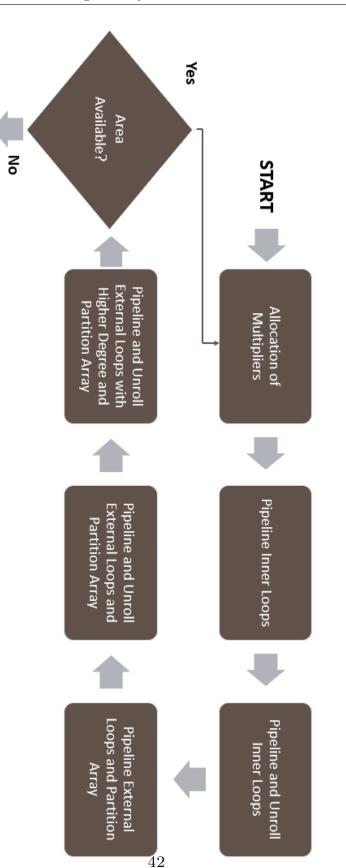

The tool used for high level synthesis is Vivado HLS, and it is a tool used to create HLD code suitable for the FPGAs of the Xilinx family. Directives can be applied to the code written in C, that is optimizations to make the code more efficient so that it can add the set objectives. There are two ways in which these directives can be applied:

• Directive file: Vivado HLS inserts all the directives adopted in a .tcl called directive.tcl, this way is useful when the goal is to to see different optimizations on the same code so as to explore the design.

• Source File: in this case the directives are applied directly to the source code as a pragma.

The main optimizations that can be made are those to improve:

- Throughput: directives such as PIPELINE or UNROLL can be applied both to loops and to functions of the C code, so as to increase parallelism, while paying attention to problems related to data dependency. Together with the aforementioned directives, the ARRAY\_PARTITION directive is also usually used to partition a given array, since it is implemented as a RAM block with a maximum of two data ports, so as to access it with a greater parallelism. Another useful directive is DATAFLOW, used to parallelize operations when there are a set of sequential tasks in the code.

- Latency: the LATENCY directive can be used to limit a certain loop to a certain number of clock cycles.

- Area: directives such as INLINE improve the occupied area because when a function is inlining the components inside it are better shared or optimized with the logic of the calling function, also the ARRAY\_MAP directive is used to improve the area, with it in fact joining small arrays mapping them into a single larger array to reduce the number of RAM blocks. Directives such as ALLOCATION or RESOURCE instead allow to better control the hardware used.