## **Youssef BENDOU**

## MNIS master 2020

## Mercury Mission Systems International, Lancy, Geneva

## FPGA Dynamic Function eXchange

from 02/03/2020 to 28/08/2020

Confidentiality : no

## Under the supervision of:

- Christian RUPPERT, christian.ruppert@ch.mrcy.com

Present at the defense : yes

- Lorena ANGHEL, lorena.anghel@grenoble-inp.fr

Ecole nationale supérieure de physique, électronique, matériaux

#### Phelma

Bât. Grenoble INP - Minatec 3 Parvis Louis Néel - CS 50257 F-38016 Grenoble Cedex 01

Tél +33 (0)4 56 52 91 00 Fax +33 (0)4 56 52 91 03

http://phelma.grenoble-inp.fr

## Acknowledgement

I would like to express my special thanks and gratitude to some people who, by their experience and guidance, made my internship a great learning experience in my journey to become an engineer:

- Mr Christian Ruppert, Manager at MMSI, my tutor, for his very valuable help and guidance through this project.

- Mr Pierrick Hascoet, Software engineer at MMSI, for his help with the software part of this project.

- Mrs Winnie Wong, FPGA project manager at MMSI, for her valuable advice on how to approach my work.

- Special thanks also to the rest of the FPGA team and the MMSI employees who could always make time to answer my questions and show me the way when needed.

## Table of Contents

| ACKNO   | WLEDGEMENT                                 |    |

|---------|--------------------------------------------|----|

| TABLE C | OF CONTENTS                                | 2  |

| FIGURE  | S                                          |    |

| TABLES  |                                            | 5  |

| GLOSSA  | ARY                                        | 6  |

| ABSTRA  | ACT                                        | 7  |

| 1.1.    | English                                    | 7  |

| 1.2.    | FRENCH                                     |    |

| 1.3.    | ITALIAN                                    | 7  |

| INTROD  | DUCTION                                    |    |

| 2. MI   | ERCURY MISSION SYSTEMS INTERNATIONAL[MMSI] | 9  |

| 2.1.    | Facts at a Glance                          | 9  |

| 2.2.    | Markets                                    | 9  |

| 3. FP   | GA DYNAMIC FUNCTION EXCHANGE               |    |

| 3.1.    | FPGA REPROGRAMMING                         |    |

| 3.2.    | DYNAMIC FUNCTION EXCHANGE (DFX)            |    |

| 3.3.    | Applications                               | 11 |

| 4. DF   | X EXAMPLE DESIGN                           |    |

| 4.1.    | Environment                                |    |

| 4.2.    | CLOCK DISTRIBUTION                         | 14 |

| 4.3.    | RESET DISTRIBUTION                         | 14 |

| 4.4.    | DFX CONTROLLER IP                          | 15 |

| 4.4     | 4.1. Role                                  |    |

| 4.4     | 4.2. Interface signals                     |    |

| 4.4     | 4.1. Detailed description                  |    |

| 4.5.    | SEM CONTROLLER IP                          |    |

| 4.5     | 5.1. Role                                  |    |

| 4.5     | 5.2. Interface signals                     |    |

| 4.5     | 5.3. Detailed description                  | 20 |

| 4.6.    | AXI BRIDGE FOR PCIE IP                     | 22 |

| 4.6     | 5.1. Role                                  | 22 |

| 4.6     | 6.2. Interface signals                     | 22 |

| 4.6     | 5.3. Detailed description                  | 23 |

| 4.7.    | AXI INTERCONNECT IP                        | 24 |

| 4.7     | 7.1. Role                                  | 24 |

| 4.7     | 7.2. Interface signals                     |    |

| 4.7     | 7.3. Detailed description                  | 25 |

| 4.8.    | BUS INTERFACE                              | 26 |

| 4.8     | 8.1. Role                                  |    |

| 4.8     | 8.2. Interface signals                     |    |

| 4.8     | 8.3. Detailed description                  | 27 |

| 4.9.    | Arbiter                                    |    |

| 4.9     | 9.1. Role                                  |    |

| 4.9.2.     | Detailed description                        | 32 |

|------------|---------------------------------------------|----|

| 4.10. Re   | CONFIGURABLE MODULE COUNTER                 | 33 |

| 4.10.1.    | Role                                        | 33 |

| 4.10.2.    | Interface signals                           | 33 |

| 4.10.3.    | Detailed description                        | 33 |

| 4.11. AX   | (I TO APB BRIDGE IP                         | 34 |

| 4.11.1.    | Role                                        | 34 |

| 4.11.2.    | Interface signals                           | 34 |

| 4.11.3.    | Detailed description                        | 34 |

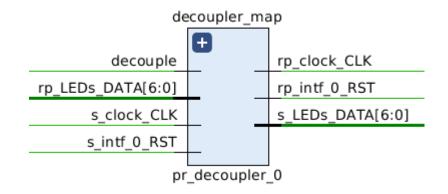

| 4.12. DE   | COUPLER IP                                  | 35 |

| 4.12.1.    | Role                                        | 35 |

| 4.12.2.    | Interface signals                           | 35 |

| 5. DFX FLC | OW                                          | 36 |

|            | FFERENCES FROM A CLASSICAL FLOW             |    |

| 5.2. DF    | FX FLOW[DFXT]                               | 36 |

| 6. MIGRA   | TION FROM ULTRASCALE TO ULTRASCALE+         | 45 |

| 6.1. SE    | M CONTROLLER CHANGES                        | 45 |

| 6.2. DF    | X CONTROLLER CHANGES                        | 45 |

| 6.3. Co    | DNSTRAINTS FILE                             | 45 |

| CONCLUSIO  | Ν                                           | 46 |

| ANNEX      |                                             | 47 |

|            | inex 1. C++ software to launch a DFX design |    |

| 6.2. AN    | INEX 2. TCL SCRIPT TO LAUNCH THE DFX FLOW   | 59 |

| REFERENCES | S                                           | 69 |

# Figures

| FIGURE 1. XILINX KINTEX ULTRASCALE FPGA                                                  | 8  |

|------------------------------------------------------------------------------------------|----|

| FIGURE 2. DYNAMIC FUNCTION EXCHANGE PRINCIPLE [DFXUG]                                    |    |

| FIGURE 3. NETWORKED MULTIPORT INTERFACE WITHOUT AND WITH PARTIAL RECONFIGURATION [DFXUG] |    |

| FIGURE 4. PACKET PROCESSOR [DFXUG]                                                       |    |

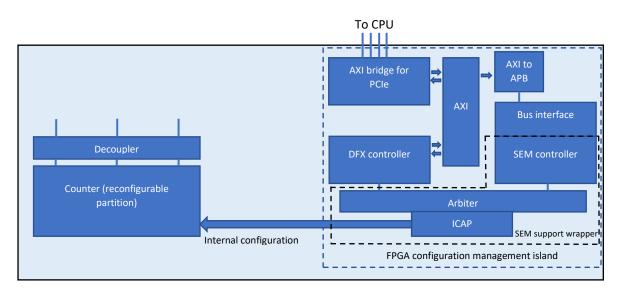

| FIGURE 5. DFX DESIGN BLOCK DIAGRAM                                                       | 13 |

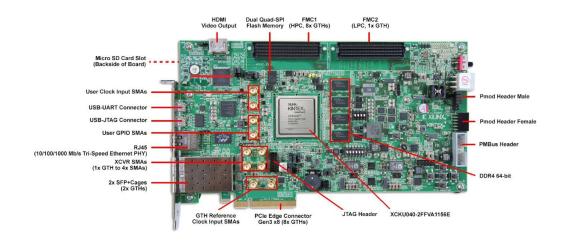

| FIGURE 6. KCU105 BOARD [KCU105EK]                                                        | 14 |

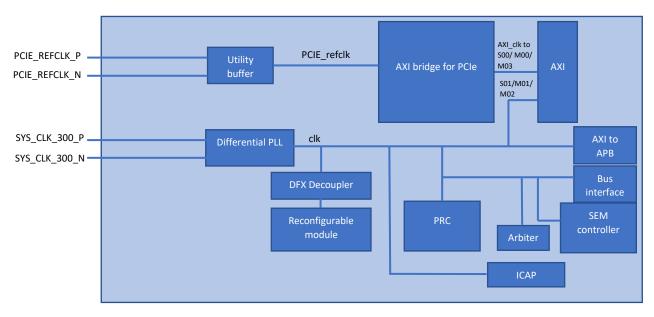

| FIGURE 7. CLOCK DISTRIBUTION DIAGRAM                                                     | 14 |

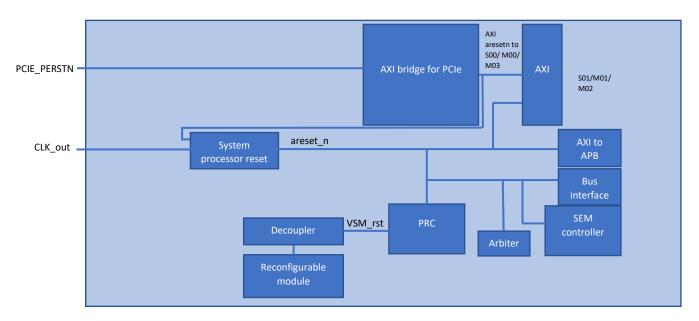

| FIGURE 8. RESET DISTRIBUTION DIAGRAM                                                     | 15 |

| FIGURE 9. DFX CONTROLLER SIGNALS[DFXCPG]                                                 |    |

| FIGURE 10. DFX CONTROLLER IP CONFIGURATION [DFXCPG]                                      |    |

| FIGURE 11. SEM CONTROLLER INTERFACE SIGNALS DIAGRAM[SEMCPG]                              |    |

| FIGURE 12. CONFIGURATION OF THE SEM IP[SEMCPG]                                           | 21 |

| FIGURE 13. AXI BRIDGE FOR PCIE SIGNALS[AXIPCIPG]                                         |    |

| FIGURE 14. AXI BRIDGE FOR PCIE CONFIGURATION [AXIPCIPG]                                  | 23 |

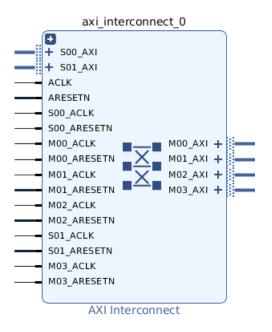

| FIGURE 15. AXI INTERCONNECT SIGNALS[AXIPG]                                               | 24 |

| FIGURE 16. SLAVE AND MASTER INTERFACES CONNECTIONS TO DIFFERENT FPGA BLOCKS              | 25 |

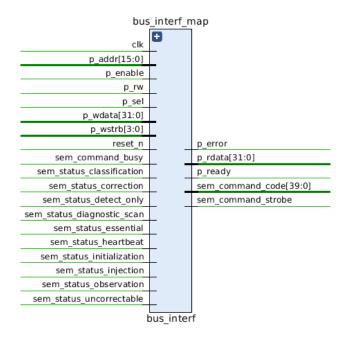

| FIGURE 17. BUS INTERFACE SIGNALS                                                         |    |

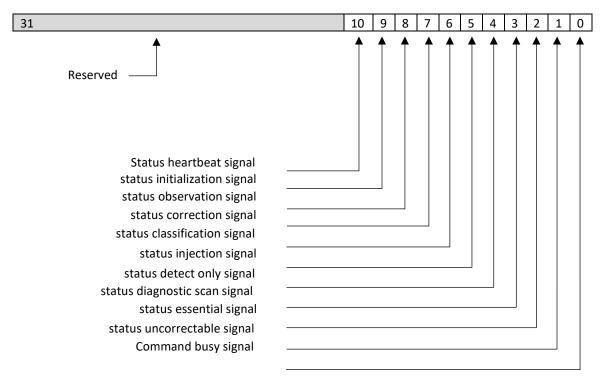

| FIGURE 18. STATUS REGISTER BIT BY BIT                                                    |    |

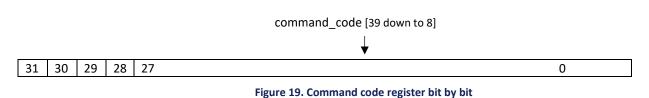

| FIGURE 19. COMMAND CODE REGISTER BIT BY BIT                                              | 29 |

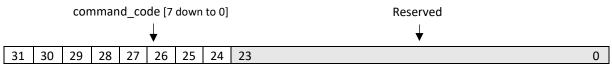

| FIGURE 20. COMPLEMENTARY COMMAND CODE REGISTER                                           |    |

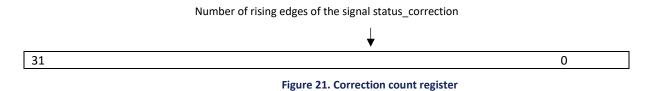

| FIGURE 21. CORRECTION COUNT REGISTER                                                     |    |

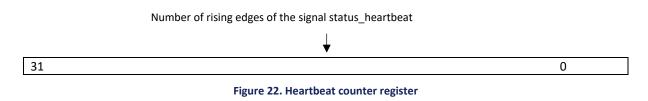

| FIGURE 22. HEARTBEAT COUNTER REGISTER                                                    |    |

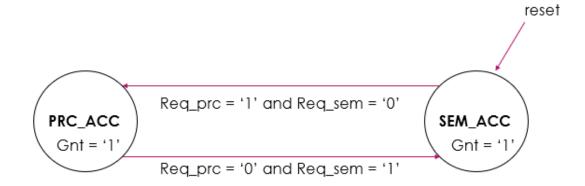

| FIGURE 23. FINITE STATE MACHINE OF THE ARBITER                                           |    |

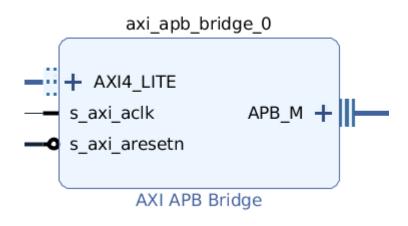

| FIGURE 24. AXI TO APB BRIDGE SIGNALS[AXIAPBPG]                                           |    |

| FIGURE 25. DECOUPLER IP SIGNALS[DFXDPG]                                                  | 35 |

| FIGURE 26. PBLOCK POSITION IN THE IMPLEMENTED DEVICE                                     |    |

# Tables

| TABLE 1. DFX CONTROLLER INPUT/OUTPUT PORTS [DFXCPG]                    | 16 |

|------------------------------------------------------------------------|----|

| TABLE 2. INTERFACE SIGNALS OF THE SEM CONTROLLER[SEMCPG]               | 19 |

| TABLE 3. AXI BRIDGE FOR PCIE INPUT/OUTPUT PORTS DESCRIPTION [AXIPCIPG] | 22 |

| TABLE 4 – AXI INTERCONNECT INPUT/OUTPUT PORTS DESCRIPTION [AXIPG]      | 24 |

| TABLE 5 – BUS INTERFACE INPUT/OUTPUT PORTS DESCRIPTION                 |    |

| TABLE 6. LIST OF THE REGISTERS                                         | 27 |

| TABLE 7. LIST OF THE BITS FOR THE STATUS REGISTER                      | 29 |

| TABLE 8. LIST OF THE BITS FOR THE COMMAND CODE REGISTER                |    |

| TABLE 9. LIST OF THE BITS OF THE COMPLEMENTARY COMMAND CODE REGISTER   |    |

| TABLE 10. LIST OF THE BITS OF THE CORRECTION COUNTER REGISTER          | 31 |

| TABLE 11. LIST OF THE BITS OF THE HEARTBEAT COUNTER REGISTER           | 31 |

| TABLE 12 – COUNTER INPUT/OUTPUT PORTS                                  |    |

| TABLE 13 – AXI TO APB BRIDGE INPUT/OUTPUT PORTS[AXIAPBPG]              |    |

| TABLE 14 – ARBITER INPUT/OUTPUT PORTS[DFXDPG]                          |    |

|                                                                        |    |

# Glossary

| AXI  | Advanced eXtensible Interface                                    |

|------|------------------------------------------------------------------|

| CPU  | Central Processing Unit                                          |

| ECC  | Error Correcting Code                                            |

| FPGA | Field Programmable Gate Array                                    |

| DFX  | Dynamic Function eXchange                                        |

| ID   | Identifier                                                       |

| MMSI | Mercury Mission System Intl                                      |

| PCle | Peripheral Component Interconnect Express                        |

| PLL  | Phase Locked Loop                                                |

| VHDL | Very High Speed Integrated Circuit Hardware Description Language |

| PRC  | Partial Reconfiguration Controller                               |

| SEM  | Single Error Mitigation                                          |

| APB  | Advanced Peripheral Bus                                          |

| ICAP | Internal Configuration Access Port                               |

| DRC  | Design Rule Checks                                               |

| 000  | Out of Context                                                   |

| SSI  | Stacked Silicon Interconnect                                     |

| SLR  | Super Logic Region                                               |

| MSB  | Most Significant Bit                                             |

| LSB  | Least significant Bit                                            |

| TCL  | Tool Command Language                                            |

| GUI  | Graphic User Interface                                           |

| RTL  | Register Transfer Level                                          |

| C++  | Programming language                                             |

| ASIC | Application Specific Integrated Circuit                          |

| IP   | Intellectual Property                                            |

| VSM  | Virtual Socket Manager                                           |

| HDL  | Hardware Description Language                                    |

| RP   | Reconfigurable Partition                                         |

| RM   | Reconfigurable Module                                            |

| IEEE | Institute of Electrical and Electronics Engineers                |

|      |                                                                  |

## Abstract

## 1.1. English

FPGAs are electrical circuits that can be reprogrammed in-field to suit the user's needs and implement whatever digital functionality wanted. This programmability feature is however constrained by the fact that the design implemented in it needs to be shutdown each time before. DFX is an upgrade of this feature that enables the user to do it dynamically and on specific partitions of the FPGA. This opens the door to many applications and enables reductions of size and cost to implement a design in an FPGA.

## 1.2. French

Les FPGA sont des circuits électriques qui peuvent être reprogrammés pour répondre aux besoins de l'utilisateur et mettre en œuvre toutes les fonctionnalités numériques souhaitées. Cette fonction de programmabilité est cependant limitée par le fait que le design qui y est implémentée doit être arrêté à chaque fois auparavant. DFX est une mise à niveau de cette fonctionnalité qui permet à l'utilisateur de le faire de manière dynamique et sur des partitions spécifiques du FPGA. Cela permets de nombreuses applications et facilite la réduction de la taille et le coût de mise en œuvre d'une conception dans un FPGA.

## 1.3. Italian

Gli FPGA sono circuiti elettrici che possono essere riprogrammati sul campo per soddisfare le esigenze dell'utente e implementare qualsiasi funzionalità digitale desiderata. Questa caratteristica di programmabilità è tuttavia limitata dal fatto che il progetto in esso implementato deve essere chiuso ogni volta prima. DFX è un aggiornamento di questa funzione che consente all'utente di farlo dinamicamente e su partizioni specifiche dell'FPGA. Questo apre la porta a molte applicazioni e consente riduzioni di dimensioni e costi per implementare un progetto in un FPGA.

## Introduction

FPGA is an acronym for Field Programmable Gate Array and it is a device that contains a significant number of transistors and other electrical components in a way that it can be programmed to implement whatever digital functionality is needed by the user. This reprogramming feature makes these FPGA devices very appealing but the constraint is that every time the circuit needs to be reprogrammed, the whole design implemented in it has to be shut down and reset to implement the new functionality. The goal of this internship project is to examine the possibility of doing this in a partial and dynamic way, which means reprogramming only some partitions of the FPGA on the fly without disturbing the other partitions in their jobs.

Figure 1. Xilinx Kintex UltraScale FPGA

Mercury Mission Systems International is a company involved in the market of defense and aerospace electronics. I was placed as an intern in the FPGA team, which is a team whose mission is to deal with the design aspect of projects. During this time, I had the chance to work on a complete design by myself from writing RTL code to bitstream generation for the programming of the FPGA and verifying the feasibility of this dynamic partial reconfiguration feature. I also did some software programming using the C++ programming language. Spending 6 months within this team has given me the chance to work under the supervision of experienced designers and managers, it was a great opportunity to learn and to get a grasp of a design engineer's work environment.

This report contains a first section about the company MMSI and its industrial context, then three sections about my work within the company to furthermore describe the assignments I had and the results I achieved.

The goal of this internship project was to make a DFX example design with a single event error mitigation feature from scratch, generate corresponding files that will serve to program the FPGA with the design wanted. Make a small C++ software that will program a CPU to do some read and write commands that will control the different blocks in the FPGA to perform a DFX operation. The aim of all of this is to prove DFX technology's feasibility to a client of Mercury Systems. I also had to write some documentation for the client to explain my work.

## 2. Mercury Mission Systems International [MMSI]

Mercury Mission Systems International (MMSI) is based in Geneva, Switzerland, and is specialized in the design, manufacturing and maintenance follow-up of computers, more specifically complex safety avionics and defense computers. It is part of Mercury Systems, an American leading commercial provider of secure sensors and mission processing subsystems.

## 2.1. Facts at a Glance

- Mercury Systems was founded in 1981.

- Mercury's solutions power a wide variety of critical defense and intelligence programs

- Mercury Systems is based in Andover, Massachusetts

- Mercury Mission Systems International is based in Geneva, Switzerland

- It counts approximately 1900 employees worldwide

- Fiscal year 2020 revenue: \$796.6M

## 2.2. Markets

Defense and commercial electronics:

- Radars

- Electronic warfare and signal intelligence

- Command, Control, Communications, Computers, Intelligence, Surveillance, Reconnaissance(C4ISR)

- Sonar

- Missiles and munitions

- Mission computing & avionics

## 3. FPGA Dynamic Function eXchange

FPGAs provide the ability to program and reprogram a circuit in-field to suit the user's needs. Dynamic function exchange takes this feature one step further, by enabling the user to do it partially if needed, and on the fly.

## 3.1. FPGA reprogramming

Field Programmable Gate Arrays contain a huge number of electrical components and routing resources that enables it to have this reprogrammable feature. To reprogram it, the most important thing is a file, called the bit file or bitstream, which contains a series of 0 and 1 binary elements that, once sent to the internal configuration memory of the FPGA, will set the functionality of the different blocks inside.

To generate this bit file, there is a whole flow to follow:

## • RTL writing

This is done using hardware description languages (HDL), which are coding languages that will serve to describe the functionality of the circuit to be programmed into the FPGA. This internship project was coded using VHDL, a hardware description language standardized by the IEEE.

## • RTL elaboration

Tools exist to do RTL elaboration, which is basically reading and understanding the HDL coding and translating it into a circuit with blocks but with no optimization, just a complete translation of the code into a schematic for the circuit. For this internship project, Vivado Design Suite from Xilinx was used all along for all of the flow.

## • Synthesis

The synthesizer will then use advanced and complex algorithms to optimize the circuit elaborated and look for shortcuts that will simplify the circuit but keep the same functionality. A netlist will be generated which is a list of all the resources and connections needed to implement this design.

## • Implementation

The implementation phase is where the tool will try to virtually place the different blocks of the design in the FPGA and assign which resources of the FPGA and which routing paths will be used to implement the design. There are also some optimization algorithms used in this step. After this, all of the placements and routings needed to make the design work are well known and chosen.

## Bitstream generation

The bitstream generation phase is where the tool will translate the implementation results into the famous file, the bit file, that contains information on which resources will be used and which connection routes will be chosen to implement the design inside the FPGA. This bit file is then loaded in the FPGA to start its job.

## **3.2.** Dynamic Function eXchange (DFX)

DFX is the ability to reprogram partitions of an FPGA dynamically. After a full bit file configures the FPGA and gets it up and running, partial bit files need to be loaded to change the functionality of specific blocks without compromising other blocks that are outside the scope of this dynamic programmability.

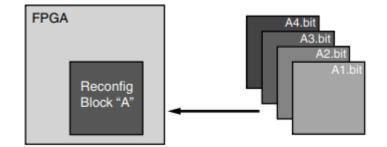

Figure 2. Dynamic function exchange principle [DFXUG]

The gray area represents static logic implemented in the FPGA, and the black area labeled Reconfig Block "A" represents reconfigurable logic that can be replaced with different partial bit files depending on the need. The black area is called a reconfigurable partition (RP), the partial bit files are called reconfigurable modules (RM).

It is a very practical feature since it enables the reduction of the size of an FPGA required to implement a function, leading to consequent reductions in cost and power consumption of a circuit. It enables some flexibility in the choice of algorithms and functions needed and it is also an efficient way to deliver updates to deployed systems.

## 3.3. Applications

## • Networked multiport interface

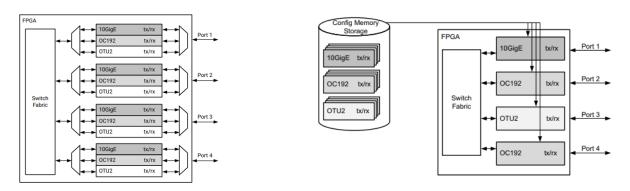

The ports at the client's side of this interface can support many protocols for interfacing but it is impossible to predict which protocol is needed so the designer is forced to have all the possible port interfaces and multiplex the inputs and outputs to be sure that all the possible protocols are treated.

Using DFX technology, port interfaces can be made as reconfigurable modules and interchanged every time depending on the type of protocol used. This is considerably better in terms of size since the designer doesn't need to implement all the different possible port interfaces in the FPGA, and the multiplexing elements would no longer be needed.

Figure 3. Networked multiport interface without and with partial reconfiguration [DFXUG]

## • Dynamically reconfigurable packet processor

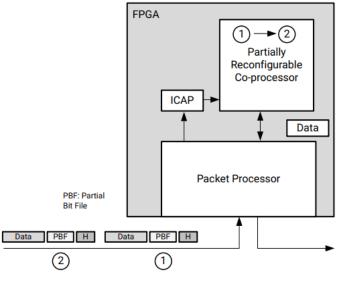

It is possible for a packet processor to change its processing functionalities.

Packets that the packet processor receives have headers, these headers could contain partial bit files that will be used to dynamically reconfigure a co-processor, thus changing the processing functionalities.

Figure 4. Packet processor [DFXUG]

## 4. DFX example design

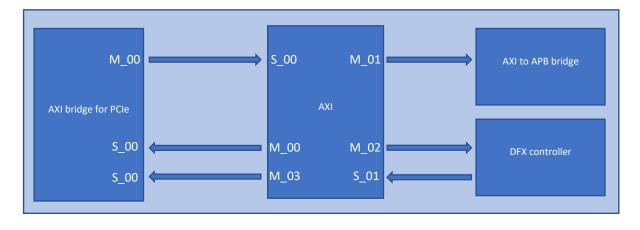

The example design that is targeted will include two controllers that are Xilinx IPs, a controller that manages the dynamic reconfiguration and a controller that is almost constantly scanning the internal configuration of the FPGA to look for errors. Both these controllers are the heart of this design and both of them need access to the internal configuration of the FPGA to do their respective jobs. An internal configuration access port (ICAP) is present in the design for this purpose.

A PCIe connection ensures communication between the controllers and an external CPU. This CPU will be programmed to send read and write requests on some internal registers of the two controllers, through this PCIe connection, to command them into doing the job needed by the user.

The reconfigurable partition is a counter that will be loaded by either a count up or a count down function. The rest of the blocks are a mix of IPs and RTL I coded myself to help the main modules communicate with each other. This includes an AXI interconnect, an AXI to APB bridge, an APB bus interface, an arbiter and a DFX decoupler.

## 4.1. Environment

The work environment is an important part of this design since there are differences that need to be taken into account depending on the type of FPGA used.

The software used for all of the flow is the Vivado Design Suite 2019.1 from Xilinx. It is a software that includes all necessary tools to make an FPGA design from RTL writing to bitstream uploading.

The FPGA used is a Kintex UltraScale FPGA, a Xilinx product that comes with the board KCU105.

## 4.2. Clock distribution

Two external clocks are used for this design, the first one is a 100 MHz PCIe differential reference clock that is exclusively generated on the KCU105 board by the PCIe edge connector for the PCIe connection in the FPGA, and the second one is a 300 MHz system clock, also generated on the board, to clock the rest of the design. The AXI\_clk is a clock generated by the AXI bridge for PCIe IP exclusively for AXI interfaces that are connected to it.

## 4.3. Reset distribution

An external reset generated on the board by the PCIe edge connector is used to reset the AXI bridge for PCIe IP. An axi\_aresetn is generated by the same IP to reset the AXI interfaces that are connected to it. The rest of the blocks use a reset that is generated locally in the FPGA.

Figure 8. Reset distribution diagram

## 4.4. DFX controller IP

## 4.4.1. Role

The purpose of this Xilinx IP is to handle DFX operations in the most efficient way. It has a slave interface that is used to access its internal configuration registers, a master interface that is responsible for the fetching of the partial bitstreams from an external CPU memory through the PCIe connection, and an ICAP interface which contains the signals that will help to send the fetched partial bitstreams into the internal configuration of the FPGA to target the reconfigurable partition and change its functionality. It is mainly made of virtual socket managers (VSM), each one of these is managing one reconfigurable partition which can have many reconfigurable modules. In this design there is only one partition and two modules so only one VSM is needed.

## 4.4.2. Interface signals

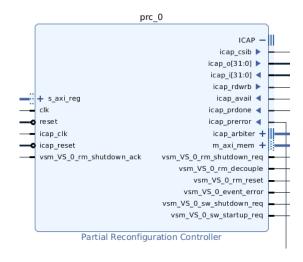

Figure 9. DFX controller signals[DFXCPG]

This table describes the interface signals of this IP. Signals that are present in the diagram but not in the table are not used for this design and can be put to a constant value if it is an input or left open if it is an output.

#### Table 1. DFX controller input/output ports [DFXCPG]

| Port                                                                                                                                         | Direction                                                                                      | Description                                                                                                                                  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| clk                                                                                                                                          | Input                                                                                          | Master clock for the controller.                                                                                                             |  |  |

| icap_clk                                                                                                                                     | Input                                                                                          | Must be the same clock that is attached to the ICAP primitive                                                                                |  |  |

| reset                                                                                                                                        | Input                                                                                          | Reset signal for the controller                                                                                                              |  |  |

| s_axi_regInterfaceAXI slave interface of the controller. This is the interface t<br>the internal configuration registers of this controller. |                                                                                                | AXI slave interface of the controller. This is the interface that permits access to the internal configuration registers of this controller. |  |  |

| icap_reset                                                                                                                                   | Input                                                                                          | Synchronous reset signal used to reset the ICAP interface logic. Needs to be synchronous to icap_clk.                                        |  |  |

| vsm_VS_0_rm_shutdown_ack                                                                                                                     | Input                                                                                          | Handshake signals with the reconfigurable logic                                                                                              |  |  |

| vsm_VS_0_rm_shutdown_req Output                                                                                                              |                                                                                                | Handshake signals with the reconfigurable logic.                                                                                             |  |  |

| ΙCAP                                                                                                                                         | Interface ICAP interface that contains all the signals that need to be control ICAP primitive. |                                                                                                                                              |  |  |

| icap_arbiter Interface Interface Arbiter interface that contains the signals need controller to the ICAP primitive.                          |                                                                                                | Arbiter interface that contains the signals needed to arbitrate the access of this controller to the ICAP primitive.                         |  |  |

| m axi mem                                                                                                                                    |                                                                                                | Master interface that is connected to the slave interface of the PCIe bridge, passing through the AXI interconnect first.                    |  |  |

| vsm_VS_0_rm_decouple                                                                                                                         | Output                                                                                         | Signal asserted by the controller when a decoupling operation is needed prior to executing DFX.                                              |  |  |

| vsm_VS_0_rm_reset                                                                                                                            | Output                                                                                         | Reset signal intended to reset the reconfigurable logic.                                                                                     |  |  |

## 4.4.1. Detailed description

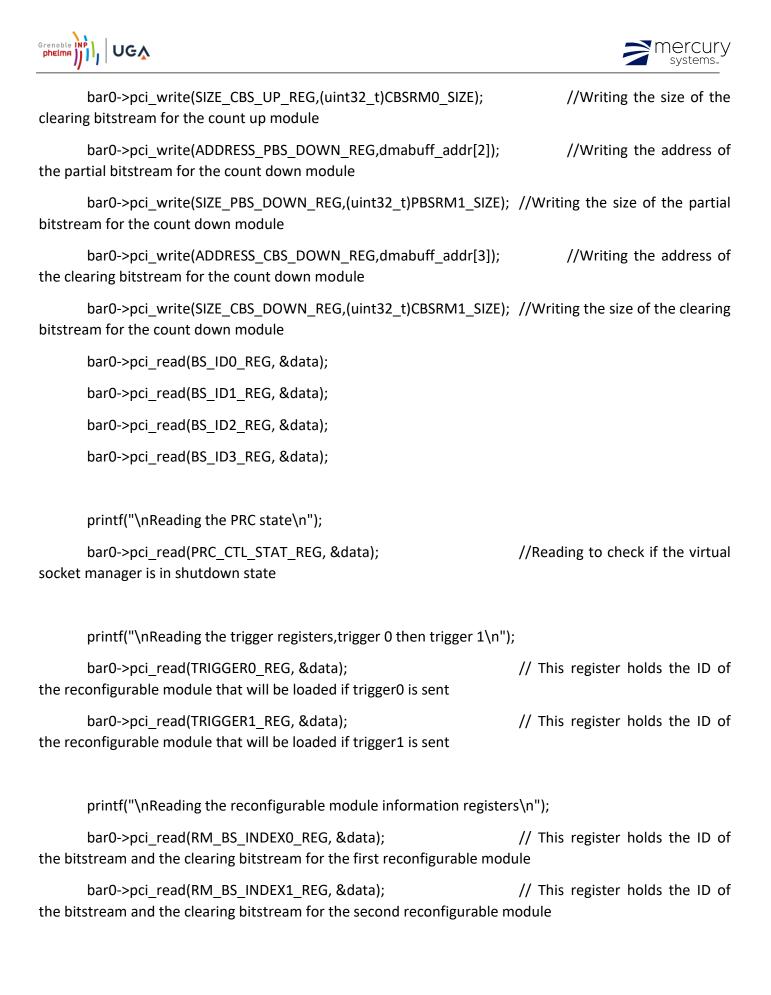

This IP is the core of this design, since it is the one responsible for all DFX operations and their management. The better this controller is configured in a way that is adapted to the design, the better the DFX operations work. Since the controller is charged with replacing partial bit files that are already implemented in the FPGA, with new ones that it has to fetch, it must know the sizes of these partial bit files, and the addresses at which it can fetch them from the CPU external memory.

It has a master interface that is responsible for the fetching operations of the partial bit files, this master interface is connected to a slave interface in the PCIe bridge through the AXI interconnect. It also has a slave interface that enables the access to different control registers and bitstream information registers. These two interfaces are the most important ones for DFX operations.

The IP can be instantiated directly using the Vivado IP catalog and can be configured to function properly:

| Partial Reconfiguration Controller (1.3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                      |                                                                                                                                                                                                                                            | A | Partial Reconfiguration Controller                                  | (1.3)                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Decomentation<br>P Symbol Validation Address Map Tr(+ > 0<br>tree disabled pots<br>- see use very Standards and standard by tree of the set of the | Component Name [pr.g.]  Coubid Options Writing Society Hamager Option Coubid Options Writing Society Hamager Option Coupling And | 8         v           The MC at manage Virtual Solets in an Utratical device         v           10 Latency has not been added to adder signal         v           0 Partial Bitchmann are not compressed         v           22         v |   | ck vsm_VS_0_rm_sh<br>reset vsm_VS_0_rm_sh<br>icap_ck vsm_VS_0_rm_VS | ICAP +<br>p_sthiter +<br>sa_mem +<br>m_decouple =<br>0_m_reset<br>sweet_error<br>widdem_req = | Component Name prc_0<br>Chabad Options Virtual Socket Man-<br>Virtual Socket Manager Options<br>Virtual Socket Manager Options<br>Number of Reis allocated<br>Trigger Options<br>Number of Interdamer Triggers | New Reconfigurable Module | Celete Virtual Socket Hank Reconfigurable Hedule Options Reconfigurable Hedule Options Reconfigurable Hedule Nodule Iso Reconfigurable Hedule Nodule Iso Startup type Reset type Duston of Reset Bacream 0 adress Bacream 0 adress Bacream 1 adress | RM 0<br>RM_0<br>Not Requ<br>Active Lo<br>3<br>0x800000<br>375996<br>am<br>0x85C000<br>26036 |

Figure 10. DFX controller IP configuration[DFXCPG]

This configuration can change depending on the number of reconfigurable partitions and modules wanted. In this design there is only one reconfigurable partition and two reconfigurable modules that can fill this partition, so only one virtual socket manager is needed. If it wasn't the case, one virtual socket manager should be added for each reconfigurable partition using the buttons in the configuration interface. Then reconfigurable modules can be added too.

Each virtual socket manager can be configured and each reconfigurable module too. For each reconfigurable module, the controller needs to know the address and size of the corresponding partial bitstream and clearing bitstream (no clearing bitstream for UltraScale+ devices). All these parameters can nevertheless be modified after the design runs with the help of the slave AXI-Lite interface of this controller, which permits access to the internal configuration registers of the controller, where the user can write new values.

Once all necessary configurations are made, there exists a register that can be written with a certain value to launch a dynamic reconfiguration. This value depends on the number of VSMs and reconfigurable modules present in the design, but each reconfigurable module of each VSM is indexed to a precise value that once written to this register, called the SWTRIGGER register, will launch an instruction for the controller to go through the PCIe connection and fetch the corresponding partial bitstream from the external CPU memory.

## 4.5. SEM controller IP

## 4.5.1. Role

The purpose of this IP is to scan for, detect, and correct errors in the FPGA configuration. To do this, it needs two primitives which are the Frame ECC primitive, that serves for the calculation of some golden error correction code values, and the ICAP primitive, which is the internal configuration access port. This controller is commanded through a command interface, it also has a status interface to keep track of its state at the moment of reading the signals, and some other interfaces that serve for the access to the ICAP or the arbitration of this access if needed.

## 4.5.2. Interface signals

Figure 11. SEM controller interface signals diagram[SEMCPG]

This table describes the interface signals of this IP. Signals that are present in the diagram but not in the table are not used for this design and can be put to a constant value if it is an input or left open if it is an output.

#### Table 2. Interface signals of the SEM controller[SEMCPG]

| Interface                  | Port                   | Dir    | Description                                                                                                                                                                                                           |

|----------------------------|------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master clock interface     | clk                    | Input  | Main clock for the SEM controller.                                                                                                                                                                                    |

| Status interface           | status_heartbeat       | Output | The heartbeat signal is active and toggles every time a frame is read when status_observation, status_detect_only, or status_diagnostic_scan are active.                                                              |

|                            | status_initialization  | Output | This signal is active during controller initialization.                                                                                                                                                               |

|                            | status_observation     | Output | This signal is active during controller observation of bit<br>upsets, it remains active after error detection while the<br>controller queries the hardware for information.                                           |

|                            | status_correction      | Output | This signal is active during controller correction of an error<br>or during a transition through this state if correction is<br>disabled.                                                                             |

|                            | status_classification  | Output | This signal is active during controller classification of an<br>error or during transition through this state if error<br>classification is disabled.                                                                 |

|                            | status_injection       | Output | This signal is active during error injection. When the error is injected it returns inactive.                                                                                                                         |

|                            | status_detect_only     | Output | This signal is active when the controller is in a detect only state. When the scan is interrupted because of an error that was found, it returns inactive                                                             |

|                            | status_diagnostic_scan | Output | This signal is active during controller diagnostic scan of the entire configuration of the FPGA. Once it finishes scanning, the signal returns inactive.                                                              |

|                            | status_uncorrectable   | Output | The controller sets this signal prior to exiting the correction state to reflect the nature of a found error.                                                                                                         |

|                            | status_essential       | Output | This signal is an error classification signal. It is set by the controller prior to exiting the error classification state to reflect whether the error occurred on an essential bit.                                 |

| Command interface          | command_busy           | Output | This signal indicates whether the SEM controller is ready to<br>process a command. command_strobe should only be<br>asserted when command_busy is low.                                                                |

|                            | command_code           | Input  | This signal is used to command the SEM controller. The<br>value on this signal is captured at the same time when<br>command_strobe is sampled active. For UltraScale devices,<br>the width of this signal is 40 bits. |

|                            | command_strobe         | Input  | This signal needs to be pulsed synchronously to the clock<br>when command_busy is low and a valid command_code<br>signal is ready to be presented.                                                                    |

| ICAP arbitration interface | cap_gnt                | Input  | This signal is to be asserted by an arbiter to tell the controller that it can start sending and receiving data from the ICAP.                                                                                        |

|                            | cap_req                | Output | This signal is to be asserted by the controller to request for ICAP access.                                                                                                                                           |

|                            | cap_rel                | Input  | This signal needs to be asserted by an arbiter to tell the controller that some other block is requesting access to the ICAP.                                                                                         |

| ICAP interface             | icap_i                 | Output | Drives the data input of the ICAP.                                                                                                                                                                                    |

|                            | icap_o                 | Input  | Is driven by the data output of the ICAP.                                                                                                                                                                             |

|                     | icap_clk            | Input     | Clock for the ICAP interface.                       |

|---------------------|---------------------|-----------|-----------------------------------------------------|

|                     | icap_csib           | Output    | Drives the CSIB input of the ICAP.                  |

|                     | icap_rdwrb          | Output    | Drives the RDWRB input of the ICAP.                 |

|                     | icap_prdone         | Input     | Is driven by the PRDONE output of the ICAP.         |

|                     | icap_prerror        | Input     | Is driven by the PRERROR output of the ICAP.        |

|                     | icap_avail          | Input     | Is driven by the AVAIL output of the ICAP.          |

| Frame ECC interface | Frame ECC interface | Interface | Interface that connects to the Frame ECC primitive. |

## 4.5.3. Detailed description

This module implements the Xilinx single error mitigation controller. The controller scans the internal configuration of the FPGA looking for errors to report and correct. To do this, it needs access to this internal configuration and this is achieved through the ICAP. There is however an arbiter in the way to the FPGA's internal configuration, because the DFX controller needs access to it too. The SEM controller sends and receives data using 32-bit wide signals in and out. It also has an arbitration interface, a status interface, and a command interface.

The command interface has a command\_code signal that is 40 bits wide, this signal is used to send instructions to the controller depending on the 4 MSBs, the 36 remaining bits are only used when in error injection mode and they serve to describe the error to be injected. However, this functionality is not used in this design as it is outside of the scope of DFX.

- MSBs = 1110: Directed state change to the Idle State.

- MSBs = 1100: Directed state change to the Error Injection State.

- MSBs = 1010: Directed state change to the Observation State.

- MSBs = 1111: Directed state change to the Detect Only State.

- MSBs = 1101: Directed state change to the Diagnostic Scan State.

- MSBs = 1011: Directed state change to do a Software Reset.

The status interface contains a number of signals that can be read to check the status of the controller at that moment and see if it is doing the job it is expected to do.

The SEM controller IP can be instantiated using the Vivado IP catalog and here is the configuration used for this design:

| Documentation 🗇 IP Location 😷 Switch to Defau                                                                  |                                                                                |                              |                         |                            |   |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------|-------------------------|----------------------------|---|

|                                                                                                                | ts                                                                             |                              |                         |                            |   |

| Show disabled ports                                                                                            | Component Name sem_ultra_0                                                     |                              |                         |                            |   |

|                                                                                                                | Basic Advanced Mitigation Summary                                              |                              |                         |                            |   |

|                                                                                                                | General                                                                        |                              |                         |                            |   |

|                                                                                                                | Mode Mitigation only 🗸                                                         |                              |                         |                            |   |

|                                                                                                                | Controller Clock Period (ps) 10000 © (5                                        | 000 - 125000)                |                         |                            |   |

|                                                                                                                |                                                                                |                              |                         |                            |   |

| (                                                                                                              | Structural Options                                                             |                              |                         |                            |   |

| monitor_bfull cap +<br>monitor_rodata[7:0] status_heartbeat                                                    | ICAP and IRAMI_LCC placement _ Lxample Design _ v                              |                              |                         |                            |   |

| <ul> <li>monitor_nempty status_initialization</li> <li>command strobe status observation</li> </ul>            | Mode description                                                               |                              |                         |                            |   |

| command_sorbde status_coservation<br>command_code[39:0] status_correction                                      | Features                                                                       |                              |                         | Modes                      |   |

| <ul> <li>tcap_dk statue_dasafication</li> </ul>                                                                | - I0 state attes initialization                                                | Mitigation + testing<br>OBSV | Mitigation only<br>OBSV | Detect + testing<br>DETECT |   |

| <ul> <li>icap_c(31:0)</li> <li>status_injection</li> <li>clap_prendr</li> <li>status_essential</li> </ul>      | Correction (Repair)                                                            | 1                            | ×                       | NA                         | T |

| <ul> <li>- icsp_prdone</li> <li>- status_uncorrectable</li> </ul>                                              | Classification<br>Error injection                                              | optional<br>V                | optional                | NA.                        | - |

| <ul> <li>icap_aval status_disgnostic_scan</li> </ul>                                                           | <ul> <li>Debugging features:</li> </ul>                                        |                              |                         |                            |   |

| <ul> <li>fect_eccerromoteingle status_detect_only</li> <li>fect_eccerrorsingle monitor_twistel[7:0]</li> </ul> | -Configuration frames and register reads                                       | × 1                          | ~                       | ~                          |   |

| <ul> <li>fect_eccentraingle</li> <li>fect_endofframe</li> <li>monitor_txwrite</li> </ul>                       | -External memory reads (if classification is enabled)<br>-Address translations |                              |                         |                            |   |

| <ul> <li>Foce_endetscan</li> <li>menitor_pread</li> </ul>                                                      | On-demand detect features:                                                     |                              |                         |                            |   |

|                                                                                                                |                                                                                | ×                            | ×                       | · ·                        |   |

| <ul> <li>fec_promor command_busy</li> </ul>                                                                    |                                                                                |                              |                         |                            |   |

| fecc_far(25:0) icap_csib                                                                                       |                                                                                |                              |                         |                            |   |

| fect_far(25:0) idap_calb<br>= aux_entor_or_ne idap_cdwtb                                                       |                                                                                |                              |                         |                            |   |

| fecc_far(25:0) icap_csib                                                                                       | •                                                                              |                              |                         |                            |   |

Grenoble **phelma**

Figure 12. Configuration of the SEM IP[SEMCPG]

The mode has been chosen here to be Mitigation Only because the purpose of this design is to demonstrate Dynamic Function eXchange on an UltraScale device and this feature is totally independent from it, but it can be modified according to the needs of the user using the Vivado interface dedicated for IP configuration.

nercur systems...

## 4.6. AXI bridge for PCIe IP

## 4.6.1. Role

The purpose of this IP is to connect the FPGA to an external CPU using a PCI express connection. This enables the CPU to arrange read and write transactions to be able to control all of the needed operations to run dynamic reconfiguration and manage the error correction operations.

## 4.6.2. Interface signals

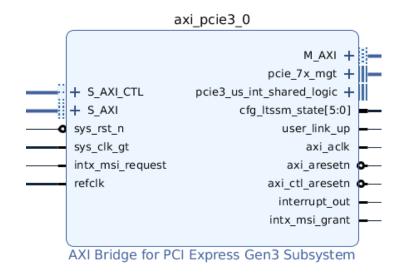

Figure 13. AXI bridge for PCIe signals[AXIPCIPG]

This table describes the interface signals of this IP. Signals that are present in the diagram but not in the table are not used for this design and can be put to a constant value if it is an input or left open if it is an output.

#### Table 3. AXI bridge for PCIe input/output ports description[AXIPCIPG]

| Port                                       | Dir       | Description                                                                                               |

|--------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------|

| M_AXI                                      | Interface | Master AXI interface connected on the slave interface of the AXI interconnect.                            |

| S_AXI_CTL                                  | Interface | Slave AXI interface meant for controlling and configuring the PCIe bridge.                                |

| S_AXI                                      | Interface | Slave AXI interface connected to a master interface on the PRC.                                           |

| axi_aclk                                   | Output    | Clock generated by the PCIe bridge meant to drive the clocks of the AXI interfaces.                       |

| axi_aresetn                                | Output    | Active low reset generated by the PCIe bridge meant for the AXI interfaces.                               |

| axi_ctl_aresetn                            | Output    | Active low reset generated by the PCIe bridge meant for the AXI interface that is connected to S_AXI_CTL. |

| sys_rst_n Output PCIe reset generated by t |           | PCIe reset generated by the PCIe edge connector itself.                                                   |

| sys_clk_gt                                 | Output    | PCle reference clock                                                                                      |

| refclk                                     | Output    | PCle reference clock.                                                                                     |

## 4.6.3. Detailed description

The PCI express bridge enables a PC to communicate with the FPGA to enable operations with the goal of controlling the different blocks in it. Its important interfaces are the S\_AXI\_CTL interface, which serves to configure this block by accessing its internal configuration registers, the S\_AXI interface which is a slave interface to be driven by the master interface of the DFX controller for the purpose of fetching partial bit files, and the M\_AXI interface which is a master interface driving a slave interface of the AXI interconnect.

It can be directly instantiated using the Vivado IP catalog but it needs to be configured. Here is the configuration that was used for this design:

| Percustomize IP@ky-compengl.ces.ch<br>AXI Bridge for PCI Express Gen3 Subsystem (3.0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|