# POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

Master's Degree Thesis

# New techniques for path delay faults functional test

Supervisors

Prof. Matteo SONZA REORDA Dr. Riccardo CANTORO Candidate

Dario FOTI

March 2020

#### Abstract

With the advance in silicon technology, recent electronic devices are becoming deeply embedded in extremely dense silicon dies and are required to comply with increasingly strict timing requirements. Under these circumstances, several faults can be induced by different causes, like defects in the manufacturing processes, process variations as well as ageing, workload, crosstalk and many others.

Some of these defects can only be detected by testing the delay characteristics of the circuit, so delay fault models are assuming a much more relevant position in fault analysis.

However, delay fault models require much more computational effort with respect to simpler and more widespread fault models when producing and evaluating the test. Applying the test is also a challenge due to the cost of ATE and the complexity introduced by BIST techniques, which obliges to search for other options.

Software Based Self Test is desirable in this context because it allows to apply at-speed tests with no hardware overhead and it can be used even in situations where controllability and observability are reduced.

In the context of this thesis, new techniques for delay-oriented online functional testing for embedded systems are proposed, focusing on path delay faults in particular.

The study was conducted using a RISC-V based core as benchmark device and has led to achieve a fast and optimized flow for functional test simulations.

It has been shown that, with the current implementation, in all case studies high percentages of path delay faults detectable with scan techniques can be also detected with functional tests. Additionally, efforts have been put to identify a relationship among stuck-at, transition delay and path delay fault coverage.

Finally, some insights about the functional testability have been extracted by analyzing statistically how many misbehaviours a path delay fault should produce before being functionally observable.

# Acknowledgements

After having travelled through the long and winding road that leads to his destination, just before taking the last step forward, the traveler should always stop and take a look back.

Those hills and valleys, those twists and turns, the people met in his way and the marks that they left on him will forever be the means for his mind to relive that journey.

As now I am the traveller about to reach his destination, I look back to remember each step I went through and I recognize I could never take the last step without showing gratitude to those people that helped me along the path.

I want to pay my special regards to my supervisors, Prof. Matteo Sonza Reorda who has given me the opportunity to work on such innovative ideas and has always provided me with the right advice and Dr. Riccardo Cantoro, whose expertise I admire and that has always been an inspiring guide.

My appreciation is also due to the research team of Lab 3, in which this work was developed, who have warmly welcomed me.

I would like to recognize the invaluable assistance that all my colleagues and friends provided during my study and my personal life: Carmelo, Nicola and Stefano, to whom I owe a lot, both personally and professionally, and that I consider irreplaceable; Benito, Dario, Hairo, Kevin, Sandro, Simone, that have made this years brighter and gave me the opportunity to learn a lot from them; Nikos, that has helped me in most of the hard times I experienced during this work; Davide, who has been the best housemate I could ever encounter; Antonio, Benedetto, Gloria, Luciano, Nancy, Paolo, Peppe, Santi and everyone of my friends who are spread around the world, with whom I shared all my life and contributed to make me the person I am.

Nothing of what I achieved through all these years could have been possible without the loving and tireless support of my father Sergio, my mother Enza, my sister Giada and my whole family, to which I wish to express my deepest gratitude for having shared the efforts and the struggles of this long journey. Lastly, I want to thank my girlfriend, Federica, that deserves part of the credit for this achievement. No words exist to express how much her presence has signified to me and how vital her care was.

> "Two roads diverged in a wood, and I I took the one less traveled by, And that has made all the difference."

> > R.Frost, The road not taken

# Table of Contents

| List of Tables VII |                    |                                                                                                                                      |    |  |  |  |  |

|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| Li                 | st of              | VI                                                                                                                                   | [] |  |  |  |  |

| 1                  | Intr               | duction                                                                                                                              | 1  |  |  |  |  |

| <b>2</b>           | Dela               | v test                                                                                                                               | 6  |  |  |  |  |

|                    | 2.1                | Relevant definitions                                                                                                                 | 6  |  |  |  |  |

|                    | 2.2                | Path Delay Test criteria                                                                                                             | 8  |  |  |  |  |

|                    |                    | $2.2.1  \text{Non-robust test}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                     | 9  |  |  |  |  |

|                    |                    | $2.2.2  \text{Robust test}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                         | 0  |  |  |  |  |

|                    |                    | 2.2.3 Untestable faults $\ldots \ldots 1$               | 1  |  |  |  |  |

|                    | 2.3                | Fault list minimization                                                                                                              | 1  |  |  |  |  |

|                    |                    | 2.3.1 Static sensitization $\ldots \ldots 1$            | 2  |  |  |  |  |

|                    |                    | 2.3.2 Dynamic sensitization $\ldots \ldots 1$                         |    |  |  |  |  |

|                    |                    | $2.3.3  \text{False paths}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                         | -  |  |  |  |  |

|                    | 2.4                | Delay testing techniques                                                                                                             |    |  |  |  |  |

|                    |                    | $2.4.1  \text{Launch-on shift}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                     |    |  |  |  |  |

|                    |                    | $2.4.2  \text{Launch-on capture}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                   | 4  |  |  |  |  |

|                    |                    | 2.4.3 Enhanced scan                                                                                                                  | 5  |  |  |  |  |

|                    |                    | 2.4.4 Functional testing $\ldots \ldots 1$              | 6  |  |  |  |  |

| 3                  | Fun                | tional Delay Testing flow 1                                                                                                          | 9  |  |  |  |  |

|                    | 3.1                | $Synthesis \ldots 1$ | 9  |  |  |  |  |

|                    | 3.2                | Static timing analysis                                                                                                               | 1  |  |  |  |  |

|                    | 3.3                | Logic simulation                                                                                                                     | 2  |  |  |  |  |

|                    | 3.4                | Combinational level fault simulation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 2$                                            | 2  |  |  |  |  |

|                    | 3.5                | Sequential level fault simulation                                                                                                    | 4  |  |  |  |  |

| 4                  | <b>Flov</b><br>4.1 | implementation2Synthesis : Design Vision                                                                                             | -  |  |  |  |  |

|                    |                    |                                                                                                                                      |    |  |  |  |  |

|          | 4.2 | Static Timing Analysis : Primetime         | 27 |

|----------|-----|--------------------------------------------|----|

|          | 4.3 |                                            | 28 |

|          | 4.4 | -                                          | 28 |

|          | 4.5 |                                            | 31 |

|          | 4.6 | -                                          | 34 |

| <b>5</b> | Exp | perimental results                         | 37 |

|          | 5.1 | Netlist data                               | 38 |

|          | 5.2 | Fault list data                            | 38 |

|          | 5.3 | Test programs information                  | 39 |

|          | 5.4 | Fault simulation data                      |    |

|          |     | 5.4.1 Combinational level fault simulation | 42 |

|          |     | 5.4.2 Fault list conversion                | 44 |

|          |     | 5.4.3 Sequential level fault simulation    | 44 |

|          |     | 5.4.4 Test programs effectiveness          |    |

|          | 5.5 | Result analysis and considerations         | 47 |

| 6        | Cor | nclusion and future improvements           | 55 |

|          | 6.1 | Functional test flow                       | 55 |

|          | 6.2 | Side goals                                 | 57 |

|          |     |                                            |    |

# List of Tables

| 5.1  | Top level core info                                        | 8  |

|------|------------------------------------------------------------|----|

| 5.2  | Report timing information                                  | 8  |

| 5.3  | Number of paths per module                                 | 59 |

| 5.4  | Test programs functional fault coverages                   | -1 |

| 5.5  | Combinational fault simulation results                     | 2  |

| 5.6  | Number of faults per primitive class                       | 4  |

| 5.7  | Functional fault simulation results                        | :5 |

| 5.8  | Most critical detected faults per program                  | -7 |

| 5.9  | Most critical functionally detected faults information 5   | 2  |

| 5.10 | Most critical functionally undetected faults information 5 | 3  |

| 5.11 | Fault coverage comparison                                  | 4  |

|      |                                                            |    |

# List of Figures

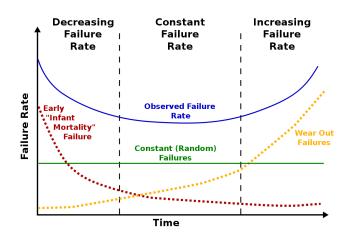

| 1.1 | Typical failure rate curve, extracted from [2]                      | 2  |

|-----|---------------------------------------------------------------------|----|

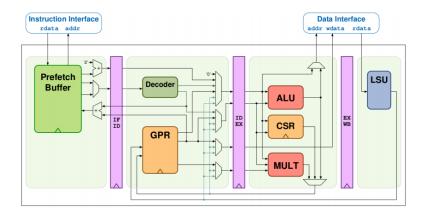

| 1.2 | PULPino RI5CY core diagram, extracted from [1]                      | 4  |

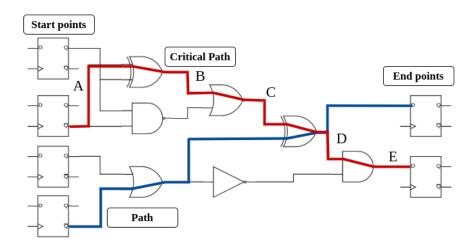

| 2.1 | Example of sequential circuit                                       | 7  |

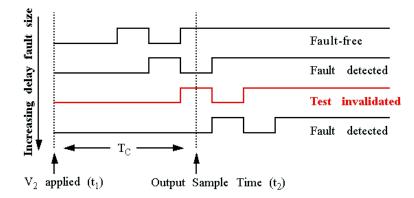

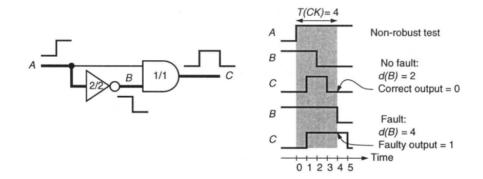

| 2.2 | Example of invalidation of a test, extracted from [8]               | 9  |

| 2.3 | Non-robust test example, extracted from [6]                         | 10 |

| 2.4 | Robust test conditions for elementary gates [6]                     | 10 |

| 2.5 | Fault classification                                                | 11 |

| 2.6 | Structural false path                                               | 13 |

| 2.7 | LOS procedure, extracted from [5]                                   | 14 |

| 2.8 | LOC procedure, extracted from [5]                                   | 15 |

| 2.9 | Enhanced scan circuit                                               | 16 |

| 3.1 | Flowchart of the tool                                               | 20 |

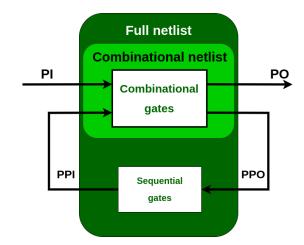

| 3.2 | Huffman model                                                       | 21 |

| 4.1 | Z01X flowchart, extracted from $[13]$                               | 32 |

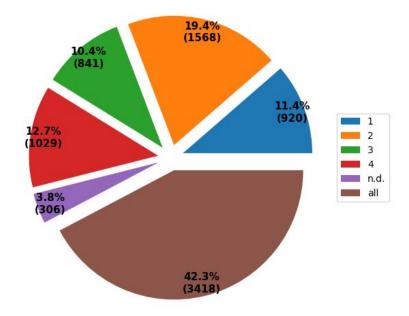

| 5.1 | Cumulative combinational fault coverage                             | 48 |

| 5.2 | Number of faults detected at combinational level shared by programs | 49 |

| 5.3 | Number of faults detected at sequential level shared by programs .  | 50 |

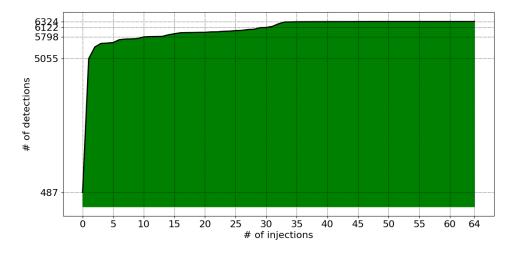

| 5.4 | Number of detected vs. number of injections                         | 51 |

|     |                                                                     |    |

# Chapter 1 Introduction

In the recent years the semiconductor industry is evolving very fast and pushing hard on new technologies that allow noticeable improvements in performances of the devices with respect to the past. In particular, the manufacturing phase of the silicon dies is moving towards more complex and sophisticated processes. Most of the added complexity is related to the shrinking of the channel length of the transistors, currently set in the order of few tens of nanometers, that allow very high working frequencies and very compact and dense designs.

This advantage comes at the price of more frequent physical defects and shorter devices lifespan. ICs are nowadays more prone to manufacturing defects, process variations, ageing effects, electromagnetic interference, parasitic effects and overheating-related issues and are in general much more sensitive to degrading than older generation devices.

In figure 1.1 the trend of a typical failure rate curve is represented. With the newest technologies, infant mortality and wear out failures happen with an increasing frequency, causing the curve ends to be narrower, assuming more of a "U" shaped appearance.

This context poses new challenges in the matter of testing. Creating high quality, cost-effective tests is very hard on these devices, for several reasons.

As an example, the cost of *Automated Test Equipment* (ATE) required for production tests is growing exponentially, because of the increased precision, the stricter timing requirements and the larger amount of storage capability required.

The increased density of VLSI devices forces controllability and observability limitations and raises problems in power dissipation, crosstalk and line resistivity that could result in a premature failure of the IC or temporary malfunctioning.

Commonly used fault models (e.g. the stuck-at-0/1) are starting to show their limitations in representing the real defect coverage of a device, while more complex models that are able to represent delay defects in the circuit are becoming far more relevant and popular. Among these, it is worth mentioning:

Figure 1.1: Typical failure rate curve, extracted from [2]

- 1. **Transition delay fault**: it models a delay defect affecting a single logical node, that causes a state transition to be slower than expected.

- 2. Path delay fault: it models a distributed delay defect affecting multiple logical nodes interconnected in sequence, that causes a state transition to traverse those nodes slower than expected.

In particular, the *Path Delay* fault model is considered to be the most accurate since it is able to catch both lumped and distributed delay defects [9].

At-speed testing is crucial for targeting these kinds of timing-related faults, but at the same time it is harder to produce suitable testing patterns. In fact, testing these faults involves finding couples of vectors able to launch a state transition and to capture it, instead than requiring a single vector to force a single value on a specific node, as it happens with the stuck-at fault model.

Moreover, since the number of faults to cover grows very fast with the size of the circuit, it is possible that a very high number of patterns should be produced to achieve high coverages; moreover, the probability of fault masking increases.

As already highlighted, external at-speed testers are not a suitable solution for their cost, while BIST techniques are quite often discarded due to the excessive area overhead, performance degradation and clock issues.

A suitable option to overcome these problems consists in relying on *Software Based Self Test* solutions, that are reliable, affordable and applicable even in situations where accessibility is reduced [9].

Currently, delay faults are usually tested resorting to scan techniques, which allow to have higher controllability and observability of the circuit and to catch a good portion of these faults even in the case of sequential circuits. By the way, there are several downsides of using these methods, like hardware and area overhead, test-length overhead due to the time spent loading/unloading the scan chains, overtesting.

It is easy to understand that using these delay fault models requires much more efforts and innovative techniques are being developed to adapt to the industry needs.

The work carried out in this thesis falls within this framework, suggesting new ideas in matter of delay-oriented online functional testing for embedded systems. Online testing, also called in-field test, is a testing technique that does not make use of external testers and it is often performed without removing the system under test from its operational environment. Two types on of online testing can be distinguished: concurrent, when the device is tested without stopping its normal functioning, or non-concurrent when the test is applied while the device is not performing its normal operation.

Therefore, this particular testing technique is useful since it can be applied at any time, monitoring the circuit during the whole lifespan and without requiring any kind of Design for Testability that may affect the circuit behaviour and/or performances.

Taking in consideration *Path Delay faults*, it is proposed a new approach for the fault coverage analysis of *Software Test Libraries* (STLs), that relies on the usage of different commercial software tools widespread in the industrial and academic fields. This is aimed at providing an integrated tool set for path delay functional tests simulations on both combinational and sequential netlists (with special emphasis on processors) that is able to evaluate the fault coverage while cutting down simulation time.

The tool has been evaluated using as benchmark device an open-source singlecore SoC platform based on a 32-bit RISC-V core, developed by ETH Zurich and Università di Bologna, named *PULPino*. For the purpose of this thesis, PULPino was configured to use the *RI5CY* core. RI5CY is an in-order, single-issue core with 4 pipeline stages, fully supports the RV32I, RV32C and RV32M instruction sets, which respectively implement integer, compressed and multiplication instructions. It can be configured to have single-precision floating-point instruction set extension (RV32F). It implements several ISA extensions such as: hardware loops, postincrementing load and store instructions, bit-manipulation instructions, MAC operations, support for fixed-point operations, packed-SIMD instructions and the dot product. It has been designed to increase the energy efficiency in ultra-lowpower signal processing applications. PULPino has also been taped-out as an ASIC in UMC 65nm technology in January 2016 [4].

This choice has been made to have the opportunity to evaluate how the flow

Figure 1.2: PULPino RI5CY core diagram, extracted from [1]

can be applied on a real commercial microcontroller device, whose architecture has been adopted by several companies and academic research centers worldwide. In particular, the main focus was put on testing the core by itself, isolated from other boundary components such as peripherals.

The study conducted in this thesis has led to devise a fast and optimized flow for path delay functional fault simulations, in which several arrangements have been made in order to properly evaluate the fault coverage while minimizing simulation time. It has been shown that in all case studies a very high percentage of the path delay faults detectable with scan techniques at combinational level can be also detected with functional tests. Additionally, efforts have been put to demonstrate if a correlation between stuck-at, transition delay and path delay fault coverage can be exposed.

Some insights about the functional testability have been extracted, also by analyzing statistically how many times a path delay fault should produce its effects before being observable on the *Primary outputs*.

In the following chapter the reader will find an overview on the delay fault models, with particular emphasis on path delay faults, that outlines the main theoretical aspects, distinctive features and state of the art.

In the third chapter the devised flow will be described, analysing the kind of tools that are needed for each step, the functionalities used and how those are linked to each other.

The fourth chapter is about an example of the actual implementation of the flow: strengths and limitations will be described for each tool, explaining how those have been integrated to automate the process.

The experimental results obtained through the implementation proposed in chapter four are reported in the subsequent chapter. Several test programs are evaluated on the benchmark device to measure the obtained fault coverage. To summarize what has been obtained and how and where it can be improved, chapter six reports the main conclusions that can be drawn from the practical usage of the flow, together with some proposal on future improvements.

# Chapter 2 Delay test

In a generic sequential system, input and output signals are synchronized with respect to a specific periodic signal, often referred as clock. All signals are supposed to assume a steady value within a certain time frame marked by clock signal edges, indicated as clock period. In real applications, signals may experience several transitions within a clock period, that can usually happen within a shorter time frame called transition region. For a manufactured circuit to function correctly, the transition region must not extend beyond the clock period; if this does not happen, the circuit is said to be affected by a delay fault [6].

This chapter is intended to give background on delay faults and context to the discussion that will follow in the next chapters. It is possible to find some fundamental concepts and definitions, an overview of the theoretical aspects of PDF testing, and some insights on the currently most used testing techniques.

## 2.1 Relevant definitions

Before diving into it, it is worth to define some useful terms that will be recurring during the course of dealing with the matter. To begin with, we can give the following definitions:

- 1. **Start point**: Either a primary input pin or the output of a sequential element of the design, that defines the beginning of a path

- 2. End point: Either a primary output pin or the input of a sequential element of the design, that defines the ending of a path

- 3. Path: Set of elementary combinational gates connected in a chain, starting from a *start point* and ending on an *end point*.

- 4. **Propagation Delay**: if referred to a *path*, it indicates the amount of time that a signal transition takes to be propagated from a *start point* to an *end point* traversing a *path*; if referred to a gate, it indicates the amount of time that a signal transition takes to be propagated from the inputs to the output of the gate itself.

- 5. Arrival time: time instant at which a state transition reaches the output of a gate or path and the output state can be considered stable.

- 6. **Slack**: Difference in time between clock period and *arrival time* for a specific gate or path. For the circuit to work correctly, it must always assume a positive value.

- 7. Critical path: Circuit *path* that shows the slowest propagation delay, or in other words the shortest slack.

Figure 2.1: Example of sequential circuit

In fig. 2.1 it is possible to see a slice of a sequential circuit. In blue, an example of *path* is highlighted, connecting two flip-flops that act as *start* and *end* point. In red instead it is indicated a *critical path*: since it runs through the highest number of combinational cells in sequence, its *arrival time* will be one of the latest in the represented netlist, exactly equal to the sum of the *propagation delays* of the cells, considering flip-flops and interconnections as ideal.

Having clear these definitions, it is possible to introduce more appropriate definitions of delay fault models:

1. **Transition delay fault**: defect which is lumped on a single gate, that affects the nominal *propagation delay* of that gate causing a specific state transition to

happen later than the sampling edge of the clock. This usually causes incorrect sampling on the sequential elements connected to that gate, preventing the circuit from working at a specific clock frequency. In a circuit composed of ngates, the number of possible transition delay faults is equal to 2n.

- 2. Path delay fault: defect which is distributed on the set of gates belonging to a *path*, that affects the nominal *propagation delay* of that *path* causing a specific state transition to happen later than the sampling edge of the clock. This usually causes incorrect sampling on the sequential elements connected to that *path*, preventing the circuit from working at a specific clock frequency. In a circuit including m paths, the number of possible path delay faults is equal to 2m.

- 3. Slow to rise: often shortened in *str*, it indicates a delay fault happening when a rising transition is applied at the input of a gate or a path.

- 4. Slow to fall: often shortened in *stf*, it indicates a delay fault happening when a falling transition is applied at the input of a gate or a path.

- 5. Controlling value: it is an input value that, irrespectively of the other input values, determines the output value of a combinational element.

- 6. Non-controlling value: it indicates a value that, if present as input of a combinational gate, does not determine by itself the output value.

- 7. **On-path input**: Considering a gate belonging to a path, it indicates its input pin traversed by the path itself.

- 8. Off-path input: Considering a gate belonging to a path, it indicates one or more input pins belonging to the gate that are not traversed by the path itself.

Referring again to the circuit in fig. 2.1, supposing to apply the *path delay fault* model to the *critical path* in red, it is supposed that the *propagation delay* of each of the traversed gates is increased. This prevents the signal transition to be on time and causes the flip-flop to sample the wrong value.

In order to propagate the transition and test the path, it is needed that the *on-path inputs* assume *controlling values*, while the opposite has to happen for *off-path inputs*. In the next section, this concept is formally expressed and analyzed more in depth.

## 2.2 Path Delay Test criteria

A circuit can pass a delay test if it is capable of producing correct outputs when specific inputs are given and outputs are observed with a specific timing. Since delay testing requires to generate and catch a state transition, test patterns must be composed of pairs of test vectors to be applied in succession.

As an example, when dealing with transition delay faults the first test vector shall be arranged such that it is able to force a certain value on the output (either a 0 or a 1), while the second vector of the pair shall force the desired gate to execute the transition while ensuring that the former is propagated up to the output. Therefore the second vector is nothing but the same vector that should be used to test a SA1 fault if a *stf* fault has to be tested, or a SA0 in case of a *str* fault.

Concerning *path delay* test in particular, it is said that a test is considered valid for a given fault if the value present at the output of the path at sample time is only controlled by the transition on the input of the path. This means that all *off-path inputs* must assume non-controlling value to make the test possible. It is possible to define different types of tests, based on how loose the conditions applied for detection are.

#### 2.2.1 Non-robust test

It is a test that guarantees to detect a fault when no other fault is present. This means that all *off-path inputs* assume non-controlling values only during the steady-state following the application of the second vector (a condition known as static sensitization), while during the application of the first vector they can assume whatever value.

This is the loosest requirement for a fault to be considered testable, and unfortunately it can be invalidated by the presence of other faults in the device or by glitches that may occur.

Figure 2.2: Example of invalidation of a test, extracted from [8]

For the test to be an effective measure of the path delay, the expected output value must be uniquely controlled by the transition propagating through the on-path inputs [6].

Figure 2.3: Non-robust test example, extracted from [6]

If a non-robust test exists for a specific fault, it is indicated as a *singly-testable* path delay fault.

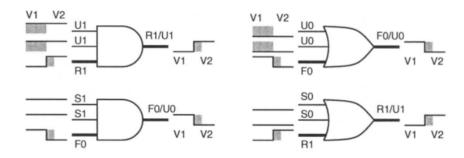

#### 2.2.2 Robust test

It is a test that guarantees to detect a fault even if multiple faults are present, therefore the detection is guaranteed to be not influenced by the delay distribution in the circuit.

To classify a test as robust, it has to produce real events, which basically means that different steady-state values for first and second vectors should appear on all *on-path inputs* and these events must produce controlling values for *on-path inputs*.

Figure 2.4: Robust test conditions for elementary gates [6]

If a robust test exists for a specific fault, it is indicated as a *robustly-testable* path delay fault.

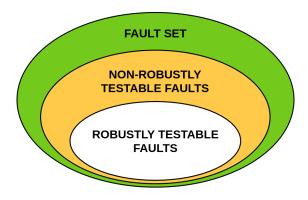

#### 2.2.3 Untestable faults

If none of the above definition applies to a test for a fault, it is indicated as an *untestable path delay fault*. They can be further divided into *structurally untestable faults* or *functionally untestable faults*. The first definition is used when no vector pair that allows detecting the fault can be generated; the second one is used when no functional input stimuli (e.g. a sequence of two instructions) that allows detecting the fault can be generated.

Therefore, structurally untestable faults appear to be a subset of the functionally untestable ones.

Figure 2.5: Fault classification

Figure 2.5 graphically shows what has been explained in this paragraph. Only for a subset of faults in the set of all possible path delay faults it is possible to produce a test. Since the non-robust criteria are the least stringent in term of requirements, a large portion of faults can be categorized as non-robustly testable. Robust conditions are more strict, therefore only few faults can be defined as robustly testable. This category of faults can be seen as a subset of the nonrobustly testable, since the robust test criteria can be intended as a sufficient (but not necessary) condition for a fault to be non-robustly testable.

### 2.3 Fault list minimization

A very important aspect in delay fault testing is the generation of the fault list. The whole process revolves around the choice of the paths that need to be tested: a larger fault list results in a wider test set, harder test generation, increased simulation times and efforts and many other side effects.

Since the number of paths in a circuit can be huge in the first place, efforts have been put in the past to find systematic ways to identify a minimum set of faults to test. Moreover, it is not rare to find a very high number of paths having comparable properties, hence a larger portion of paths should be included in the fault analysis.

It is common to extract a list of critical paths sorted by slack through static timing analysis, but usually static analyzers perform a strongly pessimistic analysis and do not consider the functionality of the design, but just its topology.

This means that a static timing analyzer may take into account paths that exist in the circuit topology but do not allow the propagation of an event. Paths falling into this category are, generally speaking, considered *false paths*. They do not affect the operating working frequency, hence they should not be considered when setting timing constraints on the design and also for testing purposes.

For some devices or modules false paths can represent the vast majority of the paths in the circuit and may represent a great obstacle for tools, as highlighted in the case if the *ISCAS85 C6288* circuit in [15] and for several other *ISCAS* benchmarks in [7].

There exist several methods to prune the list of faults that can be considered, based on the analysis of the functionality of the design. Some of the most wellestablished are listed in the following.

#### 2.3.1 Static sensitization

This method classifies a path as *statically sensitizable* if it exists at least one set of inputs that allows to propagate a transition on that path from startpoint to endpoint, regardless of the propagation delay of the gates. In other words, the input vectors can sensitize the path if in static conditions all off-path inputs assume non controlling values.

#### 2.3.2 Dynamic sensitization

While it is possible that a path may not meet the criteria for static sensitization, it is also possible that due to propagation delays some statically unsensitizable paths may enter in the condition of propagating an event (glitch) for a short period of time. Hence, paths falling into this category are declared *statically false* paths, but are at the same time also *dynamically true* paths. This shows the limitations of static sensitization: it may underestimate the real timing requirements of a design, hiding the presence of *dynamically true* paths.

From these assumptions, a path is declared *dynamically false* if those events that may occur considering timing properties cannot be propagated through the path and possibly captured by its endpoint. Otherwise, it is declared as *dynamically true*.

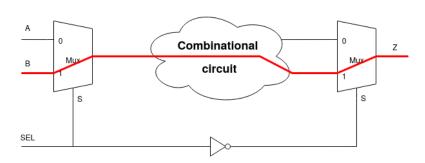

#### 2.3.3 False paths

A structural false path is identified if it is not sensitizable by means of static nor dynamic criteria because of some structural properties. An example is proposed in figure 2.6 where a path is highlighted in red. For this path a test can never be produced because no input combination exists for it to be sensitized, since the selection signals show opposite polarity. However, it may be considered critical by a static timing analyzer because the tool analysis is not aware of the functionality of the design.

We define functional false paths, instead, those paths that will never be exercised during the device mission because of some functional properties. As an example, in a processor core some opcodes may happen to be not included in the ISA. Thus, they may never be produced, preventing some structural paths to be excited.

Figure 2.6: Structural false path

### 2.4 Delay testing techniques

The most well-established testing techniques for delay testing are based on scan. The basic idea of scan techniques is to put the design in a particular mode, often referred as *test mode*, that reconfigures the circuit so as to have more controllability and observability of the circuit.

In fact, it ideally allows to break down a single sequential circuit into several combinational ones, to apply the desired test vector to each of them by shifting it directly inside the sequential element thanks to a dedicated input pin and to extract the result after test application by shifting it out from a designated output. It is worth mentioning three different types of scan-based delay tests, which are explained in detail in the next paragraphs.

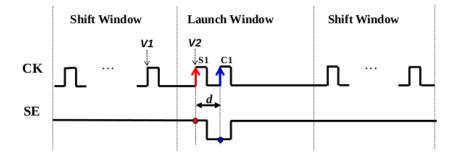

#### 2.4.1 Launch-on shift

Often abbreviated as LOS it is a test that observes the following procedure:

- 1. The circuit is put in test mode and the scan chain is enabled; the first vector of the pair is then shifted in the chain at slow clock speed.

- 2. Once the first vector is fully loaded, while the scan chain is still enabled, one more shifting cycle is generated to produce the second vector of the pair.

- 3. The scan chain is disabled and an at-speed clock cycle is produced to capture the response of the circuit.

- 4. The scan chain is enabled again so as to give the opportunity to download the scan chain, while preparing the circuit for the next pattern application uploading the first vector of the next pair.

Figure 2.7: LOS procedure, extracted from [5]

It offers the advantage of reusing the same hardware needed for other scan-based tests and of having to store only one test vector per pattern, since the second test vector is just a shifted version of the first one, allowing to cut the memory footprint of the test set.

The disadvantage is that not all possible pairs of vectors can be generated and that is difficult to produce the transitions on the signal that enables the scan chain. Moreover, there is the possibility to produce overtesting, since the second vector may assume values that cannot be generated in any condition by the device.

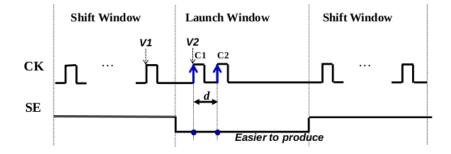

#### 2.4.2 Launch-on capture

Often abbreviated as *LOC*, it is a test that observes the following procedure:

1. The circuit is put in test mode and the scan chain is enabled; the first vector of the pair is then shifted in the chain at slow clock speed.

- 2. Once the vector is fully loaded, the scan chain is disabled and a capture cycle is generated to allow the combinational logic to respond to the first vector. This response is sampled by the sequential elements and actually serves as second vector of the pair.

- 3. An at-speed clock cycle is produced to capture the response of the circuit to the second vector.

- 4. The scan chain is enabled again so as to give the opportunity to download the scan chain, while preparing the circuit for the next pattern application uploading the first vector of the next pair.

Figure 2.8: LOC procedure, extracted from [5]

It offers the advantage of reusing the same hardware needed in other scan based tests and of having to store only one test vector per pattern, since the second test vector is directly produced by the combinational circuit reacting to the application of the first one, allowing to cut the memory footprint of the test set.

The limitation of this method is that not all possible pairs of vectors can be generated.

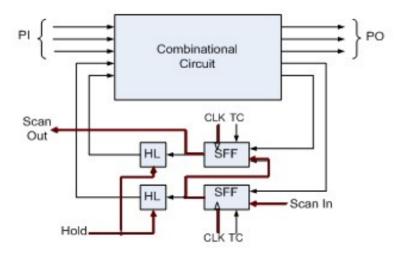

#### 2.4.3 Enhanced scan

The singularity of this test method is that it uses a particular hardware arrangement that enables more freedom during the test application.

In addition to the basic scan chain, it introduces a layer of latches used to hold one vector while the other is shifted in. This test observes the following procedure:

1. The circuit is put in test mode and the scan chain is enabled; the first vector of the pair is then shifted in the chain at slow clock speed. It is immediately applied and latched into the additional memory elements.

Figure 2.9: Enhanced scan circuit

- 2. Then, the second vector is scanned in the scan chain. Once the upload phase ends, the scan chain is disabled and an at-speed clock cycle applies the second vector and captures the response

- 3. The scan chain is enabled again so as to give the opportunity to download the scan chain, while preparing the circuit for the next pattern application uploading the first vector of the next pair.

It offers the advantage of having the possibility to apply any of the possible test patterns, thus maximizing the achievable fault coverage.

The limitation of this method consists in the larger memory footprint, since both vectors need to be stored in memory, the overhead in hardware requirements and the possibility to incur in overtesting, since it is possible to apply any value to the combinational circuit, even those that may never be produced by the device itself.

#### 2.4.4 Functional testing

The state of the art in path delay fault functional testing is still in its early stages. The only consolidated methodologies to apply delay oriented tests are based on the usage of ATE and BIST or other sort of DfT, which by the way are expensive in terms of complexity, costs and performance.

Moreover, there exist articles [11] in literature that question the effectiveness and quality of scan-based delay oriented tests. In the cited article in particular, the author raises the question of what kind of defects LOC and LOS tests applied on transition delay faults can effectively detect. Particular attention should be put in applying LOS because it can potentially lead to overtesting by activating paths from non-functional states, causing unnecessary yield losses. It is then explained how these tests mainly detect open defects, missing resistive defects in vias and interconnections; the author proposes also that these kind of tests should explicitly target open defects.

Software Based Self Test has been recognized as a valid alternative to these techniques, because it can be used in stand-alone modules as well as when the processors are deeply integrated and their accessibility is reduced and implicity avoids overtesting issues, since the test vectors used can only be generated from the subset of values that the circuit could assume during its normal functioning. The three main issues encountered in this field are the lack of software tools that allow to simulate relatively fast and effectively the test application on this fault model, to which this thesis is proposing a solution, the problem of test program generation and the problem generated by functionally untestable faults.

Some methodologies have been developed for test generation resorting to manual or automated approaches, either deterministic or heuristic, and research is still being performed on that [10].

In [9] both gate and rtl level descriptions are used to generate the test programs. The first one is used to extract the list of paths and to obtain the fault excitation conditions using Binary Decision Diagrams, while the second is used to run an evolutionary algorithm and perform fast rtl simulations useful for the automatic generation of a test program. The device used for evaluating the method was an 8051 microcontroller.

Another approach was proposed in [3], where the rtl description of two different benchmark processors, namely the 16-bit VPRO and the 32-bit DLX processor, were used to build a graph representing the pipeline behaviour with the purpose of finding the right constraints for test generation. The former was then performed resorting to ATPG techniques under those set of constraints.

The problem of test program generation is strictly bonded to the third one: identifying functionally untestable faults and removing them from the fault list may help in producing more effective and optimized self tests carefully tailored on those faults that really need to be tested, as well as their correct fault coverage evaluation.

The challenge comes from the restriction imposed from the Instruction Set Architecture, preventing some transitions to be exercised on some paths. In these cases functionally untestable faults are originated, that never determine the performance in normal operations of the circuit, and if detected during testing may lead to discard functioning chips due to overtest.

An example of applicable methodology proposed in literature is reported in [10].

Here the chosen benchmark device was the i8051 microprocessor, and the methodology was based on the analysis and simulation of the ISA to identify untestability rules (e.g. unreachable states) starting from a list of structurally testable paths and the relative test patterns.

Despite these new ideas in matter of SBST and the advantages it ensures, this technique is still not very widespread in the industry fields, but it has the potential to be employed more often in the next years.

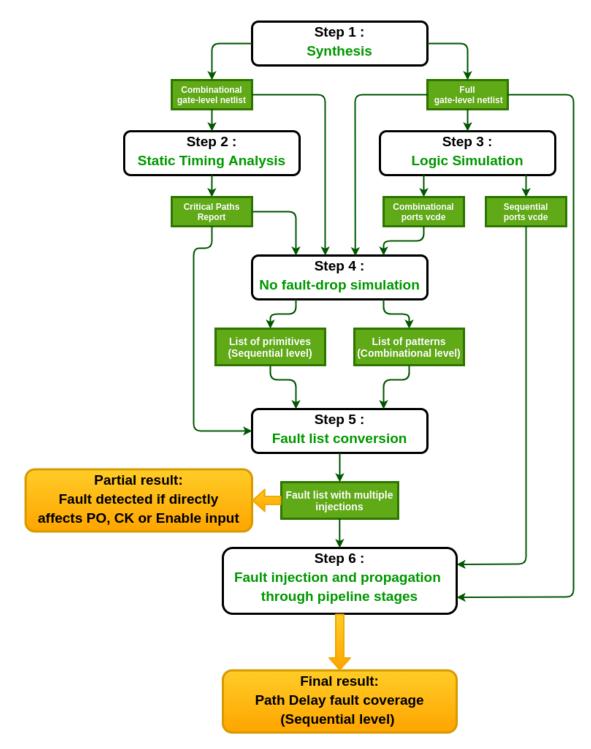

# Chapter 3 Functional Delay Testing flow

The proposed flow for path delay functional testing simulation comprises several steps, necessary to set up different aspects of the fault analysis. The steps are reported in the flowchart in figure 3.1. The purpose of this chapter is to describe the approach generically, without referring to a specific implementation or tool. Each of the phases will be explained in detail, considering how and why they should be performed and giving an overview on the required tools.

## 3.1 Synthesis

Assuming to have available the rtl-level description of the device to analyze, a preliminary step to apply the method is to synthesise it, which means to translate a behavioural description of the circuit into a structural one.

This process can be carried out by using software tools that take the name of synthesis tools and are able to produce as a result of the process a gate-level netlist of the circuit to be examined. This category of tools are in fact able to translate the high-level description of the device into a boolean network, that is then simplified by means of technology-independent and technology-dependent methods and mapped to the available set of cells. These are chosen among the ones available in the technology library, that should also be provided to the tool. The standard description languages for synthesis tools are *VHDL*, *Verilog* and *SystemVerilog*, but many tools can also work with C and *SystemC*.

This structural description of the target device, properly optimized according to the user constraints in terms of power, timing and area, will be necessary during every step of the applied flow. Moreover, it is useful for simplicity to produce two

Figure 3.1: Flowchart of the tool

netlist files: one that groups purely combinational cells, the second containing all components of the device, hence both combinational and sequential logic. The former should then replicate what's represented in figure 3.2, while the first netlist should only comprehend the section of the picture highlighted in light green. In fact, some steps of the presented approach require to work directly at the combinational level, while other take in consideration the full functionality of the IC.

Figure 3.2: Huffman model

During the synthesis phase, once the tool has mapped the design to the standard cells available in the library meeting the specified criteria, it is possible to create a new cell group that collects all the combinational cells. Then, this can be used as a lower-level hierarchical component in the design.

### 3.2 Static timing analysis

The generation of the fault list is related to the topological properties of the target device. More specifically, for each path identified in the netlist, two faults will be originated, described by the imposed transition on the startpoint of the path (either *stf* or *str*).

The fault list is usually generated by running a Static Timing Analysis (STA) in order to find which paths are the most critical in the design, or in other words, which ones are to be considered in the analysis.

Software tools that serve this jobs are called Static timing analysers and are capable of analysing the design with respect to the applied timing constraints and finding the most critical sections of the design with respect to that specific metric.

The result of the STA will be a text file where topological properties of each path are described: gates traversed by the path are listed in sequence, together with their start point and end point and the relative timing information. Paths are usually sorted by slack in increasing order.

Keeping timing information such as clock period or slack is optional during fault simulation, since the process can ignore this information to verify if the required transition can be generated and propagated through the path.

As mentioned in section 2.3, a subsequent path list reduction may be needed to minimize the number of faults that should be tested.

## 3.3 Logic simulation

Assuming to have the availability of different STL programs, either produced "by hand" or automatically generated by using ATPG tools or any other means, these need to be translated into patterns for the fault simulator.

Doing so requires to simulate the response of the fault-free circuit to the test program execution, and annotate the state of internal registers, input and output ports at each clock cycle. Suitable tools for this task are logic simulators, that have the possibility to dump user specified signals on text files using *Extended Value Change Dump* format (.vcde).

This kind of feature, more in detail, enables the user to record information about the value assumed by the signals at specific simulation times: in fact, each time a signal changes state, this is dumped on the file along with the time instant at which the transition occurred. VCDE files can be easily interpreted by fault simulators and translated into patterns.

Each pattern extracted from the file by the fault simulator will be no other than the result of the execution of two neighbour instructions of the test program.

For this purpose then, the gate-level netlist of the circuit must be instantiated within the testbench and signals of interest should be monitored while the simulation is running and included on the .vcde file.

Also in this case it could be handy to produce two separate .vcde files, one including all ports from for the combinational netlist and the other including the ports of the full netlist, since the flow expects to perform fault simulations at both levels.

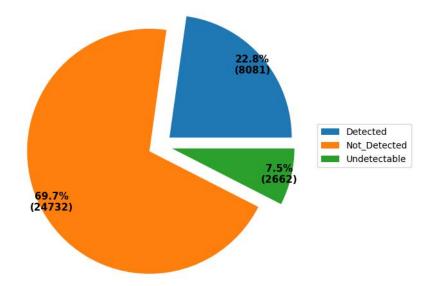

### **3.4** Combinational level fault simulation

Having performed all the preliminary steps just discussed, it is possible to move on and perform the actual fault simulation. Specific software tools are required, which are referred as fault simulators. These make it possible to simulate the behaviour of the device responding to the input patterns in presence of a fault and to compare it to the expected behaviour of the fault-free IC, to identify potential mismatches. Taking as input a structural description of the circuit, they build their own internal representation which is replicated many times to parallelize the simulation effort. For each fault it will be created one faulty replica of the device, such that only one fault at a time is active during each simulation.

The signal transitions listed in the .vcde file are read by the tool and translated into couples of test vectors; the path definition files is also read by the tool and transposed into a fault list.

The tool will then classify each of the added faults according to the outcome of the simulation. The most common classes to which a fault can be assigned to are:

- 1. **Detected** : the fault has been excited and has generated a detectable difference at an observation point with respect to the fault-free circuit;

- 2. Not detected : the fault has been excited but has not generated a detectable difference at an observation point with respect to the fault-free circuit;

- 3. Not controlled : the fault has not been excited by the test vectors used, but it could possibly exist a combination of vectors able to excite and detect it;

- 4. **Undetectable** : the fault cannot be excited or propagated to the observation point due to structural reasons.

In order to find all possible test patterns for the analyzed faults, it is useful to enable the *no fault-dropping* feature during this fault simulation: enabling it will ensure that, once a detecting pattern for a specific fault is found, it will not be removed from the fault list, but it will be still considered in the analysis. In case this option is not available, it is possible to implement some workarounds, as shown in the implementation described further in this thesis.

It is important to point out the main purposes of the combinational level fault simulation:

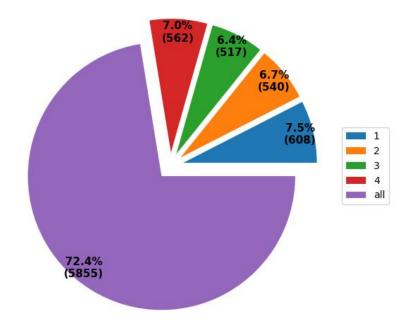

- 1. Identify whose paths can be sensitized by the test program.

- 2. Verify the fault coverage provided by the test program in use at combinational level.

- 3. Identify which and how many patterns are able to detect each fault.

Achieving a detection, at this stage of the process, signifies that a mismatch has been successfully propagated to one of the PPO primitives (e.g. a pipeline register of the processor core) and that this has been captured by the former.

Unfortunately, this is not sufficient to classify the fault detected also at sequential level, or in other words functionally detected. In consideration of the fact that this test flow is structured for functional testing, the netlist is not supposed to be provided with scan chains at all, or at very least it is supposed not to use those. This implies that the only opportunity to detect and observe faults is to experience the misbehaviour caused by the fault on one of the PO (e.g. the main memory port).

Since it is not given that a fault causing misbehaviour on a given PPO can produce similar occurrences also when observing PO only, a further effort is necessary to complete the process. It consists of propagating the fault through the sequential elements, which in the case of a processor core means traversing the pipeline stages, until reaching an observation point, that could be represented by the main memory data or address port.

The reason for a fault to never be observable at PO can be found in how the test program is devised (e.g. absence of load/store instructions, such that the fault can never be observed in memory; data dependencies that cause fault masking) or to device structural properties (e.g. structural fault masking).

### 3.5 Sequential level fault simulation

From what has been described in the previous paragraph, it is possible to understand that propagating the fault effect until reaching the POs plays a very important role in the functional fault simulation process. This can be done either with the same fault simulator tool used at combinational level if possible, or with other fault injecting methods.

Most of the currently available commercial fault simulators provide just a small support over path delay fault testing, in particular when the target devices are not provided with scan functionalities, since this model is not as popular as others. It may be possible to work with a combinational slice of the circuit, but in most of the cases the analysis boundaries can't be expanded further.

Two working modes are generally supported: *Basic Scan* mode which implies the use of scan-based procedures and the *Fast Sequential* mode, an emulation of sequential circuits working just for small time windows composed of a limited amount of clock cycles. In *Fast Sequential* mode, once both vectors have been uploaded and applied, the circuit is able to work in operating mode for a fixed amount of cycles; after that, data is download from the scan chain. Unfortunately, this solution could result impractical when a full test program has to be simulated, since their duration can reach hundreds of thousands of clock cycles.

At the current state of the art, no tool supports true *Full Sequential* mode, that is a purely functional simulation in which every consecutive couple of instructions  $(inst_i, inst_{i+1})$  constitutes the vectors couple necessary to test path delay faults.

In case a different fault injection method is chosen, the fault detecting patterns that have been individuated in the previous step can be used for this purpose:

focusing on those faults that have been detected at combinational level, patterns can be used for setting up multiple fault injections at several time instants, adding up multiple fault effects and maximizing the probability to detect the faults on the primary outputs. Different solutions can be used, based on software (fault simulators) or hardware (FPGA) tools.

# Chapter 4 Flow implementation

In order to disclose a proof of concept of the devised flow, it has been decided to implement it using well-established software tools that are cutting edge in their field of application and are considered a standard in most of the cases.

This choice has given the opportunity to validate and optimize the flow obtaining robust and trusted results. Moreover, it ensures the repeatability of the results.

The tool suite used is based on *Synopsys* softwares, which is one of the leading companies in EDA tools when dealing with advanced IC design and verification. Unless differently specified, in this chapter it is assumed that the mentioned tools are produced by it.

The functional testing flow has been automated by integrating all these software by means of *Python* and *Bash* scripts, which effectively allowed to wrap everything as it was a single tool aimed at functional test of path delay faults. Several measures have been taken in order to give a flexible and expandable shape to the implementation.

As stated in chapter 1, the benchmark device chosen for validating the implementation is a single-issue in-order RISC-V based processor core, composed of 4 pipeline stages.

In the paragraphs below some insights about the tools and how the implementation was done are given.

## 4.1 Synthesis : Design Vision

The *PULPino* core has been synthesized by means of *Design Vision*, a very popular and de-facto standard synthesis tool. The design was mapped to standard cells taken from the *Nangate open cell library*, which is an open-source standard cell library produced by *Silvaco*. This technology library is one of the most used libraries for independent EDA flow testing and academic research. The synthesis process follows this structure:

- 1. The design is analyzed by the tool, which checks for syntax errors in the *HDL* description and translates each module in an intermediate representation.

- 2. The design is elaborated, meaning that all the analyzed modules are built and connected together, mapping it to a generic gate library.

- 3. Timing constraint are applied to the design, setting the clock period, uncertainty, flip-flop internal delays, cell loads and so on.

- 4. The netlist is ungrouped to remove the hierarchy levels and synthesised. This is where the design is mapped to the *Nangate open cell library* cells.

- 5. The netlist is then regrouped to create a module containing all the combinational cells of the design, which is at the bottom of the hierarchy, instantiated as a cell inside the top level module, that will comprehend also sequential cells.

- 6. The verilog gate-level netlist is extracted for both combinational and top level modules, together with .sdf and .sdc files.

A graphic representation of the obtained hierarchy can be evinced by figure 3.2. The *Standard Delay Format* file (.sdf) and the *Synopsys Design Constraint* file (.sdc) are used to annotate cell delays and the set of constraints that were imposed during the synthesis.

# 4.2 Static Timing Analysis : Primetime

To perform static timing analysis on the core, it was chosen to adopt *PrimeTime*, that is a suite of tools used not only for timing, but also for signal integrity, power-aware and variation-aware analysis.

The flow used is fairly simple and linear:

- 1. The combinational gate-level netlist is read, together with the technology library.

- 2. The .sdc and .sdf are read, to allow the tool to apply the same conditions and constraints applied during the synthesis process.

- 3. A report of the most critical paths is generated for each path group in the design.

Since these reports have to be imported after by the fault simulator, a special command is used to produce them in a compatible format for the fault simulator without the need for post-processing, which is included in the *PrimeTime* distribution.

The list of paths has been taken as it stands, so no pruning or other advanced techniques have been applied to recognize the presence of false paths. In any case, the proposed flow accepts any paths list, hence every possible optimization or subset extraction is allowed.

No specific target module was identified when performing the STA, but instead the STA parameters have been set in order to have an homogeneus distribution of paths through the whole core, ranging from the most critical to the least critical ones.

## 4.3 Logic simulation : Questasim

Questasim is an HDL simulation environment produced by Mentor Graphics. It is part of the Questa Advanced Functional Verification Platform. It supports multiple HDL languages as VHDL, Verilog, SystemVerilog and provides very powerful and advanced verification solutions.

For the purpose of this thesis, it was just used to simulate the core behaviour when subject to the execution of various test programs and to dump the state of the circuit at each clock cycle. The process is based on these steps:

- 1. Compile the test program.

- 2. Read the netlist and testbench files and build a model for the simulation.

- 3. Run the simulation until a stop condition is reached in the testbench. Meanwhile, dump the input and output port values at both combinational and sequential level.

This process has been performed each time a new test program had to be analyzed, simply loading a new assembly file into the testbench and repeating the previous steps.

## 4.4 Combinational fault simulation : Tetramax

For the fault simulation, it has been chosen to rely on *Tetramax*, which is a fault simulator that provides different functionalities for this fault model. It is in fact designed to work with scan-based devices; it also supports the different test

procedures described in the previous chapters. It is able to provide very fast path delay fault simulations with accurate results, and gives the opportunity to produce several report that allow a deep analysis of the results.

Since no scan chains were included into the benchmark device, Tetramax was used only to perform path delay fault simulations at combinational level. Unfortunately, for this fault model the native no fault-dropping feature was not activable. This limitation has been addressed applying the following strategy:

- 1. **Perform a first fault simulation at combinational level** in order to identify which faults can be detected by the test program in use.

- 2. Divide the test program into sections, each of them containing a subset of the whole patterns set, according to the detecting patterns found in the previous step. This can be achieved by setting a breakpoint into the pattern list for each detecting pattern found in the first simulation. Then, each section will be identified by two successive breakpoints.

- 3. Implement a simulation manager in Python that, given each section, resimulates a subset of the detected faults within the range of patterns included in the section. The set of faults to be included is based on the first pattern of the section to simulate. In particular, only faults that have been detected by a pattern previous to the start of the section in the first place are selected, because later ones are certain to produce no detection within that range. If detection is found, a new smaller section is produced and appended to the list of simulations to perform. If no more detection is found, the process reaches its end. This basically replicates the no fault-drop functionality.

- 4. After section simulation, collect all the detecting patterns and associate them to faults in an appropriate data structure for future post-processing.

In algorithm 1 it is reported the pseudo-code for this phase that better explains the procedure.

Since the no fault-drop feature plays such an important role in this context, efforts have been put to highly optimize it and provide useful functionalities to the final user.

In fact, the algorithm can be ideally portrayed as an exhaustive search based on a *divide and conquer* approach. Even if the simulations are performed on relatively few patterns, the algorithm may need thousands of those simulations before completion.

To speed up the process, the user has the ability to spawn several concurrent processes internally managed by the simulation manager script. Each of those can access to shared memory objects and can run simulations independently from each

#### Algorithm 1 No drop simulation

```

if dump state file is not(empty) then

current\_state \leftarrow restore\_state(dump\_state\_file)

flist \Leftarrow current\_state.flist()

sim\_set \leftarrow current\_state.sim\_set()

next sim set \leftarrow current state.next sim set()

fault\_lut \Leftarrow current\_state.fault\_lut()

else

flist \leftarrow read paths(paths definition file)

first\_results \Leftarrow run\_comb\_sim(all\_patterns)

splits \Leftarrow list\_detecting\_patterns(first\_results)

sim\_set \Leftarrow create\_sections(splits)

fault\_lut \Leftarrow create\_lut(flist, splits)

end if

child\_procs \leftarrow create\_procs(max\_processes)

while sim set is not(empty) do

for section in sim set do

results \leftarrow child \ procs.simulate(section, fault \ lut)

if detection in results then

flist \leftarrow update\_fault\_list(results.detected())

splits \leftarrow list\_detecting\_patterns(results.new\_sections())

next\_sim\_set \Leftarrow create\_sections(splits)

end if

if elapsed\_time() > seq\_sim\_interval then

seq results \leftarrow run seq sim(flist)

flist \leftarrow drop\_faults(seq\_results.detected())

end if

dump \ state \ file \leftarrow dump(flist, sim \ set, next \ sim \ set, fault \ lut)

end for

sim\_set \Leftarrow next\_sim\_set

end while

```

other, thus shaving a huge slice of simulation time from the total, proportional to the number of processes used.

In order to minimize the overhead introduced by the management of large fault lists, internal data are represented and organized as *Pandas* data frame objects. Pandas is a python module dedicated to data frames management and in the context of this thesis has allowed to use several optimized methods and functions needed for searching, merging, updating and in general keeping track of the fault record modifications throughout the simulations. Moreover, since a huge part of the simulation time is spent in reading the path definition files and the fault definition files, a strategy has been implemented to add the least amount of paths and faults in the fastest way.

This is based on the lower boundary of the set of patterns that has to be simulated: when the simulation manager starts its analysis, it builds a lookup table where each fault is matched to the pattern that has first detected it. This avoids to read files at each simulation in favour of using internal variables, which is much faster. Then, this table is used to add only those faults that have been first detected by a pattern that precedes the start pattern of the current simulation, as outlined at page 29.

Another interesting feature is that the algorithm is implementing checkpointing: it is able to capture the state of some crucial internal variables and to store it at regular intervals. Again, being such a time consuming task, this feature allows to stop the simulation and recover it anytime automatically after restarting the tool, both if the stop is intended or if it happens for some unwanted events.

Since as a general rule the more patterns are collected during this phase, the more fault injections can be performed next, the higher the probability to detect the fault at sequential (functional) level, faults are never dropped from the fault simulation. Instead, a very peculiar strategy has been adopted.

The simulation manager script is capable of launching the fault injection of faults detected at combinational level at regular intervals of time, parameter that can be tuned by the user, and to drop faults from the combinational simulation in case of functional detection. This allows to shorten the simulation time by avoiding unnecessary overhead caused by resimulation of faults, dropping those at the first occurrence of functional detection.

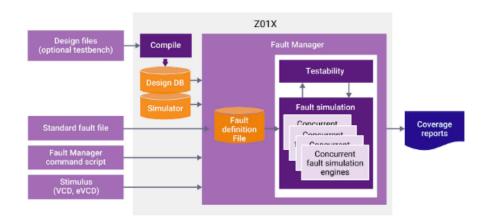

# 4.5 Sequential simulation : Z01X

As mentioned in the previous chapter, the last task to perform to achieve a functional coverage consists in propagating the fault effects to the PO. This task has been implemented thanks to the adoption of Z01X fault simulator.

This is one of the newest software tool provided by *Synopsys* and it is designed for functional fault simulations on safety-critical automotive electronic systems. Its purpose is to enable its users to meet the fault injection testing requirements listed in several safety standard, such as the ISO 26262 for automotive and the IEC 61508 in the industrial field. It ensures very fast fault simulations, also when dealing with thousands of multiple fault injections [13].

Its limitation in this context comes from the fact that it doesn't support the path delay fault model. Fault effects can, however, be replicated using the transient fault model.

Figure 4.1: Z01X flowchart, extracted from [13]

Assuming that the increase in delay resulting from the presence of a path delay fault causes the endpoint of that path to sample the opposite value with respect to the fault-free circuit, the fault effect has been modeled as a bit flip of the duration of one clock cycle affecting the output of that specific endpoint. This replicates the lack of transition at the end of the path, basically forcing the sequential element to keep the value sampled at the previous clock cycle.

Applying this strategy has a downside: faults are described in a very different manner and some post-processing needs to be applied to keep coherence between combinational and sequential fault simulation.

In fact, a path delay fault in Tetramax is represented by the path topology by itself, and could be derived in two possible transitions, namely slow-to-rise and slow-to-fall. As indicated at page 29, to each fault is associated a set of functional patterns, that represents a set of couples of vectors that test the fault. On the other hand, a faultin Z01X, according to the implementation proposed, has a specific syntax that is explained in the following:

$$\langle FS \rangle \langle FT \rangle (\langle IT \rangle) \{ |\langle PT \rangle| "\langle PN \rangle.Q" + |\langle PT \rangle| "\langle PN \rangle.QN" \}$$

More in details, regarding the syntax:

- **FS: fault status.** Within the fault list file has to be set as NA (not attempted). Its status will change after simulation according to the results.

- **FT: fault type.** To specify a toggle transient fault, the syntax requires a "~" character.

- **IT: injection times.** It is a list of time instants in which injections will be performed.

- **PT: primitive type.** Sequential elements are identified by the keyword "FLOP".

- **PN: primitive name.** The name of the sequential element on which injections are performed, according to what indicated in the netlist.

The part of the string that follows the "+" symbol is optional, and it is used only in the case the sequential element has both direct and inverted output pins.

The fault list conversion requires to:

- 1. Associate paths to respective endpoints. An endpoint can either be a PO, a latch or a flip-flop. It is important to also identify which input pin of the endpoint is affected by the path: this is helpful in reducing the fault list. For example, if the fault is affecting a PO of the circuit, it can be considered functionally detected without simulating it, so happens if the path is feeding an enable signal or a clock input.

- 2. Convert the patterns into time instants, since fault injection is time based. This can be obtained by knowing the clock period applied in simulation and the number that identifies the pattern. Beware that the injection is performed on the output of a sequential element, so if the detection at combinational level has occurred at clock cycle i corresponding to time j, injection should be done at clock cycle i+1 corresponding to time j + clock period.

- 3. Identify equivalent faults after conversion. It may happen, in fact, that two paths share the same endpoint and are detected by the same patterns. This produces two identical faults during the conversion, even if the faults were originally distinguishable at combinational level.

- 4. Remove equivalent fault from the fault list. It can be assumed that the detection of one of the replicas implies also the detection of all the others.

Therefore, the whole sequential simulation phase is conducted as follows:

- 1. Post-process the fault list inherited from the no fault-drop simulation individuating the correct endpoints for injection and associate patterns to time instants; then eliminate equivalent faults. Only faults detected at combinational level are considered.

- 2. Create a new fault list according to the *Z01X* format, where a single transient fault (bit flip) is injected multiple times on the output of each primitive for the duration of one clock cycle.

- 3. Simulate the faults on the target *Top Level netlist* monitoring POs only. The top level .vcde file is needed for this fault simulation.

- 4. **Post-process the output reports** in order to match detected faults with path delay faults.

In algorithm 2 it is reported the pseudo-code of the algorithm.

#### Algorithm 2 Sequential simulation

$prim\_list \Leftarrow get\_prim(Top\_Level\_Netlist)$   $timing\_list \Leftarrow get\_timing(Report\_pattern\_file)$   $comb\_flist \Leftarrow read\_comb\_flist()$   $for \ fault \ in \ comb\_flist \ do$   $endp \Leftarrow prim\_list(fault.path())$   $inj\_times \Leftarrow timing\_list(fault.patterns())$   $seq\_flist \Leftarrow append\_transient\_fault(endp, inj\_times)$   $end \ for$   $sequential\_results \Leftarrow run\_simulation(seq\_flist)$  $comb\_flist \Leftarrow drop\_faults(sequential\_results.detected())$

# 4.6 Software tools integration

Since the flow expects to use such diverse tools and to perform many time-consuming operations, as already briefly said it was needed to automate the process through software integration.

This has been achieved by adopting scripting in Python language predominantly, mostly used when dealing with large files, complex data structures and process handling, but also in Bash language, used instead for text parsing and result analysis.

The advantage of the integration comes also in form of modularity and reconfigurability, allowing the user to skip some sections of the flow if needed, to change some process parameters very rapidly and to expand the flow fairly easy complying with different netlists and tools.

Reconfigurability has been achieved through the use of YAML files. The former is a human-readable data-serialization language which is widely used for writing configuration files and in other kind of applications. It is very well supported with dedicated libraries and packages by the most used programming languages [14].

Using Python, the module named PyYAML can be imported, which is a YAML parser and emitter.

Each phase of the flow can be managed as a separate thread, providing that it receives the right inputs from the other sections of the flow and on its turn gives the right outputs to the next ones. This is possible because a configuration file has been structured for each phase, in addition to a global one that serves the purpose of "master" configuration file.

To comply with the structure of the global configuration file it is needed to specify three fields for each phase:

- 1. **Enable**: by setting or clearing this flag it is possible to perform the job or skip it if not necessary.

- 2. **Run folder**: specifies which folder will be used as root folder for that specific tool, so as to have separate work-spaces for each of those.

- 3. Scripts: specify a list of commands or scripts to be launched for that specific phase of the flow. This allows not only to run tool scripts, but also user made scripts for post-processing or result analysis and eventually to expand the flow functionalities even further.

#### Algorithm 3 Root script

```

for flow_section in glob_set do

if flow_section.isenabled() then

section_var <= import_config(section_file)

curr_dir <= chdir(flow_section.run_dir())

env <= set_environ(section_var)

for script in flow_section.scripts() do

run(script)

end for

env_var <= unset_environ(section_var)

curr_dir <= chdir(root_dir)

end if

end for</pre>

```