# POLITECNICO DI TORINO

Master of Science in Electronic Engineering

Master Degree Thesis

## Implementation of a post-quantum cryptography algorithm on an FPGA board

Supervisor: prof. Guido Masera Candidate: Giuseppe PULETTO

**Co-Supervisor:** prof. Maurizio Martina

ACADEMIC YEAR 2019-2020

## Abstract

Cryptography (from Ancient Greek words *kryptós* and *graphein*, which together mean "secret writing") is the set of theory and techniques used to guarantee a secure communication between sender and receiver. A communication is secure if there is no risk for the message to reach an unwanted receiver.

Cryptography originates in the military, from the need to secretly communicate with allies. Coding the message, in such a way that it is no longer understandable for who does not have the key to decrypt it, solves the problem. In cryptography literature, the encrypted message is called ciphertext. Coding and decoding are the operations to obtain the cyphertext from the plaintext and vice versa.

The encryption algorithm has to be as robust as possible. The more robust it is, the more difficult it is to understand the key to decrypt the cyphertext.

Today, cryptography finds application everywhere. Electronic commerce, chip-based payment cards, digital currencies, computer passwords, implanted medical devices make use of it. This means that even devices with limited storage and poor computational capabilities must be able to code and decode information in a robust and fast way.

Modern cryptosystems make use of public key algorithms, which use a public key and a private key. As the name suggests, the public key is known to all and is used to encode the message. Instead, the private key is secret. Only the recipient, which needs to decrypt the message, owns it. Although these two keys are linked one each other, it is impossible to recover the private key knowing only the public one.

RSA is an example of public key cryptography. The security of this cryptosystem is based on the so-called "factoring problem". This operation is computationally not sustainable by a classical computer.

In 1994, the mathematician Peter Shor invented an algorithm, which is able to break this kind of cryptosystems if executed by an ideal quantum computer.

Studying and developing cryptosystems able to resist to quantum computer attacks is urgent and inevitable.

A candidate for "post-quantum cryptography" is *McEliece* cryptosystem. It is based on the practical difficulties of decoding a generic linear code. The original version of this algorithm uses binary Goppa codes

and requires to store in memory large matrices. This makes problematic encrypting and decrypting in embedded systems with limited hardware resources.

Variants that use LDPC or QCLDPC codes solve this problem. They require less memory and computational effort. One of them is the *LEDApkc* algorithm.

The decoding technique of LEDApkc is called *Q-Decoder*. The aim of this thesis is the creation of a prototype on fpga which implements a Q-Decoder together with a client-server model communication.

An encrypted message is sent via the Internet. It is coded according LEDApkc encryption algorithm. Once received, it is decrypted employing the Q-decoder decoding method. Therefore, both the sender and the recipient are hosts, that is, computers connected to a network.

The employed Q-decoder is similar to the one developed by Kristjane Koleci in the master thesis VLSI QC-LDPC Decoder for Post-Quantum Cryptography.

According to specifications, the prototype building requires an FPGA which has at least an Ethernet port. A built-in memory large enough to store information like message, private key, syndrome, correlation, etc. could maximize the decoder flexibility and minimize hardware resources usage and time consuming. The De1-Soc Board is a good compromise and the programmable logic is enough to implement the Q-Decoder.

The whole prototype is built using VHDL as a hardware description language and the standard edition of  $Intel^{\textcircled{B}}$  Quartus Prime Design Software 16.0.

It is made up of two subsystems. The first is the HPS subsystem and includes the following IP components:

- an Hard Processor System;

- two FIFO memories to interface correctly the hard processor system with the decoder and vice versa;

- a phase locked loop for the clock inputs of the hard processor system and fifos input or output ports.

The second is in the FPGA block of the DE1-SoC and contains:

- the Q-decoder;

- the 64 MB SDRAM available in the fpga block;

- a sdram controller for the 64 MB SDRAM;

- a phase locked loop for the clock inputs of the sdram controller and fifos input or output ports;

- a parallel Input/Output component used by the HPS to start the decoding of the cyphertext.

The PLLs of the two subsystems share the reference clock of 50.0 MHz, which is the output of a clock source block.

First, the encrypted message is sent from client to server via the Ethernet. The communication between these two nodes of the network is established using the so called socket programming. This means that the two hosts run two different parts of a distributed application, that is written in C language. The server host is the hard processor system.

Once the encrypted message is received, the hps writes it, together with the private key and the transposed private key, on a fifo. Once written, they are read and stored in the SDRAM by one of the units which compose the Q-decoder.

Finally, the decoding process starts. The syndrome, that is the product of the message and the transposed private key, is computed, adjusted and written in memory. Also the correlation, which is obtained multiplying the syndrome by the private key, is stored in SDRAM. From the correlation and syndrome weight, the bits to flip in the message are found. Toggling them, the message is updated. The decoding process is an iterative algorithm. It ends when the syndrome weight is equal to zero or a maximum number of iterations is reached.

In terms of occupied resources, the Q-decoder uses the 7 % of ALMs, the 43% of pins, the 10 % of block memory bits and two out of six PLLs.

In terms of performances, the bottleneck is represented by the 64 MB SDRAM, which allows a clock signal of frequency equal or less than 143.0 MHz.

Desidero ringraziare innanzitutto il mio relatore, il Professore Guido Masera, per avermi dato la possibilità di avvicinarmi e appassionarmi a questo argomento.

Ringrazio i miei genitori, senza i quali nulla di tutto questo sarebbe mai stato possibile.

Ringrazio mia sorella, che da sempre per me è stata esempio di tenacia, forza e vita.

Ringrazio Carmelo, Davide, Giuseppe, Luca e Tommaso, che ogni giorno mi hanno regalato un sorriso diverso.

Infine ringrazio tutti quelli che in un modo o nell'altro hanno reso più leggeri questi anni di università, amici e colleghi, siete tanti e non riesco a nominarvi tutti, ma vi assicuro che vi porterò per sempre con me.

A mio padre e mia madre.

## Contents

| A۱ | bstra                                   | ct i                                                                                                 |

|----|-----------------------------------------|------------------------------------------------------------------------------------------------------|

| 1  | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4 | oduction1McEliece Cryptosystem1LEDApkc Cryptosystem2Prototype specifications3The choice of the FPGA4 |

| 2  | The                                     | prototype system IP blocks 6                                                                         |

|    | 2.1                                     | A general overview of the whole system                                                               |

|    | 2.2                                     | About Qsys system integration tool                                                                   |

|    | 2.3                                     | The HPS subsystem                                                                                    |

|    |                                         | 2.3.1 Advanced Extensible Interface bridges 8                                                        |

|    |                                         | 2.3.2 Avalon FIFO memories                                                                           |

|    |                                         | 2.3.3 SDRAM controller                                                                               |

|    |                                         | 2.3.4 Parallel Input\Ouput component 13                                                              |

|    |                                         | 2.3.5 Clock Sources and phase locked loops 13                                                        |

|    |                                         | 2.3.6 Reset signals                                                                                  |

|    | 2.4                                     | The Qsys design                                                                                      |

| 3  | $\mathbf{Eth}$                          | ernet client-server model 16                                                                         |

|    | 3.1                                     | Socket programming 16                                                                                |

|    |                                         | 3.1.1 Server steps                                                                                   |

|    |                                         | 3.1.2 Client steps                                                                                   |

|    | 3.2                                     | The client-server computer program                                                                   |

|    |                                         | 3.2.1 server_fpga.c                                                                                  |

|    |                                         | 3.2.2 client_server.c                                                                                |

|    |                                         | 3.2.3 common_functions.c                                                                             |

|    |                                         | $3.2.4$ common_function.h                                                                            |

|    | 3.3                                     | Makefile                                                                                             |

| 4  | Q-d                                     | ecoder architecture 24                                                                               |

|    | 4.1                                     | QsysSubsystem                                                                                        |

|    | 4.2                                     | WritingSDRAM                                                                                         |

|    |                                         | 4.2.1 WritingSDRAM_CU                                                                                |

|    |                                         | 4.2.2 WritingSDRAM_DP                                                                                |

|    | 4.3                                     | SyndromeCMP                                                                                          |

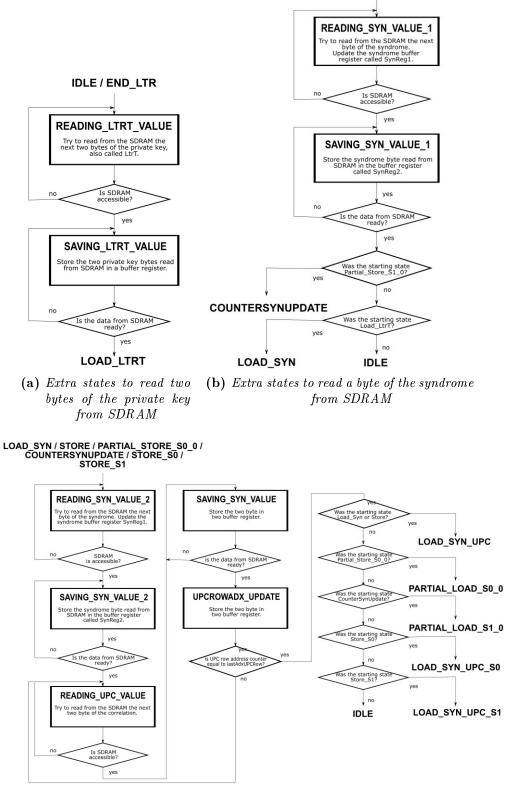

|      | 4.3.1 CU_VectorByCirculant                                | 0 |

|------|-----------------------------------------------------------|---|

|      | 4.3.2 DP_VectorByCirculant                                | 4 |

| 4.4  |                                                           | 4 |

|      | 4.4.1 CU_SyndromeAdjust_and_Weight                        | 4 |

|      | 4.4.2 DP_SyndromeAdjust_and_Weight                        | 6 |

| 4.5  |                                                           | 6 |

|      | 4.5.1 CU_VectorByCirculantInteger                         | 6 |

|      |                                                           | 1 |

| 4.6  |                                                           | 1 |

|      |                                                           | 1 |

|      |                                                           | 2 |

| 4.7  |                                                           | 2 |

| 4.8  |                                                           | 2 |

|      | $4.8.1  CU\_VectorPosFlip  \dots  \dots  \dots  \dots  4$ | 2 |

|      |                                                           | 4 |

| 4.9  |                                                           | 4 |

|      |                                                           | 4 |

|      |                                                           | 6 |

| 4.10 |                                                           | 7 |

| 4.11 |                                                           | 7 |

| 4.12 |                                                           | 8 |

| C    |                                                           | ~ |

#### **5** Conclusions

50

# List of Figures

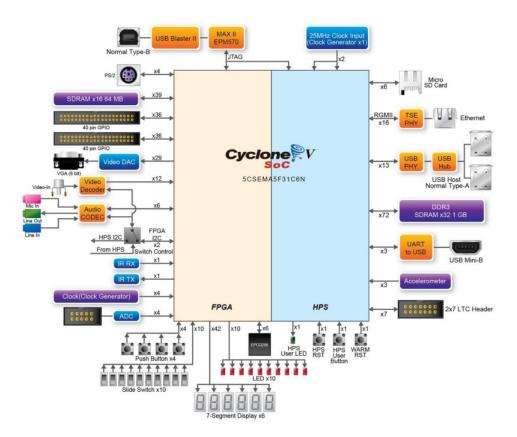

| 1.1  | DE1-Soc block diagram                                            | 5  |

|------|------------------------------------------------------------------|----|

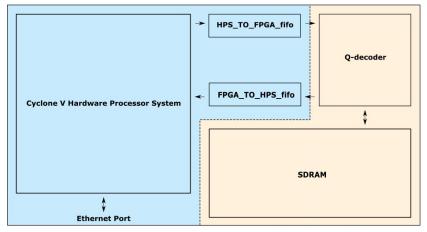

| 2.1  | Prototype system                                                 | 7  |

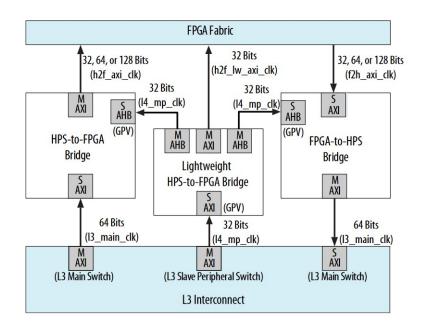

| 2.2  | AXI interfaces                                                   | 9  |

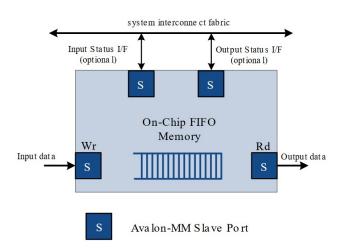

| 2.3  | Avalon-MM write slave to Avalon-MM read slave                    | 10 |

| 2.4  | SDRAM controller block diagram                                   | 11 |

| 2.5  | Avalon-MM read and write requests with <i>waitrequest</i> signal | 13 |

| 2.6  | Qsys design - FPGA IP components                                 | 15 |

| 2.7  | Qsys design - HPS IP components                                  | 15 |

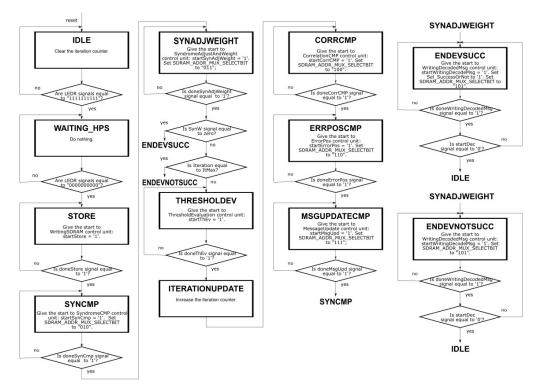

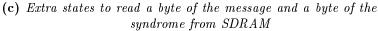

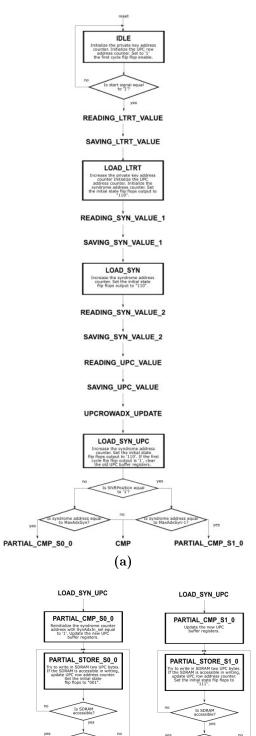

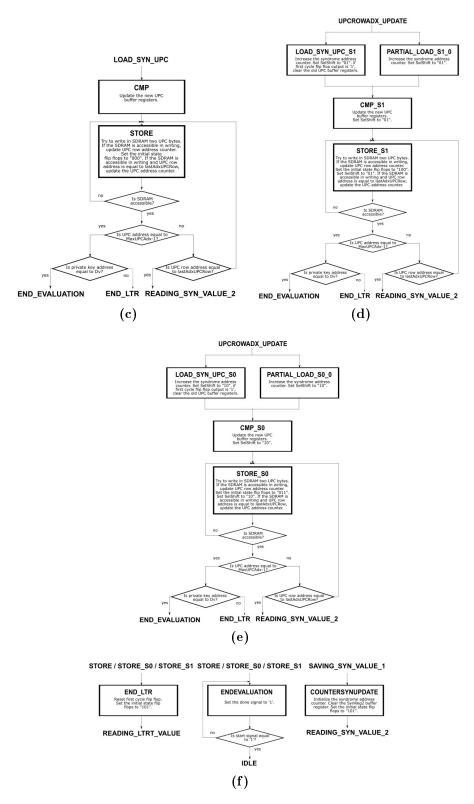

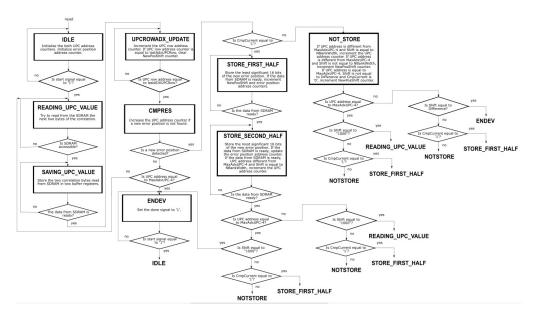

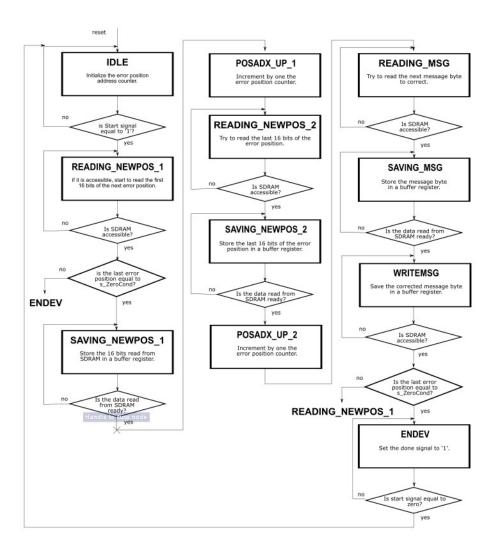

| 4.1  | Q-decoder control unit                                           | 25 |

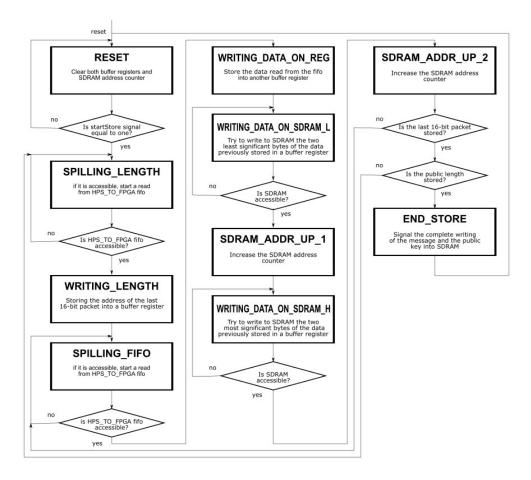

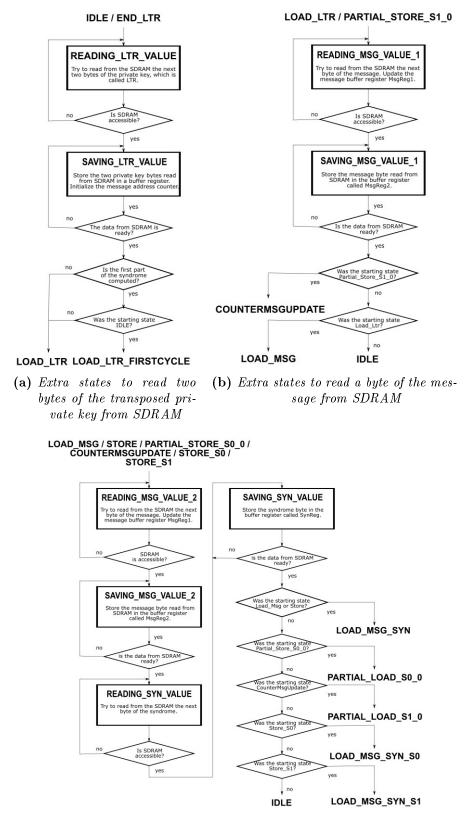

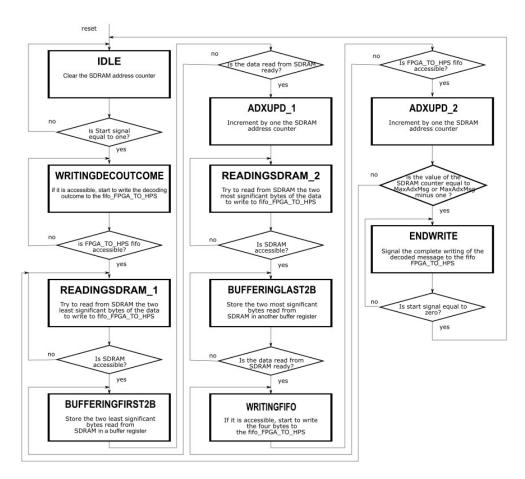

| 4.2  | WritingSDRAM control unit flowchart                              | 27 |

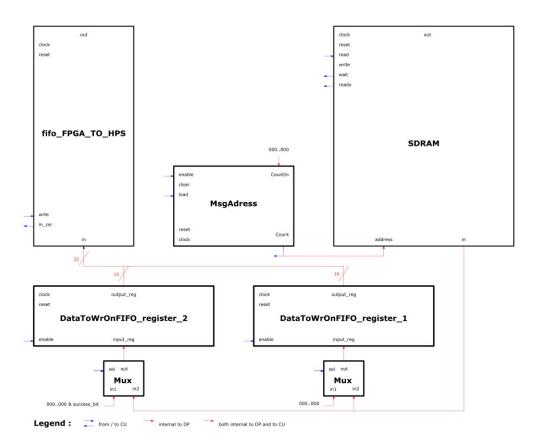

| 4.3  | WritingSDRAM datapath schematic                                  | 29 |

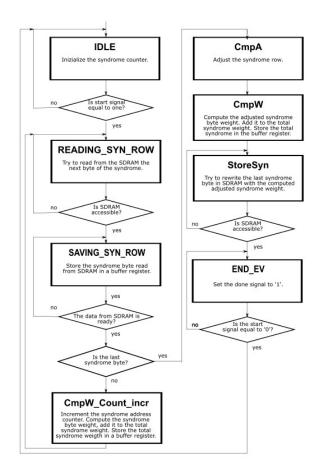

| 4.4  | VectorByCirculant control unit extra states                      | 31 |

| 4.5  | VectorByCirculant control unit                                   | 33 |

| 4.6  | WritingDecodedMsg control unit flowchart                         | 35 |

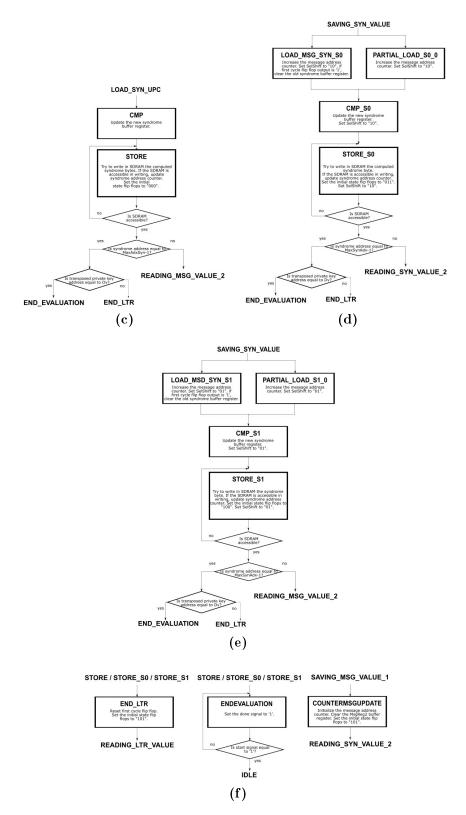

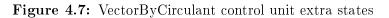

| 4.7  | VectorByCirculant control unit extra states                      | 38 |

| 4.8  | VectorByCirculantInteger control unit                            | 40 |

| 4.9  | ThresholdPos control unit flowchart                              | 42 |

| 4.10 | VectorByPos control unit flowchart                               | 43 |

| 4.11 | WritingDecodedMsg control unit flowchart                         | 45 |

| 4.12 | WritingDecodedMsg datapath schematic                             | 47 |

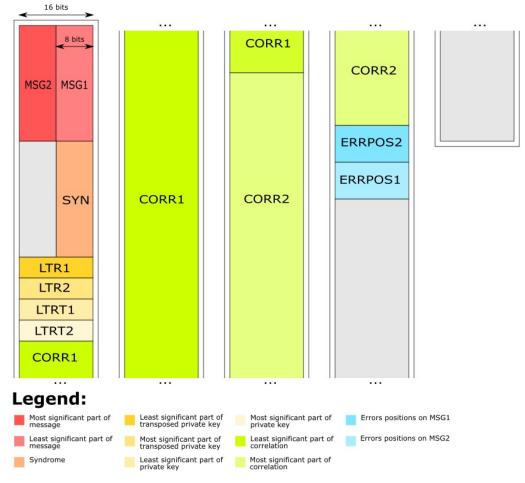

| 4.13 | SDRAM memory mapping                                             | 48 |

### Introduction

The LEDApkc Public Key Cryptosystem is the variant of MCEllie Cryptosystem for QC-LDPC codes.

#### 1.1 | McEliece Cryptosystem

The McEliece Cryptosystem takes its name from Robert J. McEliece, its inventor. The original version uses as secret codes irreducible Goppa codes, but the algorithm behind it can be generalized to other types of codes. It is an asymmetric encryption algorithm and this means that the message is coded employing a Public Key and decrypted through a Secret Key.

Let us suppose that the sender wish to transmit a message m through an insecure channel to the intended recipient. In cryptography literature, the sender is usually called *Alice*, the intended *Bob* and the adversary *Eve*. Alice and Bob derive their names from the first two letters of the alphabet, A and B, that are commonly used to mark the starting and ending point of a communication channel, a journey etc. Eve comes from eavesdropper.

Key generation and encryption. Let us imagine m as a vector  $1 \times k$ . First of all, in McEliece cryptosystem, Alice searches and finds Bob's Public Key G', a matrix  $k \times n$ . G' is a public key, so it is accessible for everyone, including Eve. Then she encrypts m, multiplying it by the matrix G and adding to the result  $\mathbf{e}$ , a random binary vector  $1 \times n$  with weight t arbitrarily generated by Alice itself:

$$x = m \times G' + e$$

x is the ciphertext, the encrypted version of the message m. Once obtained x from m, Alice can send x to Bob through the channel.

Alice and Eve have the public key G', but not the secret key. Only Bob has access to it. The private key is more than a simple matrix. The public key G' is linked to the private key, but it is impossible from G' going back to the private key. Bob generates the two keys, choosing randomly a secret binary block code C(n,k), with n as codeword length, k as information word length and a  $k \times n$  Generator matrix G. G is able to correct a number of errors less or equal than t. The relationship between G and G' is the following:

$$G' = S \times G \times P$$

**S** is a dense  $k \times k$  non singular binary scrambling matrix, P a  $n \times n$  permutation matrix. G, S and P forms together the secret key.

**Decryption.** Once received x, Bob can recover first x' multiplying x by P and then m exploiting the relationship between x' and it m:

$$x' = m \times S \times G + e \times P^{-1}$$

#### 1.2 LEDApkc Cryptosystem

The LEDApkc algorithm differs from the McEliece one because uses as secret codes non-algebraic QC-LDPC codes, the public code and the private one are neither coincident or equivalent and employs non-boundeddistance decoding algorithms.

**Key generation.** Two matrices, H and Q, form the secret key. H is a parity check-matrix made of  $r_0 \times n_0$ ,  $p \times p$  circulant blocks. Q is a transformation matrix made of  $n_0 \times n_0$ ,  $p \times p$  circulant blocks. Starting from H and Q, the matrices L and M are computed:

$$L = H \times Q = [L_0|L_1|...|L_{n_0-1}]$$

$$M = L_{n_0-1}^{-1} \times L = [M_0|M_1|...|M_{n_0-2}|I_p] = [M_l|I_p]$$

where  $I_p$  is the  $p \times p$  identity matrix, while  $M_l$  the public key.

**Encryption function.** Starting from the public key  $M_l$ , a matrix G' is computed as:

$$G' = [I_k | M_l^T]$$

where  $I_k$  is the  $k \times k$  identity matrix. Also a binary error vector  $1 \times pn_0$  with a Hamming weight t is generated. The message m is a binary vector  $1 \times p(n_0 - 1)$ . Once found G' and e, Alice can encrypt m as follows:

$$x = m \times G' + e$$

where x is the ciphertext.

**Decryption function.** Knowing H and Q, Bob computes the syndrome of the message, a binary  $p \times 1$  vector from x:

$$s^T = (H \times Q) \times x^T$$

From s, it is possible to recover e remembering that:

$$(H \times Q) \times G'^T \times m^T = 0_{p \times p(n_0 - 1)} \times u^T = 0_{p \times 1}$$

As a consequence:

$$s^{T} = (H \times Q) \times x^{T} = (H \times Q) \times (m \times G' + e)^{T} = (H \times Q) \times e^{T} = H \times (e \times Q^{T})^{T}$$

Found e, Bob recovers m from:

$$x + e = u \times [I_k | M_l^T]$$

**Q** decoder. There are several ways to recover the message m starting from the syndrome s.

The most efficient method is the one called Q-decoder. It is an iterative bit flipping algorithm with a lookup-table to reduce the number of iterations. Since it uses the transpose of matrix Q to estimate the error vector e, it is able to exploit the utmost correction power of QC-LDPC codes. This explains its remarkable efficiency and its name.

From the message m and private key Ł, that contains  $n_0$  circulant blocks, Bob finds the syndrome s. In the Kristjane Koleci's LEDA architecture,  $n_0$  is equal to 2 and each circulant block is a  $p \times p$  matrix, where p is 15013. Therefore, m is a  $1 \times n_0 * p$ , while L is a  $p \times n_0 * p$ . To compute the syndrome:

$$m \times L^T = \begin{bmatrix} m_0 & m_1 \end{bmatrix} \begin{bmatrix} L_0 \\ L_1 \end{bmatrix} = \begin{bmatrix} m_0 * L_0 \\ m_1 * L_1 \end{bmatrix} = \begin{bmatrix} s_0 \\ s_1 \end{bmatrix} = s^T$$

From s and L, the correlation UPC is evaluated:

$$s \times L = s \begin{bmatrix} L_0 & L_1 \end{bmatrix} = \begin{bmatrix} s * L_0 & s * L_1 \end{bmatrix} = UPC$$

From the syndrome weight and a proper lookup table, that derives from the chosen LEDA architecture parameters, the threshold is computed. Then, the errors positions are found subtracting each byte to the threshold. Indeed, if the correlation byte, which is related to a specific bit in the message, is higher than the threshold, the position of the bit is saved. The bit is marked as an error.

Finally, the message is updated flipping all its wrong bits.

The whole process is repeated until there are no more errors or the maximum number of iterations is reached. If no more errors remain, the decoding process ended successfully, otherwise, it failed.

#### **1.3** | Prototype specifications

The prototype is built following the guidelines described below.

- The idea is to set up a client-server model communication. An encrypted message has to be sent via the Internet. It is coded according LEDApkc encryption algorithm. Once received, it has to be decrypted employing the Q-decoder decoding method. Therefore, both the sender and the recipient have to be hosts, that is, computers connected to a network.

- The main design efforts should be spent on the Q-Decoder implementation rather than the client-server Ethernet communication.

- The decoder has to be implemented on an fpga and be as similar as possible to the one developed by Kristjane Koleci in the master thesis VLSI QC-LDPC Decoder for Post-Quantum Cryptography.

- The prototype must be as small and fast as possible in terms of occupied hardware resources and time consuming.

- The system must be flexible to a further implementation based on the red/black concept. In cryptosystems, the red/black architecture segregates carefully the black signals from the red ones. The first are the ones who carry the cyphertext, the others who carry the plaintext.

#### 1.4 | The choice of the FPGA

According to specifications, the prototype building requires an FPGA which has at least an Ethernet port. A built-in memory large enough to store information like message, private key, syndrome, correlation, etc. could maximize the decoder flexibility and minimize hardware resources usage and time consuming.

Keeping in mind the Q-decoder needs, the De1-Soc Board seems to be a good compromise. The programmable logic is enough to implement the Q-Decoder. This could be easily verified using tools like Intel Quartus Prime Design Software. These tools give the possibility to compile a VHDL project for a specific hardware programmable board. The VHDL project used id the one built by Kristjane Koleci and described in her master thesis. Furthermore The fpga integrates an ARM-based hard processor system consisting of processor, peripherals and memory interfaces. Its equipment includes an Ethernet networking and a 64MB SDRAM. 64 MB are more than enough to store the Q-decoder information. Having such a big memory also means space for further decoder improvements that could require more information to store.

The block diagram of the board is shown in figure 1.1. The picture is taken from the tutorial material offered by Altera.

Figure 1.1: DE1-Soc block diagram

The Ethernet physical layer with RJ45 connector can transmit Ethernet frames at a rate of a gigabit per second. It is located in the Hard Processor System block of the DE1-Soc board. Unfortunately, there is no direct connection between the Ethernet connector and the FPGA block. This forces to instantiate in the prototype a minimal HPS which allows the programmable logic to receive and send information via Ethernet. However, not all evils come to harm. A hard processor system could significantly reduce the design efforts on implementing a well working and robust Ethernet communication. The idea is to exploit the power of the 800 MHz Dual-core ARM Cortex-A9 MPCore processor to run a simple C program which receives and send information via Ethernet. Thanks to HPS interfaces towards the FPGA region, the information can be transferred in the 64 MB SDRAM. Once stored in the SDRAM, they are accessible at occurrence by the Q-decoder. The hard processor system also guarantees flexibility and leaves space for further and powerful decoder improvements.

# The prototype system IP blocks

#### 2.1 A general overview of the whole system

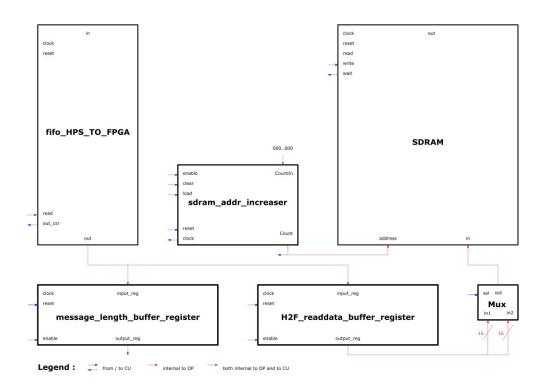

The prototype system is made up of two subsystems. The first is the HPS subsystem and includes the following IP components:

- the Arria V/Cyclone Hard Processor System, in the Qsys design called *ARM\_A9\_HPS*;

- two Avalon FIFO memories to interface correctly the hard processor system with the decoder and vice versa, in the Qsys design named as *FPGA\_to\_HPS\_fifo* and *HPS\_to\_FPGA\_fifo*;

- a phase locked loop for the clock inputs of the hard processor system, the HPS\_TO\_FPGA fifo input port and FPGA\_TO\_HPS fifo output port, in the Qsys design known as *HPS\_pll*;

The second is in the FPGA block of the DE1-SoC and contains:

- the Q-decoder;

- the 64 MB SDRAM available in the fpga block;

- a sdram controller for the 64 MB SDRAM, in the Qsys design renamed as *FPGA\_sdram\_controller*;

- a phase locked loop for the clock inputs of the sdram controller, in the Qsys system called *FPGA\_pll*, the HPS\_TO\_FPGA fifo output port and FPGA\_TO\_HPS fifo input port;

- a PIO, a parallel Input/Output component, in the Qsys design known as *LEDR\_pio*, used for debug purposes and by the HPS to start the decoding of the cyphertext;

The PLLs of the two subsystems share the reference clock of 50.0 MHz, which is the output of

• the clock source block, in the Qsys design renamed as *ref\_clock\_block*.

Figure 2.1 shows a block diagram of the whole prototype system.

Legend: 🔲 HPS subsystem 📃 FPGA subsystem

Figure 2.1: Prototype system

The whole prototype is built using VHDL as a hardware description language and the standard edition of  $Intel^{\textcircled{R}}$  Quartus Prime Design Software 16.0.

#### 2.2 About Qsys system integration tool

Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Software Suite includes a system integration tool called Qsys or Platform Designer. Qsys is the best and fastest way to use intellectual (IP) functions and subsystems. Indeed, using this software component, the user can instantiate all the IP blocks available in the chosen FPGA board. The tool also generates automatically the interconnect logic between the used components, saving design time and improving productivity.

To use Qsys, it is enough following the Qsys System Design Tutorial offered by Intel. To summarize:

- 1. in the Quartus Prime Design Software Suite, click Tools > Qsys to create a new Qsys design; the Qsys window appears and in the tab called *System Contents* a first component is already instantiated; it is the clock source  $clk_0$ ;

- 2. to add a new component, use the IP catalog tab to find a suitable IP function or subsystem and click Add;

- 3. to edit the properties of an IP block, double click on it to open the *Parameters* tab;

- 4. to rename or connect the IP blocks use the *System Contents* tab; this tab also shows the components HPS base and end addresses;

- 5. click *Generate HDL* to generate the Qsys system; it is possible choosing the HDL in which the system will be generated; the command *Generate* > *Show Instantiation Template* shows how to integrate the Qsys system with the rest of the HDL code;

- 6. click *Finish* to close the Qsys window.

#### 2.3 The HPS subsystem

The hard processor system available in the DE1-SoC board is the Cortex-A9 microprocessor unit (MPU)subsystem. It includes a 32-bit dual-core processor, a level 2 (L2) cache, an Accelerator Coherency Port ID mapper and debugging modules. The 32-bit dual-core processor is the Cortex-A9 MPCore. It is composed of two instantiation of the ARM Cortex-A9 processor. It also includes other modules: watchdog and private internal timers for each core, a global timer, a generic interrupt controller, a Snoop Control Unit and an Accelerator Coherency Port.

#### 2.3.1 Advanced Extensible Interface bridges

The HPS is connected to the FPGA fabric through a dedicated interface. It is the Advanced Extensible Interface which is also known as AXI bridge. There is a bridge to go from the HPS to the FPGA and another one for the vice versa. The first is the FPGA-TO-HPS bridge, the second the HPS-TO-FPGA bridge. These two interfaces are data width configurable: 32, 64 or 128 bits. They also manage data width conversion, clock crossing, buffering. In other words, they give all the tools to have access to HPS slaves from FPGA fabric and vice versa. There are also available lower performance AXI interfaces. They are called Lightweight FPGA-TO-HPS and FPGA-TO-HPS bridges. Their data width is fixed and equal to 32-bit and are useful for low-bandwidth traffic.

Picture 2.2 is taken from the embedded IP user guide offered by Intel and shows how AXI bridges connect FPGA fabric with HPS logic and vice versa. It also shows, in parenthesis, their clock domains.

Figure 2.2: AXI interfaces

According to prototype specifications, the system must be as fast as possible. To achieve the best performances both lightweight and fast AXI interfaces are used. Indeed the former could be used to divert part of the traffic from the latter, improving the overall performance of the system. Therefore, the lightweight bridges carry the following signals:

- the control status register signals of the input port of HPS-TO-FPGA fifo;

- the control status register signals of the output port of FPGA-TO-HPS fifo;

- the signals at the input of the parallel input \output called LEDR\_pio.

The high-performance AXI interfaces transport big data like message or secret key. These connections are specified through the *System Contents* tab of Qsys.

#### 2.3.2 Avalon FIFO memories

To buffer data and control the data flow in the Qsys system two on-chip FIFO memory core are instantiated. One, called HPS\_TO\_FPGA\_fifo, manages the traffic between the HPS logic and the FPGA fabric. The other, called FPGA\_TO\_HPS\_fifo does the same thing, but with the data from FPGA to HPS.

The two fifos help to guarantee design flexibility and an efficient data transport. Indeed, these memories can operate with a single clock, but also with separate clocks for input and output ports. The input interface

may be an Avalon Memory Mapped write slave or an Avalon Streaming sink, while the output one an Avalon Memory Mapped read slave or an Avalon Streaming source. Whatever configuration is chosen, the first data that arrives at the input is also the first data to be delivered to the output. Both in single and dual clock-mode, there is an optional interface called status interface which provides information about the state of the memory. For example, a *waitrequest* signal is asserted or not according to the fifo fill level. For write operations, it is asserted when the memory is full, while it is deasserted if there is enough space to store data. For read operations, it is asserted when the memory is empty, while it is deasserted when there is at least one data to read.

Since there is no need to use them for streaming data, both the two fifos are configured as Avalon Memory Mapped write slave to Avalon Memory Mapped read slave. In this mode, an Avalon-MM write master stores data into the memory by writing to the input port, and an Avalon-MM read master pops data out the memory by reading from its output port.

Figure 2.3: Avalon-MM write slave to Avalon-MM read slave

Picture 2.3 is taken from the embedded IP user guide offered by Intel and is a summary of a FIFO configured as Avalon-MM write slave to Avalon-MM read slave.

Since the HPS logic and the FPGA fabric may live in different clock domains, a wise choice is using the two memories with separate clocks for input and output. This choice also affects the status signals of the two ports.

The two fifos have depth equal to 8192, while their width is 32 bits. If necessary, both depth and width can be changed.

As mentioned above, the status interface for both input and output is optional: it can be included or not. In the Qsys system, they are present for both input and output for both fifos.

#### 2.3.3 SDRAM controller

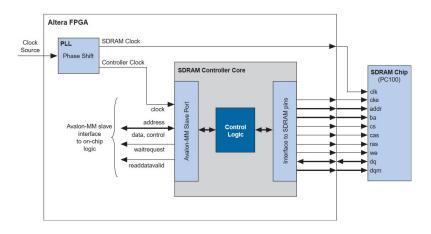

To connect easily the 64 MB SDRAM in the Qsys system a SDRAM controller is used. The SDRAM controller helps to reduce design time and efforts. Indeed, it handles all SDRAM protocol requirements. It has an Avalon Memory Mapped Interface to off-chip SDRAM and guarantees access to SDRAM with various sizes, widths and multiple chip selects. The Avalon-MM interface also allows pipelined read operations.

To handle correctly read and write operations, the SDRAM controller configuration has to match the one of the 64 MB SDRAM. Therefore, its clock frequency must match the SDRAM one. Also, address, data and control signals on SDRAM pins have to be stable when a clock edge arrives. A PLL may be useful to reduce clock skew between the controller and the SDRAM. If at low frequencies the PLL may be unnecessary, at high ones it is the only way to ensure stability of the signals at the SDRAM pins at the clock edge. For example, the PLL may add a phase shift to the SDRAM clock so that when the edge arrives the signals from the controller are already stable.

Figure 2.4 is taken from embedded IP user guide offered by Intel and shows the SDRAM controller and how it may be integrated with an SDRAM.

Figure 2.4: SDRAM controller block diagram

After opening the Qsys windows, an SDRAM controller can be chosen from the IP catalog and added to the system. Clicking on it, its configuration window appears. It has two tabs: the first is the *Memory Profile*, the second the *Timing*.

In the *Memory Profile* page it is possible configuring the data width, architecture and the address width of the memory to control. According

to the datasheet of 64 MB SDRAM, the data width is set to 16 bits, the number of chip selects to 1, the number of the banks to 4, the address row and column width respectively to 13 and 10.

In the *Timing* page it is possible choosing the right timing parameters for the controller. According to the SDRAM datasheet, the number of CAS latency cycles is set to 3, the initialization ones to 2. The CAS latency tells how many clock cycles there are from a read command to data out. The initialization refresh cycles are the refresh cycles the SDRAM controller performs as part of the initialization sequence after reset. The other SDRAM controller timing parameters are:

- how often the SDRAM controller refreshes the SDRAM (7.8  $\mu$ s);

- the delay after power up and before SDRAM initialization (100.0  $\mu$ s);

- how long is the refresh command (70.0 ns);

- how long is the precharge command (15.0 ns);

- ACTIVE to READ or WRITE delay (15.0 ns);

- access time, which depends on CAS latency (5.5 ns);

- write recovery time for precharge commands (14.0 ns).

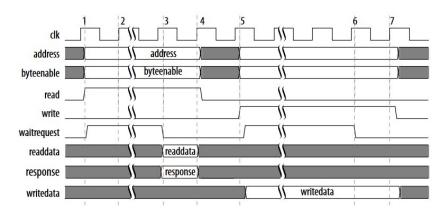

The Avalon Memory Mapped interface simplifies a lot read and write operations to the 64 MB SDRAM. It also allows the slave to stall whatever operation as many cycles as required by asserting the *waitrequest* signal. There is only one rule: if the slave uses this signal for either read or write transfers, it has to use the signal for both.

Typically signals like *address*, *read* or *write*, *writedata*, *byteenable* arrive before the rising clock edge. At this point the slave raises the *waitrequest* signal to hold off the subsequent transfers if there are any and to hold constant the signals just received. The transfer ends at the first rising clock edge after the slave interface deasserts the *waitrequest* signal. The slave can stall the communication how long it needs. Picture 2.5, taken from Avalon Interface Specifications offered by Intel, shows a timing diagram about read and write transfers with the *waitrequest* signal.

Figure 2.5: Avalon-MM read and write requests with *waitrequest* signal

#### 2.3.4 Parallel Input\Ouput component

The PIO core added to the Qsys design is used by the HPS to signal to the Q-decoder that the message and the private key are ready to be read from the HPS\_TO\_FPGA\_fifo.

The core provides an Avalon Memory Mapped interface between an Avalon-MM SLAVE port and general purpose I/O ports. In other words, this IP component offers easy I/O access to user logic or external devices when a simple "bit banging" approach is enough.

In the prototype the PIO core is used to control the red leds of the DE1-SoC board. Checking their state, on or off, the Q-decoder knows when the message and the private key are ready to be read from the HPS\_TO\_FPGA\_fifo.

Since, the red leds can be turned on or off also for debug purposes, the Qsys system controls all the ten red leds of the board. As a consequence, the width of the PIO core is set to 10 and its direction to Output. The reset value of the output ports is 0x000000000003ff.

#### 2.3.5 Clock Sources and phase locked loops

The Altera DE-series boards provides an on-board oscillator which generates a 50 MHz clock and this clock signal is connected to one or more pins usually called  $CLOCK_50$ ,  $CLOCK2_50$  and so on.

The Qsys system requires more than one clock with a frequency higher than 50 MHz and different phase shifts. Specific clocks can be generated with one or more PLLs.

Two PLLs are used and two different IP components are chosen. The first is an IP component called *Altera PLL*. The second belongs to the class of *System and SDRAM PLL* cores. The Altera PLL is more complex than the other and generates more than one clock signal, all for the FPGA part of the prototype. The System PLL is used to generate one clock signal shared by different IP components in the HPS block of the

Qsys design. Both take a reference clock signal of 50.0 MHz.

The System PLL generates a clock signal of 143.0 MHz, which is used as the clock input of all AXI bridges, the PIO component, the HPS\_TO\_FPGA fifo input port and FPGA\_TO\_HPS fifo output port.

The Altera PLL generates three 120 MHz clock signals: the first for the 64 MB SDRAM, the second for the SDRAM controller, the HPS\_TO\_FPGA fifo output port and FPGA\_TO\_HPS fifo input port, the third for the Q-decoder. The SDRAM clock signal has a phase shift of -52.0 degrees. This shift helps to reduce the clock skew between the memory and its controller. The other two clocks are almost identical. They have the same frequency and no phase shift. The only difference between the two is that the Q-decoder clock signal is exported, the other not. In Qsys exporting a signal is the only way to make it visible from the outside. Qsys allows to export both input and output signals.

If necessary, the chosen frequencies for the HPS and FPGA blocks can be changed. There is only one constraint: they have to be compatible with the Qsys IP components. For example, the 64 MB SDRAM allows a clock signal of frequency equal or less than 143.0 MHz.

#### 2.3.6 Reset signals

All the IP components share the same reset signals except for the Hard Processor System, which has its own and the fifos. About these two memories, the reset signal of both input and output ports is the OR between two reset signals: the one of the FPGA subsystem and the one of the AXI bridges.

#### 2.4 | The Qsys design

The final result is the Qsys design shown in figures 2.6 and 2.7. The first shows the FPGA subsystem, in the red square, the second the HPS one.

|                                         |                       | Louis access                    | Total Div                | - Average         | 1.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.0240 |

|-----------------------------------------|-----------------------|---------------------------------|--------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Connections                             | Name                  | Description                     | Export                   | Clock             | Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | End    |

|                                         | ref_clock_block       | Clock Source                    |                          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         | D- dk_in              | Clock Input                     | dk                       | exported          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         | D- clk_in_reset       | Reset Input                     | reset                    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         | clk                   | Clock Output                    | Double-click to export   | ref_clock_block   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         | clk_reset             | Reset Output                    | Double-click to export   |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         | E FPGA_pll            | Altera PLL                      |                          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 00000                                   |                       | Clock Input                     | Double-click to export   | ref_clock_block   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| • • •                                   |                       | Reset Input                     | Double-click to export   |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         |                       | Clock Output                    | outclk_pll_0_f0_no_shift | FPGA_pll_outdk0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         | outclk1               | Clock Output                    | Double-click to export   | FPGA_pll_outclk1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         | - outclk2             | Clock Output                    | outclk_pll_0_f0_shifted  | FPGA_pll_outclk2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         | FPGA_sdram_controller | SDRAM Controller                |                          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| +                                       |                       | Clock Input                     | Double-click to export   | FPGA_pll_outclk1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| • • • • • •                             |                       | Reset Input                     | Double-click to export   | [dk]              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| Q                                       | ○ D- s1               | Avalon Memory Mapped Slave      | sdram                    | [dk]              | at 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                         |                       | Conduit                         | wire                     |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|                                         | 回 喤 HPS_pll           | System and SDRAM Clocks for D   |                          |                   | and the second sec |        |