Master's Degree in Electronic Engineering

Master's Thesis

## Design of an OS compliant memory system for LEN5, a RISC-V Out of Order processor

Supervisor Maurizio Martina Candidate Matteo Perotti

Academic year 2018-2019

"Homo sum, humani nihil a me alienum puto." [Publio Terenzio Afro] Nor the processors.

#### Abstract

The design of a complex memory system for an Out Of Order processor can be very intriguing, especially if it should be able to support an Operating System. There is not much documentation about how to design it and how to deal with the problems that Virtual Memory can bring with itself: the goal of this work is to provide a possible practical implementation of a memory system, along with thoughts and information about all the related issues and possible solutions.

## Acknowledgements

I would like to thank Andrea Giannini and Maurizio Martina for their professional support. Moreover, I want to express my gratitude to Michele and Marco, who have shared with me this part of the journey.

Thank you Elisa, thank you "family".

# Contents

| Li                 | st of        | Tables                                           | VI            |  |

|--------------------|--------------|--------------------------------------------------|---------------|--|

| List of Figures VI |              |                                                  |               |  |

| 1                  | Intr<br>1.1  | roduction<br>Motivations                         | 1<br>1        |  |

|                    | $1.1 \\ 1.2$ | Thesis organization                              | $\frac{1}{2}$ |  |

| <b>2</b>           | Bac          | kground                                          | 5             |  |

|                    | 2.1          | Processors                                       | 5             |  |

|                    |              | 2.1.1 Basic concepts                             | 6             |  |

|                    |              | 2.1.2 What matters? The main fundamental metrics | 7             |  |

|                    |              | 2.1.3 Advanced issues and techniques             | 12            |  |

|                    | 2.2          | The Memory System                                | 13            |  |

|                    |              | 2.2.1 The interface between CPU and Memory       | 13            |  |

|                    |              | 2.2.2 The Memory Hierarchy                       | 13            |  |

|                    |              | 2.2.3 Von Neumann vs Harvard architectures       | 15            |  |

|                    |              | 2.2.4 Caches                                     | 15            |  |

|                    | 2.3          | Virtual Memory                                   | 24            |  |

|                    |              | 2.3.1 The modified Memory Hierarchy              | 24            |  |

|                    |              | 2.3.2 How does it work                           | 25            |  |

|                    |              | 2.3.3 The TLB                                    | 27            |  |

|                    |              | 2.3.4 Modern Hardware for Virtual Memory         | 28            |  |

|                    |              | 2.3.5 Memory System, Speculation and Exceptions  | 37            |  |

|                    |              | 2.3.6 Different TLB-Cache organizations          | 37            |  |

|                    |              | 2.3.7 Homonyms and Synonyms                      | 40            |  |

| 3                  | The          | e RISC-V ISA                                     | 43            |  |

| J                  | 3.1          | Peculiarities                                    | 43            |  |

|                    | 3.1<br>3.2   | The core set                                     | 43<br>44      |  |

|                    | 0.2          | 3.2.1       Privilege Modes                      | 44            |  |

|                    | 3.3          | Memory System specifications                     | 45            |  |

|                    | ა.ა          | 3.3.1 Load/Store                                 | $45 \\ 45$    |  |

|                    |              | 3.3.2 Memory Model                               | 45<br>46      |  |

|                    |              |                                                  | 40<br>46      |  |

|                    |              | 3.3.3 Virtual Memory                             | 40            |  |

| 4        | The  | LEN5 core 53                                                                                                                                                      |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.1  | Front end                                                                                                                                                         |

|          | 4.2  | Back end                                                                                                                                                          |

|          |      | 4.2.1 The Load/Store Queue $\ldots \ldots \ldots$ |

|          |      | 4.2.2 Replay using a Wake-Up signal                                                                                                                               |

|          |      | 4.2.3 Support for partial Load and Store                                                                                                                          |

| <b>5</b> | The  | LEN5 Memory System 57                                                                                                                                             |

| 0        | Inc  | 5.0.1 The Virtual Memory                                                                                                                                          |

|          |      | 5.0.2 The handshake protocol                                                                                                                                      |

|          |      | 5.0.3 SystemVerilog description                                                                                                                                   |

|          | 5.1  | L1 i-Cache                                                                                                                                                        |

|          | 0.1  | 5.1.1 Requirements and constraints                                                                                                                                |

|          |      | $5.1.2$ Design Choices $\ldots$ $63$                                                                                                                              |

|          |      | $5.1.3$ Design $\ldots$ $64$                                                                                                                                      |

|          | 5.2  | L1 i-TLB                                                                                                                                                          |

|          | 0.2  | 5.2.1 Requirements and constraints                                                                                                                                |

|          |      | 5.2.2 Design Choices                                                                                                                                              |

|          |      | 5.2.2 Design Choices                                                                                                                                              |

|          |      | 5.2.4 Further improvements                                                                                                                                        |

|          | 5.3  | L1 d-Cache                                                                                                                                                        |

|          | 0.0  | 5.3.1 Requirements and constraints                                                                                                                                |

|          |      | 5.3.2 Design Choices                                                                                                                                              |

|          |      | 5.3.3 Design                                                                                                                                                      |

|          |      | 5.3.4 Further improvements                                                                                                                                        |

|          | 5.4  | L1 d-TLB                                                                                                                                                          |

|          | 0.4  | 5.4.1 Requirements and constraints                                                                                                                                |

|          |      | 5.4.2 Design Choices                                                                                                                                              |

|          |      | 5.4.3 Design                                                                                                                                                      |

|          | 5.5  | TLB Arbiter         105                                                                                                                                           |

|          | 5.6  | L2 TLB                                                                                                                                                            |

|          | 5.0  | 5.6.1 Requirements and constraints                                                                                                                                |

|          |      | 5.6.2 Further improvements                                                                                                                                        |

|          | 5.7  | PTW                                                                                                                                                               |

|          | 0.1  | 5.7.1 Requirements and constraints                                                                                                                                |

|          |      | 5.7.2 Design Choices                                                                                                                                              |

|          |      | 5.7.2 Design Choices                                                                                                                                              |

|          |      | 5.7.4 Design                                                                                                                                                      |

|          | 5.8  | MMU Cache                                                                                                                                                         |

|          | 0.0  | 5.8.1 Requirements and constraints                                                                                                                                |

|          |      | 5.8.2 Design choices                                                                                                                                              |

|          |      | 5.8.3 Design                                                                                                                                                      |

|          |      | 5.8.4 Further Improvements                                                                                                                                        |

|          | 5.9  | $L_{2C}$ Arbiter $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $L_{24}$                                                                                            |

|          |      | L2C Arbiter                                                                                                                                                       |

|          | 0.10 | 5.10.1 Differences with the d-Cache                                                                                                                               |

|          |      | U.I.V.I DIMUTCHUES WITH THE $\mathbf{u}$ -Qaulle                                                                                                                  |

|    | 5.11           | Securi   | ty issues                                                                                                      | 127 |  |  |

|----|----------------|----------|----------------------------------------------------------------------------------------------------------------|-----|--|--|

| 6  | Ver            | ificatio | on and Synthesis                                                                                               | 129 |  |  |

|    | 6.1            | Verific  | ation                                                                                                          | 129 |  |  |

|    |                | 6.1.1    | Testbench organization                                                                                         | 129 |  |  |

|    |                | 6.1.2    | Memory emulation                                                                                               | 130 |  |  |

|    |                | 6.1.3    | L2 Cache Emulator                                                                                              | 130 |  |  |

|    |                | 6.1.4    | L2 Arbiter Testbench                                                                                           | 131 |  |  |

|    |                | 6.1.5    | i-Cache Testbench                                                                                              | 131 |  |  |

|    |                | 6.1.6    | d-Cache Testbench $\ldots \ldots \ldots$ | 131 |  |  |

|    |                | 6.1.7    | Virtual Memory Testbench                                                                                       | 132 |  |  |

|    | 6.2            | Synthe   | esis                                                                                                           | 133 |  |  |

|    |                | 6.2.1    | Architecture part                                                                                              | 133 |  |  |

|    |                | 6.2.2    | Memory part                                                                                                    | 138 |  |  |

|    |                | 6.2.3    | Overall Design                                                                                                 | 139 |  |  |

| 7  | Fina           | al rem   | arks                                                                                                           | 141 |  |  |

|    | 7.1            | Result   | 8                                                                                                              | 141 |  |  |

|    | 7.2            |          | Steps                                                                                                          |     |  |  |

| 8  | App            | pendice  | es                                                                                                             | 145 |  |  |

| Bi | Bibliography 1 |          |                                                                                                                |     |  |  |

# List of Tables

| 6.1  | Partial synthesis results. "NC": NonCombinational. "C": Combinational.                                                           | 133 |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2  | Partial and total synthesis results. "NC": NonCombinational. "C": Combi-                                                         |     |

|      | national.                                                                                                                        | 134 |

| 6.3  | Main structures of the d-Cache <sup>1</sup> block $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 134 |

| 6.4  | How the d-Cache area varies in function of the entries of the $WBB^2$ and the                                                    |     |

|      | MSHR                                                                                                                             | 135 |

| 6.5  | Size in bits of the architectural blocks with storing function, realized using                                                   |     |

|      | registers                                                                                                                        | 135 |

| 6.6  | Partial timing results for the architectural part of the Memory System. The                                                      |     |

|      | reported "Slack" is the one of the <i>timing_report</i> , without 0.07 ns of clock                                               |     |

|      | uncertainty.                                                                                                                     | 136 |

| 6.7  | Final timing results for the architectural part of the Memory System. The                                                        |     |

|      | reported "Slack" is the one of the <i>timing_report</i> , without 0.07 ns of clock                                               |     |

|      | uncertainty.                                                                                                                     | 137 |

| 6.8  | Area of the memories of the LEN5 memory system, estimated with CACTI.                                                            | 138 |

| 6.9  | Cycle and Access time of the Direct Mapped blocks of the LEN5 Memory                                                             |     |

|      | System                                                                                                                           | 139 |

|      |                                                                                                                                  | 139 |

| 6.11 | Estimation of the total critical path of the Memory System                                                                       | 140 |

| 7.1  | Final area and timing estimation for the LEN5 memory system                                                                      | 141 |

|      |                                                                                                                                  |     |

$<sup>^{1}\</sup>mathrm{Data}$  Cache

$<sup>^2 \</sup>rm Write$  Back victim Buffer

# List of Figures

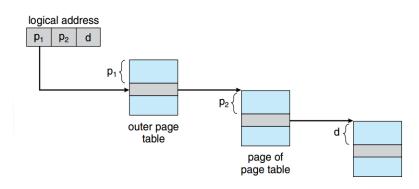

| 2.1  | A 32-bit vaddr for a 2-level page table. $(\text{from } [22]) \dots \dots$ |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | Address translation for a two-level 32-bit paging architecture. (from [22]) . 26                                                                                                 |

| 2.3  | A 64-bit vaddr for a 3-level page table. (from [22])                                                                                                                             |

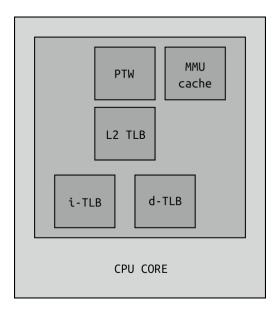

| 2.4  | Address translation hardware in modern computers                                                                                                                                 |

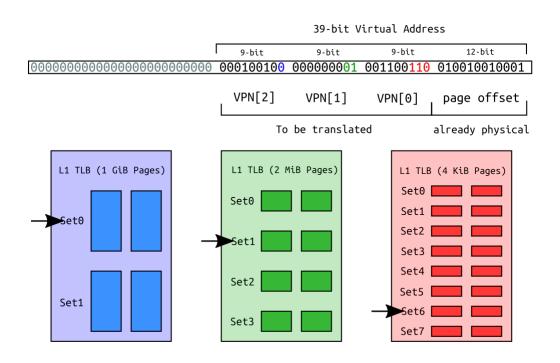

| 2.5  | Sv39 RISC-V parallel lookup for multiple page size TLBs. Index bits for                                                                                                          |

|      | different TLBs are highlighted in different colours                                                                                                                              |

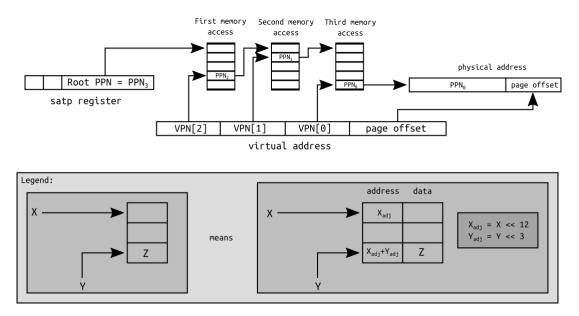

| 2.6  | Sv39 RISC-V page table walk                                                                                                                                                      |

| 2.7  | A possible Unified Page Table Cache, interpreted in Sv39 RISC-V key 34                                                                                                           |

| 2.8  | A possible Split Page Table Cache, interpreted in Sv39 RISC-V key                                                                                                                |

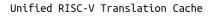

| 2.9  | A possible Unified Translation Cache, interpreted in Sv39 RISC-V key 35                                                                                                          |

| 2.10 | A possible Split Translation Cache, interpreted in Sv39 RISC-V key 35                                                                                                            |

| 2.11 | A possible Translation-Path Cache, interpreted in Sv39 RISC-V key                                                                                                                |

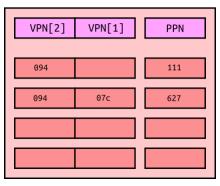

| 2.12 | Possible VIPT organization with "physical indexing" for an Sv39 RISC-                                                                                                            |

|      | V Processor. In the example the entire physical memory is limited to be                                                                                                          |

|      | addressable with 56 bits, the cache has 64 sets, the line size is 64 bytes (512                                                                                                  |

|      | bits) and the word size is 4 bytes (32 bits)                                                                                                                                     |

| 3.1  | satp register for Sv39 and Sv48 MODEs 47                                                                                                                                         |

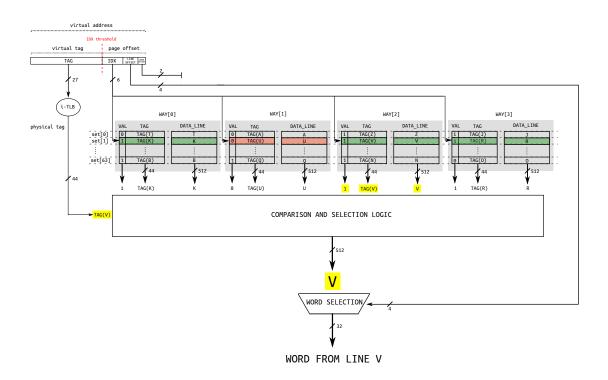

| 3.2  | Sv39 Virtual Address                                                                                                                                                             |

| 3.3  | Sv39 Physical Address                                                                                                                                                            |

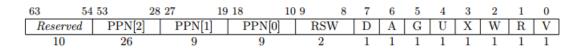

| 3.4  | Sv39 page table entry                                                                                                                                                            |

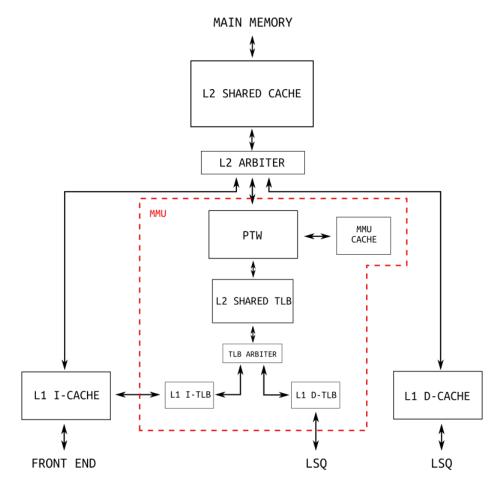

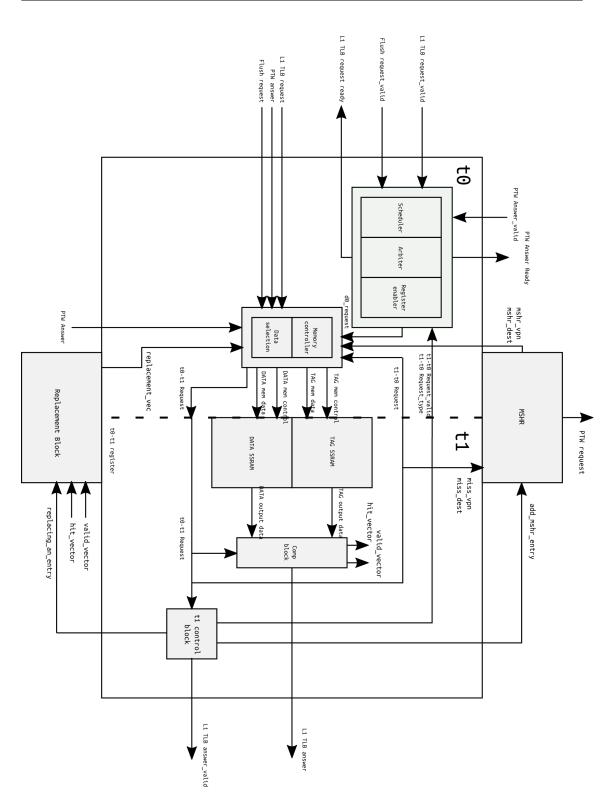

| 5.1  | Memory System of LEN5                                                                                                                                                            |

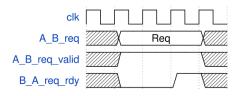

| 5.2  | Basic handshake                                                                                                                                                                  |

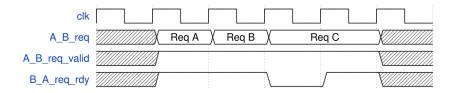

| 5.3  | Continuous and stalled handshake                                                                                                                                                 |

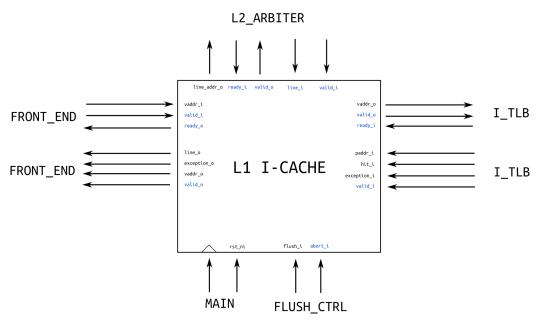

| 5.4  | $i-Cache^3$ interface                                                                                                                                                            |

| 5.5  | i-Cache interface                                                                                                                                                                |

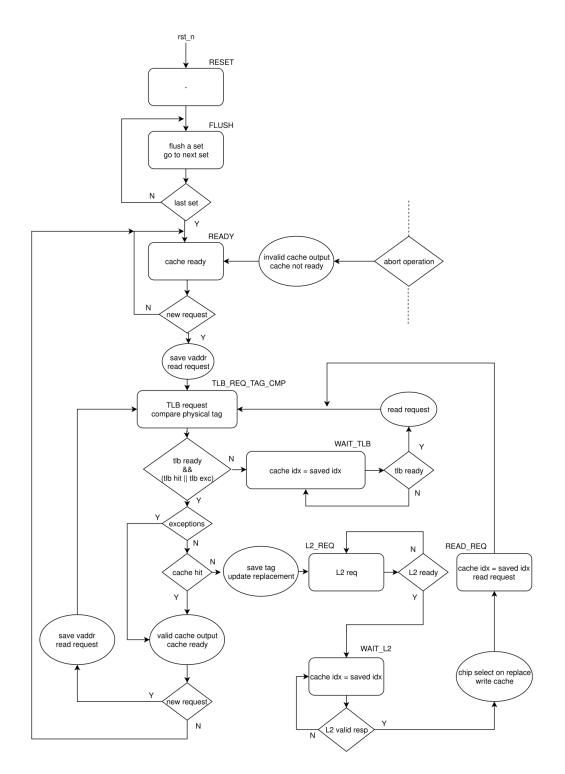

| 5.6  | i-Cache CU raw ASM                                                                                                                                                               |

| 5.7  | i-Cache interface                                                                                                                                                                |

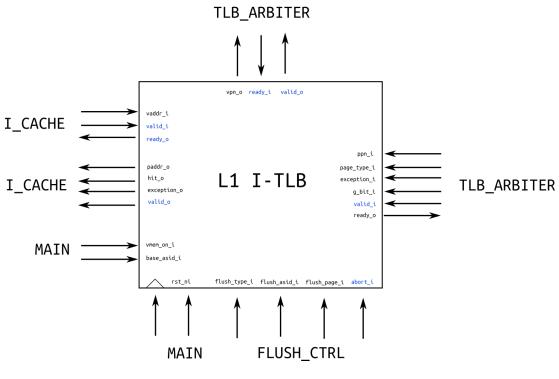

| 5.8  | i-TLB <sup>4</sup> interface. $\ldots$ $\ldots$ $\ldots$ $ 72$                                                                                                                   |

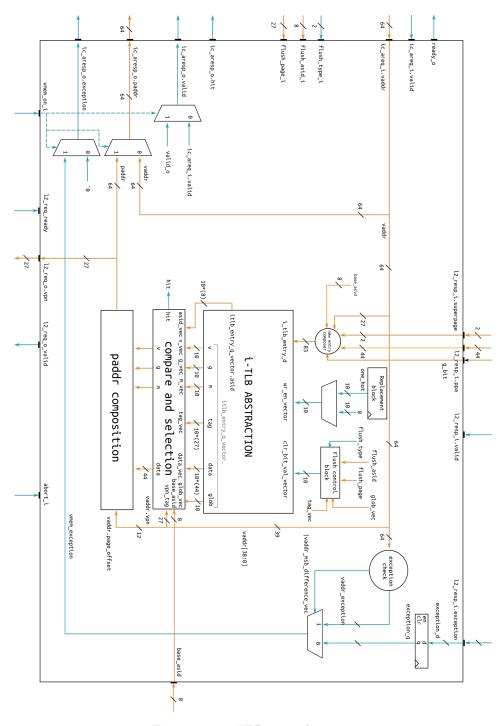

| 5.9  | i-TLB main diagram                                                                                                                                                               |

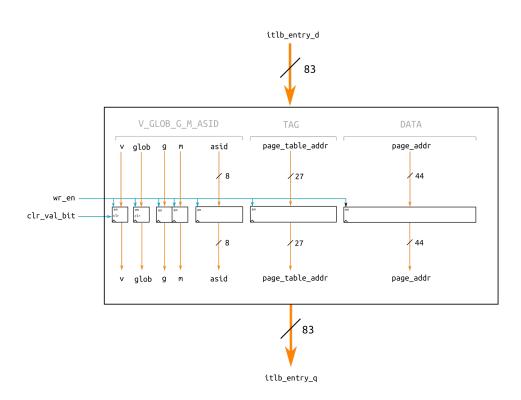

|      | i-TLB register entry abstraction                                                                                                                                                 |

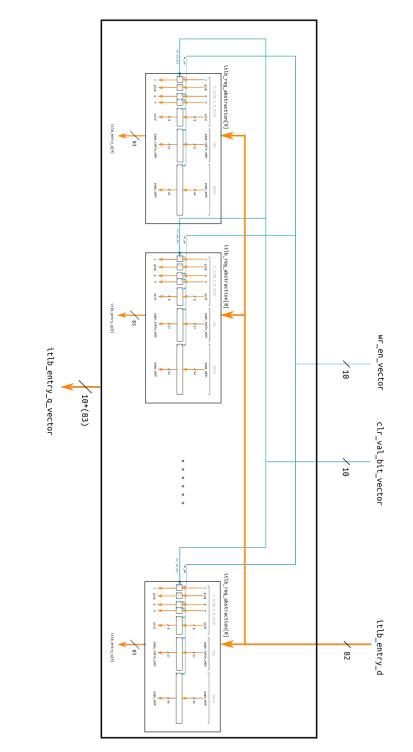

| 5.11 | i-TLB register entries abstraction                                                                                                                                               |

|      |                                                                                                                                                                                  |

$<sup>^{3} \</sup>mathrm{Instruction}$  Cache

$<sup>^4 \</sup>mathrm{Instruction}$  Translation Lookaside Buffer

| 5.12 | i-TLB raw ASM.                                                                | 77  |

|------|-------------------------------------------------------------------------------|-----|

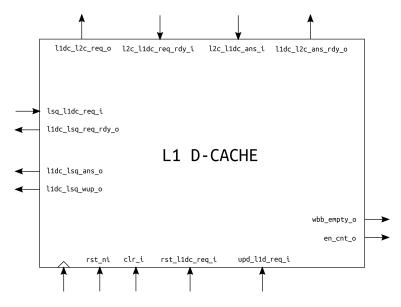

| 5.13 | d-Cache interface.                                                            | 85  |

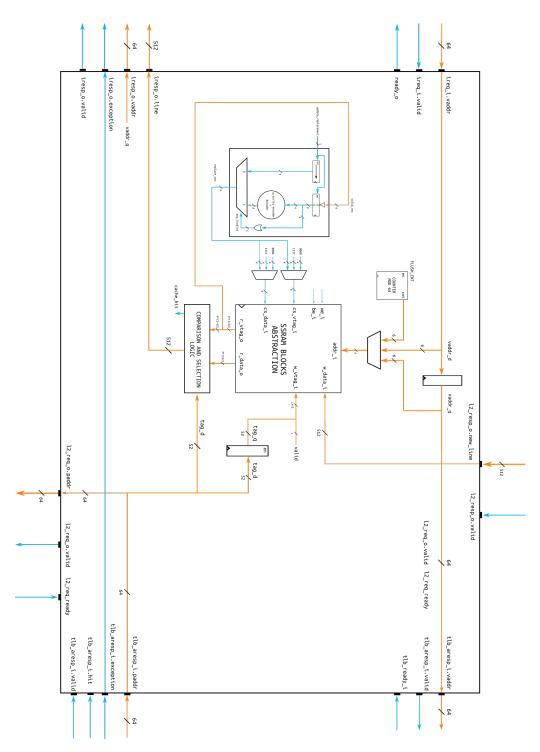

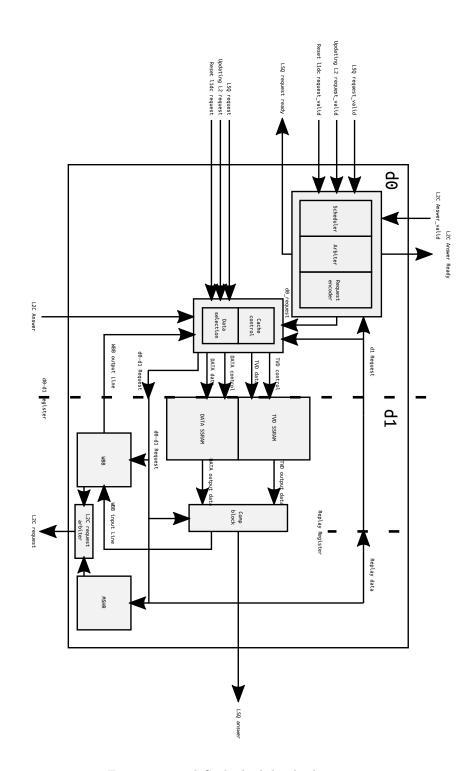

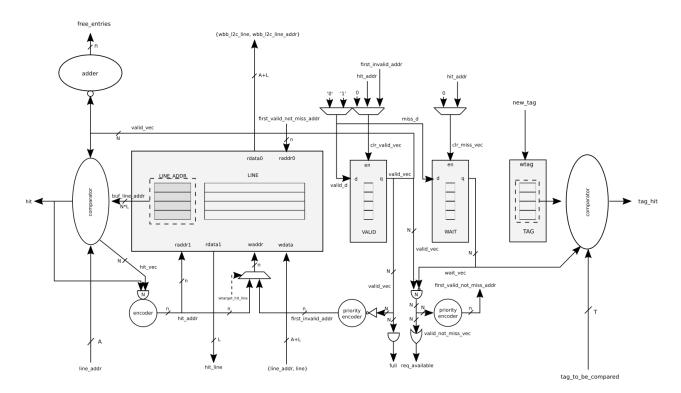

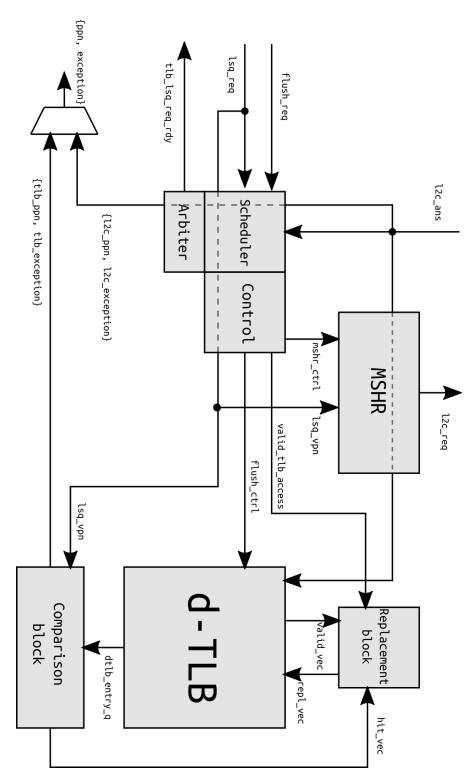

| 5.14 | d-Cache high level schematic.                                                 | 87  |

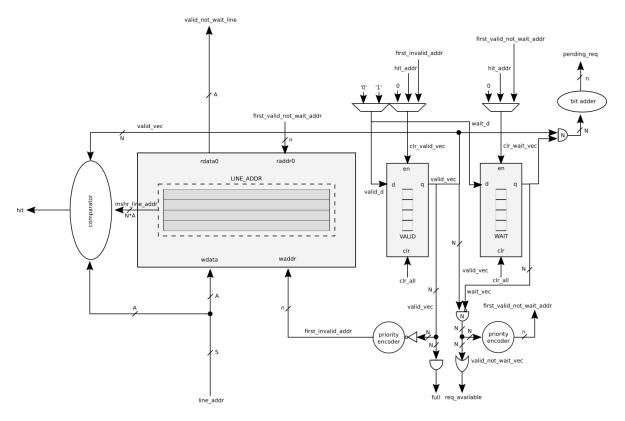

| 5.15 | MSHR interface.                                                               | 90  |

| 5.16 | MSHR main schematic.                                                          | 91  |

| 5.17 | Write Back Victim Buffer interface.                                           | 91  |

| 5.18 | Write Back Victim Buffer main schematic.                                      | 92  |

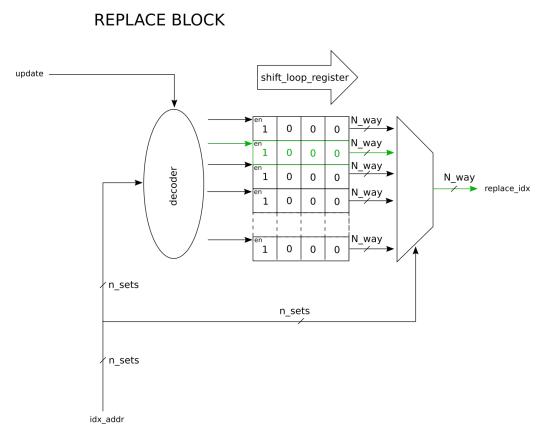

|      | d-Cache FIFO replacement block                                                | 97  |

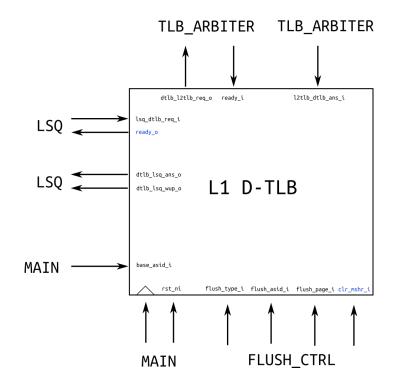

|      | Interface of the d-TLB <sup>5</sup>                                           | 101 |

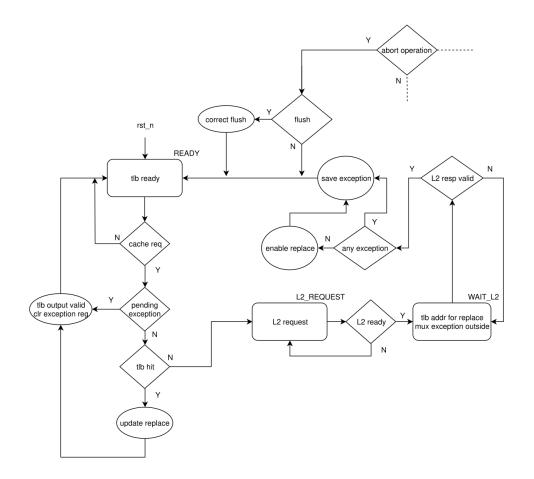

| 5.21 | Main diagram of the d-TLB                                                     | 102 |

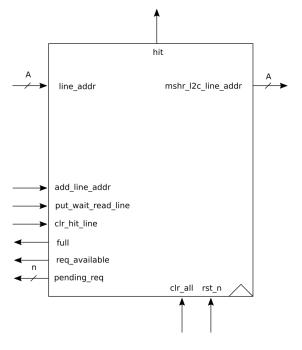

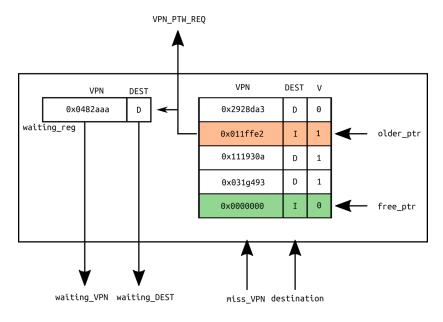

| 5.22 | MSHR of the d-TLB                                                             | 103 |

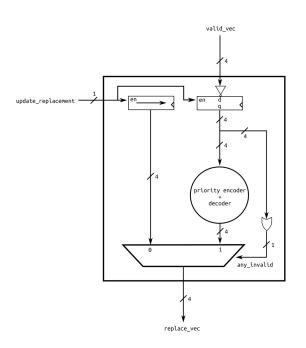

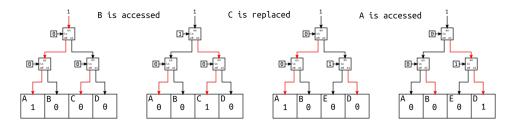

|      | Tree PLRU algorithm with 4 entries. Creation of the replacement vector        | 104 |

| 5.24 | L2 TLB MSHR                                                                   | 106 |

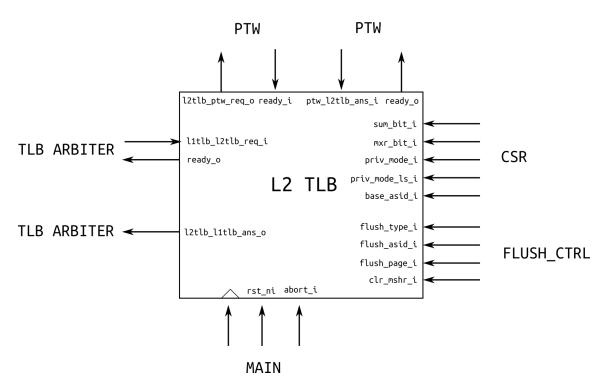

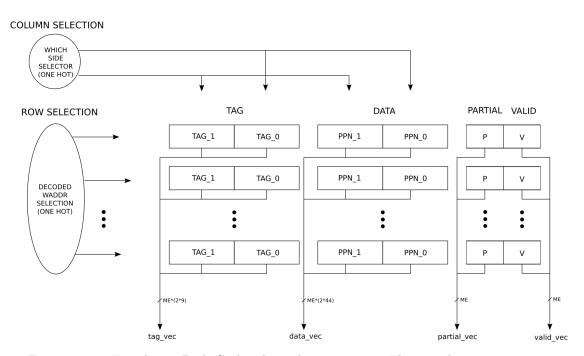

| 5.25 | L2 TLB main general schematic                                                 | 108 |

|      | L2 TLB more detailed general schematic                                        | 109 |

|      | L2 TLB MSHR                                                                   | 112 |

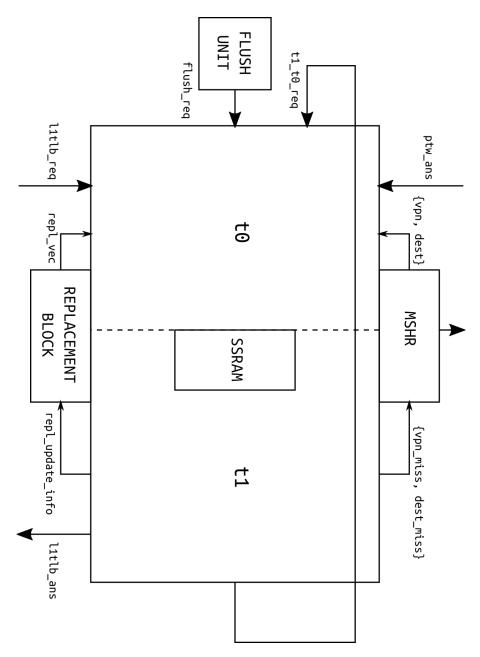

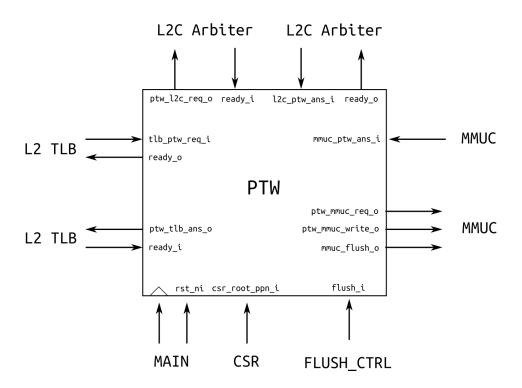

|      | The interface of the Page Table Walker                                        | 115 |

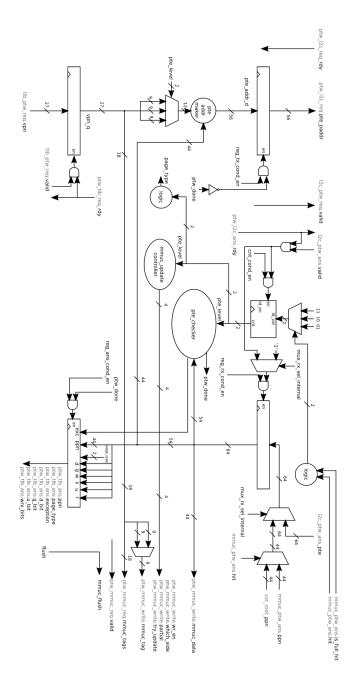

|      | The main schematic of the Page Table Walker                                   | 116 |

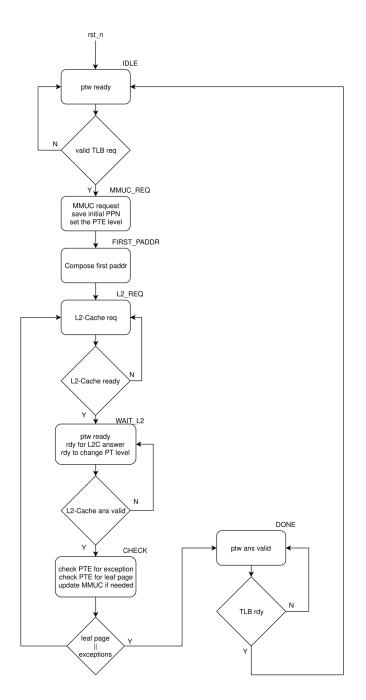

|      | PTW ASM chart                                                                 | 118 |

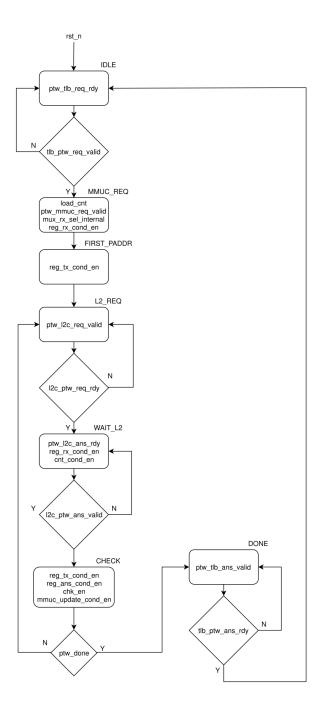

|      | PTW ctrl ASM chart.                                                           | 119 |

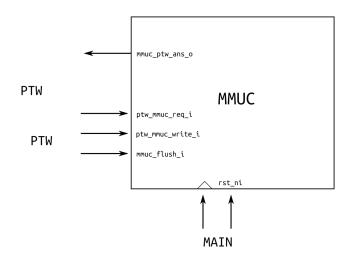

|      | MMUC interface.                                                               | 121 |

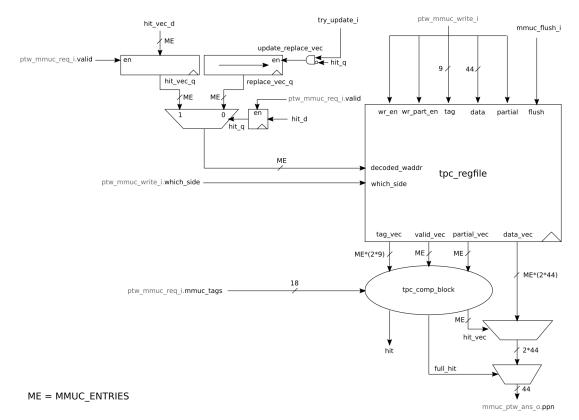

|      | Main schematic of the $MMU^6$ Cache, realized as a Translation Path Cache.    | 122 |

| 5.34 | Translation Path Cache physical organization. The actual one is a register    |     |

|      | file, but this is quite unrealistic. Maybe, a successive step will replace it |     |

|      | with a $CAM^7$                                                                | 123 |

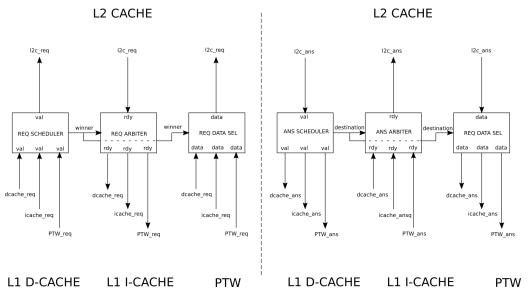

| 5.35 | L2 Cache Arbiter. It routes request channels from L1 i-Cache, L1 d-Cache,     |     |

|      | PTW to the L2 Cache and the answer channel from the L2 Cache to the           |     |

|      | correct block.                                                                | 125 |

|      |                                                                               |     |

$<sup>^5\</sup>mathrm{Data}$  Translation Lookaside Buffer

<sup>&</sup>lt;sup>6</sup>Memory Management Unit

<sup>&</sup>lt;sup>7</sup>Content Addressable Memory

# Chapter 1 Introduction

## 1.1 Motivations

This Master Thesis work presents the design of a memory system for a RISC-V Out of Order processor, capable of supporting an Operating System.

Why an attempt to design a part of a new RISC-V core? There are many answers to this question, but it's worth to underline the main one: it's challenging, and as Florian Zaruba wrote in a presentation of his Ariane core, it's funny. [1]

A plethora of other reasons can be found pointing out that this work is mainly horizontal instead of vertical: a lot of thesis works focus on a limited aspect of an entire system, with a lot of efforts made to enhance it. This thesis is an exploration through the world of the processors and the memory systems, and a huge amount of time has been spent to understand the theory to translate it into an original design.

• The RISC-V (pronounced *risk-five* [2]) ISA<sup>1</sup> is gaining popularity over the years and the interest towards it is growing both for universities and industries. The interest is shared because this is an open ISA maintained by professional people and it was developed to be useful, focusing on simplicity, modularity, and elegance.

Therefore, studying a complex architecture starting from the RISC-V specifications, manuals and literature is a great investment for the future, especially in this period.

• The world of the processors is vast, and, during the university courses, it hasn't been possible to study it in depth. In particular, the memory system has always been treated with strict and unlikely hypotheses to ease the discussion of the microarchitecture.

A lot of difficulties arose during the reading of the literature regarding this theme, and this fact suggested that a lot of work was necessary to fill up these gaps.

• It's hard to find well-documented designs for such complex processors, and a lot of things are taken for granted. This work and its documentation will be made available

<sup>&</sup>lt;sup>1</sup>Instruction Set Architecture

on GitHub, and the hope is to give to the whole academic world an easy to understand design.

• In the beginning, the project was enormous: a complete design of a multiple-issue Out of Order processor. Then, when its real complexity started to be clear, the main focus of the entire work switched to single parts of a single-issue processor.

However, the main goal was unchanged: try to deal with a complex problem and design to learn from it and ourselves.

• During the various courses offered by the university, the main HDL<sup>2</sup> chosen for the projects was VHDL. In many foreign industries and especially for the verification process, System Verilog is often used instead.

Trying to become familiar with this different HDL is an important step towards the job's world and can improve the comprehension of how modern hardware is described and verified.

The main difficulty of such a horizontal work is that also its goal was not so clear at a first glance; LEN5 (pronounced *lens*) is a general-purpose processor in its widest sense: it was not thought for a particular use, but only to study it. Therefore, a lot of choices taken to design it are mixtures of *best* choices to satisfy the majority of cases and compromises, due to the finite amount of time to complete the project.

**LEN5** and its memory system are under development and aren't optimized yet, but the project is open and the basis now exists: everyone will be able to use it for educational and academic purposes.

### 1.2 Thesis organization

The thesis work is organized as follows:

- This is the *first introductory chapter*.

- The *second chapter* is focused on giving a background to the reader, to let him have enough knowledge to understand the next parts. First of all, a general discussion on the processors introduces the theory behind them, the related issues and their fundamental metrics. Subsequently, the same thing is done for the memory hierarchy, presenting a deeper analysis of today's Memory Systems.

- In the *third chapter*, the attention is brought to the RISC-V ISA. After a brief introduction to its history and motivations, the core set is presented with particular attention to the part related to the Memory System.

- The *fourth chapter* is about the LEN5 core. It is our open-source processor that will be available on GitHub. At the present state, it is composed of a front end, a back end and this Memory System.

<sup>&</sup>lt;sup>2</sup>Hardware Description Language

- The *fifth and the sixth chapters* are the main body of the thesis work. They contain the description of the LEN5 Memory System, with its design and preliminary verification and synthesis results. During the discussion, some concepts will be repeated to highlight the motivations of the design choices. These chapters include parts of the documentation that will be available on GitHub.

- In the *seventh and last chapter* the results will be summarized, together with the main guidelines for possible future development.

In the electronic version of this document, all the words and concept that can result tough at first reading are explained in the glossary, together with the acronyms, and footnotes will aid the reader every time a new acronym is introduced.

Many parts of this thesis are more "verbose" than other similar works because the main purpose is to make this project and its documentation accessible also to students and people that have never tried to implement such a system.

# Chapter 2 Background

## 2.1 Processors

It's hard to give a unique definition of what a processor is without being too generic because this term is often used interchangeably to indicate a general processor or a  $CPU^1$ . Within this thesis work, the word *processor* will refer to a CPU.

A CPU is an electronic component of a computer system that is in charge of interpreting and executing instructions taken from a memory, elaborating data and controlling other parts of the system itself [3] [4] [5].

In the present, it's cumbersome to understand what a processor is starting the discussion with a hardware approach, because the main point is not the device itself, but the elaboration it's able to perform and why there is the need for performing it. People and industries need ways to store data and/or elaborate it in different ways. With a smartphone or a supercomputer, for controlling other systems or just for fun; the concept is the same, but how this is performed are different.

A possible way to deal with the complexity of such a goal is to divide the system into sub-blocks specialized in only a couple of works. Another great idea common in all the engineering fields is the **abstraction**. This concept is so pervasive in the life of everyone that it is often underrated and not clear.

The concept of abstraction makes sense when something should be used by someone (or something) else. If a thing is being used, there is always a goal: for example, an iPad is used to take notes, play games, listen to music. Which is the best way to allow someone to achieve his goals? Let him be focused on them. All the details about how the iPad works are irrelevant if the main goal is listening to music. Therefore, the user can use the iPad only knowing an incredibly small subset of all the characteristics of the device: if the finger press on this circle, a picture will be captured by the camera. Abstraction is the process of knowing only a small selected subset of characteristics of something, ignoring the others, to be more efficient in achieving the goal, or *what is important*, concentrating on it instead of on how the goal is achieved. This is valid also when hardware, software

<sup>&</sup>lt;sup>1</sup>Central Processing Unit

or mixed design is performed: most of the physics is hidden to a hardware designer, and most of the hardware is hidden to a software designer.

A functional way of elaborating data and controlling systems is to be concentrated on the operations that should be performed instead of on the complexity of the functional devices, and the programming languages are the best example of it. A program is a set of instructions for a computer to perform some tasks, and a programming language is the set of rules on how to write those instructions that allow the computer to understand what the programmer intends.

The instructions readable by a human are translated into formats understandable by a particular processor and are encoded in predefined formats, which are series of bits. This set of instructions should be

- Stored somewhere

- Executed

The first need is fulfilled by the memory system (see chapter 2.2 for further details), the second by the processor or other processing units.

#### 2.1.1 Basic concepts

The processor is a block that cyclically repeats a series of operations:

- 1) Fetch the correct instruction from the memory

- 2) Decode it

- If needed, prepare the data useful for the execution of the instruction

- 4) Execute the related operation

- 5) If needed, save the results in the memory

This cycle allows the processor to be a flexible device because its functionality and possibilities depend on its internal structure and on the instructions it can execute.

The entire set of instructions the processor can understand and execute is abstracted into its ISA. The ISA is the first abstraction of the processor, from the hardware to the software level. It specifies the native data types, the instructions, the registers, the addressing modes, the architecture of the memory, the handling of exceptions/interrupts and, if present, the external I/O [5] (for further details on the ISA, refer to section 3).

**Structure of a processor** Each processor works on fixed packets of bits of different dimensions. Usually, a packet is generally referred to as word. In the following, the term word will be used to identify the natural packet of bits on which the processor can do some decoding or elaboration.

The memory system feeds the processor with instructions and data, but the processor itself needs a way to store these elements during the processing. The basic element used to save useful information is the *register*.

A register is a set of *flip-flops*, electronic primitives for the storing of a single bit.

Then, the CPU is also composed of blocks useful to elaborate the instructions and the data, along with connections among all these elements.

The aforementioned *Fetch-Decode-Execute* cycle can be basically viewed in this way:

- The address of the next instruction is stored in a register, usually called the PC<sup>2</sup>. This address is given to the memory. The memory returns the requested instruction to the processor, which stores it in another register.

- The instruction is decoded and particular signals are prepared to control the execution of the instruction itself.

- The operands, if required, are fetched or prepared too.

- The control signals drive the execution of the instruction, controlling the execution units.

- The result, if needed, is saved somewhere, in a register or back to the memory.

Naturally, the reality is more complex and complicated because the processor should also be a *good* processor, but this is the base.

**Exceptions and interrupts** The described cycle can be interrupted by particular events. These events can be synchronous with the execution and generated by the processor (exceptions), or asynchronous, coming from the external world. For further details, refer to [6].

#### 2.1.2 What matters? The main fundamental metrics

It's not possible to define a *good processor*, because the concept of "good" varies a lot depending on the situation. However, three fundamental aspects usually characterize an electronic device of this type:

- Performance

- Energy and Power consumption

- Area

#### Performance

There are multiple ways to define and measure the performance of a computer, but in the following, it will be always used the *CPU time*. This is the time spent in computing for performing a particular task, without including the time spent waiting for data I/O or other tasks nonrelated to the measured one [6]. In formula, it can be expressed as:

$$t_{cpu} = N_{clk} \times t_{clk} = CPI_{avg} \times N_{instructions} \times t_{clk}$$

$$\tag{2.1}$$

<sup>&</sup>lt;sup>2</sup>Program Counter

where:

- $t_{cpu}$  is the total CPU time.

- $N_{clk}$  is the total number of clock cycles relative to a particular task.

- $CPI_{avg}$  is the average CPI<sup>3</sup>. Each instruction of the processor can require a different amount of clock cycles to be executed. The average of the CPI of each instruction, weighted with the frequency of that instruction in the complete program, is the average CPI.

- $N_i$  nstructions is the total number of instructions executed to complete the task.

- $t_{clk}$  is the clock period.

This formula is a reference when a choice finalized to performance improvement is made during the design. It is also helpful because its terms are easily measurable and can be used in practice [6].

Another fundamental equation that can aid the design especially during its first phase is Amdahl's law. It can be derived by the equation of the line. The law talks about the performance improvement achievable speeding up a part of a system: this improvement is limited by the fraction of time-dependent on that part. For example: if decoding an instruction takes 2 cycles and the execution takes 1000 cycles, it's worthless to waste resources to enhance the decoding stage to complete an instruction decoding in only 1 cycle. The decoding stage would be two times faster  $\left(\frac{2cycles}{1cycle}\right)$ , but the overall speedup would be only  $\frac{1002cycles}{1001cycle} \approx 1$  times faster. On the other side, a speedup of two times on the execution stages would have brought a total speedup of approximately two times. In formula:

$$Speedup_{overall} = \frac{ExecutionTime_{old}}{ExecutionTime_{new}} = \frac{1}{(1 - Fraction_{enhanced}) + \frac{Fraction_{enhanced}}{Speedup_{enhanced}}}$$

(2.2)

Where:

- Speedup<sub>overall</sub>: the effective ratio between the old execution time and the new one

- *ExecutionTime*<sub>old</sub>: the execution time without the improvement.

- *ExecutionTime<sub>new</sub>*: the execution time after the improvement.

- *Fraction<sub>enhanced</sub>*: the fraction of the computation time that can be converted to take advantage of the enhancement.

- *Speedup<sub>enhanced</sub>*: the speedup the system would achieve if the fraction enhanced was 1.

<sup>&</sup>lt;sup>3</sup>Cycles Per Instruction

[6]. In other words, the base concept is:

If there is a time interval that depends upon many parameters, the effective reduction in time of that interval achieved modifying one of that parameters is limited by the impact of that parameter on the total time interval.

It can seem a banality but this law is not only useful, but it is also severe.

**Techniques to improve the performances** There are different ways of improving the performance of a processor. The equation 2.1 states that there are three equally important parameters to be taken into account:

The clock period is the measure of how fast the processor works. If no power issues are present, it is determined by the critical path of the digital design. Usually, this metric seems to be the most determinant, but the reality is different: most of the time the clock period is linked to the average CPI. Adding a register can break the critical path, but it will likely increment the CPI too. Therefore, it's not wise to evaluate a design only on one of these parameters.

**Reducing the Instruction Count** If the processor is designed to support a lot of particular and complex instructions, the instruction count to complete a task can become low. For example: if there's the need for executing a  $FFT^4$  on some data and a processor implements such instruction as a single one, the instruction count for this task will be only 1. This idea guided the design of the processors for many years and brought to what is called  $CISC^5$  processor.

The main goal was to have the minor possible number of instructions to solve a particular task. The instructions were complex, and this complexity was absorbed by the hardware. A lot of silicon was used to implement execution units capable of dealing with such complex requests. The main effect was a reduction of the available area for the memory units, a higher clock cycle, and a very high average CPI.

For example, the pseudo-code operation

$$A = A * B$$

with both  $\mathbf{A}$  and  $\mathbf{B}$  stored in the memory, can be translated into only one multiply operation:

#### A MULT B

where **MULT** is a single processor operation.

During the execution of that instruction, the memory is accessed to fetch both the operand. Then they are multiplied and the result is stored back into the memory.

<sup>&</sup>lt;sup>4</sup>Fast Fourier Transform

<sup>&</sup>lt;sup>5</sup>Complex Instruction Set Computer

The main point is that usually, the more the instruction is complex, the less it is used. Wasting a lot of resources to maintain the support for instructions that were seldom used was worthless.

**Reducing the CPI** Another paradigm of designing a processor and an ISA is the  $RISC^6$  one. This approach breaks the complex CISC instructions into simple and basic ones, which can be completed in one clock cycle. The execution units are simpler, and there is more space for registers. For these reasons, there are special instructions to talk with memory. The others perform operations on data previously loaded into the registers.

Using the previous example, the pseudo-code operation

A = A \* B

with both  $\mathbf{A}$  and  $\mathbf{B}$  stored in the memory, can be translated into four basic operations:

LOAD A LOAD B A MULT B STORE RESULT

This time, the **MULT** operation is only a multiplication between two operands already loaded into the processor. Other instructions are responsible for talking to the memory.

During the execution of that instruction, the memory is accessed to fetch both the operands. Then they are multiplied and the result is stored back into the memory.

With a RISC processor, more instructions are required to complete a program, but each instruction consumes fewer cycles.

**Exploiting Instruction level parallelism** To speed up the execution it is possible to execute instructions in parallel. Even if it is not obvious, not the whole instruction execution can be parallelized. The majority of instructions, indeed, depend upon the previous ones.

For example, one of the primitive elements of the programming is the conditional branch. On a higher level it can be seen as an *if statement*:

$$if (A) \to B \tag{2.3}$$

The instructions in the  $\mathbf{B}$  block cannot be processed until  $\mathbf{A}$  is verified.

<sup>&</sup>lt;sup>6</sup>Reduced Instruction Set Computer

**Pipelining** The most important way of performing parallel works in digital processors is, without doubt, the pipelining. The name derives from the pipes: when a volume of water enters the pipe, it will exit it after an amount of time. This time can be called "latency". After this time, the water will go on exiting the pipe until it is not over. During this period, the pipe is full of water, and the flow at the exit point is continuous.

This concept is common in the industry with the name of "assembly line". Instead of building a car from the start to the end and only then begin the next one, industries began to have different people and machines continuously performing a smaller repetitive work on different cars. Mounting a glass on the first car, then on the next one, and so on. This allows having a lot of cars that are built at the same time. Each operator (or machine) works on a different car performing a different operation.

In the processors, this can be achieved dividing the unit into more different sub-blocks that are meant to perform a different operation each. For example, referring to the *Fetch-Decode-Execute* cycle, a first block can be responsible for fetching the instruction, a second block for decoding it, the third for its execution. When an instruction is fetched, it is saved into a register. The next clock cycle the instruction is decoded, while another instruction is fetched and so on. When the pipeline is full, the processor is processing three instructions, one per stage.

The pipelining can help in reducing the clock cycle and the CPI, but it's important to remember that is a form of parallelization. As already said, not all the instructions are parallelizable.

**Enhance the common case** Eventually, **Amdahl's Law** suggests that it's usually a good idea to focus the efforts on enhancing the most frequent case [6]. The common case is also usually simpler to be enhanced [7] and often is so more common than the infrequent cases that the overall performance benefit is much more positive than the hypothetical benefit from enhancement on the infrequent case.

#### **Energy and Power**

Initially, processor designers did not care about power consumption. There were relatively few transistors inside a chip, and the clock frequency was low. With the advent of the RISC architectures, the frequency started increasing and this brought to an increment of the power consumption with consequent issues with the power delivery and heat dissipation.

The power of a chip can be divided into three terms:

- Dynamic power: the power related to the energy dissipated to charge/discharge the resistive and capacitive lines of a circuit. This is the only "useful" consumed energy.

- Static power: the leakage power related to the non-idealities of the CMOS transistors. Even when they are supposed to be off, they let some charges pass through themselves.

- Short circuit power: the power related to the energy dissipated during the switching of a logic gate, inside the logic gate. It is due to the non-idealities of the dynamics of a logic gate.

In a first approximation, the third contribution can be neglected. The Static Power is a leakage power, and depends on how many transistors are off, how ideal they are, etc. Part of the device can be completely shut down to eliminate these non-ideality.

The dynamic power formula can be derived from the energy dissipated during a single commutation to charge the capacitance of a single transistor, from a logic 0 to a logic 1 or vice versa.

$$E_{tr} = \frac{1}{2} \times C_{tr} \times V^2 \tag{2.4}$$

If on average a percentage  $\alpha$  (switching activity) of all the transistors switches during a clock period and the total capacitive load is  $C_{tot}$ , the average dynamic power of the chip becomes:

$$P_{dyn} = \frac{1}{2}\alpha \times t_{clk}^{-1} \times C_{tot} \times V^2$$

(2.5)

$$P_{dyn} = \frac{1}{2}\alpha \times f \times C_{tot} \times V^2 \tag{2.6}$$

A frequency that increases can bring to greater power consumption because ideally the same work is done faster: more energy is requested in less time (for a fixed task, the requested energy remains the same). To address the problem of the power it is important to be careful at design time. There are a plethora of techniques used to mitigate this issue, but the "power wall" is the main cause that stopped the frequency increasing that was ruling the world of the processors until the first years of the XXI century. For a long time, the number of transistors inside a chip increased exponentially, and the frequency increased too: this was paid decreasing the voltage. Then, when this process reached its threshold, the power consumption became too high not to raise the concerns of the designers. Today, power consumption is one of the most important parameters to be taken into account [6].

#### Area

To understand why a large chip can be a problem it is useful to refresh how integrated circuits are made.

A cylinder of Silicon (*wafer*) is cut in slices. The largest possible number of circuits is "printed" on each slice, which has a fixed area. The slice is not perfect, and has a constant density of defects on its surface; hence, the number of defects is fixed for each slice. If a circuit is printed on a defect, it will not work. Therefore, if the single circuit is small, there will be less probability for one of them to have a defect inside it. On the contrary, a very big circuit will likely incorporate a defect. What is important for a designer is that the number of circuits that will not incur in defects grows roughly as the square of their area [6].

#### 2.1.3 Advanced issues and techniques

There are a lot of techniques that allow the processor to better exploit the *Instruction Level Parallelism*, i.e. the parallelism between different instructions. In the following, the most interesting ones (from a LEN5 perspective) will be briefly summarized.

**Dynamic Scheduling** In an *in-order* processor, each *data hazard* or unpredictable event such as a *cache miss* stalls the processor, and no new instruction is fetched, issued, executed. With dynamic scheduling, the processor can move the instructions and handling them *out-of-order* to hide the stall latency whenever is possible.

With this technique, *control hazards* can still stall the pipeline.

**Speculative processors** Some processors deal with the control-hazards predicting the outcome of the next branch. Speculative processors perform also execution on the predicted branch. They need ways to restore the initial conditions if the branch was mispredicted.

**Multiple issue processors** If a processor is able to fetch, execute and commit one instruction per clock cycle, it's not possible to reach a final CPI lower than 1. For this reasons, *superscalar* processors are designed to perform these operations on more than one instruction (this operation can be done *in-order* or *out-of-order*). LEN5 is not *superscalar*, and therefore will have a *CPI* higher than 1.

## 2.2 The Memory System

The term *memory* indicates the part of a system that stores some information. Into the processor, the information is usually stored using registers. They are fast enough to sustain the internal clock frequency, but they are expensive in terms of area and power.

Indeed, a register is composed of flip-flops, and flip-flops occupy more area than a usual RAM<sup>7</sup> memory cell [10].

#### 2.2.1 The interface between CPU and Memory

During the fetch stage, the processor needs to request the next instruction to the Memory System. The most simple request is composed of a *memory address* and a *valid request* signal. Usually, the minimum entity addressable by the processor is a single memory Byte. If the length of the address is **A** bits, the processor can address  $2^A$  Bytes.

To simplify the following discussion, we will consider words long 4 Byte (32 bit).

#### 2.2.2 The Memory Hierarchy

Usually, a processor needs a lot of storage space to have access to complex programs and data, and the internal registers are not sufficient. This information is stored in the Main Memory. Unluckily, a large memory is also much slower than the speed requested by the operating frequencies of the actual processors: this is caused by the increment of the capacitance of the memory with its increasing size. But, there is a loophole: data tend to be local both in time and in space. A processor working on some data will likely request again the same data after a brief interval of time (temporal locality), and it's also easy that it will use data stored in the proximity of the first ones (spatial locality). It's easy to see

<sup>&</sup>lt;sup>7</sup>Random Access Memory

these localities in the following C example, where each element of a vector is incremented by a constant:

```

for(int i = 0; i < N_MAX; i++) {

vector[i] += constant;

}</pre>

```

The elements of the array are stored in contiguous locations in memory and are accessed in order, one by one (*spatial locality*). On the other hand, *constant* is cyclically accessed during every sum (*temporal locality*).

These facts have brought designers to prefer a sparse and split memory system organized as a hierarchy: the *memory hierarchy*. Near the processor are present small and fast memories called **caches**, which are in communication with bigger and slower caches, that are connected to the Main Memory; as the memory size increases, the memory is physically located further away from the processor. When the processor needs data, a request is done to the lower-level caches, the ones near the CPU: if the data is not present there, the requested is forwarded to the higher-level caches (if present) and then to the Main Memory. When the data is found, it is brought to each of the memories of the lower levels and in the end to the processor. Then, the processor will find that data in the near and fast memory whenever it needs it. Different memory hierarchies can present different complexities, with a different number of levels. Usually, the first level cache is called **L1**, then the other levels, if present, are named **L2**, **L3** and so on. Then, the final memory (the biggest and the slowest) is the Main Memory. At the lowest edge of this hierarchy, before the L1 Caches, there are the registers of the processor: small and fast.

This is functional only because data manifest temporal locality. If it's likely that the same data will be preferred to the others, having them near the processor can increment the performances. To exploit spatial locality, data is moved into packets bigger than the dimension of a single word: more adjacent words are packed together to form a *line*, and the line is the minimal entity transferred to and fro the levels of the hierarchy.

The usual example done to make this concept more familiar is the producer-libraryhouse-desk one. A person can read a lot of books during his lifetime, but neither always going to the library, nor keeping all these books at home is practical. Therefore, only a small subset of those books are kept at home, the ones that are more liked and read. While studying, only two or three of those books inherent to the subject are kept on the desk and can stay there even for weeks. When another book is needed it's easy to search for it into your home and then into the library. If the book is not present there, the producer is asked for it. The book is sent to the library, then it is borrowed and arrives in the house and then on the desk. And this is efficient only because books exhibit temporal locality.

Returning to the memories, the net effect of a memory hierarchy is to give the processor the illusion to have a memory large as the Main Memory and fast as the L1 Cache. The processor is not aware of the memory hierarchy, because its interface to the Memory System is unchanged. The processor puts a valid address on the address line, makes the request and waits for the data to be returned on the data line. The Memory Hierarchy is transparent to the processor. [19]

#### 2.2.3 Von Neumann vs Harvard architectures

Sometimes, in literature, some terms evolve during the time. At the moment of their coining they mean something, but the meaning change because also the conditions change. In the beginning, for historical reasons, the architecture of a system was called *Von Neumann* if data and instructions were stored together in a unique memory, with a single path for both. On the contrary, if the paths were split with two distinct memories for instructions and data, the architecture was named *Harvard*. [19]

During the time, memory systems have evolved and memory hierarchies have modified the initial paradigm. In this thesis work, the term *Harvard architecture* is used with the following meaning, directly quoted from [7]:

"...the term Harvard architecture was coined to describe machines with distinct memories. Paying respect to history, this term is used today in a different sense to describe machines with a single main memory but with separate caches for instructions and data." [7]

#### 2.2.4 Caches

A **cache** is a small and fast memory, usually located in the proximity of the processor. It is used to store the most frequently used data. Most of the time, caches are implemented using SRAM<sup>8</sup>, which are faster than DRAM<sup>9</sup> even if they are bigger.

If the memory hierarchy is well designed, most of the time the processor will find the requested data accessing only the L1 Cache. When a request is done to a cache, there are two possible outcomes:

- Hit: the requested data was in the cache and is returned.

- Miss: the requested data was not in the cache, and it should be brought into the cache from the higher levels of the hierarchy.

#### Internal cache organization

When a particular word is requested by the processor but the request misses, the L1 Cache asks for the word to the higher levels, until the top of the memory hierarchy is reached; usually, the last block is the Main Memory. To exploit spatial locality, a block of adjacent words is transferred from the higher level to the lower one: when it reaches the cache, it is saved into a line.

In general, a cache can be logically viewed as a memory containing lines. The line is the minimal entity that is transferred to and from the cache. A block has the same size as a line, therefore the term "line" will be used indifferently to identify a block or a line. When a word request hits, a line is returned to the processor; then, the correct word can be extracted from it.

$<sup>^8 {\</sup>rm Static}$ Random Access Memory

<sup>&</sup>lt;sup>9</sup>Dynamic Random Access Memory

The cache lines are grouped into sets. A cache can contain one or more sets and each set can contain one or more lines. Each line of the Main Memory is associated with a particular set of the lower level cache. Consider the following example:

> Main Memory size: 1 GiB Cache size: 8 KiB Cache line size: 16 B per Line Word size: 4 B per Word Number of cache sets: 256 sets

The Main Memory keeps  $\frac{1}{16} \frac{GiB}{\frac{B}{Line}} = 64 \times 2^{26}$  Lines. The first 256 lines are associated with the first 256 Cache sets, line 0 to the set 0, line 1 to the set 1 and so on. The next 256 lines are again associated with the Cache sets in ascending order, and so on for all the lines. This means that if the cache is composed of **S** sets, the Main Memory line number **N** will be associated with the Cache set number **N** mod **S**. Each line is associated with one precise set only.

If the processor asks a word to the Memory System and a miss occurs, the line containing the correct word will be transferred from the Main Memory to the Cache and stored into its assigned set. It is clear that each set is assigned to many lines, but can't contain them all together. In this example, each set is assigned to  $\frac{64 \times 2^{26} Lines}{256Sets} = 16Mi \frac{Lines}{Set}$ . But physically, the Cache can contain only  $\frac{8}{16} \frac{KiB}{Line} = 512Lines$ , and each set  $\frac{512Lines}{256Sets} = 2\frac{Lines}{Set}$  at a time.

Therefore, if a Cache set is already full, a line should be evicted to make free space for the new requested line. The principle of spatial locality suggests that near lines in the Memory are likely to be used one after the other, therefore are placed in different sets to reduce the intra-set competition. This is why adjacent lines are assigned to different sets.

Each line saved in the Cache is uniquely labelled (*tagged*) with a tag which identifies it. This way it is possible to understand if the searched line is present in the set or not.

To summarize, the processor gives to the Memory an address, which is usually a Byte address and wants to receive a word. Under the following hypothesis

> Address length = 32 bit Bytes per word = 4 (addressed by the 2 bits: word offset) Words per line = 16 (addressed by the 4 bits: line offset) Number of Cache sets = 256 (addressed by 8 bits: cache index)

There are 32 - (2 + 4 + 8) = 32 - 14 = 18 bits in the address, the most significant ones, which are called tag. This is the part of the address which uniquely identifies each line. Indeed, when the set is addressed, it's not sure that the searched line is present. The tag portion of the address is associatively compared with the tags of each line to produce a hit or a miss.

**N-Way Set Associative** The organization of the Cache is named depending on the line capacity of the sets. If each set can contain N lines, the Cache is called *N-Way Set Associative* Cache. Each Main Memory line can be mapped to N lines of the Cache.

**Direct mapped** In the extreme case in which the sets contain one line only, the Cache is called *Direct Mapped*. With this organization, each Main Memory line is direct-mapped into a precise line of the Cache. When a line should be replaced in a set, the old line is evicted.

**Fully Associative** At the opposite, the Cache can be composed of only one set which contains the totality of the lines. In this case, no index is necessary, and the part of the address which is not a line offset or a word offset is a tag. Each Main Memory line can be mapped to any Cache line. When a replace occurs, there's the need for a way to select the old line to be evicted.

#### Cache performance

To understand the design choices of a cache, it is important to understand what is important. As for the processors, the fundamental metrics can vary depending on the situation, but for this work, we will focus especially on performance, area and power/energy. To understand these concepts, special terms will be used:

- Hit rate (**HR**): the probability for a request to hit

- Miss rate (**MR**): the probability for a request to miss

- Miss penalty (**MP**): the time (or the clock cycles, it will be clear from the context) spent starting when the miss occurs until the line is brought to the Cache

- Hit time (**HT**): the time spent to hit

The Memory Systems described is a *slave* of a processor. Therefore, the final metric to be taken into consideration is the execution time of the entire system, as it was hypothesized in 2.1.2.

The Memory System performance can be measured by the AMAT<sup>10</sup>. It measures the weighted average time for the processor to access data from the Cache after a request.

$$AMAT = HR \times (HT) + MR \times (HT + MP) = (1 - MR) \times (HT) + MR \times (HT + MP)$$

(2.7)

And so:

$$AMAT = HT + MR \times MP \tag{2.8}$$

There are more summed terms and the impact of an improvement on one of these can be evaluated using the reasoning of **Amdahl's Law**.

This equation is fundamental because it can help in evaluating the performance of the processor, especially if it is an In Order processor and the stalls due to the memory system overwhelm the stalls due to I/O memory contention. [6]

<sup>&</sup>lt;sup>10</sup>Average Memory Access Time

If the processor is Out of Order, the AMAT can be unlinked from the final execution time, because the impact of the stalls due to memory misses on the execution time can be mitigated by the Out of Order execution. The preferred method to evaluate design choices on the Memory Hierarchy for an Out of Order processor is usually the simulation. [6]

In this work, a full simulation was not possible. Therefore, in the first instance, minimizing the AMAT was taken as a design principle.

#### Cache design choices

**Cache Size** The more the cache is capacious, the more data will be able to hold inside. If size increases:

• Miss rate is reduced

but

- The Cache is slower (the Hit Time can increase)

- More energy requested

- More area occupied

**Associativity** If a set can host more lines, there is less intra-set competition. For example, in a direct-mapped cache, all the lines of the set 0 are mapped in one position only. In a fully associative cache with the same size, the same lines are mapped on more positions. With higher associativity, the miss rate is decreased.

The main drawback of associativity is the increasing complexity: the TAG comparison inside a set is done in parallel, and its cost increases with the number of comparisons to be done. Also, the selection of the line which hit is more complex. This affects the occupied area and the energy consumption, but can also increase the delay end possibly

Increasing the associativity:

• Lower miss rate

but

- Higher hit time

- Higher area

- Higher power consumption

- Higher miss penalty (for a more complex replacement policy)

**Replacement Policy** The replacement policy dictates which line of a full set is evicted when a new line should be stored in the same set.

The best possible policy would be implemented knowing in advance which is the line that will be requested more later in time (Bélády's algorithm). Most of the time this is not feasible in practice, even if there are ways to try to predict it [13].

There are a lot of policies which can perform better than the others with particular workloads. The main ones are:

- LRU<sup>11</sup>: the next line to be evicted is the one which has been accessed less recently. This policy is easy to be implemented with 2 Way Set associative caches because only a bit is needed. When the associativity increases, usually a pure LRU is not used.

- LFU<sup>12</sup>: the line which has been accessed less is the one which will be evicted.

- PLRU<sup>13</sup>: approximation of the LRU, it can be implemented in more than one way. If the number of elements is a power of two, it can be implemented with a tree PLRU.

- NRU<sup>14</sup>: approximation of the LRU. When a line is accessed, an *access bit* is set. Until the access bit is set, that page cannot be evicted. When the *access bit* of the last page is being asserted, all the others are cleared.

- FIFO<sup>15</sup>: The older line of the set is the next victim.

- Random: the next line to be evicted is chosen randomly or pseudo-randomly.

A good algorithm reduces the miss rate, but a complex algorithm can increase the access time and/or the miss penalty.

Line Size Larger lines can promote a higher hit rate, because of the spatial locality of the data hold into each line. But with equal Cache size, larger lines mean fewer lines, and this means higher competition in the Cache. Additionally, a bigger line can increment the miss penalty and every other transfer, because more data should be transferred between memories.

If the line size increases:

• The hit rate can be incremented thanks to better exploitation of the spatial locality

but

- The hit rate can also be decremented because of higher competition of the lines

- Higher miss penalty

- Higher costs for line transfers

<sup>13</sup>Pseudo Least Recently Used

<sup>&</sup>lt;sup>11</sup>Least Recently Used

<sup>&</sup>lt;sup>12</sup>Least Frequently Used

<sup>&</sup>lt;sup>14</sup>Not Recently Used

$<sup>^{15}\</sup>mathrm{First}$  In First Out

Write policy The processor can also need for writing data to the memory. This operation can be done in several ways, but the first distinction is about how the cache behaves when it is written. If the processor writes data into a cache line and the cache updates the higher level of the memory, the Cache implements a Write Through policy. If, on the contrary, the Cache does not immediately update the higher level of the hierarchy, the Cache implements a Write Back policy.

For a WB<sup>16</sup> cache can contain updated lines that are not stored in the upper levels of the hierarchy, they cannot be simply evicted during a replace. Every time a line is written, a special state bit is asserted: the *dirty bit*. During a replacement, if the line to be evicted is marked as dirty, it should be written back to the higher level memory to avoid loss of data.

A WB cache can reduce the inter-level memory traffic, especially if the line size is high enough. Both the policies need buffers to reach high performances: if the cache remains busy and stalls when a line is written back to the upper level the processor, especially if In Order, can be critically slowed down [11].

Write Back Victim Buffer If the cache is WB, a WBB can speed up the back-up of the dirty lines which are evicted from the cache. The Victim Buffer introduces possible RAW<sup>17</sup> hazards because the value buffered inside it are updated versions of what is present in the L2 Cache. When a request misses the cache, there's the need for checking also the WBB and use that line for reading or writing, without asking for a stale copy of it from the L2 Cache.

Write miss policy Write-misses are not as easy as read-misses. If a read request does not find the correct line, nothing bad has happened. When a store is performed, data is modified, and if the line was not the right one there is a risk of data loss.

As summarized in [11] the policy adopted by the Cache when a miss occurs is defined by three semi-independent variables and primarily affects the latency of a memory operation:

- Write allocation: a line can be allocated or not when a write misses

- Fetch on write: the right block can be fetched from the higher level of the memory when a write misses

- Write invalidation: the line of the cache is marked invalid and the data is forwarded to the higher level

If the correct block is fetched from the higher levels, it's a nonsense to mark as invalid or not to allocate a line. Therefore, in literature, the combination of Fetch on Write and Write Allocate with no line invalidation is called **Write Allocate**.

With this policy, every time a write miss occurs, a line is allocated into the lower level Cache. Then, the correct block is brought into that line and the store is replayed.

<sup>&</sup>lt;sup>16</sup>Write Back

<sup>&</sup>lt;sup>17</sup>Read After Write

Other policies hypothesize a *No Fetch on Write* policy. A possibility is to allocate a line and write only the data into an empty line. Only that piece of the line is marked as valid. This policy is called **Write Validate**. Hypothesizing also a *No Write Allocation*, the line can be either invalidated (**Write Invalidate**) when a miss occurs or kept as it is (**Write Around**), directly writing the upper level of the Memory Hierarchy [11].

The Write Allocate strategy is especially useful if the Cache is WB. This is because when data is fetched can remain in the Cache and be written more times. On the contrary, the other policies which can be collected under the name of **No Write Allocate** can be wiser to be used with a Write Through Cache, not to double the memory traffic.

The conclusion of [11] is "Write-validate and write-around always outperform fetch-onwrite" [11]. It would be interesting to understand if this is still valid, with the consideration of a possible increase in the complexity of a Write Validate policy.

**Unified or split caches** The processor, during the same clock cycle, can need for instruction and data. If the Cache is one and does not have two access ports, a Structural Hazard happens.

A possible way to deal with this hazard is to maintain two split caches, an i-Cache, and a d-Cache. Split caches force data to compete only with data and instruction with instructions. This means that the miss rate can be higher (but this is not a synonym of a lower AMAT).

If split caches with half the size of a unified cache, the first have:

- More bandwidth

- Fewer hazards

- Possibility to adopt different replacement policies and organizations

but

• A slightly higher miss rate

**Multilevel cache** The Memory hierarchy can be composed of a different number of cache levels. They can be on-chip or off-chip (the difference is in the energy requested and in the latency of the answers). There can be only one level or more.

Usually, L1 Cache is small to have a low hit time not to impact on the main clock period or the latency. But if the cache is small, the miss rate is high. The only way to keep the AMAT low is to reduce the miss penalty, as suggested in 2.8.

A possible way to do this is to interleave an additional cache level between the Main Memory and the L1 Cache: the L2 Cache. Even if the L1 Caches are split, the L2 Cache can be shared.

The L2 Cache is faster than the Main Memory because is smaller and this fact means that if a request misses the L1 cache but hits the L2 one, the miss penalty is reduced.

**Inclusion policy** If there are more cache levels, there are different ways to handle the inclusion policy.