## POLITECNICO DI TORINO

Corso di Laurea Magistrale in Ingegneria Elettronica

Tesi di Laurea Magistrale

## Computing architectures based on skyrmions

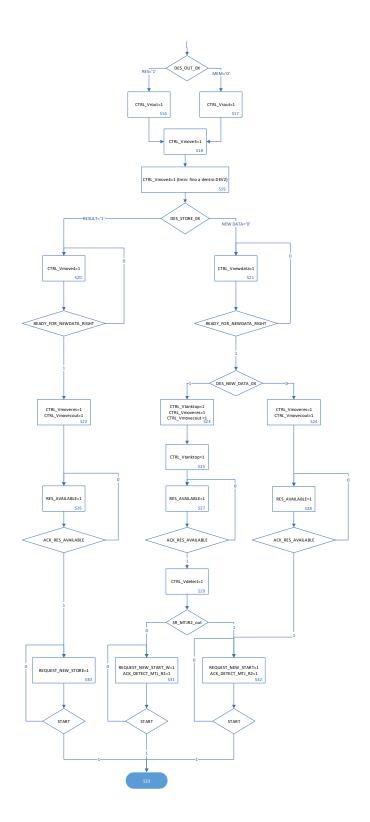

Relatori: Prof. Maurizio Zamboni Prof. Mariagrazia Graziano Prof. Marco Vacca

> Candidata: Chiara Cannavò

Dicembre 2019

## Acknowledgments

In the nine months that were needed for producing the results reported in this thesis, many people sustained me (and put up with me). First of all I want to thank professor Sandro Santucci from university of L'Aquila, for the patience he had in reading the first chapters of this work and in sending me a really appreciated feedback. I would like to thank my father, for all the support he gave me and for all the times he was available for a discussion. Finally, I would like to thank my mother, my sisters and all the friends that in these months gave me all the advices and sustain I could ever hope for.

Chiara Cannavò Torino, December 2019

## Table of contents

|          | Acknowled       | lgments                                                                                                                                                               | I |

|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1        | Introduct       | ion                                                                                                                                                                   | 1 |

| <b>2</b> | Physics a       | nd applications of skyrmions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                             | 4 |

|          | 2.1 Physica     | al properties                                                                                                                                                         | 4 |

|          | 2.1.1 <b>To</b> | pological properties                                                                                                                                                  | 5 |

|          | 2.1.1.1         | Topological charge                                                                                                                                                    | 5 |

|          | 2.1.1.2         | Dzyaloshinskii-Moriya Interaction                                                                                                                                     | 6 |

|          |                 | Spin-orbit coupling $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                             | 8 |

|          | 2.1.1.3         | Vorticity number                                                                                                                                                      | 8 |

|          | 2.1.1.4         | Helicity number and polarity $\ldots \ldots \ldots$   | 0 |

|          | 2.1.1.5         | Meaning of the helicity number $\ldots \ldots \ldots$ | 0 |

|          | 2.1.1.6         | Topological protection                                                                                                                                                | 2 |

|          | 2.1.1.7         | Practical examples                                                                                                                                                    | 2 |

|          |                 | Skyrmions and antiskyrmions                                                                                                                                           | 5 |

|          | 2.1.2 Mi        | $cromagnetic model \ldots 10$                                                     | 6 |

|          | 2.1.2.1         | LLG equation                                                                                                                                                          | 7 |

|          |                 | Micromagnetic energy density                                                                                                                                          | 8 |

|          |                 | Exchange energy                                                                                                                                                       | 8 |

|          |                 | Zeeman energy                                                                                                                                                         | 9 |

|          |                 | Demagnetizing field energy                                                                                                                                            | 9 |

|          |                 | Anisotropy energy                                                                                                                                                     | 9 |

|          |                 | DMI energy 2                                                                                                                                                          | 1 |

|          | 2.1.3 Mo        | $\mathbf{ption}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                     | 1 |

|          | 2.1.3.1         | Spin Transfer Torque (STT)                                                                                                                                            | 1 |

|          | 2.1.3.2         | Spin Hall Effect (SHE)                                                                                                                                                | 3 |

| 2.1.3.3 Thiele equation and skyrmion Hall effect                                                     |           | 25   |

|------------------------------------------------------------------------------------------------------|-----------|------|

| 2.1.3.4 Mitigation of the skyrmion Hall effect $\ldots$ $\ldots$                                     |           | 29   |

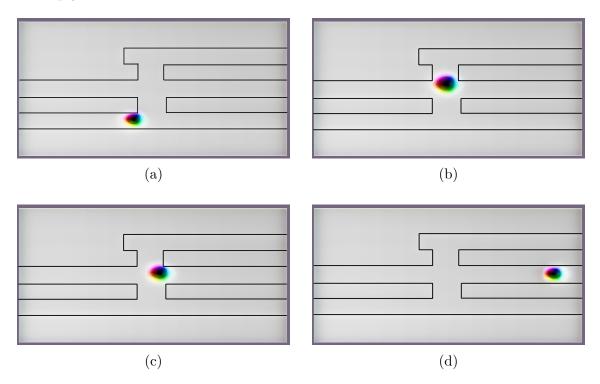

| 2.1.4 Nucleation. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            |           | 32   |

| $2.1.4.1  \mathbf{STT}  .  .  .  .  .  .  .  .  .  $                                                 |           | 32   |

| 2.1.4.2 Notch                                                                                        |           | 33   |

| 2.1.5 Detection $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$              |           | 34   |

| Spin-polarized current                                                                               |           | 34   |

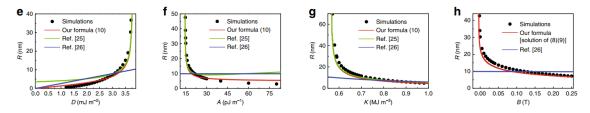

| 2.1.6 Skyrmion size                                                                                  |           | 35   |

| 2.2 Applications                                                                                     |           | 40   |

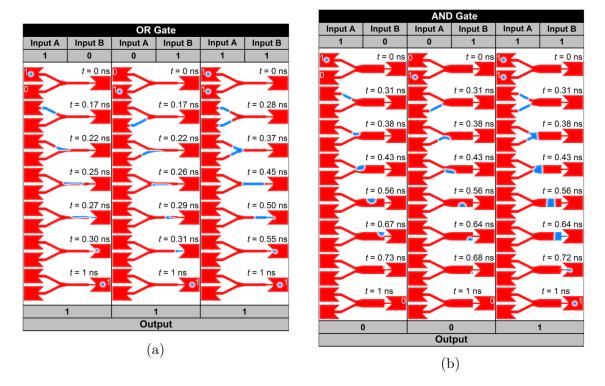

| 2.2.1 Logic gates using the DW pair-skyrmion reversible of                                           | onversior | ı 40 |

| 2.2.2 Logic gates for conservative logic systems $\ldots$ .                                          |           | 43   |

| 2.2.3 Skyrmion-based transistors                                                                     |           | 47   |

| 3 Micromagnetic analysis                                                                             |           | 50   |

| 3.1 Methods $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$         |           | 50   |

| 3.2 $INV/COPY$ gate                                                                                  |           | 53   |

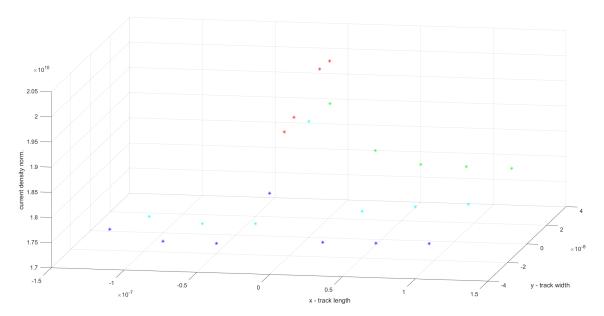

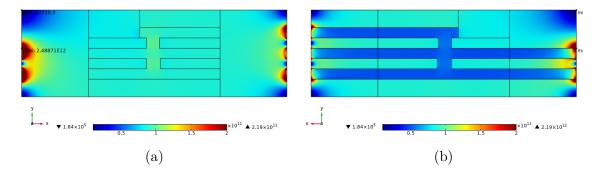

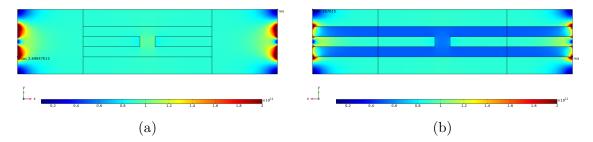

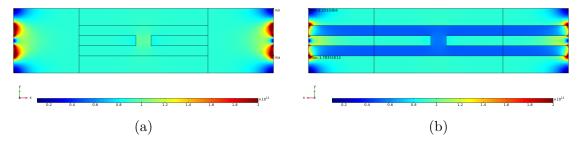

| 3.2.1 Uniform current density                                                                        |           | 53   |

| 3.2.2 Realistic current distribution                                                                 |           | 57   |

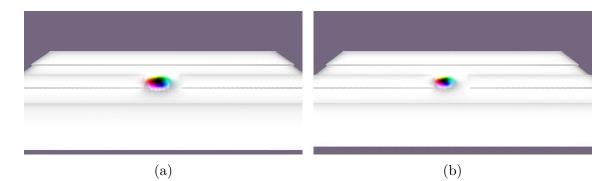

| 3.2.3 Final version $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                            |           | 62   |

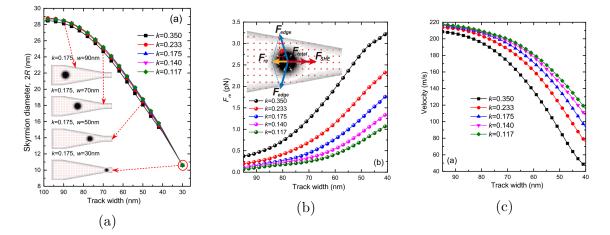

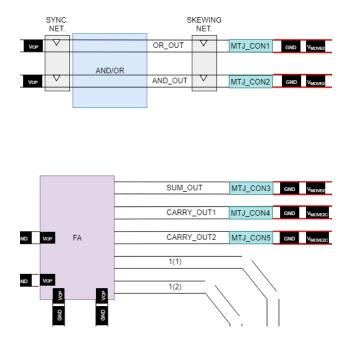

| 3.3 $AND/OR$ gate                                                                                    |           | 67   |

| 3.3.1 Uniform current density                                                                        |           | 68   |

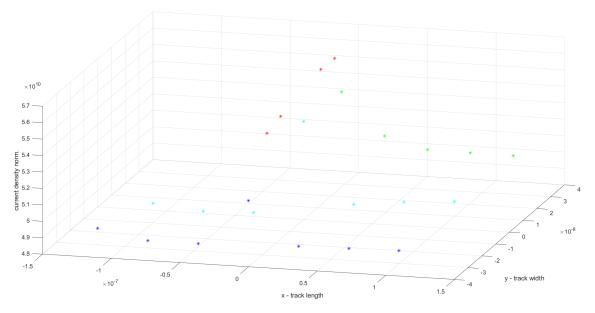

| 3.3.2 Realistic current distribution                                                                 |           | 69   |

| 3.3.3 Final version                                                                                  |           | 70   |

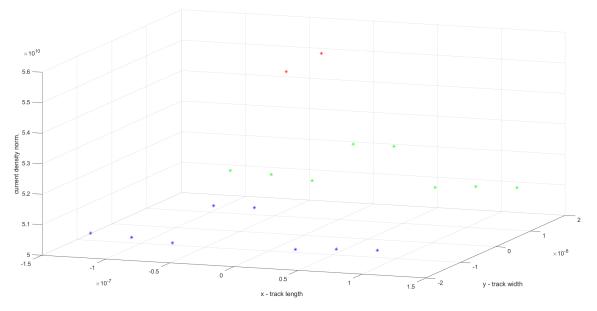

| 3.4 Balancing of current density                                                                     |           | 74   |

| 3.4.1 $INV/COPY$                                                                                     |           | 75   |

| $3.4.1.1  \text{Original version} \dots \dots$ |           | 75   |

| $3.4.1.2  \text{First version}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $     |           | 77   |

| $3.4.1.3  \text{Second version}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $    |           | 80   |

| 3.4.2 $AND/OR$                                                                                       |           | 82   |

| 3.4.2.1 Original version                                                                             |           | 82   |

| 3.4.2.2 First version                                                                                |           | 83   |

| 3.4.2.3 Second version                                                                               |           | 85   |

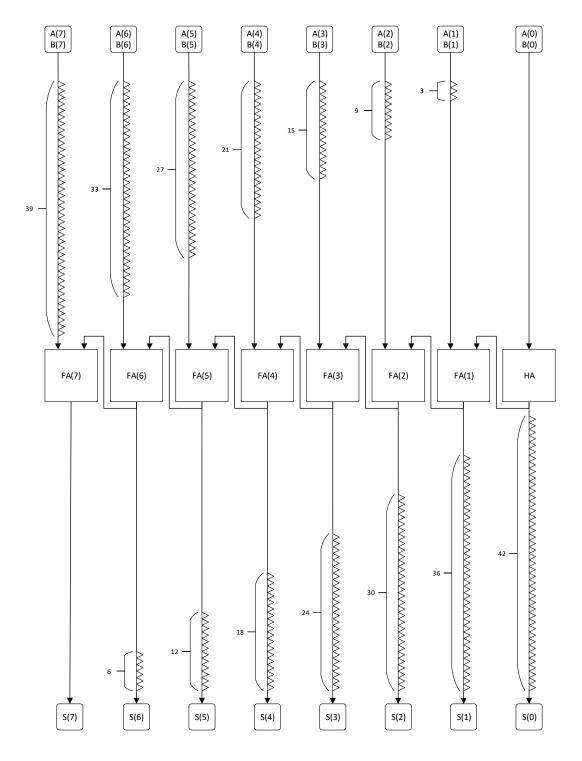

| 4 Ripple carry adder                                                                                                                         | 87  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

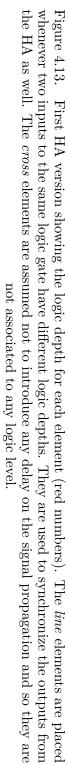

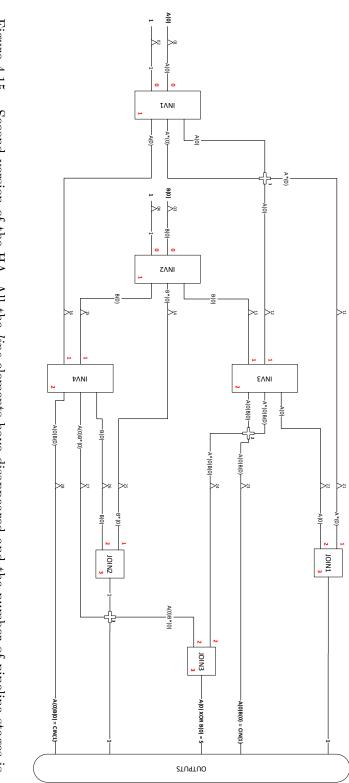

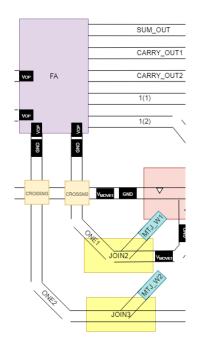

| 4.1 First version                                                                                                                            | 88  |  |

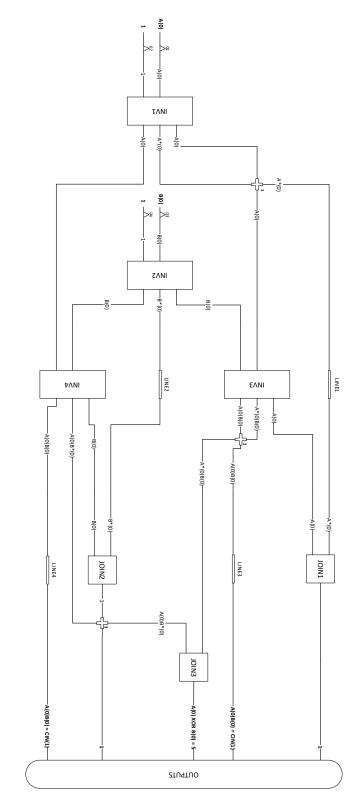

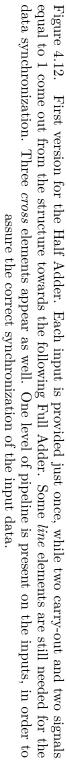

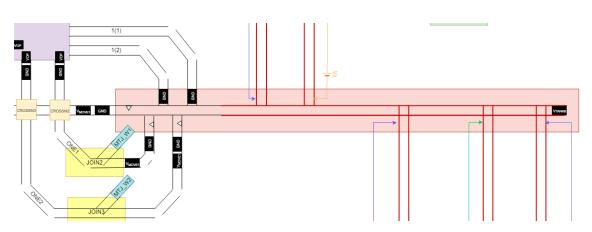

| 4.1.1 Half Adder - first version                                                                                                             | 88  |  |

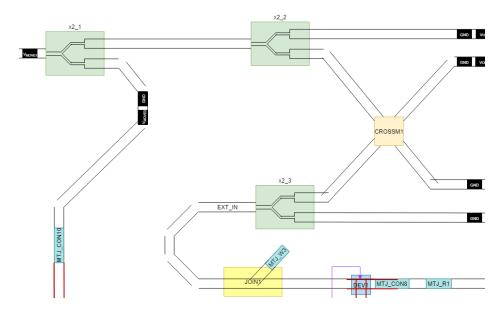

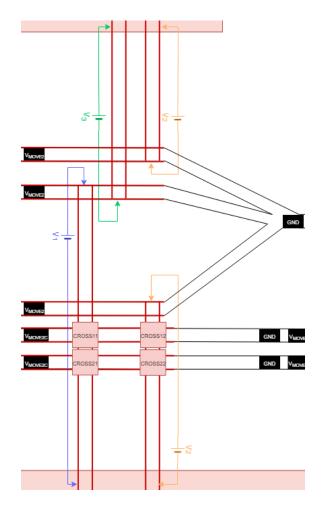

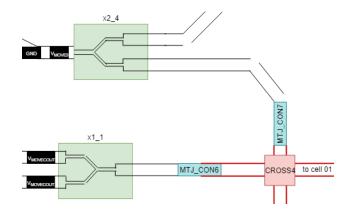

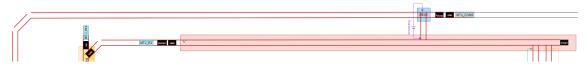

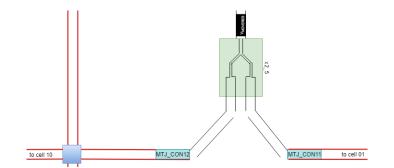

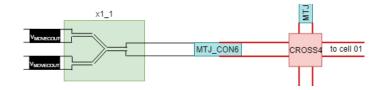

| 4.1.2 $Cross$                                                                                                                                | 91  |  |

| 4.1.3 Full Adder - first version                                                                                                             | 93  |  |

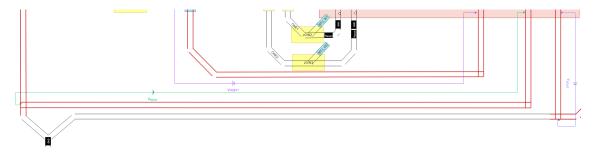

| 4.1.4 Adder - first version                                                                                                                  | 94  |  |

| 4.1.5 VHDL description                                                                                                                       | 96  |  |

| $4.1.5.1  \text{Not gate} \dots \dots$ | 97  |  |

| 4.1.5.2 Line element $\ldots$                               | 99  |  |

| 4.1.5.3 Join gate                                                                                                                            | 99  |  |

| $4.1.5.4  \text{Notch}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                     | 100 |  |

| $4.1.5.5  \text{Cross}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                            | 102 |  |

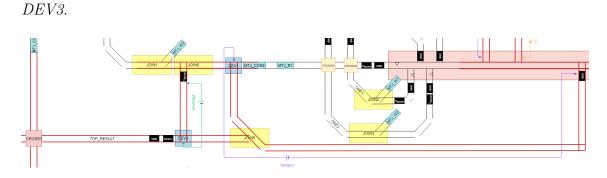

| 4.1.6 Simulation of adder $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                            | 102 |  |

| 4.1.6.1 Tuning of the delay elements $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                            | 102 |  |

| 4.1.6.2 Simulation results $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                             | 103 |  |

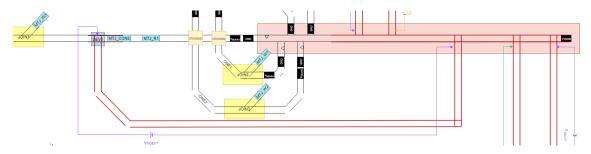

| 4.2 Increase of performance                                                                                                                  | 104 |  |

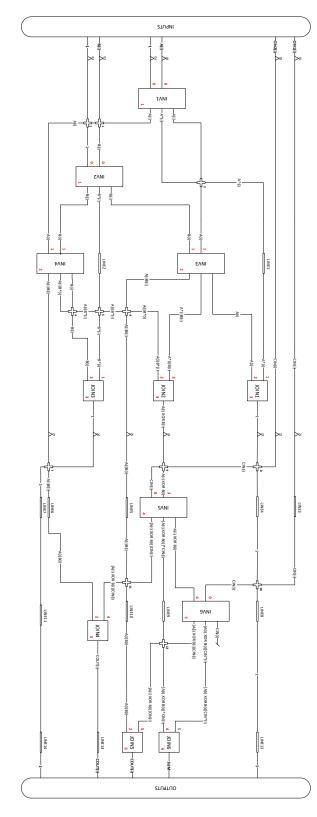

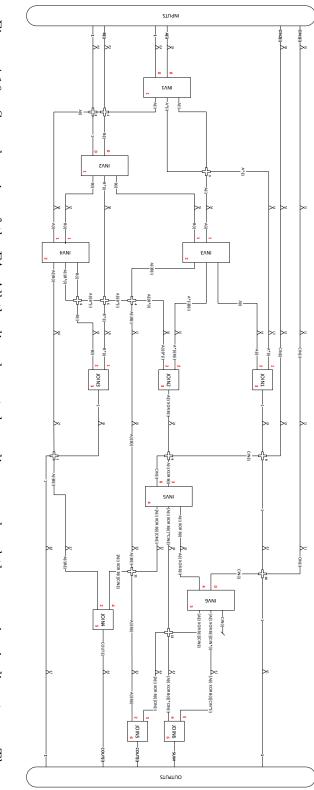

| 4.2.1 Half Adder - second version                                                                                                            | 104 |  |

| 4.2.2 Full Adder - second version                                                                                                            | 104 |  |

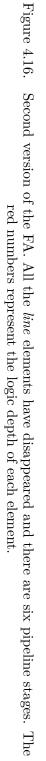

| 4.2.3 Adder - second version $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                       | 105 |  |

| 4.2.4 Simulation of adder v2 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                    | 105 |  |

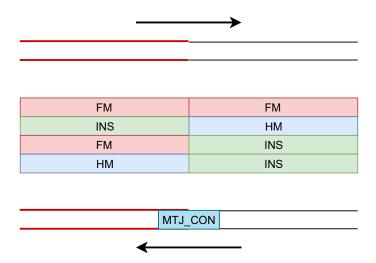

| 4.3 Pipelining. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                      | 106 |  |

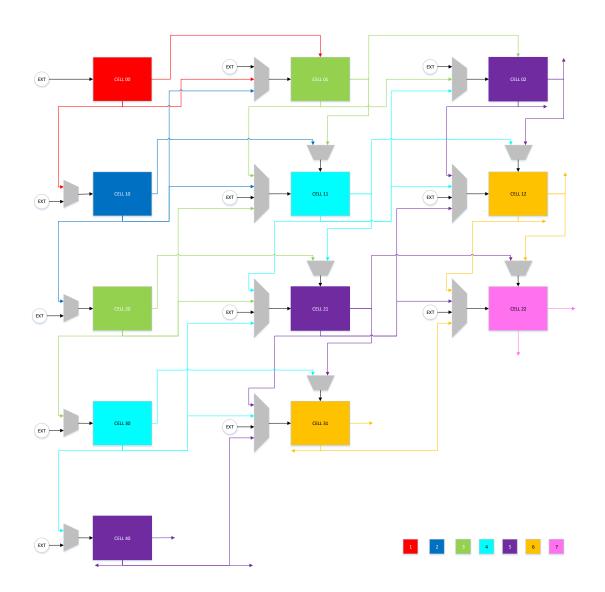

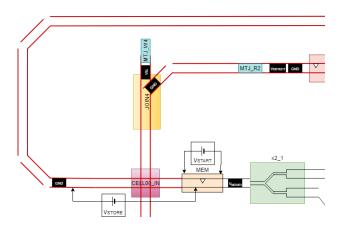

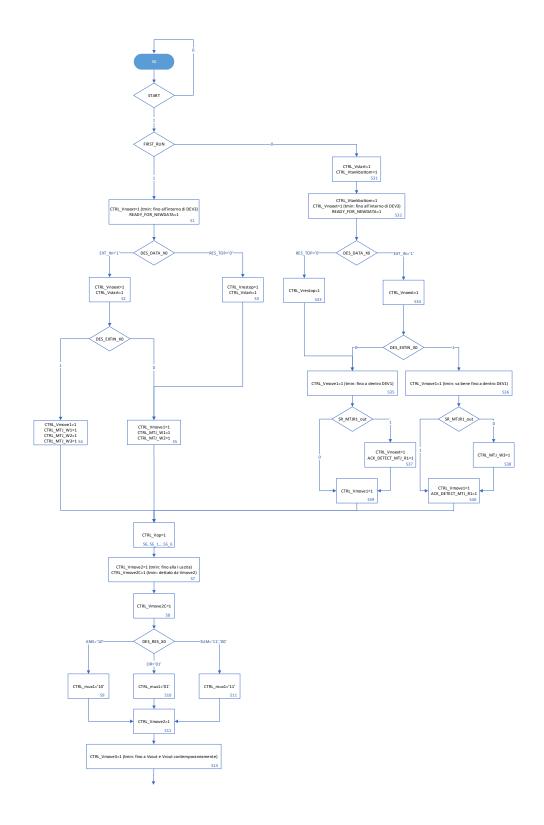

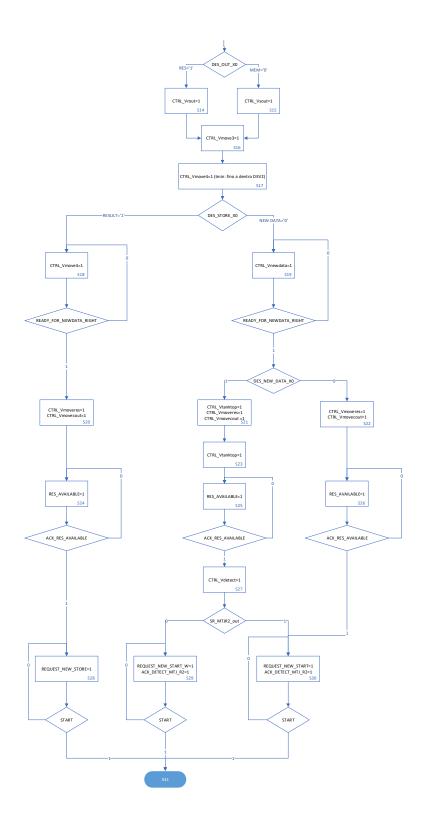

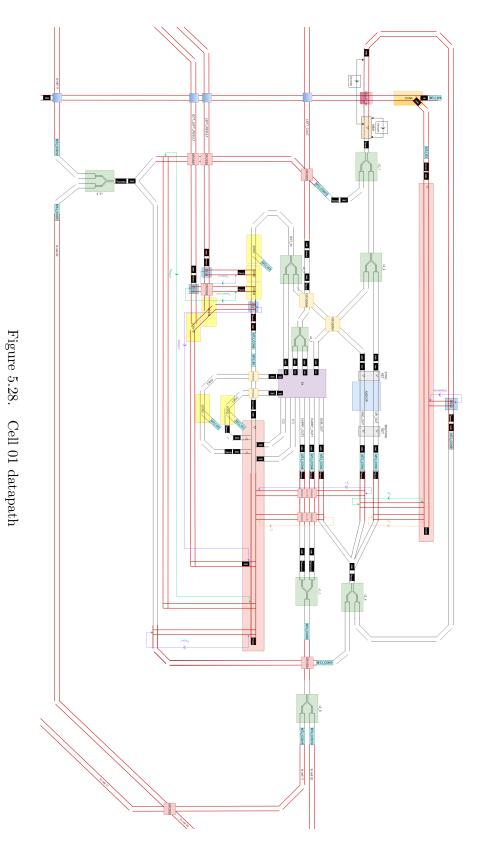

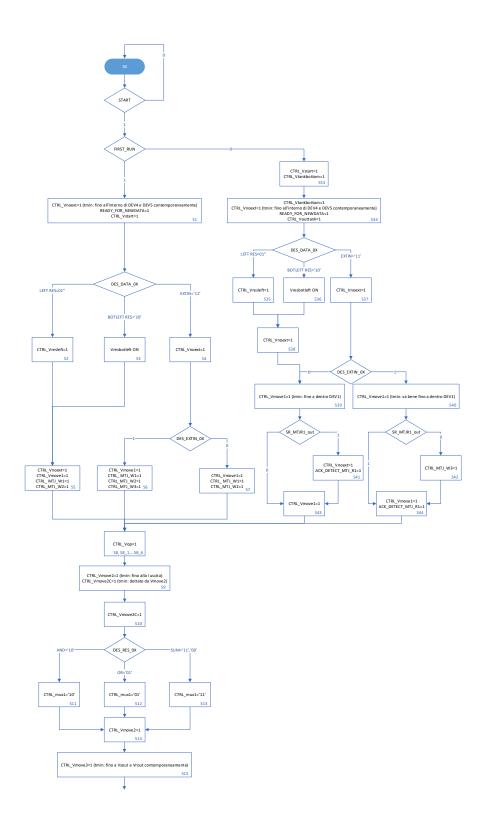

| 5 Logic in memory - first architecture                                                                                                       | 114 |  |

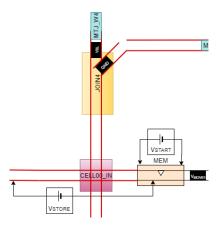

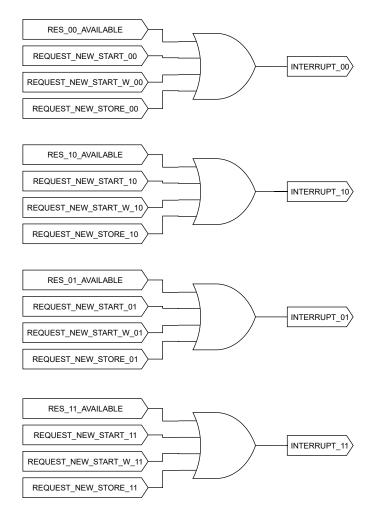

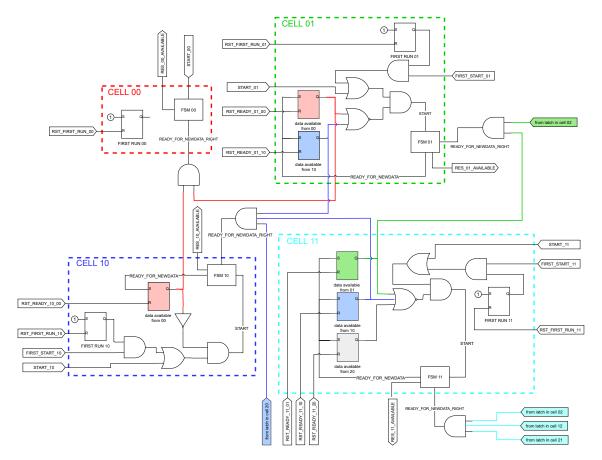

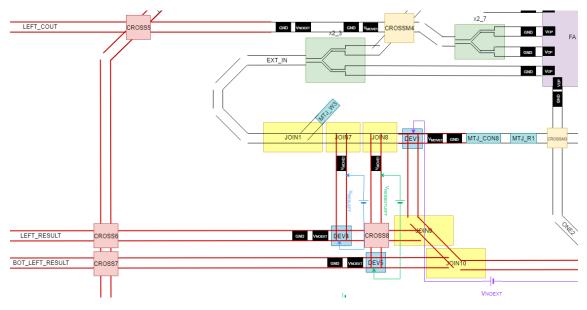

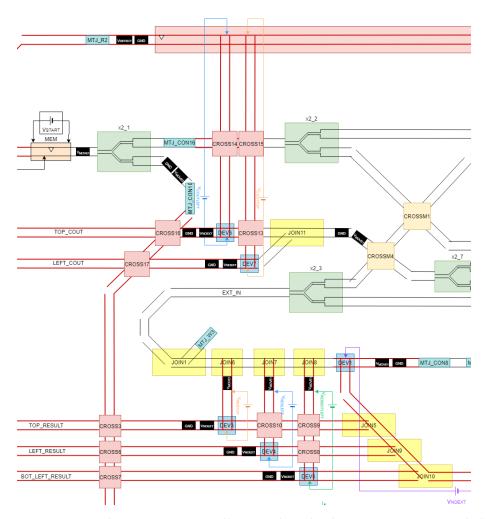

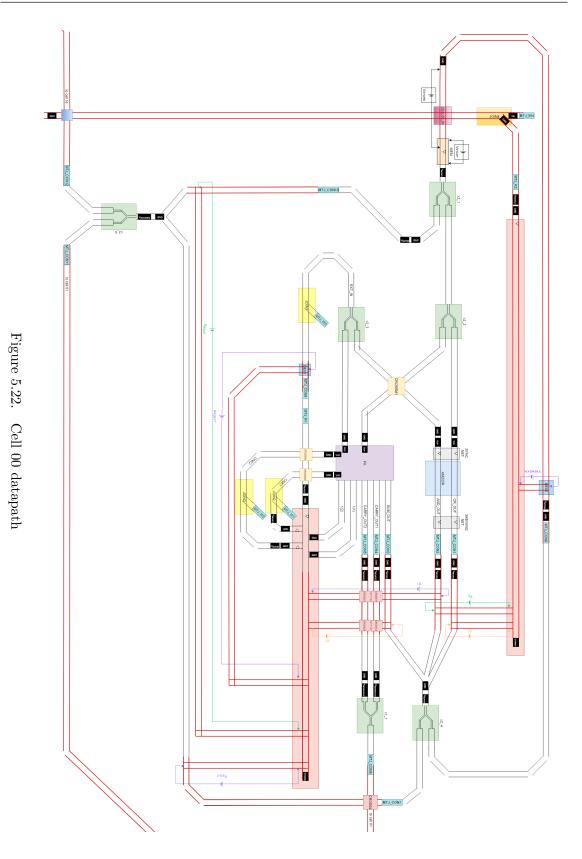

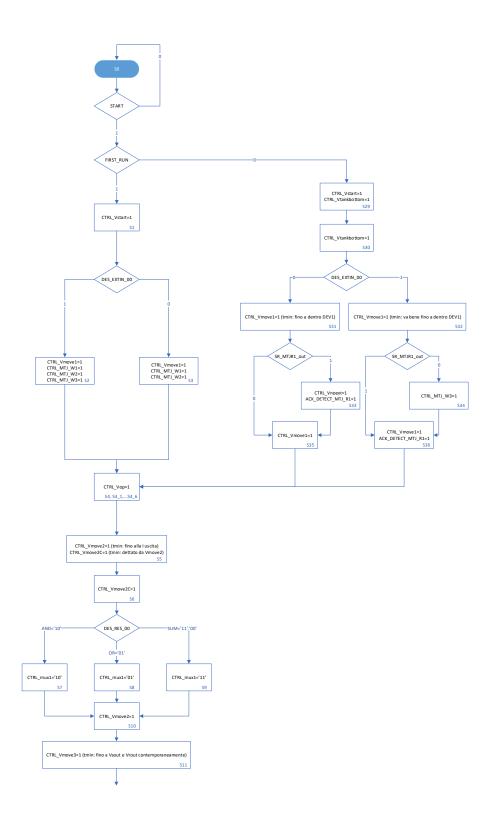

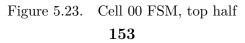

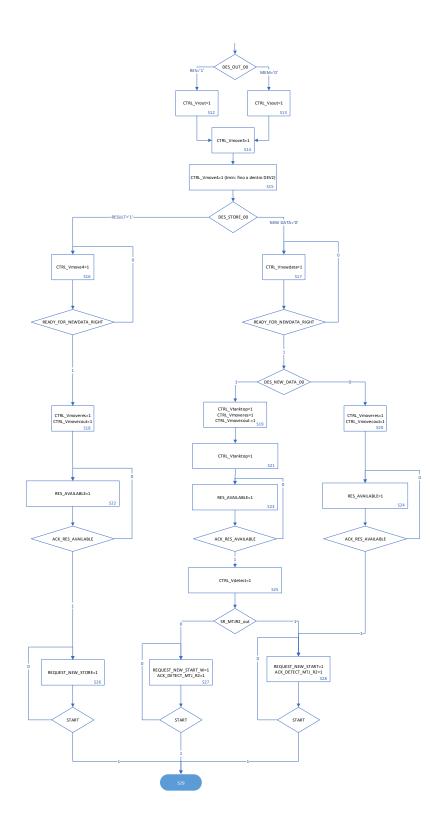

| 5.1 Cell 00                                                                                                                                  | 119 |  |

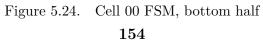

| 5.2 Cell 10                                                                                                                                  | 134 |  |

| 5.3 Master FSM and cell $01$                                                                                                                 | 137 |  |

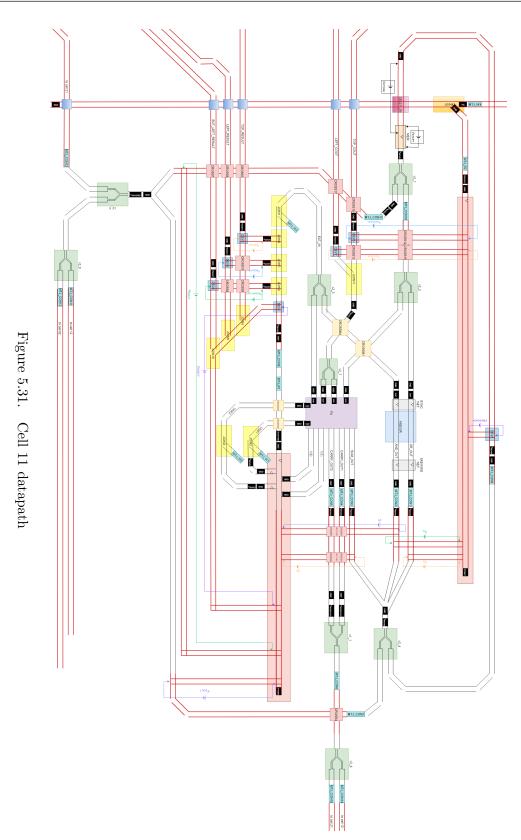

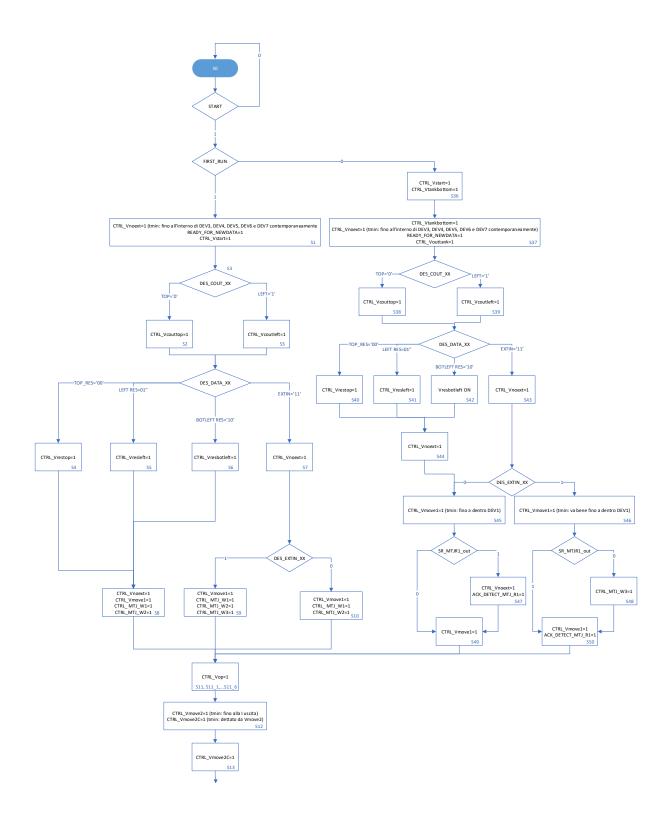

| 5.4 Cell 11                                                                                                                                  | 145 |  |

| 5.5 VHDL code                                                                                                                                | 147 |  |

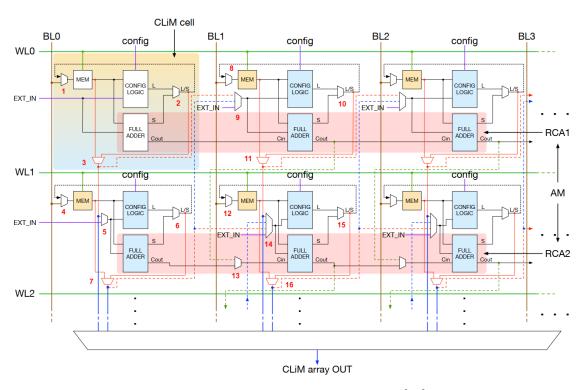

| 6 Logic in memory - second architecture                                                                                                      | 169 |  |

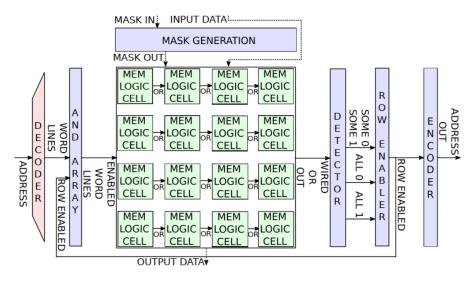

| 6.1 Original architecture and control blocks                                                                                                 | 170 |  |

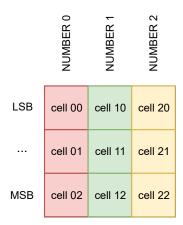

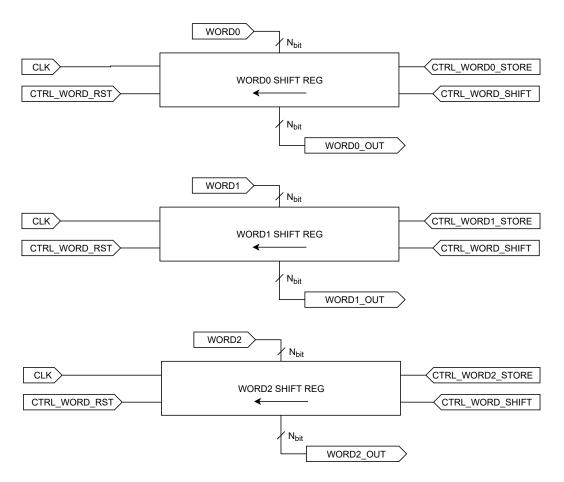

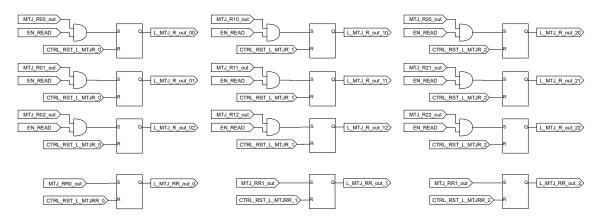

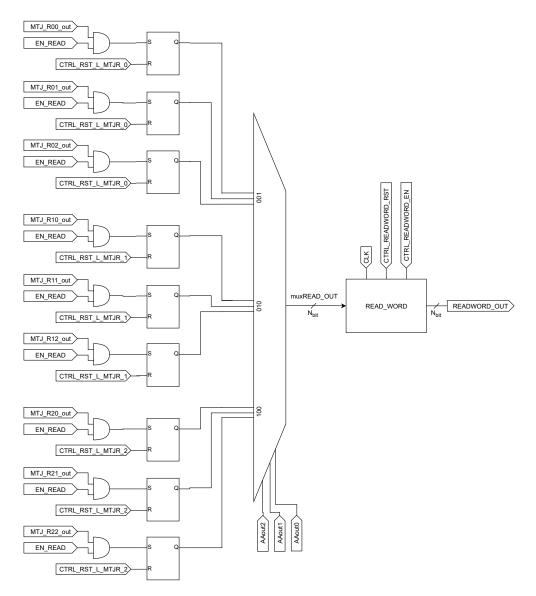

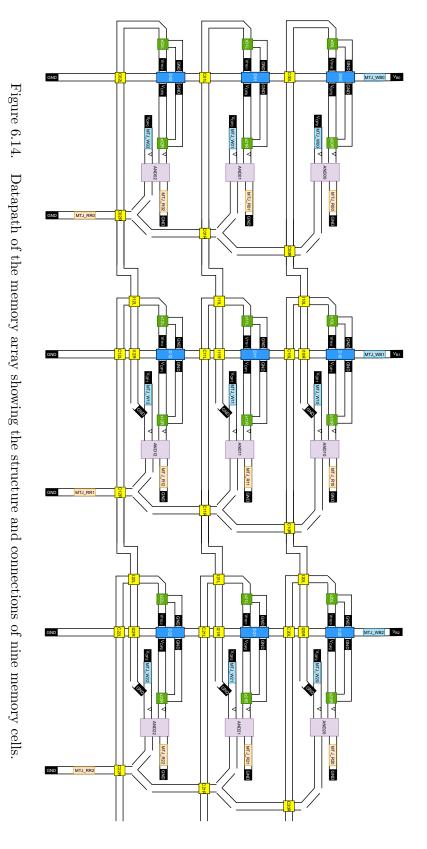

| 6.2 Memory array structure                                                                                                                   | 174 |  |

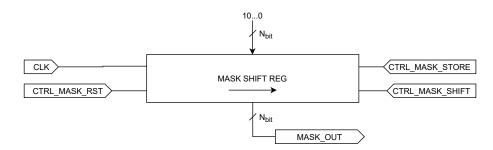

| 6.3 Control blocks                                                                                                                           | 181 |  |

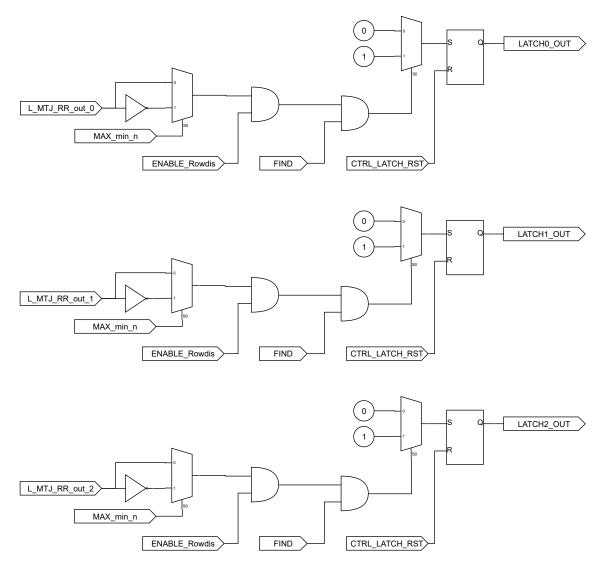

| $6.3.1  \text{Detector.}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                          |     |  |

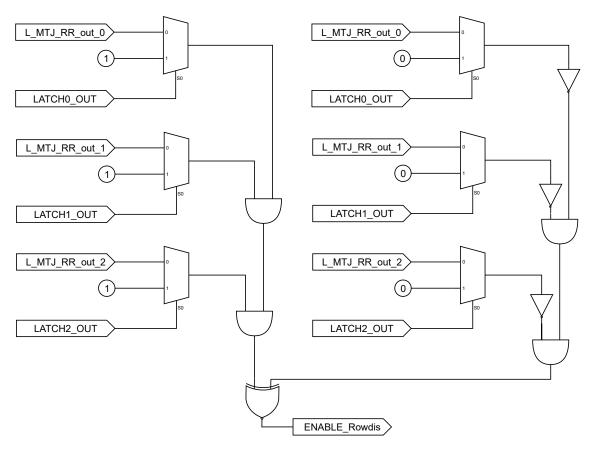

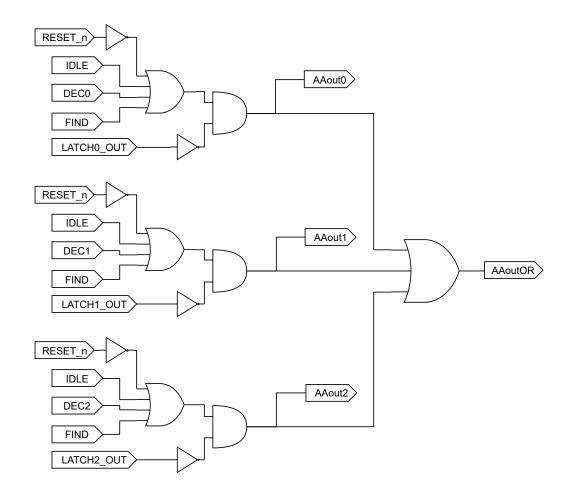

| 6.3.2 Row disabler                                                                                                                           | 183 |  |

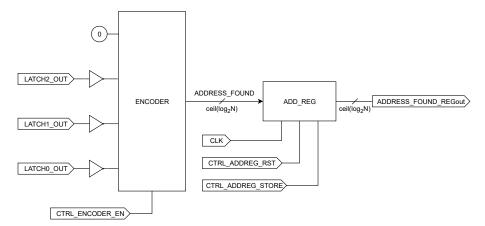

| 6.3               | $3.3  \text{Encoder} \dots \dots$ |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

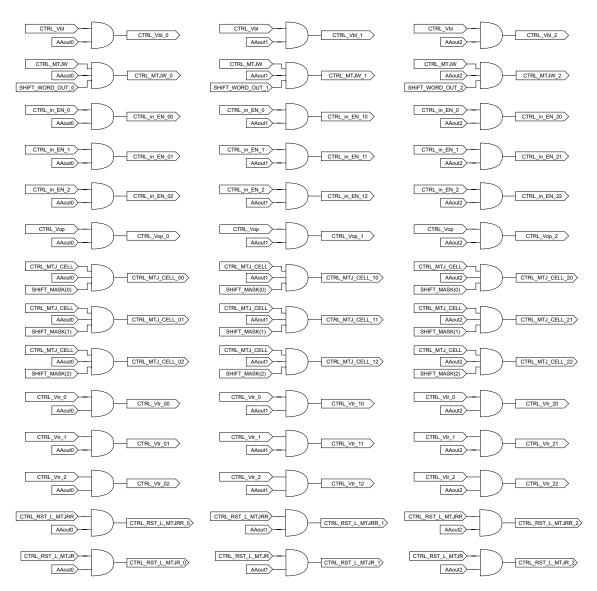

| 6.3               | 3.4 And array                                                                                                                           |

| 6.3               | 3.5 FSM-array adapter and FSM structure                                                                                                 |

| 6.4               | Conclusions                                                                                                                             |

| 7 <mark>Su</mark> | mmary and prospects for future studies $\ldots \ldots \ldots \ldots \ldots 204$                                                         |

| Bibl              | iography                                                                                                                                |

| App               | $endices. \dots \dots$            |

| A M               | $ m icromagnetic \ simulations \ code$ $ m . \ . \ . \ . \ . \ . \ . \ . \ . \ . $                                                      |

| A.1               | Not/Copy gate                                                                                                                           |

| A.2               | And/Or gate                                                                                                                             |

| A.3               | Balancing of current density                                                                                                            |

| B Ac              | lder VHDL code                                                                                                                          |

| B.1               | Adder - first version                                                                                                                   |

| B.2               | Adder - second version                                                                                                                  |

| B.3               | Adder - pipelined version                                                                                                               |

| C Lo              | gic in memory VHDL code - architecture 1                                                                                                |

| C.1               | Shared components                                                                                                                       |

| C.2               | Cell00                                                                                                                                  |

| C.3               | Cell10                                                                                                                                  |

| C.4               | Cell01                                                                                                                                  |

| C.5               | Cell11                                                                                                                                  |

| C.6               | Memory array                                                                                                                            |

| D Lo              | gic in memory VHDL code - architecture 2                                                                                                |

| D.1               | Array components and related files                                                                                                      |

| D.2               | Control blocks.                                                                                                                         |

| D.3               | Basic components                                                                                                                        |

| D.4               | FSM                                                                                                                                     |

| D.5               | Memory architecture                                                                                                                     |

| D.6               | Testbench                                                                                                                               |

## 1. Introduction

It is well known that the critical issue encountered by Moore's law since the beginning of the new millennium is the power dissipation, linked to the blast of leakage current due to the continuous miniaturization of CMOS devices. Spintronics is a technological field that aims to use the electron spin properties, rather than its electric charge, for storing and manipulating information. For this reason it is expected to carry some great advantages with respect to traditional electronic devices, such as non-volatility and low power consumption.

In the spintronics field many different possibilities have been explored. In some cases, like for the bubble memories, some of them even became a commercial product. However, bubble memories soon became uncompetitive in terms of cost and completely disappeared from the market within a decade [20]. The main issues were the need of applying an external magnetic field for manipulating them, besides their not so small dimensions. As a result, the great strides made in improving semiconductor memories completely wiped them out.

Another example are the domain walls (DWs), which have already been extensively studied both from a theoretical and from an experimental point of view. Many designs have also been proposed, like the DW-based racetrack memories, where the binary data is encoded like a sequence of spin-up or spin-down magnetic domains separated by DWs. However, the main issue of DWs is the high current density required for allowing their movement (depinning current density) with a reasonable velocity, and this raises again the issue of the Joule heating and of the consequent power dissipation.

Skyrmions are one of the possibilities for carrying information that are being explored in the field of spintronics. They show many advantages with respect to domain walls, like a lower depinning current density and a smaller size, which allows a denser storage of information. Theoretical studies have in fact proven that the depinning current density for isolated skyrmions can be as low as  $1 \times 10^8 \text{ A/m}^2$ , two or three orders of magnitude lower with respect to the depinning current density needed by domain walls [20]. Concerning its size, a skyrmion can have a diameter of only few nanometres, while a domain wall is hardly below 30 nm [20]. Since the mechanism which allows their motion while applying a current density is the same as for DWs, also their velocities are comparable under the same current applied; however, since the smaller skyrmions' dimensions allow to pack the same amount of information in a smaller space, even when moving at a lower velocity with respect to DWs they still allow to obtain a higher throughput. For this reason they are promising information carriers for future non-volatile, ultra-dense and low-power logic devices and memories.

Chapter 2 of this thesis tries to sum up the main characteristics and physical laws involved in the manipulation of skyrmions. A number of applications are also briefly presented, either to offer a more practical interpretation of the physical phenomena described, or to show the possibilities offered by the use of skyrmions as information carriers.

As proven by some of these applications, which have already appeared in literature, skyrmions can be exploited as information carriers both in logic gates and in racetrack memories. The goal of this thesis is to explore the possibilities offered by some of these designs when building a skyrmionic computing architecture. In particular, the model of logic gates used throughout the whole thesis comes from [5]. These logic gates, as it will be detailed more carefully in chapter 2, allow to perform the AND, OR and NOT elaboration of bits that are represented by skyrmions. The gates proposed in [5], however, were tested via micromagnetic simulations assuming a uniform current density throughout the gates, which is not a realistic assumption: the first aim of this thesis, then, is to prove that the behaviour of these structures is correct even when imposing the current density that should be found in reality inside the heavy metal layer of these gates. The results of the micromagnetic simulations performed with this goal can be found in chapter 3.

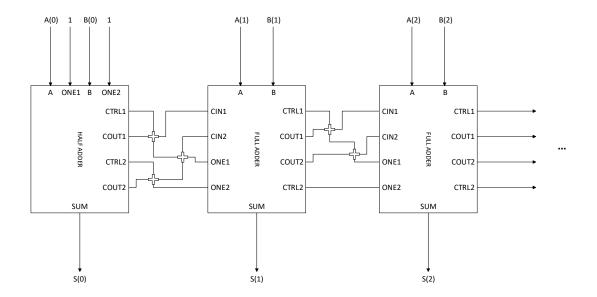

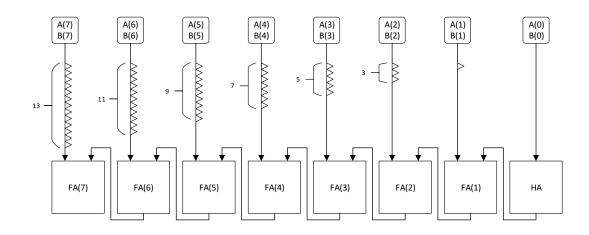

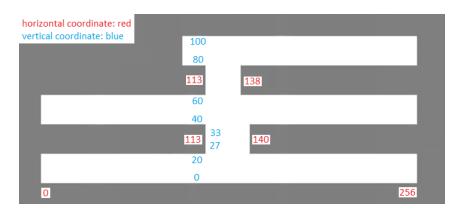

Once the behaviour of these gates is proven correct even under realistic assumptions, it makes sense to try to use them inside a more complex architecture. In chapter 4 the full adder proposed in [5] is used, slightly modified, to build a N-bit

ripple carry adder. The structure of the adder is optimized in order to reduce as much as possible the energetic inefficiencies, which are due to the need of providing skyrmions that are not needed as information carriers but only as enable signals; the performances of the adder are analysed as well, by assuming for the main physical constants and parameters the values that were found in the micromagnetic simulations of chapter 3. The design of a complex structure allows to identify some of the main challenges that still need to be solved from a physical and technological point of view: the most crucial point, in fact, is the absence, in literature, of something that could behave like the electrical via in the PCB (printed circuit boards). To date, in fact, no solution that allows two nanotracks to cross has been proposed yet.

Finally, the architectural analysis continues on a different path. Chapter 5 starts from the study of a logic in memory (LiM) architecture that has already appeared in literature, and adapts it in order to find a memory array based on skyrmions with the same functionalities and that allows the same algorithms to be executed. The LiM architecture addressed in chapter 5 allows a large flexibility and adaptability to a wide range of different algorithms, apart from introducing a mechanism useful to reuse all those skyrmions that have already been nucleated but that are no more useful for the computations; the resulting structure, however, is very complex, heavy and not optimized.

Giving up on the flexibility and on the energy-saving structures that were introduced in chapter 5, a new LiM architecture is studied in chapter 6. Focusing on the execution of a specific algorithm (the minimum/maximum search algorithm proposed in [37]), the resulting skyrmionic memory array becomes much lighter and smaller, and the execution more efficient. The LiM array obtained, however, is also less flexible and less efficient from an energetic point of view.

# 2. Physics and applications of skyrmions

In the following the main physical laws and properties of skyrmions will be described, together with the issues in using them as information carriers. Some applicative aspects, that can either be useful to better understand the practical meaning of some physical properties, or that can be helpful in solving the main issues, will be presented too. The aim of this chapter is not to give an exhaustive and detailed insight into the complex physical phenomena linked to these topological configurations, but just to offer an overview on the principal difficulties and on the main mechanisms involved when trying to use skyrmions as information carriers inside computing architectures. In the end of the chapter, moreover, will be described some applications which exploit and sum up well all the physical characteristics exposed in the first part. Among them will be presented also the results that are the starting point for the architectural analysis that is the subject of this thesis.

### 2.1. Physical properties

To employ skyrmions as information carriers it is of vital importance the ability of performing some elementary tasks, including their creation, manipulation, detection and eventually annihilation. The first topic addressed in this section is the structure of a skyrmion and what are the main energetic contributions that compete in its creation. Then will be described the laws of motion and the main possibilities available to move it along the device; finally it will be detailed how is possible to nucleate it and to detect it. The topic of the skyrmion radius will be discussed at the end of the section, since it exploits some results presented in other papers.

#### 2.1.1. Topological properties

#### 2.1.1.1. Topological charge

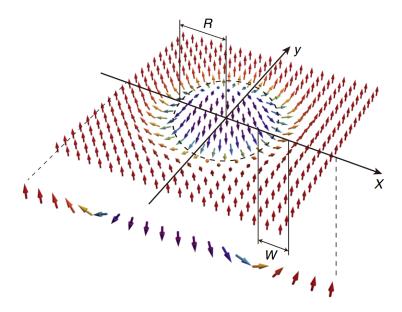

A magnetic skyrmion is a non-collinear 2D configuration of magnetic moments resulting from the competition of different energetic terms (which will be detailed in section 2.1.2.1). This configuration has a whirling structure, like shown in figure 2.1, and is described from a topological point of view by the topological charge Q, also called skyrmion number or Pontryagin number; its expression is <sup>1</sup>

$$Q = \frac{1}{4\pi} \int dx dy (\partial_x \boldsymbol{m} \times \partial_y \boldsymbol{m}) \cdot \boldsymbol{m}$$

(2.1)

where m is the unit vector representing the orientation of the local magnetic moment. The skyrmion number counts how many times the magnetic spins constituting the structure of the skyrmion can be wrapped around a unit sphere: all the spins at the boundary are collected into a single vector mapped on one pole of the sphere, and this is possible only because these spins point all in the same direction; the core is mapped at the opposite pole of the sphere, while the intermediate spins are mapped on the remaining parts of the sphere. In the case of a skyrmion-like structure, the topological charge is an integer equal to  $\pm 1$ .

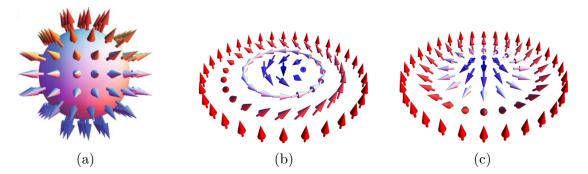

Figure 2.1. (a) Mapping of the Néel skyrmion onto the unit sphere. Figure extracted from [35]. (b) Bloch skyrmion, (c) Néel skyrmion. Figures extracted from [20].

<sup>&</sup>lt;sup>1</sup>Like observed in [23], the sign in this formula is not consistently defined in literature. An example in which the topological charge is defined with a minus sign can be found in [43].

The magnetization of a skyrmion in polar coordinates [19] is described by

$$\boldsymbol{M} = M_S \begin{bmatrix} \cos\phi(\varphi)\sin\theta(r)\\ \sin\phi(\varphi)\sin\theta(r)\\ \cos\theta(r) \end{bmatrix}$$

(2.2)

while the expression of  $\mathbf{r}$  in polar coordinates is  $\mathbf{r} = r(\cos\varphi, \sin\varphi)$ . Inserting equation 2.2 into equation 2.1 it can be obtained that

$$Q = \frac{1}{4\pi} \int_0^\infty dr \int_0^{2\pi} d\varphi \frac{d\theta(r)}{dr} \frac{d\phi(\varphi)}{d\varphi} \sin\theta(r) = \frac{1}{4\pi} \cos\theta(r) \Big|_{r=0}^{r=\infty} \phi(\varphi) \Big|_{\varphi=0}^{\varphi=2\pi}$$

(2.3)

This equation will be commented later in section 2.1.1.3.

The in-plane magnetization angle  $\phi$  is assumed to be a linear function of the azimuthal angle  $\varphi$  [19], so that

$$\phi = m\varphi + \gamma \tag{2.4}$$

This equation will be discussed later in section 2.1.1.5. For now is enough to remember this: let's assume that the skyrmion's structure lays in the *xy*-plane; the magnetic moments are organized on circumferences that are concentric with the skyrmion core (of course in first approximation and only if the skyrmion is not being deformed); the angle giving the position of each magnetic moment along the corresponding circumference with respect to the *x*-axis is  $\varphi$ , with unit vector  $\hat{\varphi}$ . Then,  $\phi$  is the angle that the spin at position  $\varphi$  has with respect to the unit vector  $\hat{\varphi}$ . For example, in the skyrmion represented in figure 2.1c, each moment has angle  $\phi = 0$ , while in the skyrmion shown in figure 2.1b each moment has an angle  $\phi = \frac{\pi}{2}$ .

#### 2.1.1.2. Dzyaloshinskii-Moriya Interaction

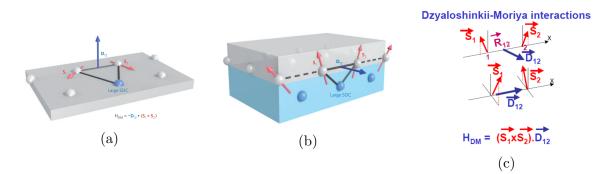

The Dzyaloshinskii-Moriya Interaction (DMI) is a key element for the stabilization of magnetic skyrmions. The bulk DMI comes from the breaking of the bulk inversion symmetry  $(\mathbf{r} \rightarrow -\mathbf{r})$  and from the presence of atoms with high spinorbit coupling in ferromagnetic alloys (for example B20 materials). The interfacial DMI (i-DMI) comes instead from the breaking of the structure inversion symmetry  $(z \rightarrow -z)$  at the interfaces of a multilayer system, where a thin layer of ferromagnetic material is deposited above a substrate made of a material with large spin-orbit coupling (for example *Co* on *Pt*) [9, 13].

These two types of DMI give rise to two different types of skyrmion structures, both shown in figure 2.1: the Bloch skyrmion (also spiral skyrmion) and the Néel skyrmion (also hedgehog skyrmion). In both cases there is a central domain and an outer domain, both with out-of-plane magnetization, separated by a domain wall. When the domain wall has a circular chirality (either clockwise or counterclockwise) the skyrmion is a Block skyrmion: in this case the magnetization rotates in the tangential plane while going from the core to the tail of the skyrmion. If the domain wall has a radial chirality (either inward or outward), then the skyrmion is of Néel type and the magnetization rotates in the radial plane [9, 20].

The DMI is an interaction between two magnetic spins mediated by the presence of a third non-magnetic atom with a strong spin-orbit coupling (SOC). The Hamiltonian of this interaction is

$$H_{DM} = -\boldsymbol{D}_{12} \cdot (\boldsymbol{S}_1 \times \boldsymbol{S}_2) \tag{2.5}$$

where  $S_1$  and  $S_2$  are the two magnetic spins and  $D_{12}$  is the DMI vector, perpendicular to the plane containing the three atoms involved. Starting from a ferromagnetic state with  $S_1$  parallel to  $S_2$ , the DMI tilts  $S_1$  with respect to  $S_2$  by a rotation around  $D_{12}$  [8]. This energetic term is minimized when the two magnetic spins are perpendicular to each other. At the same time, however, the exchange energy (detailed in section 2.1.2.1) in a ferromagnetic material is minimized when all the magnetic spins are aligned with each other: skyrmions are the result of the competition of these two mechanisms and of the minimization of the energy inside the system, like explained in section 2.1.2.1. The Néel skyrmion is the configuration minimizing the energy when  $D_{12} \perp R_{12}$ , the Bloch skyrmion instead minimizes the energy for  $D_{12} \parallel R_{12}$ [8], like shown in figure 2.2c, where  $R_{12}$  is the vector joining spin  $S_1$  with spin  $S_2$ .

The asymmetry due to the presence of the non-magnetic atom in the lattice or at the interface with the bottom metal layer is needed because, in this way, the DMI cannot be compensated by the DMI coming from a symmetric triangle [8].

The magnitude and sign of the vector  $D_{12}$  depend on the materials involved, on the interface and on the strength of the spin-orbit coupling of the non-magnetic

Figure 2.2. (a) DMI vector generated by the interaction of two atomic spins with an atom with strong SOC (blue) in a ultrathin magnetic film. (b) DMI vector generated at the interface between a FM thin layer (grey) and a metal with strong SOC (blue). Figures extracted from [8]. (c) The top configuration gives rise to a Néel skyrmion, the bottom configuration to a Bloch skyrmion. Figure extracted from [1].

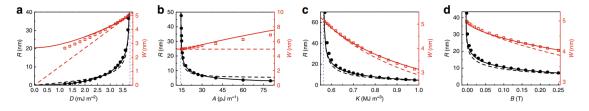

atom, and has an important role in determining the size of the resulting skyrmion, like detailed in section 2.1.6.

#### Spin-orbit coupling

While considering the orbiting motion of the electron around the proton from the point of view of the electron, the same atomic system can be seen like the proton orbiting around the electron. Due to Ampere's law, this positive charge motion generates a magnetic field, which of course will interact with the magnetic moment (proportional to the spin) of the electron: this phenomenon is known as spin-orbit coupling (SOC).

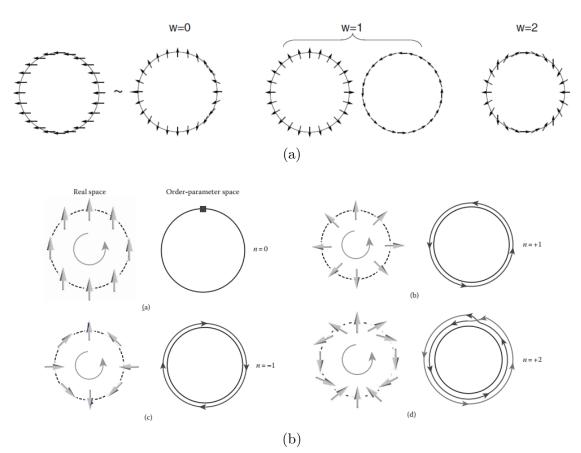

#### 2.1.1.3. Vorticity number

Another parameter useful in characterizing the skyrmion topological structure is the vorticity number m, defined as the winding number of the spin configurations projected into the xy-plane [20]. The winding number of an oriented curve counts how many times the curve encircles a well defined point in a plane in the counterclockwise direction. Describing this curve in polar coordinates  $(r,\theta)$ , the winding number can be computed like

$$W = \frac{\theta(end) - \theta(start)}{2\pi}$$

(2.6)

Since the initial and the final position, when following the full path of the curve around the point, must be coincident, then the two  $\theta$  angles must differ by an integer multiple of  $2\pi$ : this implies that the winding number is either a positive or negative integer.

In the specific case of magnetic topological structures, the winding number can be defined also like the total variation of the magnetization angle when moving counterclockwise along a circle traced around the centre of the structure, divided by  $2\pi$  [30, 1]. Each value of the magnetization angle can be mapped into a point on the circle, which in this context is formally called order-parameter space. According to the oriented movement along the order-parameter space, the winding number is computed.

Figure 2.3. (a) Examples of computation of the winding number for different spin configurations. The two cases with W = 1 can be assimilated to a Néel skyrmion (left) and to a Bloch skyrmion (right). Figure adapted from [3]. (b) Other examples of computation of the winding number, including the mapping on the order-parameter space. Figure extracted from [24].

The skyrmion number can be computed also through the vorticity number, using the relation

$$Q = \frac{m}{2} \left[ \lim_{r \to \infty} \cos(\theta(r)) - \cos(\theta(0)) \right]$$

(2.7)

which can be recognized simply like a rewriting of equation 2.3, where  $m = \frac{1}{2\pi} \phi(\varphi)|_{\varphi=0}^{\varphi=2\pi}$ is the vorticity that has just been defined. Observing 2.2 it can be deduced that  $\cos(\theta(r))$  is the z-component of the unit vector representing the local magnetic moment. So, the skyrmion number depends both on the vorticity and on the direction of the magnetization at the tail and at the core of the skyrmion. Is important to notice that, in a skyrmion, the direction of the core is always opposite to the direction of the tail, which is the same of the background magnetization present in the material.

#### 2.1.1.4. Helicity number and polarity

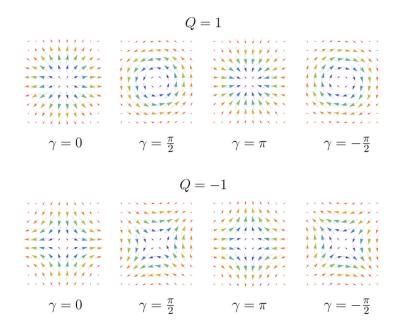

The third parameter needed to describe the skyrmion structure is the helicity number  $\gamma$ , determined uniquely by the type of DMI that intervenes in the energetic competition. A Bloch skyrmion (bulk DMI) is characterized by  $\gamma = \frac{\pi}{2}$  or  $\gamma = \frac{3\pi}{2}$ , while a Néel skyrmion (interfacial DMI) corresponds to  $\gamma = 0$  or  $\gamma = \pi$ . It's important to notice that the helicity does not contribute to the topological number.

Finally, the polarity p describes the orientation of the centre with respect to the z-direction: if p = 1 the magnetization of the core points in the positive z-direction, vice versa if p = -1.

#### 2.1.1.5. Meaning of the helicity number

Looking back at equation 2.4, which expresses the in-plane magnetization angle  $\phi$ , it can be recognized now that m is the vorticity number and  $\gamma$  the helicity number, while  $\varphi$  is the azimuthal angle of the polar coordinates system, describing the position of a point in the xy-plane. For both Bloch and Néel skyrmions the vorticity number is equal to 1, like it can be observed comparing figure 2.3a with the two structures shown in figure 2.1. In section 2.1.1.4 it has been said that for a Bloch skyrmion  $\gamma = \frac{\pi}{2}$  or  $\gamma = \frac{3\pi}{2}$ , while for a Néel skyrmion  $\gamma = 0$  or  $\gamma = \pi$ . Summing up:

From these expressions is easy to predict one of the experimental results reported in section 2.1.1.7: if  $\gamma = 0$  the in-plane magnetization is aligned with the unit vector  $\hat{\varphi}$  and the spins will be out-going, while if  $\gamma = \pi$  the magnetization is antiparallel with respect to  $\hat{\varphi}$  and the spins will be in-going. Similarly, if  $\gamma = \frac{\pi}{2}$  the in-plane magnetization has a 90° phase difference with respect to  $\hat{\varphi}$  and the spins of the Bloch skyrmion will rotate in a counterclockwise direction, while if  $\gamma = \frac{3\pi}{2}$  the phase difference is by  $-90^{\circ}$  and the spins rotate in a clockwise direction. The confirmation to these statements can be easily found in the top half of figure 2.4.

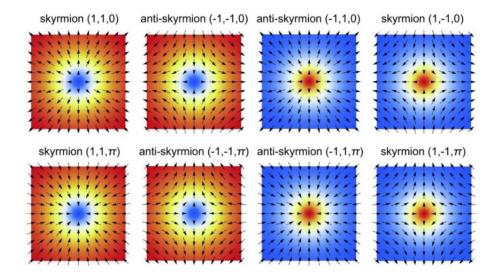

Figure 2.4. Magnetization configuration of skyrmions (Q = 1) and antiskyrmions (Q = -1) with fixed polarity (p = 1) and varying helicity  $\gamma$ . The length and direction of the arrows represents the in-plane magnetization component, while the colour represents the magnitude of the out-of-plane component: blue stands for +z, red for -z. Figure extracted from [12].

#### 2.1.1.6. Topological protection

The topological charge of skyrmions is always an integer equal to +1, at least if this particle is in a region larger than its diameter. For this reason, even if its spin texture may be deformed (for example due to the presence of impurities in the material), the Pontryagin number doesn't change and as a result the skyrmion can be neither destroyed nor separated into pieces: it is said to be topologically protected. This protection fails only when the skyrmion touches the sample edges, because in this condition the topological charge is allowed to change continuously: in this condition the skyrmion can be annihilated and the information it carries gets lost.

#### 2.1.1.7. Practical examples

Some examples, which show well the practical meaning of all the parameters presented up to this point, can be found in [40], where the results presented in [43] are exploited.

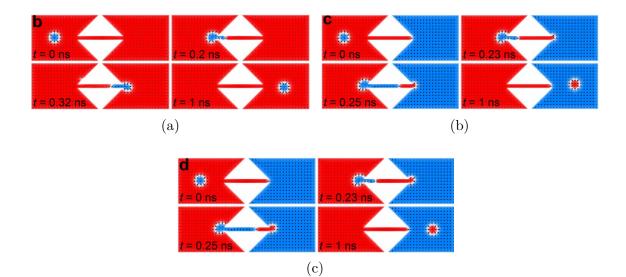

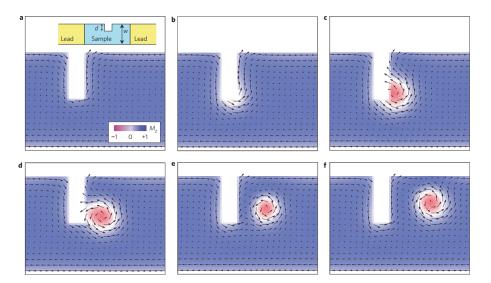

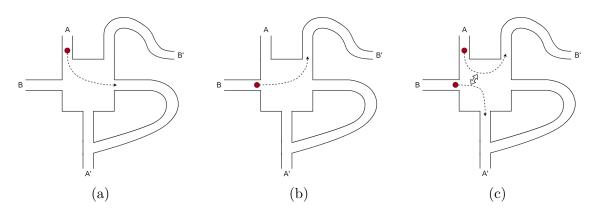

In [43] is demonstrated the possibility to convert in a reversible way a domain wall (DW) pair into a skyrmion and vice versa by using a junction made of a narrow nanowire (W < 2R, where W is the width of the nanotrack and R the skyrmion radius) connected to a wide nanowire (W > 2R). Like explained in [40], when a topological object, like a skyrmion, that previously was in a wide region enters a narrow region, it loses its topological numbers, like the skyrmion number and the helicity, and becomes a DW pair, which is a non-topological object (Q = 0); when it is ejected again into a new wide region, it is assigned new topological numbers to adjust the physical properties of the new region, which may be different from the properties of the former wide region. Skyrmions, as mentioned, are topologically protected only when the sample is enough large, and this protection is broken when they touch an edge: this is what happens when the skyrmion enters the narrow junction.

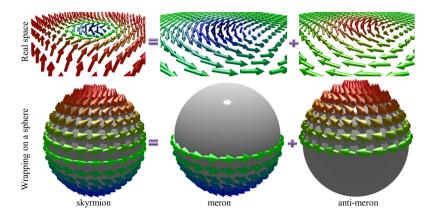

Another result of [43] that has been used in [40] (like explained in section 2.2.1) is shown in figure 2.5b (g-l frames): using the same junction but reducing the current density needed to move the domain wall, the particle obtained is not a skyrmion, but a meron. A meron is a different type of topological object, very similar to a skyrmion, but with  $|Q| = \frac{1}{2}$ : this means that its spins can wrap only the north pole

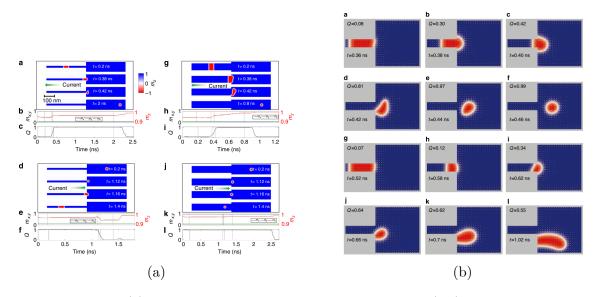

Figure 2.5. (a) Reversible conversion DW pair $\rightarrow$ skyrmion (a-c) and vice versa (d-f). g-l: when the size of the narrow part of the junction increases the DW pair is still converted into a skyrmion, but with more fluctuations in the radius and the shape (g-i); the skyrmion instead cannot be converted back into a DW pair (j-l). The middle plots show the time variation of the components of the magnetization; the bottom plots show the time variation of the skyrmion number. (b) Detail on the conversion from DW pair. a-f: when the current density is high enough the right DW pins at the junction, while the remaining part of the DW pair continues to move: as a result, the DW is deformed into a curve shape. When the other DW reaches the junction the skyrmion is formed. g-l: when the current density is reduced a meron is formed; the meron remains in contact with the nanotrack edge. Figures extracted from [43].

or the south pole of the unit sphere, like shown in figure 2.6. Its peculiarity is to remain attached to the sample edges even during its movement.

The first part of [40] verifies how different physical properties of the materials on the left and on the right side of a narrow nanotrack influence the assignment of new topological numbers to the skyrmion ejected from the junction, and allows to understand the practical meaning that these numbers have when considering the skyrmion's structure.

In figure 2.7a the parameter that changes from left to right is the sign of the DMI, which is positive on the left side and negative on the right side. As mentioned in section 2.1.1.4, the helicity is uniquely determined by the DMI. Since the skyrmions considered in this article are only of Néel type, the helicity can be either  $\gamma = 0$  or  $\gamma = \pi$ . On the left side the triplet of numbers  $(Q,m,\gamma)$  (topological charge, vorticity

Figure 2.6. Splitting a skyrmion in two halves, a meron and an anti-meron are obtained. A skyrmion covers the entire unit sphere, while a meron covers only half of it: so the topological charge of a meron is  $\pm \frac{1}{2}$ . Figure extracted from [22].

and helicity; this notation will be used from now on in all the rest of this thesis) is (1,1,0), whereas on the right side it is  $(1,1,\pi)$  (while in the junction it becomes (0,0,0)). Observing the picture, it can be noticed that the direction of the core has remained -z, while the spins from out-going have become in-going. So the helicity, like anticipated in section 2.1.1.5, determines the radial direction of the spins: when  $\gamma = 0$  the spins point outwards, when  $\gamma = \pi$  they point inwards.

In figure 2.7b the sign of the DMI is the same in both regions, while the direction of the background magnetization is reversed from left to right. According to equation 2.7, the topological charge depends both on the vorticity and on the direction of the spins at the core and at the tail of the skyrmion, and the spin direction at the tail is always the same as the background magnetization. Reversing the background magnetization then the second factor of 2.7 is reversed (from the picture it can be observed that the core now points in the +z direction and the tail in the -zdirection), while the vorticity remains unchanged: as a consequence the topological number becomes Q = -1 and the magnetic texture obtained is called antiskyrmion. Moreover, in this condition also the helicity changes from  $\gamma = 0$  to  $\gamma = \pi$  to minimize the energy of the system. So, the topological numbers change as  $(1,1,0) \rightarrow (-1,1,\pi)$ .

Finally, in 2.7c both the sign of the DMI and the background magnetization are reversed from left to right. Combining the two effects discussed above, then, the skyrmion becomes an antiskyrmion due to the background reversal, while the helicity remains unchanged and so the spin direction remains out-going. The change of the topological numbers is  $(1,1,0) \rightarrow (-1,1,0)$

Figure 2.7. Skyrmion $\rightarrow$ DW pair $\rightarrow$ skyrmion conversion. Red(blue) is the +z(-z) direction of the magnetization. (a) Reversing the sign of the DMI  $(1,1,0) \rightarrow (1,1,\pi)$  (b) Reversing the background magnetization  $(1,1,0) \rightarrow (-1,1,\pi)$  (c) Reversing both DMI and background magnetization  $(1,1,0) \rightarrow (-1,1,\pi)$ . Figures extracted from [40].

#### Skyrmions and antiskyrmions

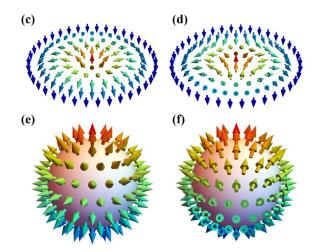

Like mentioned, antiskyrmions are spin textures very similar to skyrmions, but with topological charge equal to  $-1^2$ . They can still be mapped on a unit sphere, like shown in figure 2.8. Some examples of antiskyrmions can be found also in the bottom half of figure 2.4, where is shown the disposition of the in-plane magnetization by varying the helicity.

According to the examples just discussed and to the theory exposed up to now, the skyrmion and antiskyrmion main figures are summed up in table 2.1 (if the background magnetization is along +z, then  $\lim_{r\to\infty} \cos(\theta(r)) - \cos(\theta(0)) = 2$ , while if it is along  $-z \lim_{r\to\infty} \cos(\theta(r)) - \cos(\theta(0)) = -2$ ).

<sup>&</sup>lt;sup>2</sup>Some attention must be paid in the definition of antiskyrmions. Many examples in literature define as antiskyrmions those particles with Q = -1, while other authors consider antiskyrmions those particles that have m = -1, usually regardless of the topological charge. This inconsistency is evident when reading [40] and its supplementary information, [21], [13], [25] and [4]. In this thesis we conform ourselves to the first definition.

Figure 2.8. Mapping of a skyrmion (1,1,0) and of an antiskyrmion (-1, -1,0) with p = 1 on the unit sphere (order-parameter space). Figure extracted from [14].

Table 2.1. Summary of topological numbers for skyrmions and anti-<br/>skyrmionsBACKGROUND: +zBACKGROUND: -zSKYRMIONQ = 1, m = 1Q = 1, m = -1ANTISKYRMIONQ = -1, m = -1Q = -1, m = 1

The confirmation to this table can be found in the supplementary information of [40], where the figure 2.9 is shown.

#### 2.1.2. Micromagnetic model

The static properties of skyrmions can be studied theoretically with the help of the micromagnetic model, a theory used to describe the magnetization of a material from the nanoscale to the microscale. This length scale is large enough for avoiding the use of all the mathematical operators required by quantum mechanics, but at the same time it is small enough to carefully describe magnetization patterns like skyrmions or domain walls, among the others [19]. This theory allows to model the relationship between the spatial distribution of the effective magnetic field  $H_{eff}$ , determined by the energetic contributions competing in the system, and the magnetization vector field M [9]. The key equation on which the micromagnetic model is based is the Landau-Lifshitz-Gilbert (LLG) equation.

Figure 2.9. Examples of skyrmions and antiskyrmions by varying vorticity, helicity and background magnetization (and so polarization). Each triplet of numbers reports  $(Q,m,\gamma)$ ; red(blue) denotes the +z(-z) direction of the magnetization. Figure extracted from the supplementary information of [40].

#### 2.1.2.1. LLG equation

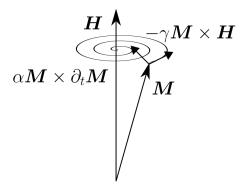

This equation relates the effective field  $H_{eff}$  to the time evolution of the magnetization vector field M. It is a torque equation, and its expression is

$$\frac{d\boldsymbol{M}}{dt} = -\gamma_0 \boldsymbol{M} \times \boldsymbol{H}_{eff} + \alpha \left( \boldsymbol{M} \times \frac{d\boldsymbol{M}}{dt} \right)$$

(2.10)

where M is the magnetization,  $H_{eff}$  is the effective magnetic field (not necessarily an external magnetic field, it can be also the field experienced locally by the magnetic moments inside the material),  $\gamma_0$  is the gyromagnetic ratio and  $\alpha$  the Gilbert damping coefficient. The first term describes the precession movement that the magnetic moments perform around the effective magnetic field when they are not fully aligned with it: this is known as Larmor precession. While performing this precession movement the magnetization also relaxes along the field line, finally becoming aligned with it, in order to minimize the energy of the system: this is modelled by the second term, containing the Gilbert damping.

It can be demonstrated [19] that only the direction of the magnetization changes with time, while its magnitude remains constantly equal to the saturation magnetization  $M_s$ .

Figure 2.10. Sketch of the Larmor precession performed by a magnetic moment around a field line of  $H_{eff}$ , and of the Gilbert damping contribution which, determining a spiraling motion around the field line, eventually makes the magnetic moment align with it. Figure extracted from [19].

The direction of the effective magnetic field is the direction in which the magnetization will have the minimum of the micromagnetic energy: therefore the effective field can be written in terms of the micromagnetic energy [19] as

$$\boldsymbol{H}_{eff} = -\frac{1}{\mu_0} \frac{\partial E_V}{\partial \boldsymbol{M}} \tag{2.11}$$

where  $E_V$  is the micromagnetic energy density.

#### Micromagnetic energy density

The contributions to the micromagnetic energy come from the exchange energy, the Zeeman energy, the demagnetizing field energy, the anisotropy energy and the DMI. Also other terms could be considered, like the RKKY (Ruderman-Kittel-Kasuya-Yosida) interaction, but when considering skyrmions in most of the cases they are neglected, so they won't be considered here.

**Exchange energy** The exchange interaction (sometimes also Heisenberg interaction) is the phenomenon which makes the magnetic moments inside a ferromagnetic material align with each other, allowing them to generate a magnetic field observable from the external. If the sign of the exchange constant J present in the Hamiltonian of this interaction is positive, then the material is a ferromagnetic material and the spins align parallel to each other; if the sign of J is negative, instead, the material is an antiferromagnet and the spins arrange antiparallel to each other. The energy density of the exchange interaction is [20]

$$E_V = A[\nabla \boldsymbol{m}]^2 \tag{2.12}$$

where A is the exchange constant.

**Zeeman energy** When applying an external magnetic field, the magnetic moments tend to align with its field lines: this is due to the Zeeman interaction. Its energy density is [43]

$$E_V = -\mu_0 \boldsymbol{M} \cdot \boldsymbol{H}_{ext} \tag{2.13}$$

where  $H_{ext}$  is the magnetic field applied externally.

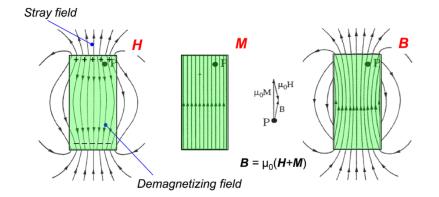

**Demagnetizing field energy** The magnetic induction is  $\boldsymbol{B} = \mu_0(\boldsymbol{H} + \boldsymbol{M})$ , where  $\boldsymbol{H}$  is the magnetic field and  $\boldsymbol{M}$  is the magnetization. Since  $\boldsymbol{M} = \chi \boldsymbol{H}$ , where  $\chi = \mu_r - 1$  is the susceptibility, then  $\boldsymbol{B} = \mu_0(1 + \chi)\boldsymbol{H} = \mu_0\mu_r\boldsymbol{H}$ .

Inside a magnetic material H is directed oppositely with respect to M, like shown in figure 2.11. For this reason, when considering the value of B inside the material, H contributes by reducing this value. This is why it is called demagnetizing field (while it is named stray field outside the material).

The energy density associated to the demagnetizing field  $H_d$  is

$$E_V = -\frac{\mu_0}{2} \boldsymbol{M} \cdot \boldsymbol{H}_d(\boldsymbol{M}) \tag{2.14}$$

Anisotropy energy The magnetocrystalline anisotropy is the property of some magnetic materials which makes some directions for the magnetization more energetically favourable than others; it is is linked to the spin-orbit coupling and to the atomic structure of the material. As a result, some directions may be easier to be magnetized than others. In particular, when this energetically favourable direction (called easy-axis) is perpendicular to the material, then we're dealing with the perpendicular magnetic anisotropy (PMA). The PMA can be found in some layered ultrathin films, like for example Pd/Co [19].

Figure 2.11. Depiction of the magnetic field  $\boldsymbol{H}$ , the magnetization  $\boldsymbol{M}$  and the magnetic induction  $\boldsymbol{B}$  inside a magnetic material. The magnetic field  $\boldsymbol{H}$  takes the name of demagnetizing field inside the material and of stray field outside it. Figure adapted from [7].

The energy density for the PMA is [43]

$$E_V = K_u [1 - (\boldsymbol{m} \cdot \hat{\boldsymbol{z}})^2]$$

(2.15)

where  $K_u$  is the uniaxial anisotropy constant and the unit vector  $\hat{z}$  represents the easy-axis.

In layered structures of ultrathin films, where the surface effects are not negligible, a form of PMA arises at the interface due to exchange interactions between some of the electronic orbitals of the materials involved. It has been discovered that the strength of this PMA can be modified by applying an external electric field: this field modifies the occupation of the orbitals and so is able to affect the exchange interactions [19].

As a result, if  $K_u$  is the PMA constant, the voltage controlled PMA will induce a variation  $\Delta K_{uv}E$  dependent on the electric field applied, so that the expression of the total PMA constant is [42]

$$K_{uv} = K_u + \Delta K_{uv} E \tag{2.16}$$

Of course, according to the sign of the z-component of the electric field, the PMA can either increase or decrease with respect to its bias level  $K_u$ .

**DMI energy** The bulk DMI energy density is [19]

$$E_V^{(bulk)} = D\boldsymbol{m} \cdot (\nabla \times \boldsymbol{m}) \tag{2.17}$$

The interfacial DMI energy density is instead (assuming to consider an ultrathin film, where  $\frac{\partial \mathbf{m}}{\partial z} = 0$ ) [43]

$$E_V^{(interfacial)} = D[m_z(\nabla \cdot \boldsymbol{m}) - (\boldsymbol{m} \cdot \nabla)m_z]$$

(2.18)

Summing all these energy density contributions together the total energy density  $E_{V,TOT}$  is obtained. The total energy of a system of volume V is

$$E_{TOT} = \int_{V} E_{V,TOT} dV \tag{2.19}$$

The spin configuration then is found by minimizing the total energy  $E_{TOT}$  [1].

#### 2.1.3. Motion

There are many possibilities both for nucleating and for moving skyrmions: some of them consist in applying an external magnetic field or temperature gradients. However, is clear than none of these options can be easily used inside an integrated circuit based on skyrmions, where it would be preferable to use current-based mechanisms instead.

When it comes to current, there are mainly two mechanisms available, both exploiting the spin-transfer-torque phenomenon.

#### 2.1.3.1. Spin Transfer Torque (STT)

When a charge current is injected into a material with a certain magnetization pattern, the spin of each conduction electron will interact with the magnetization vector field. This interaction leads to the formation of two torques: one tends to align the spin of the electron with the direction of the local magnetic moment, while the other, equal and opposite due to the conservation of the total angular momentum, at the same time tries to align the local magnetization with the direction of the electron spin. This is the spin-transfer-torque (STT) mechanism.

The STT contributes in modifying the orientation of the local magnetic moment: for this reason it can be included in the LLG equation. Since the current flows inside the ferromagnet along the in-plane direction, this torque is indicated as  $\tau_{IP}$ . It is composed by two contributions. The first is the adiabatic STT, where adiabatic refers to the assumption that the spin of the electron passing through the magnetic material relaxes fast enough so that is always aligns with the local magnetic moment [19]. The second term of  $\tau_{IP}$  has been added phenomenologically to explain unexpected experimental results and it is the non-adiabatic STT: the adiabatic approximation fails when the magnetization pattern changes so quickly in space that the electrons are not fast enough to align their spin with the local magnetic moment.

The expression of  $\tau_{IP}$  is

$$\boldsymbol{\tau}_{IP} = \frac{\gamma_0 \hbar P}{2\mu_0 e M_S} (\boldsymbol{j} \cdot \nabla) \boldsymbol{m} - \frac{\gamma_0 \hbar P}{2\mu_0 e M_S} \beta \boldsymbol{m} \times (\boldsymbol{j} \cdot \nabla) \boldsymbol{m}$$

(2.20)

where the first term is the adiabatic STT and the second term is the non-adiabatic STT. Here  $\gamma_0$  is the gyromagnetic ratio, P is the polarization coefficient of the inplane electrical current, e is the electron charge,  $M_S$  is the saturation magnetization,  $\boldsymbol{j}$  is the in-plane electrical current flowing through the ferromagnet,  $\boldsymbol{m}$  is the normalized magnetization, and  $\beta$  is the non-adiabaticity factor, quantifying the relative strength of the non-adiabatic STT with respect to the adiabatic STT.

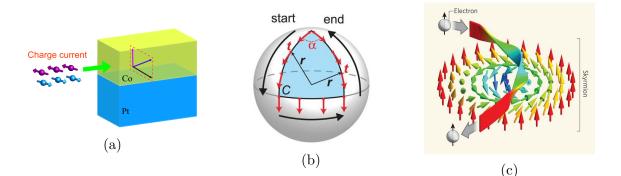

The term  $\tau_{IP}$  is added to the LLG equation when a current is flowing along the in-plane direction of a ferromagnet. The geometry used for the skyrmion motion that uses this effect is then called current-in-plane (CIP) geometry and is shown in figure 2.12a.

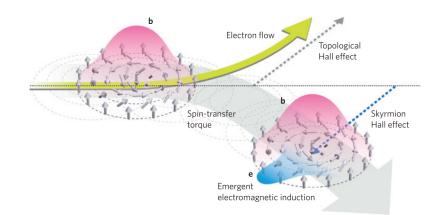

As mentioned, the spins of the conduction electrons exert a torque on the spin texture of the skyrmion; at the same time, the spin texture exerts a torque equal in magnitude and opposite in sign on the spin of the conduction electrons. As a result, the magnetic moments of the skyrmion subjected to the torque will rotate, allowing the movement of the particle, and at the same time the conduction electrons are deflected from the original direction of the current flux: this is known as topological Hall effect, and the reason behind this is the Berry phase.

The Berry phase is the rotation that a vector experiences while moving along a closed path on a curved surface. The skyrmion, as already mentioned, is a 2D structure, but the magnetic moments that constitute it can be organized on a unit sphere: assuming that the conduction electrons are able to follow exactly the orientation of the local magnetic moment of the skyrmion (adiabatic approximation), while crossing the particle they gain a Berry phase. This Berry phase is the reason behind the emergent magnetic field experienced by the conduction electrons. This field will make the conduction electrons experience a Lorentz force

$$F = q(\boldsymbol{E} + \boldsymbol{v} \times \boldsymbol{B}) \tag{2.21}$$

If the skyrmion texture is localized in the xy plane, the emergent field points along the z-axis, so the Lorentz force belongs to the xy plane and is perpendicular to the motion of the conduction electrons, making them deflect from their original direction [19].

Figure 2.12. (a) CIP configuration: a spin-polarized current flows directly inside the FM layer (yellow) deposited above the HM layer (blue). Figure extracted from [20]. (b) Sketch of the Berry phase  $\alpha$  acquired by a vector t (depicted in red) in the movement along the oriented curve on the curved surface of a sphere. Figure extracted from [11]. (c) Effect of the torque exerted by the skyrmion texture on the spin of the conduction electron and depiction of the topological Hall effect. Figure extracted from [32].

#### 2.1.3.2. Spin Hall Effect (SHE)

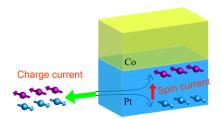

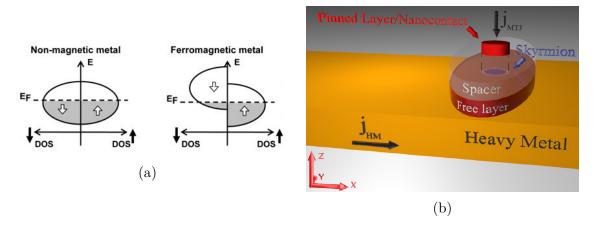

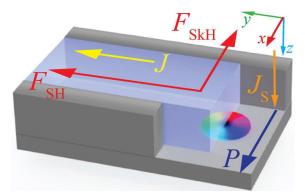

The spin Hall effect is a phenomenon that originates in spin-Hall devices, where a ferromagnetic (FM) thin film is deposited above a heavy metal (HM) substrate, like shown in figure 2.13. Here the electrical current is injected inside the HM layer. Due to spin-dependent scattering mechanisms (which include also SOC [29]), the electrons will experience a deflection perpendicular to their flow direction and to the orientation of their spin. As a result, the SHE leads to an accumulation of charges at the sides of the wire, and each side is populated by electrons with a well defined spin orientation. For example, if the current flows in the +x-direction and if the anomalous velocity acquired by the electrons is directed along the +z-axis, making them accumulate at the top surface of the wire, their spin orientation will be along the +y-axis. Moreover, this spin current flowing in the z-direction and polarized along the y-direction, can be collected by the FM thin film deposited above the HM substrate. This transverse spin current then will interact with the magnetization of the HM layer, again through the STT mechanism [26, 29].

Since this time the current that interacts with the magnetization is directed perpendicularly to the film plane, this configuration is called current-perpendicularto-plane (CPP) geometry.

Figure 2.13. CPP configuration: an electrical current flows inside the HM layer (blue); the spin-Hall effect determines the creation of a spin-polarized current directed in the vertical direction that is collected by the FM layer (yellow) deposited above. Figure extracted from [20]

The expression of the torque  $\tau_{SHE}$  associated to this phenomenon is

$$\boldsymbol{\tau}_{SHE} = -\frac{\gamma_0 \hbar j \theta_{sh}}{2\mu_0 e M_S t_f} \boldsymbol{m} \times (\boldsymbol{m} \times \boldsymbol{p})$$

(2.22)

where  $t_f$  is the thickness of the FM layer, p is the spin-current polarization direction (+y in the example reported above), j is the current density and  $\theta_{sh}$  is the spin Hall angle. The spin Hall angle measures the efficiency of the conversion from charge current  $J_{ch}$  to spin current  $J_s$  and depends on material parameters [39]. Its

expression is

$$\theta_{sh} = \frac{J_s}{J_{ch}} \tag{2.23}$$

#### 2.1.3.3. Thiele equation and skyrmion Hall effect

When assuming that the skyrmion moves without deforming its texture, the time-dependent evolution of the magnetization pattern can be written like

$$\boldsymbol{M}(\boldsymbol{r},t) = \boldsymbol{M}_0[\boldsymbol{r} - \boldsymbol{R}(t)]$$

(2.24)

where  $M_0$  is the initial configuration of the skyrmion when located in the axis origin, and  $\mathbf{R}(t)$  is the position of the skyrmion's centre of mass at time t [27]. Thiele recognized that, in this case, the time derivative of the magnetization can be written as

$$\frac{d\boldsymbol{M}}{dt} = \frac{\partial \boldsymbol{R}}{\partial t} \frac{\partial \boldsymbol{M}}{\partial \boldsymbol{R}} = \frac{\partial \boldsymbol{R}}{\partial t} \left( -\frac{\partial \boldsymbol{M}}{\partial \boldsymbol{r}} \right) = -(\boldsymbol{v} \cdot \nabla) \boldsymbol{M}$$

(2.25)

Substituting the time derivatives that appear in the LLG equation with the expression 2.25, and converting the LLG equation into a force density equation, like detailed in [27], the LLG equation can be rewritten into the Thiele equation [19]. Its expression for the CIP configuration is

$$\boldsymbol{G} \times (\boldsymbol{v}_s - \boldsymbol{v}_d) + \mathcal{D}(\beta \boldsymbol{v}_s - \alpha \boldsymbol{v}_d) + \nabla \boldsymbol{V}(\boldsymbol{r}) = 0$$

(2.26)

Here  $\mathbf{G} = (0,0,G) = (0,0,4\pi Q)$  is the gyromagnetic coupling vector;  $\mathbf{v}_d$  is the drift velocity of the skyrmion core;  $\mathbf{v}_s$  is the velocity of the conduction electrons, where  $\mathbf{v}_s = -\frac{Pa^3}{2eM_s}\mathbf{j}$  (*P* is the spin polarization of the electrical current and *a* is the lattice constant);  $\mathcal{D}$  is the dissipative force tensor, where  $\mathcal{D} = \begin{pmatrix} \mathcal{D}_{xx} & 0\\ 0 & \mathcal{D}_{yy} \end{pmatrix}$  and  $\mathcal{D}_{xx} = \mathcal{D}_{yy} = \int_{unit \ cell} (\partial_i \mathbf{m} \cdot \partial_j \mathbf{m}) dx dy$  for both skyrmions and antiskyrmions;  $\beta$  is the non-adiabaticity factor;  $\alpha$  is the Gilbert damping;  $\nabla \mathbf{V}(\mathbf{r})$  represents the repulsion forces due to process impurities, the nanotrack edges or due to skyrmion-skyrmion repulsion.

Considering a skyrmion that moves far away from the edges along the x-axis (so,

$\boldsymbol{v}_{s,x} \neq 0, \ \boldsymbol{v}_{s,y} = 0 \text{ and } V = 0$ , it can be found that [41]

$$\begin{cases} v_{d,x} = \left(\frac{\beta}{\alpha} + \frac{G^2}{\alpha} \frac{\alpha - \beta}{G^2 + (\alpha D)^2}\right) v_{s,x} \\ v_{d,y} = \left(\mathcal{D}G \frac{\alpha - \beta}{G^2 + (\alpha D)^2}\right) v_{s,x} \end{cases}$$

(2.27)

The Thiele equation for the CPP configuration is

$$\boldsymbol{G} \times \boldsymbol{v}_d - \alpha \boldsymbol{\mathcal{D}} \cdot \boldsymbol{v}_d + 4\pi \boldsymbol{\mathcal{B}} \cdot \boldsymbol{J}_{HM} + \nabla \boldsymbol{V}(\boldsymbol{r}) = 0$$

(2.28)

Here  $\mathcal{B} = \begin{pmatrix} \mathcal{B}_{xx} & 0 \\ 0 & \mathcal{B}_{yy} \end{pmatrix}$ , where  $\mathcal{B}_{xx} = \mathcal{B}_{yy}$  for skyrmions and  $\mathcal{B}_{xx} = -\mathcal{B}_{yy}$  for antiskyrmions, is the tensor linked to the STT effect quantifying the efficiency of the spin Hall-spin torque over the spin texture of the skyrmion [18], and it can be determined starting from the spin configuration;  $J_{HM} = \frac{J_s}{\theta_{sh}}$  is the electrical current density flowing in the HM, where  $J_s$  is the spin current density and  $\theta_{sh}$  is the spin Hall angle of the HM [20, 18].

From the Thiele equation of the CPP configuration it can be proven that the velocity components of both skyrmion and antiskyrmion are [15, 17]

$$\begin{cases} v_{d,x} = \frac{-j\alpha \mathcal{D}\mathcal{B}_{xx}}{(\alpha \mathcal{D})^2 + Q^2} \\ v_{d,y} = \frac{jQ\mathcal{B}_{xx}}{(\alpha \mathcal{D})^2 + Q^2} \end{cases}$$

(2.29)

It has been demonstrated in [20] that the driving efficiency of the CPP configuration is much higher with respect to the efficiency of the CIP configuration: applying the same current density, the skyrmion velocity obtained with the CPP geometry is higher than the velocity obtained with the CIP geometry.

The drift velocity  $\mathbf{v}_d$  for both geometries includes not only a component  $v_{d,x}$ parallel to the direction of the driving current, but also a transverse component  $v_{d,y}$ perpendicular to it that drives the skyrmion towards the track edges. The term inside the Thiele equation that gives rise to this component is the Magnus force  $\mathbf{G} \times \mathbf{v}_d$ . Since  $\mathbf{G} = (0,0,4\pi Q)$ , the reason why the skyrmion is subjected to this force is that it carries a topological charge different from 0. With both configurations, increasing the current density also the skyrmion velocity will increase. However, there is a limit current density above which the repulsive forces from the edges of the nanotrack, due to the tilting of the magnetization induced by the DMI [15, 16] and taken into account with the term  $\nabla V(\mathbf{r})$ , are not strong enough to balance the Magnus force, so that the skyrmion collides with the edges and gets annihilated due to the breaking of the topological protection.

The Magnus force behaves like the Lorentz force for electrical charges and gives rise to a phenomenon very similar to the traditional Hall effect, even if here the skyrmion does not carry any electrical charge but only a topological charge. This is why this effect is called skyrmion Hall effect.

Like discussed in [18] and in [15], reversing the sign of the magnetization and thus the sign of the topological charge, turning it from Q = +1 to Q = -1, the topological Magnus force  $\mathbf{G} \times \mathbf{v}_d$  is reversed, since  $\mathbf{G} = (0,0,4\pi Q)$  is strictly related to the skyrmion number. As a consequence, reversing the sign of the topological charge, the skyrmions become antiskyrmions and will be accumulated at the opposite edge of the sample, in strict analogy to what happened with the Hall effect for electrical charges. Of course, when the Magnus force deviates the trajectory of an antiskyrmion, the resulting effect is called antiskyrmion Hall effect.

This can be proven also looking at the expression of  $v_{d,y}$  for both geometries:

$$v_{d,y} = \begin{cases} \left( \mathcal{D}G \frac{\alpha - \beta}{G^2 + (\alpha \mathcal{D})^2} \right) v_{s,x} & \text{for CIP} \\ \\ \frac{jQ\mathcal{B}_{xx}}{(\alpha \mathcal{D})^2 + Q^2} & \text{for CPP} \end{cases}$$

(2.30)

The  $v_{d,y}$  component for the CIP case is directly proportional to  $G = 4\pi Q$ : reversing the sign of the topological charge also the velocity component will be reversed. The component for the CPP case is proportional directly to Q and thus behaves in the same way. So, applying the same current density, both skyrmions and antiskyrmions propagate in the x-direction with the same speed, while they exhibit equal and opposite transverse velocities.

The (anti)skyrmion Hall angle is defined as the angle between the direction of the applied current and the direction of the resulting motion of the texture, and its expression is

$$\Phi_{sk} = \arctan\left(\frac{v_y}{v_x}\right) \tag{2.31}$$

Figure 2.14. Schematic representation of the topological Hall effect and of the skyrmion Hall effect. Electrons are deflected by the Lorentz force due to the emergent magnetic field of the skyrmion, and this results into the topological Hall effect. The velocity of the skyrmion has a transverse component due to the Magnus force in the Thiele equation, and this is the skyrmion Hall effect. Due to the time variation of the emergent magnetic field carried by the skyrmion, is present also an emergent electric field, that is, emergent electromagnetic induction. Figure extracted from [31].

Focusing on the CPP geometry, both the skyrmion and the antiskyrmion Hall angle [15, 18] are equal to

$$\Phi_{sk} = \arctan\left(-\frac{Q}{\alpha \mathcal{D}}\right) \tag{2.32}$$

This equality can be easily found by substituting equation 2.29 inside the definition of the (anti)skyrmion Hall angle.

Due to some differences inside the symmetry of the spin texture constituting the antiskyrmions, the antiskyrmion Hall angle, differently from the skyrmion Hall angle, is dependent on the angle  $\theta$  that the applied current density has with the *x*-direction, so that its complete expression actually is

$$\Phi_{ask} = \arctan\left(-\frac{Q}{\alpha \mathcal{D}}\right) - 2\theta \tag{2.33}$$

It has been proven in [15] that if the current is injected along the direction  $\theta = \frac{1}{2} \arctan(-\frac{Q}{\alpha D})$ , so that  $\Phi_{ask} = 0$ , the antiskyrmion Hall effect is cancelled and the texture moves exactly along the current direction, without any transverse motion. Since the maximum speed at which both skyrmions and antiskyrmions can move inside a nanotrack without being annihilated is limited by the competition between

the (anti)skyrmion Hall effect and the edge repulsion, enabling a motion with zero antiskyrmion Hall angle can largely increase the maximum velocity of antiskyrmions, allowing a higher throughput for the devices potentially based on them.

#### 2.1.3.4. Mitigation of the skyrmion Hall effect

Since the skyrmion Hall effect may lead to the annihilation of the particle and so of the information it carries, it is a well known issue in the design of skyrmionic devices. Looking at the expression of  $v_{d,y}$  in 2.27, it can be noticed that if  $\alpha = \beta$  the transverse velocity component is cancelled and the skyrmion Hall effect disappears. However, these two parameters depend on material properties, and it's clear that is impossible to rely on this equality from a design point of view; of course, thanks to the repulsion from the edges of the nanotrack, the skyrmion is able to travel along the nanotrack even if  $\beta$  is not too different from  $\alpha$ , but in this case the current density must remain below a certain threshold so that the Magnus force doesn't overcome the repulsive forces from the boundaries, and this of course limits the maximum throughput of the device. So, it's clear why some other solutions to the skyrmion Hall effect must be found, and these solutions must be able to work both with the CIP and with the CPP geometry (even if the CPP configuration has a higher driving efficiency with respect to CIP).

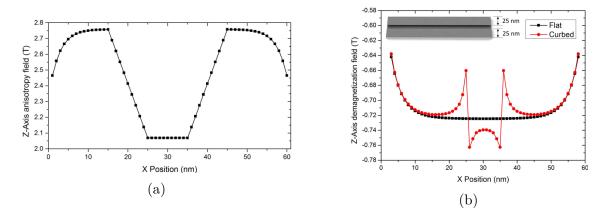

In [10] two methods have been proposed for engineering a potential well, needed for confining the skyrmion in the centre of the nanotrack and preventing its annihilation. The first method proposed tunes the magnetic anisotropy along the width of the nanotrack, reducing the value of the PMA in the centre with respect to the edges. This will form a path of lower resistance all along the nanotrack, since there the magnetization will be allowed to flip more easily due to a lower value of the effective field. Of course, however, there is still a certain value of velocity above which the repulsion from the edges won't be enough and the skyrmion can be destroyed. The patterning of the PMA can be performed by ion irradiation, combined together with high-resolution litography. Of course this must be done during the fabrication step and is a static control, without any possibility of change during the lifetime of the device.

The second method proposed is to add more ferromagnetic material at the edges of the nanotrack. Doing so the demagnetization field is increased at the inner edges of the modified nanotrack and decreased at its centre: so there is again a magnetic potential well which forces the skyrmion to move at the centre of the track. The threshold velocity above which annihilation happens in this case is even higher that the one that can be obtained through PMA patterning.

Figure 2.15. (a) z-axis anisotropy field along the width of the nanotrack after patterning of the PMA constant:  $K_u$  has a lower value at the centre of the nanotrack. (b) z-axis demagnetization field for the traditional nanotrack (black curve) and for the modified nanotrack shown in the inset (red curve). Figures extracted from [10].

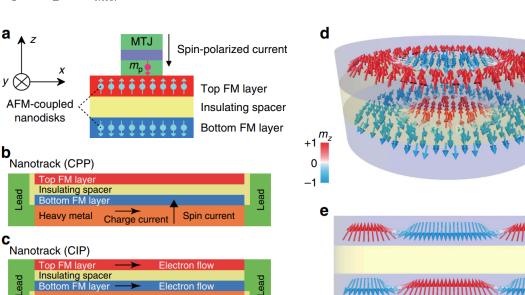

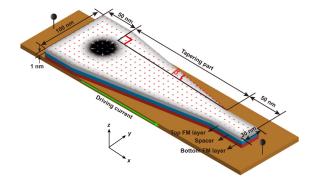

A completely different possibility is presented in [41]. The structure of the device described in this article is reported in figure 2.16: a FM layer with positive background magnetization is separated from a bottom FM layer with opposite background magnetization by an insulating spacer. Below the bottom FM layer, a HM substrate allows the flow of a current in the x-direction and is able to generate a spinpolarized current vertically directed with spin direction along +y. The peculiarity of this structure is to have an antiferromagnetic (AFM) exchange coupling between the top and the bottom FM layers. The Hamiltonian for this kind of interaction is

$$H_{inter} = -A_{inter} \sum_{i} \boldsymbol{m}_{i}^{T} \cdot \boldsymbol{m}_{i}^{B}$$

(2.34)

where T stands for top, B stands for bottom and  $A_{inter}$ , the interlayer AFM exchange stiffness, is negative. As a result, if the magnetic moments of the top layer point in one direction, the moments of the bottom layer will point exactly in the opposite direction, in order to minimize the total energy of the system, equal to  $H_{total}$  =

$H_T + H_B + H_{inter}$ .

Heavy metal

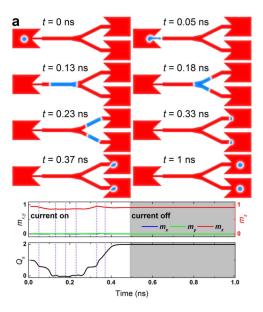

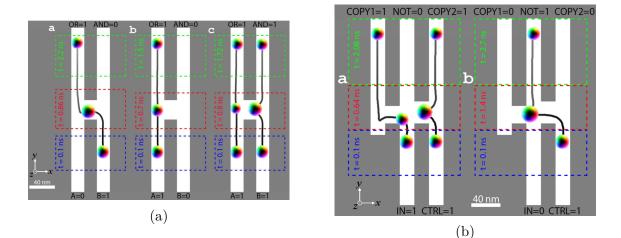

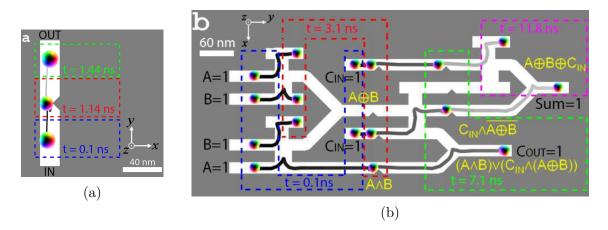

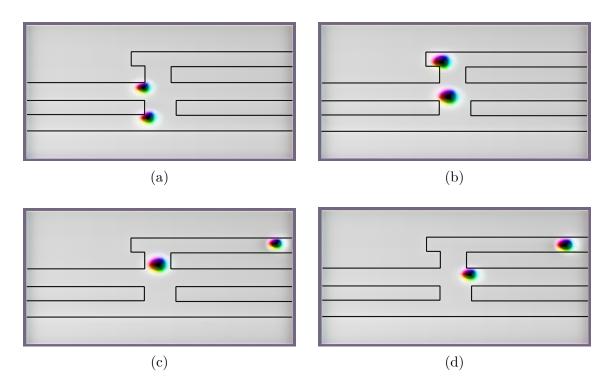

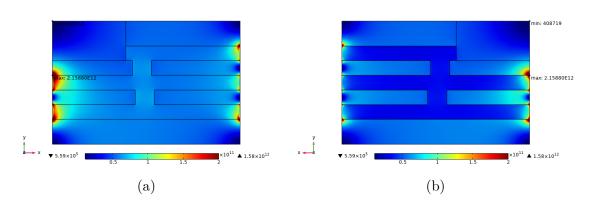

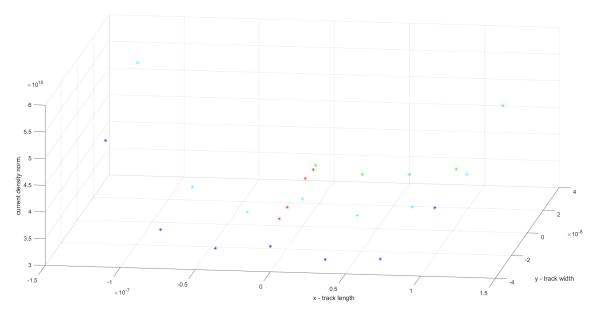

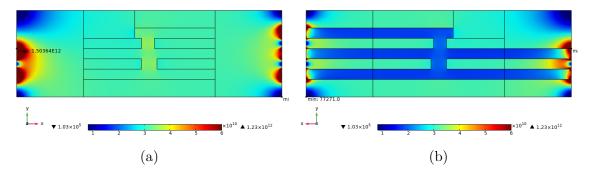

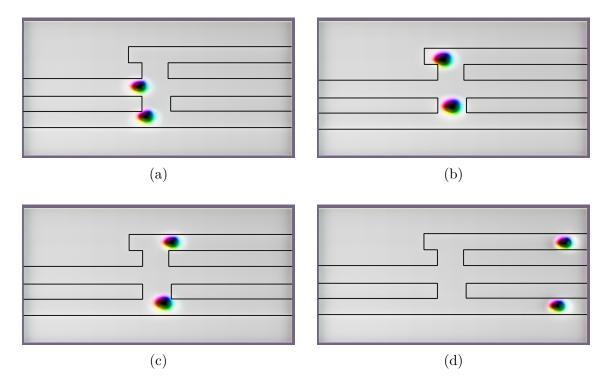

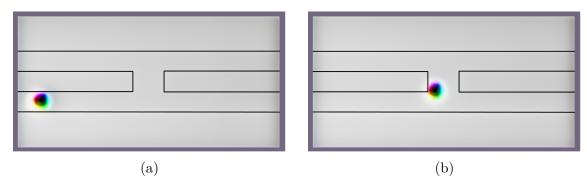

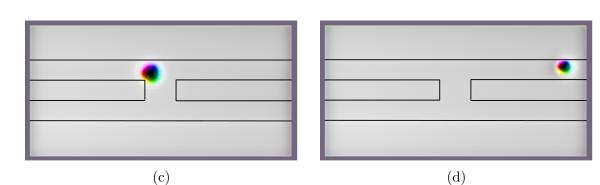

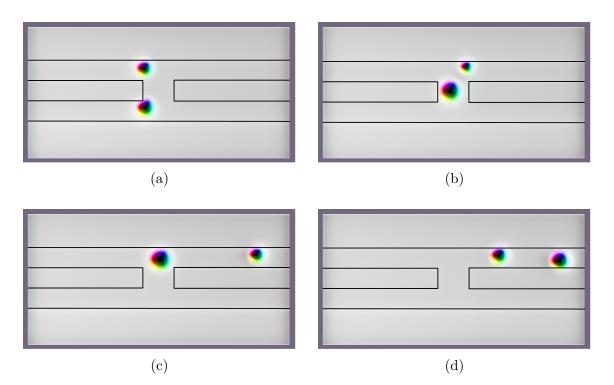

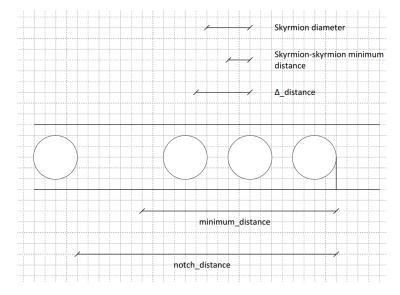

Figure 2.16. Schematic of the AFM exchange coupled bilayer system. (a) MTJ write-head needed for the nucleation of a single skyrmion in the top FM layer. (b-c) Bilayer nanotrack where the CPP geometry (b) or the CIP geometry (c) is exploited for the skyrmion motion. (d) Illustration of the bilayer-skyrmion. (e) Side view of the bilayer skyrmion along the diameter section. Figure extracted from [41].