# ROBUSTNESS TO SOFTWARE ERRORS IN A SYSTEM ON CHIP INTERCONNECT STMICROELECTRONICS

### **Thomas MARTIN**

I realized my 6 months internship at STMicroelectronics Grenoble in hardware digital design for a division which is in charge of designing ASICs for Aerospace, defense, microwave communication and mass market applications.

Details on the work carried out during the internship on the verso.

## GRENOBLE-INP PHELMA

**NANOTECH**

**MASTER THESIS**

DIGITAL ELECTRONICS

SUPERVISORS:

IGNAZIO URZI

(COMPANY)

LORENA ANGHEL

(SCHOOL)

#### **STMICROELECTRONICS**

12 Rue Jules Horowitz, 38000 Grenoble

From 2/11/19 to 8/09/19

Microcontroller and IC digital group

Aerospace and Microwave

Communication division

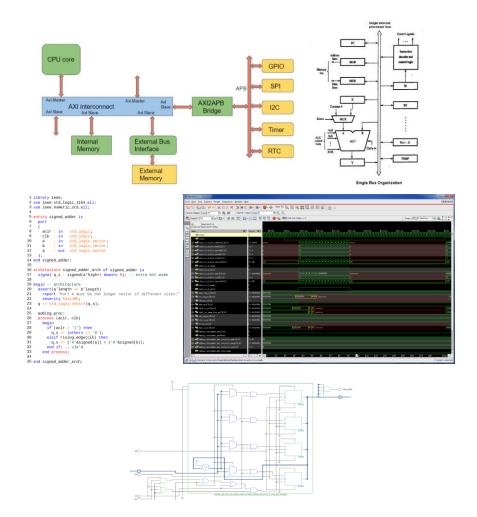

IPs microarchitecture, RTL design, UVM based standalone functional verification and synthesis have been carried out based on system specifications for enhancing the stability and security of the interconnect of new microprocessors. All the design is fully configurable to be easily integrated into other systems and synthesizable with the required timing constraints of the first targeted SoC.

**RTL DESIGN**

**VERIFICATION**

**SYNTHESIS**

# LANGUAGES AND TOOLS:

VHDL, VERILOG, SYSTEMVERILOG, IP-XACT, CADENCE, SYNOPSYS, MAGILLEM

#### **SOURCES**

All the images used in the poster are non-contractually binding to the real performed activities.

- STMicroelectronics general presentation

- https://anysilicon.com/ understanding-amba-busarchitechture-protocols/

- https://github.com/chipsalliance /rocket-chip/issues/1046 -https://vlsi.eelabs.technion.ac.il/ experiments/editorial-experiment/