# **POLITECNICO DI TORINO**

Corso di Laurea Magistrale in Ingegneria Elettrica (LM 28)

Tesi di Laurea Magistrale

# Modulation techniques for AC/DC converters in ultrafast battery charger applications

Relatore Prof. Bojoi Radu Candidato Di Franca Salvatore Marco

Correlatore

Cittanti Davide

Anno Accademico 2018/2019

# LIST OF CHAPTERS

|    | List of symbols                              | p. 5  |

|----|----------------------------------------------|-------|

|    | List of figures                              | р. б  |

|    | List of charts                               | p. 9  |

|    | Acknowledgement - Ringraziamenti             | p. 10 |

|    | Abstract                                     | p. 11 |

|    | Introduction                                 | p. 12 |

| 1. | State of art of UFC (ultrafast charger)      | p. 14 |

|    | 1.1 Advantages of multi-level conversion     | p. 14 |

|    | 1.2 List of topologies for AC/DC converters  | p. 21 |

|    | 1.3 T-type interleaved as active rectifier   | p. 28 |

|    | 1.4 Mid-point balancing                      | p. 36 |

|    | 1.5 Modulation strategies                    | p. 40 |

|    | 1.5.1 SVPWM                                  | p. 43 |

|    | 1.5.2 DPWM4                                  | p. 44 |

|    | 1.5.3 THREE LEVELS SPACE VECTOR PWM          | p. 46 |

|    | (TLSVPWM)                                    |       |

|    | 1.5.4 ZMPC                                   | p. 48 |

|    | 1.5.5 Duty cycles comparison table           | p. 51 |

| 2. | Simulative results                           |       |

|    | 2.1 Case study                               | p. 53 |

|    | 2.2 Hardware design                          | p. 58 |

|    | 2.2.1 Interleaving layout and reactive       |       |

|    | components design                            | p. 59 |

|    | 2.2.2 Grid-converter interface (LCL filter)  | p. 65 |

|    | 2.3 Block simulation of the T-type converter | p. 73 |

|    | 2.4 Design of current and voltage loops      | p. 77 |

|    | 2.5 Simulative results and analysis          | p. 86 |

|    | Conclusions                                  | p. 90 |

### Appendix

| <i>A1</i> .  | Duty cycles routine                              | p. 91  |

|--------------|--------------------------------------------------|--------|

| <i>A2</i> .  | PWMCompute example code                          | p. 92  |

| <i>A3</i> .  | DPWM4 code example                               | p. 92  |

| <i>A4</i> .  | CSVM (TLSVPWM) code example                      | p. 93  |

| A5.          | ZMPC code example                                | p. 94  |

| <i>A6</i> .  | Algorithm for LCL parameters calculation         | p. 95  |

| A7.          | Algorithm for LCL plots                          | p. 96  |

| <i>A8</i> .  | C routine for PI current control for all the     |        |

|              | current loop of the converter                    | p. 97  |

| A9.          | Current control parameters setup                 | p. 98  |

| <i>A10</i> . | Voltage control parameters setup                 | p. 98  |

| <i>A11</i> . | C routine for PI voltage control                 | p. 99  |

| <i>A12</i> . | C routine duties calculation for voltage control | p. 102 |

| Bibliography |                                                  |        |

"Non multa, sed multum

# LIST OF SYMBOLS

| В         | flux density                             | [T]             |

|-----------|------------------------------------------|-----------------|

| Ψ         | flux (RMS and peak-to-peak values)       | [Wb]            |

| S         | surface                                  | $[mm^2]$        |

| N         | numbers of turns of the coil             | [-]             |

| f         | frequency                                | [Hz]            |

| ω         | angular frequency                        | [rad/s]         |

| V         | voltage                                  | [V]             |

| $v_M$     | mid-point voltage                        | [V]             |

| Ι         | current                                  | [A]             |

| $i_M$     | mid-point current                        | [A]             |

| Q         | charge                                   | [C]             |

| С         | capacitance                              | [F]             |

| L         | inductance                               | [H]             |

| т         | modulation index                         | [-]             |

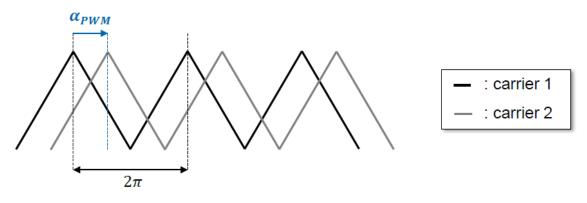

| α         | carrier phase shift                      | [°]             |

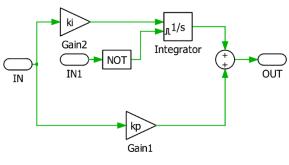

| $k_p$     | PI proportional gain                     | [V/A]           |

| <i>ki</i> | PI integral gain                         | [V/As]          |

| d         | duty cycle                               | [-]             |

| S         | switch state                             | [-]             |

| sgn(x)    | $\{(x) < 0\} = -1: [(x) == 0] = 0]: 1\}$ | [sign function] |

### **LIST OF FIGURES**

- *Fig. 1: Example of grid-battery connection.*

- *Fig. 2: LF solution with galvanic isolation.*

- *Fig. 3: HF solution with galvanic isolation.*

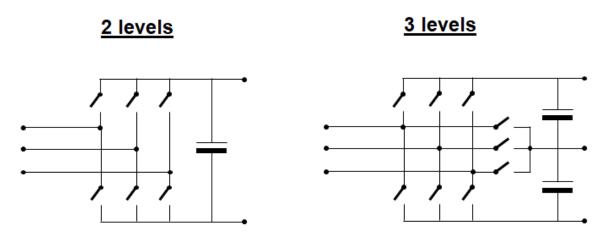

- *Fig. 4: Model of a 2 levels and a 3 levels converter.*

- *Fig. 5: Model of a 2 levels regulation on the 3-phase hexagon.*

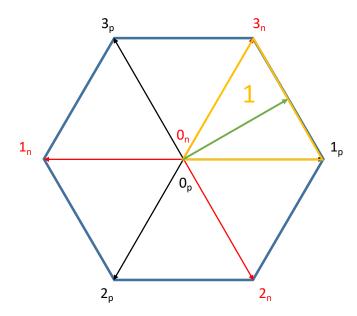

- *Fig. 6: Model of a 3 levels regulation on the 3-phase hexagon.*

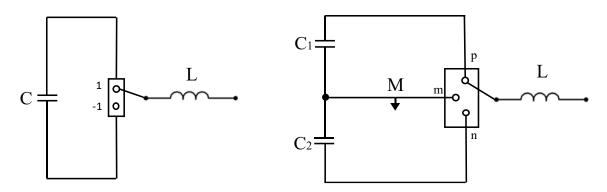

- *Fig. 7:* Comparison between 3-pole and 4-pole model for single-level and multi-level conversion.

- Fig. 8: AFE with 2-levels rectifier/inverter.

- *Fig. 9: AFE rectifier with NPC technology (1).*

- *Fig. 10: AFE inverter with NPC technology (2).*

- Fig. 11: AFE technology with Vienna rectifier layout.

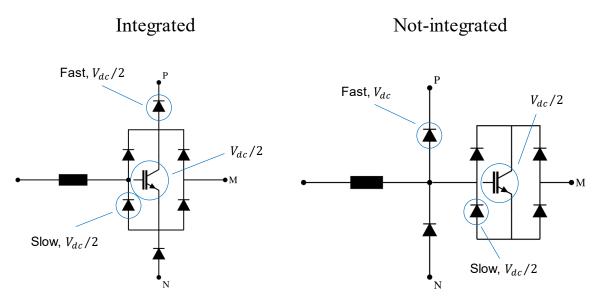

- Fig. 12: Vienna topology in integrated and non-integrated layout.

- *Fig. 13: AFE technology with T-type rectifier layout.*

- *Fig. 14:* Comparison layout between *T*-type and *NPC*-non-integrated.

- *Fig. 15: AFE technology with T-type inverter layout.*

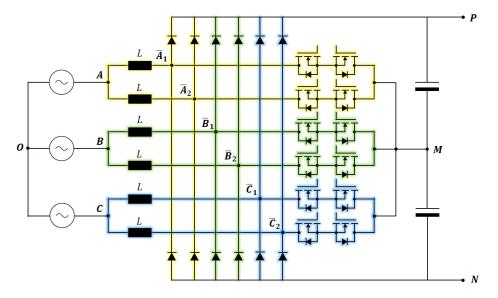

- *Fig. 16: T-type interleaved AFE.*

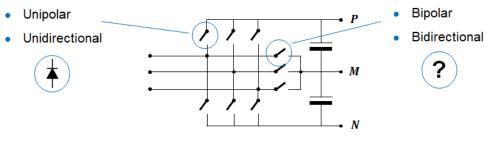

- *Fig. 17: Basic model for AC/DC interface.*

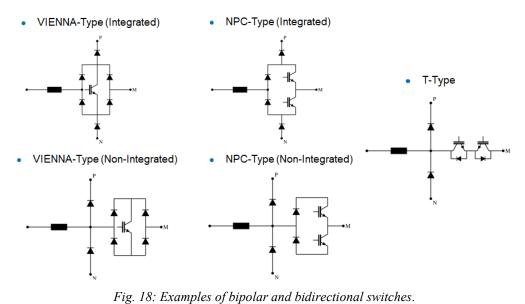

- *Fig. 18: Examples of bipolar and bidirectional switches.*

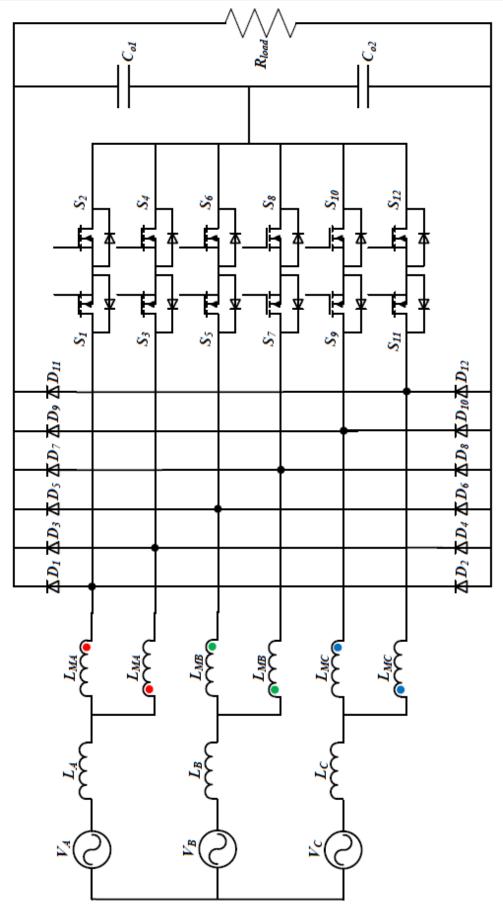

- *Fig. 19: Interleaved T-type converter.*

- *Fig. 20: Operation principle of T-type converter, single unit (1).*

- *Fig. 21: Operation principle of T-type converter, interleaved, single unit (2).*

- Fig. 22: Input voltage formation.

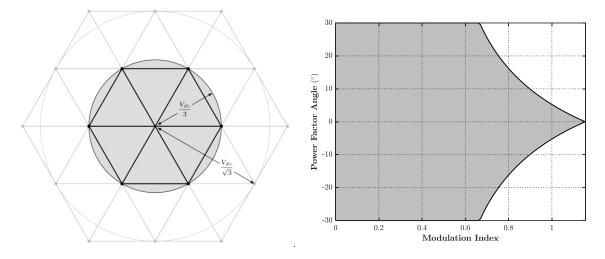

- *Fig. 23:* Voltage selection in a 3-levels 3-phase hexagon.

- *Fig. 24: SV representation of instantaneous voltage vector.*

- *Fig. 25:* Limits of regulation in 3-phase 3-levels hexagon and (m, cos $\phi$ ) chart of the converter.

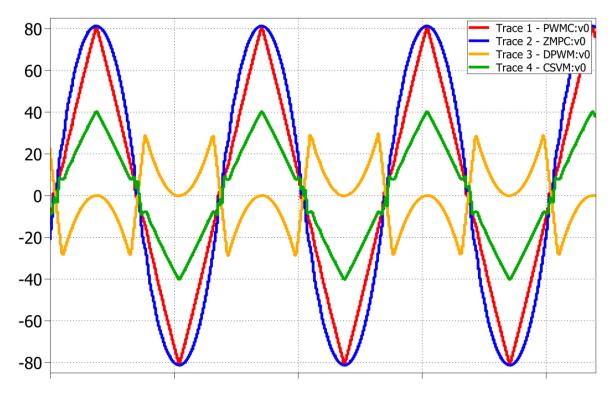

- Fig. 26: Examples of  $v_{0_{LF}}$  for different modulation strategies (PWMC, ZMPC, CSVM and DPWMC).

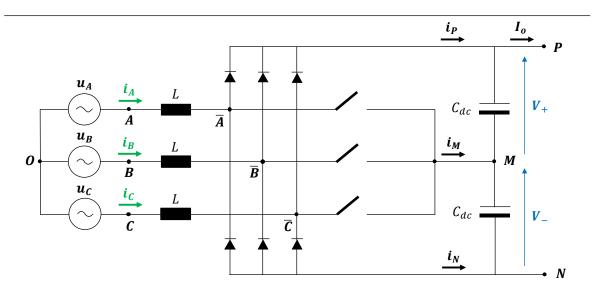

- *Fig. 27: EC of the T-type interleaved converter.*

- Fig. 28: Vector illustration of phase currents.

- Fig. 29: AFE overview.

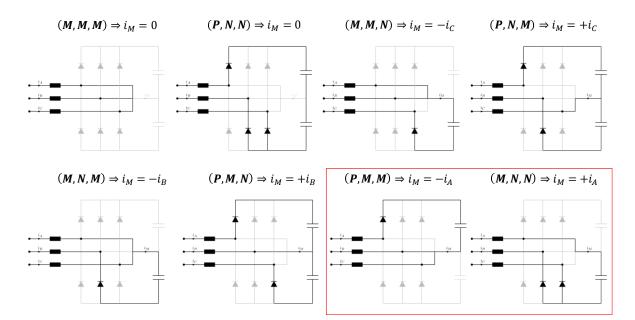

- *Fig. 30: AFE possible switch states.*

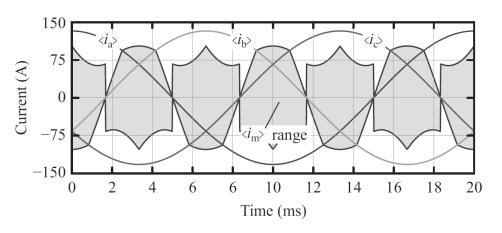

- Fig. 31: Maximum instantaneous range of i<sub>M.</sub>

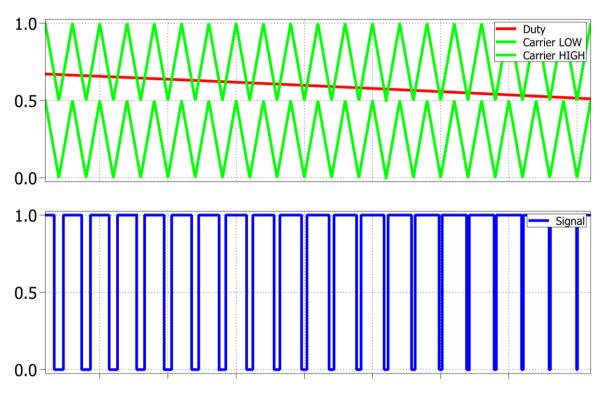

- *Fig. 32: Example of 3-levels PWM modulation.*

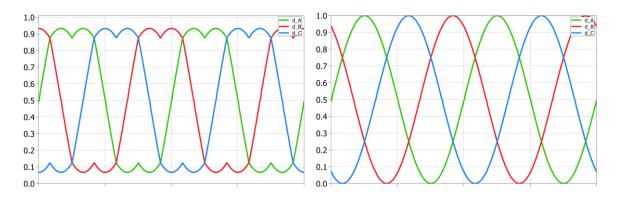

- Fig. 33: Duties comparison with disabled or enabled BEM.

- Fig. 34: Expected waveforms with PWMCompute.

- Fig. 35: DPWM4 expected waveforms.

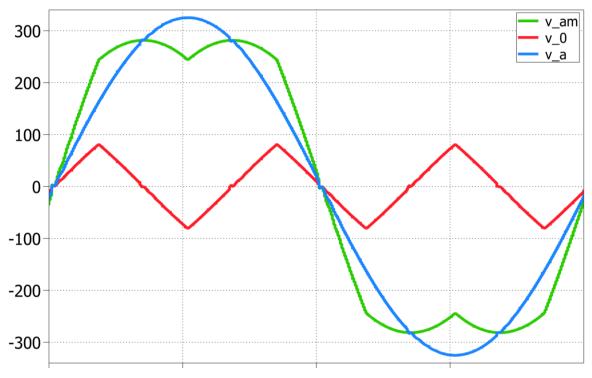

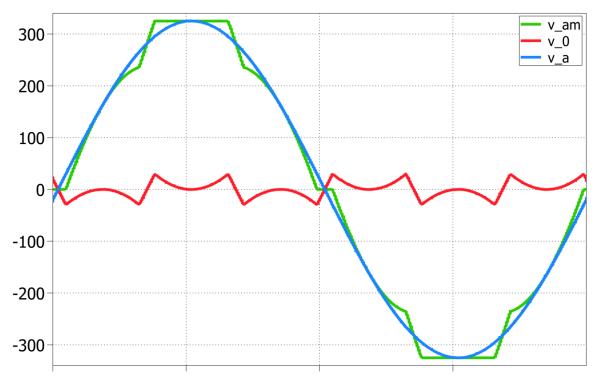

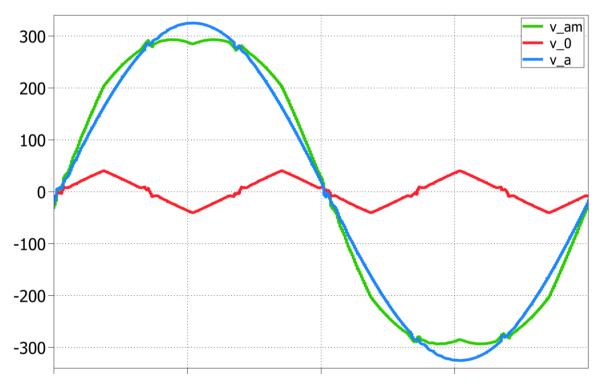

- Fig. 36: CSVM expected waveforms.

- Fig. 37: ZMPC expected waveforms.

- *Fig.* 38:  $i_M$  ripple component for different modulation techniques.

- *Fig. 39: i*<sub>M</sub> periodic average values for different modulation techniques.

- Fig. 40: PWMC duties.

- *Fig. 41: DPWMC duties.*

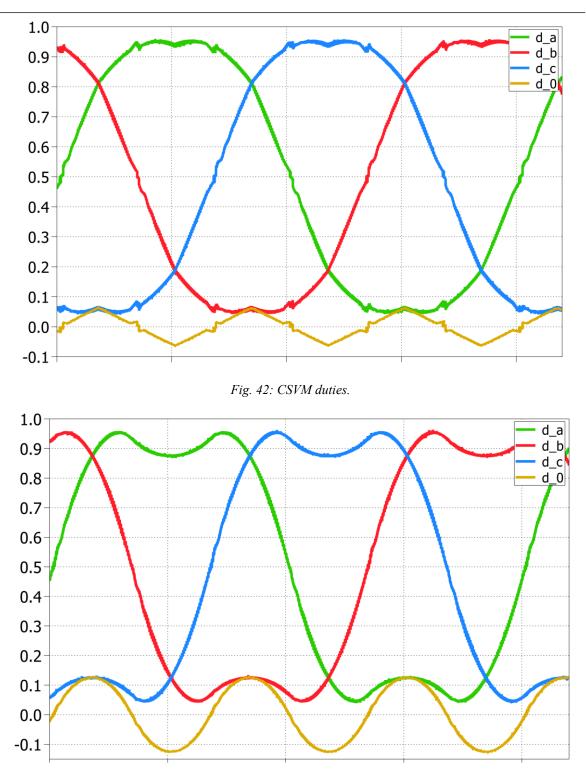

- Fig. 42: CSVM duties.

- Fig. 43: ZMPC duties.

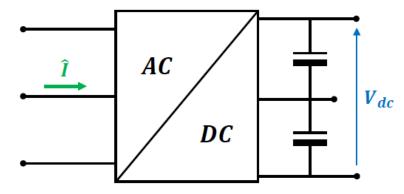

- *Fig. 44: Model of the AC/DC stage and voltage DC-link.*

- Fig. 45: Final model of the interleaved T-type rectifier.

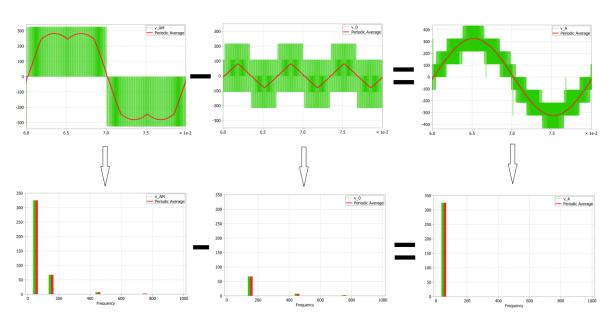

- *Fig. 46: Harmonic properties of voltages generated by a 3-levels T-type rectifier.*

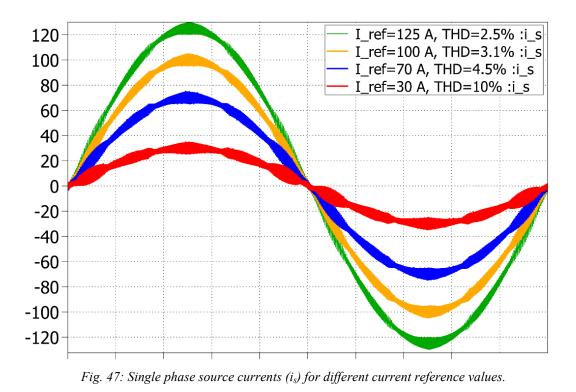

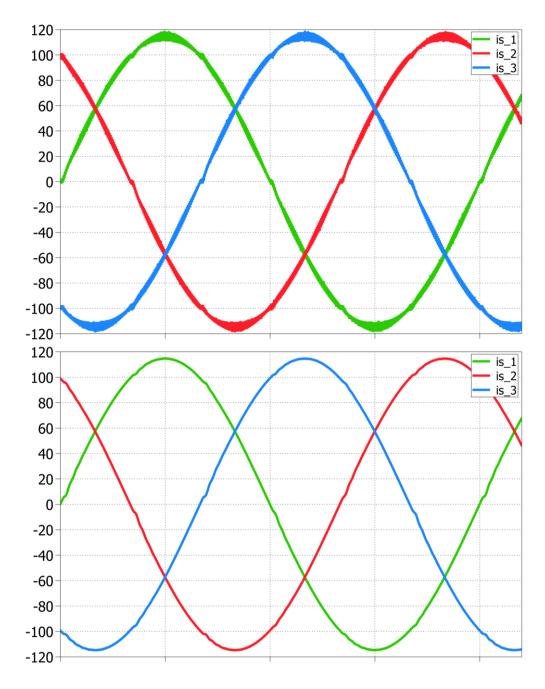

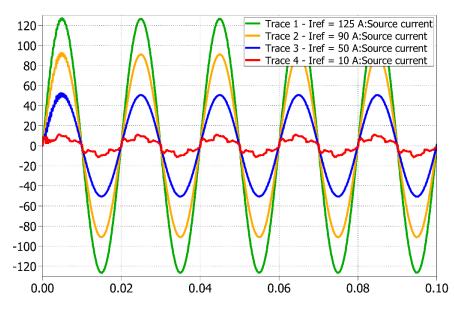

- *Fig.* 47: Single phase source currents (*i*<sub>s</sub>) for different current reference values.

- *Fig.* 48: *Aluminium electrolytic capacitor used in DC-link of AFE.*

- Fig. 49: Shifted carriers for 3-levels PWM control routine.

- *Fig. 50:* Some remarkable  $\alpha_{PWM}$  alignment cases.

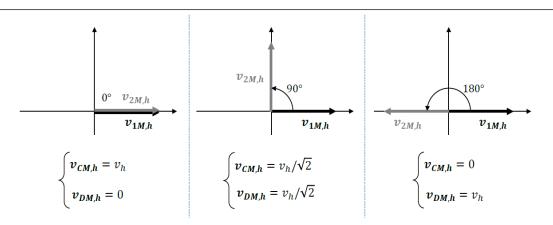

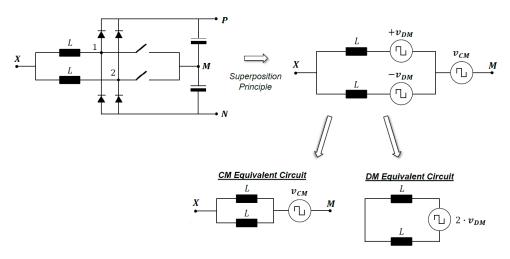

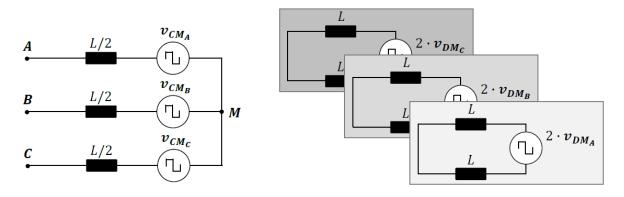

- *Fig. 51:* Identification of common and differential voltage components.

- *Fig. 52:* 3-phase EC (equivalent circuit) of common and differential voltage components.

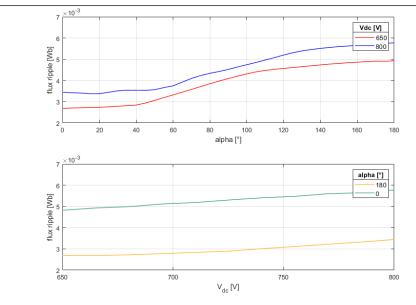

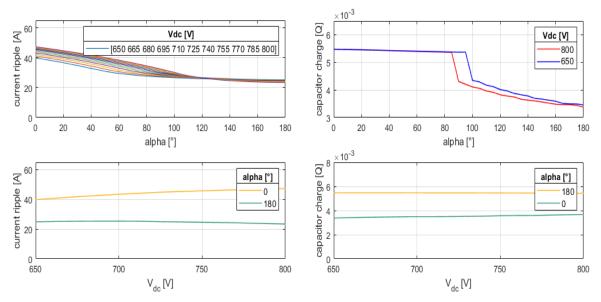

- Fig. 53: Peak-to-peak flux evaluation for different values of  $\alpha_{PWM}$  and  $V_{dc.}$

- Fig. 54: capacitor current and charge peak-to-peak ripple evaluation for different values of  $\alpha_{PWM}$  and  $V_{dc}$

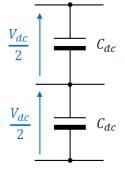

- Fig. 55: split DC-link capacitor.

- Fig. 56: Vishay datasheet for MAL2259 series.

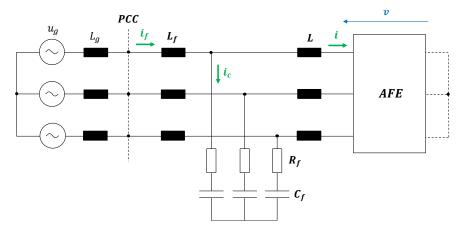

- Fig. 57: LCL collocation as grid/converter interface for EM compatibility.

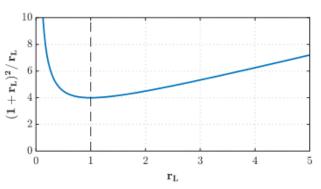

- *Fig.* 58: Sensitivity of output-to-input inductance ratio  $r_L$ .

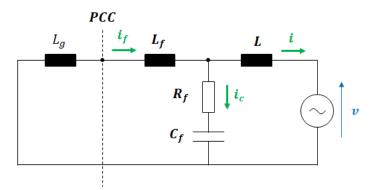

- Fig. 59: Small signal EC for LCL filter.

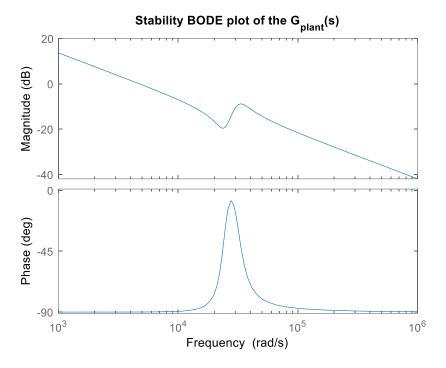

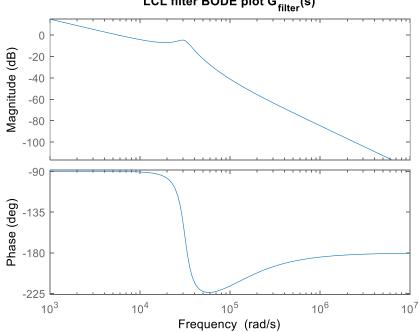

- *Fig.* 60: Bode plot of the transfer function of the system Y(s).

- *Fig.* 61: Bode plot of the transfer function of the filter  $Y_f(s)$ .

- *Fig. 62: Comparison about L filter and LCL filter absorbed grid current.*

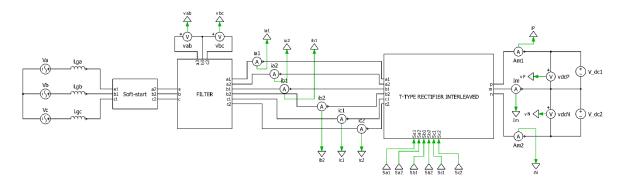

- *Fig. 63: Schematic of the converter T-type.*

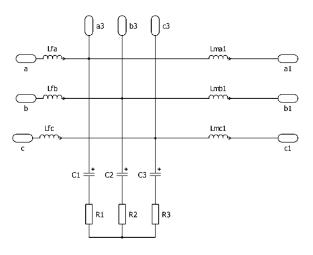

- *Fig.* 64: *Schematic of the LCL filter with interleaved topology.*

- *Fig. 65: Schematic of the AC/DC stage (T-type layout) with interleaved topology.*

- *Fig. 66: Schematic of the PI.*

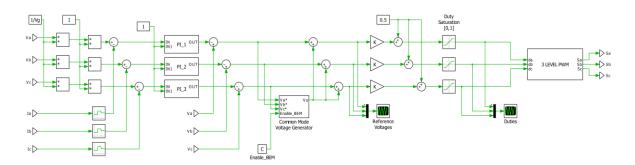

- *Fig.* 67: Schematic of the control of the converter in block simulation.

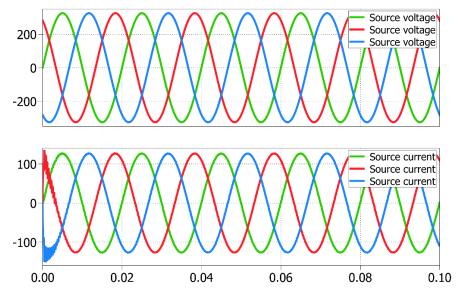

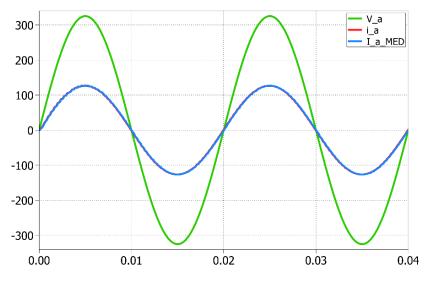

- *Fig.* 68: *Grid voltages and current absorbed by the converter.*

- *Fig.* 69: *Current absorbed by the converter with different current reference values.*

- *Fig. 70: Current reference and periodic average of phase a current.*

- *Fig. 71: Simplified model of the T-type converter.*

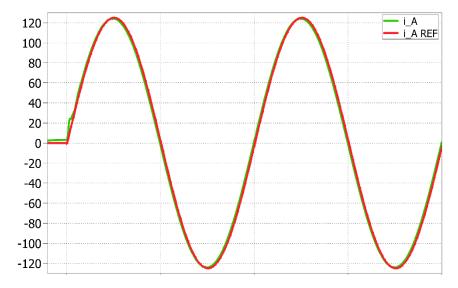

- Fig. 72: Current control check.

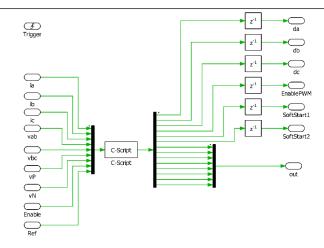

- Fig. 73: Schematic of the control routine (C-Script).

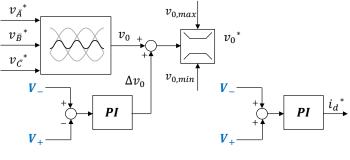

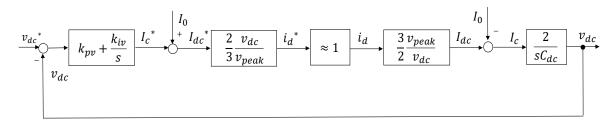

- *Fig. 74:* Block model of the voltage control.

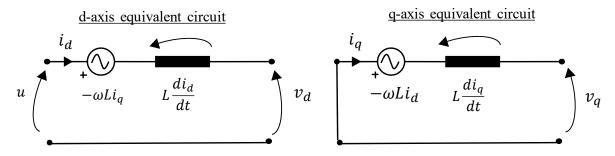

- *Fig.* 75: *EC of the converter on dq frame.*

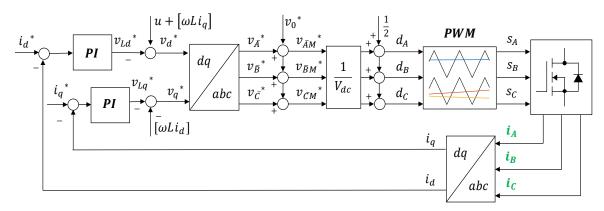

- *Fig.* 76: Block model of the control of the whole converter.

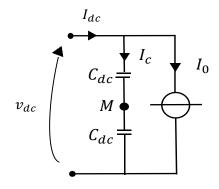

- *Fig.* 77: *EC of the DC-link.*

- Fig. 78: Voltage loop of the plant.

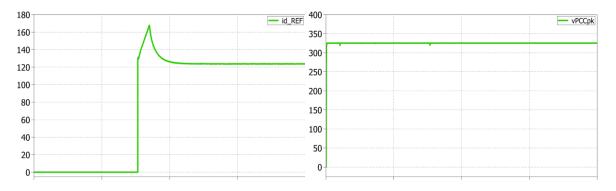

- *Fig.* 79: Instantaneous *v*<sub>peak</sub> values and *i*<sub>d</sub> reference for voltage control.

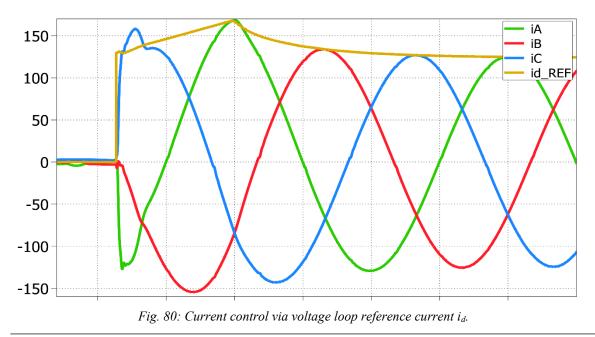

- *Fig.* 80: *Current control via voltage loop reference current id.*

- Fig. 81: Differential mode equivalent circuit.

- Fig. 82: EM compatibility of high harmonic orders of source current.

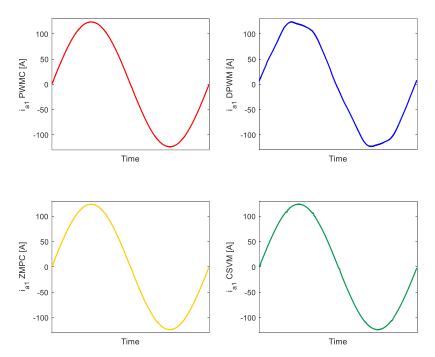

- *Fig.* 83: Comparison of waveforms of absorbed phase current per different modulation strategies.

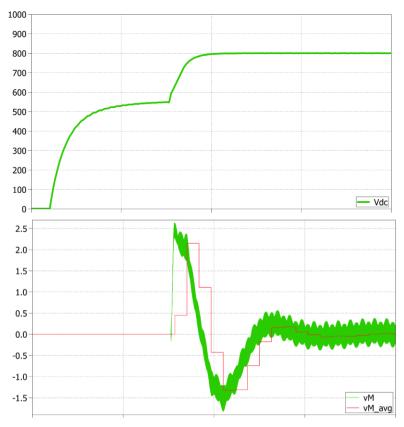

- *Fig.* 84:  $V_{dc}$  and  $v_M$  voltage waveforms.

- *Fig.* 85: Comparison of *v*<sub>M</sub> voltage waveforms per different modulation strategies.

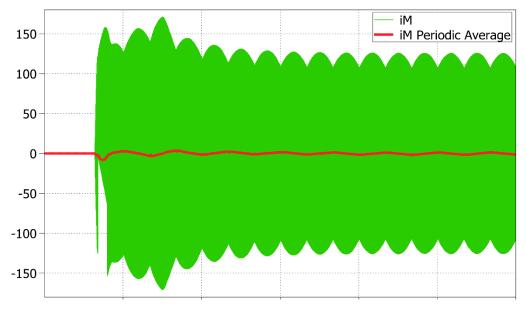

- Fig. 86: Real waveform of mid-point current  $(i_M)$  (periodic average and instantaneous value) with the use of ZMPC

## LIST OF CHARTS

- *Chart 1: Vectors to control in sector 1 in a 2 levels 3-phases hexagon.*

- Chart 2: Size of LCL reactive components.

- *Chart 3: LCL guaranteed attenuation per fixed frequency.*

- *Chart 4: Source current (phase a) characteristics.*

- *Chart 5: Mid-point current (i<sub>M</sub>) characteristics.*

# **ACKNOWLEDGEMENT - RINGRAZIAMENTI**

Il lavoro di tesi è stato interamente scritto in lingua inglese. Nonostante questo, ritengo necessario esprimere i miei ringraziamenti in lingua italiana.

Un primo ringraziamento va al PEIC (Power Electronics Innovation Center) del Politecnico di Torino, il cui team ha lavorato in prima persona sul progetto esposto in questo lavoro di tesi. In particolare, un ringraziamento speciale va al professore Bojoi Radu, che mi ha coinvolto in tale attività quale interessantissimo approfondimento tecnico, aiutandomi peraltro, personalmente, nella realizzazione dell'elaborato. Un ulteriore ringraziamento accademico va al correlatore Davide Cittanti poiché senza la sua collaborazione non sarebbe stato possibile realizzare questa tesi.

Alla fine del mio percorso universitario, ormai pluriennale, non posso non ringraziare nuovamente la mia famiglia, mio fratello ed i miei genitori, che nonostante la distanza si sono sempre dimostrati vicini al mio lavoro con la mente e con il cuore. Ringrazio inoltre la mia amata Veronica, per il supporto che per me ha rappresentato in questi anni, soprattutto nei momenti più difficili della mia carriera accademica.

Ringrazio chi è presente qui quest'oggi, i parenti e tutti gli amici che hanno direttamente od indirettamente partecipato alla cerimonia di proclamazione odierna. Ringrazio infine coloro che ho sbadatamente dimenticato in queste poche righe.

### ABSTRACT

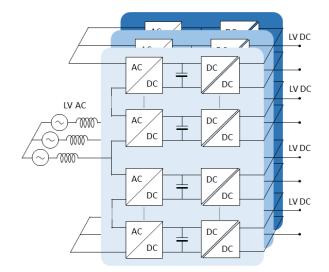

Concerning today's exigencies of electrical mains, the possibility to build a reliable technology of electric energy distributed storage in conjunction with the growing market of electric and hybrid vehicles (EV and HEV) address the actual producers' interest mostly on batteries and charger station. Indeed, the UFC (ultrafast charger) technology has been becoming dominant in this ambit for last years, because these devices guarantee high density of power and a variety of combinations in terms of layout (bidirectional or unidirectional applications).

According to the previous motivations, this thesis regards the report of a project of an ultrafast charger conceived by *PEIC (Power Electronics Innovation Center)* of the Turin Polytechnic, patented in symbiosis with "*VISHAY Semiconductor Italia*", a leader company in the electronic and electric components market.

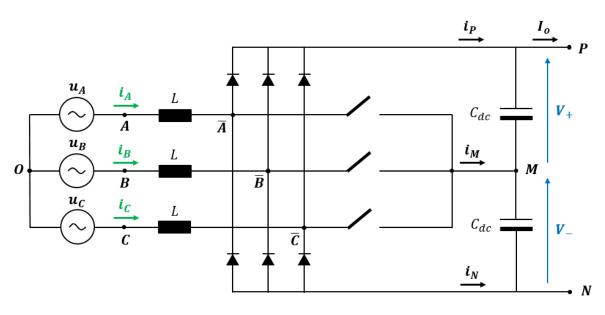

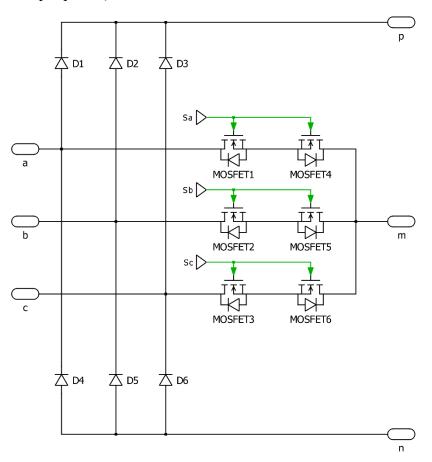

The charger consists of two different converters: the first one is an AC/DC (active front end) converter while the second one a DC/DC converter (LLC resonant). This paper focuses on the AC/DC stage and highlights how to set up the most efficient control strategy for the structure. In particular, in this AC/DC application an AFE (active front end) converter has been realized. This topology represents an example of multi-level converter, with 3 output connections (p, m, n) instead of 2 (1, 0). It leverages bidirectional T-type switches for midpoint connection.

The principal points of the thesis deal with the advantages guaranteed by the converter (unitary  $\cos\varphi$ , low impact on absorbed current by the grid so low THD and TDD, galvanic isolation of the battery, possibility to charge more vehicles contemporaneously, power sharing strategy, and so on) and also with the major issues affecting it (mid-point current control and DC-link balance).

The main problem concerning the control of the structure regards the mid-point balancing. A suitable modulation technique and a proper voltage control are presented as methods to overcome this problematic. This modulation technique is known in technical literature as ZMPC (Zero-Mid-Point-Current) PWM and it is feasible for this application since it acts by nulling the periodic value of the mid-point current on the central connection of the DC-link. In the end, several considerations, supported by proper figures and comments, are presented in this paper and a final section reports further conclusions about the treated topics.

# **INTRODUCTION**

The growing interest in electric mobility (HEV, PEV and EV) in conjunction with the possibility to achieve demand-side-management, have been the motivations leading the efforts of power electronic researches on ultrafast charger technologies for last years, in order to satisfy different market and users necessities. The main pointed out topics of interest regard:

- the possibility to build an *new electric infrastructure* for users' direct grid connection, in order to permit them to recharge their vehicles anywhere (like petrol stations) and in the lowest possible time (so with the highest possible current flow);

- the necessity, for the grid owner, to create a real high capacity *distributed storage* that, in specific circumstances, could be used to guarantee a bidirectional power flow (the charger is as a load for the grid in case of vehicle recharge but it may act as a generator in case of electric energy peak demand).

- the obligation to meet the *EMI requirements* for these kind of electronic devices;

- the responsibility of today's generation to evaluate the possibility for a new way of intending mobility as electric and sustainable (*zero emission mobility challenge*);

The main issue tied with the proposal targets regards the huge required power density of this kind of chargers. They have to be not only compact but also powerful (up to 300 kW of power provided per single charger). As a first sight, it is not trivial to highlight that, in almost all the cases, these kind of devices are made up of more than a single unit. Usually, 5 or more units are connected in parallel and in this way the power absorbed by the single unit can be significantly lower than the whole power absorbed by the charger. Without this shrewdness, the realization of the charger could even be impossible.

A simple solution might be searched in MV grid connection (up to 1 kV) but at the moment the state of art of semiconductors for such kind of applications can be really complex, due to the voltage rating of the components (IGBTs, MOSFETs switches and diodes). Consequently, the majority of producers prefer to deal with LV grid connected converters, providing then a higher current flow to fulfill the power request. Nevertheless, the power demand of these devices cannot be reached without the use of a specific topology for the converter and this is the reason why the interleaved topology is the preferred one. It is the most diffused and suitable since enables both to obtain the condition of LV grid connection and high current request in order to achieve the desired power demand. UFC (UltraFast Charger) is the name used in literature to describe these kind of devices.

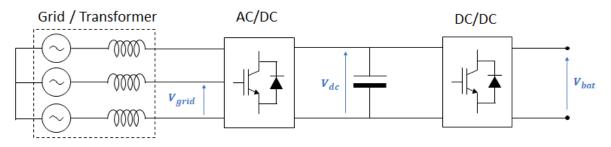

The UFC has to be connected in any time both to the grid and to loads (the vehicles to recharge). As a consequence, the UFC is indeed a back-to-back converter, with an AC/DC interface (for grid-converter connection) and a DC/DC stage (for converter-load connection). Between the stages of the converter is interposed a voltage DC-LINK in order to guarantee continuity of voltage for loads and also protection from voltage dips and swells originated by the grid.

The purpose of the thesis is to provide an accurate and precise study, both simulative and experimental, of the AC/DC stage of an UFC, with a specific focus on the control of the converter, considering the main issues of the case, for example:

- the optimal choose of the converter to use among different alternatives in literature (in terms of layouts, components and technologies);

- the necessity to guarantee the immunity of the converter from the disturbances coming from the grid (in order to satisfy the EMI standards for the phase current absorbed by the grid in terms of TDD, Total Demand Distortion);

- the critical point of the control of the converter;

- the performances that may be obtained by the converter using a variety of different modulation techniques;

In addition, a conclusive chapter is proposed to summarize the activities of the thesis and to provide further considerations about the treated topic and their eventual future scenarios.

## **CHAPTER 1: STATE OF ART OF UFC**

#### 1.1 Advantages of multi-level conversion

Today's state of art of UFC charger permits to recharge the battery pack of an electric vehicle in a reasonable time (400 km of autonomy in 10 minutes of recharge). In order to achieve this result, it is necessary to have a huge power density (at least 300 kW), to guarantee a sufficient current flow (up to 300  $A_{RMS}$ ). As already suggested in the introduction, the use of MV grid (up to 1 kV) is not really feasible, due to the voltage rating of switches and semiconductors properties. For this reason, the use of classical 2-levels topologies for the converters within the charger could result in an inefficient structure or even in a not achievable one in certain cases. As a consequence, preferred topologies for these kind of devices are oriented to multi-level converters and interleaved topology. These are the two main features of the UFC that will be described in the case study of this thesis. In this paragraph and in the following one, it will be shown both the advantages of multi-level conversion and the mainly used topologies for this kind of applications. As a useful example, let introduce firstly, same practical measure of grid/battery connection in terms of voltage and current values [7]:

• existent electric vehicle batteries may have a wide voltage range, usually:

$$V_{batt} = 200 \div 1000 V$$

• considering a *boost-type* AC/DC converter topology (as it is normally the case), the actual value of voltage could float among 0.9 pu and 1.1 pu of the nominal value of voltage, thus:

$V_{grid} = (400 \pm 10\%) V_{RMS}$  yields to  $V_{dc,min} = \sqrt{3} \cdot 400 \cdot 0.9 V_{RMS} \cong 625 V_{RMS}$

The  $V_{dc}$  choice is of utmost importance, since it influences the voltage rating of the semiconductor devices and the DC/DC converter topology;

• the maximum battery charging current impacts the DC/DC converter design and it is limited by the connector, according to the *CCS Combo* standard to:

$$I_{batt} = 350 A_{RMS} at 1000 V$$

Thus, in this case:

$$I_{grid} = 565 A_{RMS} at 625 V_{RMS}$$

Where the last value of current ( $I_{grid}$ ) represents the actual current absorbed by the grid at the fixed voltage of  $V_{dc,min}$  (for the assigned power of 350 kW).

The power electronics supply of high-power electrical systems from the three-phase ac mains to the load is usually carried out in two stages, i.e., the mains ac voltage is first converted into a dc voltage and then adapted to the load voltage level with a DC/DC converter (with or without galvanic isolation). Therefore, the typical grid-load connection consists in [7]:

- grid/transformer interface;

- AC/DC stage (conversion stage);

- Voltage DC link;

- DC/DC stage (for battery/grid connection);

Fig. 1: Example of grid-battery connection.

In the simplest case, the rectifier consists in a unidirectional three-phase diode rectifiers with capacitive smoothing of the output voltage and inductors on the AC or DC side (assuring voltage and current continuity for loads). Despite the low complexity and high robustness (no control, sensors, auxiliary supplies, or electromagnetic interference EMI filtering) of this concept must, this structure has to face against the disadvantages of relatively high effects on the mains and an unregulated output voltage directly dependent on the mains voltage level. Then, the AC/DC stage has to be chosen carefully in order to guarantee both load and grid specifications, for example:

- *unitary power factor*  $(\cos \varphi \approx 1)$ ;

- low THD and TDD (*TDD* < 0.05, in order to assume current waveform as sinusoidal);

- high efficiency (so, *reduced losses* in nominal working conditions);

- *high power density* (reduced devices and reactive components encumbrance).

Consequently, a proper AC/DC structure has to be patented in order to match this requirements. The *AFE converter (Active Front End)* is a AC/DC converter derived from the one-phase PFC (Power Factor Corrector) that permits to mitigate the harmonic distortion of the current absorbed by the converter from the grid, in order to eliminate the disturbances on

the load reducing further the dimensions and the cost of the reactive components (capacitors and inductors) necessary for the filtering operations.

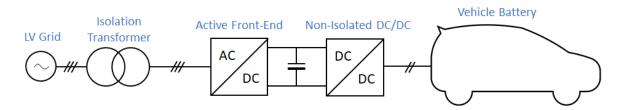

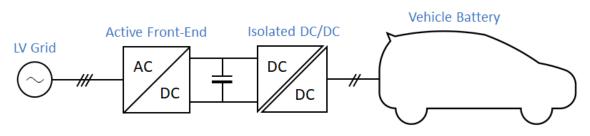

A primal split among AFE applications for UFC regards *low frequency solutions* and *high frequency solutions*. In both cases, it is necessary to provide an effective galvanic isolation between the grid and the load, definitely [7].

Fig. 2: LF solution with galvanic isolation.

Fig. 3: HF solution with galvanic isolation.

In LF applications the isolation is provided through the use of a dedicated *isolation transformer* that permit to isolate the load from the grid and further it keeps constant the voltage at the AC/DC stage input (in an independent grid manner). These kind of devices have the drawback of being bulky. Anyway, they enable the use of a non-isolated DC/DC converter stage (reducing costs and complexity of the system). On the contrary, in HF application, the isolation is provided by the DC/DC stage directly, since the system layout can be "*transformer-less*". This is the direction followed by the majority of UFC constructor, since it guarantees the main advantages (low costs, high efficiency, compactness and so on). A *high-frequency transformer* is a special transformer used in HF application ( $f_{sw}$  almost of kHz or even MHz) to guarantee galvanic isolation between grid and load or between two different levels of a multi-level converter.

These kind of devices are characterized by:

• *reduced encumbrance* in comparison with traditional LF transformer, due to the fact that for transformer the RMS value of the voltage depends on:

$$V_{RMS} = \frac{2\pi}{\sqrt{2}} B f S N \tag{1.1}$$

the flux density B [T], the frequency f [Hz], the surface S the flux density insists on [mm<sup>2</sup>] and the numbers of turns of the coil N [-]; therefore, at constant flux density B, if frequency f increases, the surface S decreases proportionally.

- the *iron losses*  $P_{fe}$  *are reduced* thanks to the creation of internal air gaps within the conductors (sintering ferrite), that mitigate the circulation of parasitic current;

- *high power density* (thanks to a reduced surfaces S).

These are the major motivations that have been orienting the developing of AFE technology for last years. The AFE converters are examples of multi-level converters. *Multi-level converters* are converters in which the base layout is not represented by the canonical cell for hard commutation (combination of switch and diode for freewheeling operations) but they consist of the combination of more devices with a specific topology.

The NPC circuits (isolated or non-isolated), the Vienna rectifier and the T-type rectifier are examples of 3-levels converters. The AC/DC stage is configured as follow

Fig. 4: Model of a 2 levels and a 3 levels converter.

With the use of a 2 levels converter it is possible to control switches only up and down (thus 1 or -1 as modulation index or 1 and 0 as bits). The chance to have more possible states for switches (for example in a 3 levels converter switches state can vary between up, down and mid, thus p, n and m state) enables to *increase the resolution of regulation in amplitude*.

This fact leads to a variety of advantages, for example:

- *increase the accuracy and precision of regulation*, since the *error* of regulation can be *halved* increasing the number of levels from 2 to 3;

- as a consequence, the previous fact permits to *decrease the dimensions of reactive filters* necessary to provide EMI standard and guarantee the quality of the voltage profile for loads (assuring also a reduction of cost of the reactive components);

- *decrease the boost inductance dimensions* at converter input;

- *reduce the commutation losses P*<sub>comm</sub>, since it is now possible commutate within smaller field of regulation. Thus:

$$P_{comm} = f(V_c, I_L)$$

$V_{c}$  represented the commutated voltage and  $I_{L}$  represents the current absorbed by the load.

In 2-levels converters (for example in a 2-levels VSI) the load voltage regulation is realized through the use of the *triangulation method* (within the regulation hexagon), thus with the use of a single carrier PWM and the BEM technique. Therefore, the vector  $\vec{v}_m$  (shown in fig. 5) can be realized only generating a proper error in magnitude and phase. In this example,  $\vec{v}_m$  belongs to the sector  $(1_p 3_n 0_n^p)$  and for this reason only the m<sub>2</sub> (modulation index of leg 2) varies to realize the desired regulation. As an example, it is to note the following figure.

| SECTOR [1] $(1_p, 3_n, 0_n^p)$ |              |  |

|--------------------------------|--------------|--|

| VECTORS                        |              |  |

| 1 <sub>p</sub>                 | (1, -1, -1)  |  |

| 3 <sub>n</sub>                 | (1,1,-1)     |  |

| 0 <sub>p</sub>                 | (1,1,1)      |  |

| 0 <sub>n</sub>                 | (-1, -1, -1) |  |

Fig. 5: Vectors to control in sector 1 in a 2 levels 3-phases hexagon

Chart 1: Vectors to control in sector 1.

To obtain the vector  $\vec{v}_m$  (within sector 1), only the second switch varies from -1 to 1 (the others maintain their states), according to the following statement:

$$m_f \in [-1,1]$$

where  $f = 1, 2, 3$  (1.2)

Increasing the switch states from 2 to 3 it is possible to double the resolution in magnitude, which means, at the same time, a halved error of regulation. A multi-level converter is always more precise and accurate than a single-level converter.

Fig. 6: Model of a 3 levels regulation on the 3-phase hexagon.

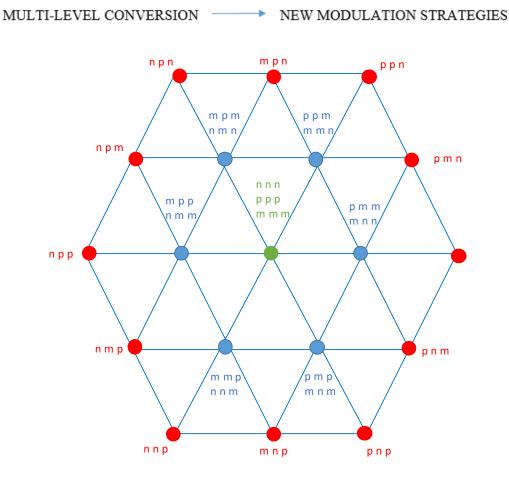

Figure 6 has to be interpreted defining the *multiplicity of a state* (v). In particular:

$v_a = 1$  (3-levels VSI)  $v_a = 2$  (2-levels VSI)  $v_a = 3$  (numbers of zeros of the system)

In each multi-level converter the multiplicity of zeros, (p p p), (m m m) and (n n n), is equal to the number of switch states permitted  $N_L$ . Consequently:

$$N_L = v \tag{1.3}$$

On the contrary, in a 3-levels converters (for example in a 3-levels VSI) the regulation hexagon will be characterized by 3 levels of *zero multiplicity* instead of 2 (as shown in fig.6). As a reference model, the canonical cell for hard commutation (2 levels multiplexer) is substituted by a *4-pole model* (3 levels multiplexer) as shown in figure 7.

Fig. 7: Comparison between 3-pole and 4-pole model for single-level and multi-level conversion.

In the second figure it is to note that in a multi-level converter (3 levels), it is possible to control 3 different hard switching states (m, p and n). The *mid-point of the 4-pole* is the point M. It represents the mid-point of a split DC link and the centre of the triad (p, n, m).

Differently from 2 levels converters, it is possible to see the mid-point M from outside and  $v_M$  moves due to the presence of differential mode component of DC-link voltage. For example, the control strategy of the converter could be addressed to manage the mean value of that voltage ( $v_M$ ) to zero. As a first sight, the major *drawbacks* of multi-level conversion regard:

#### • high circuit complexity (higher number of switches and degrees of freedom);

#### • control of the output voltage mid-point required.

A variety of modulation strategies has been developed for mid-point voltage and current control. The reader has to move to paragraph 1.5 to see a brief review of modulation strategies reported in the thesis (for simulative goals).

#### 1.2 List of topologies for AC/DC converters

A variety of different topologies have been presented in technical literature about 2-levels or 3-levels converters in AC/DC applications. Indeed, these devices can be used both as inverter or rectifier, according to the specific connection source-load of the components (diodes and switches) and their properties (unidirectional or bidirectional switches). Concerning low voltage ultrafast-charging solutions (LV UFC), the utmost interesting solutions for AFE converters (AC/DC interface) existing and/or proposed in literature regards the following topologies:

- 2-levels rectifier/inverter;

- NPC (neutral point clamped);

- Vienna rectifier;

- T-type rectifier/inverter.

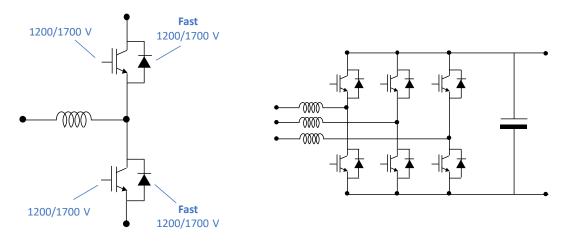

As a basic model, a *2-levels rectifier/inverter* (both for AC/DC and DC/AC conversion) is shown in the following figure.

Fig. 8: AFE with 2-levels rectifier/inverter

Each converter leg requires at least 2 fast diodes ( $V_{rated,D} = 1200/1700$  V) and 2 transistors ( $V_{rated,MOS} = 1200/1700$  V). This structure guarantees same interesting advantages:

- *simplicity* of topology;

- *low conduction losses* (due to the low number of active devices required);

- possibility of bidirectional flow and storage capability (even if the bi-directionality of the converter should be evaluated from an economic perspective, it does not represent a prime specification for these kind of devices, especially without the integration of an energy storage into the charging facility);

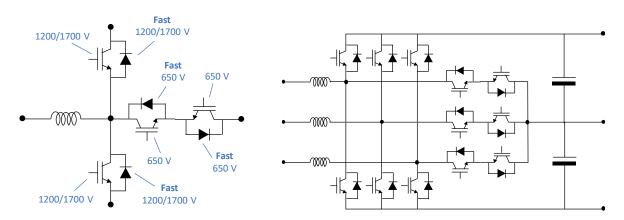

On the other hand, the main disadvantage of the structure is the fact that the semiconductor devices are full-voltage rated and this obliges to use IGBTs for high voltage applications (up to 1 kV of operating voltage) and fast diodes for freewheeling operations. These components have high costs and limitations in terms of voltage rating and frequency since, if frequency increases, then the switching losses can lead to an overall low efficiency of the converter. A more suitable topology for AC/DC converters is represented by *NPC (neutral point clamped) topology*. The NPC technology is an example of multi-level converter. The NPC-type can be both integrated or not integrated and used in rectifier or inverter application independently. The schematics are represented in the following figures (9 and 10)

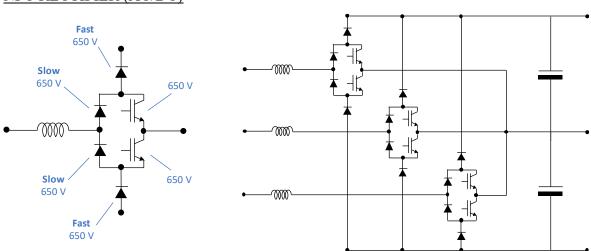

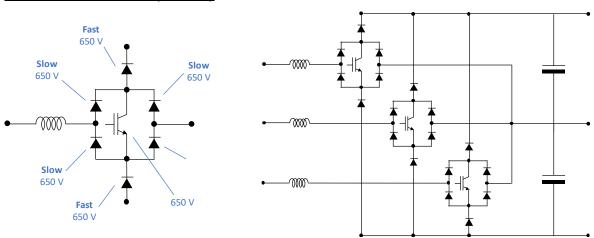

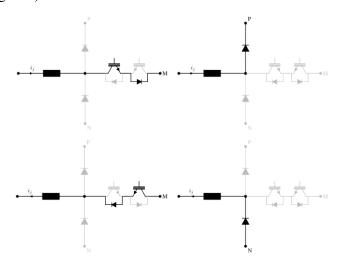

#### NPC RECTIFIER (AC/DC)

Fig. 9: AFE rectifier with NPC technology (1).

Each converter leg requires 2 fast diodes ( $V_{rated,D_{fast}} = 650 \text{ V}$ ), 2 slow diodes ( $V_{rated,D_{slow}} = 650 \text{ V}$ ) and 2 transistors ( $V_{rated,MOS} = 650 \text{ V}$ ). In this layout only 6 active switches are required (they can be unidirectional). As shown in figure 10, the NPC technology can be used also in inverter DC/AC applications. In this case, each converter leg requires 6 fast diodes ( $V_{rated,D_{fast}} = 650 \text{ V}$ ) and 4 transistors ( $V_{rated,MOS} = 650 \text{ V}$ ), thus at least 10 active switches (bidirectional) are required.

#### NPC INVERTER (DC/AC)

Fig. 10: AFE inverter with NPC technology (2).

NPC technology represents today's state of art for 3-levels converters. It guarantees:

- *half-voltage rated for semiconductor devices*, permitting to use LV devices also in MV applications with minimum voltage rating (until 1,7 kV of rated voltage);

- *reduced conduction losses* in comparison with an equivalent 2-levels structure (due to the decreasing of devices operating voltage).

Contrariwise, the main disadvantages regard:

- *increase in terms of cost* (more devices necessary);

- high parasitic capacitance (this issue is reduced if NPC is realized on an IC integrated circuit);

- more *complexity* of drivers and control systems.

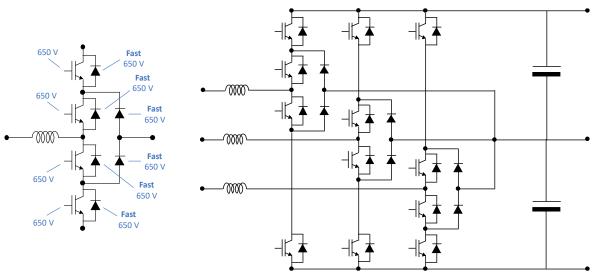

Among 3-levels topologies, *Vienna rectifier* has been widely used to achieve high conversion efficiency. Each converter leg requires 2 fast diodes ( $V_{rated,D_{fast}} = 650 V$ ), 4 slow diodes ( $V_{rated,D_{slow}} = 650 V$ ) and only 1 transistor ( $V_{rated,MOS} = 650 V$ ). The configuration proposed (figure 11) is the integrated one but Vienna-type can be both realized in integrated and not integrated configuration as shown in figure 12.

In Vienna-type only one transistor per leg is required. In comparison with NPC layout an inferior number of active switches is needed (reducing costs and losses of the converter). In non-integrated layout the losses can be even reduced with respect to integrated one, since clamping diode (up and down rail connections) are used only in freewheeling operations (but they have to be voltage fully rated). On the contrary, integrated topology is preferred for

higher voltage applications (because all devices are half voltage rated). The following pictures show the layout of the converters in integrated and not integrated topology.

#### VIENNA RECTIFIER (AC/DC)

Fig. 11: AFE technology with Vienna rectifier layout.

Fig. 12: Vienna topology in integrated and non-integrated layout.

In conclusion, the T-type converter is presented. This converter represents an innovative layout among 3-levels AC/DC or DC/AC applications, since it combines both the advantages of NPC structure and non-integrated Vienna-type. Thus, T-type guarantees:

- low conduction losses (like Vienna-type);

- low number of active components per leg required;

- simplicity of control (only one driver per leg is required).

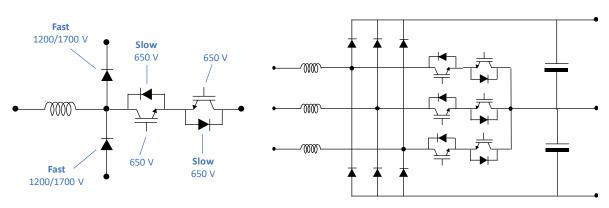

The T-type structure can be used both in AC/DC (as a rectifier) and in DC/AC application (as a multi-level VSI). The schematics of those converters are shown in the following figures (13 and 14).

#### T-TYPE RECTIFIER (AC/DC)

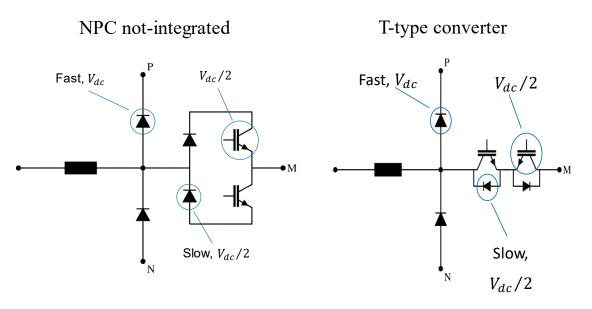

Fig. 13: AFE technology with T-type rectifier layout.

Each converter leg requires 2 fast diodes ( $V_{rated,D_fast} = (1200 \div 1700)$  V), 2 slow diodes ( $V_{rated,D_slow} = 650$  V) and 2 transistors ( $V_{rated,MOS} = 650$  V). The last two couples of devices can be substituted by two MOSFETs (using as a slow diode the embedded diode within the transistors). Only 6 active switches (unidirectional) are required.

Per each phase leg, one diode is used for positive or negative rail clamping while the remaining ones are anti-series connected to two switches (MOSFETs) to realized middle point connection. This is the striking difference between NPC-non-integrated and T-type converter: in the former the mid-point connection was realized by two anti-parallel switches, in the latter by anti-series ones.

Fig. 14: Comparison layout between T-type and NPC-non-integrated.

As a reminder, the 3-levels T-type converter basically combines the positive aspects of the two-level converter (such as low conduction losses, small part count and a simple operation principle) with the advantages of the 3-levels converter such as low switching losses and superior output voltage quality. Furthermore, with the use of SiC Schottky diodes, the reverse recovery loss from diodes can be eliminated, which makes T-type rectifier a promising topology in achieving high efficiency for today and future applications. Additionally, it is suitable for bidirectional current flow. For these reasons, *T-type rectifier is regarded as the basic converter unit for interleaved system*.

Finally, the T-type for DC/AC application is presented (figure 15). Each converter leg requires 2 fast diodes ( $V_{rated,D_{fast}HV} = (1200 \div 1700)$  V), 2 transistors ( $V_{rated,MOS_HV} = (1200 \div 1700)$  V), 2 fast diodes ( $V_{rated,D_{fast}LV} = 650$  V) and 2 transistors ( $V_{rated,MOS_LV} = 650$  V). The last two couples of devices can be substituted by two MOSFETs (using as a slow diode the body diode within the transistors). At least 12 switches (bidirectional) are required in DC/AC applications. Both structures guarantee very low conduction losses.

#### T-TYPE INVERTER (DC/AC)

Fig. 15: AFE technology with T-type inverter layout.

The state of art for multi-level converters for UFC is oriented to obtain a reliable and efficient structure, in order to manage easily switching operation at higher and higher rated voltage values. The use of parallel T-type structures is the preferred layout for AFE application in UFC, since it leads to a converter with very low conduction losses, easy control drivers and interleaved connection for high voltage application. This converter is called as *T-type interleaved*. The following schematic has been already presented in [5].

Fig. 16: T-type interleaved AFE.

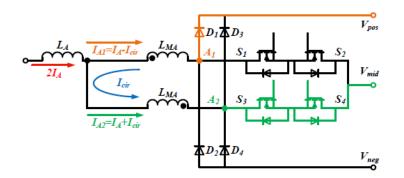

#### **1.3** T-type interleaved as active rectifier

[5] In high power applications, the multi-level, mixed topologies, or parallel multiple methods (interleaving) is an effective way for expansion of the capacity of the converter. In three-phase parallel systems there are many advantages, such as increasing the current level, reducing the current and voltage ripple, and last but not least, achieving higher bandwidth. In addition, the cancellation effect among interleaved sub-converters allows smaller input filters (lower filtering inductance  $L_F$ ) and helps to meet EMI requirements. In other words, interleaving permits to obtain the same power quality with the same passive components but with lower *switching frequency*  $f_{sw}$  of each sub-converter than a single converter layout, ensuring smaller switching loss. The basic scheme of a single unit of the AC/DC interface is shown in figure 17.

Fig. 17: Basic model for AC/DC interface.

The P and N rails of AFE converter are simple diodes of a bridge rectifier (AC/DC interface) and for this reason they are chosen only in terms of rated voltage. Diodes are simple unidirectional and unipolar devices and this leads to a remarkable robustness and easiness of control. Conversely, the mid-point switches have to be *bipolar and bidirectional*. This is the main issue of the converter because in practice, those devices *do not exist*.

Therefore, these switches are realized by a suitable combination of existing semiconductor devices, through the use of one of the topology already seen in the previous section (paragraph 1.2).

The T-type interleaved converter is obtained connecting in parallel at least two identical Ttype converters. Thus, *T-type interleaved converter* represents the fittest device for AFE application (and active power filters in general).

Fig. 19: Interleaved T-type converter.

The operation principle of the T-type converter is explained in figure 20 (with reference to the single operating unit).

Fig. 20: Operation principle of T-type converter, single unit (1)

The circuit on the left shows the active phase switching of the converter, while the right ones display freewheeling operations. A boost inductor is usually collocated upstream the converter to perform both boost and filtering tasks. In certain application, the two corresponding phase legs (in different sub-converters) are then linked together with an

ulterior inter-phase inductor in series to the boost inductors (figure 21), to increase the whole input inductance of the converter (for flux ripple and HF circulating current reduction).

The T-type converter is a *current-commutated converter*: the devices participating in commutation are determined by current direction. With reference to figure 21, if current  $I_{A1}$  is positive [5], the commutation will involve the components  $D_1$ ,  $S_1$  and  $S_2$ . As a result, the voltage potential at point  $A_1$  with reference to the middle point of DC bus will be either half of whole DC bus voltage (with  $S_1$  and  $S_2$  off) or zero (with  $S_1$  and  $S_2$  on).

Fig. 21: Operation principle of T-type converter, interleaved, single unit (2).

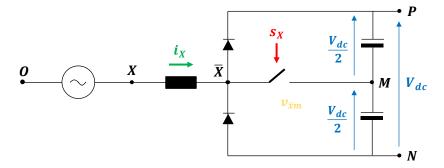

Indeed, the previous consideration it is valid for all phases; thus, the input voltage formation depends only on (see figure 22)

- the mid-point switch state  $s_x$  (the only one controllable by the driver);

- the current direction  $sgn(i_x)$  due to the unidirectional nature of the rectifier stage.

$$v_{\bar{x}m} = (1 - s_x) \cdot sgn(i_x) \cdot \frac{v_{dc}}{2}$$

(1.4)

Consequently, only three values of voltage can be realized by the converter:

Fig. 22: Input voltage formation.

Vector selection for instantaneous voltage regulation is depicted in a 3-levels 3-phase hexagon, shown in figure 23 [5]. The blue circle in the picture represents the track of the output voltage vector.

Fig. 23: Voltage selection in a 3-levels 3-phase hexagon.

In particular, the states m, n and p stand for three different instantaneous voltage values performed by the converter.

$$\begin{cases} \mathbf{P} \text{ state } \Rightarrow v_{\bar{X}M} = +\frac{V_{dc}}{2} \\ \mathbf{M} \text{ state } \Rightarrow v_{\bar{X}M} = 0 \\ \mathbf{N} \text{ state } \Rightarrow v_{\bar{X}M} = -\frac{V_{dc}}{2} \end{cases}$$

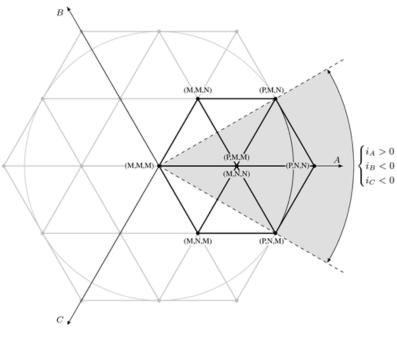

Space vector representation is useful to understand the operation of the 3-level converter.

Fig. 24: SV representation of instantaneous voltage vector.

There are 6 different sextants, defined by the 3 currents directions. In each one, there are  $2^3$  switching states and 7 voltage vectors (then, 2 are redundant). Thus, those  $3^3 = 27$  switching states (p, m, n for each bridge leg) yield to 19 voltage vectors (considering redundant states). Voltage and current vectors can be expressed through the following formulas

$$\begin{cases} \vec{v} = \frac{2}{3} \cdot \left( v_{\bar{A}} + v_{\bar{B}} \cdot e^{j\frac{2\pi}{3}} + v_{\bar{C}} \cdot e^{j\frac{4\pi}{3}} \right) \\ \vec{i} = \frac{2}{3} \cdot \left( i_{A} + i_{B} \cdot e^{j\frac{2\pi}{3}} + i_{C} \cdot e^{j\frac{4\pi}{3}} \right) \end{cases}$$

(1.5)

The space vector representation directly highlights the upper voltage limit in linearity (figure 25): the max phase voltage value is calculated as usually, assuming  $V_{dc}$  for voltage DC-link maximum amplitude.

$$v_{\bar{x},max} = \frac{V_{dc}}{\sqrt{3}} \text{ in non-linearity operations}$$

(1.6)

The formula (1.6) displays the advantage in terms of regulation to master the common mode voltage, since the max output voltage increase as shown in figure 25 (from  $\frac{1}{3}$  to  $\frac{1}{\sqrt{3}}$  of the voltage DC-link max value V<sub>dc</sub>).

Fig. 25: Limits of regulation in 3-phase 3-levels hexagon and (m, cos  $\varphi$ ) chart of the converter.

As usually, the modulation index is defined as by the following formula

$$m = \frac{|\vec{v}|}{\frac{V_{dc}}{2}}, \quad m \in \left[0, \frac{2}{\sqrt{3}}\right] \tag{1.7}$$

Since 2 of the 7 voltage vectors are located  $\pm 30^{\circ}$  outside the 60° current sector, it is possible to operate the rectifier with up to  $-30^{\circ} < \phi < +30^{\circ}$  phase shift between input voltage and current vectors. However, as the rectifier input voltage amplitude  $|\vec{v}|$  approaches its maximum value  $v_{\vec{x},max} = \frac{V_{dc}}{\sqrt{3}}$ , the maximum phase shift decreases until it reaches zero at the

maximum rectifier input voltage amplitude (as shown in figure 24 and 25). In this manner, the (m,  $\cos\varphi$ ) chart of the converter is plotted according to (1.6) equations (figure 25, right).

$$|\varphi|_{max} < \begin{cases} \frac{\pi}{6} \text{ if } m \le \frac{2}{\sqrt{3}} \text{ linearity operation} \\ \frac{\pi}{3} - \arccos\left(\frac{1}{\sqrt{3} \cdot m}\right) \text{ otherwise (non - linearity)} \end{cases}$$

(1.8)

In non-linearity operation, the common mode voltage component  $v_{0_{LF}}$  is used to adjust the voltage output to the desired value (over-modulation). The common mode voltage component  $v_{0_{LF}}$  is limited since the rectifier input voltage of each phase (i.e.  $v_{\bar{X}M}$ ) is limited between 0 and  $sgn(i_X) \cdot V_{dc}/2$ . Consequently,

$$\begin{cases} \boldsymbol{v}_{0,max} = min\left(\frac{V_{dc}}{4} \cdot (sign(i_X) + 1) - v_{\bar{X}_{LF}}\right) \\ \boldsymbol{v}_{0,min} = max\left(\frac{V_{dc}}{4} \cdot (sign(i_X) - 1) - v_{\bar{X}_{LF}}\right) \end{cases}$$

(1.9)

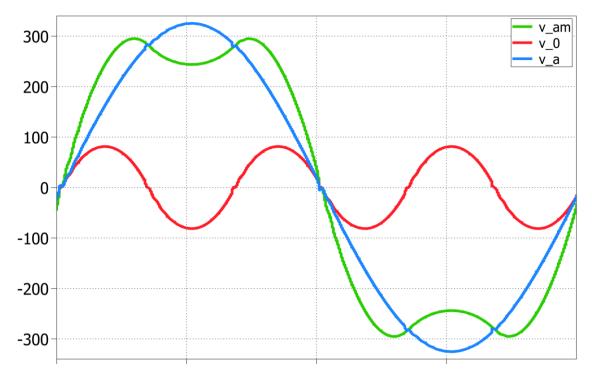

The waveform of the common mode voltage  $v_{0_{LF}}$  depends on the specific modulation strategy used to control the converter. Figure 27 shows same examples of common mode voltage component using 4 different modulation techniques reported in literature (PWMC, ZMPC, CSVM and DPWMC).

Fig. 26: Examples of  $v_{0_{LF}}$  for different modulation strategies (PWMC, ZMPC, CSVM and DPWMC).

Furthermore, to operate the whole converter in interleaved manner, the control can introduce a *phase shift*  $\alpha$  between the carriers of the two corresponding phases in different subconverters. The phase shift between the carriers can be used to achieve different results, for example, reduction of flux ripple on L<sub>Boost</sub>, current distortion cancellation (to obtain a considerable low THD or TDD) and mitigation of current ripple on output DC-link. A specific paragraph will be dedicated to the topic (*2.2 Hardware design*).

In an interleaved system, all phases operate in a simultaneous way and for this reason, the common mode voltage  $v_0$  results as a linear combination of the phase voltages  $v_{AM}$ ,  $v_{BM}$  and  $v_{CM}$ .

$$v_0 = \frac{v_{\bar{A}M} + v_{\bar{B}M} + v_{\bar{C}M}}{3} \tag{1.10}$$

And then, the phase voltages

$$\begin{cases}

\nu_{\bar{A}} = \nu_{\bar{A}M} - \nu_{0} \\

\nu_{\bar{B}} = \nu_{\bar{B}M} - \nu_{0} \\

\nu_{\bar{C}} = \nu_{\bar{C}M} - \nu_{0}

\end{cases} (1.11)$$

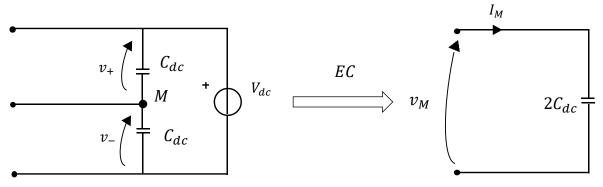

The equivalent circuit (EC) of the t-Type converter is described in the following figure.

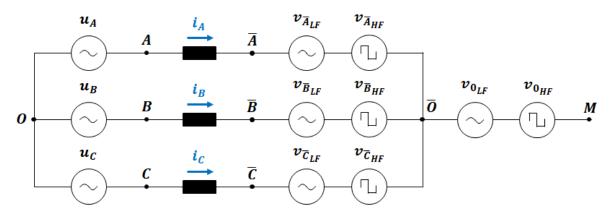

Fig. 27: EC of the T-type interleaved converter.

The phase voltages are classified in LF (low frequency) and HF (high frequency) components. LF voltages components  $(v_{\bar{A}_{LF}}, v_{\bar{B}_{LF}}, v_{\bar{C}_{LF}})$  permits to generate the mains current fundamental components  $(i_{A_{LF}}, i_{B_{LF}}, i_{C_{LF}})$ , while the HF components  $(v_{\bar{A}_{HF}}, v_{\bar{B}_{HF}}, v_{\bar{C}_{HF}})$  deals with the mains current at switching frequency (ripple component generation,  $i_{A_{HF}}, i_{B_{HF}}, i_{C_{HF}}$ ). For this reason, it is necessary to tune an appropriate filter (LCL design) in order to reduce those HF residual component and meet EMI standards, moreover eliminating ripple and noise component (see paragraph 2.2.2 Grid-converter interface, LCL filter design).

The phase current is generated by the interaction between the mains phase voltage and the  $1^{st}$  harmonic of the formed bridge voltage (u<sub>A</sub>, u<sub>B</sub>, u<sub>C</sub>). The  $\delta$  angle is negligible since L is small (due to *high f<sub>sw</sub>*).

$$\begin{cases}

i_{A} = \frac{u_{A} - v_{\bar{A}_{LF}}}{j\omega L} \\

i_{B} = \frac{u_{B} - v_{\bar{B}_{LF}}}{j\omega L} \\

i_{C} = \frac{u_{C} - v_{\bar{C}_{LF}}}{j\omega L}

\end{cases}$$

(1.12)

$$j\omega L \cdot i_{X} \\

\int \delta \\

v_{\bar{X}_{LF}}

\end{cases}$$

Fig. 28: Vector illustration of phase currents.

$i_X$

The LF common mode voltage  $(v_{0_{LF}})$  is used in usual regulation operations (extension of the modulation range, DC-link mid-point voltage balancing, switching loss minimization, etc.) but at the same time it generates a switching frequency common-mode current ripple that is a unique issue for interleaved converter, known as *circulation current*  $i_{CM_{HF}}$ .

#### **1.4 Mid-point balancing**

[5] Interleaving two sub-converters brings unwanted circulating current into the system. Circulating current is the current produced by LF differential mode voltage ( $v_M^{LF}$ ), calculated as the difference between interleaved phases (called V<sub>+</sub> and V<sub>-</sub> in figure 29).

In accordance with figure 21, the current flowing through input boost inductor is defined as  $2I_A$ . In both interconnected sub-converter, each complementary phase is crossed by currents  $I_{A1}$ ,  $I_{A2}$ . If the system had been ideal, the magnitude of those currents would have been equal for both phases, thus

$$I_{A1} = I_{A2} = I_A \tag{1.13}$$

Because the circulating current would have been null. In real system, is necessary to assume

$$\begin{cases} I_{A1} = I_A - I_{circ} \\ I_{A2} = I_A + I_{circ} \end{cases}$$

(1.14)

Then, the system results to be inherently unbalanced. The *circulating current* is highlighted as the halved-difference between the two phase currents.

$$I_{circ} = \frac{1}{2} (I_{A2} - I_{A1}) \tag{1.15}$$

[5] For example, if point  $A_1$  is clamped to positive rail by diode  $D_1$  and  $A_2$  is connected to middle point of DC-bus by  $S_3$  and  $S_4$  (coloured in green in figure 21), the voltage difference between  $A_1$  and  $A_2$  will generate the circulating current within the two phases. If the impedance between the two points is not large enough, the circulating current will not only create additional conduction loss and HF disturbances emission but also impede the functionality of the converter. In extremal unbalanced situations, when  $I_A$  is positive, point A1 should be clamped to either positive rail by  $D_1$  or middle point of DC bus by  $S_1$  and  $S_2$ . However, if  $I_{cir}$  is so high that  $I_{A1} = I_A - I_{cir} < 0$ , point  $A_1$  will not be able to be connected to positive rail when  $S_1$  and  $S_2$  are off, instead, it will be clamped to negative rail, resulting in *false modulation*. In conclusion, circulating current in interleaved current-commutated converters should be well controlled (it has to be the lowest possible, in ideal system, it should be null). Anyway, in real interleaved converters, the voltage difference between the two points  $A_1$  and  $A_2$  is inevitable.

A practical way to attenuate the circulating current would be to increase the impedance between the two interleaved points  $A_1$  and  $A_2$  (or others) at frequencies close to switching frequency. Adding *coupled inductors (inter-phase inductors)* between interleaved phases (like  $L_{MA}$  for phase  $A_1$  and  $A_2$  in figure 21) can effectively increase the impedance of the circulating loop, while keeping minor influence on the common current (I<sub>A</sub>). However, the use of inter-phase inductors could lead to a global increase in terms of cost (more components necessary) and losses. Moreover, design of the inter-phase inductors has not been explicitly described in any literature yet. For these reasons, it is preferred not to use inter-phase inductors and rather to search for specific modulation strategies to manage the circulating current to zero. An example of a suited modulation technique is *Zero-Mid-Point-Current* modulation (that permits to reduce to minimum the mean value of circulating current, even to zero if the system is studied under ideal switching hypothesis). For a comprehensive description of this and other modulation techniques cited in this paper, the reader should move to paragraph 1.5.

The circulation current issue is directly connected with *mid-point balancing*. In fact, it is to note that, referring to figure 29, the current  $i_P$ ,  $i_N$  and  $i_M$  are tied together by the Kirchhoff's current law applied to point M.

$$i_P + i_N + i_M = 0 (1.16)$$

In this way, the voltage difference between positive and negative voltages ( $V_+$  and  $V_-$ ) of the split DC-link may be expressed through the mid-point current in the Laplace's domain as:

$$v_M(s) = [V_+ - V_-](s) = \frac{1}{sC_{dc}}(i_P + i_N) = -\frac{i_M}{sC_{dc}}$$

(1.17)

Fig. 29: AFE overview.

In other words, the mid-point current causes a voltage unbalance at the output of the AC/DC stage. Theoretically, the two output DC-link capacitors in series should split the output voltage in two equal parts (i.e.  $\frac{V_{dc}}{2}$ ). Nevertheless, in real working conditions not only the non-null circulating current but also other factors could lead to a global voltage unbalance for the system, for example:

- physical difference between the two capacitors ( $C_{dc+} \neq C_{dc-}$ );

- mains-side voltage unbalance;

- different switching dead-times between bridge legs;

- load unbalance on the DC-link side.

Two voltage control loops must be realized to provide an efficient converter voltage control: the first one which regulates the full  $V_{dc}$  output voltage (i.e. by regulating the input power) and the second one which controls the voltage difference between the two capacitors to zero (i.e. by means of a suitable common-mode voltage injection). It is to note that, the first voltage loop acts at the main period (50 or 60 Hz, for UE or USA grid), while the second it is to intend as a *third harmonic voltage control*. Thus, a couple of relations may be verified by the control instantaneously:

$$\begin{cases} V_{+} + V_{-} = V_{dc} \\ V_{+} - V_{-} = v_{M} = 0 \end{cases}$$

(1.18)

Considering all the possible state for the structure (figure 30), the redundant states (P, M, M) and (M, N, N) (they represent the same voltage vector) can be used to balance the mid-point current, by time partitioning the two intervals (state duration).

Fig. 30: AFE possible switch states.

There is a strict correlation between the time partitioning of the redundant space vectors (SVM control) and the third-harmonic common-mode voltage injection (PWM control). By defining, ( $\alpha_A$ ,  $\alpha_B$ ,  $\alpha_C$ ) as the *relative ON-times of bridge leg switches*:

$$\begin{cases} \alpha_{A} = 1 - \frac{|v_{\bar{A}M_{LF}}|}{V_{dc/2}} \\ \alpha_{B} = 1 - \frac{|v_{\bar{B}M_{LF}}|}{V_{dc/2}} \\ \alpha_{C} = 1 - \frac{|v_{\bar{C}M_{LF}}|}{V_{dc/2}} \end{cases}$$

(1.19)

Assuming that  $v_{\bar{X}M_{LF}} = v_{\bar{X}_{LF}} + v_{0_{LF}}$  (and x = A, B, C) it will be

$$i_M = \alpha_A \cdot i_A + \alpha_B \cdot i_B + \alpha_C \cdot i_C \tag{1.20}$$

Formula 1.20 demonstrates the fact that the mid-point current local average  $i_M$  depends on the common-mode voltage component  $v_{\bar{X}M_{LF}}$  (where  $\bar{X} = \{\bar{A}, \bar{B}, \bar{C}\}$ ). Consequently, also the  $i_M$  waveform varies depending on the modulation technique used to achieve a certain common mode voltage (PWMC, DPWMC, CSVM or ZMPC). Due to the common-mode voltage limits, also the mid-current regulation is limited. Finally, 1.21 and 1.22 formulas state this dependency.

$$\begin{cases} \mathbf{i}_{M,max} = -\frac{1}{V_{dc}/2} \cdot \left( \left( v_{\bar{A}_{LF}} + v_{0_{max}} \right) \cdot |i_{A}| + \left( v_{\bar{B}_{LF}} + v_{0_{max}} \right) \cdot |i_{B}| + \left( v_{\bar{C}_{LF}} + v_{0_{max}} \right) \cdot |i_{C}| \right) \\ \mathbf{i}_{M,min} = -\frac{1}{V_{dc}/2} \cdot \left( \left( v_{\bar{A}_{LF}} + v_{0_{min}} \right) \cdot |i_{A}| + \left( v_{\bar{B}_{LF}} + v_{0_{min}} \right) \cdot |i_{B}| + \left( v_{\bar{C}_{LF}} + v_{0_{min}} \right) \cdot |i_{C}| \right) \end{cases}$$

Fig. 31: Maximum instantaneous range of  $i_{M}$ .

In conclusion, the output voltage balance is inherently limited by the mid-point current restrictions (could become more difficult as voltage magnitude increases).

### **1.5 Modulation strategies**

A variety of different modulation techniques have been presented in literature about 2-levels and 3-levels converters control. The modulation technique largely defines the generated harmonic content of voltages and currents, making this aspect of the project of the converter a key point that must be studied in depth; thus, depending on the application, there will be a modulation technique more suitable than others. All modulation schemes applicable to 2levels rectifiers can be applied to interleaved or multi-level converters since any sub-unit can generate their outputs independently.

A primal characterization concerns *continuous* and *discontinuous modulation techniques*. In continuous technique each phase modulation index  $m_f$ , with  $f = \{a, b, c\}$  (or duties  $d_A$ ,  $d_B$ ,  $d_C$ ), varies with continuity instantaneously, while in discontinuous techniques, for a certain interval of time (or exactly, phase), one or more phase indexes result to be clamped to the to the upper and lower DC-link rails (both or singularly). In this way, discontinuous techniques avoid switching around the maxima [5] (because the clamping happens when the phase current results close to its maximum value) but they are not suited for  $i_M$  control.

Consequently, discontinuous techniques are chosen if the purpose of control is oriented to switching loss reduction, while continuous one are preferred in terms of performance (ripple reduction), flexibility, and high frequency component attenuation.

In this paper, 4 different techniques will be presented:

- Space Vector PWM (SVPWM), where the common-mode voltage v<sub>0</sub> is the one obtained by the standard space-vector approach (PWM compute as in 2-levels converter);

- *Discontinuous PWM with 30° Upper/Lower Clamping (DPWM4)* in which each phase is alternatively clamped to the upper and lower DC-link rails, each for 30°;

- *Three Level SVPWM (TLSVPWM or simply CSVM, continuous space vector modulation)*, in which the duty calculation works in a continuous manner in all phases (PWM compute for 3-levels converters);

- Zero Mid-Point Current PWM (ZMPCPWM), in which the modulation strategies is wholly oriented to mid-point current magnitude minimization.

Next paragraphs will explain in a comprehensive way the main features of those techniques, considering phase voltages, common-mode voltage injection, duties waveform and grid current harmonic content.

In a 3-levels AC/DC converter *the only state that can be controlled is the M state*. In fact, P and N states represents respectively the upper and lower rails connection, which work like in a 2-levels rectifier (thus they reach the output voltage of  $\pm \frac{1}{2}V_{dc}$ , respectively). The control function of the entire converter is  $s = (s_A, s_B, s_C)$  is then calculated with the use of a 3-levels *PWM modulation*, implemented in a logical way only with the use of a Boolean algorithm. In a 3-levels PWM are used two carriers (one called as low carrier  $c_L$  and the other as high carrier  $c_H$ )

$$\begin{cases} d(t) > c_H(t) \to P \text{ state } \to v(t) = V_{dc} \\ c_L(t) < d(t) < c_H(t) \to M \text{ state } \to v(t) = 0 \\ d(t) < c_L(t) \to N \text{ state } \to v(t) = -V_{dc} \end{cases}$$

(1.23)

Thus, the t-Type M switch is enabled (ON) while the duty cycle of a certain phase x is inside the low and high carriers. In this case the output voltage is equal to zero. In a similar way, the output voltage is equal to  $(-V_{dc})$  and the transistor is disabled (OFF) if the duty is beneath both carriers (otherwise, is equal to  $V_{dc}$  if the duty stays over both carriers). Duty cycles are expressed analytically through (1.24) formula (where the x = {a, b, c} as usually).

$$d_x = \frac{1}{2} + \frac{v_x + v_0}{v_{dc}} \tag{1.24}$$

Figure 33 displays considerations shown by 1.21 (valid for any modulation technique).

Fig. 32: Example of 3-levels PWM modulation.

Thus, the logical control of mid-point switches could be rewrite in a simple way as follow

$$\begin{cases} s_x = 0 \text{ if } (d_x \ge c_H) \text{ or } (d_x \le c_L) \\ s_x = 1 \text{ if } (d_x < c_H) \text{ and } (d_x > c_L) \end{cases}$$

(1.25)

The BEM (balanced enveloped modulation) can be implemented also in a 3-levels converters. In this way, it is possible to guarantee the best voltage usage of the converter, since the balancing of positive and negative envelops permits to over-modulate the output voltage (accordingly,  $m_{max,notmodulated} = 1$  and  $m_{max,BEM} = 2/\sqrt{3} \approx 1,15$ ) without distortions when working in non-linearity conditions (thus, between 1 and  $2/\sqrt{3}$ ). The next figure shows the waveforms of the duties in both circumstances.

Fig. 33: Duties comparison with disabled or enabled BEM.

In conclusion, the control routine for duty generation is reported in the appendix A1.

### **1.5.1 Space Vector Modulation (SVPWM)**

The PWMCompute function is used to calculate abc duty-cycles starting from phase voltages reference. It is the easiest technique which permits to apply BEM to the output voltages. In practical, the control algorithm works as in a 2-levels converter.

However, it is necessary in any case to evaluate exactly the *voltage zero sequence*  $v_{zs}$  (called v\_o in the code, appendix A2). Consequently, the duties are distorted by the control to achieve the increase of the output voltage with a proper common mode addition ( $v_{zs}$ ). The  $v_{zs}$  can be obtained in many manners: in the code it is half of the medium voltage of the abc triad (then it is necessary to provide to an adequate sorting algorithm).

$$v_0^{LF} = v_{zs} = -\frac{1}{2}(EN_n + EP_n)$$

(1.26)

$EN_n$  and  $EP_n$  are the non-modulated positive and negative voltage envelops (instantaneous max and min voltages of the triad abc). The following figure shows the periodic average of expected waveforms using this technique.

Fig. 34: Expected waveforms with PWMCompute.

A comparison may be relevant, between SPWM (sinusoidal PWM, in which no voltage common mode is injected) and Space Vector PWM Computation (PWMC) already described. As shown in figure 33, the former has high quality of the output waveform, but the more switching frequency increase the more switching losses become relevant, and in

any case it has low utilization of DC voltage. On the contrary, the latter can get better output voltage waveform with not very high switching frequency, and maintaining a higher utilization rates of DC voltage. In addition, SVPWM together with inter-leaving paralleled technology would be a better method to mitigate the circulation current.

In conclusion, is reported in the Appendix A2 the code implemented to run PWMCompute technique.

# 1.5.2 Discontinuous PWM with 30° Upper/Lower Clamping (DPWM4)

The crucial point of discontinuous PWM modulation strategies regards the reduction of switching loss of the converter. As presented in article [4], the turn-on loss energy for a single conversion unit (switch and diode) can be expressed through the following formula:

$$E_{turn-ON} = \frac{1}{2} V_{out} I_{load} \Delta t_{turn-ON} + \frac{1}{2} V_{out} Q_{diode}$$

(1.27)

In the last formula (1.23), it is assumed that:

- *V<sub>out</sub>* is the DC bus voltage;

- *I*<sub>load</sub> is the current absorbed by the load (different load currents could lead to different turn-ON energy);

- *Q*<sub>diode</sub> is the total capacitive charge of the junction capacitor of the fast diodes, which could be found in datasheet of the diodes (it could be consider negligible using Schottky SiC diodes). It is to note that diodes with higher current capability (I<sub>MAX,rated</sub>) have higher Q<sub>diode</sub> (that means at the same time higher switching loss);

The expression of turn-OFF energy is not reported in this paper (but it results to be quite similar to 1.27). The discontinuous PWM technique are then oriented to reducing of switching loss without reducing the switching frequency  $f_{sw}$ , through the reduction of the numbers of commutation per period of switching (2 per 3 switches, thus 6 commutations). Consequently, discontinuous techniques have to work in a trivial way: the output phase with the momentary highest current is not switched over a fixed electrical angle (30°, 60° or 120°) and it remains clamped to the maximum voltage value permitted, that is the DC-link rail voltage (positive or negative, as appropriate). This keeps a significant reduction of switching losses but could lead to an increasing mains current ripple (constraining to use bigger filter). [5] To achieve phase clamping, for example, in area 1 (figure 23), vector [p n n], [p n m] and [p n m] are selected for the lower part, while vector [p m m], [p m n] and [p n n] are selected

for the upper part. These selections ensure that phase *A* is clamped to positive rail when the desired output voltage vector is in area 1. It is worth noting that, in area 1, current in phase *A* is close to its maxima. In area 2, vector [p m m], [p m n] and [m m n] are selected to ensure phase B is clamped to middle point, where current in phase B crosses zero. Thus, this scheme not only avoids switching around the maxima but also avoids switching around zero crossing of associated phase current. The last phenomenon is caused by  $O_p$  and  $O_n$  states overlapping within the interleaved structure. A suitable discontinuous modulation technique should be oriented to avoid zero overlapping through the elimination of one zero state ([n n n] or [p p p], as reported in [4]). For example, a 30° DPWM technique (DPWM4) for lower and upper 30° phase rail clamping, can be implemented as described in appendix A3.

Fig. 35: DPWM4 expected waveforms.

### **1.5.3 Three levels Space Vector PWM (TLSVPWMC)**

In TLSVPWMC (3-levels Space Vector Pulse Width Modulation Compute or simply continuous space vector modulation, CSVM) technique the  $v_{zs}$  component is obtained in a similar way of SVPWM (using a sorting algorithm) but in this case all phases contribute simultaneously to common mode calculation. In addition, an ulterior voltage common mode component (called v shift in the code) is used to duty calculation, defined as follow:

$$v_{shift} = \frac{1}{2} \cdot \left[ V_{dc} - (EP_n + EN_n) \right]$$

(1.28)

$EP_n$  and  $EN_n$  are also in this case the instantaneous maximum and minimum value of phase voltages of the triad abc (not modulated). Then, the modulated voltages,  $v_a$ ,  $v_b$ ,  $v_c$  are calculated through the use of *finod* function which returns the floating-point remainder of *numerator/denominator* (rounded towards zero). Assuming that  $u_a$ ,  $u_b$ ,  $u_c$  are the initial voltage value (not shifted), the modulated voltages (shifted), are calculated analytically as follow:

$$\begin{cases} v_{a} = fmod[(u_{a} + v_{shift}), (1/2 \cdot V_{dc})] \\ v_{b} = fmod[(u_{b} + v_{shift}), (1/2 \cdot V_{dc})] \\ v_{c} = fmod[(u_{c} + v_{shift}), (1/2 \cdot V_{dc})] \end{cases}$$

(1.29)

The sorting procedure starts like in SVPWM and  $EP_m$  and  $EN_m$  are calculated (were  $EP_m$  and  $EN_m$  stand for the positive and negative envelop of modulated voltages  $v_a$ ,  $v_b$ ,  $v_c$ ); then, duties are evaluated with the use of a new  $v_{zs}$  defined as:

$$v_{zs} = -\frac{1}{2} \cdot (EP_n + EN_n) - \frac{1}{2} \cdot (EP_m + EN_m) + \frac{1}{4} \cdot V_{dc}$$

(1.30)

The last formula (1.30) demonstrated that all phases are used by this modulation strategy for  $v_{zs}$  calculation, resulting finally in an overall improving of voltage output quality for the load with respect to the simple SVPWM compute for 2-levels converters described in paragraph 1.5.1.

The next figure shows the expected waveform for CSVM technique.

Finally, the appendix A4 shows an example of code to implement CSVM.

### 1.5.4 Zero Mid-Point Current PWM (ZMPCPWM)

Nevertheless multi-level and parallel converters are effective methods for enhancing both the voltage and current capacity and the performances of a power electronic converter, putting modules in parallel is not risk free.

Zero Mid-Point Current PWM is the most appropriate modulation technique for AFE interleaved converters. [4] In fact, one of the major concerns for the parallel operation of a three-phase interleaved system is the *cross-coupling* between the three-phase system parallel modules. For example, when each module of a converter, in a certain switching state, is connected contemporaneously to the same DC bus and to a common power supply or load, a privileged path for circulating current may occurs (cross coupling effect). In order to avoid this problem, the traditional method is to use an isolation transformer. However, the use of transformer will undoubtedly increase the size and cost of the entire system, especially in high power and low switching frequency occasions, where this problem results prominent.

Therefore, the circulating current result to be generated from the difference of voltage between two analogous points of the same phase of the two (or more) interleaved units. The expected waveform of circulating current is then associated to the state of 2 coupled switches of 3 belonging to a single 3-phase module.

The main disadvantages related to the circulating current issue regard:

- *increasing of passive component dimensions* (the size of boost and filter inductors increases in comparison with ideal condition in which there is not any circulating current effect);

- in extremal unbalanced systems the circulating current issue could even lead to a whole *impossibility of control* (false modulation);

A winning way to deal with circulating current without using further hardware components is to manage an adequate common mode voltage  $v_0^{LF}$  to obtain the minimum mean value of  $i_M$ . The ZMPC modulation strategy is used to achieve this result. It guarantees a variety of advantages:

- reduction of flux ripple  $\Delta \Psi_{pp}$  on the boost inductance;

- reduction of peak value of circulating current i<sub>M</sub> (that is in any circumstance a zero mean value waveform);

- reduction of RMS value of capacitor current of the split DC-link;

- reduction of THD and TDD of the current absorbed from the grid.

As a consequence, the ZMPC is suitable for optimal hardware design project and it represents a consistent and robust solution to manage mid-point balancing in interleaved multi-level converters. The following figure shows the expected waveforms of phase and common mode voltages generated with ZMPC technique. In addition, a code example for ZMPC implementation is described in appendix A5.

Fig. 37: ZMPC expected waveforms.

The common mode voltage  $v_0$  results to be a purely 3th harmonic waveform, with null fundamental component. This leads to a magnitude reduction of the mid-point current, which in ideal conditions result even to be null. The phase medium-point voltage seems to follow a "helmet waveform" due to the fact that  $v_{\bar{A}M} = v_{\bar{A}} + v_0$  (formula 1.11) and thus it depends on the common mode component (it decreases, with respect to the phase voltage, as  $v_0$  decreases).

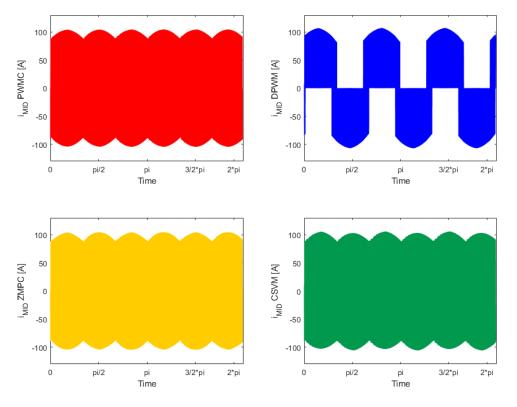

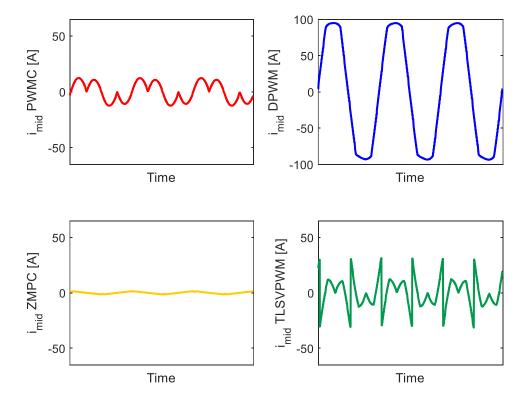

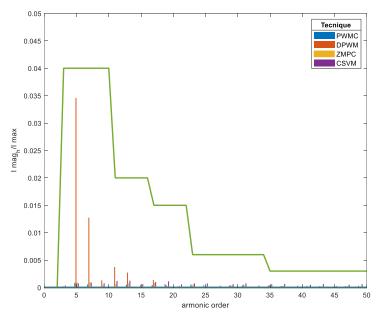

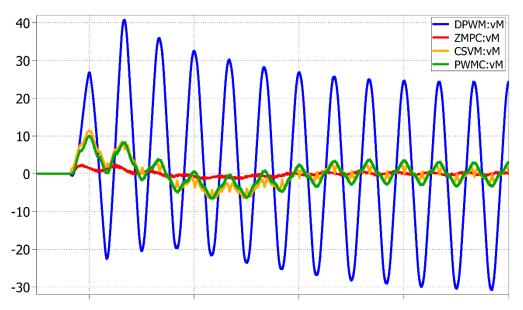

The following pictures (figure 38 and 39) display a comparison of mid-point current per modulation techniques in terms both of ripple and periodic average component (from left to right, left top PWMC, right top DPWM, left bottom ZMPC and finally right bottom CSVM).

Fig. 38: *i<sub>M</sub>* ripple component for different modulation techniques.

Fig. 39: *i*<sub>M</sub> periodic average values for different modulation techniques.

### 1.5.5 Duty cycles comparison table

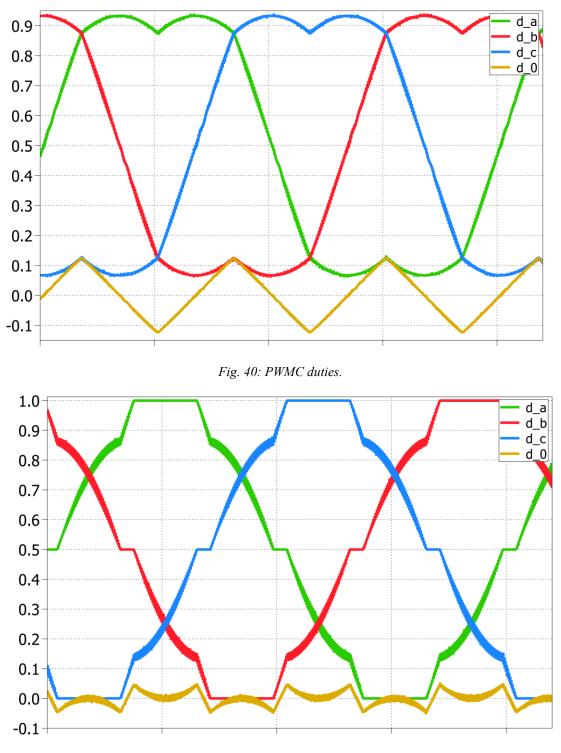

Finally, a comparison between different duty cycles generated with each modulation technique is reported in this paragraph. The expected waveform take in account of all phases of the triad abc (thus  $(d_A, d_B, d_C)$  as reported in the following figures) of a single sub-converter unit and also the common mode index (called as  $d_0$ ).

Fig. 41: DPWMC duties.

Fig. 43: ZMPC duties.

Duty  $d_0$  represents the additional duty cycle contribute that is generated in order to achieve the proper  $v_0^{LF}$  addition. Furthermore, the *total duty function*  $d_{tot,X}$  is defined as follows:

$$\begin{cases} d_{tot,A} = d_A + d_0 \\ d_{tot,B} = d_B + d_0 \\ d_{tot,C} = d_C + d_0 \end{cases}$$

(1.31)

# **CHAPTER 2: SIMULATIVE RESULTS**

### 2.1 Case study

The purpose of the thesis is to provide a comprehensive and systematic study about the project of the AC/DC stage of an ultrafast charger (UFC) for EV charging station applications. The project has been realized in association with "*Vishay Semiconductor Italia SPA*". The whole charger consists in a *two stages back-to-back converter*, in which, the grid interface is a 3-levels active rectifier (AFE, downstream of a LCL filter for EM compatibility) while the load interface is a HF DC/DC converter (resonant LLC converter). The two stages are connected through a voltage DC-link providing voltage continuity for the load and protection for the converter from voltage dips and swells.

The simulation results have been prepared with the use of a proper Power Electronic software (PLECS) and the post-processing analysis with the use of MATLAB.

In particular, the target of the thesis regards both the evaluation of the most adequate modulation technique to use in order to control the device and the experimental test in HIL (hardware in the loop) ambient to validate the simulation results.

Fig. 44: Model of the AC/DC stage and voltage DC-link.

The entire charger consists in a charging station of 360 kW, made up of 6 charging units each one of 60 kW. This shrewdness leads to several advantages:

- it permits to regulate the output power request by the load in the most efficient way (*power sharing strategy*);

- it has a *modular layout* (for example, in case of fault is sufficient to substitute a single unit instead of the whole converter);

- it guarantees a considerable flexibility in terms of switches and components to use within the converter (enabling to high current density purposes without too high level of voltage, so it is a *suitable solution also for LV application*).

A primal hypothesis to prepare an accurate model of the plant consist in assuming a *unitary power factor value*, that means, for a single unit of P = 60 kW

$$\cos\varphi \cong 1 \text{ and } S = \frac{P}{\cos\varphi} \cong 60 \text{ kVA thus} \begin{cases} V = V_n = 230 \text{ V} (LV \text{ application}) \\ I = \frac{2 \cdot S}{3 \cdot V} \cong 125 \text{ A} \cong 88 \text{ A}_{RMS} \end{cases}$$

(2.1)

This hypothesis is validated assuming that the AFE interface works correctly as an active rectifier, adjusting the output to maintain  $\cos\varphi = 1$  (a 0.5% of deviation is assumed as maximum). In addition, it is to note that the single module should carry 88 A<sub>RMS</sub> of current by the use a single-module layout (not-interleaved). The output current peak value per module (I<sub>peak</sub> = 125 A) results to be superior to the major low cost switches rated current. For this reason, the interleaved topology represents a valid technical expedient to halve the output current carried by each single module (with a striking reduction in terms of cost and losses). The output DC-link voltage  $V_{dc}$  has to be chosen carefully, considering:

- that the rectifier must be able to handle the peak input phase voltage (at least 325 V);

- the boost inductors stress increase with  $V_{dc}$ ;

- switching loss increases roughly with  $(V_{dc}^2)$ ;

- the DC-link capacitor volume increases with  $(V_{dc}^2)$ .

Consequently, the  $V_{dc}$  must be the lowest possible. As reported in literature [7], using the ZMPC modulation technique, the  $V_{dc}$  voltage can be evaluated through the following formula (2.2):

$$V_{dc,min} = \frac{\frac{2}{\sqrt{3}}}{1.1} \cdot \sqrt{3 \cdot \left(V_{peak,max}\right)^2 + 3 \cdot \left[\omega \cdot L \cdot \left(I_{peak,max}\right)\right]^2} \cong \frac{2}{1.1} \cdot V_{peak,max}$$

(2.2)

Yields to