# Politecnico di Torino

# DIPARTIMENTO DI ELETTRONICA E TELECOMUNICAZIONI Corso di Laurea Magistrale in Electronic Micro and Nanosystems

Tesi di Laurea Magistrale

# DMA Support for the Sancus Architecture

Relatore: Prof. Guido Masera

Correlatori: Prof. Jan Tobias Mühlberg Dr. Jo Van Bulck Dr. Pieter Maene Candidato: Sergio Seminara

# Abstract

Computing devices have a predominant role in our lives, changing most of our daily activities. With the advent of the IoT, more and more embedded devices are expected to be connected, with expected numbers around 20 billion of units for the 2020. Nevertheless, the increase in connectivity does not imply an enhancement of security. Programmable devices, especially connected ones, are at risk of being tampered with: recent history has shown many examples of malicious software attacks compromising their security. Considering that embedded device are required to be cheap in terms of resources they are implemented on low-end microcontrollers, which lack of any memory protection technique, making them unsuitable to implement solutions from the high-end world.

Hence, researchers have been recently focusing on strategies to provide them with security guarantees that hold even in case of an attacker with full control on the system, including the Operating System (OS). A promising solution is found in *Protected (software) Module Architectures* (PMAs): security architectures that can execute protected code in an isolated area of the memory, inaccessible to other software. PMAs can support secure execution of small portion of code, the software modules (SMs), even on devices that are, e.g., malware infected.

The target architecture of this thesis is Sancus, an open-source, hardware-only PMA, designed for lightweight embedded devices. The objective of the work is to extend the architecture with Direct Memory Access (DMA) support, a feature that provides peripherals with a secondary channel to access the memory without involving the CPU, and to explore what does it entail from a security prospective. Usually lightweight PMAs do not support DMA, as the benefits coming from its inclusion on the system do not comply with security properties of these architectures: protected memory isolation and confidentiality are no longer guaranteed if a secondary channel, that directly access the memory independently from the CPU, is provided. Main achievements of the thesis are to extend the Sancus 2.0 architecture with DMA support, showing how this affects its security properties and providing a secure way to implement DMA. From the discussion of the upcoming chapters, two solutions stood out: the first one is currently implemented on Sancus, and it consists in entirely excluding DMA from accessing protected memory, preserving SMs security guarantees. The second theoretical solution aims to provide the software modules with DMA functionalities, by allowing some security guarantees for a confined regions inside protected memory. The latter solution is discussed in details and some design options are provided, whereas its implementation is deferred as future work.

# Sammanfattning

Datorer har en dominerande roll i våra liv och förändrar de flesta av våra dagliga aktiviteter. Med tillkomsten av IoT förväntas fler och fler inbyggda enheter anslutas, med förväntat antal cirka 20 miljarder enheter för 2020. Ändå innebär ökningen av anslutning inte en ökning av säkerheten. Programmerbara enheter, särskilt anslutna, riskerar att bli manipulerade med: den senaste historiken har visat många exempel på skadliga programattacker som äventyrar deras säkerhet. Med tanke på att inbäddad enhet krävs för att vara billig när det gäller resurser, de implementeras på low-end mikrokontroller, vilket saknar någon virtualisering av minnesstöd, detta gör dem olämpliga att genomföra lösningar från high-endvärlden.

Därför har forskare nyligen fokuserat på strategier för att ge dem säkerhetsgarantier som håller fast vid en angripare med full kontroll på systemet, inklusive operativsystemet (OS). En lovande lösning finns i *Protected (Software) Module Architectures* (PMA): säkerhetsarkitekturer som kan utföra skyddad kod i ett isolerat område i minnet, otillgängligt för annan programvara. PMA kan stödja säker utförande av liten del av kod, mjukvarumoduler (SM), även på enheter som är t ex skadlig programvara.

Målarkitekturen för den här avhandlingen är Sancus, en öppen källkod, maskinvara endast PMA, avsedd för lätt inbyggda enheter. Syftet med arbetet är att utöka arkitekturen med DMA-stöd (Direct Memory Access), en funktion som ger kringutrustning till en sekundär kanal för att komma åt minnet utan att involvera CPU, och att undersöka vad det medför från en säkerhetsperspektiv. Vanligtvis är lätta PMA: er inte stöd för DMA, eftersom fördelarna som följer av att den ingår i systemet inte överensstämmer med säkerhetsegenskaperna hos dessa arkitekturer: skyddad minnesisolering och konfidentialitet garanteras inte längre om en sekundär kanal, som direkt åtkomst till minnet oberoende av CPU, tillhandahålls. Huvuddragen i avhandlingen är att utöka Sancus 2.0-arkitekturen med DMA-support, vilket visar hur det påverkar sina säkerhetsegenskaper och ger ett säkert sätt att implementera DMA. Från diskussionen av de kommande kapitlen stod två lösningar: den första är för närvarande implementerad på Sancus och består helt och hållet av att DMA inte ska få tillgång till skyddat minne och bevarar säkerhetsgarantier från SM. Den andra teoretiska lösningen syftar till att tillhandahålla mjukvarumoduler med DMA-funktioner, genom att tillåta vissa säkerhetsgarantier för en begränsad region inom skyddat minne. Den senare lösningen diskuteras i detalj och vissa designalternativ ges, medan dess genomförande skjuts upp som framtida arbete.

# Contents

| Co | onten                     | ts                                    | i                                                                                  |

|----|---------------------------|---------------------------------------|------------------------------------------------------------------------------------|

| Li | st of                     | Figures                               | $\mathbf{v}$                                                                       |

| Li | st of                     | Tables                                | ix                                                                                 |

| Li | st of                     | Abbreviations                         | xi                                                                                 |

| 1  | <b>Intr</b><br>1.1<br>1.2 | oduction<br>History                   | <b>1</b><br>1<br>3                                                                 |

| 2  | Bacl<br>2.1<br>2.2<br>2.3 | 2.3.1       Overview                  | 7<br>8<br>9<br>10<br>10<br>12<br>16<br>17<br>17<br>17                              |

| 9  | 2.4                       | Direct Memory Access (DMA)            | <ol> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>22</li> <li>24</li> </ol> |

| 3  | <b>Pro</b><br>3.1<br>3.2  | DMA on Protected Module Architectures | 27<br>27<br>28                                                                     |

|          |                        | $3.2.1 \\ 3.2.2$        | Leak Secret Data    Inject Malicious Data or Code           |                 |

|----------|------------------------|-------------------------|-------------------------------------------------------------|-----------------|

|          | _                      |                         | •                                                           |                 |

| 4        |                        | -                       | d Discussion                                                | 35              |

|          | 4.1                    |                         | ty Objectives                                               | 35              |

|          | 4.2                    |                         | ker Model                                                   | 36              |

|          | 4.3                    |                         | iew                                                         | 38              |

|          | 4.4                    |                         | t of the DMA on Sancus Security Properties                  | 39              |

|          | 4.5                    | Protec                  | ction of System Memory from DMA Attacks                     | 41              |

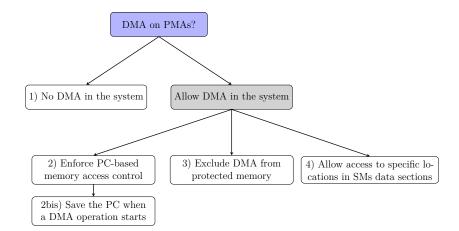

|          |                        | 4.5.1                   | No DMA in the System                                        | 42              |

|          |                        | 4.5.2                   | Enforce MAL on DMA Accesses                                 | 42              |

|          |                        | 4.5.3                   | Exclude DMA from Protected Memory                           | 44              |

|          |                        | 4.5.4                   | Allow Access to Specific Locations inside SMs Data Sections | 45              |

|          |                        |                         | 4.5.4.1 Reduce the Register Overhead                        | 48              |

|          | 4.6                    |                         | ary of Memory Access Rights                                 | 50              |

|          | 4.7                    | Open                    | Problems                                                    | 50              |

| ٣        |                        | Γ <b>Λ</b> . <b>Τ Λ</b> |                                                             | ۳۹              |

| <b>5</b> |                        |                         | erface Implementation                                       | <b>53</b><br>53 |

|          | 5.1                    | 5.1.1                   | ed DMA Interface for Sancus on OpenMSP430                   | ээ<br>55        |

|          |                        | -                       | Frontend Modification                                       | 55<br>56        |

|          |                        | 5.1.2<br>5.1.2          |                                                             |                 |

|          |                        | 5.1.3                   | Execution Unit Modification                                 | 57              |

| 6        | $\mathbf{D}\mathbf{M}$ | [A Cor                  | ntroller Implementation                                     | <b>59</b>       |

|          | 6.1                    | Overv                   | iew of the DMA Controller                                   | 59              |

|          | 6.2                    | Mode                    | of Operation of the DMA Controller                          | 61              |

|          | 6.3                    | Implei                  | mentation of the DMA Controller                             | 61              |

|          |                        | 6.3.1                   | DMA Protocol - Read Operation                               | 62              |

|          |                        | 6.3.2                   | DMA Protocol - Write Operation                              | 63              |

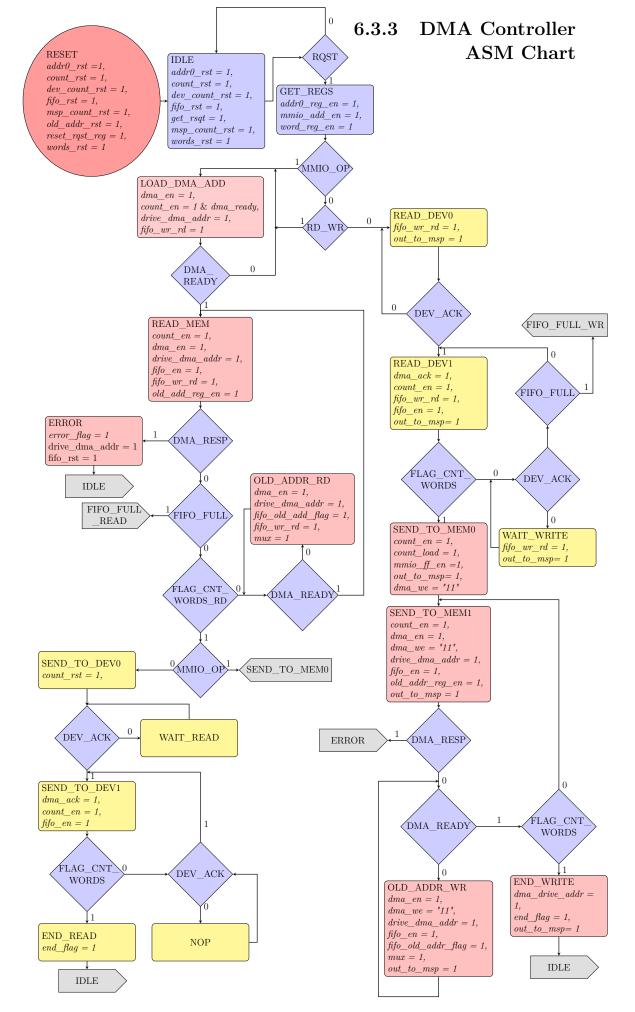

|          |                        | 6.3.3                   | DMA Controller ASM Chart                                    | 65              |

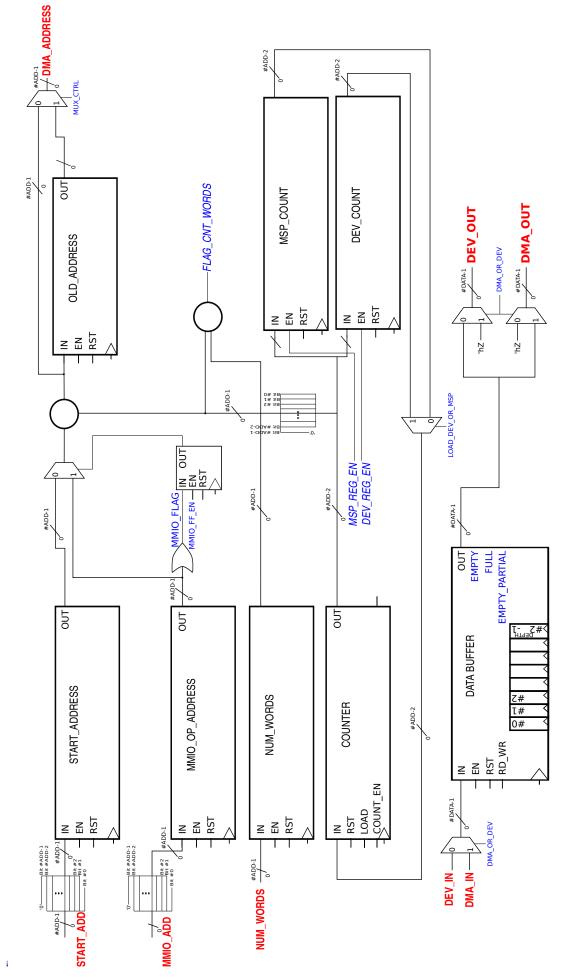

|          |                        | 6.3.4                   | DMA Controller Data Path                                    | 67              |

|          |                        |                         | 6.3.4.1 Internal Registers                                  | 67              |

|          |                        |                         | 6.3.4.2 Data Buffer                                         | 70              |

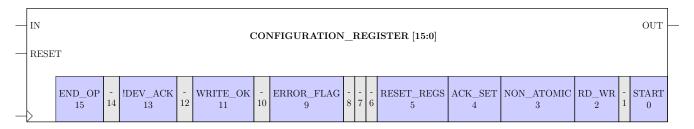

|          | 6.4                    | DMA                     | Controller Driver                                           | 71              |

|          | 6.5                    | Device                  | e with DMA Capabilities                                     | 73              |

|          |                        | 6.5.1                   | Overview of DMA Read and Write Operations                   | 74              |

|          | 6.6                    | DMA                     | Tesbenches                                                  | 75              |

|          |                        | 6.6.1                   | DMA Controller Read Branch                                  | 75              |

|          |                        |                         | 6.6.1.1 Read from System Memory                             | 75              |

|          |                        |                         | 6.6.1.2 Write to a DMA Device                               | 77              |

|          |                        | 6.6.2                   | DMA Controller Write Branch                                 | 79              |

|          |                        |                         |                                                             |                 |

|              |       |                         | 6.6.2.1    | Read from a DMA Device                            | 79              |

|--------------|-------|-------------------------|------------|---------------------------------------------------|-----------------|

|              |       |                         | 6.6.2.2    | Write into System Memory                          | 81              |

|              |       | 6.6.3                   | Emptyin    | g the Controller Data Buffer                      | 81              |

|              |       |                         | 6.6.3.1    | Emptying the Buffer - Output to External Device . | 83              |

|              |       |                         | 6.6.3.2    | Emptying the Buffer - Output to System Memory .   | 83              |

|              | 6.7   | Attack                  | Scenario   | on DMA-Secure Sancus Implementation               | 84              |

| Co           |       | <b>sions</b><br>re Worl | k          |                                                   | <b>89</b><br>90 |

| Bi           | bliog | raphy                   |            |                                                   | 93              |

| $\mathbf{A}$ | Sou   | rce Co                  | de and I   | nstallation                                       | 99              |

|              | A.1   | Latest                  | Version I  | nformation                                        | 99              |

|              | A.2   | Installa                | ation Inst | ructions                                          | 100             |

# List of Figures

| 2.1 | Representation of a Sancus node with a software module $SM_1$ loaded.                                                                  | 13 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Overview of the hardware block constituting a Sancus core. Lightly shaded blocks are part of the original openMSP core, whereas darker |    |

|     | shaded ones were specifically added for Sancus                                                                                         | 18 |

| 2.3 | Schematic of the Memory Access Logic (MAL), the hardware used                                                                          |    |

|     | to enforce the memory access rules for each protected module $[39].$ .                                                                 | 18 |

| 2.4 | Overview of the openMSP430 core internals, with DMA support                                                                            |    |

|     | [18]. Memory can be accessed both through the normal system bus,                                                                       |    |

|     | along with DMA interface                                                                                                               | 22 |

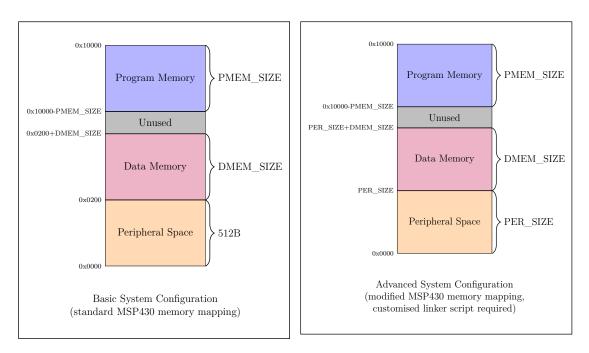

| 2.5 | Organisation of the memory in the openMSP430 core [18]. Mem-                                                                           |    |

|     | ory is seen as a single memory block, with program memory, data                                                                        |    |

|     | memory and peripheral space arranged sequentially                                                                                      | 23 |

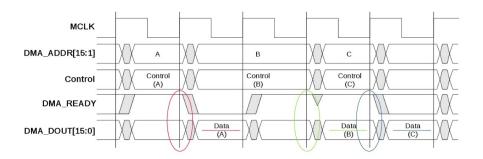

| 2.6 | Timing diagram of a read operation with wait state on the open-                                                                        |    |

|     | MSP430 DMA interface                                                                                                                   | 25 |

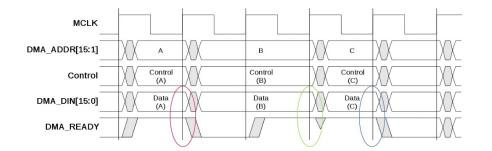

| 2.7 | Timing diagram of a write operation with wait state on the open-                                                                       |    |

|     | MSP430 DMA interface                                                                                                                   | 25 |

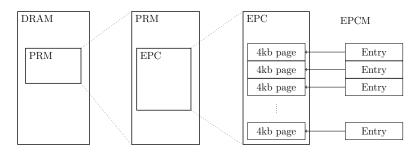

| 3.1 | Detail of Processor Reserved Memory (PRM), together with Enclave                                                                       |    |

| 0.1 | Page Cache (EPC) in Intel SGX. The PRM is a contiguous range of                                                                        |    |

|     | DRAM that cannot be accessed by system software or peripherals [13].                                                                   | 28 |

|     | DIAM that cannot be accessed by system software of peripherals [15].                                                                   | 20 |

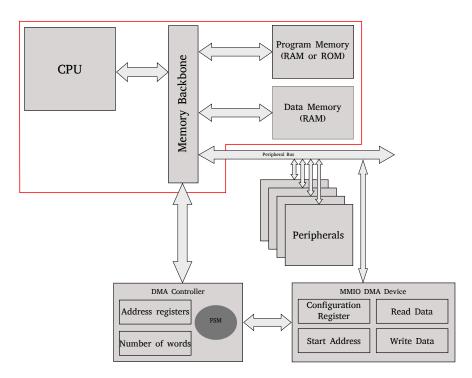

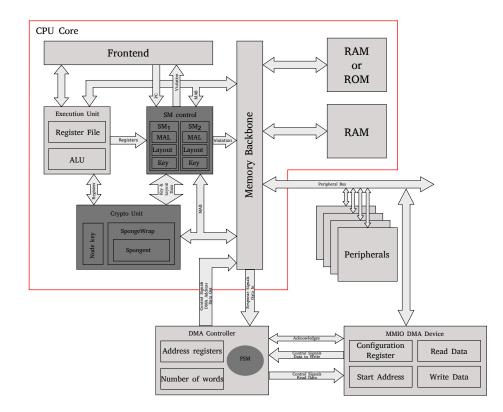

| 4.1 | Overview of the system architecture, showing the DMA controller                                                                        |    |

|     | and a peripheral with DMA capabilities, connected to it. Every-                                                                        |    |

|     | thing related to the DMA or peripherals is outside the TCB                                                                             | 37 |

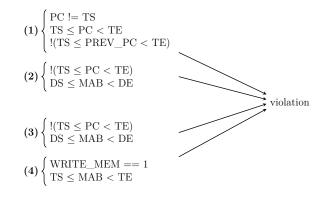

| 4.2 | Representation of the Memory Access Logic (MAL), enforcing pro-                                                                        |    |

|     | gram counter-based access control rule                                                                                                 | 38 |

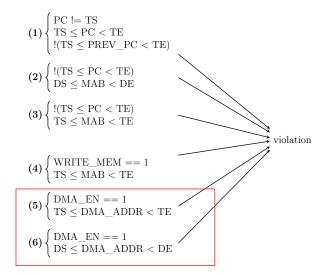

| 4.3 | A recapitulatory tree diagram of the explored ideas to include DMA                                                                     |    |

|     | on PMAs. Among these, only the last leaves, numbers 3 and 4,                                                                           |    |

|     | propose an actual solution to the problem                                                                                              | 42 |

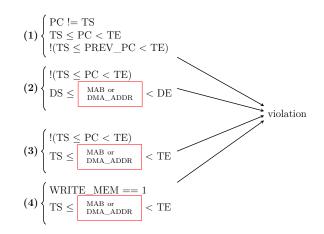

| 4.4 | Modifications of the Memory Access Logic (MAL) to enforce PC-                                                                          |    |

|     | based access control on the DMA address.                                                                                               | 43 |

| 4.5 | Representation of Memory Access Logic (MAL) that prevents any DMA access to protected memory.                                                                                                                                                                        | 44       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.6 | Representation of the Memory Access Logic (MAL) that allows<br>DMA access to specific protected memory locations. DMA_PS and<br>DMA_PE are the DMA Protected Start and DMA Protected End<br>addresses.                                                               | 46       |

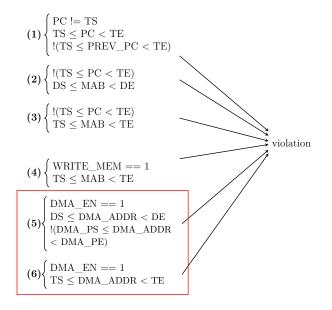

| 4.7 | Representation of a node with a software module loaded, in the new framework of allowing DMA access to specific locations inside the data section.                                                                                                                   | 47       |

| 5.1 | Detailed overview of the system architecture, showing the DMA controller and a peripheral with DMA capabilities, connected to it. Constituent blocks of the core are here shown. Everything related to the DMA or peripherals is outside the TCB.                    | 54       |

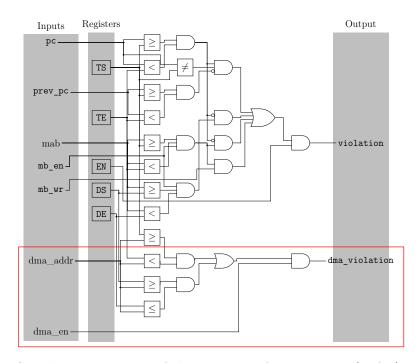

| 5.2 | Single instantiation of the Memory Access Logic (MAL) circuit, used<br>to enforce the memory access rules in the nodes. The highlighted<br>box shows the hardware that realises the protection mechanism of<br>that prevents DMA to access to SMs protected sections | 56       |

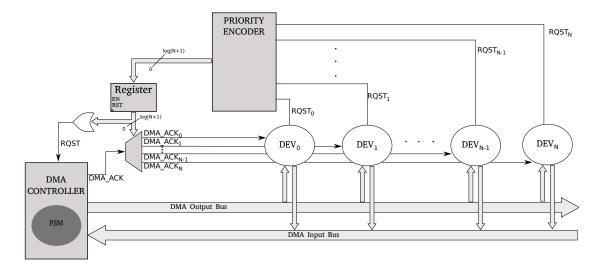

| 6.1 | Overview of the arbitration circuitry that solves multiple DMA re-                                                                                                                                                                                                   |          |

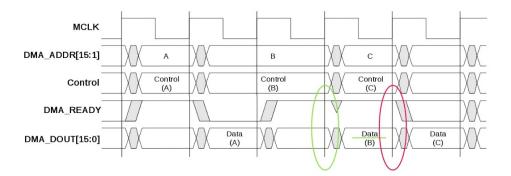

| 6.2 | quests from the peripherals                                                                                                                                                                                                                                          | 60<br>63 |

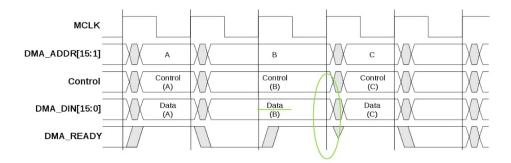

| 6.3 | Timing diagram of a write operation when interfacing with the DMA interface in use on the openMSP430 (details on the proto-<br>col at subsubsection 2.4.2.2)                                                                                                         | 64       |

| 6.4 | DMA controller FSM. Yellow blocks refer to the interface between<br>the DMA controller and the openMSP430, whereas pink ones to the<br>interface between DMA controller and device.                                                                                  | 65       |

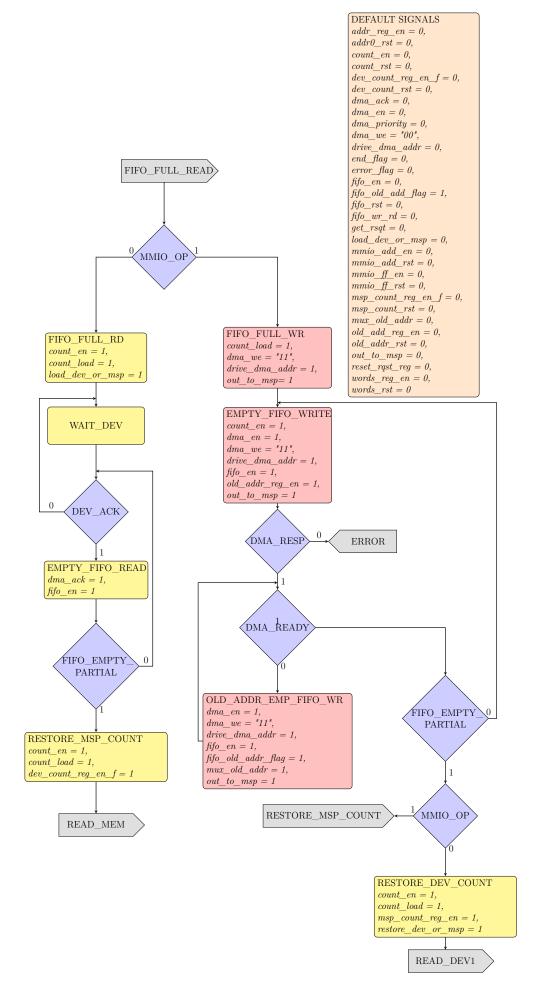

| 6.5 | ASM chart of the DMA FSM: detail of FIFO_FULL branches, and view of default values for the signals of the FSM.                                                                                                                                                       | 66       |

| 6.6 | DMA controller data path: an overview of the controller fundamen-<br>tal components as well as of the signals ruling its FSM behaviour is<br>here provided.                                                                                                          | 69       |

| 6.7 | openMSP430 - DMA protocol: violation when synchronous registers                                                                                                                                                                                                      |          |

| 6.8 | are used, at markers C and D                                                                                                                                                                                                                                         | 70       |

| 6.9 | isters are used                                                                                                                                                                                                                                                      | 71<br>74 |

| 76       |

|----------|

| 76<br>78 |

| 10       |

|          |

|          |

|          |

| 78       |

|          |

|          |

|          |

| 79       |

|          |

|          |

|          |

|          |

|          |

| 80       |

| 80       |

|          |

| 82       |

|          |

| 82       |

|          |

| 84       |

|          |

# List of Tables

| 2.1 | Access control rules to the memory in PC based memory access        |    |

|-----|---------------------------------------------------------------------|----|

|     | control. Access rights are shown in a Unix notation, indicating how |    |

|     | code executing in the 'from' may access the 'to' section [39]       | 9  |

| 2.2 | Overview of the keys used in Sancus, how they are created, stored,  |    |

|     | and who can access them $[39]$                                      | 11 |

| 2.3 | List of all the signals compoding the DMA interface.                | 23 |

| 4.9 | Mamony access rights in program counter based memory access con     |    |

| 4.2 | Memory access rights in program counter-based memory access con-    | ٣1 |

|     | trol on Sancus. Access rights are shown for CPU memory accesses .   | 51 |

| 4.3 | Memory access rights in program-counter based memory access con-    |    |

|     | trol. Access rights are also shown for DMA accesses, for all the    |    |

|     | -                                                                   |    |

|     | proposed solutions from section 4.5.                                | 51 |

# List of Abbreviations

| $\mathbf{ALU}$ | Arithmetic Logic Unit           |

|----------------|---------------------------------|

| $\mathbf{ASM}$ | Algorithmic State Machine       |

| $\mathbf{CPU}$ | Central Processing Unit         |

| $\mathbf{CU}$  | Control Unit                    |

| $\mathbf{DE}$  | Data section End                |

| DMA            | Direct Memory Access            |

| DMA_PE         | DMA Protected End address       |

| $DMA_PS$       | DMA Protected Start address     |

| DMAC           | Direct Memory Access Controller |

| $\mathbf{DS}$  | Data section Start              |

| $\mathbf{ELF}$ | Executable and Linkable Format  |

| FIFO           | First In First Out              |

| $\mathbf{FSM}$ | Finite State Machine            |

| IoT            | Internet of Things              |

| IP             | Infrastructure Provider         |

| $\mathbf{IRQ}$ | Interrupt Request               |

| $\mathbf{ISR}$ | Interrupt Service Routine       |

| MAB            | Memory Access Bus               |

| MAC            | Memory Authentication Code      |

| MAL            | Memory Authentication Logic     |

| MMIO           | Memory-Mapped Input/Output      |

| $\mathbf{MMU}$ | Memory Management Unit          |

| $\mathbf{PMA}$ | Protected Module Architecture   |

| $\mathbf{PSA}$ | Protected Storage Area          |

| $\mathbf{SM}$  | Software Module                 |

| $\mathbf{SP}$  | Software Provider               |

| TCB            | Trusted Computing Base          |

| $\mathbf{TE}$  | Text section End                |

| $\mathbf{TS}$  | Text section Start              |

|                |                                 |

# Chapter 1 Introduction

# 1.1 History

Nowadays, computing devices have a predominant role in our lives, unveiling us new services that irreversibly changed most of our daily activities. All of this is possible since we rely on the providers of those services to securely process our data on our devices. However programmable devices are at risk of being tampered with, especially connected ones: recent history has shown that these devices are subject to malware infections and, in general, software attacks that compromise integrity and data confidentiality: in one word, the devices security [15]. Relevant experience has been gained for securing established high-end systems, such as desktops and servers, which have been on the market for a long time. In order to protect them from malicious exploits, some solutions arose, trying to fix the flaws as they are exploited by attackers.

With the advent of IoT future isn't brighter. Promoted by the enhancement of the technology, more and more embedded devices are expected to be connected, wit expected numbers around 20 billion of units for the 2020 [2, 3, 16]. Nevertheless, the increase in connectivity and the impact of devices on our society do not entail an enhancement of security. Critical software vulnerabilities have been disconed in home appliances [31], cars [38] and even industrial sites [47], each implying different level of threats: an hacked fridge could leak some personal data, at worst, but when it comes to cars, industries or medical devices, the threat becomes far more worrying [30].

Therefore, on the past years, researchers have tried to answer the open question of how to secure networked programmable devices, and to allow a stakeholder to assess the trustworthiness of a computing device. Important solutions are virtualization of the memory in combination with processor privilege levels, and the implementation of a memory-safe virtual machine. Both relying on a secured software layer, either the operating system (OS) or the virtual machine implementation, the two solutions provide isolation of the software running on the processor. The first technique takes advantages of hardware support, generally a Memory Management Unit (MMU), to provide an abstraction of the storage resource so that the main memory appears to be larger than it really is. The operating system, which also relies on protection rings, assigns separate memory space to running processes and guards the interaction among them. The second technique involves the uses of a memory-safe virtual machine, where software is deployed in memory-safe bytecodes and a security architecture, usually an hypervisor, guards the interaction of different software modules [45]. However, with classical solutions it is non-trivial to provide an attestation mechanism, which a remote stakeholder can rely on to check that a specific software module is running untampered with on a remote device. Finally, while software-based solutions have the advantage of compatibility, they also negatively impact on performances and, most important, they cannot protect from system-level attacks: once the relying software layer - OS or hypervisor - has been compromised [49], security of the system can no longer be guaranteed: a malicious operating system can, in fact, allow manipulation of the software, breaking the root of trust. To ensure resilience even in these cases, hardware-based solutions have to be used.

Embedded device are required to be cheap in terms of resources such as chip area, chip complexity, power consumption and performance, thus they are implemented on low-end, resource-constrained microcontrollers. This makes them unsuitable to implement established solutions from high-end devices world, which require a more complex, thus expensive, architecture to be integrated.

A promising solution is found in *Protected (software) Module Architectures* (PMAs): security architectures running independently from a classic operating system, that can execute code in an isolated area of the memory. The isolation is not built on the operating system, thus improving the security [45]. The idea of PMAs originally arose from the need to split complex software into smaller *protected modules*, isolated between them, whose correctness would have been easier to verify [34]. The use of PMAs also provides a secure way to support *remote attestation* where classical solutions could not. Remote attestation is the capability of a stakeholder to remotely check that a specific software module is running untampered with on a remote device. In general, a device is said to be *trusted* if it behaves as expected even when tampered with at the software level [33], i.e. even when an attacker gains control on the operating system [30].

Currently different PMAs are available, each coming with a different cost in terms of hardware onhead and performance. Some provide isolation of application on high-end devices, for example the Intel SGX [13] which extends x86 architectures and whose cost is not considered lightweight at all. Others leverage Memory Encryption Engines to encrypt/decrypt sensitive code and data when leaving/entering the main memory, like for example Atlas [29], or make use of lightweigth Memory Protection Units to enforce an execution-aware memory access control, as done in TrustLite [26]. Finally, architecture like SMART [14] aim to provide only some security guarantees with the minimal set of hardware changes. Programcounter based memory is a memory protection technique whose aim is to provide isolation between software modules running on the same node, but that do not necessarily trust each other [45]. PC based memory access proposes memory access control based on the current value of the program counter, resulting in being a low-cost alternative to the virtualization of the memory or the use of a memorysafe virtual machine.

# **1.2** Problem Statement and Goal of the Thesis

The combination of PMAs and hardware implementations of the program-counter based memory access control is one way to extend protected module idea to the low-end microcontroller world, achieving hardware-based trusted computing. An architecture of this kind enhances security guarantees of the system by having the root of trust buried in the hardware, which is considered to be immutable from attackers [30]. For this reasons it is preferable to develop on hardware-based architectures rather than software-based, although some software-based architectures with interesting results have been proposed [4, 24, 32, 43, 46].

The target architecture of this thesis is Sancus<sup>1</sup>, an open-source,<sup>2</sup> hardwareonly PMA designed for lightweight embedded devices. By leveraging an hardware implementation of the PC based memory access control, Sancus guarantees the secure execution of protected applications. The root of trust is, thus, buried into hardware, enhancing the security guarantees of the architecture. It allows external peripherals connection but it natively does not support Direct Memory Access.

Direct Memory Access (DMA) is a feature of CPUs that allows hardware subsystems to directly access the memory, without the participation of the Control Unit (CU). First proofs of DMA integration on computing systems date back to

<sup>&</sup>lt;sup>1</sup>Designed in 2013 by Noorman et al., Sancus is an ongoing project of imec-DistriNet and COSIC research groups of KU Leuven, that reached its second version.

Sancus 2.0 guarantees a set of security properties, such as software isolation as well as with local and remote attestation. Moreon, it supports secure linking and secure communication . For more details you can visit https://distrinet.cs.kuleuven.be/software/sancus/index.php

<sup>&</sup>lt;sup>2</sup>More details about Sancus source code are provided in section A.1

the Intel 8085 (1976) Intel 8 bit microprocessor, or the IBM Personal Computer (1981), both provided with the DMA Controller (DMAC) chip known as Intel 8237 [22]. By means of DMA, devices can transparently access the main memory unburdening the CPU from I/O loads. This latter is then free to handle other operations, while the data transfer is happening. In this sense, DMA speeds up the system.

Generally PMAs do not support DMA. The reason is that an attacker with DMA capabilities can tamper with any location of the system memory at runtime, as DMA bypasses any MMU-like control. Program-counter based memory access control is, in fact, enforced on the memory access bus (MAB) alone, i.e. on every access to the memory going through the CPU. What if the untrusted element resides outside CPU domain? What if there was a way to directly access the memory, bypassing any CPU control, so that no violation is raised on illegal accesses? Hence, a protection mechanism has to be provided if DMA is going to be implemented on a PMA, in order to prevent disastrous outcomes.

Some attacks have successfully shown that it is possible to exploit DMA capabilities of ad-hoc compromised devices [44, 11, 41, 12, 37, 6] to tamper with the host system, as reported in [42].

The goal of this thesis is, first, to extend Sancus 2.0 architecture with DMA capabilities, then, to show that such a functionality breaches security guarantees of the system. Lastly some ideas to secure Sancus SMs from DMA attacks have been explored; the aim it to extend the same memory hierarchy that rules the internal memory accesses to DMA peripherals, and to keep the hardware onhead as small as possible. Section 3.2, "Exploitation of Naive DMA Support", guides the reader through a simple attack targetting the Sancus architecture. It leverages the disruptive capabilities of a naive DMA implementation, in which no memory access control is enforced on the DMA bus, to leak secret data from a Sancus software module and to inject malicious content in the data section. section 6.7 reports the outcomes of a similar attack when carried on two different Sancus implementations: one equipped with a direct implementation of the DMA interface, and the other supporting secure DMA. The provided results underline the importance of providing a secure DMA channel on Protected Modules Architectures. Hence, the main contributions of the thesis can be summarised in:

- 1. Show that the inclusion of DMA support on Sancus 2.0 breaks isolation and confidentiality guarantees for the architecture (section 4.4), and underline the need to validate DMA accesses independently from the PC (subsection 4.5.2).

- 2. Implement a simple solution to preserve Sancus security guarantees, by preventing DMA to access any protected memory location (subsection 4.5.3).

## 1.2. PROBLEM STATEMENT AND GOAL OF THE THESIS

3. Propose a further conceptual solution to extend software modules capabilities with DMA functionalities, at the expense of relaxing isolation and confidentiality guarantees for a confined region inside modules protected memory (subsection 4.5.4).

CHAPTER 1. INTRODUCTION

# Chapter 2 Background

Computing devices play a predominant role in our lives and daily activities. Basing on the enormous number of data available, they can provide us with an entire new level of personalised services. With the advent of Internet of Things (IoT) the phenomenon is only going to increase, with embedded devices becoming omnipresent and interconnected, handling safety-critical and privacy-sensitive data. Yet, the increase in connectivity does not entail an enhancement of the security these devices guarantees. To minimize production costs and power consumption they are usually implemented on lightweight architectures, which lack of hardware support for classical solutions from high-end devices world, such as the virtualization of the memory, in conjunction with processor privilege levels, or the use of a virtual machine to run critical code in a safe environment.

The increasing trend of connecting computing devices opened to malware infections and, in general, software attacks that compromise systems security [15]. Computer security is a growing field of the broader information security, that aims to protect computing systems and the data that they store or access to. During last decades, a rich body of experience has been acquired in securing high-end computing devices, such as desktops and servers, through the classical solutions aforementioned. Unfortunately, these solutions do not comply with the resourceconstrained, low-end devices world, characterised by a very simple memory hierarchy in which the use of Memory Management Units (MMUs) is not contemplated.

A recent line of research focused on Protected Module Architectures (PMAs) as alternative to tackle the problem of security by means of a fine-grained memory access control. PMAs can give user security guarantees about the behaviour of software running on them, achieving the main goal of *trusted computing*, which is to protect applications and users from malicious exploitation. When a system keeps behaving as expected even when tampered with, i.e. even when an attacker gains control on it, it is said to be *trusted* [30]. An important part of trusted computing is to provide security guarantees even in case the OS is tampered with. Unfortunately, software-based solutions are inadequate in achieving this goal, as an attacker can always manipulate software if the OS is not trusted. In order to provide strong guarantees even in this eventuality, hardware-only based architectures have to be considered. For these systems the root of trust is said to be buried in the hardware and is more resilient to malicious attacks than software solutions, to the extent that hardware is considered to be immutable.

Finally, the minimization of the Trusting Computing Base (TCB) has been a paramount goal of computer security, since the start of the field, and many hardwareonly PMAs manage to provide security guarantees with a small TCB.

The TCB is defined as "the set of the hardware and software components which are considered critical for the security of the whole system. The TCB is designed so that, even in case of tampering with other parts of the system, the device cannot misbehave" [30].

A more detailed explanation of the PMAs together with the protection techniques used to provide modules isolation is outlined in the following section 2.1.

# 2.1 Protected Module Architectures

Protected architectures run independently of the Operating System (OS) and allow the secure and isolated execution of software modules [30]. The idea of PMAs originally addressed the need to split complex software into smaller protected modules, isolated between them, whose correctness would have been easier to verify [34]. Several prototypes have been developed both for embedded systems – such as Sancus [39], TrustLite [26], TyTAN [8] or Soteria [21] – as well as for high-end systems – such as Intel Software Guards eXtensions (SGX) [35] or Iso-X [17] – ensuring modules isolation.

A countermeasure to software complexity is to use a divide-and-conquer approach, where big bunches of code are divided in smaller, and more maintainable, software modules (SMs). A SM essentially consists of two separated text and data sections. The former contains the module protected code and can be entered only via few predefined addresses of memory locations, called entry points. Each software module should maintain its own private call stack, for example by saving it in its private data section. The latter contains private data of the module and can be accessed (read or written) only when the program counter is pointing within the code section of the corresponding module. The access rules are enforced by the PMA on which the SM is running.

By combining the PMAs idea with the program-counter based memory access control it is possible to extend memory protection mechanism to low-end embedded devices.

#### 2.2. PROGRAM-COUNTER BASED MEMORY ACCESS CONTROL

| from $\setminus$ to | Protected   |      |      | Unprotected |

|---------------------|-------------|------|------|-------------|

|                     | Entry point | Code | Data |             |

| Protected           | r x         | r x  | r w  | r w x       |

| Unprotected         | x           |      |      | r w x       |

Table 2.1: Access control rules to the memory in PC based memory access control. Access rights are shown in a Unix notation, indicating how code executing in the 'from' may access the 'to' section [39].

# 2.2 Program-Counter Based Memory Access Control

Program-counter based memory access control is a memory protection technique based on the current value of the program counter: depending on where the code is being executed, different access rights to the memory are enforced. Code executing from unprotected memory regions has no access rights to protected memory, except for execution rights on the entry point of a software module. Accesses from protected to unprotected memory are granted with full access permissions. Notice that only code executing from within a software module can access to its text and data sections. In this way, module isolation is guaranteed, as only SMs have direct access to their own text and data sections. When more than one software module are loaded on the same PMA, the rules for accessing its private sections treat all other modules as unprotected memory regions [45]. Table 2.1 shows the access rights enforced for code executing in protected and unprotected memory locations.

Notice that PC based memory access control is sufficiently strong to preserve all the isolation guarantees that modern programming languages can provide, such as information hiding and encapsulation - which is basically what is ensured when declaring a private variable in high level programming languages, as C++ or Java, for example. However, all these guarantees are typically lost when the program is compiled, as an attacker operating at machine code level can always break isolation and confidentiality of the compiled code by directly tampering with it in the system memory. Interestingly, it has been shown [1, 40] that source code securely compiled to a PMA maintains the source code level abstractions even against machine code level attacks. For hardware-only PMAs these guarantees even hold in case of a compromised OS.

# 2.3 Sancus 2.0

## 2.3.1 Overview

Program-counter based memory access can be implemented in different ways; the target architecture of this thesis is Sancus, a hardware-level implementation that provides strong isolation, remote attestation, as well as a series of security properties as secure communication, secure linking, confidential software deployment and hardware breach confinement.

**System model** The architecture addresses the problem of securing an infrastructure made up of a set of interconnected low-end microprocessor-based systems, which are referred as nodes  $N_i$ . The infrastructure provider IP, owner of the network, allows some software providers, with public IDs  $SP_i$ , the access to the nodes, giving them the possibility to deploy software module SM onto them. The TCB on the networked devices is hardware-only, specifically each node does not trust any software, including the operating system running on it.

Attacker model The attacker is consider to have two critical capabilities. First it can manipulate all the software on the node, including tamper with the OS, and it can act as a software provider by deploying malicious software modules on the nodes. Second, it can control the communication network used by the software provider and the nodes to communicate with each other; attacker can sniff the network, modify traffic and mount man-in-the-middle attacks.

However, it cannot break cryptographic primitives and does not have physical access to the hardware: it cannot modify it, nor connect probes, nor disconnect components, and so forth.

**Cryptographic primitives and node keys** The architecture design relies on three cryptographic primitives:

- a classical cryptographic hash function to compute digest of data [36];

- a key derivation function [36], used to derive a key from a master key ans some diversification data:

$K_{Master,Data} = kdf(K_{Master},Data)$

• a pair of authenticated encryption and authenticated decryption with associated data. The encryption function takes as input a key K, a plaintext P and associated data D, and produces in output a ciphertext C of the plaintext,

| Key           | Creation           | Accessible by   | $Saved^1$    |

|---------------|--------------------|-----------------|--------------|

| $K_N$         | Random             | IP, N           | $\checkmark$ |

| $K_{N,SP}$    | $kdf(K_N, SP)$     | SP              |              |

| $K_{N,SP,SM}$ | $kdf(K_{N,SP},SM)$ | SM (indirectly) |              |

Table 2.2: Overview of the keys used in Sancus, how they are created, stored, and who can access them [39].

plus a Message Authentication Code (MAC) T on both the plaintext and the associated data [36].

$$C, T = \texttt{aead-encrypt}(K, P, A)$$

$$P = \texttt{aead-decrypt}(K, C, A, T)$$

(2.1)

The cryptographic keys are handled by the many parties of the network: the IP shares a symmetric key with each of its nodes, the node master key  $K_N$ . This is saved in an internal register of the CPU, accessible only indirectly through specific processor instructions. The software providers allowed to deploy modules on a specific node are provided with the intended software provider key  $K_{N,SP}$ , computed by the IP with through the key derivation function  $kdf(K_N, SP)$ . Notice that Sancus nodes host an hardware implementation of the kdf, hence they can compute  $K_{N,SP}$  by themself. The key derivation function used in the current Sancus implementation is the SpongeWrap. Finally, nodes can compute the symmetric key  $K_{N,SP,SM}$  relative to the software module SM. The key is stored in a protected area of the processor, inaccessible from the software. Consider that software providers can compute keys relative to their own modules, as it received the  $K_{N,SP}$  from the IP, and it knows the identities of the modules it is loading on N.

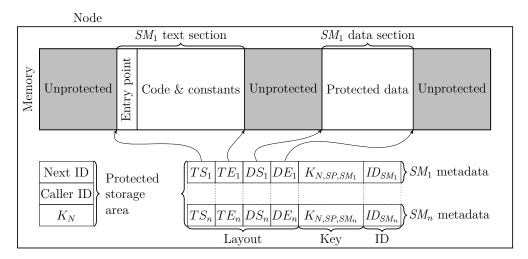

**Software modules** Software modules,  $SM_i$  are binary files composed of a text section and a data section. The former contains code and constants of the software module and can only be accessed by jumping to one of its fixed entry points; the content of text section is enforced to be read only, after memory protection is enabled. The latter contains runtime data of a module, such as the call stack which is included in the data section to avoid leaks. The Sancus architecture comes with a specific compiler that automatically handles the inclusion of every runtime metadata in the data section.

When a software module SM is loaded in the main memory, the processor saves the *layout* of the module in a protected storage area inside the CPU: the Protected

<sup>&</sup>lt;sup>1</sup>Saved in the Protected Storage Area of the node CPU.

Storage Area (PSA). The layout consists of the start and end addresses of both text and data sections. The *identity* of the module is obtained, by computing the hash of the layout and the content of the text section of a module, and it's stored in the PSA.

Finally, the symmetric module key  $K_{N,SP,SM} = kdf(K_{N,SP}, SM)$  is computed and stored in the protected area, to be used with cryptographic functions as assurance of module integrity. In this regard, notice that the software provider SP can also compute  $K_{N,SP,SM}$ , since it received  $K_{N,SP}$  from IP and knows the identity of the deployed module SM. Therefore  $K_{N,SP,SM}$  is to encrypt data before sending it on the untrusted communication network, and decrypt them once received, securing the communication. Data decryption only works if both the players computes the same key  $K_{N,SP,SM} = kdf(K_{N,SP}, SM)$ : in other words, the mechanism works as long as the software module SM is not compromised before the key is computed – i.e. before the protection is enabled. After that moment modules isolation assures that the content of modules private sections is inaccessible from the outside the modules (here it is implicitly assumed that software provider has not been tampered with, as well as  $K_{N,SP}$  has been correctly computed by IP and received by SP).

## 2.3.2 Security Properties

Here follows a summary of the security guarantees that the Sancus architecture achieves, as presented in [39]

**Software module isolation** The isolation property can be considered the fundamental property of the system: software modules run isolated on a node if their protected section cannot be accessed from outside the module themself. In Sancus this is achieved through a program-counter based memory access control [46], which implies that control flow enters into a module text section only by calling the entry point of that specific module. Moreover, the module data section is only accessed from code executing in the text section of the intended module. Notice that the protection is enabled only after the execution of the **protect** instruction:

#### protect(layout, SP)

until that moment, the content of a SM can be modified, by an attacker with full software capabilities. Any modification to the text section, occurring before the **protect** instruction is called, alters the module identity. This causes a mismatch between the key computed and stored into the node  $K'_{N,SP,SM}$  and the the key computed by the software provider  $K_{N,SP,SM}$  (Table 2.2), with consequent failure of successive attestations. On the contrary, modifications to the data section

#### 2.3. SANCUS 2.0

are not a concern since the **protect** instruction zero initialize the content of the section, when called. The processor **protect** instruction does:

- check that the layout of the new module does not overlap with any existing modules and, if this is the case, continue with the deployment by storing its layout in the PSA of the processor;

- enable the memory access control on the loaded module;

- compute the module key  $K_{N,SP,SM}$  basing of the layout informations, and store it in the PSA of the node;

The only way to lift the memory protection is through the processor instruction unprotect(continuation) from the inside of the module to be deactivated. To prevent any leakage, the instruction also clears module's code and data sections. Since the unprotect instruction is itself part of module's text section, a pointer to the code where the execution is to be resumed must be provided as *continuation* argument [39].

Figure 2.1: Representation of a Sancus node with a software module  $SM_1$  loaded. The content of the processor Protected Storage Area (PSA) is shown: it's important to underline that node key  $K_N$ , together with all SMs keys  $K_{N,SP,SM_i}$ , are stored in the PSA, which is not mapped into the system memory, and indirectly accessed by the software through specific processor instructions. Thus, they cannot be leaked. This is a peculiarity of the Sancus architecture in contrast to other solutions which leak the key, as it happens, for example, with Intel SGX in the Foreshadow attack [9].

**Remote attestation** Remote attestation is a crucial property for a networked infrastructure as the one Sancus has been thought for. Being able to remotely attest the identity of software modules executing on a remote node is a fundamental requirement for a software provider, since it guarantees that the intended module is correctly executing. In order to achieve it, two cryptographic primitives - encrypt and decrypt - are used (Equation 2.1). Due to the use of a freshness guarantee, they are resilient to replay attacks. The process of remotely attesting a SM running on a node N starts with the software provider SP sending a fresh nonce No to the node. The nonce is passed by the untrusted software running on N to the module, as argument of the encryption function to be called. Then, the module SM encrypts the received nonce  $N_0$  using its module key  $K_{N,SP,SM}$ , as shown in Equation 2.2. By discarding the output cyphertext C a Message Authentication Code T is obtained, which solely refers to the data  $N_0$ .

$$C, T = \texttt{aead-encrypt}(K, \{\}, D)$$

(2.2)

The computed MAC is then sent to the SP, which will compute a copy by means of its own copy of the module key  $K_{N,SP,SM}$ . If the two tags coincide, it is a proof that the software module SM is running untampered on the node N at this point of time. Notice that this property deeply leverages on the assumption that, after protection is enabled, SMs protected sections cannot be modified.

**Secure communication** By relying on the same mechanism used for remote attestation, it is possible to set a secure communication between software modules and software providers. Whenever a software provider SP wants to receive some data from a module SM, running on a node N, it sends a nonce No and, possibly, input data I to the intended module. The request is received by the untrusted software on the node and passed to the software module, which executes the code and produces an output O. The SM encrypts the output through the encrypt function  $C, T = aead - encrypt(K_{N,SM,SP}, O, No||I)$ , and sends the resulting cyphertext C and the tag T to the SP, on the unsecure network. Since SP knows the key  $K_{N,SM,SP}$  (remember the key management of Table 2.2) it can verify the tag and decrypt the output. In this way the software provider has strong assurance that the output O has been produced by SM on node N, given nonce No and input I.

**Secure linking** High assurance of calling the intended module must be provided when a software module tries to link with another module, on the same node. In order to do so, the module  $SM_1$  that wants to connect to module  $SM_2$ , needs to include  $SM_2$ 's identity in its text section<sup>2</sup>. In order to allow secure linking, the

<sup>&</sup>lt;sup>2</sup>Note that if  $SM_2$  wants to connect to  $SM_1$  too, this method creates a circular dependency between their identities. A solution is that the software provider does not include the identity

#### 2.3. SANCUS 2.0

processor is provided with two special instructions:

#### attest(address, expected hash)

The attest instruction proceeds by:

- verifying that a module, with protection enabled, is loaded at the provided *address*;

- computing the identity of that module, by using the cryptographic primitive hash function of page 10 on that module's text section and layout;

- comparing the result with the *expected hash* parameter of the instruction;

- returning module's ID in case the hashes were equal, zero otherwise;

Since the authentication process includes the computation of an hash, it is rather time consuming and expensive. Therefore the processor assigns sequential IDs to the loaded modules; the IDs are ensured to be used just once within one boot cycle<sup>3</sup>.

Hence, the IDs of verified modules are used to speed up subsequent attestations: it suffices to check that the same module with the same ID is still loaded at that address. The processor function

#### get-id(address)

checks that a protected module is loaded at *address* and returns the ID of that module. For caller authentication the node keeps track of the previously executing module by recording its ID in a register "*Caller ID*" of the PSA. The register is updated every time the execution flow enters in a different module. Modules can attest the caller identity though two instructions attest-caller and getcaller-id, whose usage is analogous to, respectively, the attest and get-id instructions, except that they implicitly use the caller ID.

**Confidential loading** Module's content is indeed protected, but only after protect instruction has been enabled; up to that moment an attacker can easily read the text section, without being noticed<sup>4</sup>. A software provider can deploy encrypted

of one of the two module in the text section, but it securely sends it after deployment has been done, storing in the data section [39].

<sup>&</sup>lt;sup>3</sup>This can be easily done by having the ID to be used for the next module stored in a register "Next ID" in the PSA. The value of the register is automatically incremented every time a new module is enabled, and it generates an error when it overflows.

<sup>&</sup>lt;sup>4</sup>Remember from page 12 that if the attacker modifies the text section, it causes a change in the module's key, which is detected in subsequent attestation; data section is not worrying since its content is zero initialized after protection has been enabled.

modules that will be decrypted in place before loading. In this way the content of a module is inaccessible for an attacker. Therefore a second way of using protect instruction is provided:

### protect(layout,SP,MAC)

The MAC is the authentication encryption tag provided by the SP which encrypted the text section of the module, with the key  $K_{N,SP}$ .

The instruction behaves exactly the same as before, except that it decrypts the module before calculating the module key. If the integrity check using the given MAC fails, the text section is cleared and the protection disabled.

**Hardware breach confinement** In the possibility that an attacker manages to breach the hardware protection of a node, the breach should be confined to the node in question and not affect the rest of the infrastructure. Since every node possesses its own private key, a compromised node does not provide to the attacker any further information regarding the *other* nodes. Therefore, an attacker could impersonate software modules form the compromised node, but it cannot extend the breach to other nodes.

**Memory access violation** When a memory access violation is detected the architecture simply resets the processor, clearing the memory to prevent any leak. This has the advantage of being a secure mechanism, as no information can leak, and simple at the same time. A big disadvantage is that it can have a bad impact on availability of the node: a bug or a malicious software may cause the node to keep resetting and clearing its memory.

## 2.3.3 Attacker Model

The attackers considered in Sancus are assumed with the following capabilities:

- Attackers can manipulate all the software on the node. Specifically they can act as a software providers and deploy malicious modules on the node, tamper with the operating system or even install a completely new one.

- Attackers can control the communication network that is used by the software providers and nodes to communicate between each other. Independently of the security of the communication channel, which is out of scope, they can sniff the network, modify traffic, or mount man-in-the-middle attacks.

- Attackers cannot break cryptographic primitives, but they can perform protocollevel attacks.<sup>5</sup>

- Attackers cannot have physical access to the hardware, thus they cannot probe the memory bus nor disconnect components, and so forth.

## 2.3.4 Implementation

#### 2.3.4.1 Hardware Implementation

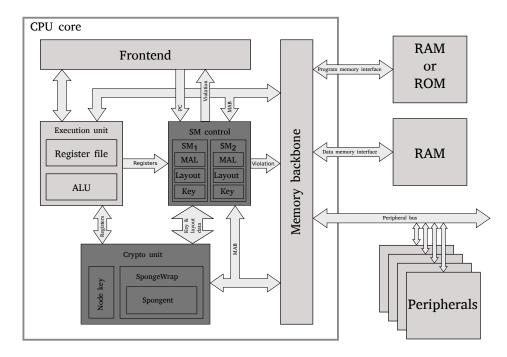

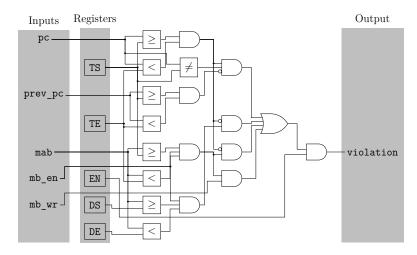

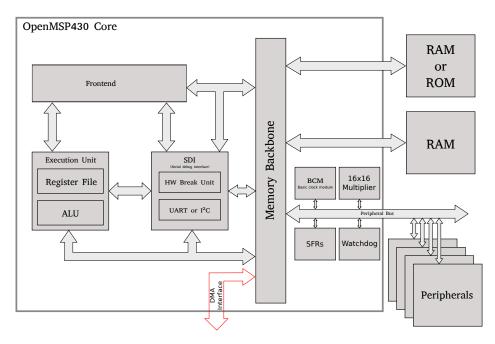

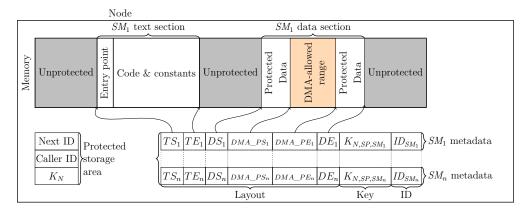

Sancus nodes are based on the open source implementation of the TI MSP430 corefrom the Open Core project [18]. In order to provide nodes with secure functionalities some modifications are carried out: first of all, modules layout informations as well as the modules keys  $K_{N,SP,SM}$  and identities are saved in internal CPU registers, thus only a finite set of modules can be deployed. Second, several instantiations of the *Memory Access Logic (MAL)* circuit are created, one for each module that can be instantiated in the system  $N_{SM}$ . Each circuitry implements the program-counter based memory access control. It has five inputs: current and previous program counters (PC), current address of the memory access bus (MAB) as well as memory access bus enable and write flags. It compares the PC and the MAB with the start and end addresses of text and data sections of a SM, when the protection EN bit is asserted. In case of illegal access to the memory a violation signal  $sm\_violation$  is raised. The MAL circuit is instantiated  $N_{SM}$  times, with  $N_{SM}$  being the maximum number of software modules that can be deployed on the node. You can find a representation of MAL circuit in Figure 2.3.

OpenMSP430 version in use in Sancus it is not natively provided with a DMA interface. The first tasks of this thesis is to upgrade Sancus by extending it with DMA interface functionalities as provided in the last version of openMSP430<sup>6</sup>. In order to do so, substantial modifications to the memory backbone carried out, as the DMA interface signals have to correctly interact with memory accesses of fetch, decode and execute CPU phases. Further details can be found in chapter 5.

#### 2.3.4.2 The Compiler

Although software developers can rely on Sancus security functions to create protected modules. However doing this correctly still requires doing this correctly still requires carefulness to not introduce software bugs that may invalidate the system security. Firstly a module must have only one entry point. Secondly each

<sup>&</sup>lt;sup>5</sup>Protocol-level attack is defined as the exploitation of specific feature or implementation bug of some protocol installed at the victim for consuming huge amount of its resources.

<sup>&</sup>lt;sup>6</sup>At the time of writing, the openMSP430 core is realeased with version r211.

Figure 2.2: Overview of the hardware block constituting a Sancus core. Lightly shaded blocks are part of the original openMSP core, whereas darker shaded ones are specifically added for Sancus. Remember that the number of SMs  $N_{SM}$  is set when synthesizing the core. Notice how the SM control unit takes the program counter (PC) and the memory access bus (MAB) as inputs for memory access logic (MAL) circuits [39].

Figure 2.3: Schematic of the Memory Access Logic (MAL), the hardware used to enforce the memory access rules for each protected module [39].

#### 2.3. SANCUS 2.0

module need to implement its own call stack to avoid leakage of sensitive data to unprotected code. Thirdly, exiting from a module, or calls to another one, requires specific instructions to be carried out in the right order. The compiler assures that everything is correctly handled, with no further burden on the programmer side. To deals with these low level details, Sancus authors implemented a compiler extension based on LLVM [19], together with support library that offers API to perform some commonly used function like calculate a MAC of data. "The compiler compiles C standard files, and it uses Clang [19] as compiler frontend. To benefit from Sancus, developers only need to indicate which functions should be part of protected module, which should be the entry points and what data should be in the protected section. This is done by means of compiler attributes -SM\_FUNC, SM\_ENTRY and SM\_DATA- respectively used to annotate functions, entry points and modules private data." [39].

**Entry points** The compiler implements multiple logic entry points on top of the single physical entry point of a software module, by means of a jump table. The compiler assigns a unique ID to every logical entry point; when code tries to jump to one of these entries, its ID is stored in a register and the jump is redirected to the correct physical entry point of the module. The code, then, jumps to the correct called function based on the ID passed in the register.

**Stack handling** The compiler also takes care of reserving a space in the protected section of the module for the stack. The first time a module is entered the stack pointer is loaded with the address of this start location of the module stack. Stack pointer of the module is saved on exits, for further usage.

**Exiting Modules and Secure Linking** When exiting from a module any register that is not holding a parameter to be returned is cleared, to avoid leakages. Calls to protected modules automatically verify the caller ID: in order to do so a software provider needs provide its key to the compiler.

## 2.3.4.3 Software Stack for Deployment

Deploying a module is a sensitive operation: module's identity, thus its key, depends on module's load address on the node. These SP must be aware of those addresses in order to correctly compute  $K_{N,SP,SM}$ . Enforcing static loading is not a scalable solution given that the target system supports module loading from different software providers. Hence the need to implement a software stack to dynamically deploy modules on a node. The process starts with the SP creating an Executable and Linkable Format (ELF) file of the SM and sending it to the node N. The host software on the node receives the files, finds a free memory area to load the SM and relocates it using a dynamic ELF loader. Then hardware protection is enabled and a symbol table is sent back to the SP. The symbol table contains the addresses of any global functions along with the load addresses of all protected modules on the node N. By using the symbol table the software provider can reconstruct the exact same image of SM as loaded on the N, which can be use for the computation of the module key.

Loading of encrypted modules requires an extra step, since the dynamic loader need to inspect and update parts of the text section, which is inaccessible in case of encrypted modules. First the SP sends a request to the N specifying the size of the encrypted module it wants to load. Then the host software allocates memory for the module's sections and answers back with an handle identifying the memory allocated location, and the symbol table. SP links locally the SM and sends the resulting image back to N, together with the memory handle. The host software on the node loads it in the pre-allocated memory sections and enables the protection. After the SM has been deployed, the software on the node provides an interface to be able to call its entry point. From this moment the module is fully operative on the node, thus the SP can use the provided interface to start operations on the module, such attesting its status or performing I/O accesses to its data. The interface is used to provide the SM with the identities of the other modules, it can securely link to. To this end, the SP computes the identity hashes from the symbol table, which contains the image of the loaded modules or, if the module to be loaded belongs to a different software provider, it receives them from the respective providers. Finally the hashes are encrypted with the  $K_{N,SP,SM}$  and sent to the node.

# 2.4 Direct Memory Access (DMA)

## 2.4.1 Overview

Direct Memory Access (DMA) is a feature of CPUs that allows hardware subsystems to directly access the memory, without the participation of the Control Unit (CU). Without DMA mechanism, CPU would be fully occupied during I/O operations, thus unavailable to perform other tasks. In this sense, DMA speeds up the system, unburdening the CPU from I/O loads. In general DMA traffic is supervised by a DMA Controller (DMAC): the device that wants to start a DMA operation has to configure the DMAC internal registers, specifying the starting address of the memory location where the operation should occur and the number of words to be handled. Depending on the architecture on which it will be released, DMAC may possess further features such as interrupt capabilities, different modes

#### 2.4. DIRECT MEMORY ACCESS (DMA)

of operation, and so forth.

**Operation Modes** DMA transfers can occur in three different modalities:

- Burst mode In burst mode DMA accesses are performed atomically: once the CPU grants DMA the access to the memory bus, a data transfer starts; it lasts until an entire block of data is sequentially transferred, then DMAC releases the control of the system bus back to the CPU. This is the fastest transfer mode, but it also prevents CPU to access the memory for long periods of time.

- Cycle stealing mode The cycle stealing mode is a good compromise between transfer speed and CPU memory access time. This transfer mode should be used in those cases where the CPU cannot be inactive for the whole length of a burst mode transfer. The difference with respect to the latter is that CPU gains back control of the bus after one byte of data has been transferred. Hence block transfer proceeds byte-per-byte, with the DMAC having to request the access to the system bus each time.

- **Transparent mode** Transparent mode is the slowest operation mode, yet the most efficient mode in terms of overall system performance. In transparent mode DMAC transfers data only when the CPU is not using the system bus; the primary advantage of this mode is that CPU never stops waiting for the system bus. The disadvantage is that DMA transfers takes longer times to complete, besides the hardware needs to determine when CPU is not using the system bus; in some cases this can be complex.

## 2.4.2 DMA Interface for OpenMSP430

The openMSP430 microprocessor offers a DMA interface that acts as gateway to the whole memory of the system.

Memory in the openMSP430 architecture In openMSP430 architecture the memory is seen as a single block, composed by program memory, data memory and peripheral space arranged sequentially as shown in Figure 2.5. Each physical memory location is a 16 bits word, whereas logical memory words are 8 bits long; hence logical memory is perceived as double the dimension of the physical memory. When accessing a logical memory location through a logical address, physical address needs first to be retrieved: this operation is automatically done in the memory backbone of the system, where the logical address is compared with the starting and ending points of logical memory regions (program, data or peripheral

Figure 2.4: Overview of the openMSP430 core internals, with DMA support [18]. Memory can be accessed both through the normal system bus, along with DMA interface.

space), in order to find the correct one to access to. After that, the starting address of the resulting region is subtracted from the logical address  $LOGICAL' = LOGICAL - START_POINT$ . Finally, the physical address is obtained with a simple bitwise right shift PHYSICAL = LOGICAL'/2.

### 2.4.2.1 DMA Interface - Signals

Here a list of all the signals of the DMA interface is presented in Table 2.3; each of these signals takes part in a DMA transfer and it's driven either by the core or by the DMAC. Description of the signal is also given. Notice that the DMA interface of the core is meant to be connected to a general DMA arbiter, as DMA controllers, bootloaders, and so forth. For this reason in this section the term DMA Master will be use, to keep the discussion as generic as possible; keep in mind that the DMA Master of the Sancus architecture is a DMA Controller.

#### 2.4. DIRECT MEMORY ACCESS (DMA)

Figure 2.5: Organisation of the memory in the openMSP430 core [18]. Memory is seen as a single memory block, with program memory, data memory and peripheral space arranged sequentially. Each physical memory location is of 16 bits, whereas logical memory words are 8 bits long, hence the logical memory is perceived as twice as the physical memory. A more advanced system configuration is available, allowing to further extend the peripheral space; this would result in a shift of the start and end points of data memory (image on the right).

Table 2.3: List of all the signals of the DMA interface. A brief description of the signals composing the DMA interface, along with their I/O direction, is reported. Notice that the DMA Master can be any device capable of correctly driving the DMA interface signals such as bootloaders, DMA controllers, Memory-BIST or any other hardware unit requiring direct read/write access to the CPU memory space. Source [18].

| Signal Name | Description                                                                                                                  | I/0 Direction            |               |

|-------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|

| MCLK        | It's the system clock that times all DMA                                                                                     | openMSP430               | $\rightarrow$ |

|             | transfers.                                                                                                                   | DMA Master               |               |

| PUC_RST     | It's the system reset signal and it is active<br>HIGH. This signal is used to reset the<br>system, including the DMA master. | openMSP430<br>DMA Master | $\rightarrow$ |

| DMA_DOUT[15:0] | The read data bus is used to transfer<br>data from the openMSP430 memory to<br>the DMA master. It needs to stay valid<br>until transfer is complete, as signalled by<br>DMA_READY.                                           | openMSP430 $\rightarrow$ DMA Master |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| DMA_READY      | This signal flags a transfer complete when HIGH.                                                                                                                                                                             | openMSP430 $\rightarrow$ DMA Master |

| DMA_RESP       | The response signal it's driven HIGH on transfer errors.                                                                                                                                                                     | openMSP430 $\rightarrow$ DMA Master |

| DMA_ADDR[15:1] | Logical address of the 16-bit word currently accessed by the interface.                                                                                                                                                      | DMA Master $\rightarrow$ openMSP430 |

| DMA_DIN[15:0]  | It's the write data bus used to transfer<br>data from the DMA master to the sys-<br>tem memory. It needs to stay valid un-<br>til transfer is complete, as signalled by<br>DMA_READY.                                        | DMA Master $\rightarrow$ openMSP430 |

| DMA_EN         | The enable signals indicates that the current DMA transfer is active. It needs to be driven HIGH until completion of the transfer, as signalled by DMA_READY.                                                                | DMA Master $\rightarrow$ openMSP430 |

| DMA_WE[1:0]    | Each of the two bits indicate a transfer<br>on the selected byte, when HIGH, and a<br>read transfer when LOW.                                                                                                                | DMA Master $\rightarrow$ openMSP430 |