## POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

Master's Thesis

# In-Memory Binary Neural Networks

Supervisors: Prof. Maurizio ZAMBONI Prof. Mariagrazia GRAZIANO Prof. Marco VACCA

> Candidate: Andrea COLUCCIO

April 10, 2019

## Acknowledgments

I would like to thank all the people who made possible this course of studies.

A special and most important recognition goes to my parents, who gave me the opportunity to face these academic years with peace of mind, giving me all the support I needed.

I also thank my girlfriend Martina for having been always close, even in the most difficult moments and complicated choices. Thank you for supporting me everytime.

A special thank to my aunt Maria for her support.

I would like to express my gratitude to my high school Professor Anna Civarelli, who has always motivated me to do my best from the beginning of my scholastic carrier until now. She played an important role in my education, allowing me to develop a strong interest in Electronics.

I am grateful to the Politecnico di Torino who provided me with the means to fulfill myself in my field of interest; in particular, I thank my mentors Prof. Maurizio Zamboni, Prof. Mariagrazia Graziano and Prof. Marco Vacca who have encouraged me to give the best of me to achieve this important thesis.

Lastly, I address a thought of thanks to all those who have supported me over the years.

Sincerely, Andrea Coluccio Turin, April 10 2019.

## Glossary

- 1T1R One transistor, one resistor: a memory cells' implementation used in RRAM to isolate the current of the selected cell from the others. 11, 51, 54, 58, 93, 94

- ACCA Accumulation array. 107

- AlexNet AlexNet is a convolutional neural network, which competed in the ImageNet Large Scale Visual Recognition Challenge in 2012. The network achieved a top-5 error of 15.3% [1].. 9, 11, 12, 23, 24, 28, 32, 48–50, 101, 109–116, 122, 124, 125, 250

- **BCNN** Binary convolutional neural network. 48, 49, 102, 103

- **BNN** Binary neural network. 11, 13, 61, 70, 71

- CIFAR-10 The CIFAR-10 dataset (Canadian Institute For Advanced Research) is a collection of images. The CIFAR-10 dataset contains 60000 32x32x3 images in 10 different classes. The 10 different classes represent airplanes, cars, birds, cats, deer, dogs, frogs, horses, ships, and trucks. [2]. 12, 25, 32, 34, 38, 39, 58, 60, 62, 103, 112

- CIM Computation in memory. 45, 49, 126

- CNN Convolutional neural network. 7, 9–11, 14, 23, 27–29, 35, 37, 39, 45, 49, 52, 53, 58, 62, 74, 75, 82, 95, 99, 101, 102, 107, 108, 113, 119, 121, 123, 128, 137

- **DPU** Digital processing unit: a separated unit (external from memory) used to perform computations which are not executable in-memory. 49

- **DW** Domain wall (magnetic). 50, 51, 53

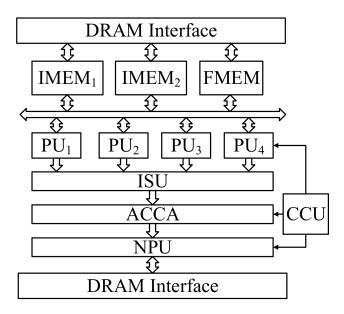

- FMEM Filter memory. 107

- **IFMAP** Input feature map. 7, 8, 10, 62, 91, 98, 99, 101, 105, 108, 133, 134, 136, 201, 203

- ImageNet The ImageNet project is a large visual database designed for use in visual object recognition software research. It contains about 14 million images [3]. 6, 10–12, 23, 27, 28, 32, 39, 49, 110–112

- **IMEM** Image memory. 107

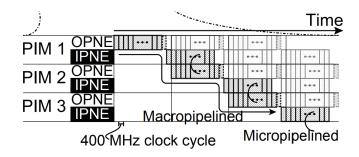

- IPNE Input parallel neural engine, inputs are in parallel, while outputs are delivered in serial. Output of this configuration is compatible with OPNE's input. 12, 72–74, 115, 118–120, 123, 126–130

- **ISU** Input feature map summation unit. 107

- LeNet LeNet is a type of convolutional neural network. 86, 90, 91, 116

- MLC Multi level cell, more then one bit can be hold into a single cell. 11, 12, 41, 42, 55–57, 94, 115, 118–120, 122, 126, 130

- MLCS Memory logic conjugated system. 75–78

- MLP Multilayer perceptron is a class of artificial neural network. Each node is a neuron that uses a nonlinear activation function, except for the inputs. MLP uses backpropagation for training. [4]. 8, 9, 12, 14, 23, 58, 60, 61, 66, 67, 86, 113, 115, 121–123, 134, 137, 146, 235, 236, 246

- MLSA Multi level sense amplifier. 60–62, 123

- MNIST The MNIST database (Modified National Institute of Standards and Technology database) is a dataset of handwritten digits with 60000 images in B/W.

[5]. 13, 19, 34, 45, 58, 60–62, 66–68, 75, 81, 86, 91, 119, 131, 133, 138, 139, 201, 235

- MRAM Magnetoresistive random-access memory (MRAM) is a non-volatile randomaccess memory technology. Data in MRAM is not stored as electric charge or current flows, but by magnetic storage elements. 6, 10, 41, 42, 46, 47

- **MSC** Modified sensing circuit, designed for logic and full-add operations. 10, 42, 43, 45

- MTJ Magnetic Tunnel Junction is a component composed by two ferromagnets separated by an insulator. Electrons can tunnel from one ferromagnet into the other.[6]. 6, 10, 41–43, 45, 47, 48, 50–53, 93, 117, 119, 120, 126, 129

- NDP Near Data Processing. 95

- **NPU** Neuron processing unit. 106, 107

- **NVM** Non-volatile memory. 46, 92, 93

- **OFMAP** Output feature map. 7, 8, 10, 37, 46, 62, 75, 91, 105, 132, 133, 136

- **OOM** Out of memory implementation.. 7, 8, 16–20, 87, 117, 121, 127, 148, 156, 171, 174, 188, 192, 205–208, 210, 211, 214, 218, 219, 221–223, 241–250, 252–254

- **OPNE** Output parallel neural engine, inputs are in serial, while outputs are delivered in parallel. Output of this configuration is compatible with IPNE's input. 12, 72–74, 115, 118–120, 123, 126–130

- **PIM** Processing in memory module: it is formed by the combination of an OPNE and an IPNE. 74, 115, 123, 128

- PU Processing unit. 105

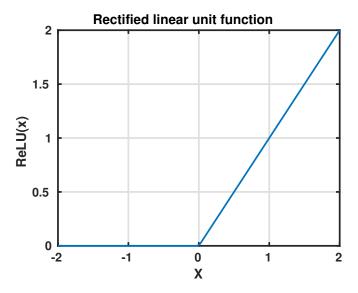

- **ReLU** Rectified linear unit, a type of neuron's activation function which consists into ReLU(x) = max(0,x). In terms of training time, it is the best choice.. 24, 25, 34, 102–104, 106

- **RRAM** Resistive switching random access memory. 6, 7, 10–12, 54–58, 61, 67, 69, 92–94, 115, 117, 123, 124, 126–130

- SC Stochastic computing. 87, 88, 91

- **SCT** Synapse configuration table. 70–72

- SGD Stochastic gradient descent method. 37, 66, 67, 133

- **SOT** Spin-orbit torque: a type of magnetic RAM. 6, 10, 12, 46, 47, 50, 115, 118, 120, 122, 126, 128–130

- stride stride, in the context of CNNs, is the distance between the receptive field centers of neighboring neurons in a kernel map. 8–10, 24–26, 35, 99

- STT Spin-transfer torque is an effect in which the orientation of a magnetic layer in a MTJ can be modified using a spin-polarized current [7]. 6, 12, 41, 42, 50, 92, 115, 118, 119, 122, 126, 130

- **SVHN** SVHN (Street View House Numbers) is a dataset. It consists in a training set of 604K and a test set of 26K 32x 32 color images representing digits ranging from 0 to 9.. 34

- top-1 top-1 error is measured by checking if the top class (the one having the highest probability) is the same as the target label. 10, 11, 25, 26, 39, 109, 110, 112

- top-5 top-5 error is measured by checking if the target label is one of your top 5 predictions (the 5 ones with the highest probabilities).. 10, 12, 25, 26, 39, 111

#### Summary

In this thesis, an In-Memory architecture of a binary neural network is presented. The concept of "In-Memory" is related to the possibility to place near-memory very simple computational units, such as logic gates or full-adders, to implement a distributed circuit instead of Von Neumann's classical one. This choice brings to relevant benefits such as lower energy consumption/delay, since the computation is performed very close to memory, the wasted energy and the corresponding latency caused by the data fetching are heavily reduced, allowing an higher parallelization.

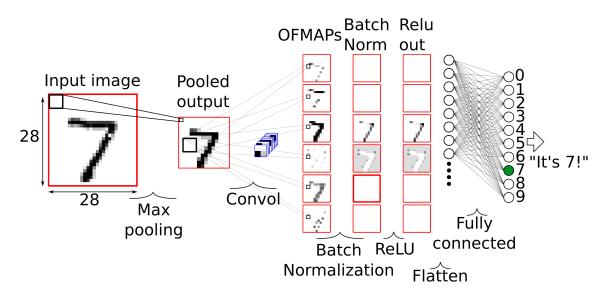

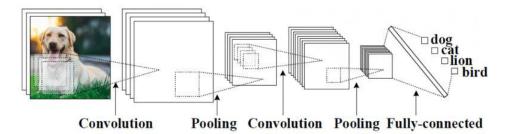

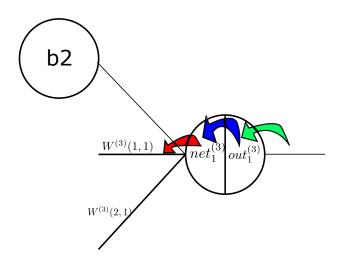

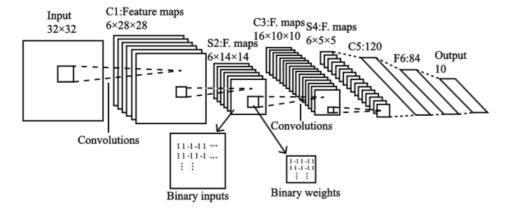

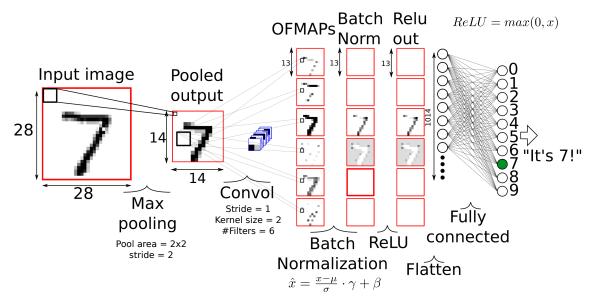

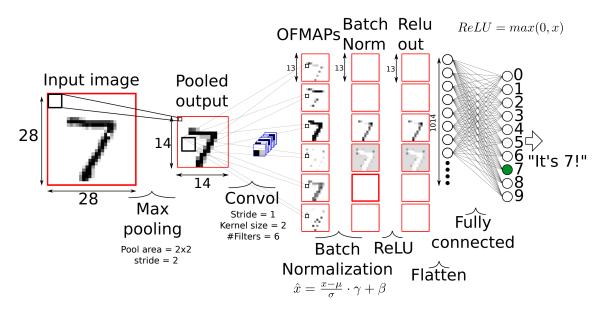

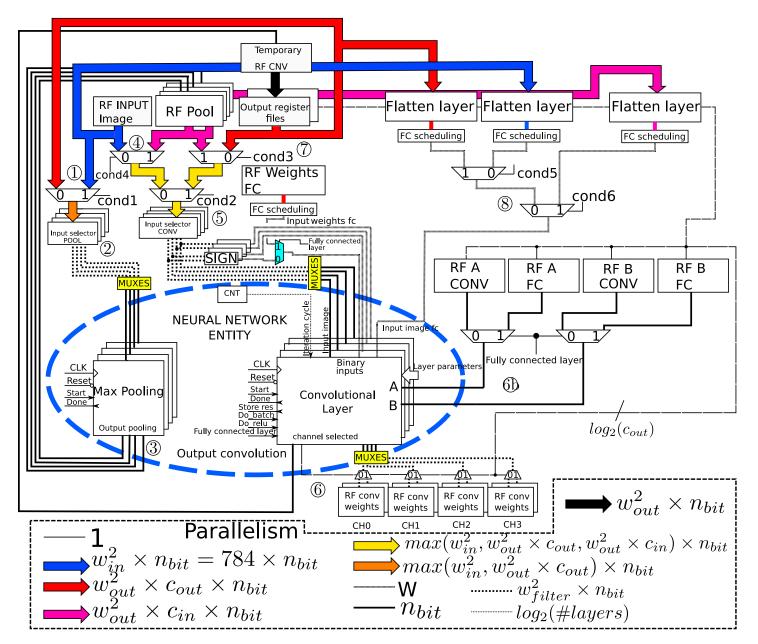

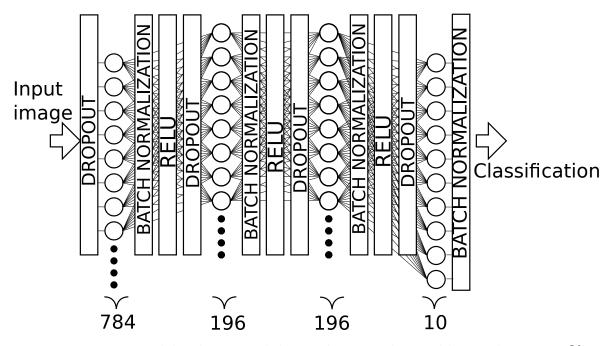

Figure 1: Convolutional neural network used as starting model. MNIST database is used, which is composed by handwritten digits in range  $0 \div 9$ .

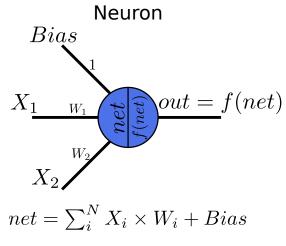

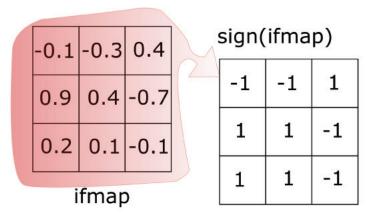

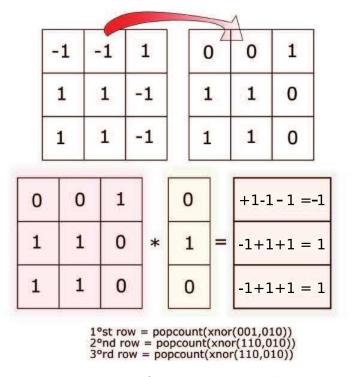

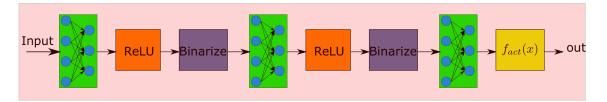

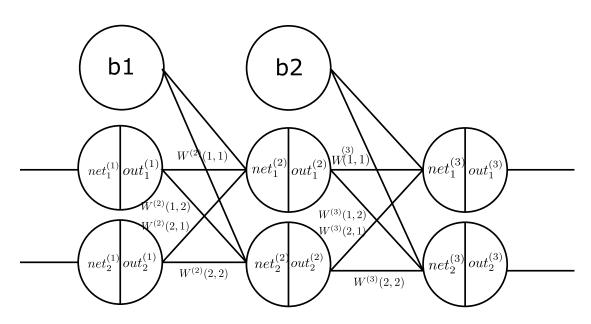

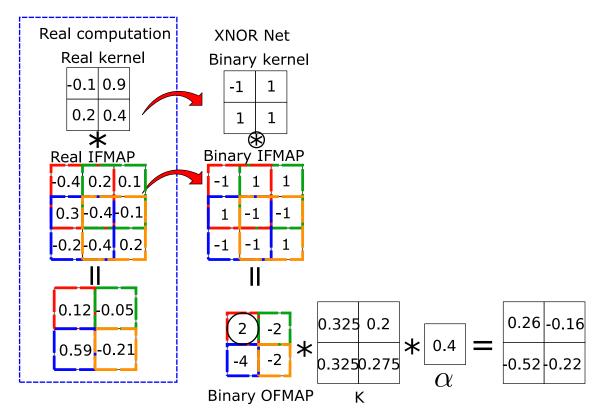

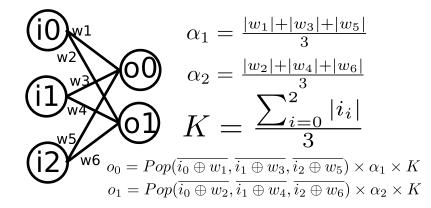

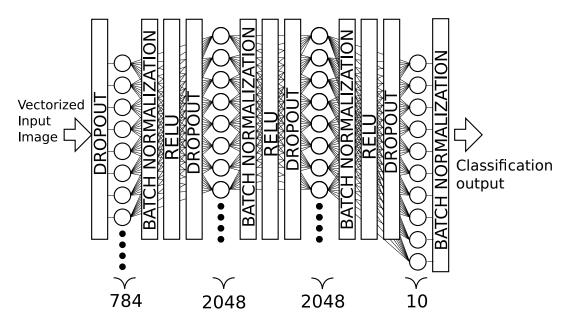

As computational models, Convolutional Neural Networks (Figure 1) have been chosen. They are a class of neural networks that are able to recognize/classify raw data, such as images, sounds, natural language etc. The key parameters of a neural network are the number of layers and their dimensions, that influence the accuracy achievable and the usable dataset's complexity. A "binary" approximation called **XNOR Net** is considered, in which weights (**W**) and inputs (**I**) are binarized between  $\{-1, +1\}$  by taking the sign, reducing the multiply-accumulate operations used in convolution into XNORs-popcounting sequences. The term "pop-counting" refers to the following operation: number of 1s - number of 0s. The value computed is then multiplied by two scaling factors (**K** and  $\alpha$ ), obtaining the approximated convolution. This choice reduces memory required and computational cost, but degrades the achievable accuracy (from ~ 97% to ~ 84% for the model in Figure 1).

#### Architectures

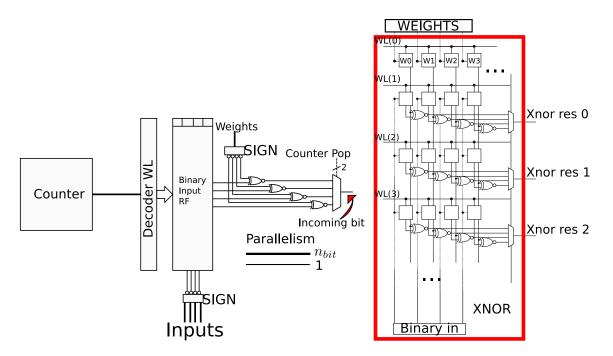

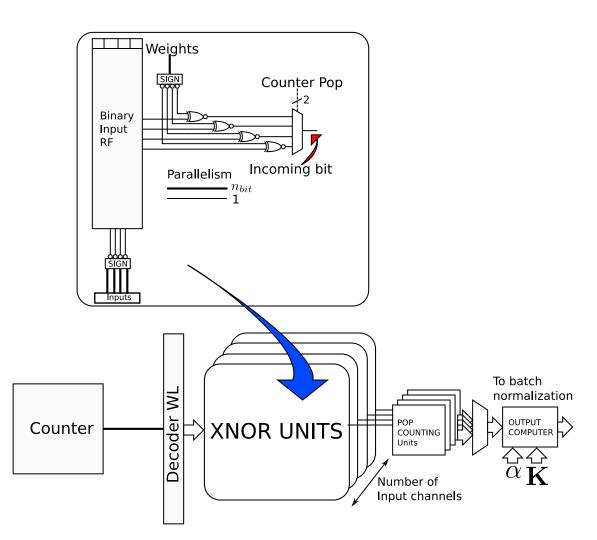

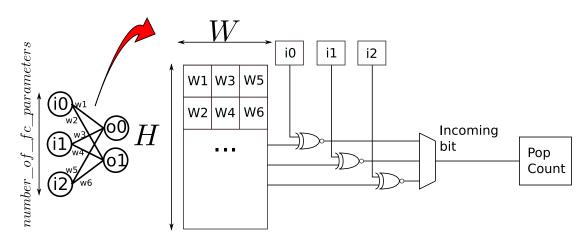

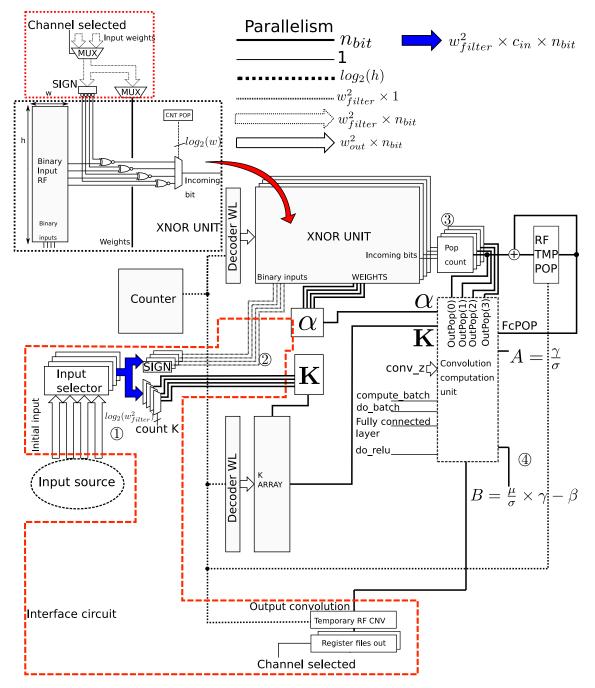

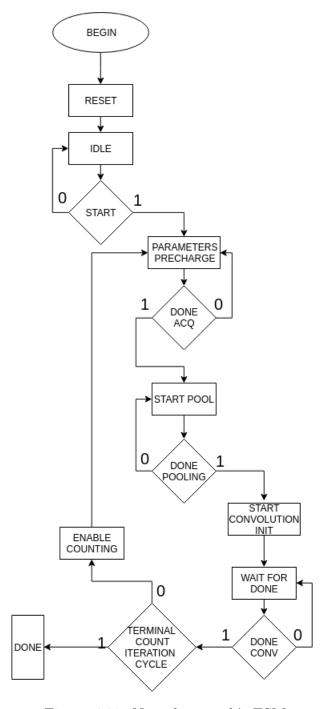

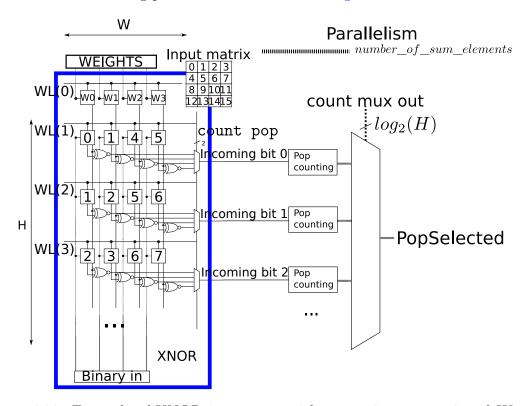

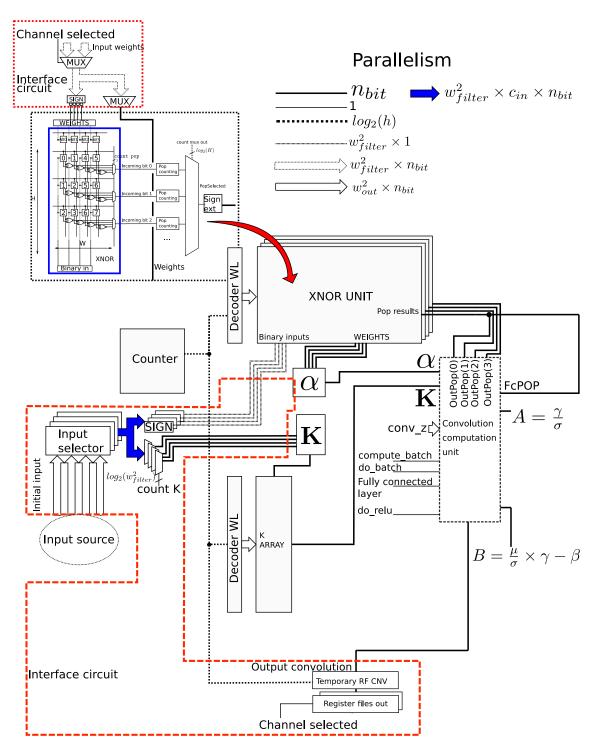

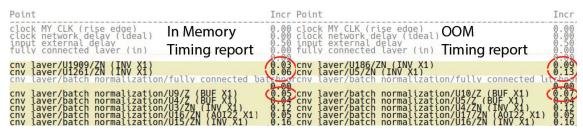

Figure 2: Classical implementation. Binary input RF, the binary signs are Inputs are precharged into the memprecharged and then fetched one row per ory cells and the XNOR gates perclock cycle to compute the XNORs. incoming bit selected goes to pop-counting binary weights  $(W_0, W_1, ...)$  and inputs. unit.

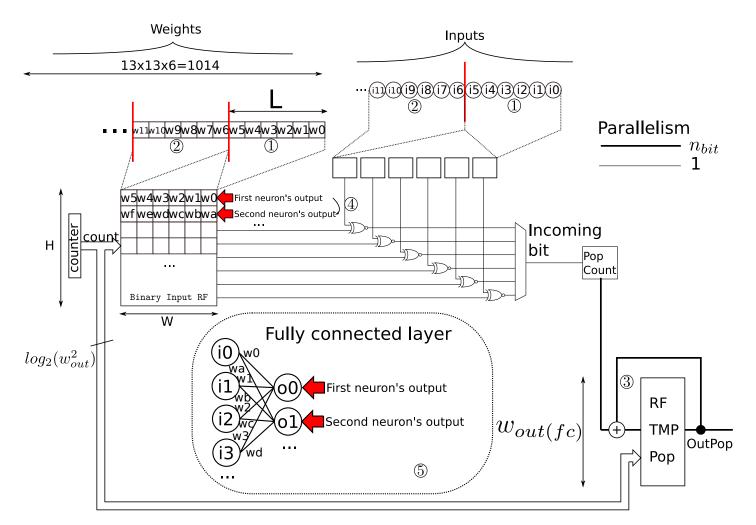

In Figure 3: In-Memory implementation. The form the xnor operation between the Xnor results are then fetched from pop-counting parts.

Two architectures based on 45nm CMOS technology (In-Memory and classical implementations respectively), have been developed. The classical implementation has been used as reference architecture to compare the performance achieved in the In-Memory case. The computational model is well-suited for an In-Memory implementation, since XNOR gates and pop-counting circuits are very simple units that can be integrated into a memory array. In the classical implementation in Figure 2, a traditional memory has been used, in which data are simply stored and the computation is done out-of-memory (OOM). In the In-Memory alternative (Figure 3), the traditional structure has been replaced with a CAM-like array and the computation is performed inside the mesh by computing the xnors between binarized weights-inputs. One of the main advantage in the In-Memory alternative is the parallelization of the XNOR/pop-counting computations, which reduces the time required by the algorithm and the energy consumed.

#### Validation flow

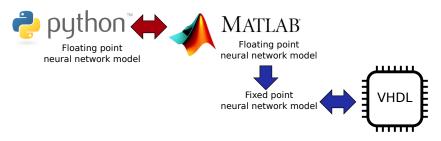

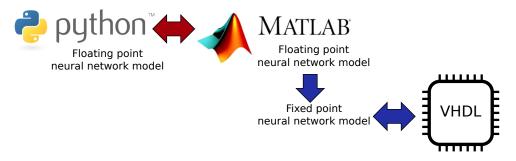

Since the neural networks are often realized in software (for example Python with TensorFlow and Keras), a MATLAB model that computes both in floating point and fixed point representation has been carried out to convalidate the correctness of the VHDL implementation: when the floating point results are validated, the fixed point model is then verified, obtaining the validation flow depicted in Figure 4.

Figure 4: Validation flow of the neural network model.

### Performance

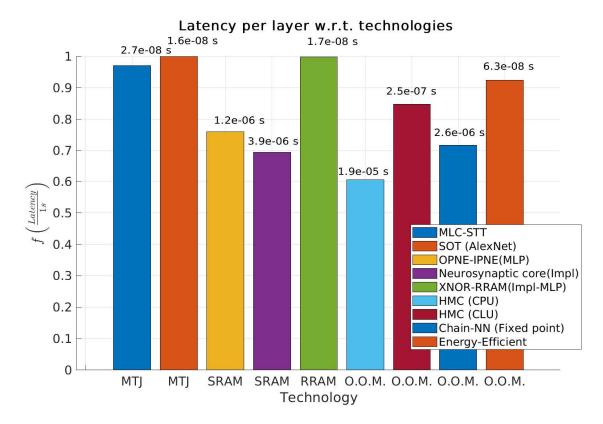

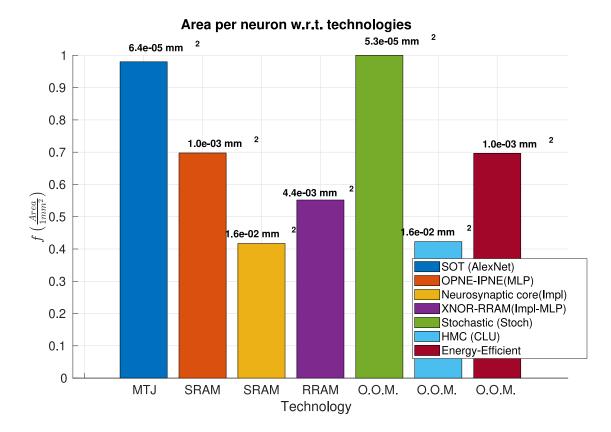

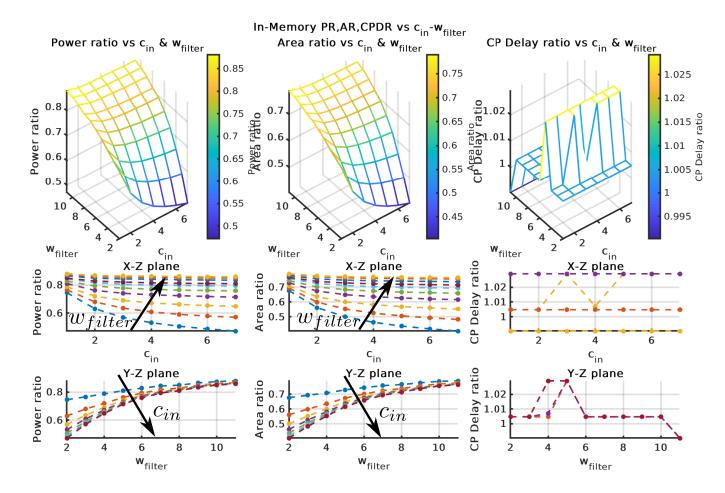

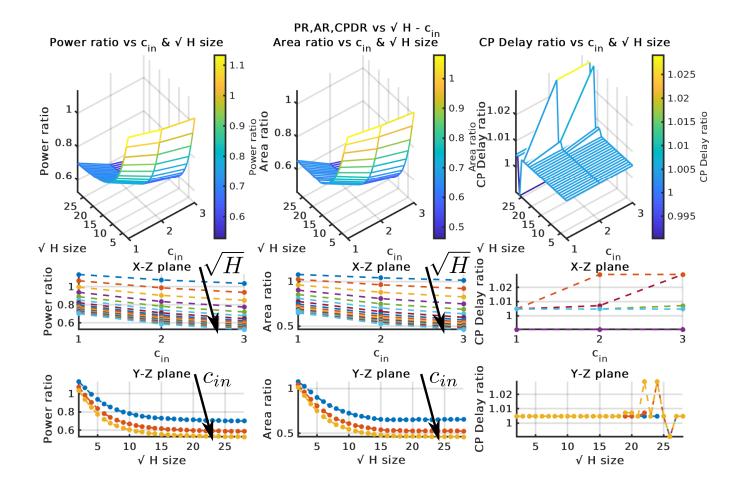

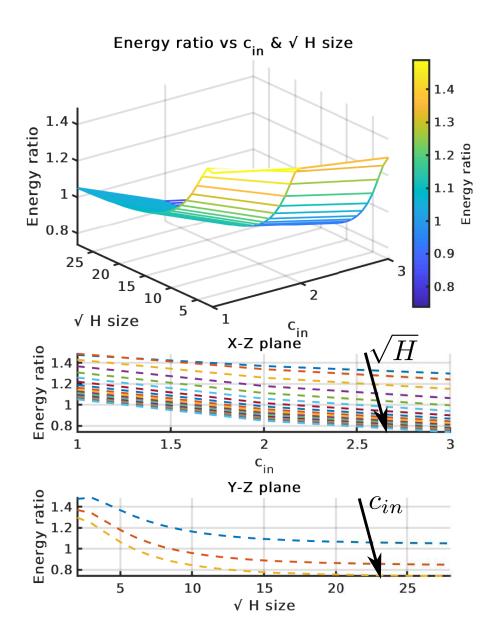

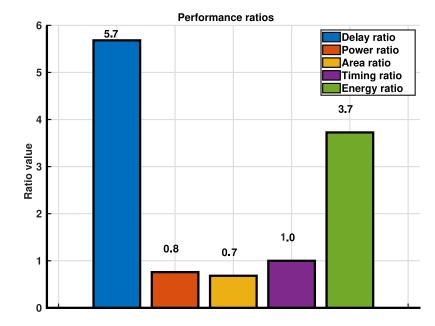

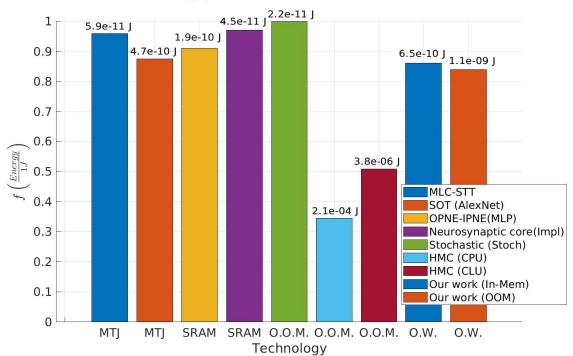

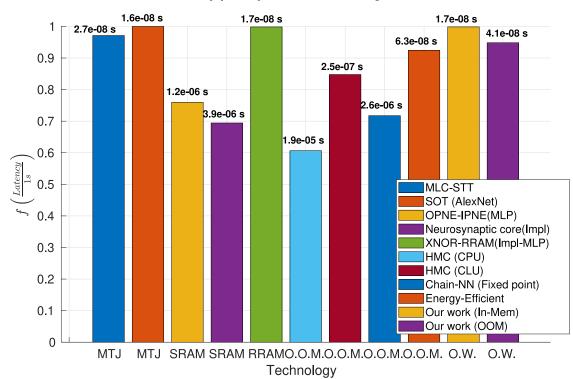

The results show that the classical implementation needs  $\sim 2.5 \times$  more computational time than the In-Memory architecture with an higher energy consumed  $(\sim 1.7 \times)$ , for the model in Figure 1. The architectures implemented have the possibility to realize any kind of neural network, with more complex models or datasets. For the model depicted in Figure 1, the framerate achieved in the In-Memory case is 16337 fps with 0.79  $\mu J$  consumed, while for the OOM case is 6652 fps with  $1.33\mu J$  and a clock frequency of 4.22ns for both cases. By evaluating the architectures' perfomance for different neural network models, the In-Memory alternative is able to consume  $\sim 3.7 \times$  less energy and to save up to  $\sim 5.7 \times$  computational delay than the classical counterpart. Roughly comparisons have been performed with the state-of-the-art based on innovative technologies (such as RRAMs, MTJs Memristors, etc.), showing very good computational delay with relatively low energy consumption results for the In-Memory architecture: the perfomance estimations for this case are pessimistic, since the memory array has been synthesized by Synopsys Design Compiler as a register file and each cell as a flip-flop, that is more complex than a custom memory cell. However, the resulting normalized energy and delay for the In-Memory case are  $\sim 650 pJ/neuron$  and  $\sim 17 ns/neuron$  respectively, that are comparable to an analog MTJ-based single-level-cell solution with an energy value of ~ 450 pJ/neuron and a normalized delay of ~ 16ns/neuron. Choosing beyond-CMOS technologies, enables the realization of very efficient solutions.

### Thesis structure

This work is composed by the following chapters:

- 1. **State-of-the-art**, in which actual neural network implementations and technologies are reported (both In-Memory and <u>OOM</u> solutions);

- 2. **Comparisons**: the implementations discussed in the state-of-the-art are compared in terms of perfomance;

- 3. Software implementation: an explanation of the starting neural network model is provided, in which Python code is analyzed and discussed;

- 4. Hardware implementations: a detailed explanation on how the neural network has been realized in VHDL is given, for both the computational model (<u>OOM</u> and In-Memory respectively). In this part, the neural network model depicted in Figure 1 is used, because it is easier to understand. Next, it is demonstrated how the circuit can be used to implement different neural network models, with any kind of structure and dimension;

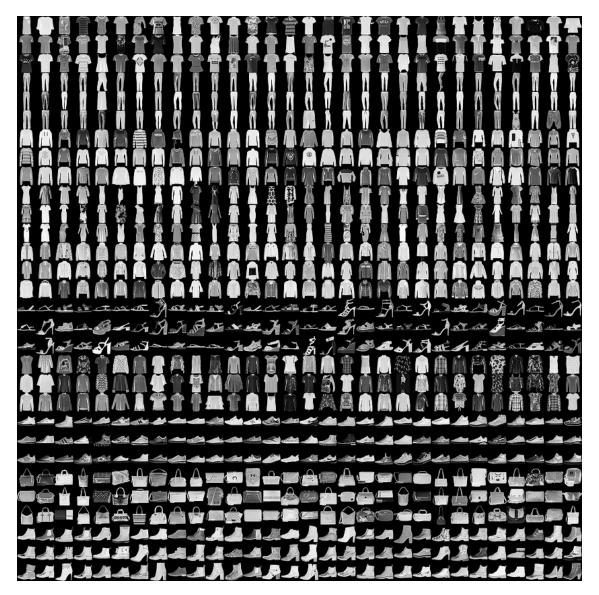

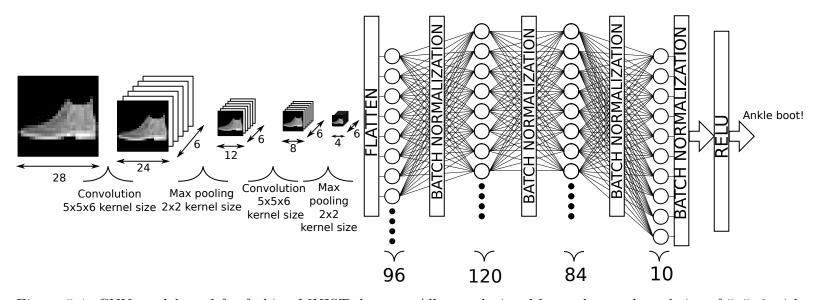

- 5. Verification: the results are compared and the correspondence between Python-Matlab-VHDL is tested, as already described in Figure 4. Here, three different neural network models are tested to demonstrate the capability of the circuits to implement any kind of neural network model and dataset: the original one (Figure 1), an <u>MLP</u> network and a fashion-MNIST based <u>CNN</u>;

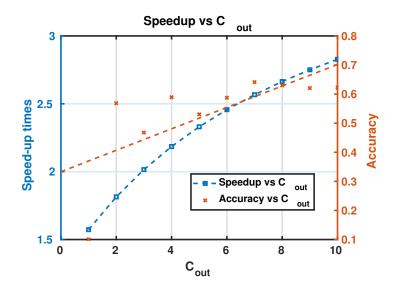

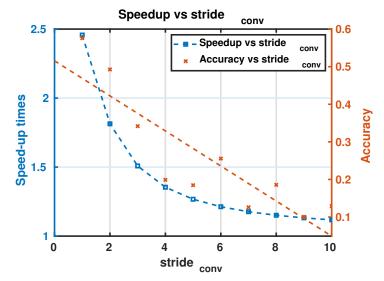

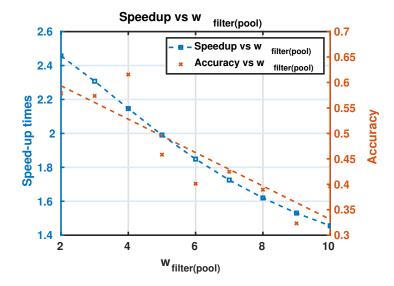

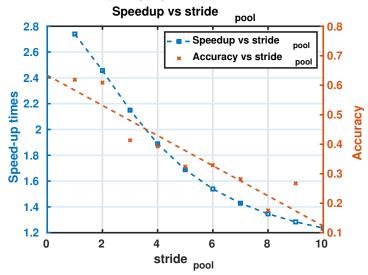

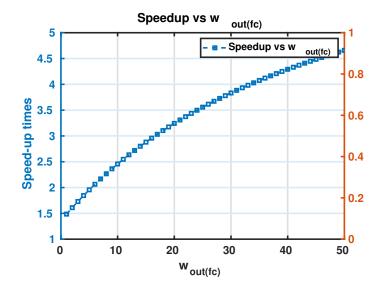

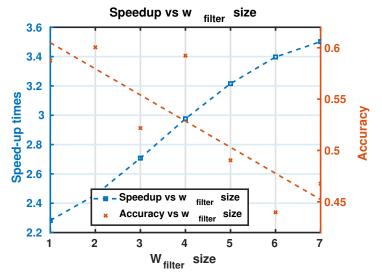

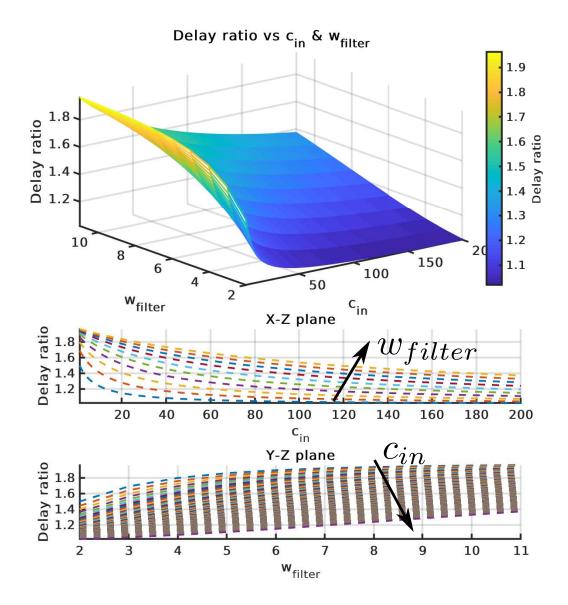

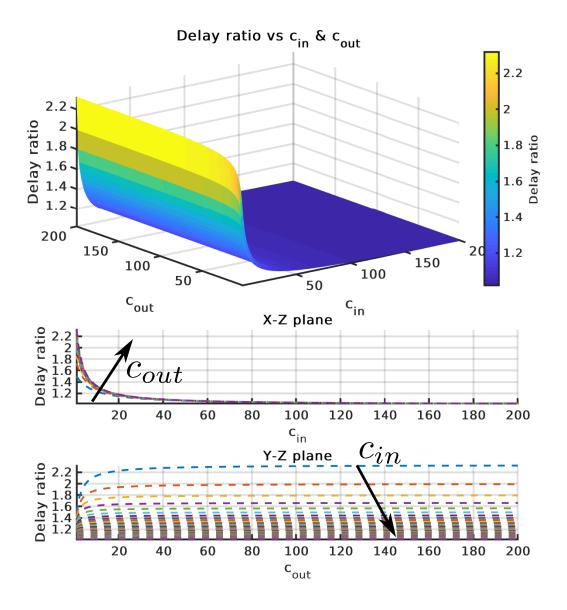

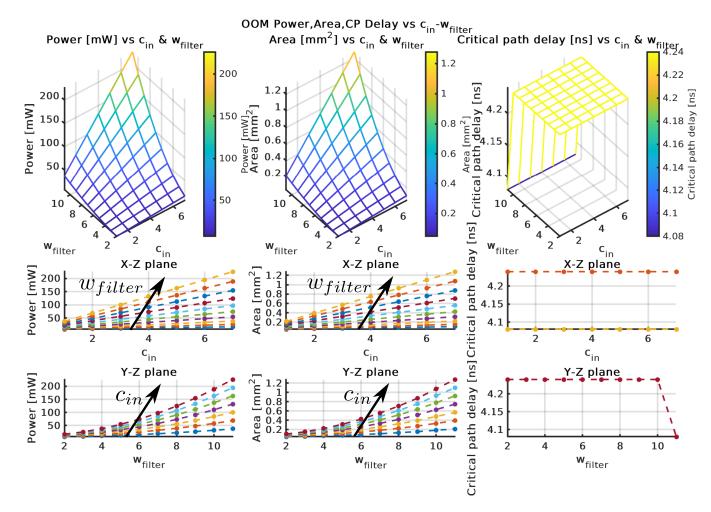

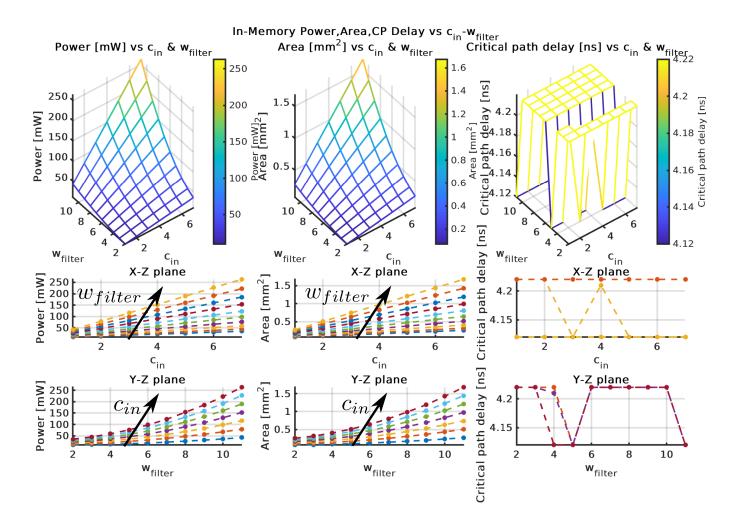

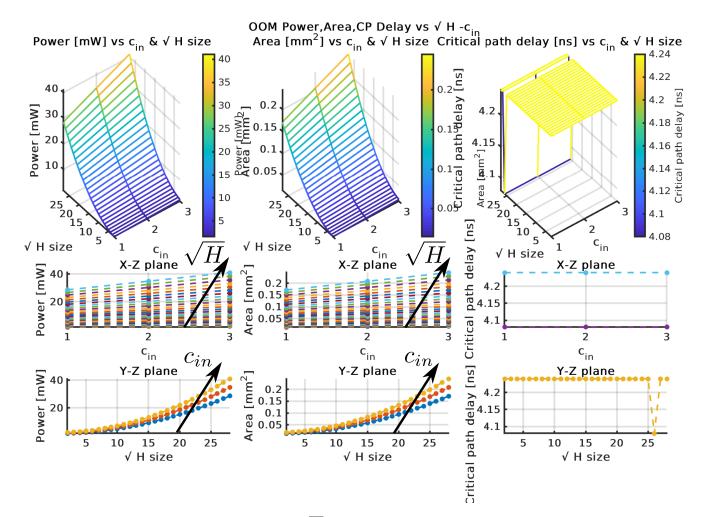

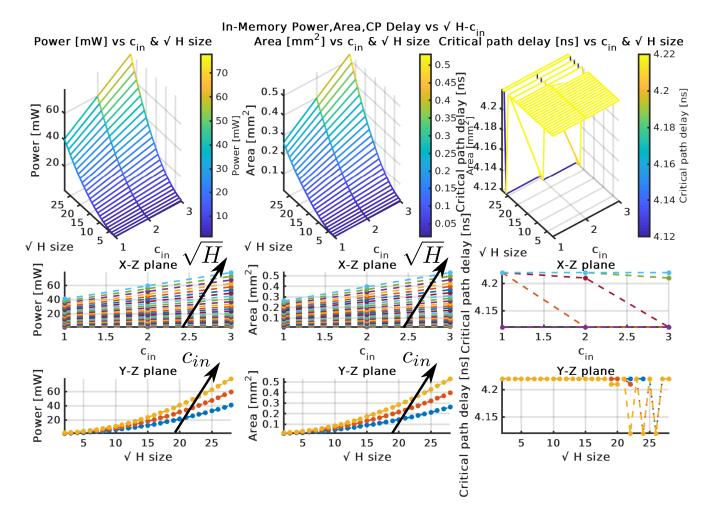

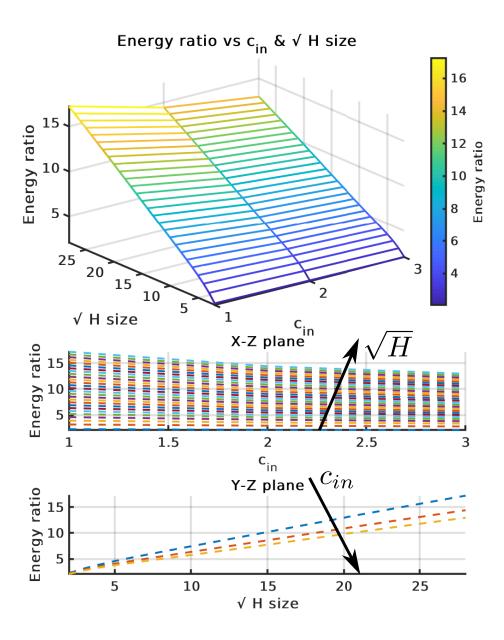

- 6. Synthesis Place&Route: performance results are provided for the models analyzed in the verification part. Moreover, by performing several synthesis, a parametric sweep is performed on the key parameters of the neural network (such as <u>IFMAP</u> sizes, <u>OFMAP</u> sizes, contemporary input channels and so on), to evaluate the trend of Power, Area, Timing and energy for both In-Memory and <u>OOM</u> architectures respectively. Roughly comparisons with the state-of-the-art are performed in this part;

- 7. Conclusions and future work: conclusions and improvements are proposed.

# Table of contents

### Acknowledgments

| 1 | Stat | te of t | he art                                                                | 1  |

|---|------|---------|-----------------------------------------------------------------------|----|

|   | 1.1  | Introd  | luction                                                               | 1  |

|   |      | 1.1.1   | Artificial neural network                                             | 1  |

|   |      | 1.1.2   | Convolutional neural networks                                         | 7  |

|   |      | 1.1.3   | Binary neural network                                                 | 11 |

|   |      | 1.1.4   | Backpropagation algorithm                                             | 13 |

|   | 1.2  | Softwa  | are based neural networks                                             | 23 |

|   |      | 1.2.1   | ImageNet Classification with Deep Convolutional Neural Net-           |    |

|   |      |         | works                                                                 | 23 |

|   |      | 1.2.2   | XNOR-Net: ImageNet Classification Using Binary Convolu-               |    |

|   |      |         | tional Neural Networks                                                | 28 |

|   |      | 1.2.3   | BinaryConnect: Training Deep Neural Networks with binary              |    |

|   |      |         | weights during propagations                                           | 32 |

|   |      | 1.2.4   | A Ternary Weight Binary Input Convolutional Neural Net-               |    |

|   |      |         | work: Realization on the Embedded Processor                           | 34 |

|   | 1.3  | MTJ-    | Based BNN                                                             | 41 |

|   |      | 1.3.1   | A Multilevel Cell <u>STT</u> - <u>MRAM</u> -Based Computing In-Memory |    |

|   |      |         | Accelerator for Binary Convolutional Neural Network                   | 41 |

|   |      | 1.3.2   | Energy Efficient In-Memory Binary Deep Neural Network Ac-             |    |

|   |      |         | celerator with Dual-Mode SOT - MRAM                                   | 46 |

|   |      | 1.3.3   | A Logic-in-Memory Design with 3-Terminal Magnetic Tunnel              |    |

|   |      |         | Junction Function Evaluators for Convolutional Neural Net-            |    |

|   |      |         | works                                                                 | 50 |

|   | 1.4  | RRAN    | M Based                                                               | 54 |

|   |      | 1.4.1   | The application of Non-volatile Look-up-table Operations based        |    |

|   |      |         | on Multilevel-cell of Resistance Switching Random Access Mem-         |    |

|   |      |         | ory                                                                   | 55 |

|   |      | 1.4.2   | XNOR-RRAM: A Scalable and Parallel Resistive Synaptic Ar-             |    |

|   |      |         | chitecture for Binary Neural Networks                                 | 58 |

Ι

|   |      | 1.4.3             | MAGIC-Memristor-Aided Logic                                                                                                 | . 63  |

|---|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|

|   |      | 1.4.4             | Mixed-precision architecture based on computational memory                                                                  |       |

|   |      |                   | for training deep neural networks                                                                                           | . 65  |

|   |      | 1.4.5             | A hardware neural network for handwritten digits recognition                                                                |       |

|   |      |                   | using binary <u>RRAM</u> as synaptic weight element                                                                         | . 67  |

|   |      | 1.4.6             | Challenges of emerging memory and memristor based circuits:                                                                 |       |

|   |      |                   | Nonvolatile logics, IoT security, deep learning and neuromor-                                                               |       |

|   |      |                   | phic computing                                                                                                              | . 69  |

|   | 1.5  | SRAM              | $f based \dots \dots$ |       |

|   |      | 1.5.1             | In-Memory Area-Efficient Signal Streaming Processor Design                                                                  |       |

|   |      |                   | for Binary Neural Networks                                                                                                  | . 72  |

|   |      | 1.5.2             | Deep learning consideration with novel approach - look-up-                                                                  |       |

|   |      |                   | table based processing conjugated memory                                                                                    | . 77  |

|   |      | 1.5.3             | A digital neurosynaptic core using embedded crossbar memory                                                                 |       |

|   |      |                   | with 45pJ per spike in 45nm                                                                                                 | . 80  |

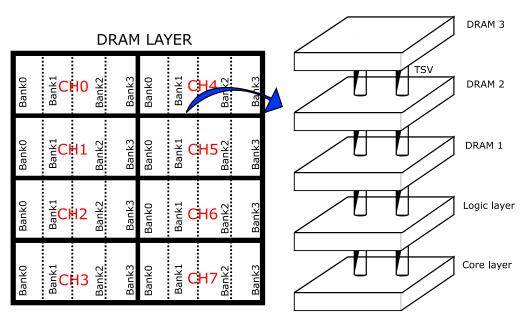

|   | 1.6  | DRAM              | A Based                                                                                                                     | . 84  |

|   |      | 1.6.1             | XNOR-POP: A processing-in-memory architecture for binary                                                                    |       |

|   |      |                   | Convolutional Neural Networks in Wide-IO2 DRAMs                                                                             | . 84  |

|   | 1.7  | $\underline{OOM}$ | implementations                                                                                                             | . 89  |

|   |      | 1.7.1             | Energy-Efficient Hybrid Stochastic-Binary Neural Networks                                                                   |       |

|   |      |                   | for Near-Sensor Computing                                                                                                   | . 89  |

|   |      | 1.7.2             | Towards Near Data Processing of Convolutional Neural Net-                                                                   |       |

|   |      |                   | works                                                                                                                       | . 94  |

|   |      | 1.7.3             | Chain-NN: An energy-efficient 1D chain architecture for ac-                                                                 |       |

|   |      |                   | celerating deep convolutional neural networks                                                                               | . 97  |

|   |      | 1.7.4             | An Energy-Efficient Architecture for Binary Weight Convolu-                                                                 |       |

|   |      |                   | tional Neural Networks                                                                                                      | . 101 |

| 2 | Cor  | npariso           |                                                                                                                             | 108   |

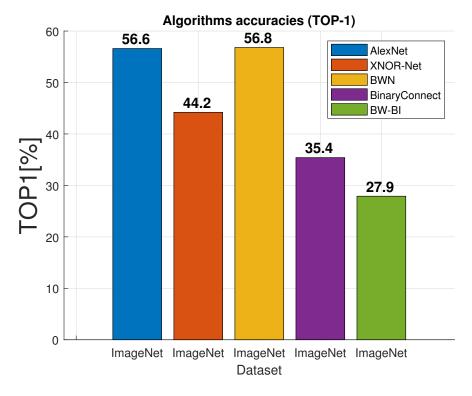

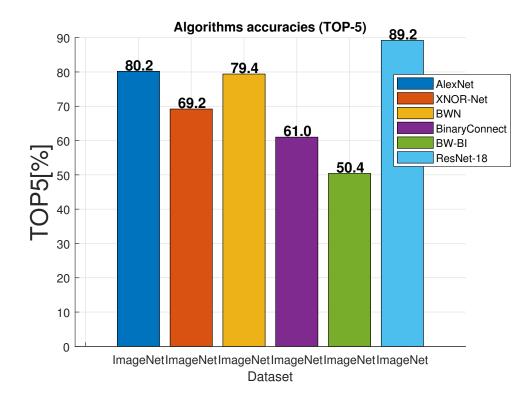

| 4 | 2.1  | -                 | thm accuracies $\ldots$                                                                                                     |       |

|   | 2.1  | 0                 | Performance comparisons                                                                                                     |       |

|   |      | 2.1.1<br>2.1.2    | Conclusions                                                                                                                 |       |

|   |      | 2.1.2             |                                                                                                                             | . 129 |

| 3 | Soft | ware i            | mplementation                                                                                                               | 130   |

|   | 3.1  | Netwo             | rk model                                                                                                                    | . 130 |

|   | 3.2  | Netwo             | rk's computational model                                                                                                    | . 133 |

|   |      | 3.2.1             | Python code                                                                                                                 | . 136 |

| , |      |                   | · · · · · · · · · · · · · · · · · · ·                                                                                       |       |

| 4 |      |                   | implementations                                                                                                             | 147   |

|   | 4.1  |                   | implementation                                                                                                              |       |

|   |      | 4.1.1             | Max pooling layer                                                                                                           | . 148 |

|    |       | 4.1.2 Convolutional and fully-connected layers | . 156 |

|----|-------|------------------------------------------------|-------|

|    |       | 4.1.3 Flatten layer                            | . 190 |

|    |       | 4.1.4 Neural network entity                    | . 191 |

|    |       | 4.1.5 VHDL implementation                      | . 199 |

|    | 4.2   | In-memory implementation                       | . 206 |

|    |       | 4.2.1 Convolutional/fully connected layer      | . 206 |

|    | 4.3   | Memories' sizes                                |       |

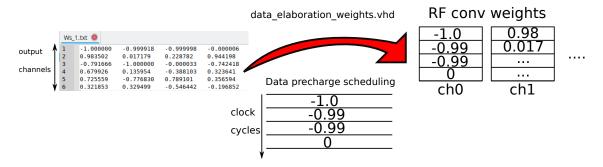

|    |       | 4.3.1 Parameters precharging                   | . 216 |

|    |       | 4.3.2 Memory required                          | . 217 |

|    | 4.4   | Timing comparison                              |       |

|    |       | 4.4.1 $OOM$ implementation                     | . 219 |

|    |       | 4.4.2 In-memory implementation                 |       |

|    |       | 4.4.3 General cases                            | . 223 |

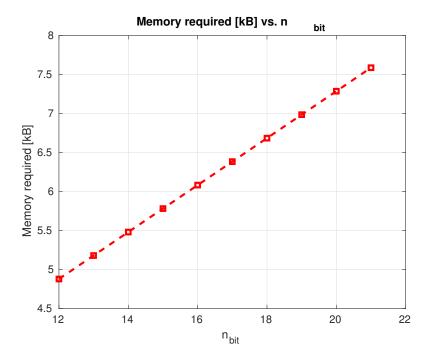

|    | 4.5   | Choosing the number of bits $(n\_bit)$         | . 234 |

| 5  | Ver   | ification                                      | 236   |

|    | 5.1   | VHDL's output                                  |       |

|    | 5.2   | MATLAB's output                                |       |

|    | 5.3   | Other neural network models                    |       |

|    |       | 5.3.1 MLP Implementation                       |       |

|    |       | 5.3.2 Fashion-MNIST neural network model       |       |

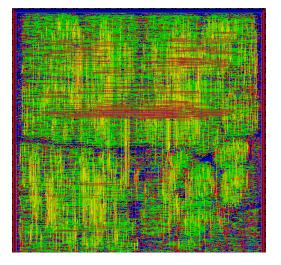

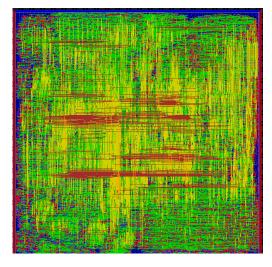

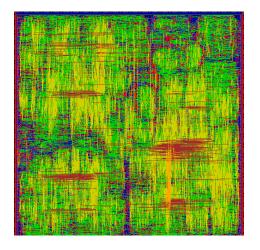

| 6  | Svn   | thesis - Place & Route                         | 256   |

|    | 6.1   | Original architecture                          | . 256 |

|    |       | 6.1.1 Synthesis                                |       |

|    |       | 6.1.2 Place & Route                            |       |

|    | 6.2   | MLP architecture                               |       |

|    |       | 6.2.1 Synthesis & Place-Route chips            |       |

|    | 6.3   | Fashion-MNIST CNN                              |       |

|    | 6.4   | General cases                                  | . 271 |

|    | 6.5   | State-of-the-art comparisons                   |       |

|    |       | 6.5.1 Number of neurons                        |       |

|    |       | 6.5.2 Results                                  |       |

| _  | C     |                                                | 000   |

| 7  |       | nclusions and future work                      | 292   |

|    | 7.1   | Future work                                    | . 292 |

| Bi | bliog | graphy                                         | 294   |

# List of figures

| 1    | Convolutional neural network used as starting model. MNIST database          |    |

|------|------------------------------------------------------------------------------|----|

|      | is used, which is composed by handwritten digits in range $0 \div 9$         | 5  |

| 2    | Classical implementation. In <b>Binary input RF</b> , the binary signs       |    |

|      | are precharged and then fetched one row per clock cycle to compute           |    |

|      | the XNORs. The incoming bit selected goes to pop-counting unit               | 6  |

| 3    | In-Memory implementation. Inputs are precharged into the memory              |    |

|      | cells and the XNOR gates perform the xnor operation between the              |    |

|      | binary weights $(W_0, W_1,)$ and inputs. Xnor results are then fetched       |    |

|      | from pop-counting parts.                                                     | 6  |

| 4    | Validation flow of the neural network model                                  | 7  |

| 1.1  | Neuron's structure                                                           | 1  |

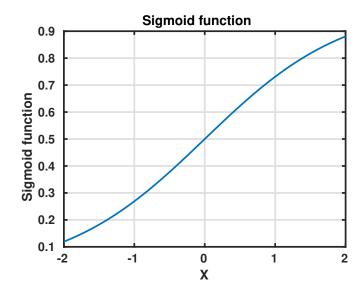

| 1.2  | Sigmoid activation function                                                  | 3  |

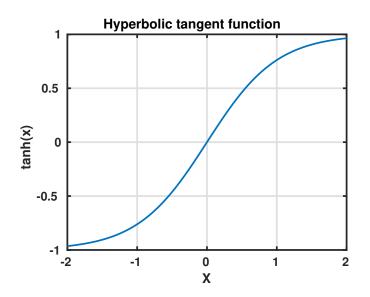

| 1.3  | Hyperbolic tangent activation function                                       | 3  |

| 1.4  | ReLU activation function                                                     | 4  |

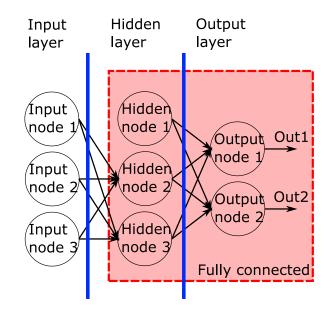

| 1.5  | Neural network example from [32]                                             | 5  |

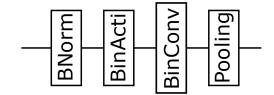

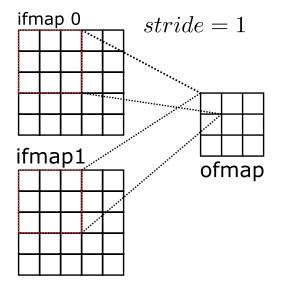

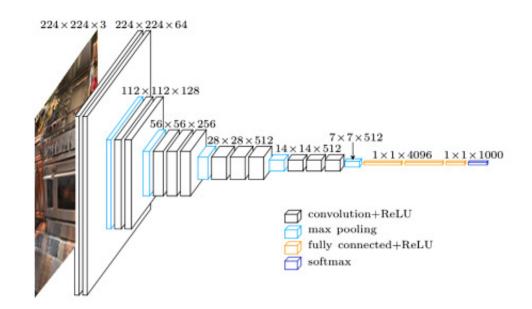

| 1.6  | CNN example from [33]. There are several layers such as convolution,         |    |

|      | pooling, fully connected (already described) and normalization that          |    |

|      | can be trained in order to classify the input. In this case, an image        |    |

|      | is used but the <u>CNN</u> s can be used for different applications, such as |    |

|      | natural language and speech recognition [34]                                 | 7  |

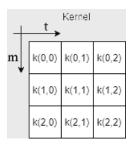

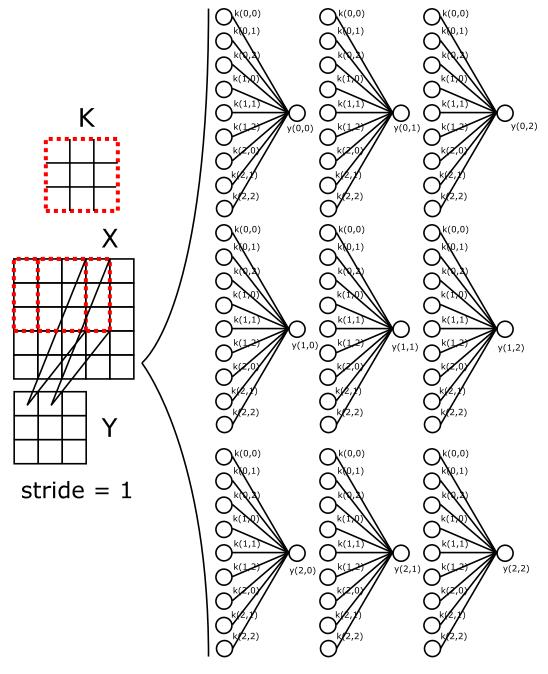

| 1.7  | Example of a kernel in a <u>CNN</u> with 3x3 size                            | 7  |

| 1.8  | Convolution example with FC network. The weights used in the fully           |    |

|      | connected part are the same of the kernel.                                   | 9  |

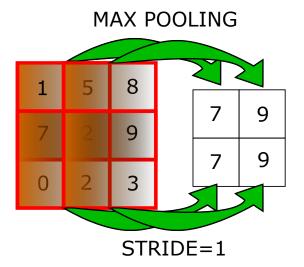

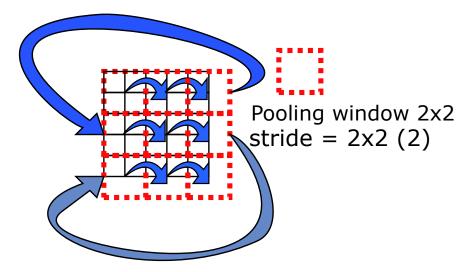

| 1.9  | Example of max-pooling 2x2 and <u>stride</u> of 1 [35]                       | 10 |

| 1.10 |                                                                              |    |

|      | s/activations.                                                               | 11 |

| 1.11 | Binary XNOR-Popcount based computation.                                      | 12 |

|      | BNN implementation. The green boxes are fully connected layers               | 13 |

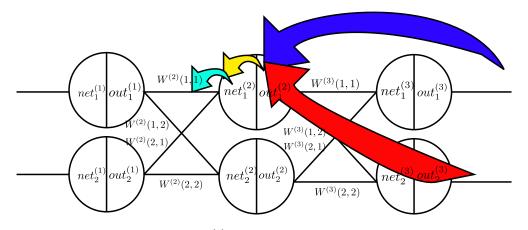

|      | Neural network example. It is analyzed an <u>MLP</u> , in order to simplify  |    |

|      | the explanations. The same approach can be used in <u>CNN</u> s              | 14 |

| 1.14 | First output neuron                                                          | 15 |

|      |                                                                              |    |

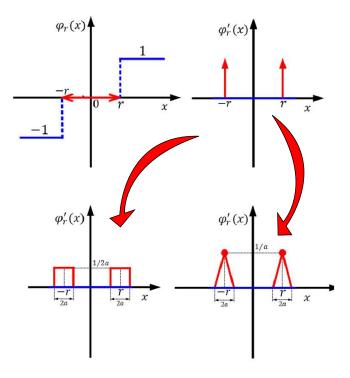

|      | Approximation of the derivative of the sign function from $[36]$                                                                  | 17  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.16 | Example of $w_1$ ( $W^{(2)}(1,1)$ ) computation from [10]. Biases are not                                                         |     |

|      | reported because they are not used in the computation                                                                             | 19  |

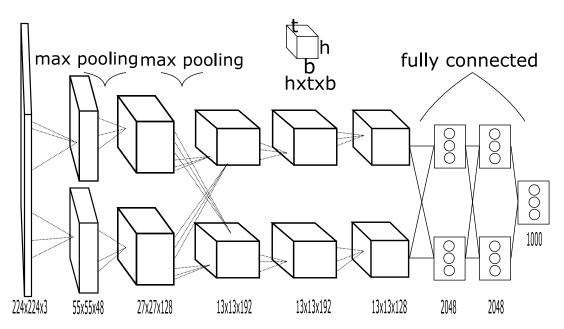

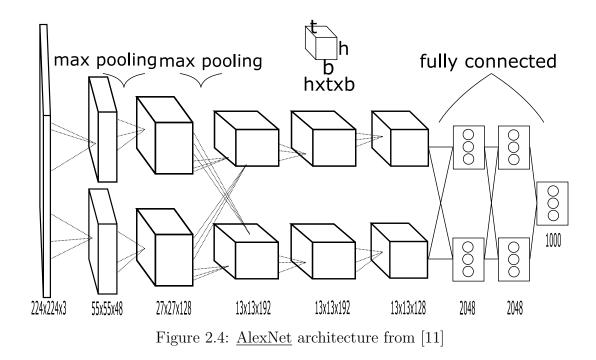

| 1.17 | <u>AlexNet</u> architecture from [11]. The architecture is divided into two                                                       |     |

|      | parts handled by the two GPUs respectively, with some layers in                                                                   |     |

|      | which they communicate with a DMA (direct memory access) ap-                                                                      |     |

|      | proach. The two parts are identical and so the dimensions reported                                                                |     |

|      | are the same.                                                                                                                     | 24  |

| 1.18 | Example of a non-overlapped pooling and pooling procedural steps $\ .$                                                            | 25  |

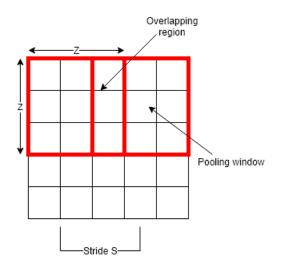

| 1.19 | An example of a 3x3 window with an overlapping pooling with <u>stride</u>                                                         |     |

|      | s = 2 and $z = 3$                                                                                                                 | 26  |

| 1.20 | Example of Dropout technique from [37]                                                                                            | 27  |

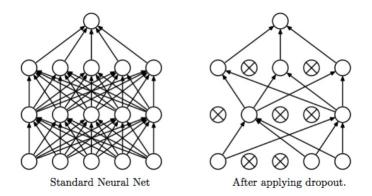

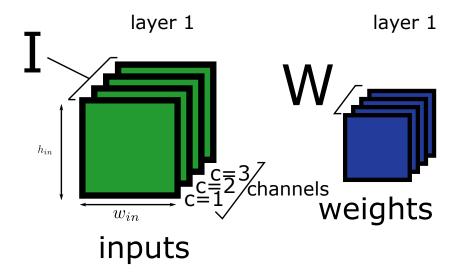

| 1.21 | Weights and inputs represented as tensors                                                                                         | 29  |

| 1.22 | Structure of the XNOR-Net from [12]                                                                                               | 31  |

| 1.23 | Example of the 2D convolutional operation for the ternary weight and                                                              |     |

|      | binary input                                                                                                                      | 38  |

| 1.24 | VGG16 architecture from [38]. It is composed by 16 layers and it                                                                  |     |

|      | is able to reach up to $70\%$ on top-1 and $90\%$ in top-5 recognition                                                            |     |

|      | accuracies respectively on <u>ImageNet</u>                                                                                        | 39  |

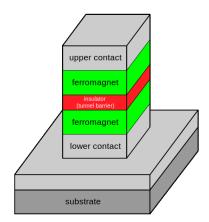

| 1.25 | Magnetic tunnel junction (schematic) from [6]                                                                                     | 41  |

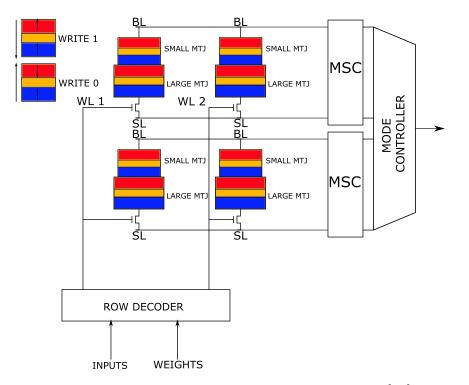

| 1.26 | Cell structure and example of a $2x2$ array from [15]. <u>MSC</u> stands                                                          |     |

|      | for "modified sensing circuit" and it is able to do some computations                                                             |     |

|      | based on the current of the source/bit lines. The mode controller                                                                 |     |

|      | is able to choose which operation to perform, while the row decoder                                                               |     |

|      | handles the word lines. In order to write into the $\underline{MTJ}$ , a current has                                              |     |

|      | to flow through it, and the direction is expressed here. If "1" has to                                                            |     |

|      | be stored, the current has to magnetize the layers in a parallel way,                                                             |     |

|      | resulting less $\underline{MTJ}$ resistance (LRS), so a positive voltage is applied                                               |     |

|      | between BL and SL; otherwise, with "0", the magnetizations must                                                                   | 10  |

| 1.05 | have antiparallel direction.                                                                                                      | 42  |

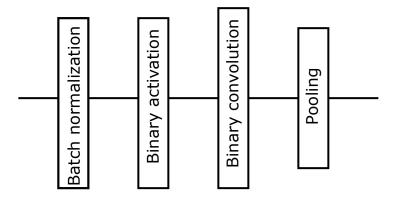

|      | CNN architecture used in [15]                                                                                                     | 44  |

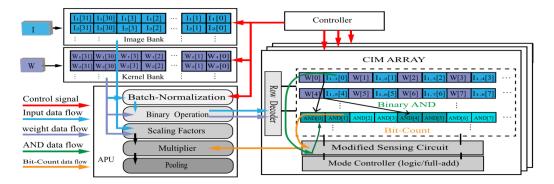

| 1.28 | BCNN Accelerator from [15]. The logical computations are performed                                                                |     |

|      | inside the memory array, while other intensive operations, such as                                                                |     |

|      | batch normalization or scaling factors computations are performed                                                                 | 4.4 |

| 1.00 | outside the memory in a separate unit.                                                                                            | 44  |

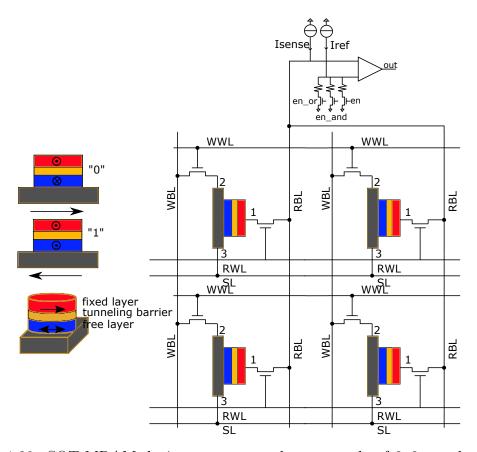

| 1.29 | <u>SOT-MRAM</u> device structure and an example of $2x2$ crossbar array                                                           | 17  |

| 1.90 | from [16]                                                                                                                         | 47  |

| 1.30 | Inputs and weights are in ImageBanks and then it will be computed<br>the binary compution by performing on In Memory AND logic on |     |

|      | the binary convolution by performing an In-Memory AND logic op-                                                                   | 40  |

|      | eration followed by a Bitcounting. Source: [16]                                                                                   | 49  |

| 1.31 | Crosspoint array architecture from [17]; two different types of <u>MTJ</u> s are used in [17]: the synaptic <u>MTJ</u> s are the classical ones, with two                                                                                                                                                                                                               |          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | possible values of resistances $(\overline{R_P} \text{ and } R_{AP})$ ; while the thresholding                                                                                                                                                                                                                                                                          |          |

|      | MTJs are the ones discussed so far. The last MTJ (indicated by an                                                                                                                                                                                                                                                                                                       |          |

|      | arrow) acts as function evaluator and it implements the activation                                                                                                                                                                                                                                                                                                      |          |

|      | function of the neuron. This crossbar can be seen as an array of                                                                                                                                                                                                                                                                                                        |          |

|      | variable resistances.                                                                                                                                                                                                                                                                                                                                                   | 52       |

| 1.32 | 1T1R configuration from [39]                                                                                                                                                                                                                                                                                                                                            | 54       |

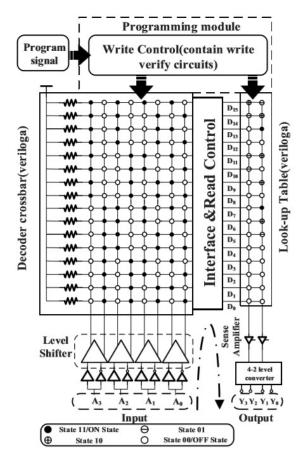

| 1.33 | Crossbar array cell's organization from [18]. Each memory cell is a <u>RRAM</u> .                                                                                                                                                                                                                                                                                       | 55       |

| 1.34 | Architecture of the multiplier based on <u>MLC</u> <u>RRAM</u> from [18] $\ldots$                                                                                                                                                                                                                                                                                       | 56       |

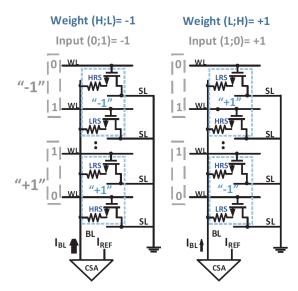

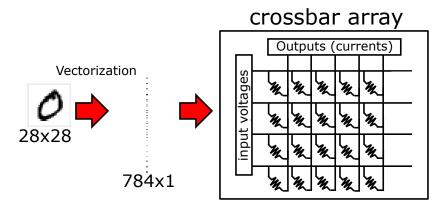

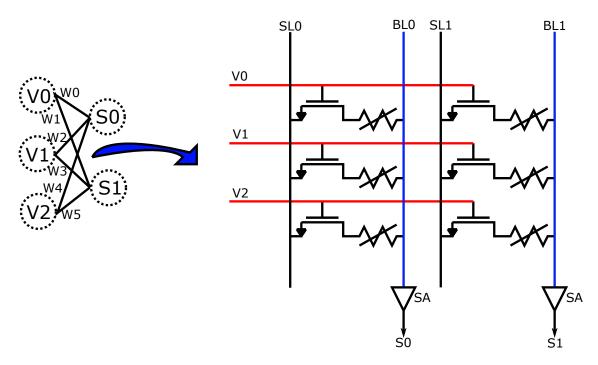

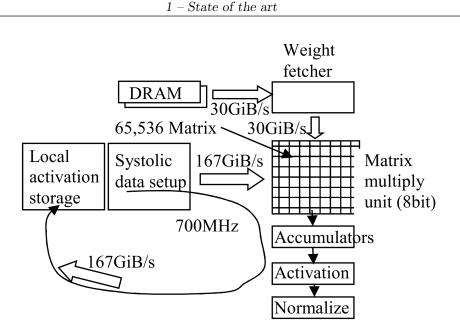

|      | Bit cell structure from [19]                                                                                                                                                                                                                                                                                                                                            | 59       |

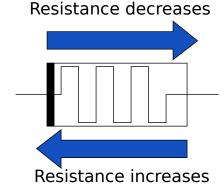

|      | Memristor behavior from [20] depending on the current flow direction.                                                                                                                                                                                                                                                                                                   | 63       |

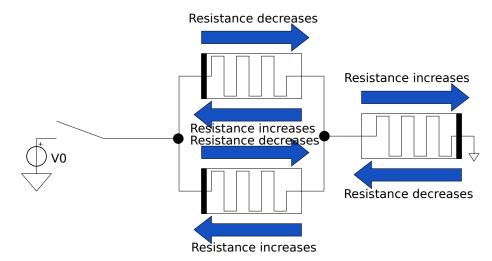

|      | NOR Gate with memristors from [20]                                                                                                                                                                                                                                                                                                                                      | 63       |

| 1.38 | Memristor-based crossbar array: configuration for NOR logic gate                                                                                                                                                                                                                                                                                                        |          |

|      | from [20]                                                                                                                                                                                                                                                                                                                                                               | 64       |

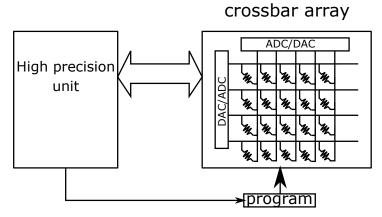

| 1.39 | Principle scheme of the mixed precision architecture. Source: $[21]$                                                                                                                                                                                                                                                                                                    | 65       |

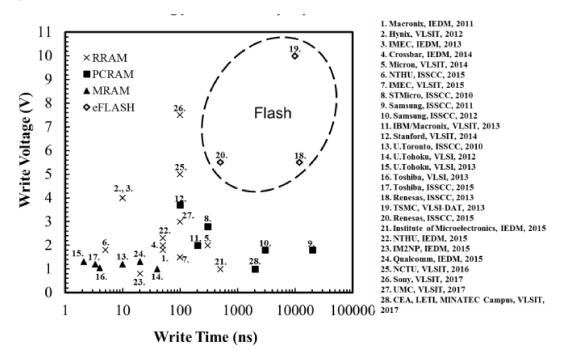

| 1.40 | Network structure from [22]                                                                                                                                                                                                                                                                                                                                             | 68       |

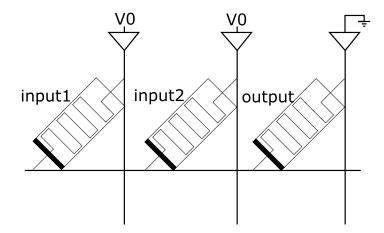

| 1.41 | Write voltages of different technologies. Source: [23]                                                                                                                                                                                                                                                                                                                  | 69       |

| 1.42 | Simplified 3-2 neural network implemented with RRAMs <u>1T1R</u> con-<br>figuration. Source: [23]                                                                                                                                                                                                                                                                       | 71       |

| 1.43 | An example of a 3-2 <u>BNN</u> from [24] and the transformation into a fully<br>connected configuration. The Synapse configuration table is reported<br>indicating the meaning of the connections. The fully connected net-<br>work has been implemented considering also bias and mask signals.<br>At the end, three popcounting results will be added together and it |          |

|      | is taken the sign of the result, that defines the output.                                                                                                                                                                                                                                                                                                               | 73       |

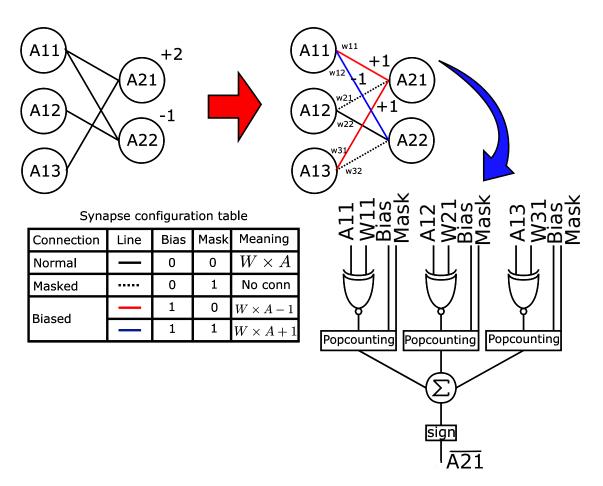

| 1.44 | DL calculation structure at 700MHz from [25]                                                                                                                                                                                                                                                                                                                            | 78       |

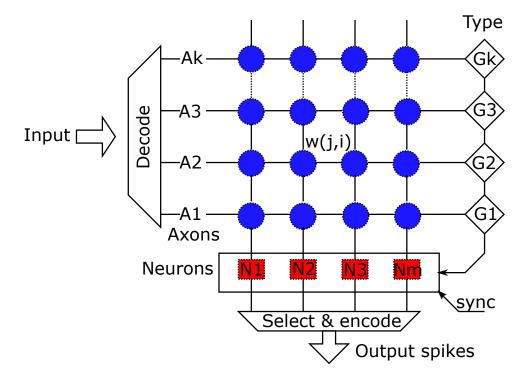

| 1.45 | Structure of the neurosynaptic core from [26]                                                                                                                                                                                                                                                                                                                           | 81       |

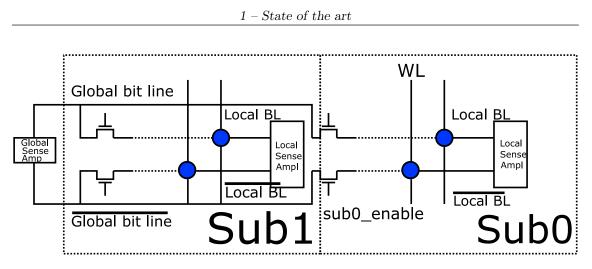

| 1.46 | Architecture proposed by [27]. Source: [27]                                                                                                                                                                                                                                                                                                                             | 84       |

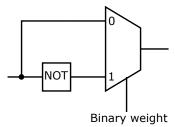

| 1.47 | Building blocks of a XNOR-NET from [27]                                                                                                                                                                                                                                                                                                                                 | 85       |

| 1.48 | Bank structure. Source: [27]                                                                                                                                                                                                                                                                                                                                            | 86       |

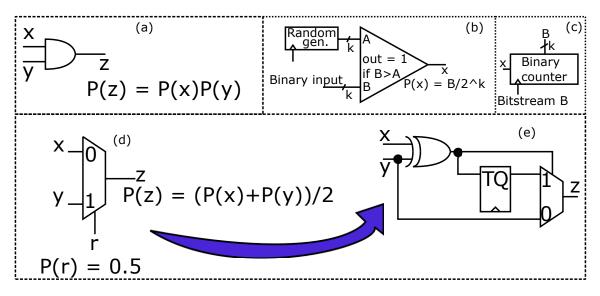

| 1.49 | (a) Multiplier; (b) Binary - Stochastic converter; (c) Stochastic -<br>Binary converter; (d) Multiplexer adder with random input r; (e)                                                                                                                                                                                                                                 | 00       |

| 1 50 | Improved version of the adder, without the random input. Source: [28]                                                                                                                                                                                                                                                                                                   | 90       |

|      | Example of computations of the new stochastic adder. Source: [28] .                                                                                                                                                                                                                                                                                                     | 92       |

|      | Architecture structure. Source: [29]                                                                                                                                                                                                                                                                                                                                    | 95<br>95 |

| 1.52 | Complete and partial result computation. Source: [29]                                                                                                                                                                                                                                                                                                                   | 96       |

| 1.53 | Chain NN architecture with $k = 3$ , where k is the kernel size. 9 pro-                                            |

|------|--------------------------------------------------------------------------------------------------------------------|

|      | cessing elements are needed because for each PE, a different weight                                                |

|      | is used. Inside a PE there are a MAC and a register and eventu-                                                    |

|      | ally the corresponding outputs can be pipelined, in order to improve                                               |

|      | performance (red dashed lines). Example of computation. Source: [30] 99                                            |

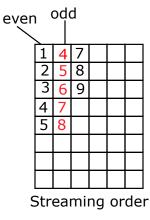

| 1.54 | Streaming order in dual channel architecture. Source: [30] 100                                                     |

|      | Architecture. Source: [31]                                                                                         |

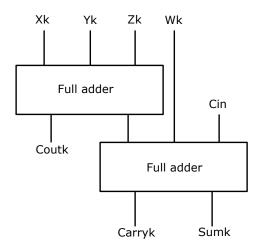

| 1.56 | 4:2 compressors used in [31]                                                                                       |

|      | Approximate multiplier. Source: [31]                                                                               |

| 2.1  | Comparison among different algorithms (ImageNet): top-1. <u>AlexNet</u> :                                          |

|      | [11], XNOR-Net: [12], BWN: [12], BinaryConnect: [13]. BW-BI: [13] 109                                              |

| 2.2  | top-5 errors for the same dataset ImageNet. <u>AlexNet</u> : [11], XNOR-                                           |

|      | Net: [12], BWN: [12], BinaryConnect: [13]. BW-BI: [13] 110                                                         |

| 2.3  | Accuracy comparison for <u>CIFAR-10</u> dataset. XNOR-Net: [12], BWN:                                              |

|      | [12], BinaryConnect: [13], Ternary: [14]                                                                           |

| 2.4  | <u>AlexNet</u> architecture from $[11]$                                                                            |

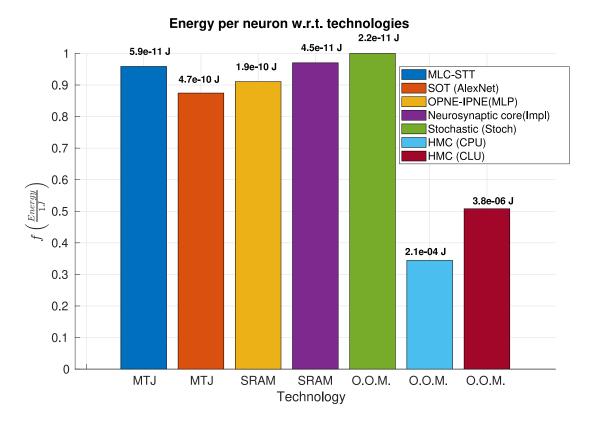

| 2.5  | Energy comparison: the higher is better. <u>MLC-STT</u> : [15], <u>SOT</u> : [16],                                 |

|      | <u>OPNE-IPNE</u> : [40], Neurosynaptic core: [26], Stochastic: [28], CPU-                                          |

|      | CLU: [29]                                                                                                          |

| 2.6  | Macro-pipeline structure [40]. Once <u>OPNE</u> terminates, <u>IPNE</u> starts                                     |

|      | producing a serial output: this is elaborated by the following <u>OPNE</u> . 119                                   |

| 2.7  | Delay comparison: the higher is better. $\underline{MLC}$ - $\underline{STT}$ [15], $\underline{SOT}$ [16],        |

|      | <u>OPNE-IPNE</u> [40], Neurosynaptic core [26], XNOR- <u>RRAM</u> [19], HMC                                        |

|      | [29], Chain-NN [30], Energy-efficient [31]                                                                         |

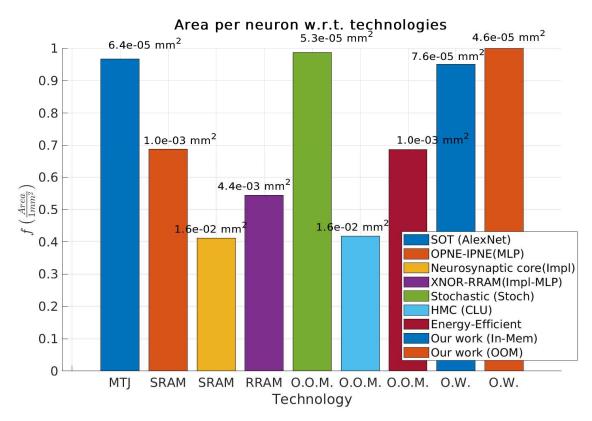

| 2.8  | Area comparison: the higher is better. <u>SOT</u> [16], <u>OPNE-IPNE</u> [40],                                     |

|      | Neurosynaptic core [26], XNOR- <u>RRAM</u> [19] (MLP), Stochastic [28],                                            |

|      | HMC [29], Energy-efficient [31]                                                                                    |

| 3.1  | Neural network model                                                                                               |

| 3.2  | Xnor net computation example                                                                                       |

| 3.3  | Fully connected layer - toy example                                                                                |

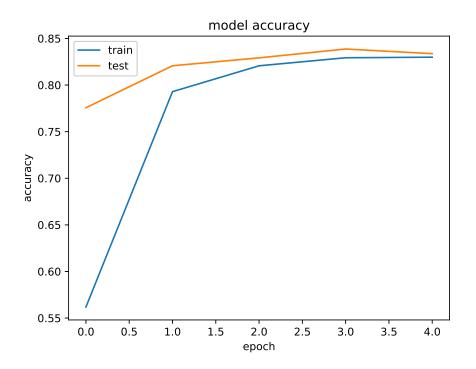

| 3.4  | Accuracies' trend over 5 epochs and batch size of 10                                                               |

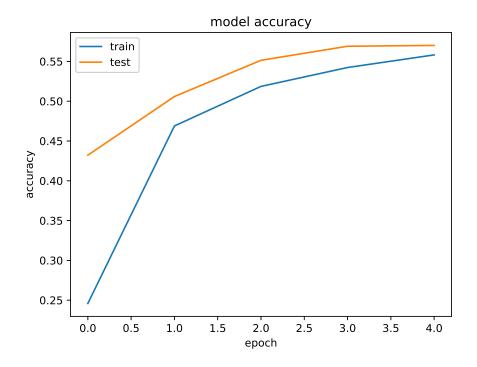

| 3.5  | Accuracies' trend over 5 epochs and batch size of 100                                                              |

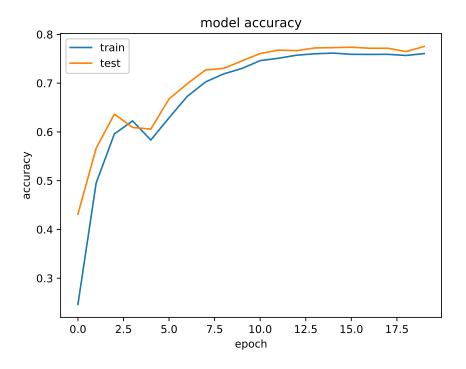

| 3.6  | Accuracies' trend over 20 epochs and batch size of 100                                                             |

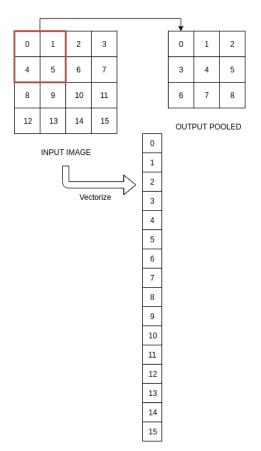

| 3.7  | Example of <b>K</b> and $\alpha_i$ computation in the fully connected layer 145                                    |

| 3.8  | <u>MLP</u> network used to test the approximation drawback. This struc-                                            |

|      | ture is able to achieve an accuracy of around 97% after 20 training                                                |

|      | epochs                                                                                                             |

| 4.1  | Neural network model used as starting point                                                                        |

| 4.2  | Max pooling: indexing example with $w_{in} = 4$ , $w_{filter} = 2$ and stride                                      |

|      | $= 1 \dots $ |

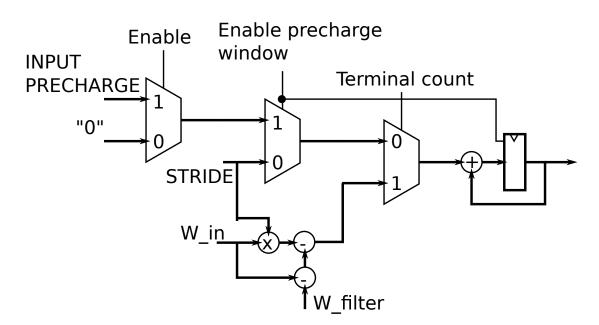

| 4.3  | Input selection circuit                                                                                            |

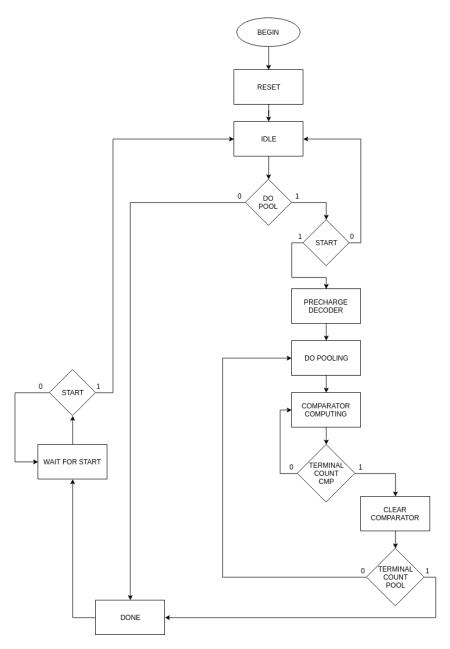

| 4.4  | Max pooling layer FSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 153 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

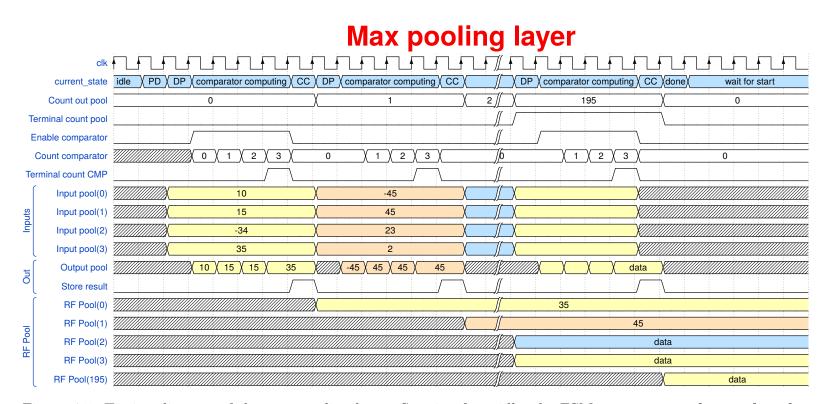

| 4.5  | Timing diagram of the max pooling layer. Starting from idle, the FSM moves to <b>precharge decoder</b> (PD), in which the external decoder is precharged with its initial values. During <b>do pooling</b> , the inputs are provided to the max pooling layer and the computation starts with <b>comparator computing</b> , in which <b>Count comparator</b> is increased until it reaches $w_{filter(pool)}^2 - 1$ value, that in the neural network model depicted in Figure 4.1 is equal to 3 (4-1). When the <b>terminal count CMP</b> is asserted, the FSM migrates to <b>clear comparator</b> (CC), in which the stored value inside the comparator is reset to the minimum. The result is stored inside the <b>RF Pool</b> , which is placed outside the chip (see Figure 4.27) and it is addressed by <b>count out pool</b> . The entire procedure is repeated until <b>count out pool</b> has not reached the <b>terminal count pool</b> , which is asserted when <b>count out pool</b> is equal to $w_{out(pool)}^2$ , that in the neural network model in Figure 4.1 is 196. At this point, <b>done</b> and <b>wait for start</b> are reached, where |     |

|      | FSM waits for a new start signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 155 |

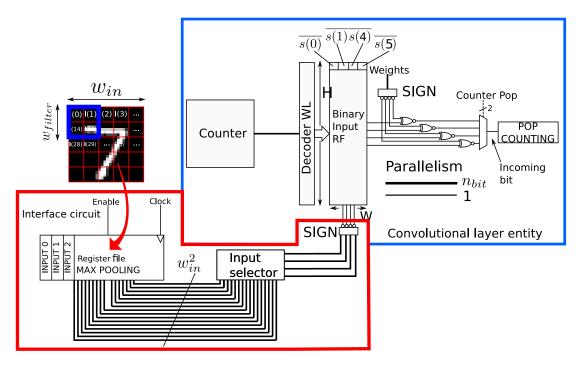

| 4.6  | Example of a $w_{in} = 4, w_{filter} = 2, stride = 1$ input selection and<br>saving circuits. The inputs are selected from the input selector and<br>their sign is stored into the register file $(\overline{s(0)}, \overline{s(1)}, \overline{s(4)}, \overline{s(5)})$ . Then,<br>once the saving procedure is completed, the inputs are fetched from<br>the <b>Binary Input RF</b> and XNORed with weights' signs. The XNOR<br>results are selected from a multiplexer (Incoming bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 157 |

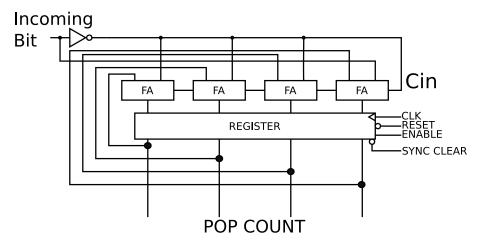

| 4.7  | Pop-counting circuit: 4 bits example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 158 |

| 4.8  | Multiple input channels architecture. The XNOR and pop-counting<br>units are replicated for a number of input channels times, obtaining<br>a parallel computation. Each channel contribution is added in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 159 |

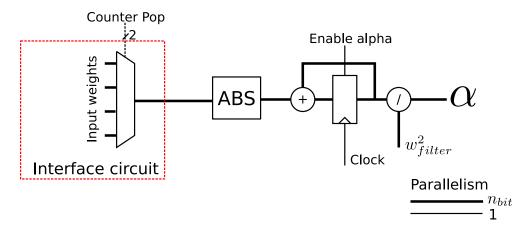

| 4.9  | Alpha computational unit: example with $w_{filter} = 2$ . The input multiplexer has been instatiated into an external unit, in order to reduce the total number of inputs of the chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 160 |

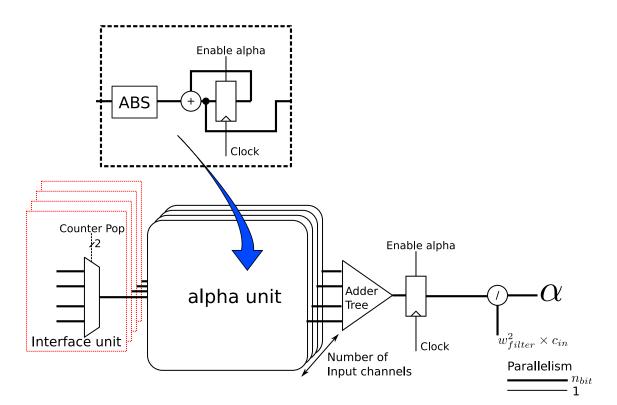

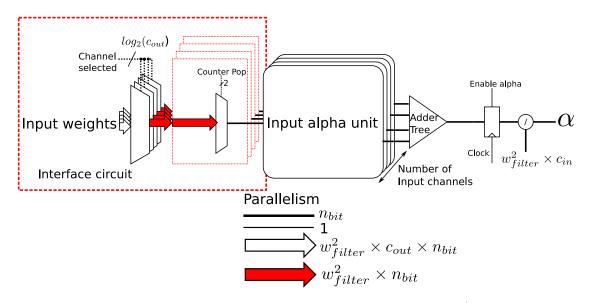

| 4.10 | Alpha computation unit in case of multiple input channels. An adder<br>tree adds all the multiplexed weights from the $c_{in}$ inputs. The last<br>division is performed also by the number of input channels. Re-timing<br>technique has been used for the loop register, in order to reduce the<br>critical path caused by an adder tree and a divider.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 161 |

| 4.11 | Alpha computation unit in case of multiple output/input channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

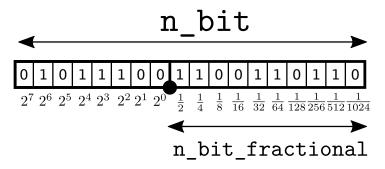

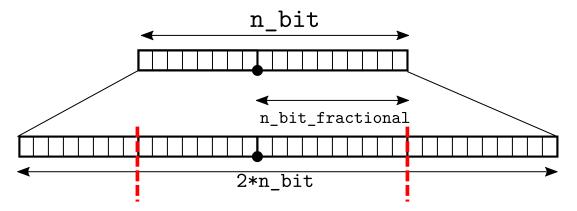

|      | Fixed point representation: example with $n_bit = 18$ and $n_bit_fractional$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | $= 10  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 163 |

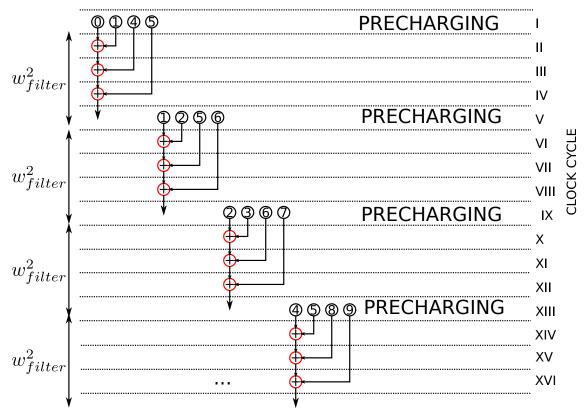

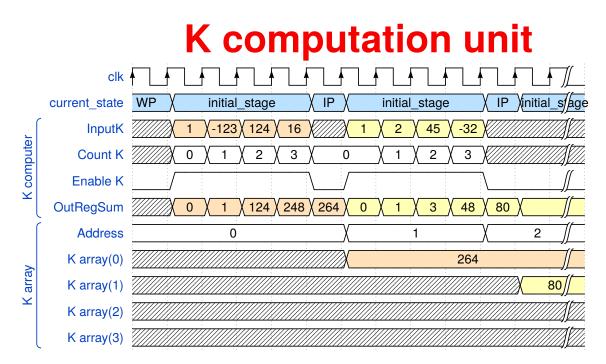

| <b>K</b> scheduling. Example with $w_{in} = 4$ and $w_{filter} = 2$ . Everytime a new data is precharged, <b>K</b> computation starts and lasts for $w_{filter}^2$ clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 165 |

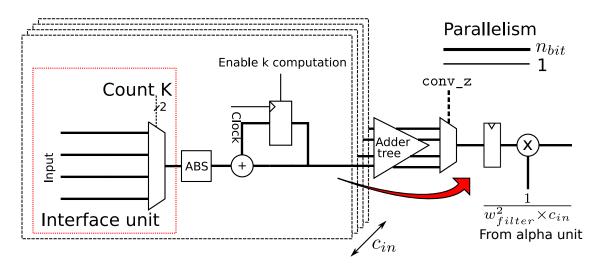

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Example of <b>K</b> unit with $w_{filter} = 2$ with multiple input channels. The input multiplexer has been integrated into an external unit in order to reduce the number of contemporary inputs into the architecture. Since <b>conv_z</b> is fixed, the multiplexer selects only one input per time: the register indicated by the red arrow has been moved from its original location by applying re-timing: this technique avoids to have multiple adders connected to the final multiplier, reducing the critical path delay. The last term $\left(\frac{1}{w_{filter}^2 \times c_{in}}\right)$ is taken directly from the alpha unit. | . 167 |

| Example of fully connected layer integration. The data precharging pattern is inverted to compute the outputs values of the neurons of and o1. $number\_of\_fc\_parameters$ indicates the number of input neurons that in this example is equal to 3. In the real case depicted in Figure 4.1, $number\_of\_fc\_parameters = 1014$                                                                                                                                                                                                                                                                                                           | . 168 |

| Fully connected layer scheduling. Inputs and weights are divided into<br>subgroups of L elements and precharged inside the <b>Binary Input</b><br><b>RF</b> . At each cycle, once the pop-counting has finished, a new set of<br>inputs/weights is precharged in the <b>Binary Input RF</b> and the pop-<br>counting part starts again. The register file <b>RF TMP Pop</b> holds the<br>temporary values of pop-counting and it is addressed by the counter:<br>the total number of registers used in <b>RF TMP Pop</b> is equal to the<br>number of output neurons that, as in Figure 4.1, it is equal to 10.                              | . 169 |

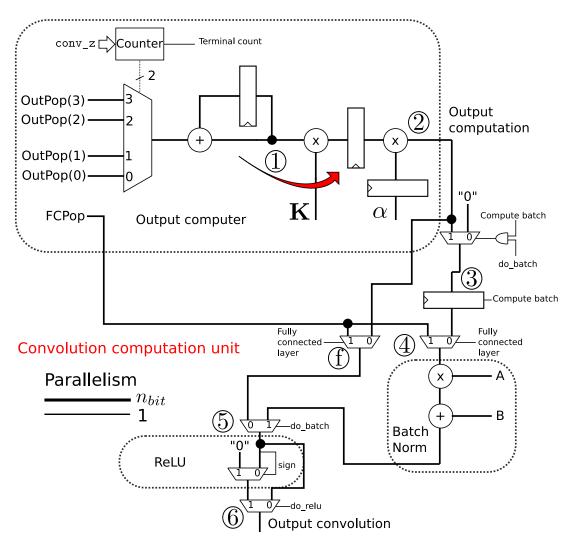

| Convolution computation unit. Example of a 4 input channels output computer unit, with batch normalization and ReLU. $\alpha$ is delayed by a register in order to reduce the critical path. A, B are the batch normalization terms. The path indicated by the red arrow has been retimed to reduce the critical path delay.                                                                                                                                                                                                                                                                                                                 | . 172 |

| Multiplication scheme: example with $n_bit=18$ and $n_bit_fractional = 10 \dots $                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 174 |

| Entire convolutional layer datapath: example with $C_{out} = 2$ , $C_{in} = 4$ .<br>The area highlighted by the red dashed line is implemented in an external unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 176 |

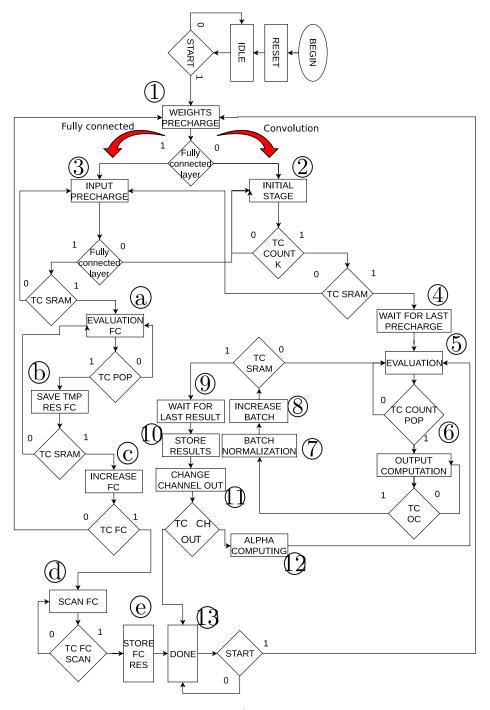

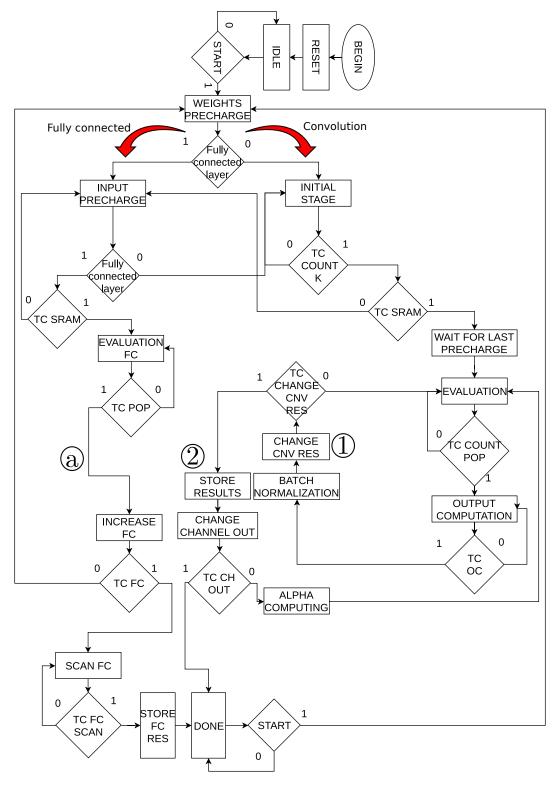

| FSM of the convolutional/fully connected layers. The term "TC" indicates terminal count.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 177 |

$\mathbf{17}$

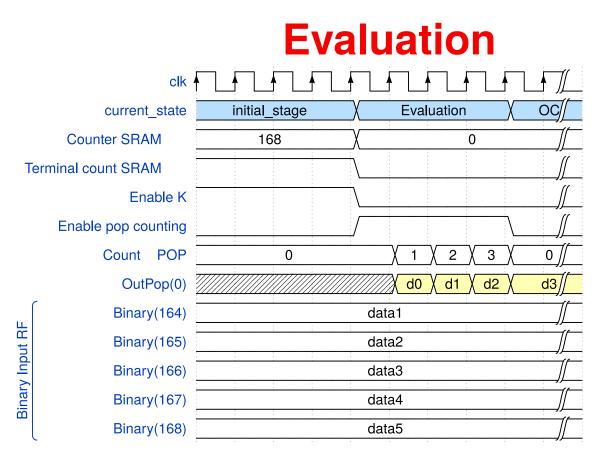

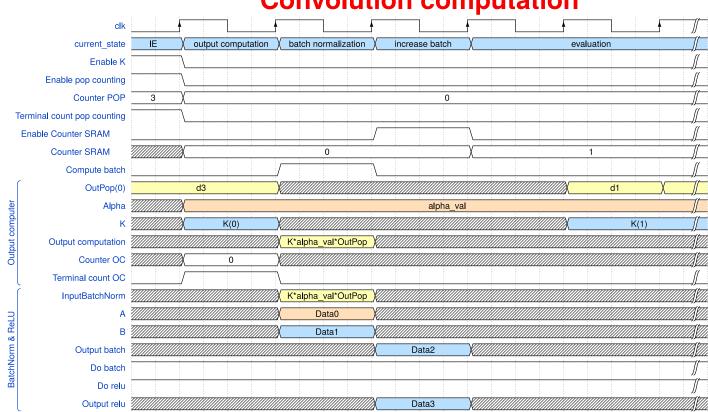

- 4.23 Timing diagram for the convolution computation. As it is possible to see, the FSM moves from **Evaluation** (IE) to **output computa**tion when terminal count pop counting is '1'. During output computation, the values of K (selected by the counter SRAM) and alpha are fed to the **output computer**, which performs the product between the **OutPop** result and these two values, obtaining **Output computation** (reference Figure 4.17). The FSM waits until **terminal count OC**, which is asserted when the **output computer** has scanned all the parallel input channels (Figure 4.17), so after  $c_{in}$  clock cycles. Since in the reference architecture depicted in Figure 4.1 there is only one parallel input channel, the FSM passes immediately to batch normalization state, which computes Batch Normalization/ReLU within a clock cycle. Moving to **increase batch** state, the **Counter SRAM** is enabled and the counting is increased, in order to consider another Binary input set from **Binary Input RF** and a new value of K, which is addressed by the counter itself. At the same time the convolution result is saved inside a temporary register file (**Temporary CNV RF** in (Figure 4.27)). The procedure

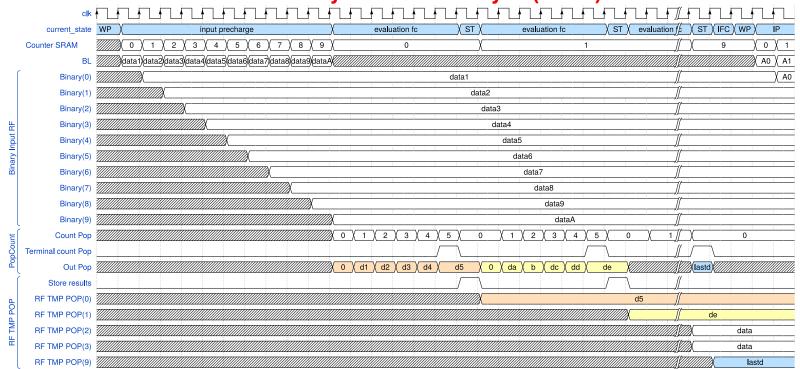

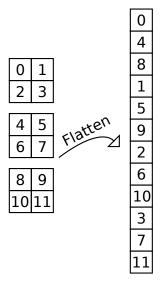

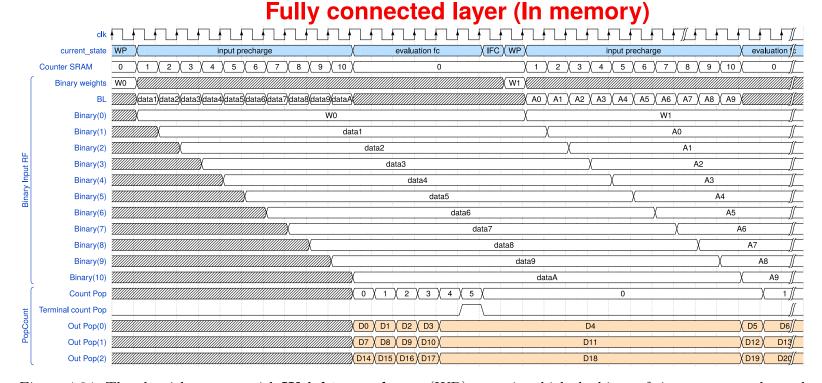

- 4.25 Timing diagram of the fully connected part. After weight precharge (WP), the FSM starts to save the binary values inside the **Binary Input RF** during **Input precharge**, as already discussed. After that, evaluation can start, in particular the first line addressed by **Counter SRAM** is pop-counted. The pop-counting procedure has a time duration equal to  $L \times t_{ck}$ , that in the neural network model depicted in Figure 4.1 is equal to  $6 \times t_{ck}$ . Once **Count Pop** has reached 5, the FSM moves to save tmp results fc (ST), in which the temporary result of the pop-counting procedure is saved inside the **RF TMP POP** (depicted in Figure 4.19) and the last register of the pop-counting unit is cleared (Figure 4.7). A new evaluation procedure starts, but now the second row of the **Binary Input RF** is considered, since **Counter SRAM** is increased. The entire procedure for the first part of the fc scheduling (discussed in section 4.1.2) ends when the value of **Counter SRAM** is equal to the number of output neurons, that in the neural network model depicted in Figure 4.1, it is 10. After that, the state **Increase fc** increases the value of **Count** fc, which allows to select another inputs/weights set, as reported in section 4.1.2. These computational steps are repeated for  $n_{iter} =$ 4.26 Example of flattening procedure. Each matrix represents a convolu-4.27 Example of a neural network top entity with  $c_{out} = 2$ ,  $c_{in} = 4$ . The hardware in the dashed border-line are included in the Neural network top entity. This scheme is valid for both OOM and In-Memory architecture  $\ldots \ldots 192$

##

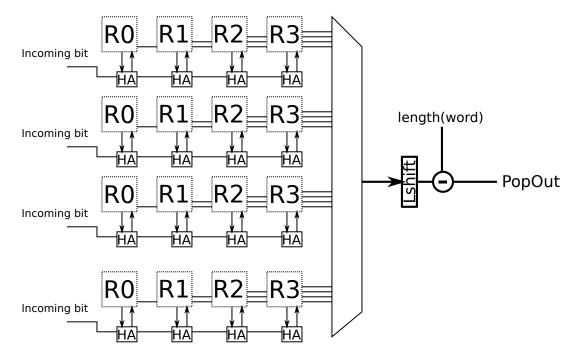

| 4.30 | Example of XNOR in memory with $w_{in} = 4$ , $w_{filter} = 2$ and $W = 4$ . |

|------|------------------------------------------------------------------------------|

|      | For each memory cell there is a XNOR gate that computes the xnor             |

|      | between the binary weights (first row) and the corresponding binary          |

|      | inputs. At the end of each row (excluding the first one reserved to          |

|      | the binary weights), there is a multiplexer which selects the Incoming       |

|      | bit as discussed in the <u>OOM</u> implementation. For each incoming bit     |

|      | there is a pop-counting unit and each pop-output is selected by a final      |

|      | multiplexer                                                                  |

| 4.31 | Example of an in-memory convolutional layer architecture with $c_{in} =$ |    |

|------|--------------------------------------------------------------------------|----|

|      | 4 and $c_{out} = 220$                                                    | 08 |

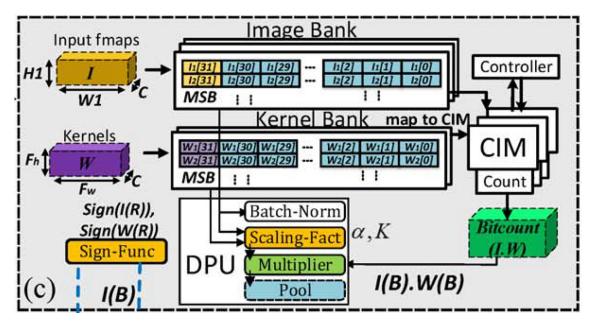

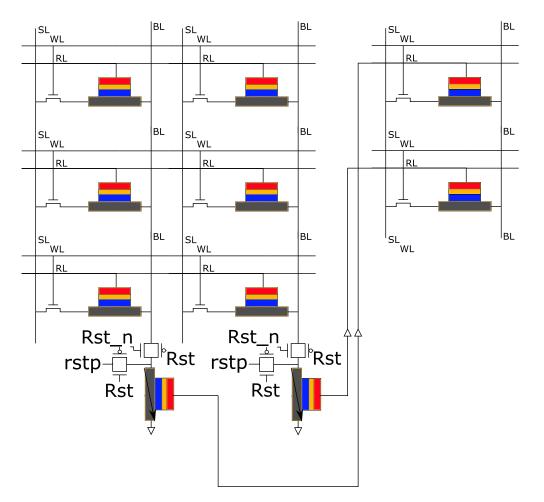

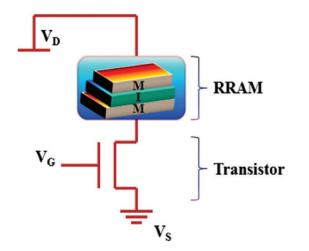

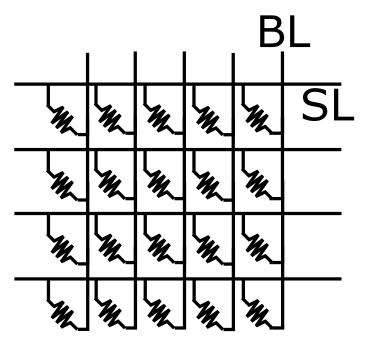

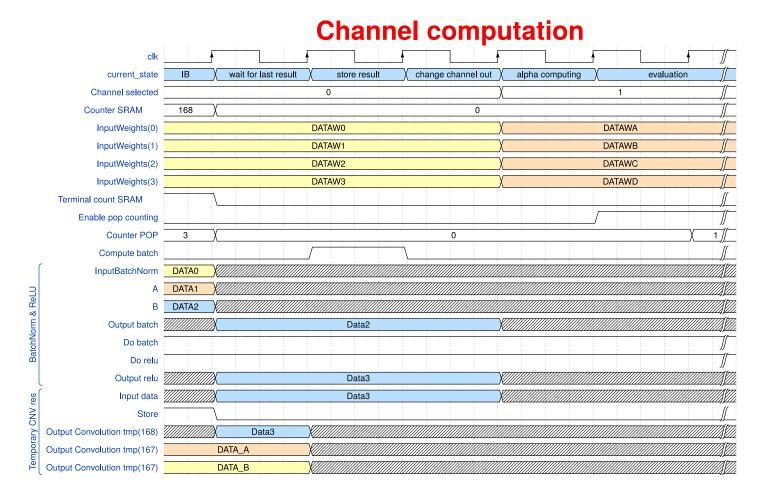

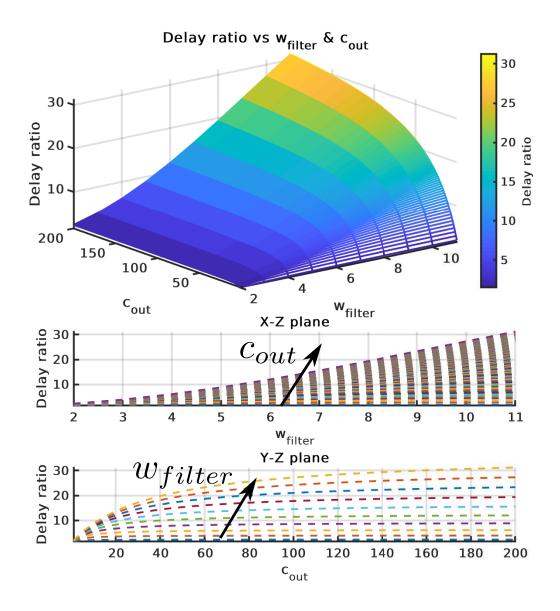

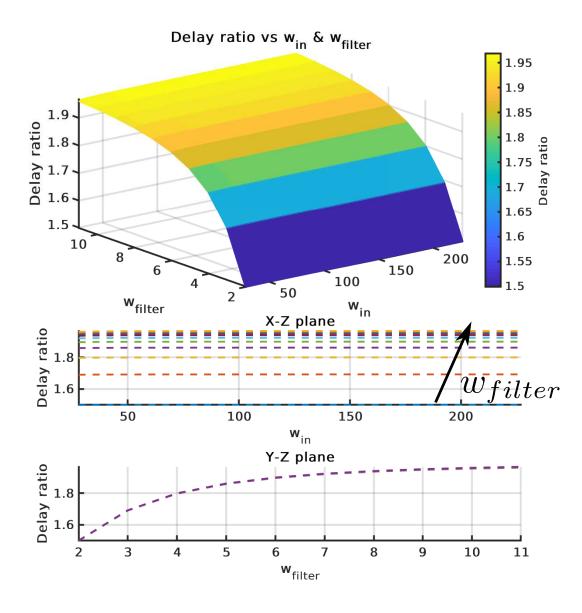

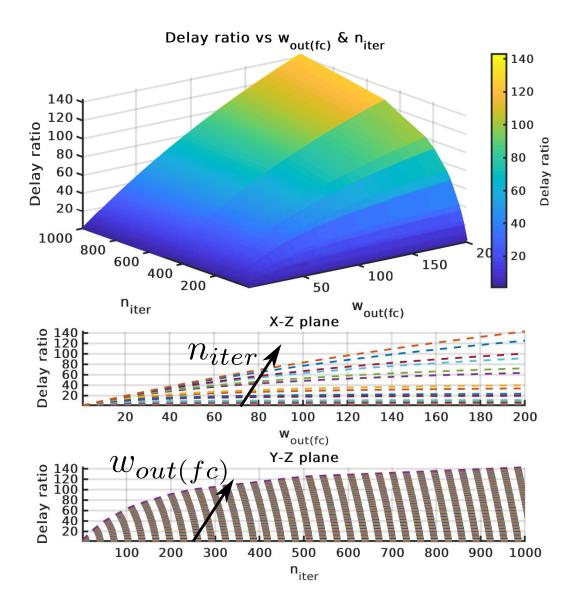

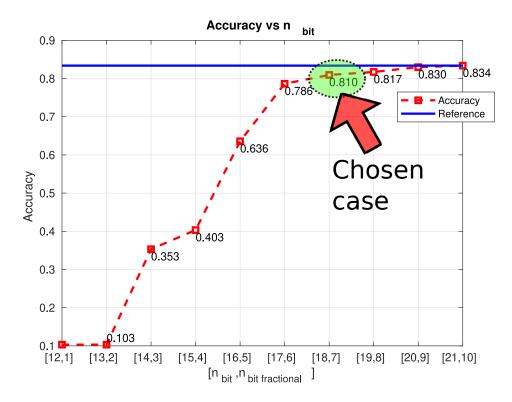

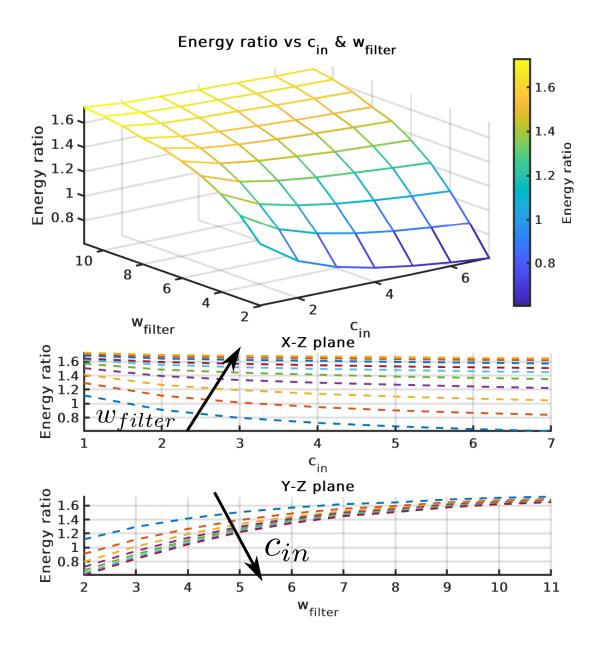

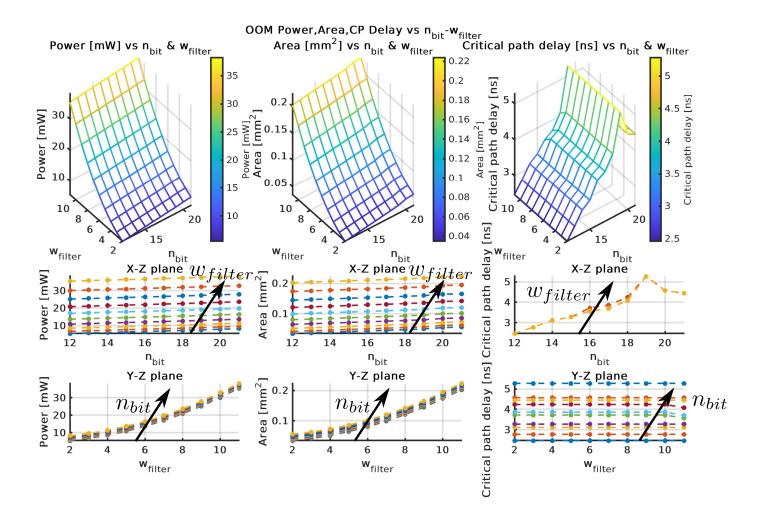

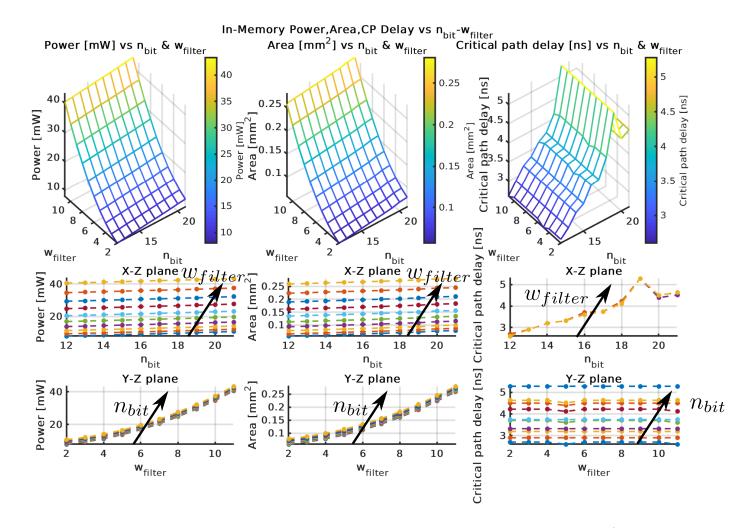

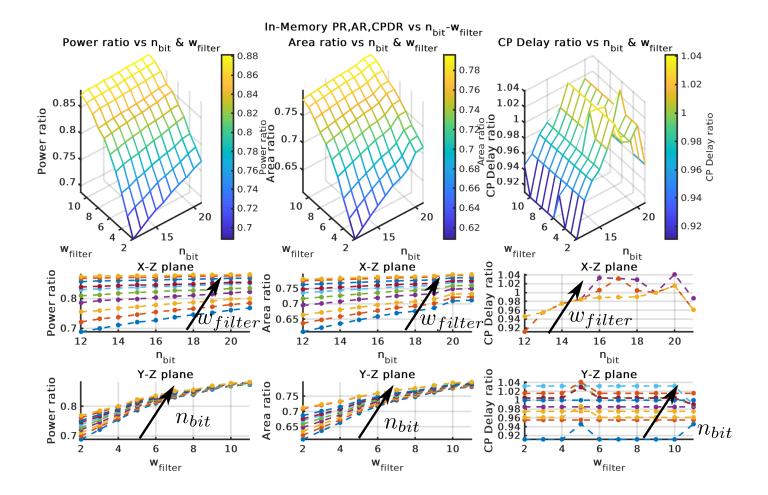

- 4.33 Timing diagram of convolution computation in the In-Memory architecture. Starting from Weights precharge (WP), the binary weights are precharged inside the first row of the **XNOR UNIT**. During **Initial stage**, K computation starts requiring  $w_{filter}^2$  clock cycles. Binary inputs are precharged inside the memory array during **Input precharge** (IP), in which also the **Counter SRAM** is increased. During evaluation,  $\alpha$  starts and the pop-counting results will be computed in parallel, requiring  $w_{filter}^2$  clock cycles: this is the most important difference respect to OOM architecture, in which the evaluation process has to be repeated for each output (Figure 4.23). After pop-counting has finished, **output computation** (OC), **batch normalization** (BN) and **ReLU** computations are performed and repeated for each output. In Change CNV Res (CNV), the count mux out is increased and the final multiplexer in Figure 4.30, addresses another output. The procedure finishes when **count mux out** is 168 and, at this point, the second weight set is selected,  $\alpha$  is computed again and the FSM restarts with **evaluation** (EV). . . . . 211