## Omar Sakr

# Master's of Nanotechnologies for integrated circuits 2017/2018

## NXP Semiconductors 45 allée des ormes, Mougins, 06250

## i.MX8 clock and power management

from 19/02/2018 to 17/08/2018

Under the supervision of:

- Company supervisor: Olivier Milou

- Phelma Tutor: Lorena Anghel

email: <u>olivier.milou@nxp.com</u>

email: lorena.anghel@grenoble-inp.fr

Confidentiality: yes

Ecole nationale supérieure de physique, électronique, matériaux

#### Phelma

Bât. Grenoble INP - Minatec 3 Parvis Louis Néel - CS 50257 F-38016 Grenoble Cedex 01

Tél +33 (0)4 56 52 91 00 Fax +33 (0)4 56 52 91 03

http://phelma.grenoble-inp.fr

## Abstract

The i.MX8 is a series of NXP applications processors mainly dedicated for automotive applications. The architecture of these processors involves having in each subsystem a clock generator block, called Distributed Slave Controller (DSC). Currently, the DSC is hardened in the design and contains many hardened modules at different hierarchical level, which is suspected to induce high clock latency of the block and leads to performance limitation and leakage and dynamic power increase. So, the aim is to redesign the DSC with a different strategy to decrease the latency. As a first step, the slices, which are the clock dividers in the DSC, were redesigned completely flat without any hardening. Then they were implemented directly in the CCI subsystem (taken as an example) with another module as hard Macros and the rest of the DSC was flattened. As a result of this new design strategy, the latency decreased by the 30%. Therefore, the leakage power decrease by 50% for the slices and 10% for the subsystem and the area decreased by 15% for the slices and 7.5% for the CCI.

L'i.MX8 est une famille de processeurs de NXP principalement dédiés au domaine de l'automotive. L'architecture de ses processeurs met en place un block générateur des signaux d'horloge, appelé Distributed Slave Controller (DSC). Actuellement, le design du DSC est implémenté comme Hard Macro et il en contient beaucoup à différents niveaux hiérarchiques, ce qui induit une latence d'horloge élevée et entraine par conséquent une limitation de performance et augmente la fuite de puissance ainsi que la consommation dynamique. Alors le but du stage est de refaire le design du DSC avec une stratégie différente pour diminuer la latence. En première étape, les blocks diviseurs d'horloge sont refaits complètement à plat sans aucune Hard Macro. Ensuite, ils

sont implémentés directement dans le sous-système CCI (Pris comme exemple) avec un autre module en tant que Hard Macro et le reste du DSC est mis à plat. Grace à cette nouvelle stratégie, la latence a diminué de 30%. Par conséquent, la fuite de puissance a diminué de 50% pour les diviseurs et de 10% pour le sous-système. L'aire a diminué de 15% pour les diviseurs et de 7.5% pour le CCI.

L'i.MX8 è una famiglia di processori prodotti da NXP, principalmente utilizzati nelle applicazioni in ambito automotive. L'architettura di questi processori fa si che in ogni sottosistema vi sia un blocco per generare il clock, chiamato Distributed Slave Controller (DSC). Attualmente il DSC è implementato tramite una macro a diversi livelli gerarchici, ciò introduce un'elevata latenza nel segnale di clock del blocco con un conseguente peggioramento delle prestazioni in termini di performance e potenza. L'obiettivo è di ridisegnare il DSC con una strategia diversa per ridurre la latenza. Come primo passo, gli "slices" che dividono il clock nel DSC, sono state riprogettati completamente senza l'utilizzo di macro. Successivamente sono stati implementati direttamente nel sottosistema CCI (utilizzato come campione) inglobando la logica del DSC nel sottositema con la nuova versione degli "slices". Come risultato di questa nuova strategia di progettazione, la latenza è diminuita del 30%, la dissipazione in termini di potenza si è ridotta del 50% per gli "slices" e del 10% per il sottosistema con un decremento dell'area pari al 15% per i primi e del 7,5% per il modulo CCI.

## Acknowledgements

Before getting into the details of the work I did for 6 months, I would like to thank the people whom help made this experience happens in the best way that allowed me to evolve and learn.

Many thanks go to my NXP tutor, Olivier MILOU, senior design engineer, for all the things he taught me during my internship, for all the advises he gave me and his well guidance of the project. I would like to thank him also for his patience in answering to all my questions and for all his explanations. Besides I appreciate his help in my integration to the team.

I thank also Fabien JUMEL, the SOC design team manager, for recruiting me for this internship and for giving me the chance to have this great experience that will be a main building block of my professional career. I am also grateful for his advises on different phases and deliverables of the project.

I would like to thank a lot all the members of the backend design team, first for integrating me and making me feel a real part of the team, second for their help on the technical issues, their explanations and to allow me to learn from their expertise and their experiences.

I am thankful also for my all colleagues at NXP for the welcoming and joyful atmosphere in which I worked during the past 6 months. It has been a remarkable period for me.

I thank also Professor Lorena ANGHEL for her time to review and follow-up with me on my work and her remarks on the report.

## **Table of Contents**

| 1. | Ι   | ntro  | oduct | tion                                            | 4  |

|----|-----|-------|-------|-------------------------------------------------|----|

|    | 1.1 |       | NXP   | semiconductors                                  |    |

|    | 1.2 |       | i.MX  | 8 microcontrollers                              |    |

|    | 1.3 |       | Inter | rnship objective                                | 6  |

|    | 1.4 |       | Proj  | ect Schedule and Gantt diagram                  | 7  |

| 2. | Γ   | DSC   | arch  | itecture                                        |    |

| 3. | S   | Sing  | le sm | nall asynchronous clock divider slice (ssslice) |    |

|    | 3.1 |       | RTL   | Analysis                                        |    |

|    | 3   | 3.1.1 | •     | dsc_clkctrl_gcm5                                |    |

|    | 3   | 3.1.2 |       | Dsc_clkctrl_ctrl                                |    |

|    | 3   | 3.1.3 |       | Dsc_clkctrl_div                                 |    |

|    | 3   | 8.1.4 | •     | Parts_clkctrl_divgen                            | 13 |

|    | 3.2 |       | Perf  | ormance assessment                              | 13 |

|    | 3.3 |       | Phys  | sical views                                     | 15 |

| 4. | S   | SSSli | ce sy | ynthesis                                        |    |

|    | 4.1 |       | Synt  | hesis characteristics                           |    |

|    | 4.2 |       | Afte  | rmath checks                                    | 20 |

| 5. | S   | SSSli | ce Pl | lace and Route                                  | 21 |

|    | 5.1 |       | Desi  | gn characteristics                              | 21 |

|    | 5.2 |       | Post  | -layout checks                                  | 25 |

|    | 5.3 |       | Timi  | ing ECO                                         | 27 |

| 6. | F   | Flatt | ened  | 1 DSC                                           | 29 |

|    | 6.1 |       | Mor   | e Improved Ssslice                              | 29 |

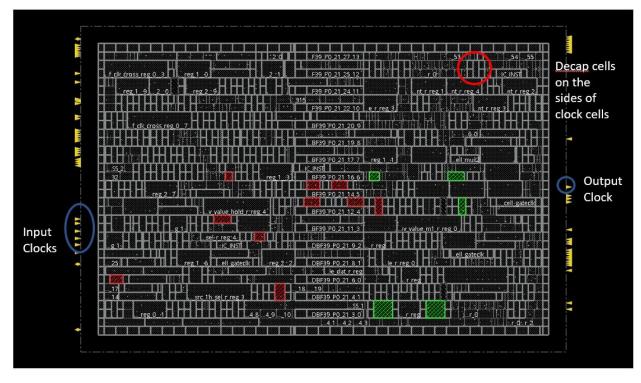

|    | 6   | 5.1.1 | •     | Pre-placed clock cells                          | 29 |

|    | 6   | 5.1.2 |       | Smaller Ssslice                                 |    |

|    | 6.2 |       | Slsli | ce design                                       |    |

|    | 6.3 |       | Msli  | ce design                                       |    |

|    | 6.4 |       | Integ | gration in CCI                                  |    |

|    | 6   | 5.4.1 | •     | CCI Introduction                                |    |

|    | 6.4.2 | 2. New design              | 7 |

|----|-------|----------------------------|---|

|    | 6.4.3 | 3. Performances Assessment | 9 |

| 7. | Con   | clusion41                  | 1 |

|    | 7.1.  | Technical Conclusion       | 1 |

|    | 7.2.  | Personal feedback          | 2 |

| 8. | Refe  | rences43                   | 3 |

## List of figures

| Figure 1: i.MX8 family architecture [3]                                                         | 5  |

|-------------------------------------------------------------------------------------------------|----|

| Figure 1: i.MX8 family architecture [3]<br>Figure 2: DSC hierarchical view of the main modules  | 8  |

| Figure 3: MSI bus ring [3]                                                                      | 9  |

| Figure 4: Hierarchical representation of the ssslice module. It represents all the included     |    |

| RTL modules                                                                                     | 10 |

| Figure 5: dsc_clkctrl_gcm5 module schematic (All the clocks are multiplexed with the            |    |

| srm_clk (scan/reset clock), but for the visibility they are replaced with black dots)           | 12 |

| Figure 6: parts_clkctrl_divgen schematic                                                        | 13 |

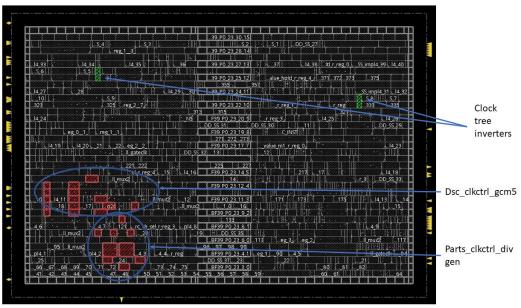

| Figure 7: Physical view of the dsc_clkctrl_gcm5 module showing the path of the clock pll_0      | 16 |

| Figure 8: Physical view of the ssslice module showing the path of the clock pll_0. (A circle is |    |

| the start point of a signal and a cross is its endpoint)                                        | 17 |

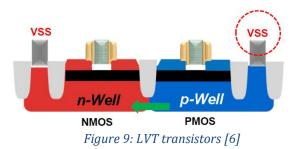

| Figure 9: LVT transistors [6]                                                                   | 18 |

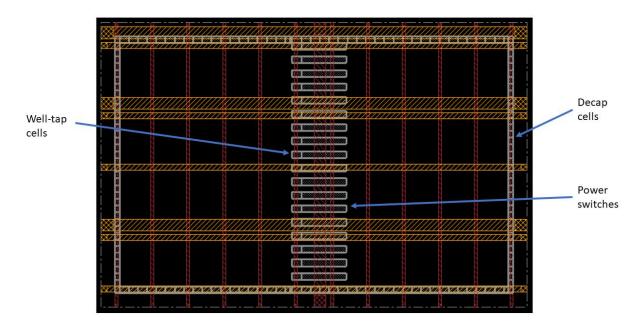

| Figure 10: ssslice floorplan                                                                    | 22 |

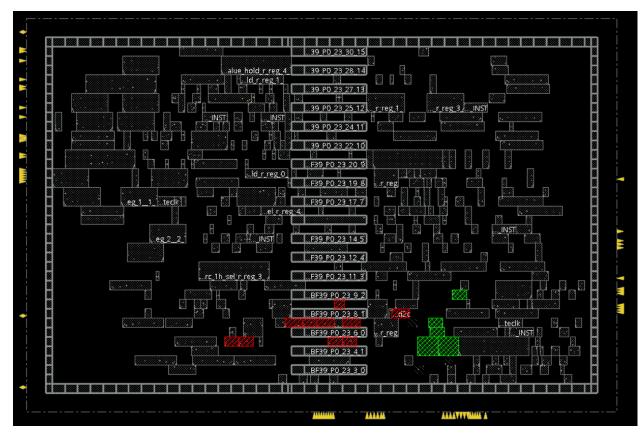

| Figure 11: ssslice after place step                                                             | 24 |

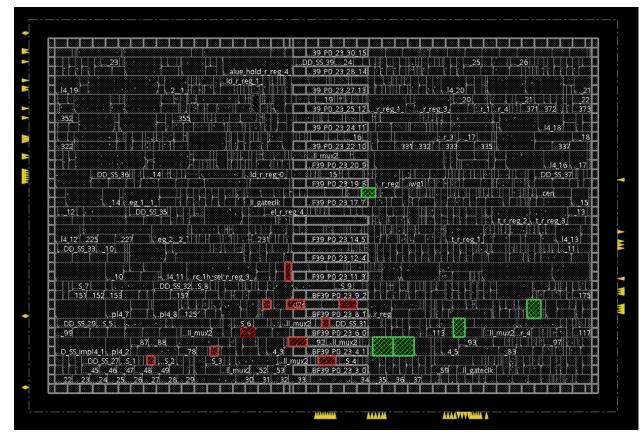

| Figure 12: ssslice final layout                                                                 |    |

| Figure 13: Ssslice layout with preplaced z_cells                                                | 30 |

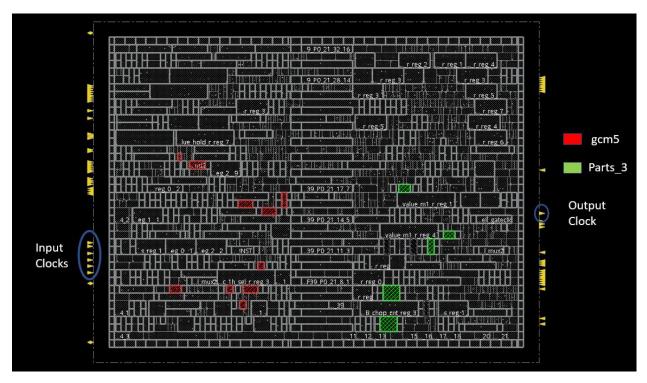

| Figure 14: ssslice final design implemented in the CCI                                          |    |

| Figure 15: slslice final design                                                                 | 33 |

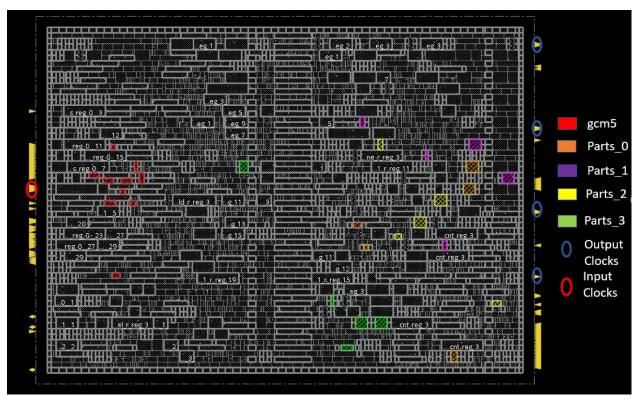

| Figure 16: mslice final design                                                                  | 35 |

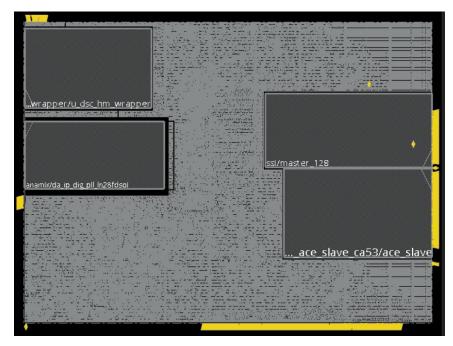

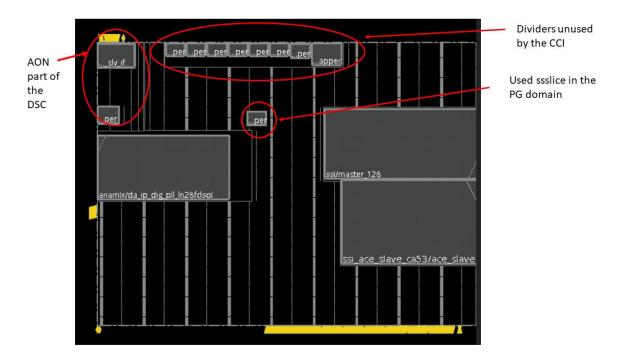

| Figure 17: CCI current physical layout                                                          | 36 |

| Figure 18: CCI new floorplan                                                                    |    |

## List of tables

| Table 1: Project schedule                  | 7 |

|--------------------------------------------|---|

| Table 2: Latency analysis results (in ns)  |   |

| Table 3: Power consumption results (in mW) |   |

| Table 4: Cells distribution                |   |

|                                            |   |

| Table 5: Defined clocks                                                          | 19 |

|----------------------------------------------------------------------------------|----|

| Table 6: Clocks latencies for flattened ssslice (ns)                             | 26 |

| Table 7: Power consumption for the flattened ssslice (mW)                        | 26 |

| Table 8: Latency results after timing eco (ns)                                   | 27 |

| Table 9: Power consumption after timing eco (mW)                                 | 27 |

| Table 10: Timing constraints with overdrive (OD) and underdrive (UD) definitions | 32 |

| Table 11: Performances summary of the new improved design                        | 32 |

| Table 12: Slslice analysis summary                                               | 34 |

| Table 13: Mslice latency results                                                 | 35 |

| Table 14: Mslice power results                                                   |    |

| Table 15: Analysis Results of actual CCI                                         | 39 |

| Table 16: Analysis results of redesigned CCI                                     | 40 |

|     | Abbreviations                |

|-----|------------------------------|

| RTL | Register Transfer Language   |

| STA | Static Timing Analysis       |

| DRV | Design Rule Violation        |

| DRC | Design Rule Check            |

| AON | Always ON                    |

| PG  | Power Gated                  |

| LVS | Layout Versus Schematic      |

| ECO | Engineering Change Order     |

| DSC | Distributed Slave Controller |

| SCU | System Control Unit          |

| MSI | Medium Speed Interface       |

| PnR | Place And Route              |

| CCI | Cache Coherence Interface    |

| CTS | Clock Tree Synthesis         |

## 1. Introduction

#### 1.1. NXP semiconductors

NXP is a Dutch company which is a leader in the semiconductors field. It designs and manufactures a wide variety of products in the application areas of connected cars, security, wearable electronics and Internet of Things (IOT). The company has 31,000 employees in more than 33 countries and a posted revenue of \$9.5 billion in 2016. [1]

The internship was held in the French R&D site of Mougins. The main activities of the site are the design of microcontrollers with embedded microprocessors (mainly for automotive applications), security solutions based on NFC chips which targets online and wireless payment applications, and connectivity solutions with advanced protocols integrated on chips for IOT applications. The site has around 250 employees divided on 3 business units, each one of them works on a specific high-end application. The internship took place in the SOC back-end team of the MICR business unit which works on microcontrollers design. The team's role is to receive from the front-end team the RTL codes modeling the circuits to be designed at the behavioral level and to perform tasks going from synthesis to physical design, which results in transforming the codes into a physical layout that can be sent to the foundry for manufacturing. This process consists of many steps with various tools for either design or performance analysis (for power consumption, timing analysis, ...). The latter is important to make sure the design corresponds to the chip specifications.

#### 1.2. i.MX8 microcontrollers

The i.MX8 series of applications processors is a feature- and performance-scalable multi-core platform that includes single-, dual-, and quad-core families based on the Arm® Cortex® architecture including combined Cortex-A72 + Cortex-A53, Cortex-A35, and Cortex-M4 based solutions for advanced graphics, imaging, machine vision, audio, voice, video, and safety-critical applications.

i.MX8QM is a microcontroller that belongs to this family and is the subject of this internship project. It targets high end automotive and industrial market segments. It is built in 28 FDSOI leading edge technology to achieve both high performances and low power consumption [2].

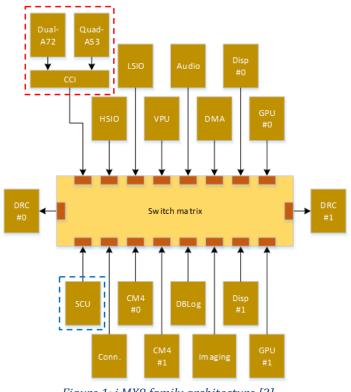

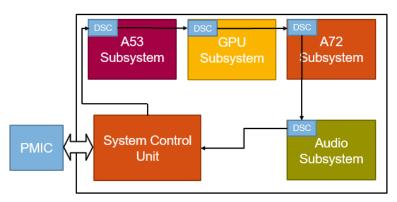

Each device of the family has one switch matrix where all subsystems are plugged-in, a SCU (System Controller Unit) which manages the subsystems of the device, up to 16x

subsystems (including SCU) and one/two DRAM controller(s). This architecture allows the devices to be scalable, as any subsystem can be replaced easily. This involves only disconnecting it from the switch matrix and connecting the new subsystem. This also gives an easiness in designing all the devices of the family. The SCU has an upper-hand control over the subsystems concerning boot, power, clock and reset management as well as resource partitioning / access control. All those mechanisms are abstracted thanks to a system control firmware running in the SCU. [3]

Each subsystem contains a block called the DSC (Distributed system controller). It provides power management and clock control to the subsystem. It is then the local controller used by the SCU to manage the different subsystems. The SCU interfaces with all the DSCs in the device through an MSI bus. The DSC embeds all the control logic to power up and power down domain(s) of a subsystem. It has reset register to control reset of power domain(s). It includes PLL(s) and clock dividers that provides source clocks to IP blocks of a subsystem according to the needs of the latter [3].

Figure 1: i.MX8 family architecture [3]

#### 1.3. Internship objective

The main objective of the internship is the analysis and the optimization of the DSC block. The DSC is an important IP for the company for different reasons. First, it has been used in all the i.MX8 chips. Second, it is used in all the subsystems, which means it has a global effect on the whole chip. And last, it has a critical role from a functional point of view. It is responsible for clock generation to all the subsystems, which means it directly affect the performance/speed and the total power consumption of the chip. Therefore, the optimization of the DSC is an important issue for the future projects of the business unit.

The main issue of the actual design of the DSC is the high clock latency between the input and the output, which means the time between the arrival of clock rising edge to the DSC and the generation of an equivalent rising edge is too high. Decreasing the DSC's latency will lead to enhancing the performance of the subsystems and will allow them to run faster. In addition, optimizing the clock latency results in a decrease of the number of hold violations created on the subsystem level, which leads to a decrease of hold buffers needed at the subsystem level to fix hold violations and thus decreases the subsystem consumption. As the DSC is contained in all the subsystems, this decrease leads to an overall decrease of the number of violations leads to less work in the subsystems design and a shorter development time, which is not a negligible benefit. These elements further explain why this internship subject is important for the company.

The suspected technical reason behind the high latency of the DSC is the use of too much hardening in its design. Hardening means that some modules are processed by the full backend design flow (synthesis and place & route), then they are implemented as a one-unit cell in the higher level of hierarchy (like the technology library cells). This is then repeated at different level of the hierarchy of the DSC. This strategy is suspected to prevent the backend design tools from optimizing the timing, which results in the high latency. The objective of the internship is then the analysis of these modules to understand the relevance of this hardening and to adopt different design strategies to decrease the latency of the DSC.

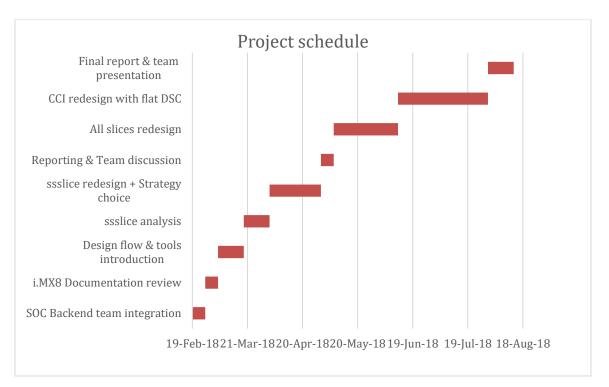

#### 1.4. Project Schedule and Gantt diagram

#### Table 1: Project schedule

| Steps                              | Start     | Duration<br>(Days) |

|------------------------------------|-----------|--------------------|

| SOC Backend team integration       | 19-Feb-18 | 7                  |

| i.MX8 Documentation review         | 26-Feb-18 | 7                  |

| Design flow & tools introduction   | 5-Mar-18  | 14                 |

| ssslice analysis                   | 19-Mar-18 | 14                 |

| ssslice redesign + Strategy choice | 2-Apr-18  | 28                 |

| Reporting & Team discussion        | 30-Apr-18 | 7                  |

| All slices redesign                | 7-May-18  | 35                 |

| CCI redesign with flat DSC         | 11-Jun-18 | 49                 |

| Final report & team presentation   | 30-Jul-18 | 14                 |

Note: There is no cost evaluation included in the report. This stems from the fact that the project didn't require any physical material. The only material used are the computer software used for design and checks. So, the cost can be related to the licenses used. However, it is irrelevant to use the licenses price to evaluate the cost as these licenses are already used by all the engineers of design teams in different sites.

## 2. DSC architecture

As previously stated, the DSC acts as an interface between the system controller unit (SCU) and each individual subsystem. It provides clocks, power control and some additional functions which may be managed by firmware running on the system controller function which in turn interfaces to software. [4]

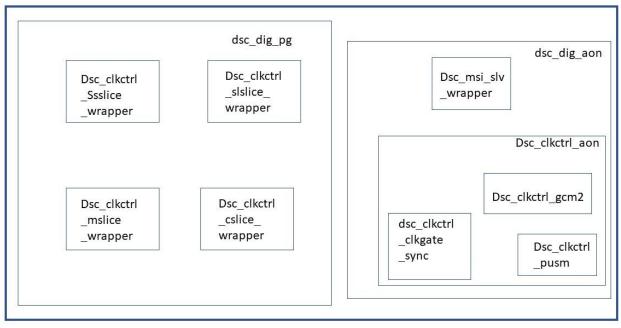

As **Figure 2** shows, the DSC consists of two main blocks entitled dsc\_dig\_aon and dsc\_dig\_pg. The dsc\_dig\_aon represents the always-on part (AON), which is always supplied with power. It is implemented to ensure that the SCU keeps its control over all the DSCs of the different subsystems, even if one of the DSCs is switched off with its subsystem shut-down. This is required as the connection between the DSC and the SCU is implemented as a ring of MSI (Medium Speed Interconnect) bus showed on **Figure 3**, thus this ring needs to always function.

Figure 2: DSC hierarchical view of the main modules

Page | 8

#### Figure 3: MSI bus ring [3]

The dsc\_dig\_pg consists of the power gated part, which can be switched off when needed. It is the biggest part of the DSC. It is responsible of the clock management, which is the main function of the DSC. It contains the clock dividers responsible for generating the required frequencies to the subsystem according to some input control signals translating the timing requirements of the subsystems. These dividers are entitled ssslice for single short slice, slslice for single long slice, mslice for multiple slice and the cslice for cpu slice. The cslice is providing clocks to the cpu and is different and is used only by one subsystem. The other slices contain the same modules and differ only by the number of instantiations of these modules. The slslice provides higher division rate than the ssslice and the mslice contains internal multiple dividers and is then capable to produce multiple clocks synchronous to each other.

## 3. Single small asynchronous clock divider slice (ssslice)

After analyzing the global architecture of the dsc, it was decided to focus on one clock divider module. This stems from the fact that the different dividers are the main highlevel modules of the power gated domain of the dsc. All the dividers (except the cslice) consist of the instantiation of the same module which represent the core of the dividers. They differ only by the value of the instantiation parameters specifying the number of dividers included, the width of the chopper and the highest division value possible, which makes analyzing the architecture of one divider enough to understand how they work. At the same time, it can be expected that optimizations done on the ssslice will also be beneficial for the other dividers. Under these facts, the ssslice has been chosen as it is smaller and so it is more practical to be run with the different flows. So, it is good to work on as a starting point.

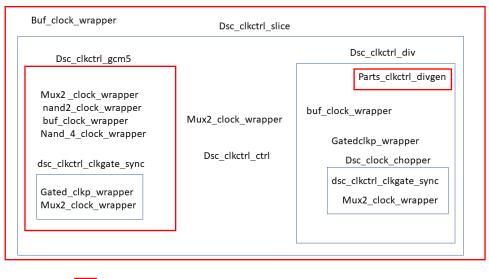

Dsc\_clkctrl\_ssslice\_wrapper

Legend: Hardened modules in the backend flow

Figure 4: Hierarchical representation of the ssslice module. It represents all the included RTL modules

#### 3.1. RTL Analysis

The RTL codes of the different modules consisting the ssslice were analyzed to understand the functional behavior of the module and to understand its architecture. This is a key point to understand the current design. The hierarchy of these modules is presented on **Figure 4** and the main ones are presented below.

#### 3.1.1. dsc\_clkctrl\_gcm5

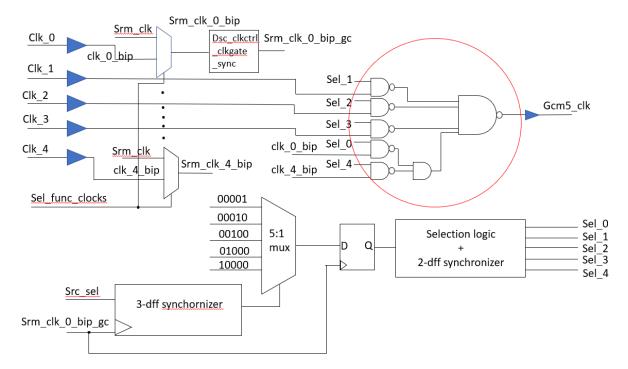

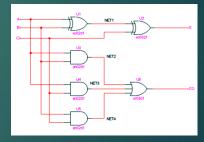

This module has the function of a 5-to-1 glitch-less multiplexer. It allows a safe switching between the 5 input clocks of the dsc, which are 3 pll clocks, the 24 MHz crystal clock (xtal24m clk) and the bypass reference clock (byp ref clk). However, the module is designed in a generic way with respect to the clocks, which means no special considerations in the design were made for one of the clocks. It allows also the selection of the reset or the scan clock to flow in the design when needed. The clock is muxed at the input of the module with every other clock. It is one of the hardened modules inside the ssslice. As Figure 5 shows, the module transforms the 3-bits input selection signal (src sel), which is first synchronized through 3 dff, into a one-hot code to select one of the five input clocks. According to this code, a logic block turns on only one selection signal which is synchronized to the clock to be selected through 2 dff (same for the turned off selection signals). The Nands block, having as input the input clocks and the internal selection signals generates the right output clock. This block is the main reason of the hardening of the module, as during the design, it was found that physically distancing these Nand gate induces a duty cycle degradation. As a result, a design decision was made to physically approach the gates and then to harden the module to deal with this point only once during the backend design of the DSC.<sup>1</sup> A clock gate is implemented in the module to gate off clk 0 when the reset is asserted, because otherwise the reset of the synchronization dff forces the selection of clk 0 at the 5:1 multiplexer.

Page | 11

<sup>&</sup>lt;sup>1</sup> This information was confirmed by the frontend designer of the DSC during a call.

Figure 5: dsc\_clkctrl\_gcm5 module schematic (All the clocks are multiplexed with the srm\_clk (scan/reset clock), but for the visibility they are replaced with black dots)

#### 3.1.2. Dsc\_clkctrl\_ctrl

This module manages all the controlling signals of the divider. It transforms the firmware, hardware and software enabling signals coming to the ssslice to **Dsc\_clkctrl\_div** as one "enable" signal respecting the specifications of these signals. In addition, it checks if the divider has already an ongoing division operation before passing the new synchronized division value to the divider. It also synchronizes all the signals to the selected clock to make sure no glitches are generated.

#### 3.1.3. Dsc\_clkctrl\_div

This module implements the actual divided clock generator **Parts\_clkctrl\_divgen**. It contains also the logic that feeds it according to the division factor and the enable signals. Through this logic, it allows the divider to count the rising edges (and the falling edges in the case of an odd division factor) of the input clock. It makes sure the division factor change is only taken in account when the divider finishes any ongoing division operation. The module has also a clock gate that turns off the output clock when the enable signal coming from **Dsc\_clkctrl\_ctrl** is 0.

Page | 12

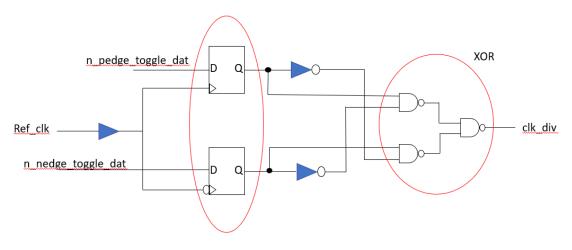

#### 3.1.4. Parts\_clkctrl\_divgen

It is the second hardened module in the ssslice. Its function is the generation of the output divided clock. Using a rising edge DFF and a falling edge DFF whose outputs are xor-ed using 2-input nand gates (to minimize the skew), it generates a 50% duty cycle divided clock. These DFF are clocked using the selected clock at the output of the dsc\_clkctrl\_gcm5. Their inputs are controlled by the logic in **Dsc\_clkctrl\_div** so that n\_pedge\_toggle\_dat toggles for any division factor, but n\_nedge\_toggle\_dat toggles only for an odd one (to generates the 50% duty cycle), otherwise it remains 0. As for the dsc\_clkctrl\_gcm5, the module is hardened to physically approach the Nand gates forming the XOR gate and the division flip-flops, which are circled in red on **Figure 6**, in order to protect the duty cycle of the clock from degradation (same as in dsc\_clkctrl\_gcm5).

Figure 6: parts\_clkctrl\_divgen schematic

#### 3.2. Performance assessment

The current performances of the ssslice were evaluated to have a reference point for the following optimization steps of the project. Some parameters were defined to be the evaluation parameters: latency of the divider between the input clock and the output (the main inconvenient of the actual dsc), the duty cycle degradation, the power consumption and the cells distribution. The goal is to optimize the latency without negatively affecting the power consumption nor the area. To analyze these parameters, a STA (static timing analysis) was run using cadence tempus tool at the post-route stage. (An STA is computation method which "determines worst case arrival time of signals at all pins of design elements", without test functionality [5]). Seven different design corners were run, but only the worst results are reported below. Design corners takes in account PVT

(Process, Voltage, Temperature) variations. Each corner models the cells timing values and power consumption differently depending on the environment characteristics. Their use allows to have a better estimation of the circuit behavior in the design stage.

| Clock   | Byp_ref | PII_0 | PII_1 | PII_2 | xtal24m |

|---------|---------|-------|-------|-------|---------|

| Latency | 0.575   | 0.537 | 0.551 | 0.529 | 0.574   |

Table 2: Latency analysis results (in ns)<sup>2</sup>

Concerning the latency, the worst results were obtained for the corner (worst case: 0.9V, -40 °C, cmax). The latency was computed as the propagation time of a positive edge from the clock input ports to the output clock port (ssslice\_clkdiv). The latency analysis required defining an output delay on a data output port, which led the tool to report the latency as the clock insertion delay in the timing report concerning this data port.

To measure the duty cycle degradation, the difference between the highest rise time and the lowest fall time as well as the lowest rise time and the highest fall time. The highest number represents the worst duty cycle degradation and was represented as a percentage of the clock period. The worst results, obtained for the corner (worst case: 0.9V, -40 °C, cmax), were 13.39% for pll\_0 clock and 14.04% for byp\_ref clock. These values were measured at the output clock port of the ssslice.

For the power analysis, the default "report\_power" command of tempus was used. The worst results were obtained for the corner (best case: 1.1V, 125 °C, rcmax). The analysis was done with the default tempus parameters which won't change later to have a fixed reference for the power analysis. The most relevant data is the leakage power as it comes from an accurate calculation related to the cells characteristics.

| Table 3: Power | consumption | results (in mW) |  |

|----------------|-------------|-----------------|--|

|                |             |                 |  |

| Internal | Switching | Leakage | Total |

|----------|-----------|---------|-------|

| power    | power     | power   | power |

| 0.437    | 0.3742    | 0.2129  | 1.024 |

<sup>&</sup>lt;sup>2</sup> All shown results are obtained for nominal timing constraints that are also used for constraints (see Table 5).

Page | 14

#### Table 4: Cells distribution

|              | PO  | P4 | P10 | P16 |

|--------------|-----|----|-----|-----|

| Clock        | 74  | 22 | 0   | 5   |

| Not<br>clock | 68  | 74 | 42  | 295 |

| Total        | 142 | 96 | 42  | 300 |

Through a script, the cells distribution was deduced from the post-route netlist. The result on **Table 4** divide the cells into clock and not clock cells to have the correlation between this distribution and the timing performance of the design. This distribution invokes also the type of the cell (P0, P4, P10, P16). Each cell in the technology library has four types. All have the same sizes, but the decrease of the figure following the P means an increase of the cell speed but also of its power consumption. It relates physically to the change of the threshold voltage Vt of the transistors in the cell (decrease of Vt => faster cell). Swapping between the different "P" is then efficient to easily enhancing the design performances or fixing timing problems. This table is reported as moving to high P values is better, so it can be used to compare the designs.

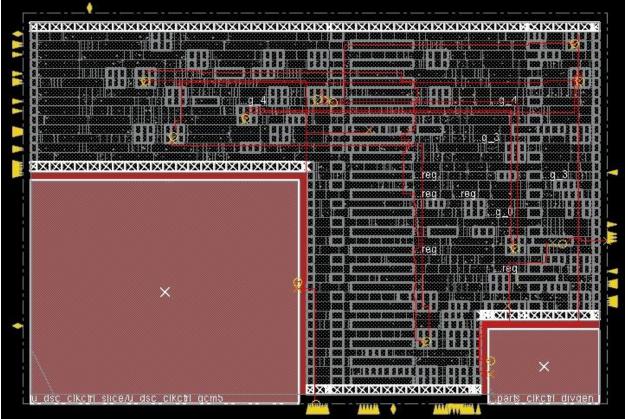

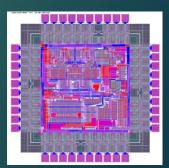

#### 3.3. Physical views

As the main remark made on the dsc is the efficiency of the hardening of certain modules inside the block, a physical view of the ssslice was retrieved from innovus cadence tool (**Figure 8**) to investigate this remark. The **Figure 7** shows the physical view of the dsc\_clkctrl\_gcm5 module being the biggest hard marco in the ssslice. On both figures, the path of the clock pll\_0, through all the nets from the input to the output, is highlighted.

As a conclusion of the analysis, the clock path in the ssslice and in the dsc\_clkctrl\_gcm5 is too complex. The latency being the main issue of the current dsc, this path should be optimized. This advantages flattening the ssslice to try to optimize the path in its globality to avoid adding complexity by internally hardening modules. This is supported by the fact that the hardened modules consist of  $z_cells^3$ , which means they are all conserved through the backend flow. In addition, the physical views don't show any

<sup>&</sup>lt;sup>3</sup> Z\_cells are technology library cells which are directly instantiated in the RTL codes and which should be kept during the whole backend flow. Their instances names start with the prefix z\_cell.

special steps made for the place and route. As a result, designing the ssslice without any hard-macros will help the place and route (PnR) tool to better place the cells to optimize the latency. This should be done while keeping the gates mentioned on chapters **3.1.1** and **3.1.4** physically close to protect the duty cycle from degradation.

| × 🚓 🚓 🦗 🗛 ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | × et a et a             | No 80                  | <u> A A A</u>    | * *                    | <u>60 66 6</u>      | 52 🔬 🛛           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|------------------|------------------------|---------------------|------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>, 11</u>             | 265                    | 268jn_1          | 269 <u>  buf</u>       | ,                   | mux2             |

| 251                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _253                    | LVT_34                 |                  |                        | <b>-</b>            |                  |

| 239240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |                        | LVT_32           |                        | 247,248             | i jeni           |

| src_1h_sel_r_reg_1 g613                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | etn                     |                        | LVT 30           | LI F                   | 234235              | 236              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>T9</u> _216          | FILLECO LVT            | 29 .1 buf21      | 8                      | 220 221             |                  |

| 204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>C0_scan_sh</u>       | <u>it_in_1</u>         |                  | Aross_reg_0            | LVT_28              | 206              |

| 185                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>T 8</u>              | <u>. 191, LVT_</u>     | 26               | <u>.T_27</u>           | 196                 | 2 <mark>1</mark> |

| g612 . 173 .cg/z_cell_gatecik                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SE 200000000 2000 20000 | _sel_r_reg_3           | LVT_24           | 178                    | 179                 | 1; <u>2</u>      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         | 1_clk_cross_re         | g_0 .LVT_22      | .1_0_clk_cross_1       | eg_0 <u>k169k.</u>  | 170 7            |

| src_1h_sel_r_reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         | <u>  157 c</u>         |                  | sel_0_clk_cros         | <u>s_reg_1T_21</u>  | . 50             |

| 133134 <u>GIC_INST</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         | lk_cross_reg_0         |                  | LVT_19                 |                     | 1.7.             |

| 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |                        | and2a LVIII      |                        |                     | <u>. 107</u>     |

| 106    , LVT_15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>T5</u>               |                        | IK_ross_reg_1.se |                        |                     | 1 3 114          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 597 g411 ross           | s_reg_ <i>1</i> 1.1_96 | LVT_13           |                        |                     |                  |

| src_1h_sel_r_reg_2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         | γ^∧_+                  | <u>LVT 11</u>    |                        | _861 <u>1_8711</u>  | 50               |

| src_1h_sel_r_reg_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         |                        |                  | LVT_9_1                |                     |                  |

| g600 gate1 g | T 3 1 52                |                        | stan_shft_in_0   | Salataration Stationer | 1 58 1 59           |                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6 LVT                   | LVT 3 n                |                  | clk_cross_reg          |                     |                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |                        |                  |                        | 1 1 25<br>1 cell mu |                  |